Page 1

CommandLineToolsUser Guide

(FormerlytheDevelopmentSystemReferenceGuide)

UG628(v13.1)March2,2011

Page 2

Xilinxisdisclosingthisuserguide,manual,releasenote,and/orspecication(the“Documentation”)toyou

solelyforuseinthedevelopmentofdesignstooperatewithXilinxhardwaredevices.Youmaynotreproduce,

distribute,republish,download,display,post,ortransmittheDocumentationinanyformorbyanymeans

including,butnotlimitedto,electronic,mechanical,photocopying,recording,orotherwise,withouttheprior

writtenconsentofXilinx.XilinxexpresslydisclaimsanyliabilityarisingoutofyouruseoftheDocumentation.

Xilinxreservestheright,atitssolediscretion,tochangetheDocumentationwithoutnoticeatanytime.Xilinx

assumesnoobligationtocorrectanyerrorscontainedintheDocumentation,ortoadviseyouofanycorrections

orupdates.Xilinxexpresslydisclaimsanyliabilityinconnectionwithtechnicalsupportorassistancethatmaybe

providedtoyouinconnectionwiththeInformation.

THEDOCUMENTATIONISDISCLOSEDTOYOU“ AS-IS”WITHNOWARRANTYOFANYKIND.XILINX

MAKESNOOTHERWARRANTIES,WHETHEREXPRESS,IMPLIED,ORSTATUTORY,REGARDING

THEDOCUMENTA TION,INCLUDINGANYW ARRANTIESOFMERCHANTABILITY,FITNESSFORA

PARTICULARPURPOSE,ORNONINFRINGEMENTOFTHIRD-PARTYRIGHTS.INNOEVENTWILL

XILINXBELIABLEFORANYCONSEQUENTIAL,INDIRECT,EXEMPLARY ,SPECIAL,ORINCIDENTAL

DAMAGES,INCLUDINGANYLOSSOFDATAORLOSTPROFITS,ARISINGFROMYOURUSEOFTHE

DOCUMENTA TION.

©Copyright2002-2011XilinxInc.AllRightsReserved.XILINX,theXilinxlogo,theBrandWindowandother

designatedbrandsincludedhereinaretrademarksofXilinx,Inc.Allothertrademarksarethepropertyoftheir

respectiveowners.ThePowerPCnameandlogoareregisteredtrademarksofIBMCorp.,andusedunderlicense.

Allothertrademarksarethepropertyoftheirrespectiveowners.

RevisionHistory

Thefollowingtableshowstherevisionhistoryforthisdocument.

Date

03/01/2011

03/02/2011

Version

13.1downloadAddinginformationforXilinx®7seriesFPGAdevices.

13.1WebreleaseAdditionalupdatesforXilinx7seriesFPGAdevices.

2w

w w . x i l i n x . c o m UG628(v13.1)March2,2011

CommandLineToolsUserGuide

Page 3

TableofContents

RevisionHistory....................................................................................................2

Chapter1Introduction.................................................................................................9

CommandLineProgramOverview......................................................................9

CommandLineSyntax.........................................................................................10

CommandLineOptions......................................................................................10

InvokingCommandLinePrograms....................................................................14

Chapter2DesignFlow...............................................................................................15

DesignFlowOverview........................................................................................15

DesignEntryandSynthesis................................................................................18

DesignImplementation.......................................................................................22

DesignVerication...............................................................................................25

FPGADesignTips...............................................................................................31

Chapter3PARTGen...................................................................................................33

PARTGenOverview.............................................................................................33

PARTGenSyntax..................................................................................................39

PARTGenCommandLineOptions.....................................................................39

Chapter4NetGen.......................................................................................................43

NetGenOverview................................................................................................43

NetGenSimulationFlow.....................................................................................45

NetGenEquivalenceCheckingFlow..................................................................55

NetGenStaticTimingAnalysisFlow.................................................................59

PreservingandWritingHierarchyFiles.............................................................63

DedicatedGlobalSignalsinBack-AnnotationSimulation..............................65

Chapter5LogicalDesignRuleCheck(DRC)...........................................................67

LogicalDRCOverview........................................................................................67

LogicalDRCChecks............................................................................................67

Chapter6NGDBuild...................................................................................................71

NGDBuildOverview...........................................................................................71

NGDBuildSyntax................................................................................................74

NGDBuildOptions..............................................................................................75

Chapter7MAP............................................................................................................81

MAPOverview.....................................................................................................81

CommandLineToolsUserGuide

UG628(v13.1)March2,2011w

w w . x i l i n x . c o m 3

Page 4

MAPProcess.........................................................................................................83

MAPSyntax..........................................................................................................84

MAPOptions........................................................................................................86

ResynthesisandPhysicalSynthesisOptimizations..........................................97

GuidedMapping..................................................................................................98

SimulatingMapResults......................................................................................99

MAPReport(MRP)File.....................................................................................100

PhysicalSynthesisReport(PSR)File................................................................105

HaltingMAP......................................................................................................107

Chapter8PhysicalDesignRuleCheck..................................................................109

DRCOverview...................................................................................................109

DRCSyntax........................................................................................................110

DRCOptions......................................................................................................110

DRCChecks.......................................................................................................111

DRCErrorsandWarnings.................................................................................111

Chapter9PlaceandRoute(PAR)...........................................................................113

PAROverview....................................................................................................113

PARProcess........................................................................................................115

PARSyntax.........................................................................................................116

DetailedListingofOptions...............................................................................117

PARReports.......................................................................................................123

ReportGen..........................................................................................................132

HaltingPAR........................................................................................................134

Chapter10SmartXplorer.........................................................................................135

What’sNew.........................................................................................................135

SmartXplorerOverview.....................................................................................136

UsingSmartXplorer...........................................................................................137

SelectingtheBestStrategy................................................................................143

RunningMultipleStrategiesinParallel...........................................................144

CustomStrategies..............................................................................................146

SmartXplorerCommandLineReference..........................................................148

SmartXplorerReports........................................................................................158

SettingUpSmartXplorertoRunonSSH.........................................................161

Chapter11XPWR(XPWR).......................................................................................163

XPWROverview................................................................................................163

XPWRSyntax......................................................................................................164

4w

CommandLineToolsUserGuide

w w . x i l i n x . c o m UG628(v13.1)March2,2011

Page 5

XPWRCommandLineOptions........................................................................165

XPWRCommandLineExamples......................................................................167

UsingXPWR.......................................................................................................167

PowerReports....................................................................................................169

Chapter12PIN2UCF................................................................................................171

PIN2UCFOverview...........................................................................................171

PIN2UCFSyntax................................................................................................174

PIN2UCFCommandLineOptions...................................................................175

Chapter13TRACE....................................................................................................177

TRACEOverview...............................................................................................177

TRACESyntax....................................................................................................178

TRACEOptions.................................................................................................179

TRACECommandLineExamples....................................................................183

TRACEReports..................................................................................................184

OFFSETConstraints...........................................................................................200

PERIODConstraints..........................................................................................207

HaltingTRACE..................................................................................................211

Chapter14Speedprint.............................................................................................213

SpeedprintOverview.........................................................................................213

SpeedprintCommandLineSyntax...................................................................217

SpeedprintCommandLineOptions.................................................................217

Chapter15BitGen....................................................................................................219

BitGenOverview...............................................................................................219

BitGenCommandLineSyntax..........................................................................221

BitGenCommandLineOptions.......................................................................222

Chapter16BSDLAnno.............................................................................................245

BSDLAnnoOverview........................................................................................245

BSDLAnnoCommandLineSyntax..................................................................246

BSDLAnnoCommandLineOptions................................................................246

BSDLAnnoFileComposition...........................................................................247

BoundaryScanBehaviorinXilinxDevices......................................................253

Chapter17PROMGen..............................................................................................255

PROMGenOverview.........................................................................................255

PROMGenSyntax..............................................................................................256

PROMGenOptions............................................................................................257

BitSwappinginPROMFiles............................................................................263

CommandLineToolsUserGuide

UG628(v13.1)March2,2011w

w w . x i l i n x . c o m 5

Page 6

PROMGenExamples.........................................................................................264

Chapter18IBISWriter..............................................................................................265

IBISWriterOverview.........................................................................................265

IBISWriterSyntax..............................................................................................266

IBISWriterOptions............................................................................................267

Chapter19CPLDFit..................................................................................................269

CPLDFitOverview.............................................................................................269

CPLDFitSyntax..................................................................................................270

CPLDFitOptions................................................................................................271

Chapter20TSIM.......................................................................................................279

TSIMOverview..................................................................................................279

TSIMSyntax.......................................................................................................279

Chapter21TAEngine...............................................................................................281

TAEngineOverview...........................................................................................281

TAEngineSyntax................................................................................................282

TAEngineOptions..............................................................................................282

Chapter22Hprep6...................................................................................................283

Hprep6Overview...............................................................................................283

Hprep6Options..................................................................................................284

Chapter23XFLOW...................................................................................................287

XFLOWOverview..............................................................................................287

XFLOWSyntax...................................................................................................292

XFLOWFlowTypes...........................................................................................292

FlowFiles............................................................................................................297

XFLOWOptionFiles..........................................................................................300

XFLOWOptions.................................................................................................301

RunningXFLOW................................................................................................305

Chapter24NGCBuild...............................................................................................307

NGCBuildOverview.........................................................................................307

NGCBuildSyntax..............................................................................................308

NGCBuildOptions............................................................................................309

Chapter25Compxlib...............................................................................................315

CompxlibOverview...........................................................................................315

CompxlibSyntax................................................................................................316

CompxlibOptions..............................................................................................317

6w

CommandLineToolsUserGuide

w w . x i l i n x . c o m UG628(v13.1)March2,2011

Page 7

CompxlibCommandLineExamples................................................................322

SpecifyingRuntimeOptions.............................................................................323

SampleCongurationFile(WindowsV ersion)...............................................326

Chapter26XWebTalk...............................................................................................331

WebTalkOverview.............................................................................................331

XWebTalkSyntax...............................................................................................332

XWebTalkOptions.............................................................................................332

Chapter27TclReference........................................................................................335

TclOverview.......................................................................................................335

TclFundamentals...............................................................................................336

ProjectandProcessProperties...........................................................................338

XilinxTclCommandsforGeneralUse.............................................................356

XilinxTclCommandsforAdvancedScripting.................................................373

ExampleTclScripts............................................................................................388

AppendixAISEDesignSuiteFiles.........................................................................393

AppendixBEDIF2NGDandNGDBuild...................................................................397

EDIF2NGDOverview........................................................................................397

EDIF2NGDOptions...........................................................................................399

NGDBuild..........................................................................................................401

AppendixCAdditionalResources..........................................................................411

CommandLineToolsUserGuide

UG628(v13.1)March2,2011w

w w . x i l i n x . c o m 7

Page 8

8w

CommandLineToolsUserGuide

w w . x i l i n x . c o m UG628(v13.1)March2,2011

Page 9

Introduction

ThischapterdescribesthecommandlineprogramsfortheISE®DesignSuite.This

guidewasformerlyknownastheDevelopmentSystemReferenceGuide,buthasbeen

renamedtoCommandLineToolsUserGuide.

CommandLineProgramOverview

Xilinx®softwarecommandlineprogramsallowyoutoimplementandverifyyour

design.Thefollowingtableliststheprogramsyoucanuseforeachstepinthedesign

ow.Fordetailedinformation,seetheDesignFlowchapter.

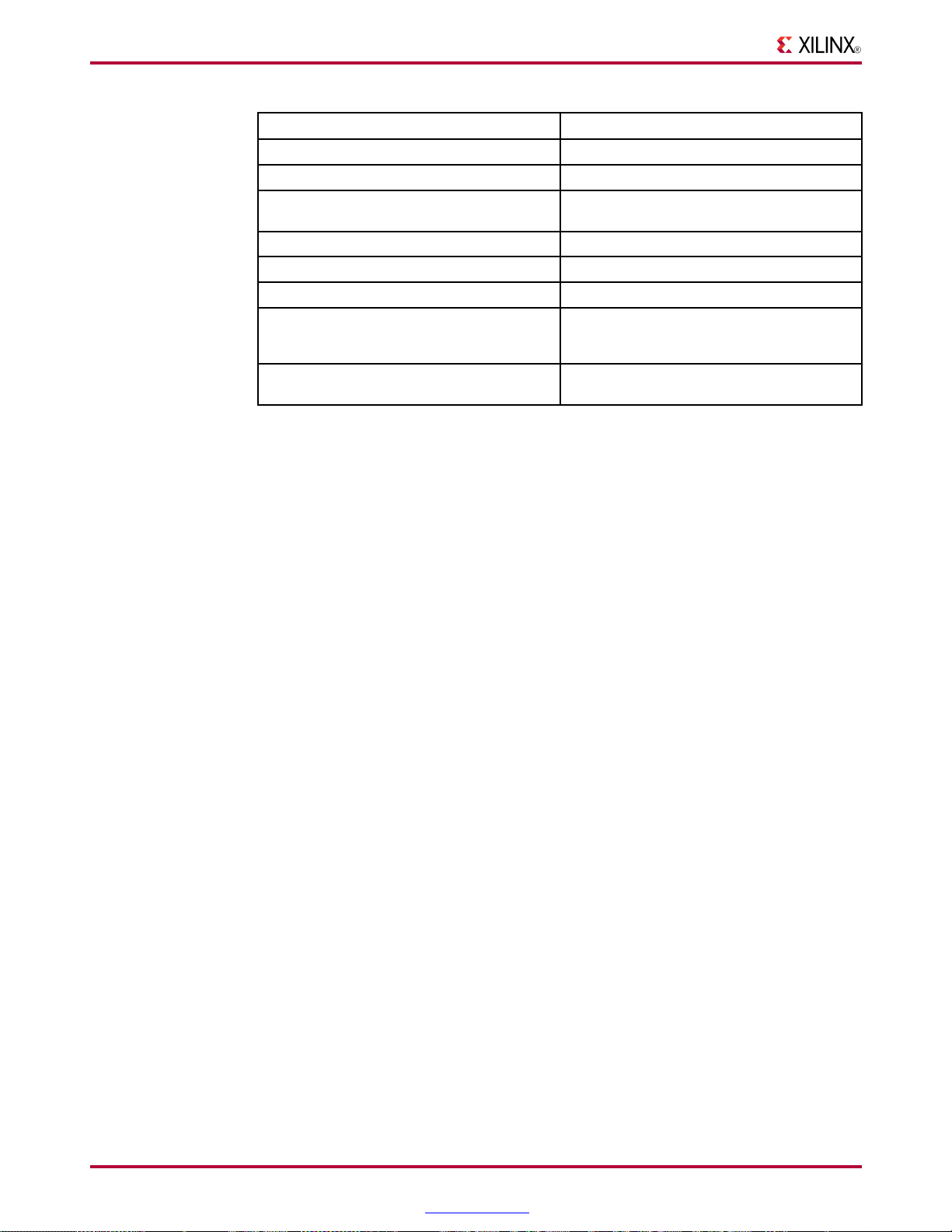

CommandLineProgramsintheDesignFlow

Chapter1

DesignFlowStepCommandLineProgram

DesignImplementationNGDBuild,MAP ,PAR,SmartXplorer,BitGen

Timing-drivenPlacementandRouting,

Re-synthesis,&PhysicalSynthesis

Optimizations

TimingSimulationandBackAnnotation

(DesignVerication)

StaticTimingAnalysis

(DesignVerication)

Youcanruntheseprogramsinthestandarddesignoworusespecialoptionstorunthe

programsfordesignpreservation.Eachcommandlineprogramhasmultipleoptions,

whichallowyoutocontrolhowaprogramexecutes.Forexample,youcansetoptionsto

changeoutputlenames,tosetapartnumberforyourdesign,ortospecifylestoread

inwhenexecutingtheprogram.Youcanalsouseoptionstocreateguidelesandrun

guidemodetomaintaintheperformanceofapreviouslyimplementeddesign.

Someofthecommandlineprogramsdescribedinthisguideunderliemanyofthe

XilinxGraphicalUserInterfaces(GUIs).TheGUIscanbeusedwiththecommand

lineprogramsoralone.ForinformationontheGUIs,seetheonlineHelpprovided

witheachXilinxtool.

MAP

NoteMAPusesspeciedoptionstoenable

timing-drivenplacementandrouting

(-timing),andre-synthesisandphysical

synthesisoptimizationsthatcantransforma

designtomeettimingrequirements.

NetGen

TRACE

CommandLineToolsUserGuide

UG628(v13.1)March2,2011w

w w . x i l i n x . c o m 9

Page 10

Chapter1:Introduction

CommandLineSyntax

Commandlinesyntaxalwaysbeginswiththecommandlineprogramname.The

programnameisfollowedbyanyoptionsandthenbylenames.Usethefollowing

ruleswhenspecifyingcommandlineoptions:

•Enteroptionsinanyorder,precededthemwithadash(minussignonthekeyboard)

andseparatethemwithspaces.

•Beconsistentwithuppercaseandlowercase.

•Whenanoptionrequiresaparameter,separatetheparameterfromtheoptionby

spacesortabs.Forexample,thefollowingshowsthecommandlinesyntaxfor

runningPARwiththeeffortlevelsettohigh:

–Correct:par-olhigh

–Incorrect:par-olhigh

•Whenusingoptionsthatcanbespeciedmultipletimes,precedeeachparameter

withtheoptionletter.Inthisexample,the-loptionshowsthelistoflibrariesto

search:

–Correct:-lxilinxun-lsynopsys

–Incorrect:-lxilinxunsynopsys

•Enterparametersthatareboundtoanoptionaftertheoption.

–Correct:-fcommand_file

–Incorrect:command_file-f

CommandLineOptions

-f(ExecuteCommandsFile)

Usethefollowingruleswhenspecifyinglenames:

•Enterlenamesintheorderspeciedinthechapterthatdescribesthecommand

lineprogram.Inthisexamplethecorrectorderisprogram,inputle,outputle,

andthenphysicalconstraintsle.

–Correct:parinput.ncdoutput.ncdfreq.pcf

–Incorrect:parinput.ncdfreq.pcfoutput.ncd

•Uselowercaseforallleextensions(forexample,.ncd).

Thefollowingoptionsarecommontomanyofthecommandlineprogramsprovided

withtheISE®DesignSuite.

•-f(ExecuteCommandsFile)

•-h(Help)

•-intstyle(IntegrationStyle)

•-p(PartNumber)

WithanyXilinx®commandlineprogramforusewithFPGAdesigns,youcanstore

commandlineprogramoptionsandlenamesinacommandle.Youcanthenexecute

theargumentsbyenteringtheprogramnamewiththe-foptionfollowedbythename

ofthecommandle.Thisisusefulifyoufrequentlyexecutethesameargumentseach

timeyouexecuteaprogramorifthecommandlinecommandbecomestoolong.

Syntax

-fcommand_file

10w

CommandLineToolsUserGuide

w w . x i l i n x . c o m UG628(v13.1)March2,2011

Page 11

Chapter1:Introduction

Youcanusetheleinthefollowingways:

•Tosupplyallofthecommandoptionsandlenamesfortheprogram,asinthe

followingexample:

par-fcommand_le

command_leisthenameofthelethatcontainsthecommandoptionsandle

names.

•Toinsertcertaincommandoptionsandlenameswithinthecommandline,asin

thefollowingexample:

par-fplaceoptions-frouteoptionsdesign_i.ncddesign_o.ncd

–placeoptionsisthenameofalecontainingplacementcommandparameters.

–routeoptionsisthenameofalecontainingroutingcommandparameters.

YoucreatethecommandleinASCIIformat.Usethefollowingruleswhencreating

thecommandle:

•Separateprogramoptionsandlenameswithspaces.

•Precedecommentswiththepoundsign(#).

•PutnewlinesortabsanywherewhitespaceisallowedontheLinuxorDOS

commandline.

•Putallargumentsonthesameline,oneargumentperline,oracombinationofthese.

•Allcarriagereturnsandothernon-printablecharactersaretreatedasspacesand

ignored.

•Nolinelengthlimitationexistswithinthele.

Example

Followingisanexampleofacommandle:

#commandlineoptionsforparfordesignmine.ncd

-w

0l5

/home/yourname/designs/xilinx/mine.ncd

#directoryforoutputdesigns

/home/yourname/designs/xilinx/output.dir

#usetimingconstraintsfile

/home/yourname/designs/xilinx/mine.pcf

-h(Help)

Whenyouentertheprogramnamefollowedbythisoption,youwillgetamessage

listingalloptionsfortheprogramandtheirparameters,aswellastheletypesusedby

theprogram.Themessagealsoexplainseachoftheoptions.

Syntax

-h

-help

CommandLineToolsUserGuide

UG628(v13.1)March2,2011w

w w . x i l i n x . c o m 11

Page 12

Chapter1:Introduction

SymbolDescription

[]

{}

italicsIndicatesavariablenameornumberforwhich

,

-

:

|

()

Enclosesitemsthatareoptional.

Enclosesitemsthatmayberepeated.

youmustsubstituteinformation.

Showsarangeforanintegervariable.

Showsthestartofanoptionname.

Bindsavariablenametoarange.

LogicalORtoshowachoiceofoneoutof

manyitems.TheORoperatormayonly

separatelogicalgroupsorliteralkeywords.

Enclosesalogicalgroupingforachoice

betweensub-formats.

Example

Followingareexamplesofsyntaxusedforlenames:

•inle[.ncd]showsthattypingthe.ncdextensionisoptionalbutthattheextension

mustbe.ncd.

•inle.ednshowsthatthe.ednextensionisoptionalandisappendedonlyifthere

isnootherextensioninthelename.

Forarchitecture-specicprograms,suchasBitGen,youcanenterthefollowingtogeta

verbosehelpmessageforthespeciedarchitecture:

program_name-harchitecture_name

Youcanredirectthehelpmessagetoaletoreadlaterortoprintoutbyenteringthe

following:

program_name-h>lename

OntheLinuxcommandline,enterthefollowingtoredirectthehelpmessagetoale

andreturntothecommandprompt.

program_name-h>&lename

-intstyle(IntegrationStyle)

Thisoptionlimitsscreenoutput,basedontheintegrationstylethatyouarerunning,to

warninganderrormessagesonly.

Syntax

-intstyleise|xflow|silent

Whenusing-intstyle,oneofthreemodesmustbespecied:

•-intstyleiseindicatestheprogramisbeingrunaspartofanintegrateddesign

environment.

•-intstylexflowindicatestheprogramisbeingrunaspartofanintegrated

batchow.

•-intstylesilentlimitsscreenoutputtowarninganderrormessagesonly.

Note-intstyleisautomaticallyinvokedwhenrunninginanintegratedenvironment

suchasProjectNavigatororXFLOW.

12w

CommandLineToolsUserGuide

w w . x i l i n x . c o m UG628(v13.1)March2,2011

Page 13

Chapter1:Introduction

-p(PartNumber)

Thisoptionspeciesthepartintowhichyourdesignisimplemented.

Syntax

-ppart_number

Thisoptioncanspecifyanarchitectureonly,acompletepartspecication(device,

package,andspeed),orapartialspecication(forexample,deviceandpackageonly).

Thepartnumberordevicenamemustbefromadevicelibraryyouhaveinstalledon

yoursystem.

AcompleteXilinx®partnumberconsistsofthefollowingelements:

•Architecture(forexample,spartan3e)

•Device(forexample,xc3s100e)

•Package(forexample,vq100)

•Speed(forexample,-4)

NoteTheSpeedprintprogramlistsblockdelaysfordevicespeedgrades.The-soption

letsyouspecifyaspeedgrade.Ifyoudonotspecifyaspeedgrade,Speedprintreports

thedefaultspeedgradeforthedeviceyouaretargeting.

SpecifyingPartNumbers

Youcanspecifyapartnumberatvariouspointsinthedesignow,notallofwhich

requirethe-poption.

•Intheinputnetlist(doesnotrequirethe-poption)

•InaNetlistConstraintsFile(NCF)(doesnotrequirethe-poption)

•Withthe-poptionwhenyourunanetlistreader(EDIF2NGD)

•IntheUserConstraintsFile(UCF)(doesnotrequirethe-poption)

•Withthe-poptionwhenyourunNGDBuild

BythetimeyourunNGDBuild,youmusthavealreadyspeciedadevice

architecture.

•Withthe-poptionwhenyourunMAP

WhenyourunMAPyoumustspecifyanarchitecture,device,andpackage,either

ontheMAPcommandlineorearlierinthedesignow.Ifyoudonotspecifya

speed,MAPselectsadefaultspeed.YoucanonlyrunMAPusingapartnumber

fromthearchitectureyouspeciedwhenyouranNGCBuild.

•Withthe-poptionwhenyourunSmartXplorer(FPGAdesignsonly)

•Withthe-poptionwhenyourunCPLDFit(CPLDdesignsonly)

NotePartnumbersspeciedinalaterstepofthedesignowoverrideapartnumber

speciedinanearlierstep.Forexample,apartspeciedwhenyourunMAPoverridesa

partspeciedintheinputnetlist.

Examples

Thefollowingexamplesshowhowtospecifypartsonthecommandline.

CommandLineToolsUserGuide

UG628(v13.1)March2,2011w

w w . x i l i n x . c o m 13

Page 14

Chapter1:Introduction

SpecificationExamples

Architectureonly

Deviceonlyxc4vfx12

DevicePackagexc4fx12sf363

Device-Packagexc4vfx12-sf363

DeviceSpeed-Packagexc4vfx1210-sf363

DevicePackage-Speedxc4fx12sf363-10

Device-Speed-Packagexc4vfx12-10-sf363

Device-SpeedPackagexc4vfx12-10sf363

virtex4

virtex5

spartan3

spartan3a

xc9500

xpla3(CoolRunner™XPLA3devices)

xc3s100e

xc3s100evq100

xc3s100e-vq100

xc3s100e4-vq100

xc3s100evq100-4

xc3s100e-4-vq100

xc3s100e-4vq100

InvokingCommandLinePrograms

YoustartXilinx®commandlineprogramsbyenteringacommandattheLinuxorDOS

commandline.Seetheprogram-specicchaptersinthisbookfortheappropriatesyntax

XilinxalsoofferstheXFLOWprogram,whichletsyouautomatetherunningofseveral

programsatonetime.SeetheXFLOWchapterformoreinformation.

14w

CommandLineToolsUserGuide

w w . x i l i n x . c o m UG628(v13.1)March2,2011

Page 15

DesignFlow

Thischapterdescribestheprocessforcreating,implementing,verifying,and

downloadingdesignsforXilinx®FPGAandCPLDdevices.Foracomplete

descriptionofXilinxFPGAandCPLDsdevices,refertotheXilinxDataSheetsat:

t t p : / / w w w . x i l i n x . c o m / s u p p o r t / d o c u m e n t a t i o n / i n d e x . h t m

h

DesignFlowOverview

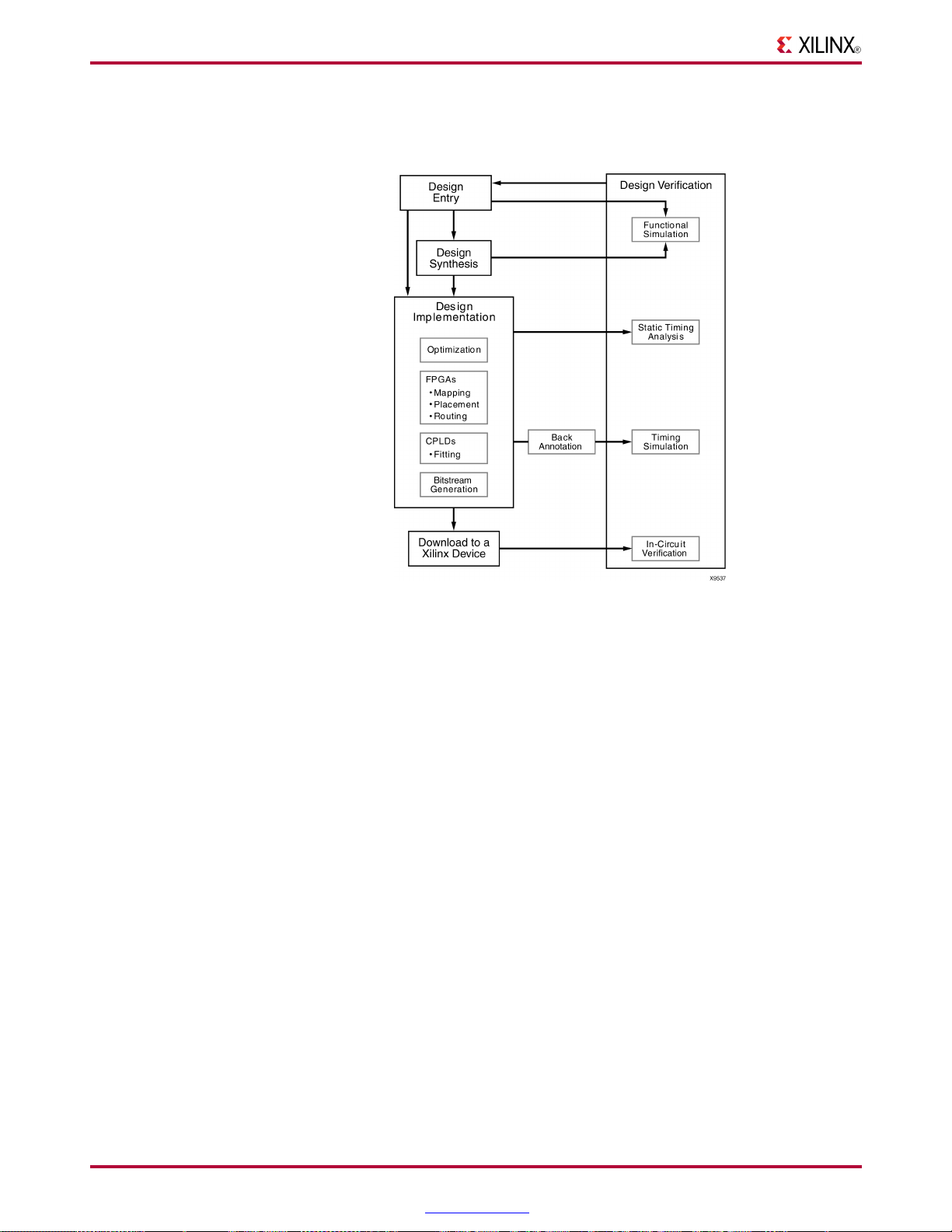

Thestandarddesignowcomprisesthefollowingsteps:

1.DesignEntryandSynthesis-CreateyourdesignusingaXilinx®-supported

schematiceditor,aHardwareDescriptionLanguage(HDL)fortext-basedentry ,or

both.IfyouuseanHDLfortext-basedentry ,youmustsynthesizetheHDLleinto

anEDIFleor,ifyouareusingtheXilinxSynthesisTechnology(XST)GUI,you

mustsynthesizetheHDLleintoanNGCle.

2.DesignImplementation-Convertthelogicaldesignleformat,suchasEDIF ,that

youcreatedinthedesignentryandsynthesisstageintoaphysicalleformatby

implementingtoaspecicXilinxarchitecture.Thephysicalinformationiscontained

intheNativeCircuitDescription(NCD)leforFPGAsandtheVM6leforCPLDs.

ThencreateabitstreamlefromtheselesandoptionallyprogramaPROMor

EPROMforsubsequentprogrammingofyourXilinxdevice.

3.DesignV erication-Usingagate-levelsimulatororcable,ensurethatyourdesign

meetstimingrequirementsandfunctionsproperly .SeetheiMPACTonlinehelpfor

informationaboutXilinxdownloadcablesanddemonstrationboards.

Chapter2

Thefulldesignowisaniterativeprocessofentering,implementing,andverifying

yourdesignuntilitiscorrectandcomplete.Thecommandlinetoolsprovidedwiththe

ISE®DesignSuiteallowquickdesigniterationsthroughthedesignowcycle.Xilinx

devicespermitunlimitedreprogramming.Youdonotneedtodiscarddeviceswhen

debuggingyourdesignincircuit.

CommandLineToolsUserGuide

UG628(v13.1)March2,2011w

w w . x i l i n x . c o m 15

Page 16

Chapter2:DesignFlow

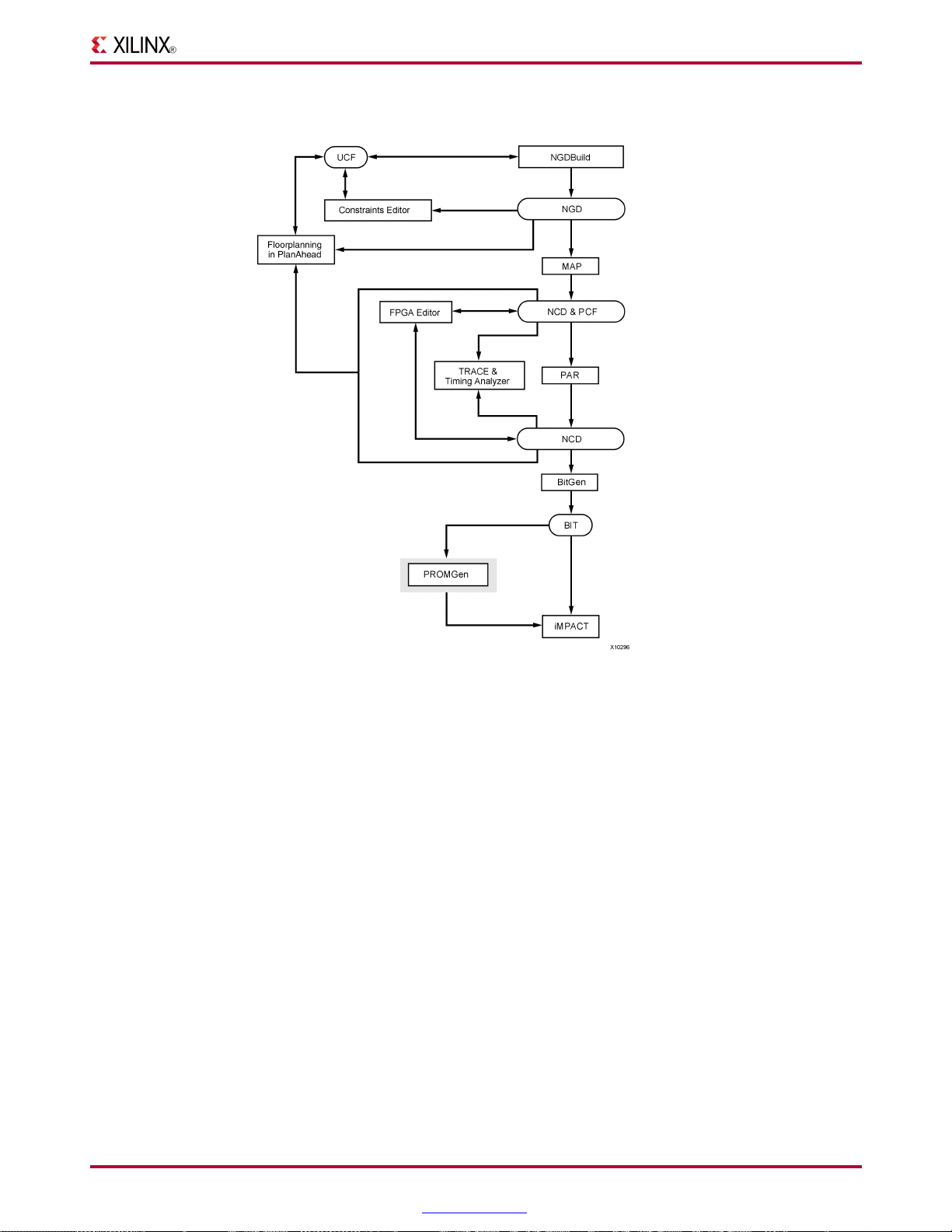

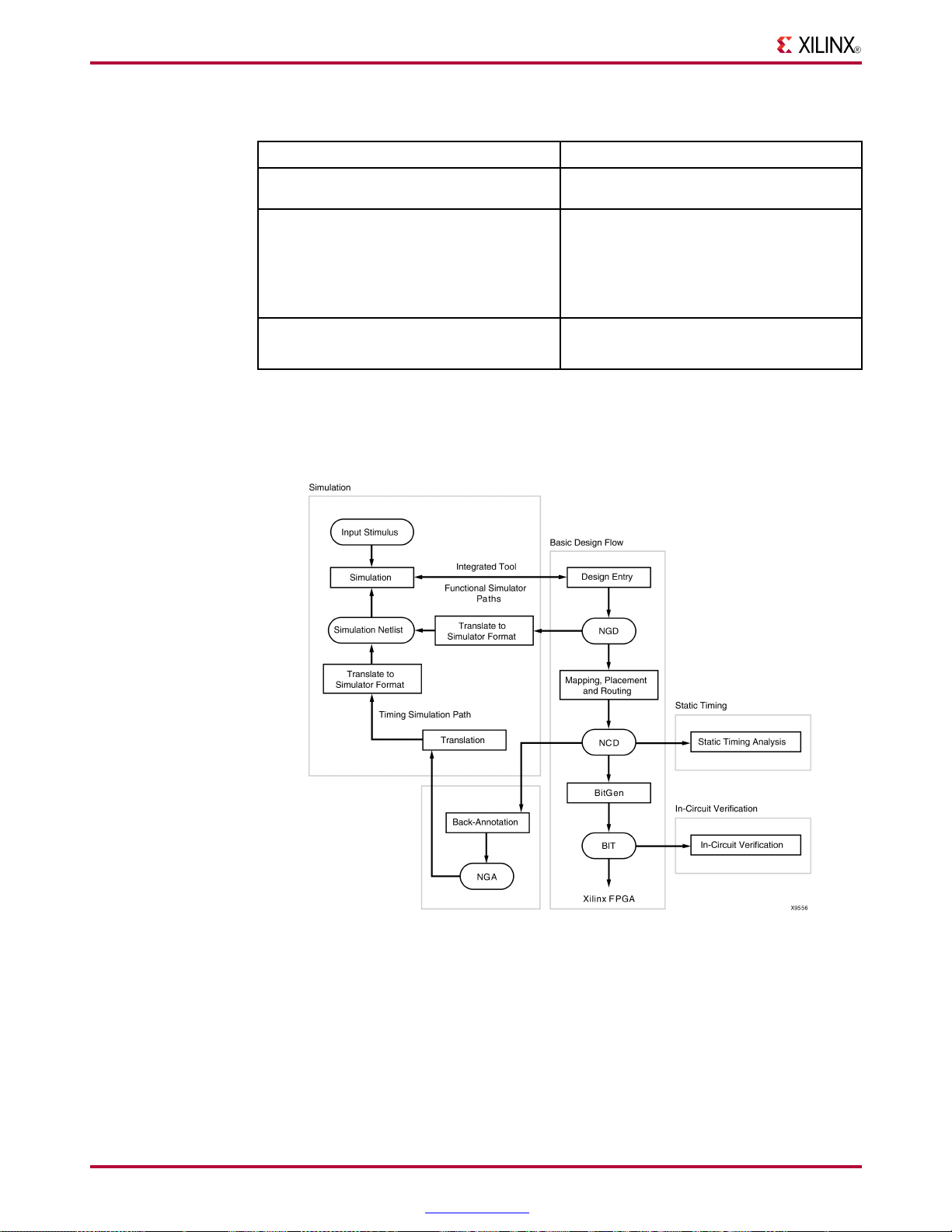

XilinxDesignFlow

ThisgureshowsthestandardXilinxdesignow.

16w

CommandLineToolsUserGuide

w w . x i l i n x . c o m UG628(v13.1)March2,2011

Page 17

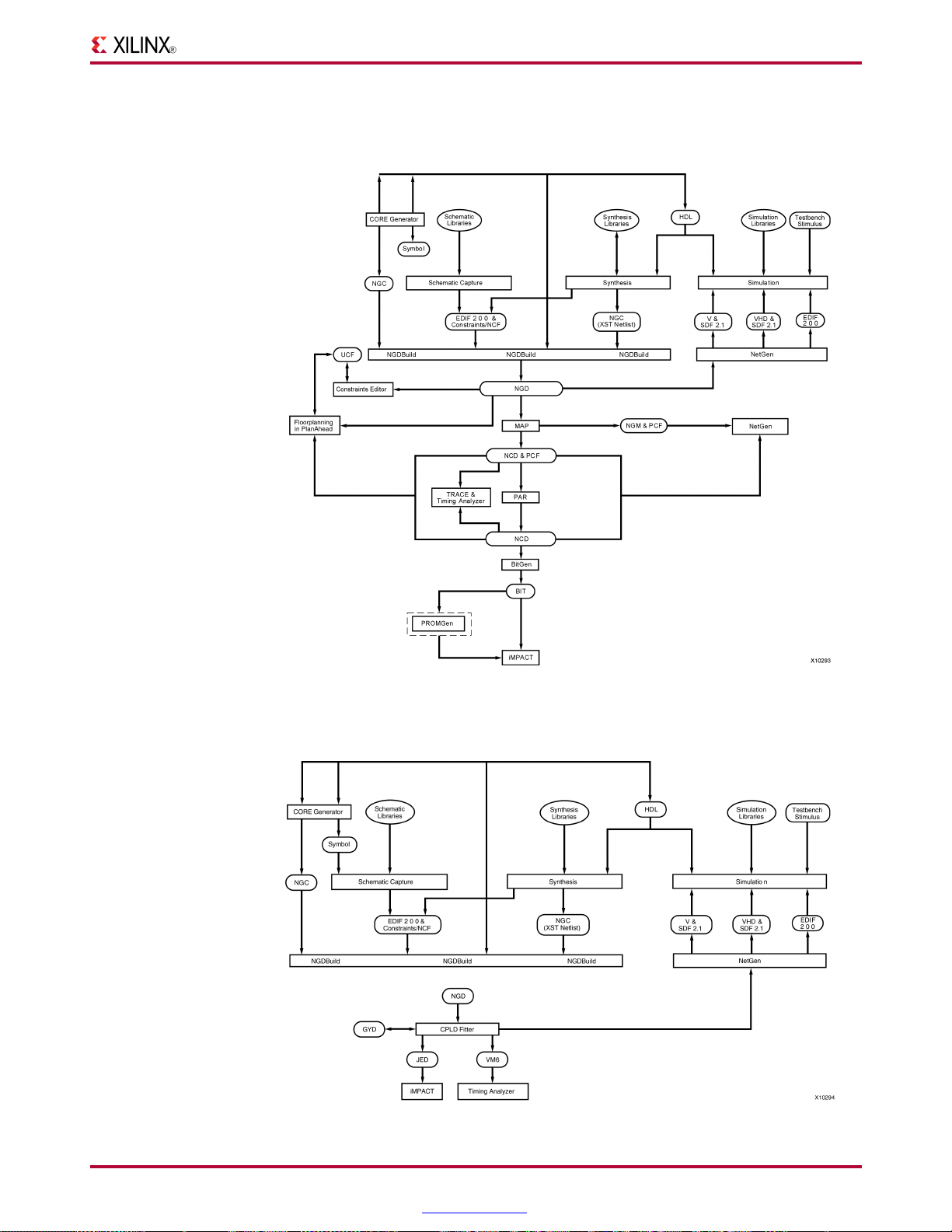

XilinxSoftwareDesignFlow(FPGAs)

ThisgureshowstheXilinxsoftwareowchartforFPGAdesigns.

Chapter2:DesignFlow

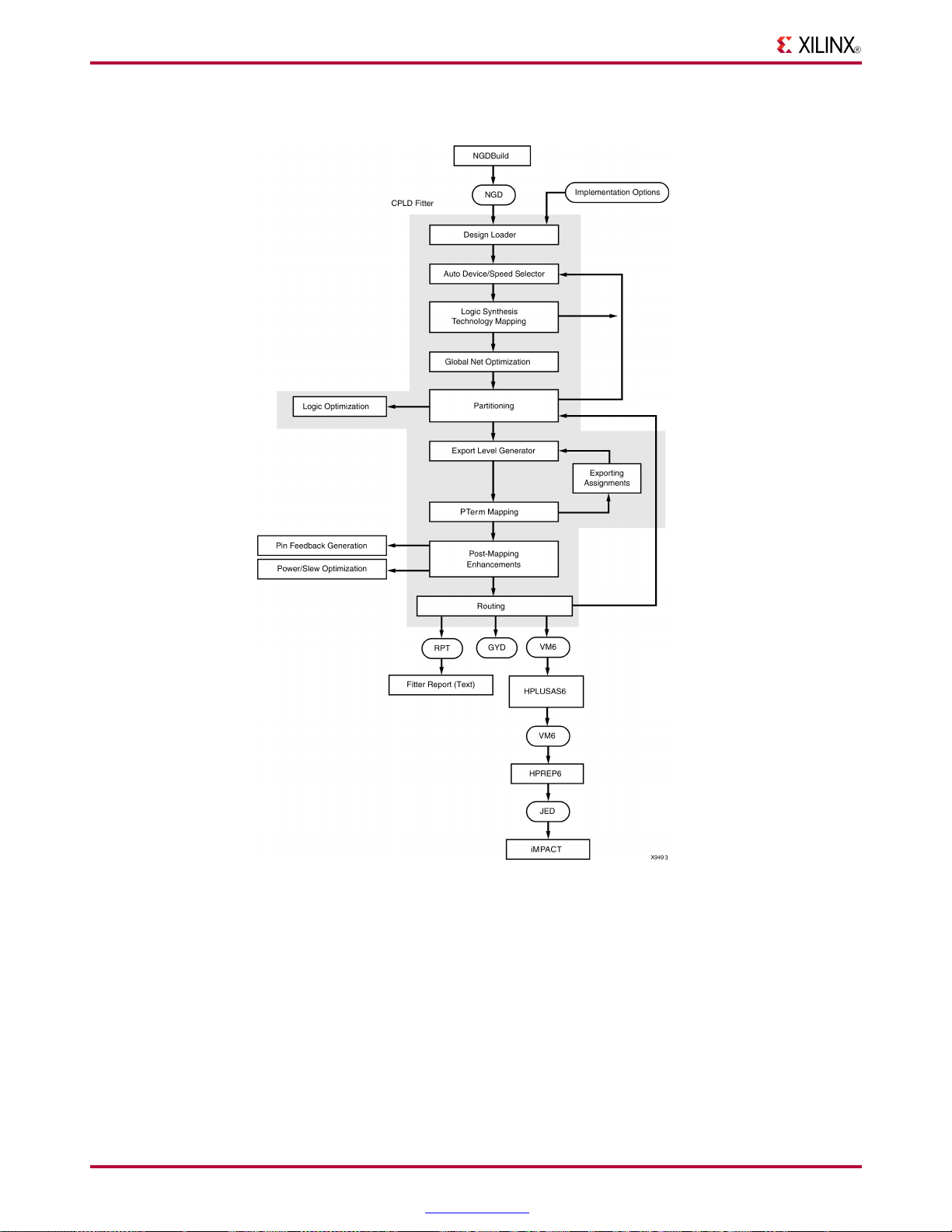

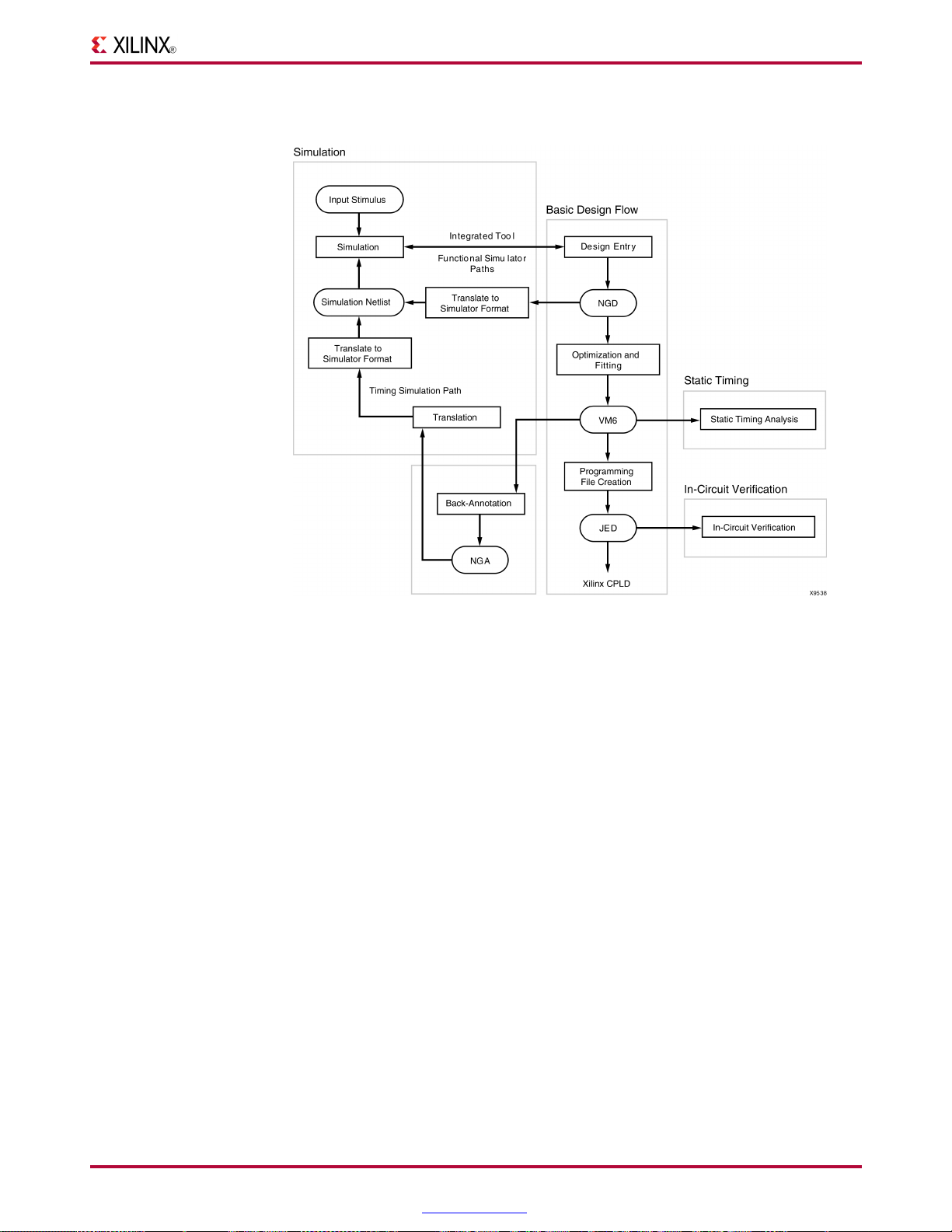

XilinxSoftwareDesignFlow(CPLDs)

ThisgureshowstheXilinxsoftwareowchartforCPLDdesigns.

CommandLineToolsUserGuide

UG628(v13.1)March2,2011w

w w . x i l i n x . c o m 17

Page 18

Chapter2:DesignFlow

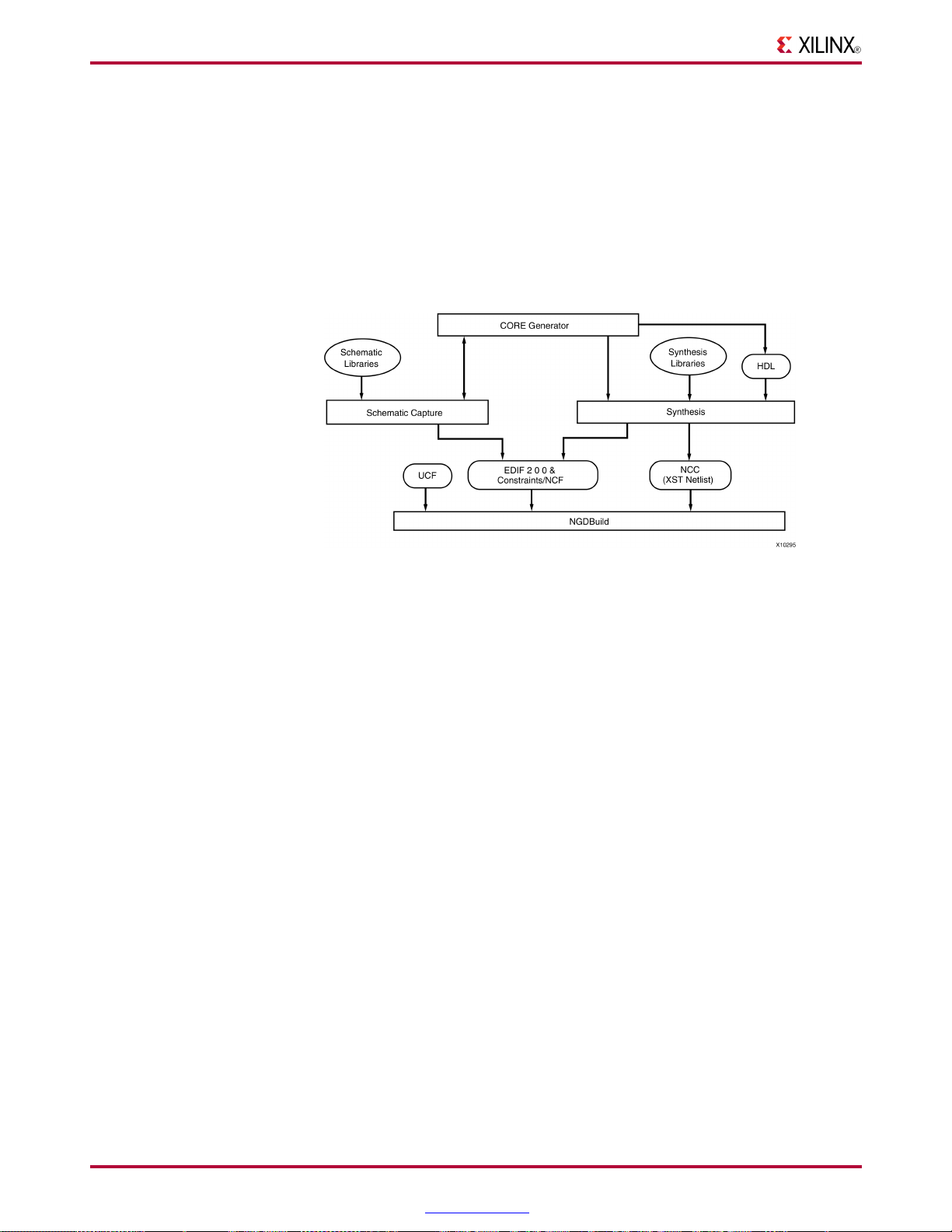

DesignEntryandSynthesis

Youcanenteradesignwithaschematiceditororatext-basedtool.Designentrybegins

withadesignconcept,expressedasadrawingorfunctionaldescription.Fromthe

originaldesign,anetlistiscreated,thensynthesizedandtranslatedintoanativegeneric

object(NGO)le.ThisleisfedintotheXilinx®softwareprogramcalledNGDBuild,

whichproducesalogicalNativeGenericDatabase(NGD)le.

Thefollowinggureshowsthedesignentryandsynthesisprocess.

DesignEntryFlow

HierarchicalDesign

DesignhierarchyisimportantinbothschematicandHDLentryforthefollowing

reasons:

•Helpsyouconceptualizeyourdesign

•Addsstructuretoyourdesign

•Promoteseasierdesigndebugging

•Makesiteasiertocombinedifferentdesignentrymethods(schematic,HDL,orstate

editor)fordifferentpartsofyourdesign

•Makesiteasiertodesignincrementally ,whichconsistsofdesigning,implementing,

andverifyingindividualpartsofadesigninstages

•Reducesoptimizationtime

•Facilitatesconcurrentdesign,whichistheprocessofdividingadesignamonga

numberofpeoplewhodevelopdifferentpartsofthedesigninparallel.

Inhierarchicaldesigning,aspecichierarchicalnameidentieseachlibraryelement,

uniqueblock,andinstanceyoucreate.Thefollowingexampleshowsahierarchical

namewitha2-inputORgateintherstinstanceofamultiplexerina4-bitcounter:

/Acc/alu_1/mult_4/8count_3/4bit_0/mux_1/or2

Xilinx®stronglyrecommendsthatyounamethecomponentsandnetsinyourdesign.

ThesenamesarepreservedandusedbyFPGAEditor.Thesenamesarealsousedfor

back-annotationandappearinthedebugandanalysistools.Ifyoudonotnameyour

componentsandnets,theSchematicEditorautomaticallygeneratesthenames.For

example,ifleftunnamed,thesoftwaremightnamethepreviousexample,asfollows:

/$1a123/$1b942/$1c23/$1d235/$1e121/$1g123/$1h57

NoteItisdifculttoanalyzecircuitswithautomaticallygeneratednames,becausethe

namesonlyhavemeaningforXilinxsoftware.

18w

CommandLineToolsUserGuide

w w . x i l i n x . c o m UG628(v13.1)March2,2011

Page 19

Chapter2:DesignFlow

Partitions

Inhierarchicaldesignows,suchasDesignPreservationandPartialReconguration,

partitionsareusedtodenehierarchicalboundariessothatacomplexdesigncanbe

brokenupintosmallerblocks.Partitionscreateaboundaryorinsulationaroundthe

hierarchicalmodule,whichisolatesthemodulefromotherpartsofthedesign.A

partitionthathasbeenimplementedandexportedcanbere-insertedintothedesign

usingasimplecut-and-pastetypefunction,whichpreservestheplacementandrouting

resultsfortheisolatedmodule.Allofthepartitiondenitionsandcontrolsaredoneina

lecalledxpartition.pxml.Formoreinformationonusinghierarchicaldesignows

andimplementingpartitions,seetheHierarchicalDesignMethodologyGuide(UG748).

PXMLFile

Partitiondenitionsarecontainedinthexpartition.pxmlle.ThePXMLlename

iscase-sensitive,andmustbenamedxpartition.pxml.Thetoplevelmodule

ofthedesignmustbedenedasapartitioninadditiontoanyoptionallowerlevel

partitions.ThePXMLlecanbecreatedbyhand,fromscripts,orfromatoolsuchas

thePlanAhead™software.ThePXMLwillbepickedupautomaticallybytheISE®

DesignSuiteimplementationtoolswhenlocatedinthecurrentworkingdirectory.

Formoreinformationaboutusingthexpartition.pxmlle,seetheHierarchical

DesignMethodologyGuide(UG748).Anexamplexpartition.pxmlleisavailable

at%XILINX%/PlanAhead/testcases/templates(where%XILINX%isyour

installationdirectory)ifyouwishtocreateaPXMLlebyhand.

NoteAllpathsinthePXMLlemustbeabsolutepaths.

<?xmlversion="1.0"encoding="UTF-8"?>

<ProjectFileVersion="1.2"Name="Example"ProjectVersion="2.0">

<PartitionName="/top"State="implement"ImportLocation="NONE">

<PartitionName="/top/module_A"State="import"ImportLocation="/home/user/Example/import"Preserve="routing">

</Partition>

<PartitionName="/top/module_B"State="import"ImportLocation="/home/user/Example/import"Preserve="routing">

</Partition>

<PartitionName="/top/module_C"State="implement"ImportLocation="/home/user/Example/import"Preserve="placement">

</Partition>

</Partition>

</Project>

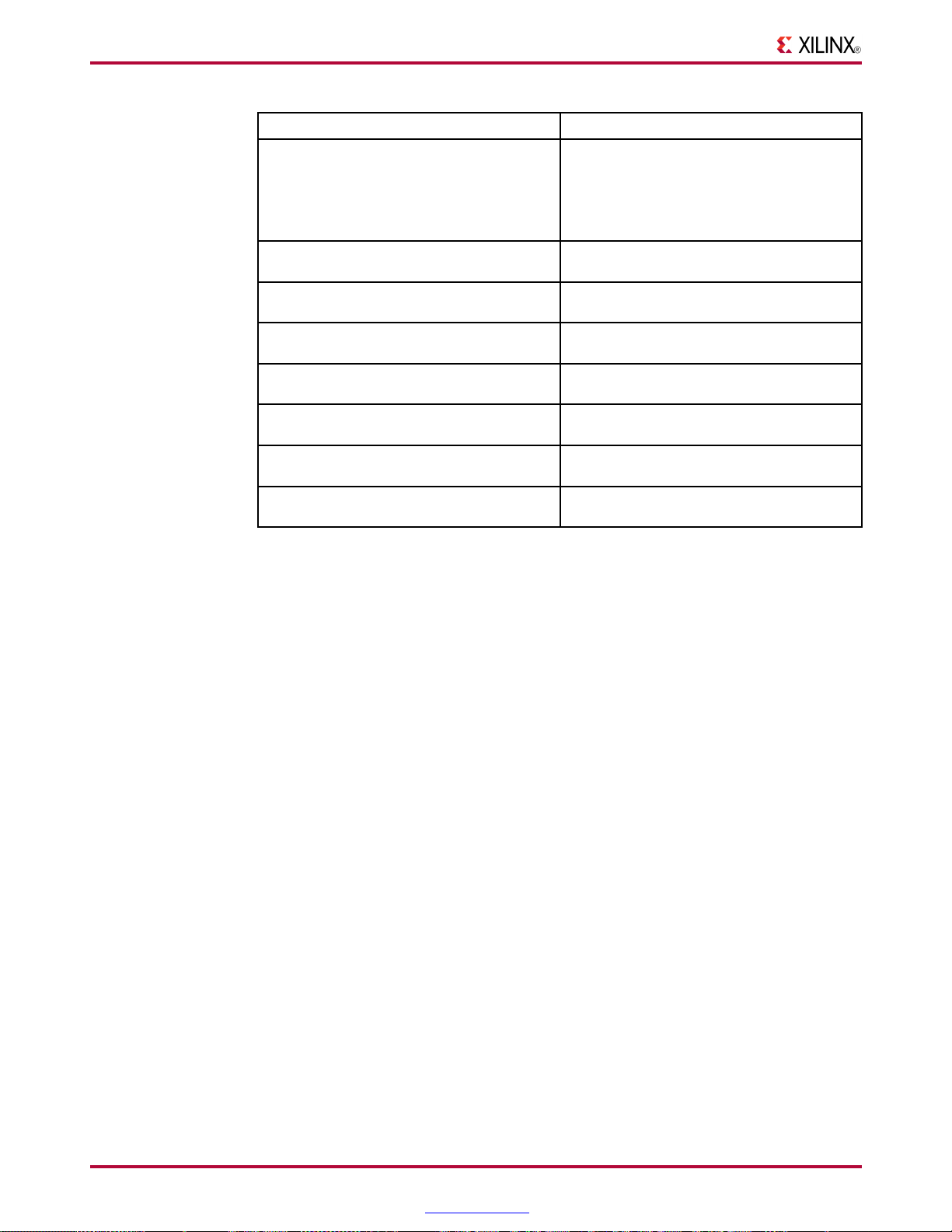

PXMLattributesforProjectdefinition

Attributename

FileVersion

Name

ProjectVersion2.0

Value

1.2

Project_Name

Description

Usedforinternalpurposes.Donotchangethis

value.

Project_Nameisuserdened.

Usedforinternalpurposes.Donotchangethis

value.

CommandLineToolsUserGuide

UG628(v13.1)March2,2011w

w w . x i l i n x . c o m 19

Page 20

Chapter2:DesignFlow

PXMLattributesforPartitiondefinition

Attributename

Name

State

ImportLocation

ImportTag

Preserve

BoundaryOpt

Value

Partition_Name

“implement”Partitionisimplementedfromscratch.

“import”

pathIgnoredifStatedoesnotequal“import.”

Partition_Name

“routing”

“placement”Placementispreservedbutroutingcanbe

“synthesis”Placementandroutingcanbemodied.

“inherit”Inheritvaluefromtheparentpartition.Thisis

“all”Enablestheimplementationtoolstodo

“none”

Description

Hierarchicalinstancenameofmoduleinwhich

thepartitionshouldbeapplied.

Partitionisimportedandpreservedaccording

tothelevelsetbyPreserve.

Thepathcanberelativeorabsolute,butthe

locationspeciedmustcontainavalid"export"

directorywhenState=import.“NONE”isa

predenedkeywordfornoimportdirectory .

Allowsapartitiontobeimportedintoa

differentlevelofhierarchythanitwasinitially

implementedin.Setthevaluetothehierarchical

instancenameofthepartitionwhereitwas

implemented.

100%placementandroutingispreserved.This

isthedefaultforthetoplevelPartition.

modied.

thedefaultforallpartitionsexceptthetoplevel

partition.

optimizationonpartitionportsconnectedto

constraintsaswellasunusedpartitionports.

Normalpartitionoptimizationrulesapply .

Optimizationisallowedonlywithinpartition

boundaries.Thisisthedefaultvalue.

SchematicEntryOverview

Schematictoolsprovideagraphicinterfacefordesignentry.Youcanusethesetoolsto

connectsymbolsrepresentingthelogiccomponentsinyourdesign.Youcanbuildyour

designwithindividualgates,oryoucancombinegatestocreatefunctionalblocks.

Thissectionfocusesonwaystoenterfunctionalblocksusinglibraryelementsandthe

COREGenerator™tool.

LibraryElements

Primitivesandmacrosarethe“buildingblocks”ofcomponentlibraries.Xilinx®

librariesprovideprimitives,aswellascommonhigh-levelmacrofunctions.Primitives

arebasiccircuitelements,suchasANDandORgates.Eachprimitivehasaunique

libraryname,symbol,anddescription.Macroscontainmultiplelibraryelements,which

canincludeprimitivesandothermacros.

YoucanusethefollowingtypesofmacroswithXilinxFPGAs:

•Softmacroshavepre-denedfunctionalitybuthaveexiblemapping,placement,

androuting.SoftmacrosareavailableforallFPGAs.

•Relationallyplacedmacros(RPMs)havexedmappingandrelativeplacement.

RPMsareavailableforalldevicefamilies,excepttheXC9500family .

20w

CommandLineToolsUserGuide

w w . x i l i n x . c o m UG628(v13.1)March2,2011

Page 21

HDLEntryandSynthesis

Macrosarenotavailableforsynthesisbecausesynthesistoolshavetheirownmodule

generatorsanddonotrequireRPMs.Ifyouwishtooverridethemodulegeneration,you

caninstantiatemodulescreatedusingCOREGenerator.Formostleading-edgesynthesis

tools,thisdoesnotofferanadvantageunlessitisforamodulethatcannotbeinferred.

COREGeneratorTool(FPGAsOnly)

TheXilinxCOREGeneratortooldeliversparameterizablecoresthatareoptimized

forXilinxFPGAs.Thelibraryincludescoresrangingfromsimpledelayelementsto

complexDSP(DigitalSignalProcessing)ltersandmultiplexers.Fordetails,refertothe

COREGeneratorHelp(partofISEHelp).Y oucanalsorefertotheXilinxIP(Intellectual

Property)CenterWebsiteath

solutions.Thesesolutionsincludedesignreusetools,freereferencedesigns,Digital

SignalProcessing(DSP),PCI™solutions,IPimplementationtools,cores,specialized

systemlevelservices,andverticalapplicationIPsolutions.

AtypicalHardwareDescriptionLanguage(HDL)supportsamixed-leveldescriptionin

whichgateandnetlistconstructsareusedwithfunctionaldescriptions.Thismixed-level

capabilityletsyoudescribesystemarchitecturesatahighlevelofabstractionandthen

incrementallyrenethedetailedgate-levelimplementationofadesign.

t t p : / / w w w . x i l i n x . c o m / i p c e n t e r ,whichoffersthelatestIP

Chapter2:DesignFlow

FunctionalSimulation

HDLdescriptionsofferthefollowingadvantages:

•Youcanverifydesignfunctionalityearlyinthedesignprocess.Adesignwrittenas

anHDLdescriptioncanbesimulatedimmediately .Designsimulationatthishigh

level,atthegate-levelbeforeimplementation,allowsyoutoevaluatearchitectural

anddesigndecisions.

•AnHDLdescriptionismoreeasilyreadandunderstoodthananetlistorschematic

description.HDLdescriptionsprovidetechnology-independentdocumentation

ofadesignanditsfunctionality.BecausetheinitialHDLdesigndescriptionis

technologyindependent,youcanuseitagaintogeneratethedesigninadifferent

technology,withouthavingtotranslateitfromtheoriginaltechnology .

•LargedesignsareeasiertohandlewithHDLtoolsthanschematictools.

AfteryoucreateyourHDLdesign,youmustsynthesizeit.Duringsynthesis,behavioral

informationintheHDLleistranslatedintoastructuralnetlist,andthedesignis

optimizedforaXilinx®device.XilinxsupportsHDLsynthesistoolsforseveral

third-partysynthesisvendors.Inaddition,Xilinxoffersitsownsynthesistool,Xilinx

SynthesisTechnology(XST).Formoreinformation,seetheXSTUserGuideforVirtex-4,

Virtex-5,Spartan-3,andNewerCPLDDevices(UG627)ortheXSTUserGuideforVirtex-6,

Spartan-6,and7SeriesDevices(UG687).Fordetailedinformationonsynthesis,seethe

SynthesisandSimulationDesignGuide(UG626).

Afteryoucreateyourdesign,youcansimulateit.Functionalsimulationteststhe

logicinyourdesigntodetermineifitworksproperly .Youcansavetimeduring

subsequentdesignstepsifyouperformfunctionalsimulationearlyinthedesignow.

SeeSimulationformoreinformation.

Constraints

Youmaywanttoconstrainyourdesignwithincertaintimingorplacementparameters.

Youcanspecifymapping,blockplacement,andtimingspecications.

CommandLineToolsUserGuide

UG628(v13.1)March2,2011w

w w . x i l i n x . c o m 21

Page 22

Chapter2:DesignFlow

MappingConstraints(FPGAsOnly)

BlockPlacement

YoucanenterconstraintsmanuallyorusetheConstraintsEditororFPGAEditor,which

aregraphicaluserinterface(GUI)toolsprovidedbyXilinx®.YoucanusetheTiming

AnalyzerGUIorTRACEcommandlineprogramtoevaluatethecircuitagainstthese

constraintsbygeneratingastatictiminganalysisofyourdesign.SeetheTRACEchapter

andtheonlineHelpprovidedwiththeISE®DesignSuiteformoreinformation.For

moreinformationonconstraints,seetheConstraintsGuide(UG625).

YoucanspecifyhowablockoflogicismappedintoCLBsusinganFMAPforall

Spartan®andVirtex®FPGAarchitectures.Thesemappingsymbolscanbeusedin

yourschematic.However,ifyouoverusethesespecications,itmaybedifcultto

routeyourdesign.

Blockplacementcanbeconstrainedtoaspeciclocation,tooneofmultiplelocations,or

toalocationrange.Locationscanbespeciedintheschematic,withsynthesistools,

orintheUserConstraintsFile(UCF).Poorblockplacementcanadverselyaffectboth

theplacementandtheroutingofadesign.OnlyI/Oblocksrequireplacementtomeet

externalpinrequirements.

TimingSpecifications

Youcanspecifytimingrequirementsforpathsinyourdesign.PARusesthesetiming

specicationstoachieveoptimumperformancewhenplacingandroutingyourdesign.

NetlistTranslationPrograms

NetlisttranslationprogramsletyoureadnetlistsintotheXilinx®softwaretools.

EDIF2NGDletsyoureadanElectronicDataInterchangeFormat(EDIF)200le.The

NGDBuildprogramautomaticallyinvokestheseprogramsasneededtoconvertyour

EDIFletoanNGDle,therequiredformatfortheXilinxsoftwaretools.NGCles

outputfromtheXilinxXSTsynthesistoolarereadinbyNGDBuilddirectly .

YoucannddetaileddescriptionsoftheEDIF2NGD,andNGDBuildprogramsinthe

NGDBuildchapterandtheEDIF2NGDandNGDBuildAppendix.

DesignImplementation

DesignImplementationbeginswiththemappingorttingofalogicaldesignletoa

specicdeviceandiscompletewhenthephysicaldesignissuccessfullyroutedanda

bitstreamisgenerated.Youcanalterconstraintsduringimplementationjustasyoudid

duringtheDesignEntrystep.SeeConstraintsforinformation.

ThefollowinggureshowsthedesignimplementationprocessforFPGAdesigns:

22w

CommandLineToolsUserGuide

w w . x i l i n x . c o m UG628(v13.1)March2,2011

Page 23

DesignImplementationFlow(FPGAs)

Chapter2:DesignFlow

ThefollowinggureshowsthedesignimplementationprocessforCPLDdesigns:

CommandLineToolsUserGuide

UG628(v13.1)March2,2011w

w w . x i l i n x . c o m 23

Page 24

Chapter2:DesignFlow

DesignImplementationFlow(CPLDs)

Mapping(FPGAsOnly)

ForFPGAs,theMAPcommandlineprogrammapsalogicaldesigntoaXilinx®FPGA.

TheinputtoMAPisanNGDle,whichcontainsalogicaldescriptionofthedesignin

termsofboththehierarchicalcomponentsusedtodevelopthedesignandthelower-level

Xilinxprimitives,andanynumberofNMC(hardplaced-and-routedmacro)les,each

ofwhichcontainsthedenitionofaphysicalmacro.MAPthenmapsthelogictothe

components(logiccells,I/Ocells,andothercomponents)inthetargetXilinxFPGA.

TheoutputdesignfromMAPisanNCDle,whichisaphysicalrepresentationof

thedesignmappedtothecomponentsintheXilinxFPGA.TheNCDlecanthenbe

placedandrouted,usingthePARcommandlineprogram.SeetheMAPchapterfor

detailedinformation.

24w

CommandLineToolsUserGuide

w w . x i l i n x . c o m UG628(v13.1)March2,2011

Page 25

NoteMAPprovidesoptionsthatenableadvancedoptimizationsthatarecapable

ofimprovingtimingresultsbeyondstandardimplementations.Theseadvanced

optimizationscantransformadesignpriortoorafterplacement.Optimizationscan

beappliedattwodifferentstagesintheXilinxdesignow.Therststagehappens

rightaftertheinitialmappingofthelogictothearchitectureslices;thesecondstageif

afterplacement.SeeRe-SynthesisandPhysicalSynthesisOptimizationsintheMAP

chapterformoreinformation.

PlacingandRouting(FPGAsOnly)

ForFPGAs,thePARcommandlineprogramtakesamappedNCDleasinput,places

androutesthedesign,andoutputsaplacedandroutedNativeCircuitDescription

(NCD)le,whichisusedbythebitstreamgenerator,BitGen.TheoutputNCDlecan

alsoactasaguidelewhenyoureiterateplacementandroutingforadesigntowhich

minorchangeshavebeenmadeafterthepreviousiteration.SeethePARchapterfor

detailedinformation.

YoucanalsouseFPGAEditortodothefollowing:

•Placeandroutecriticalcomponentsbeforerunningautomaticplaceandroutetools

onanentiredesign.

•Modifyplacementandroutingmanually.Theeditorallowsbothautomaticand

manualcomponentplacementandrouting.

Chapter2:DesignFlow

NoteFormoreinformation,seetheonlineHelpprovidedwithFPGAEditor.

BitstreamGeneration(FPGAsOnly)

ForFPGAs,theBitGencommandlineprogramproducesabitstreamforXilinx®

deviceconguration.BitGentakesafullyroutedNCDleasitsinputandproduces

acongurationbitstream,whichisabinarylewitha.bitextension.TheBITle

containsallofthecongurationinformationfromtheNCDledeningtheinternal

logicandinterconnectionsoftheFPGA,plusdevice-specicinformationfromotherles

associatedwiththetargetdevice.SeetheBitGenchapterfordetailedinformation.

AfteryougenerateyourBITle,youcandownloadittoadeviceusingtheiMPACTGUI.

YoucanalsoformattheBITleintoaPROMleusingthePROMGencommandline

programandthendownloadittoadeviceusingtheiMPACTGUI.SeethePROMGen

chapterofthisguideortheiMPACTonlinehelpformoreinformation.

DesignVerification

Designvericationistestingthefunctionalityandperformanceofyourdesign.Y oucan

verifyXilinx®designsinthefollowingways:

•Simulation(functionalandtiming)

•Statictiminganalysis

•In-circuitverication

Thefollowingtableliststhedifferentdesigntoolsusedforeachvericationtype.

CommandLineToolsUserGuide

UG628(v13.1)March2,2011w

w w . x i l i n x . c o m 25

Page 26

Chapter2:DesignFlow

VerificationTools

VerificationTypeTools

SimulationThird-partysimulators(integratedand

non-integrated)

StaticTimingAnalysisTRACE(commandlineprogram)

TimingAnalyzer(GUI)

MentorGraphicsTAUandInnovedaBLAST

softwareforusewiththeSTAMPleformat

(forI/Otimingvericationonly)

In-CircuitVericationDesignRuleChecker(commandlineprogram)

Downloadcable

Designvericationproceduresshouldoccurthroughoutyourdesignprocess,asshown

inthefollowinggures.

ThreeVerificationMethodsoftheDesignFlow(FPGAs)

ThefollowinggureshowsthevericationmethodsofthedesignowforCPLDs.

26w

CommandLineToolsUserGuide

w w . x i l i n x . c o m UG628(v13.1)March2,2011

Page 27

ThreeVerificationMethodsoftheDesignFlow(CPLDs)

Chapter2:DesignFlow

Simulation

Youcanrunfunctionalortimingsimulationtoverifyyourdesign.Thissectiondescribes

theback-annotationprocessthatmustoccurpriortotimingsimulation.Italsodescribes

thefunctionalandtimingsimulationmethodsforbothschematicandHDL-based

designs.

Back-Annotation

Beforetimingsimulationcanoccur,thephysicaldesigninformationmustbetranslated

anddistributedbacktothelogicaldesign.ForFPGAs,thisback-annotationprocessis

donewithaprogramcalledNetGen.ForCPLDs,back-annotationisperformedwith

theTSimTimingSimulator.Theseprogramscreateadatabase,whichtranslatesthe

back-annotatedinformationintoanetlistformatthatcanbeusedfortimingsimulation.

CommandLineToolsUserGuide

UG628(v13.1)March2,2011w

w w . x i l i n x . c o m 27

Page 28

Chapter2:DesignFlow

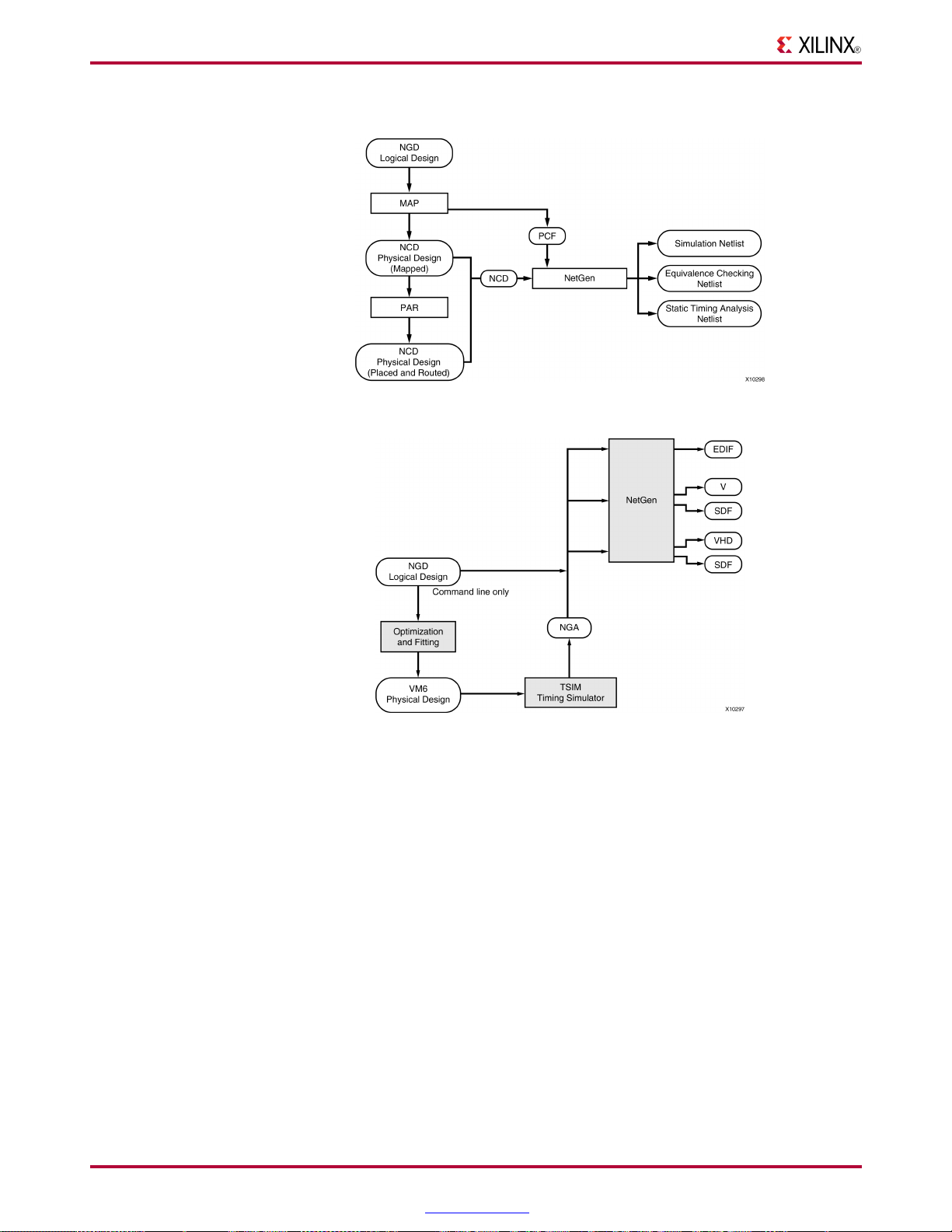

Back-AnnotationFlowforFPGAs

Back-Annotation(CPLDs)

NetGen

NetGenisacommandlineprogramthatdistributesinformationaboutdelays,setup

andholdtimes,clocktoout,andpulsewidthsfoundinthephysicalNativeCircuit

Description(NCD)designlebacktothelogicalNativeGenericDatabase(NGD)le

andgeneratesaVerilogorVHDLnetlistforusewithsupportedtimingsimulation,

equivalencechecking,andstatictiminganalysistools.

NetGenreadsanNCDasinput.TheNCDlecanbeamapped-onlydesign,ora

partiallyorfullyplacedandrouteddesign.AnNGMle,createdbyMAP ,isanoptional

sourceofinput.NetGenmergesmappinginformationfromtheoptionalNGMlewith

placement,routing,andtiminginformationfromtheNCDle.

NoteNetGenreadsanNGAleasinputtogenerateatimingsimulationnetlistfor

CPLDdesigns.

SeetheNetGenchapterfordetailedinformation.

FunctionalSimulation

Functionalsimulationdeterminesifthelogicinyourdesigniscorrectbeforeyou

implementitinadevice.Functionalsimulationcantakeplaceattheearlieststagesof

thedesignow .Becausetiminginformationfortheimplementeddesignisnotavailable

atthisstage,thesimulatorteststhelogicinthedesignusingunitdelays.

28w

CommandLineToolsUserGuide

w w . x i l i n x . c o m UG628(v13.1)March2,2011

Page 29

NoteItisusuallyfasterandeasiertocorrectdesignerrorsifyouperformfunctional

simulationearlyinthedesignow.

TimingSimulation

Timingsimulationveriesthatyourdesignrunsatthedesiredspeedforyourdevice

underworst-caseconditions.Thisprocessisperformedafteryourdesignismapped,

placed,androutedforFPGAsorttedforCPLDs.Atthistime,alldesigndelaysare

known.

Timingsimulationisvaluablebecauseitcanverifytimingrelationshipsanddetermine

thecriticalpathsforthedesignunderworst-caseconditions.Itcanalsodetermine

whetherornotthedesigncontainsset-uporholdviolations.

Beforeyoucansimulateyourdesign,youmustgothroughtheback-annotationprocess,

above.Duringthisprocess,NetGencreatessuitableformatsforvarioussimulators.

HDL-BasedSimulation

Xilinx®supportsfunctionalandtimingsimulationofHDLdesignsatthefollowing

points:

•RegisterTransferLevel(RTL)simulation,whichmayincludethefollowing:

•Post-synthesisfunctionalsimulationwithoneofthefollowing:

•Post-implementationback-annotatedtimingsimulationwiththefollowing:

Chapter2:DesignFlow

–InstantiatedUNISIMlibrarycomponents

–COREGenerator™models

–HardIP(SecureIP)

–Gate-levelUNISIMlibrarycomponents

–COREGeneratormodels

–HardIP(SecureIP)

–SIMPRIMlibrarycomponents

–HardIP(SecureIP)

–StandardDelayFormat(SDF)le

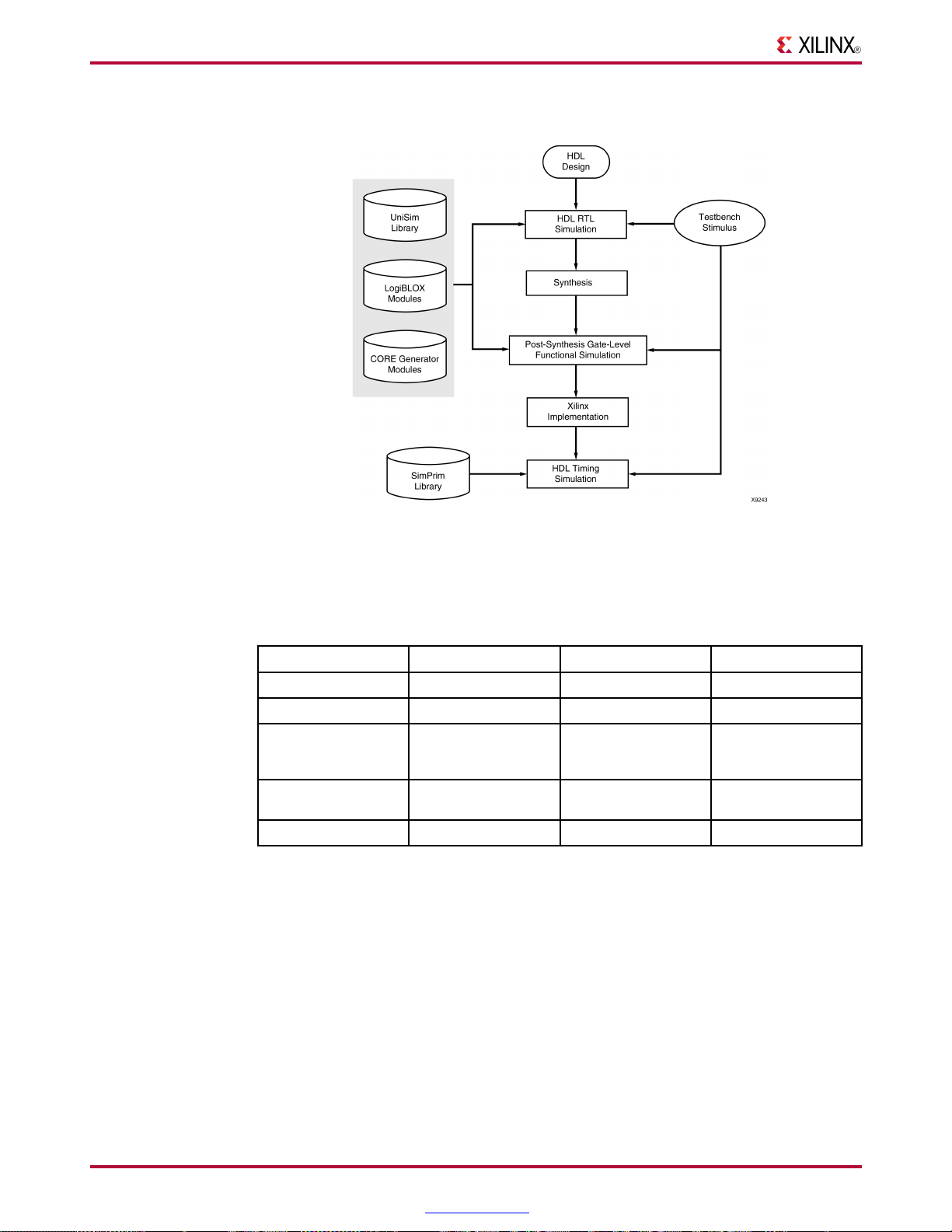

Thefollowinggureshowswhenyoucanperformfunctionalandtimingsimulation:

CommandLineToolsUserGuide

UG628(v13.1)March2,2011w

w w . x i l i n x . c o m 29

Page 30

Chapter2:DesignFlow

SimulationPointsforHDLDesigns

Thethreeprimarysimulationpointscanbeexpandedtoallowfortwopost-synthesis

simulations.ThesepointscanbeusedifthesynthesistoolcannotwriteVHDLor

Verilog,orifthenetlistisnotintermsofUNISIMcomponents.Thefollowingtablelists

allthesimulationpointsavailableintheHDLdesignow .

FiveSimulationPointsinHDLDesignFlow

SimulationUNISIMSIMPRIMSDF

RTL

Post-Synthesis

Functional

Post-NGDBuild

(Optional)

FunctionalPost-MAP

(Optional)

Post-RouteTiming

Thesesimulationpointsaredescribedinthe“SimulationPoints”sectionoftheSynthesis

andSimulationDesignGuide(UG626).

Thelibrariesrequiredtosupportthesimulationowsaredescribedindetailin

the“VHDL/VerilogLibrariesandModels”sectionoftheSynthesisandSimulation

DesignGuide(UG626).Theowsandlibrariessupportclosefunctionalequivalenceof

initializationbehaviorbetweenfunctionalandtimingsimulations.Thisisduetothe

additionofmethodologiesandlibrarycellstosimulateGlobalSet/Reset(GSR)and

Global3-State(GTS)behavior.

X

X

X

XX

XX

XilinxVHDLsimulationsupportstheVITALstandard.Thisstandardallowsyou

tosimulatewithanyVITAL-compliantsimulator.Built-inVerilogsupportallows

youtosimulatewiththeCadenceVerilog-XLandcompatiblesimulators.XilinxHDL

simulationsupportsallcurrentXilinxFPGAandCPLDdevices.RefertotheSynthesis

andSimulationDesignGuide(UG626)forthelistofsupportedVHDLandV erilog

standards.

30w

CommandLineToolsUserGuide

w w . x i l i n x . c o m UG628(v13.1)March2,2011

Page 31

StaticTimingAnalysis(FPGAsOnly)

Statictimingallowsyoutodeterminepathdelaysinyourdesign.Followingarethe

twomajorgoalsofstatictiminganalysis:

•Timingverication

Thisisverifyingthatthedesignmeetsyourtimingconstraints.

•Reporting

Thisisenumeratinginputconstraintviolationsandplacingthemintoanaccessible

le.Youcananalyzepartiallyorcompletelyplacedandrouteddesigns.Thetiming

informationdependsontheplacementandroutingoftheinputdesign.

YoucanrunstatictiminganalysisusingtheTimingReporterAndCircuitEvaluator

(TRACE)commandlineprogram.SeetheTRACEchapterfordetailedinformation.Y ou

canalsousetheTimingAnalyzertoperformthisfunction.SeetheHelpthatcomeswith

TimingAnalyzerforadditionalinformation.Useeithertooltoevaluatehowwellthe

placeandroutetoolsmettheinputtimingconstraints.

In-CircuitVerification

Asanaltest,youcanverifyhowyourdesignperformsinthetargetapplication.

In-circuitvericationteststhecircuitundertypicaloperatingconditions.Becauseyou

canprogramyourFPGAdevicesrepeatedly ,youcaneasilyloaddifferentiterationsof

yourdesignintoyourdeviceandtestitin-circuit.Toverifyyourdesignin-circuit,

downloadyourdesignbitstreamintoadevicewiththeappropriateXilinx®cable.

Chapter2:DesignFlow

NoteForinformationaboutXilinxcablesandhardware,seetheiMPACTonlinehelp.

DesignRuleChecker(FPGAsOnly)

Beforegeneratingthenalbitstream,itisimportanttousetheDRCoptioninBitGen

toevaluatetheNCDleforproblemsthatcouldpreventthedesignfromfunctioning

properly.DRCisinvokedautomaticallyunlessyouusethe-doption.SeethePhysical

DesignRuleCheckchapterandtheBitGenchapterfordetailedinformation.

Probe

TheXilinxPROBEfunctioninFPGAEditorprovidesreal-timedebugcapabilitygood

foranalyzingafewsignalsatatime.UsingPROBEadesignercanquicklyidentifyand

routeanyinternalsignalstoavailableI/Opinswithouthavingtoreplaceandroutethe

design.Thereal-timeactivityofthesignalcanthenbemonitoredusingnormallabtest

equipmentsuchaslogic/stateanalyzersandoscilloscopes.

ChipScope™ILAandChipScopePro

TheChipScopetoolsetwasdevelopedtoassistengineersworkingatthePCBlevel.

ChipScopeILAactuallyembedslogicanalyzercoresintoyourdesign.Theselogiccores

allowtheusertoviewalltheinternalsignalsandnodeswithinanFPGA.Triggersare

changeableinreal-timewithoutaffectingtheuserlogicorrequiringrecompilation

oftheuserdesign.

FPGADesignTips

TheXilinx®FPGAarchitectureisbestsuitedforsynchronousdesign.Strictsynchronous

designensuresthatallregistersaredrivenfromthesametimebasewithnoclockskew.

Thissectiondescribesseveraltipsforproducinghigh-performancesynchronousdesigns.

CommandLineToolsUserGuide

UG628(v13.1)March2,2011w

w w . x i l i n x . c o m 31

Page 32

Chapter2:DesignFlow

DesignSizeandPerformance

Informationaboutdesignsizeandperformancecanhelpyoutooptimizeyourdesign.

Whenyouplaceandrouteyourdesign,theresultingreportleslistthenumberof

CLBs,IOBs,andotherdeviceresourcesavailable.Arstpassestimatecanbeobtained

byprocessingthedesignthroughtheMAPprogram.

Ifyouwanttodeterminethedesignsizeandperformancewithoutrunningautomatic

implementationsoftware,youcanquicklyobtainanestimatefromaroughcalculation

basedontheXilinxFPGAarchitecture.

32w

CommandLineToolsUserGuide

w w . x i l i n x . c o m UG628(v13.1)March2,2011

Page 33

PARTGen

ThischapterdescribesPARTGen.

PARTGenOverview

PARTGenisaXilinx®commandlinetoolthatdisplaysarchitecturaldetailsabout

supportedXilinxdevices.

DeviceSupport

Thisprogramiscompatiblewiththefollowingdevicefamilies:

•7series

•Spartan®-3,Spartan-3A,Spartan-3E,andSpartan-6

•Virtex®-4,Virtex-5,andVirtex-6

•CoolRunner™XPLA3andCoolRunner-II

•XC9500andXC9500XL

Chapter3

PARTGenInputFiles

PARTGendoesnothaveanyuserinputles.

PARTGenOutputFiles

PARTGenoutputstwoletypes:

•PARTGenPartlistFiles(ASCIIandXML)

•PARTGenPackageFiles(ASCII)

PARTGenPartlistFiles

PARTGenpartlistlescontaindetailedinformationaboutarchitecturesanddevices,

includingsupportedsynthesistools.PartlistlesaregeneratedinbothASCII(.xct)

andXML(.xml)formats.

ThepartlistleisautomaticallygeneratedinXMLformatwheneverapartlistleis

createdwiththePARTGen-p(GeneratePartlistandPackageFiles)orPARTGen-v

(GeneratePartlistandPackageFiles)options.Noseparatecommandlineoptionis

required.

CommandLineToolsUserGuide

UG628(v13.1)March2,2011w

w w . x i l i n x . c o m 33

Page 34

Chapter3:PARTGen

Thepartlistleisaseriesofpartentries.Thereisoneentryforeverypartsupported

intheinstalledsoftware.Thefollowingsectionsdescribetheinformationcontained

inthepartlistle.

•PARTGenPartlistFileHeader

•PARTGenPartlistFileDeviceAttributesforBoth-pand-vOptions

•PARTGenPartlistFileDeviceAttributesfor-vOptionOnly

PARTGenPartlistFileHeader

TherstpartofaP ARTGenpartlistleisaheaderfortheentry .

partarchitecturefamilypartnamedienamepackagefilename

PARTGenPartlistFileHeaderExampleforXC6VLX550TFF1759Device

partVIRTEXXC6VLX550Tff1759NA.diexc6vlx550tff1759.pkg

PARTGenPartlistFileDeviceAttributesforboth-pand-vOptions

ThefollowingPARTGenpartlistledeviceattributesdisplayforboththe-pand-v

commandlineoptions.

•CLBrowandcolumnsizes

NCLBROWS=#NCLBCOLS=#

•Sub-familydesignation

STYLE=sub_family(Forexample,STYLE=Virtex6)

•Inputregisters

IN_FF_PER_IOB=#

•Outputregisters

OUT_FF_PER_IOB=#

•Numberofpadsperrowandpercolumn

NPADS_PER_ROW=#NP ADS_PER_COL=#

•Bitstreaminformation

–Numberofframes:NFRAMES=#

–Numberbits/frame:NBITSPERFRAME=#

•Steppinglevelssupported:STEP=#

•I/OStandards

ForeachI/Ostandard,PARTGennowreportsallpropertiesinaparsableformat.

ThisallowsthirdpartytoolstoperformcompleteI/Obankingdesignruleschecking

(DRC).

Thefollowinginformationhasbeenaddedtothepartlist.xctand

partlist.xmloutputforeachavailableI/Ostandard:

IOSTD_NAME:LVTTL\

IOSTD_DRIVE:1224681624\

IOSTD_SLEW:SLOWFAST\

IOSTD_DIRECTION:INPUT=1OUTPUT=1BIDIR=1\

IOSTD_INPUTTERM:NONE\

IOSTD_OUTPUTTERM:NONE\

IOSTD_VCCO:3.300000\

IOSTD_VREF:100.000000\

IOSTD_VRREQUIRED:0\

IOSTD_DIFFTERMREQUIRED:0\

34w

CommandLineToolsUserGuide

w w . x i l i n x . c o m UG628(v13.1)March2,2011

Page 35

Chapter3:PARTGen

ForIOSTD_DRIVEandIOSTD_SLEW,thedefaultvaluesarereportedrstinthe

list.Fortrue/falsevalues:

–1indicatestrue

–0indicatesfalse

Avalueof100.000000forIOSTD_VREFindicatesthatthiskeywordisundened

forthisstandard.

•SOandWASSOCalculations

PARTGennowexportsI/Ostandardanddevicepropertiesinamachinereadable

format.ThisallowsthirdpartytoolstoperformSSOandW ASSOcalculations.

SSOdataconsistsoftwoparts:

–ThemaximumnumberofSSOsallowedperpower/groundpair

–Thenumberofpower/groundpairsforagivenbank.

Thisdatahasbeenaddedtothepartlist.xctandpartlist.xmloutputfor

eachdevice/packagecombination.Thenumberofpower/groundpairsislisted

bybanknumber:

PER_BANK_PWRGND_PAIRS\

BANK_SSONAME=0TYPE=INT1\

BANK_SSONAME=1TYPE=INT1\

BANK_SSONAME=2TYPE=INT1\

BANK_SSONAME=3TYPE=INT1\

BANK_SSONAME=4TYPE=INT1\

BANK_SSONAME=5TYPE=INT5\

BANK_SSONAME=6TYPE=INT5\

BANK_SSONAME=7TYPE=INT3\

BANK_SSONAME=8TYPE=INT3\

ThemaximumnumberofSSOsallowedperpower/groundpairisreportedusing

theSSO_PER_IOSTDkeyword.EachentryreectsthemaximumnumberofSSOs

(column6)fortheI/Ostandard(column3),drivestrength(column2),andslew

rate(column4)shown.

Forexample,L VTTL,withdrivestrength12andslewrateSLOW ,hasamaximumof

15SSOsperpower/groundpair.

MAX_SSO_PER_IOSTD_PER_BANK\

IOSTD_SSODRIVE=12NAME=LVTTLSLEW=SLOWTYPE=INT15\

IOSTD_SSODRIVE=12NAME=LVTTLSLEW=FASTTYPE=INT10\

IOSTD_SSODRIVE=2NAME=LVTTLSLEW=SLOWTYPE=INT68\

IOSTD_SSODRIVE=2NAME=LVTTLSLEW=FASTTYPE=INT40\

IOSTD_SSODRIVE=4NAME=LVTTLSLEW=SLOWTYPE=INT41\

IOSTD_SSODRIVE=4NAME=LVTTLSLEW=FASTTYPE=INT24\

IOSTD_SSODRIVE=6NAME=LVTTLSLEW=SLOWTYPE=INT29\

IOSTD_SSODRIVE=6NAME=LVTTLSLEW=FASTTYPE=INT17\

IOSTD_SSODRIVE=8NAME=LVTTLSLEW=SLOWTYPE=INT22\

IOSTD_SSODRIVE=8NAME=LVTTLSLEW=FASTTYPE=INT13\

IOSTD_SSODRIVE=16NAME=LVTTLSLEW=SLOWTYPE=INT11\

IOSTD_SSODRIVE=16NAME=LVTTLSLEW=FASTTYPE=INT8\

IOSTD_SSODRIVE=24NAME=LVTTLSLEW=SLOWTYPE=INT7\

IOSTD_SSODRIVE=24NAME=LVTTLSLEW=FASTTYPE=INT5\

•Deviceglobal,localandregionalclockingproperties

Foreachtypeofclockavailableonthedevice,PARTGennowreports:

–Whichpinnumbercanbehaveaswhichclocktype

–WhichI/Ocanbedrivenbythisclockpin

CommandLineToolsUserGuide

UG628(v13.1)March2,2011w

w w . x i l i n x . c o m 35

Page 36

Chapter3:PARTGen

ThisallowsthirdpartytoolstoassignpinsonXilinx®packageswithoutviolating

clockingrules.

Thefollowinginformationhasbeenaddedtothepartlist.xctand

partlist.xmloutputforeachclockregionofadevice:

DEVICE_CLKRGN\

NUM_CLKRGNTYPE=INT8\

NUM_CLKRGN_ROWTYPE=INT4\

NUM_CLKRGN_COLTYPE=INT2\

CLKRGNTYPE=STRINGX0Y0\

CLK_CAPABLE_SCOPE\

UNASSOCIATED_PINS\

NUM_UNBONDED_PINSTYPE=INT2\

UNBONDED_PIN_LISTTYPE=STRINGLISTT17R17\

UNBONDED_IOB_LISTTYPE=STRINGLISTIOB_X0Y15IOB_X0Y17\

ASSOCIATED_BUFIO\

NUM_BUFIOTYPE=INT4\

BUFIO_SITESTYPE=STRINGLISTBUFIO_X0Y0BUFIO_X0Y1BUFIO_X1Y0BUFIO_X1Y1\

ASSOCIATED_BUFR\

NUM_BUFRTYPE=INT2\

BUFR_SITESTYPE=STRINGLISTBUFR_X0Y0BUFR_X0Y1\

ASSOCIATED_PINS\

NUM_BONDED_PINSTYPE=INT39\

BONDED_PIN_LISTTYPE=STRINGLISTV18V17W17Y17W19W18U17U16V20V19U15T15U19U18T18\

T17R18R17T20T19R16R15R20R19W8W9Y9Y10W7Y7W10W11W6Y6Y11Y12W5Y5W12\

BONDED_IOB_LISTTYPE=STRINGLISTIOB_X0Y0IOB_X0Y1IOB_X0Y2IOB_X0Y3IOB_X0Y4IOB_X0Y5IOB_\

X0Y6IOB_X0Y7IOB_X0Y8IOB_X0Y9IOB_X0Y10IOB_X0Y11IOB_X0Y12IOB_X0Y13IOB_X0Y14IOB_\

X0Y15IOB_X0Y16IOB_X0Y17IOB_X0Y18IOB_X0Y19IOB_X0Y22IOB_X0Y23IOB_X0Y24IOB_X0Y25IOB_\

X1Y16IOB_X1Y17IOB_X1Y18IOB_X1Y19IOB_X1Y20IOB_X1Y21IOB_X1Y22IOB_X1Y23IOB_X1Y24IOB_\

X1Y25IOB_X1Y26IOB_X1Y27IOB_X1Y28IOB_X1Y29IOB_X1Y30\

PARTGenPartlistFileDeviceAttributesforpartgen-vOptionOnly

ThefollowingPARTGenpartlistledeviceattributesdisplayforthe-vcommand

lineoptiononly.

•NumberofIOBSindevice

NIOBS=#

•NumberofbondedIOBS

NBIOBS=#

•SlicesperCLB:SLICES_PER_CLB=#

Forslice-basedarchitectures.Fornon-slicebasedarchitectures,assumeoneslice

perCLB.

•Flip-opsforeachslice

FFS_PER_SLICE=#

•Latchesforeachslice

CANBELATCHES={TRUE|FALSE}

•NumberofDCMs,PLLsand/orMMCMs

•LUTsinaslice:LUT_NAME=nameLUT_SIZE=#

•Numberofglobalbuffers:NUM_GLOBAL_BUFFERS=#

(Thenumberofplaceswhereabuffercandriveaglobalclockcombination)

•BlockRAM

36w

CommandLineToolsUserGuide

w w . x i l i n x . c o m UG628(v13.1)March2,2011

Page 37

Chapter3:PARTGen

NUM_BLK_RAMS=#BLK_RAM_COLS=#BLK_RAM_COL0=#BLK_RAMCOL1=#

BLK_RAM_COL2=#BLK_RAM_COL_3=#BLK_RAM_SIZE=4096x1

BLK_RAM_SIZE=2048x2BLK_RAM_SIZE=512x8BLK_RAM_SIZE=256x16

BlockRAMlocationsaregivenwithreferencetoCLBcolumns.Inthefollowing

example,BlockRAM5ispositionedinCLBcolumn32.

NUM_BLK_RAMS=10BLK_RAM_COL_5=32BLK_RAM_SIZE=4096X1

•SelectRAM

NUM_SEL_RAMS=#SEL_RAM_SIZE=#X#

•SelectDualPortRAM

SEL_DP_RAM={TRUE|FALSE}

ThiseldindicateswhethertheselectRAMcanbeusedasadualportram.The

assumptionisthatthenumberofaddressableelementsisreducedbyhalf,thatis,the

sizeoftheselectRAMinDualPortModeishalfthatindicatedbySEL_RAM_SIZE.

•Speedgradeinformation:SPEEDGRADE=#

DelaysinformationnolongerappearsintheXCTandXMLpartlistles.Delay

informationcanbeobtainedusingSpeedprint.Formoreinformation,seethe

Speedprintchapterinthisdocument.

•MaximumLUTconstructedinaslice

MAX_LUT_PER_SLICE=#(FromalltheLUTsintheslice)

•MaxLUTconstructedinaCLB:MAX_LUT_PER_CLB=#

ThiselddescribeshowwideaLUTcanbeconstructedintheCLBfromthe

availableLUTsintheslice.

•Numberofinternaltristatebuffersinadevice

NUM_TBUFSPERROW=#

•Ifavailableonaparticulardeviceorpackage,PartGenreports:

PARTGenPackageFiles

PARTGenpackagelesareASCIIformattedlesthatcorrelateIOBswithoutput

pinnames.PackagelesareinXACTpackageformat,whichisasetofcolumnsof

informationaboutthepinsofaparticularpackage.The-p(terse)commandlineoption

generatesathreecolumnentrydescribingthepins.The-v(verbose)commandline

optionaddssixmorecolumnsdescribingthepins.Thefollowingsectionsdescribethe

informationcontainedinthepackageles.

•PARTGenPackageFilesWiththe-pOption

•PARTGenPackageFilesWiththe-vOption

PARTGenPackageFilesUsingthe-pOption

Thepartgen-pcommandlineoptiongeneratespackagelesanddisplaysa

three-columnentrydescribingthepins.Seethefollowingtable.

NUM_PPC=#

NUM_GT=#

NUM_MONITOR=#

NUM_DPM=#

NUM_PMCD=#

NUM_DSP=#

NUM_FIFO=#

NUM_EMAC=#

NUM_MULT=#

CommandLineToolsUserGuide

UG628(v13.1)March2,2011w

w w . x i l i n x . c o m 37

Page 38

Chapter3:PARTGen

PackageFilesColumnDescriptions

ColumnContentsDescription

1

2

3

Forexample,thecommandpartgen-pxc6vlx75tgeneratesthefollowingpackage

les:

•xc6vlx75tff484.pkg

•xc6vlx75tff784.pkg

PackageFileExampleUsingthe-pOption

Followingisanexampleofaportionofthepackageleforanxc6vlx75tff484package:

pin(useraccessiblepin)orpkgpin

(dedicatedpin)

pinname

packagepinSpeciesthepackagepin

Containseitherpin(useraccessiblepin)

orpkgpin(dedicatedpin)

Foruseraccessiblepins,thenameofthe

pinisthebondedpadnameassociated

withanIOBonthedevice,orthename

ofamulti-purposepin.Fordedicated

pins,thenameiseitherthefunctional

nameofthepin,ornoconnection(N.C.

packagexc6vlx75tff484

pinIPAD_X1Y25G3

pinIPAD_X0Y31M11

pinIOB_X0Y39M18

.

.

.

PARTGenPackageFilesUsingthe-vOption

Thepartgen-vcommandlineoptiongeneratespackagelesanddisplaysa

nine-columnentrydescribingthepins.Seethefollowingtable.

PackageFilesColumnDescriptions

ColumnContentsDescription

1

2

3

4

5

6

pin(useraccessiblepin)orpkgpin

(dedicatedpin)

pinname

packagepinSpeciesthepackagepin

VREFBANK

VCCOBANK

functionnameConsistsofastringindicatinghowthe

Containseitherpin(useraccessiblepin)

orpkgpin(dedicatedpin)

Foruseraccessiblepins,thenameofthe

pinisthebondedpadnameassociated

withanIOBonthedevice,orthename

ofamulti-purposepin.Fordedicated

pins,thenameiseitherthefunctional

nameofthepin,ornoconnection(N.C.

Apositiveintegerassociatedwith

therelativebank,or1fornobank

association

Apositiveintegerassociatedwith

therelativebank,or1fornobank

association

pinisused.Ifthepinisdedicated,

thenthestringwillindicateaspecic

function.Ifthepinisagenericuser

38w

CommandLineToolsUserGuide

w w . x i l i n x . c o m UG628(v13.1)March2,2011

Page 39

ColumnContentsDescription

7

8

9

CLB

LVDSIOB

ight-timedataFlight-timedatainunitsofmicrons.

PARTGenVerbosePinDescriptorsExample

FollowingareexamplesoftheverbosepindescriptorsinPARTGen.

Chapter3:PARTGen

pin,thestringis“IO”.Ifthepinis

multipurpose,anunderscore-separated

setofcharacterswillmakeupthestring

ClosestCLBroworcolumntothepin,

andappearsintheform

R[0-9]C[0-9]orx[0-9]y[0-9]

Astringforeachpinassociatedwitha

LVDSIOB.Thestringconsistsofand

indexandtheletterMorS.Indexvalues

willgofrom0tothenumberofL VDS

pairs.Thevalueforanon-L VDSpin

defaultstoN.A.

Ifnoight-timedataisavailable,this

columncontainsN/A.

packagexc6vlx75tff484

#PartGenL.44

#padpinvrefvccofunctionnearestdiff.tracelength

#namenamebankbanknameCLBpair(um)

pinIPAD_X1Y25G3-1-1MGTRXP0_115N.A.N.A.8594

pinIPAD_X0Y31M1100VN_0N.A.N.A.1915

pinIOB_X0Y39M181414IO_L0P_14X0Y380M4111

pinIOB_X0Y38N181414IO_L0N_14X0Y380S3390

PARTGenSyntax

ThePARTGencommandlinesyntaxis:

partgenoptions

optionscanbeanynumberoftheoptionslistedinP ARTGenCommandLineOptions.

Enteroptionsinanyorder,precededthemwithadash(minussignonthekeyboard)

andseparatethemwithspaces.

Bothpackageandpartlistlescanbegeneratedusingthepartgen-p(terse)and

partgen-v(verbose)options.

•partgen-pgeneratesathreecolumnentrydescribingthepins.

•partgen-vaddssixmorecolumnsdescribingthepins.

PARTGenCommandLineOptions

ThissectiondescribesthePARTGencommandlineoptions.

•PARTGen–arch(OutputInformationforSpeciedArchitecture)

•PARTGen–i(OutputListofDevices,Packages,andSpeeds)

•PARTGen–intstyle(SpecifyIntegrationStyle)

•PARTGen–nopkgle(GenerateNoPackageFile)

•PARTGen–p(GeneratePartlistandPackageFiles)

•PARTGen–v(GeneratePartlistandPackageFiles)

CommandLineToolsUserGuide

UG628(v13.1)March2,2011w

w w . x i l i n x . c o m 39

Page 40

Chapter3:PARTGen

-arch(OutputInformationforSpecifiedArchitecture)

Thisoptionoutputsalistofdevices,packages,andspeedsforaspeciedarchitecture.

Syntax

-archarchitecture_name

Allowedvaluesforarchitecture_nameare:

•acr2(forAutomotiveCoolRunner™-II)

•aspartan3(forAutomotiveSpartan®-3)

•aspartan3a(forAutomotiveSpartan-3A)

•aspartan3adsp(forAutomotiveSpartan-3ADSP)

•aspartan3e(forAutomotiveSpartan-3E)

•aspartan6(forAutomotiveSpartan-6)

•kintex7(forKintex™-7)

•kintex7l(forKintex-7LowerPower)

•qrvirtex4(forQPro™Virtex®-4RadTolerant)

•qvirtex4(forQProVirtex-4Hi-Rel)

•qvirtex5(forQProVirtex-5Hi-Rel)

•qspartan6(forQProSpartan-6Hi-Rel)

•qvirtex6(forQProVirtex-6Hi-Rel)

•spartan3(forSpartan-3)

•spartan3a(forSpartan-3A)

•spartan3adsp(forSpartan-3ADSP)

•spartan3e(forSpartan-3E)

•spartan6(forSpartan-6)

•virtex4(forVirtex-4)

•virtex5(forVirtex-5)

•virtex6(forVirtex-6)

•virtex6l(forVirtex-6LowerPower)

•virtex7(forVirtex-7)

•virtex7l(forVirtex-7LowerPower)

•xa9500xl(forAutomotiveXC9500XL)

•xbr(forCoolRunner-II)

•xc9500(forXC9500)

•xc9500xl(forXC9500XL)

•xpla3(forCoolRunnerXPLA3)

-i(OutputListofDevices,Packages,andSpeeds)

Thisoptionoutputsalistofdevices,packages,andspeedsforeveryinstalleddevice.

Syntax

-i

40w

CommandLineToolsUserGuide

w w . x i l i n x . c o m UG628(v13.1)March2,2011

Page 41

-intstyle(IntegrationStyle)

Thisoptionlimitsscreenoutput,basedontheintegrationstylethatyouarerunning,to

warninganderrormessagesonly.

Syntax

-intstyleise|xflow|silent

Whenusing-intstyle,oneofthreemodesmustbespecied:

•-intstyleiseindicatestheprogramisbeingrunaspartofanintegrateddesign

environment.

•-intstylexflowindicatestheprogramisbeingrunaspartofanintegrated

batchow.

•-intstylesilentlimitsscreenoutputtowarninganderrormessagesonly.

Note-intstyleisautomaticallyinvokedwhenrunninginanintegratedenvironment

suchasProjectNavigatororXFLOW.

-nopkgfile(GenerateNoPackageFile)

Chapter3:PARTGen

Thisoptioncancelstheproductionofthepackageleswhenthe-pand-voptionsare

used.The-nopkgfileoptionallowsyoutobypasscreatingpackageles.

Syntax

-nopkgfile

-p(GeneratePartlistandPackageFiles)

Thiscommandlineoptiongenerates:

•PartlistlesinASCII(.xct)andXML(.xml)formats

•PackagelesinASCII(.pkg)format

Syntax

-pname

Validentriesfornameinclude:

•architectures

•devices

•parts

Alllesareplacedintheworkingdirectory.

Ifanarchitecture,device,orpartisnotspeciedwiththisoption,detailedinformation

foreveryinstalleddeviceissubmittedtothepartlist.xctle.Formoreinformation,

seePARTGenPartlistFiles.

The-poptiongeneratesmoredetailedinformationthanthe-archoption,butless

informationthanthe-voption.The-pand-voptionsaremutuallyexclusive.Youcan

specifyoneortheotherbutnotboth.Formoreinformationsee:

•PARTGenPackageFiles

•PARTGenPartlistFiles

CommandLineToolsUserGuide

UG628(v13.1)March2,2011w

w w . x i l i n x . c o m 41

Page 42

Chapter3:PARTGen

-v(GeneratePartlistandPackageFiles)

ExamplesofValidCommandLineEntries

NameExampleCommandLineEntry

architecture

device

part

-pvirtex5

-pxc5vlx110t

-pxc5vlx110tff1136

Thiscommandlineoptiongenerates:

•PartlistlesinASCII(.xct)andXML(.xml)formats

•PackagelesinASCII(.pkg)format

Syntax

-vname

Validentriesfornameinclude:

•architectures

•devices

•parts

Ifnoarchitecture,device,orpartisspeciedwiththe-voption,informationforevery

installeddeviceissubmittedtothepartlistle.Formoreinformation,seePARTGen

PartlistFiles.

The-voptiongeneratesmoredetailedinformationthanthe-poption.The-pand-v

optionsaremutuallyexclusive.Youcanspecifyoneortheotherbutnotboth.For

moreinformation,see:

•PARTGenPackageFiles