TLC556, TLC556Y

DUAL LinCMOS TIMERS

SLFS047B – FEBRUARY 1984 – REVISED SEPTEMBER 1997

D

Very Low Power Consumption ...2 mW

Typ at VDD = 5 V

D

Capable of Operation in Astable Mode

D

CMOS Output Capable of Swinging Rail to

Rail

D

High Output-Current Capability

Sink 100 mA Typ

Source 10 mA Typ

D

Output Fully Compatible With CMOS, TTL,

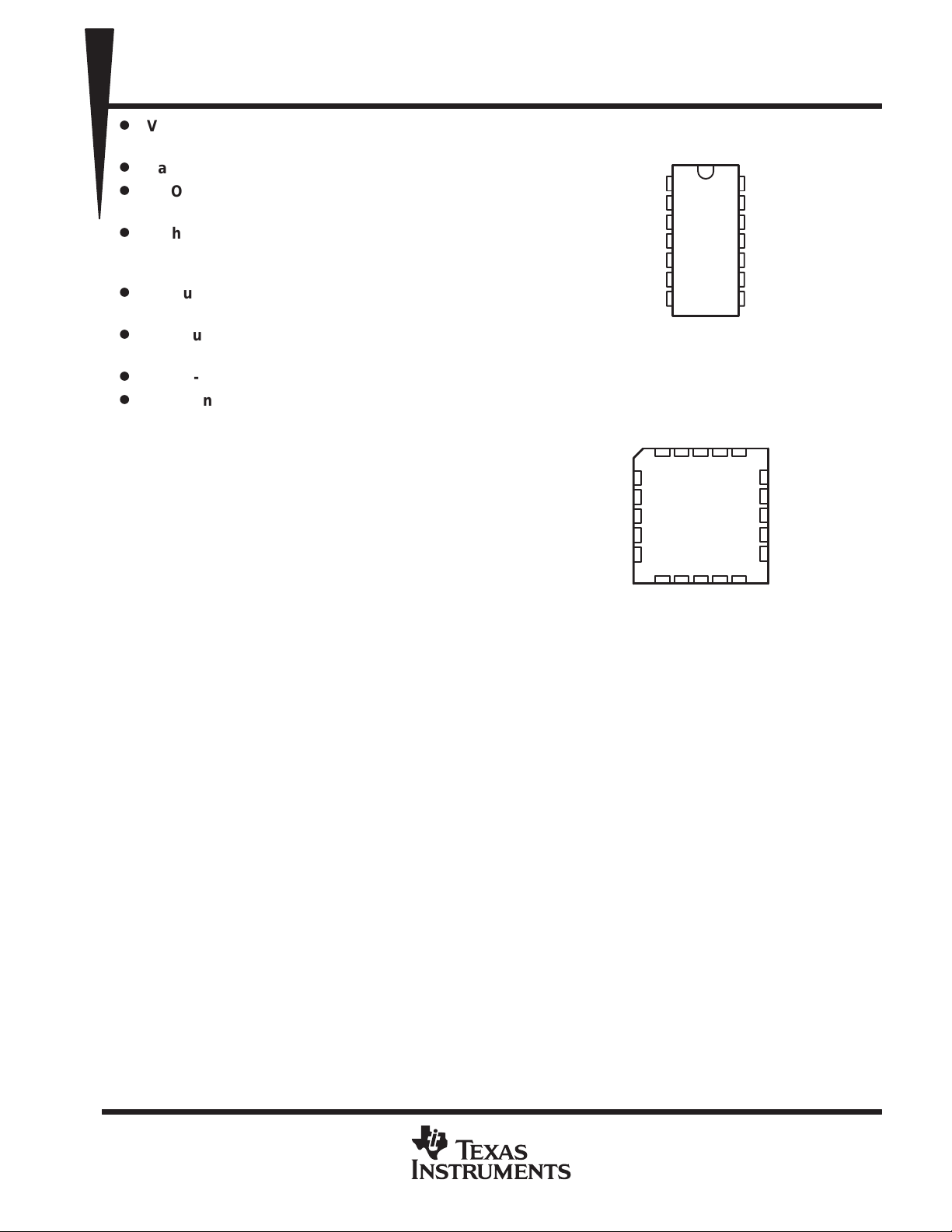

D, J, OR N PACKAGE

(TOP VIEW)

1 DISCH

1 THRES

1 CONT

1 RESET

1 OUT

1 TRIG

GND

1

2

3

4

5

6

7

13

12

11

10

9

8

DD

2 DISCH

2 THRES

2 CONT

2 RESET

2 OUT

2 TRIG

V

14

and MOS

D

Low Supply Current Reduces Spikes

During Output Transitions

D

Single-Supply Operation From 2 V to 15 V

D

Functionally interchangeable With the

NE556; Has Same Pinout

description

The TLC556 series are monolithic timing circuits

fabricated using the TI LinCMOS process, which

provides full compatibility with CMOS, TTL, and

MOS logic and operates at frequencies up to

2 MHz. Accurate time delays and oscillations are

1 CONT

NC

1 RESET

NC

1 OUT

FK PACKAGE

(TOP VIEW)

1 THRES

1 DISCH

NC

3 2 1 20 19

4

5

6

7

8

910111213

DD

V

2 DISCH

18

17

16

15

14

2 THRES

NC

2 CONT

NC

2 RESET

possible with smaller, less-expensive timing

capacitors than the NE556 because of the high

input impedance. Power consumption is low

across the full range of power supply voltages.

Like the NE556, the TLC556 has a trigger level

NC–No internal connection

GND

1 TRIG

NC

2 OUT

2 TRIG

approximately one-third of the supply voltage and

a threshold level approximately two-thirds of the supply voltage. These levels can be altered by use of the control

voltage terminal. When the trigger input falls below the trigger level, the flip-flop is set and the output goes high.

If the trigger input is above the trigger level and the threshold input is above the threshold level, the flip-flop is

reset and the output is low. The reset input can override all other inputs and can be used to initiate a new timing

cycle. If the reset input is low, the flip-flop is reset and the output is low. Whenever the output is low, a

low-impedance path is provided between the discharge terminal and ground.

While the CMOS output is capable of sinking over 100 mA and sourcing over 10 mA, the TLC556 exhibits greatly

reduced supply-current spikes during output transitions. This minimizes the need for the large decoupling

capacitors required by the NE556.

These devices have internal electrostatic-discharge (ESD) protection circuits that prevent catastrophic failures

at voltages up to 2000 V as tested under MIL-STD-883C, Method 3015. However, care should be exercised in

handling these devices, as exposure to ESD may result in degradation of the device parametric performance.

All unused inputs should be tied to an appropriate logic level to prevent false triggering.

The TLC556C is characterized for operation from 0°C to 70°C. The TLC556I is characterized for operation from

–40°C to 85°C. The TLC556M is characterized for operation over the full military temperature range of –55°C

to 125°C.

LinCMOS is a trademark of Texas Instruments Incorporated.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Copyright 1997, Texas Instruments Incorporated

1

TLC556, TLC556Y

T

V

CHIP FORM

DUAL LinCMOS TIMERS

SLFS047B – FEBRUARY 1984 – REVISED SEPTEMBER 1997

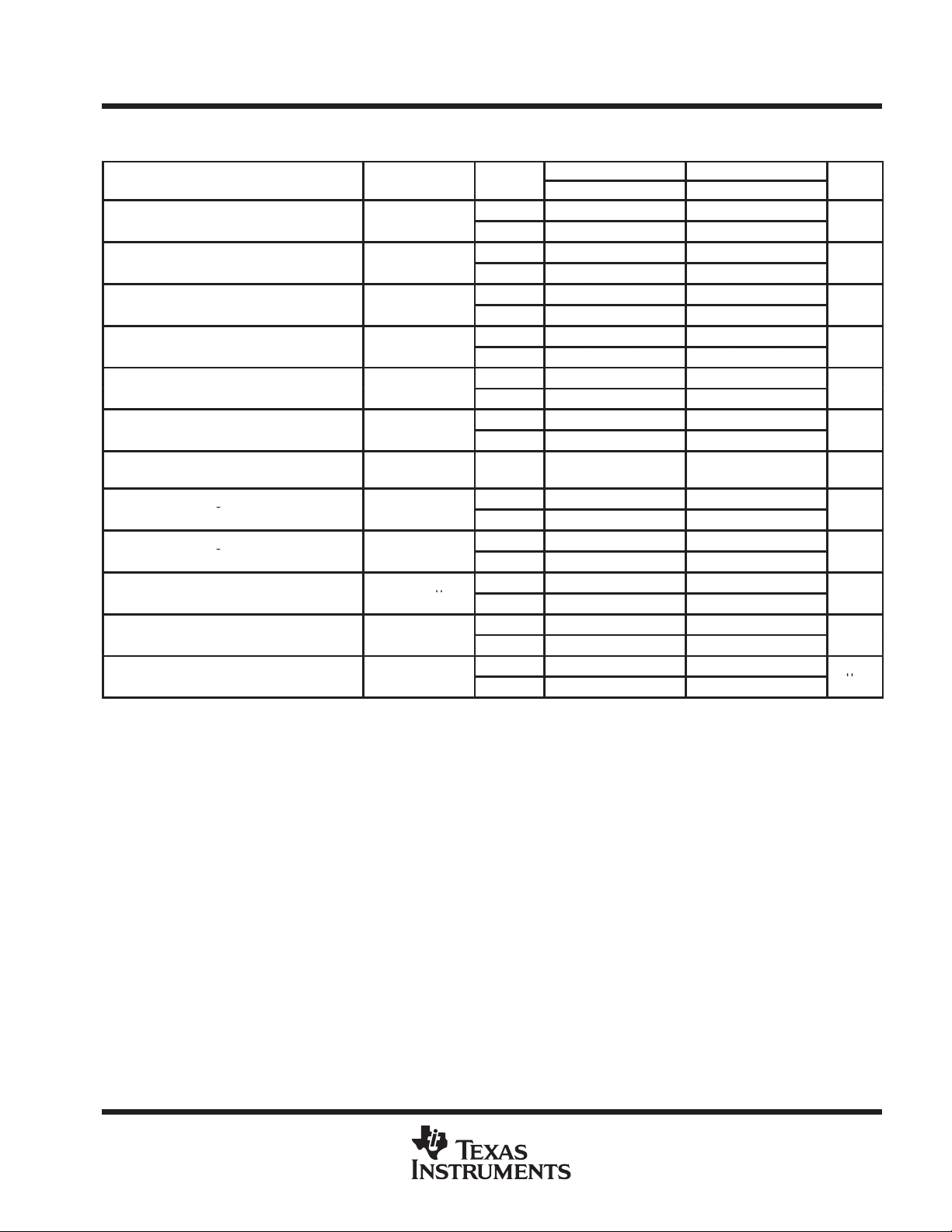

AVAILABLE OPTIONS

A

RANGE

O°C

to

70°C

–4O°C

to

85°C

–55°C

to

125°C

The D package is available taped and reeled. Add the suffix R to the device type (e.g., TLC556CDR).

†

DD

RANGE

2 V

to

18 V

3 V

to

18 V

5 V

to

18 V

RESET

VOLTAGE

< MIN Irrelevant Irrelevant L On

> MAX < MIN Irrelevant H Off

>MAX >MAX >MAX L On

> MAX > MAX < MIN As previously established

For conditions shown as MIN or MAX, use the appropriate value specified under electrical characteristics.

SMALL OUTLINE

(D)

TLC556CD TLC556CN TLC556Y

TLC556lD TLC556IN

TLC556MD TLC556MFK TLC556MJ TLC556MN

†

TRIGGER

VOLTAGE

CHIP CARRIER

FUNCTION TABLE

†

PACKAGE

(FK)

THRESHOLD

VOLTAGE

†

CERAMIC DIP

(J)

OUTPUT

PLASTIC DIP

(N)

DISCHARGE

SWITCH

(Y)

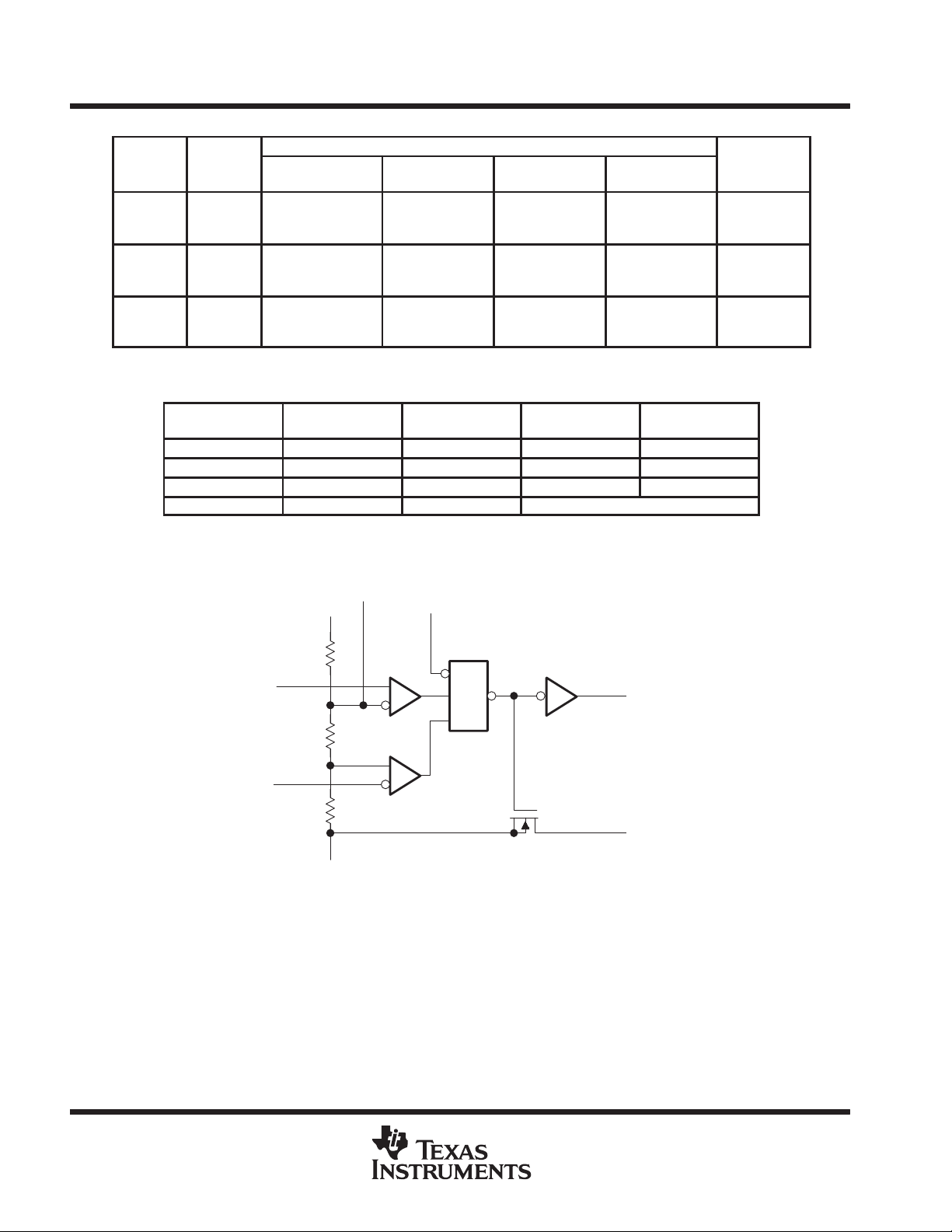

functional block diagram (each timer)

CONT

V

DD

14

R

THRES

TRIG

RESET can override TRIG and THRES.

TRIG can override THRES.

Pin numbers shown are for the D, J, or N packages.

2

R

6

R

7

GND

RESET

3

4

R1

RS1

5

OUT

1

DISCH

2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TLC556, TLC556Y

DUAL LinCMOS TIMERS

SLFS047B – FEBRUARY 1984 – REVISED SEPTEMBER 1997

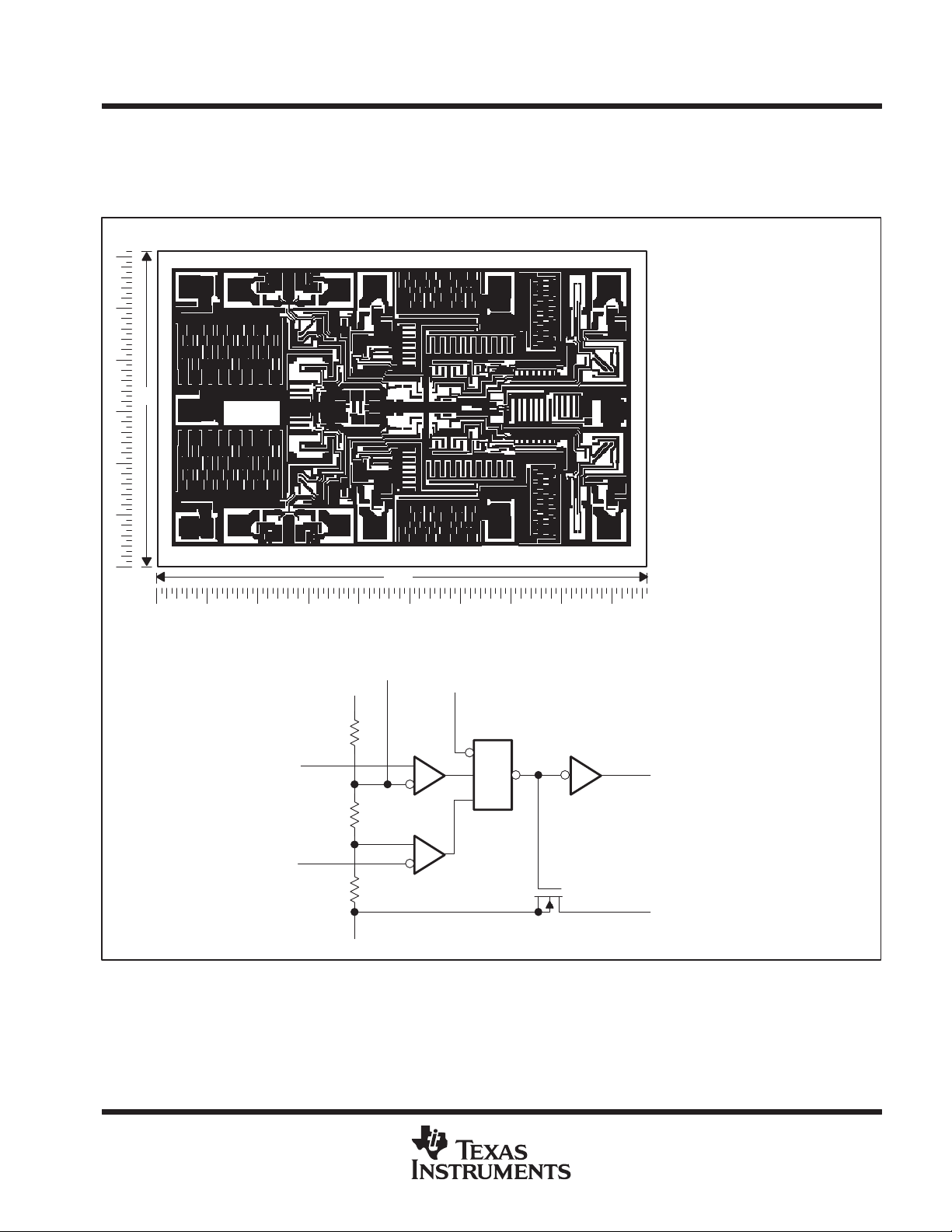

TLC556Y chip information

These chips, properly assembled, display characteristics similar to the TLC556 (see electrical table). Thermal

compression or ultrasonic bonding may be used on the doped aluminum bonding pads. Chips may be mounted

with conductive epoxy or a gold-silicon preform.

BONDING PAD ASSIGNMENTS

CHIP THICKNESS: 15 TYPICAL

BONDING PADS: 4 × 4 MINIMUM

TJ max = 150°C

61

TOLERANCES ARE ±10%

ALL DIMENSIONS ARE IN MILS

NO BACKSIDE METALLIZATION

PIN (7) INTERNALLY CONNECTED

TO BACKSIDE OF CHIP

THRESH

TRIG

97

FUNCTIONAL BLOCK DIAGRAM (EACH TIMER)

(2)

(6)

(14)

V

DD

GND

CONT

R

R

R

(7)

(3)

RESET

(4)

R1

RS1

(5)

(1)

OUT

DISCH

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

3

TLC556, TLC556Y

DUAL LinCMOS TIMERS

SLFS047B – FEBRUARY 1984 – REVISED SEPTEMBER 1997

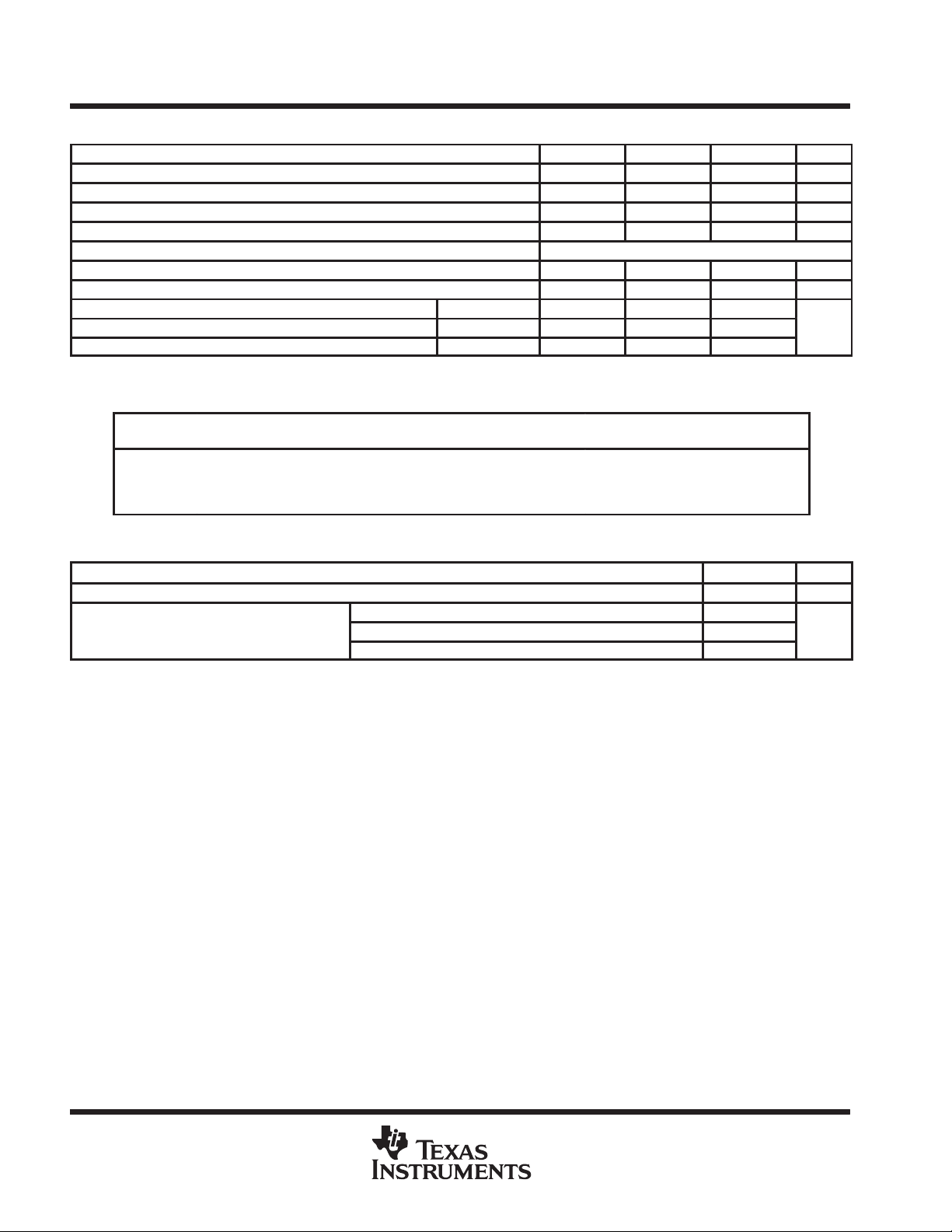

absolute maximum ratings over operating free-air temperature (unless otherwise noted)

TLC556C TLC556I TLC556M UNIT

Supply voltage, VDD (see Note 1) 18 18 18 V

Input voltage range, V

Sink current, discharge or output 150 150 150 mA

Source current, output 15 15 15 mA

Continuous total power dissipation See Dissipation Rating Table

Operating free-air temperature range 0 to 70 –40 to 85 –55 to 125 °C

Storage temperature range –65 to 150 –65 to 150 –65 to 150 °C

Case temperature for 60 seconds FK package 260

Lead temperature 1,6 mm (1/16 inch) from case for 60 seconds J package 300

Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds D or N package 260 260

NOTE 1: All voltage values are with respect to network ground terminal.

PACKAGE

D

FK

N

I

DISSIPATION RATING TABLE

TA ≤ 25°C

POWER RATING

950 mW

J

1375 mW

1375 mW

1150 mW

DERATING FACTOR

ABOVE TA = 25°C

7.6 mW/°C

11.0 mW/°C

11.0 mW/°C

9.2 mW/°C

TA = 70°C

POWER RATING

608 mW

880 mW

880 mW

736 mW

–0.3 to V

–0.3 to V

DD

TA = 85°C

POWER RATING

494 mW

715 mW

715 mW

598 mW

–0.3 to V

DD

TA = 125°C

POWER RATING

N/A

275 mW

275 mW

N/A

DD

V

°C

recommended operating conditions

Supply voltage, V

Operating free-air temperature range, T

DD

A

MIN MAX UNIT

2 15 V

TLC556C 0 70

TLC556I –40 85 °C

TLC556M –55 125

4

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

PARAMETER

T

†

UNIT

VITInput threshold voltage

V

Threshold current

pA

V

Trigger voltage

V

I

Trigger current

pA

V

Reset voltage

V

I

Reset current

pA

g

I

mA

V

g

nA

VOHHigh-level output voltage

I

300 µA

V

VOLLow-level output voltage

I

mA

V

IDDSupply current

See Note 2

A

TLC556, TLC556Y

DUAL LinCMOS TIMERS

SLFS047B – FEBRUARY 1984 – REVISED SEPTEMBER 1997

electrical characteristics at specified free-air temperature, VDD = 2 V for TLC556C, VDD = 3 V for

TLC556I

TEST

CONDITIONS

p

(trigger)

(trigger)

(reset)

(reset)

Control voltage (open circuit) as

a percentage of supply voltage

Discharge switch on-state voltage

Discharge switch off-state current

p

p

pp

†

Full range is 0°C to 70°C for TLC556C and –40°C to 85°C for TLC556I.

NOTE 2: These values apply for the expected operating configurations in which THRES is connected directly to DISCH or TRIG.

OL

OH

OL

= 1

= –

= 1

A

25°C 0.95 1.33 1.65 1.6 2 2.4

Full range 0.85 1.75 1.5 2.5

25°C 10 10

MAX 75 150

25°C 0.4 0.67 0.95 0.71 1 1.29

Full range 0.3 1.05 0.61 1.39

25°C 10 10

MAX 75 150

25°C 0.4 1.1 1.5 0.4 1.1 1.5

Full range 0.3 1.8 0.3 1.8

25°C 10 10

MAX 75 150

MAX 66.7% 66.7%

25°C 0.04 0.2 0.03 0.2

Full range 0.25 0.375

25°C 0.1 0.1

MAX 0.5 120

25°C 1.5 1.9 1.5 1.9

Full range 1.5 2.5

25°C 0.07 0.3 0.07 0.3

Full range 0.35 0.4

25°C 130 500 130 500

Full range 800 1000

TLC556C TLC556I

MIN TYP MAX MIN TYP MAX

p

p

p

µ

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

5

Loading...

Loading...