Texas Instruments TLC3704MJB, TLC3704MFKB, TLC3704MJ, TLC3704MD, TLC3704IPWR Datasheet

...

TLC3704, TLC3704Q

QUAD MICROPOWER LinCMOS VOLTAGE COMPARATORS

SLCS117A – NOVEMBER 1986 – REVISED OCT OBER 1996

1

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

D

Push-Pull CMOS Output Drives Capacitive

Loads Without Pullup Resistor,

I

O

= ± 8 mA

D

Very Low Power...200 µW Typ at 5 V

D

Fast Response Time ...t

PLH

= 2.7 µs Typ

With 5-mV Overdrive

D

Single Supply Operation...3 V to 16 V

TLC3704M ...4 V to 16 V

D

On-Chip ESD Protection

description

The TLC3704 consists of four independent

micropower voltage comparators designed to

operate from a single supply and be compatible

with modern HCMOS logic systems. They are

functionally similar to the LM339 but use 1/20th

the power for similar response times. The

push-pull CMOS output stage drives capacitive

loads directly without a power-consuming pullup

resistor to achieve the stated response time.

Eliminating the pullup resistor not only reduces

power dissipation, but also saves board space

and component cost. The output stage is also fully

compatible with TTL requirements.

Texas Instruments LinCMOS process offers

superior analog performance to standard CMOS

processes. Along with the standard CMOS

advantages of low power without sacrificing

speed, high input impedance, and low bias

currents, the LinCMOS process offers extremely

stable input offset voltages with large differential

input voltages. This characteristic makes it

possible to build reliable CMOS comparators.

The TLC3704C is characterized for operation over the commercial temperature range of 0°C to 70°C. The

TLC3704I is characterized for operation over the extended industrial temperature range of – 40°C to 85°C. The

TLC3704M is characterized for operation over the full military temperature range of – 55°C to 125°C. The

TLC3704Q is characterized for operation from – 40°C to 125°C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

LinCMOS is a trademark of Texas Instruments Incorporated.

Copyright 1996, Texas Instruments Incorporated

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

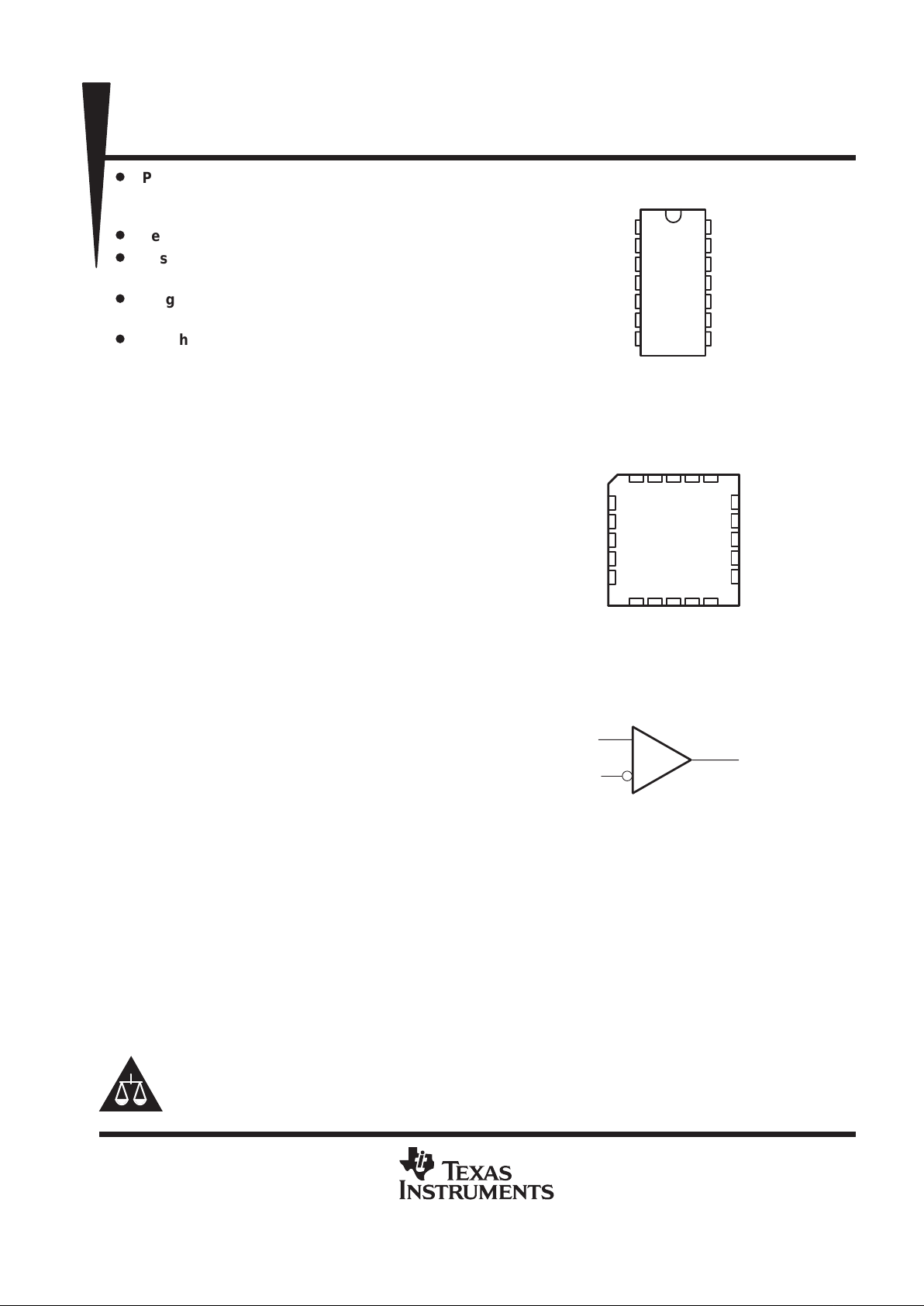

3 2 1 20 19

910111213

4

5

6

7

8

18

17

16

15

14

GND

NC

4IN+

NC

4IN–

V

DD

NC

2IN–

NC

2IN+

FK PACKAGE

(TOP VIEW)

2OUT

1OUT

NC

3IN–

3IN+

3OUT

4OUT

1IN+

NC

1IN–

D, J, OR N PACKAGE

(TOP VIEW)

NC – No internal connection

OUT

symbol (each comparator)

IN+

IN–

1

2

3

4

5

6

7

14

13

12

11

10

9

8

1OUT

2OUT

V

DD

2IN–

2IN+

1IN–

1IN+

3OUT

4OUT

GND

4IN+

4IN–

3IN+

3IN–

TLC3704, TLC3704Q

QUAD MICROPOWER LinCMOS VOLTAGE COMPARATORS

SLCS117A – NOVEMBER 1986 – REVISED OCT OBER 1996

2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

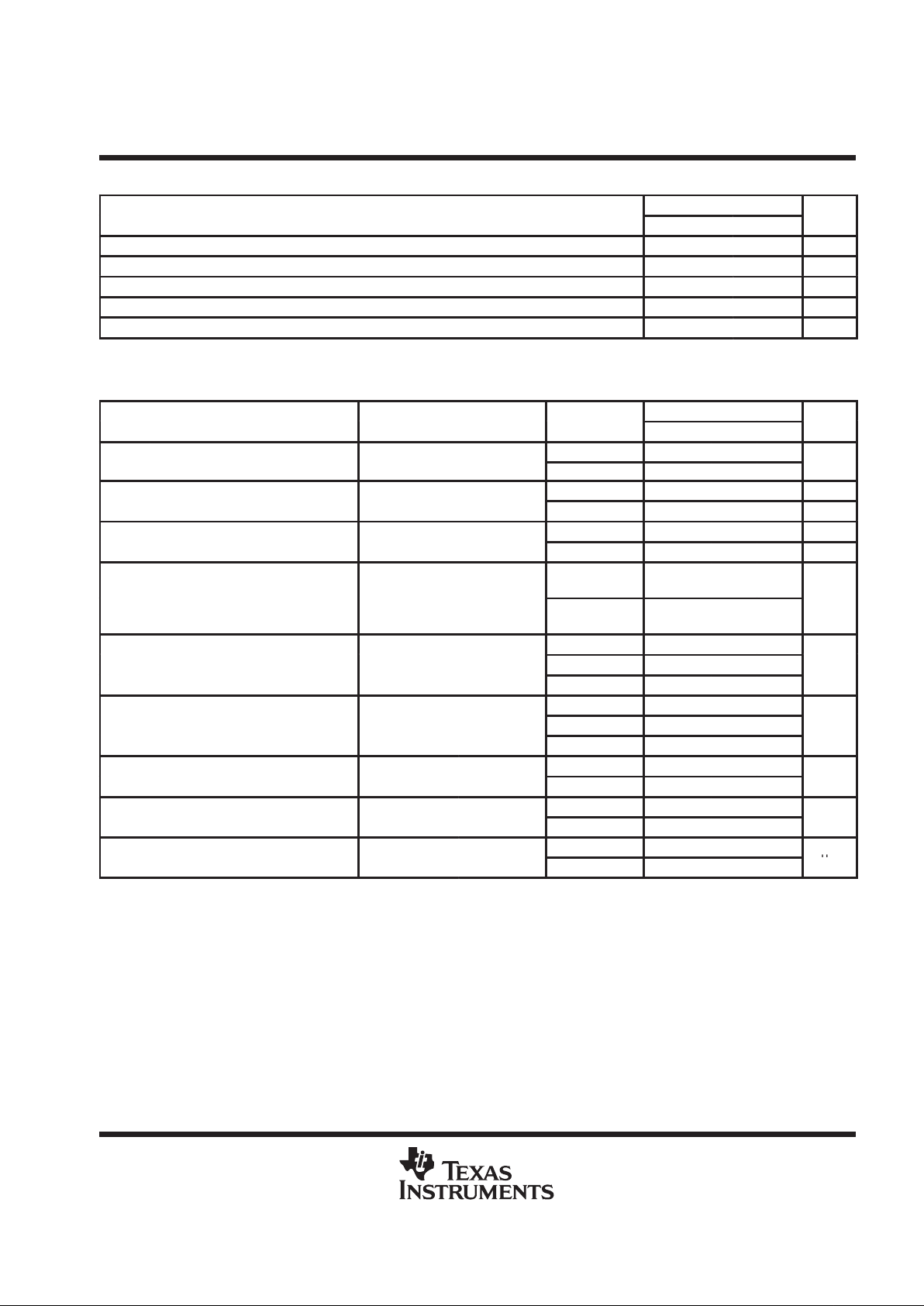

AVAILABLE OPTIONS

PACKAGE

T

A

VIOmax

at 25°C

SMALL OUTLINE

(D)

CERAMIC

(FK)

CERAMIC DIP

(J)

PLASTIC DIP

(N)

0°C to 70°C 5 mV TLC3704CD — — TLC3704CN

–40°C to 85°C 5 mV TLC3704ID — — TLC3704IN

–55°C to 125°C 5 mV — TLC3704MFK TLC3704MJ —

–40°C to 125°C 5 mV — — TLC3704QJ —

The D package is available taped and reeled. Add R suffix to the device type (e.g., TLC3704CDR).

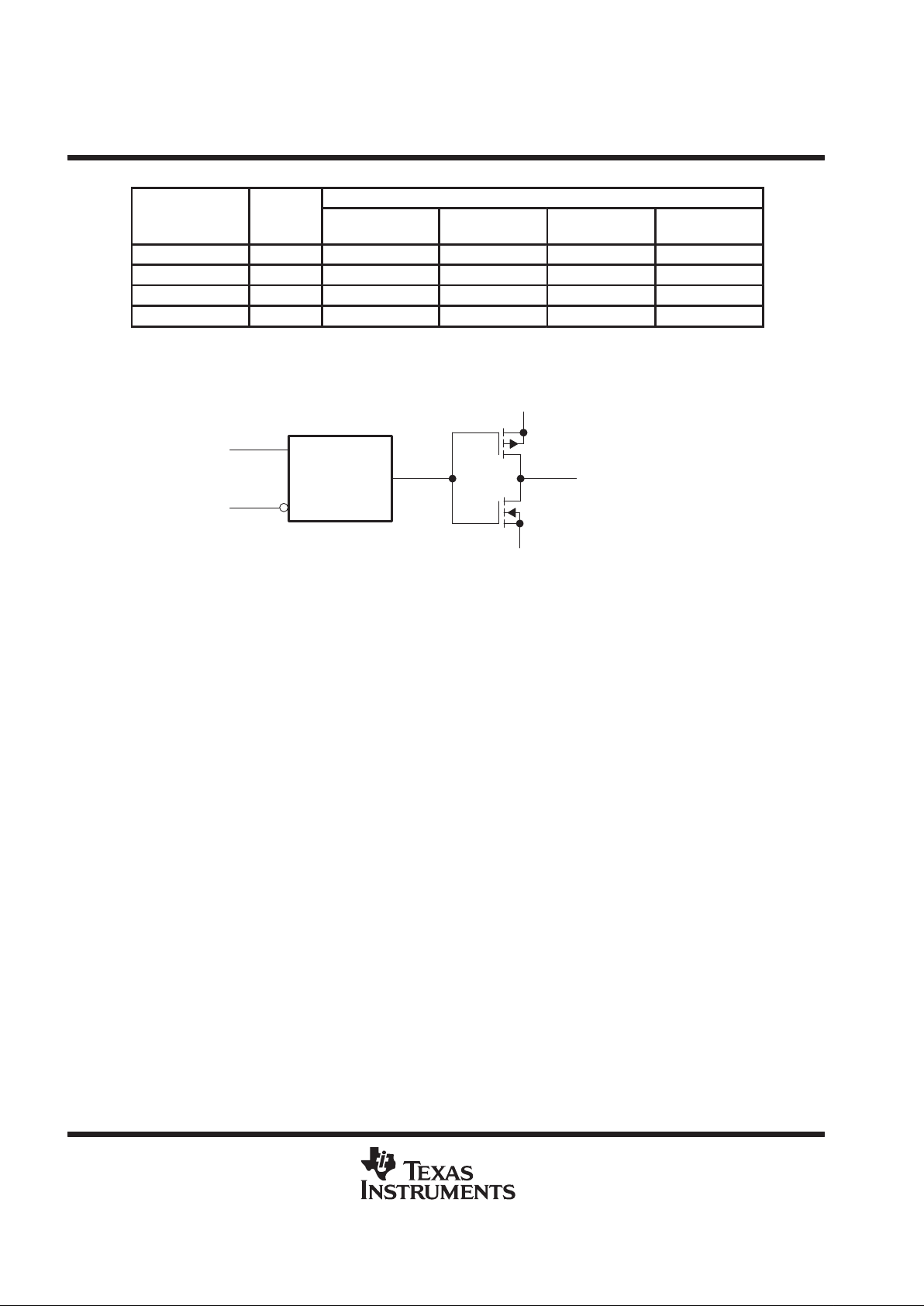

functional block diagram (each comparator)

V

DD

GND

OUT

Differential

Input

Circuits

IN+

IN–

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

†

Supply voltage range, V

DD

(see Note 1) – 0.3 V to 18 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Differential input voltage, V

ID

(see Note 2) ± 18 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input voltage range, V

I

– 0.3 to V

DD

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Output voltage range, V

O

– 0.3 to V

DD

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input current, I

I

± 5 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Output current, I

O

(each output) ± 20 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Total supply current into V

DD

40 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Total current out of GND 60 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Continuous total power dissipation See Dissipation Rating Table. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operating free-air temperature range, T

A

: TLC3704C 0 to 70°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

TLC3704I – 40°C to 85°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

TLC3704M – 55°C to 125°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

TLC3704Q – 40°C to 125°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage temperature range – 65°C to 150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Case temperature for 60 seconds: FK package 260°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds: D or N package 260°C. . . . . . . . . . . . . . . .

Lead temperature 1,6 mm (1/16 inch) from case for 60 seconds: J package 300°C. . . . . . . . . . . . . . . . . . . . .

†

Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. All voltage values, except differential voltages, are with respect to network ground.

2. Differential voltages are at IN+ with respect to IN–.

TLC3704, TLC3704Q

QUAD MICROPOWER LinCMOS VOLTAGE COMPARATORS

SLCS117A – NOVEMBER 1986 – REVISED OCT OBER 1996

3

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

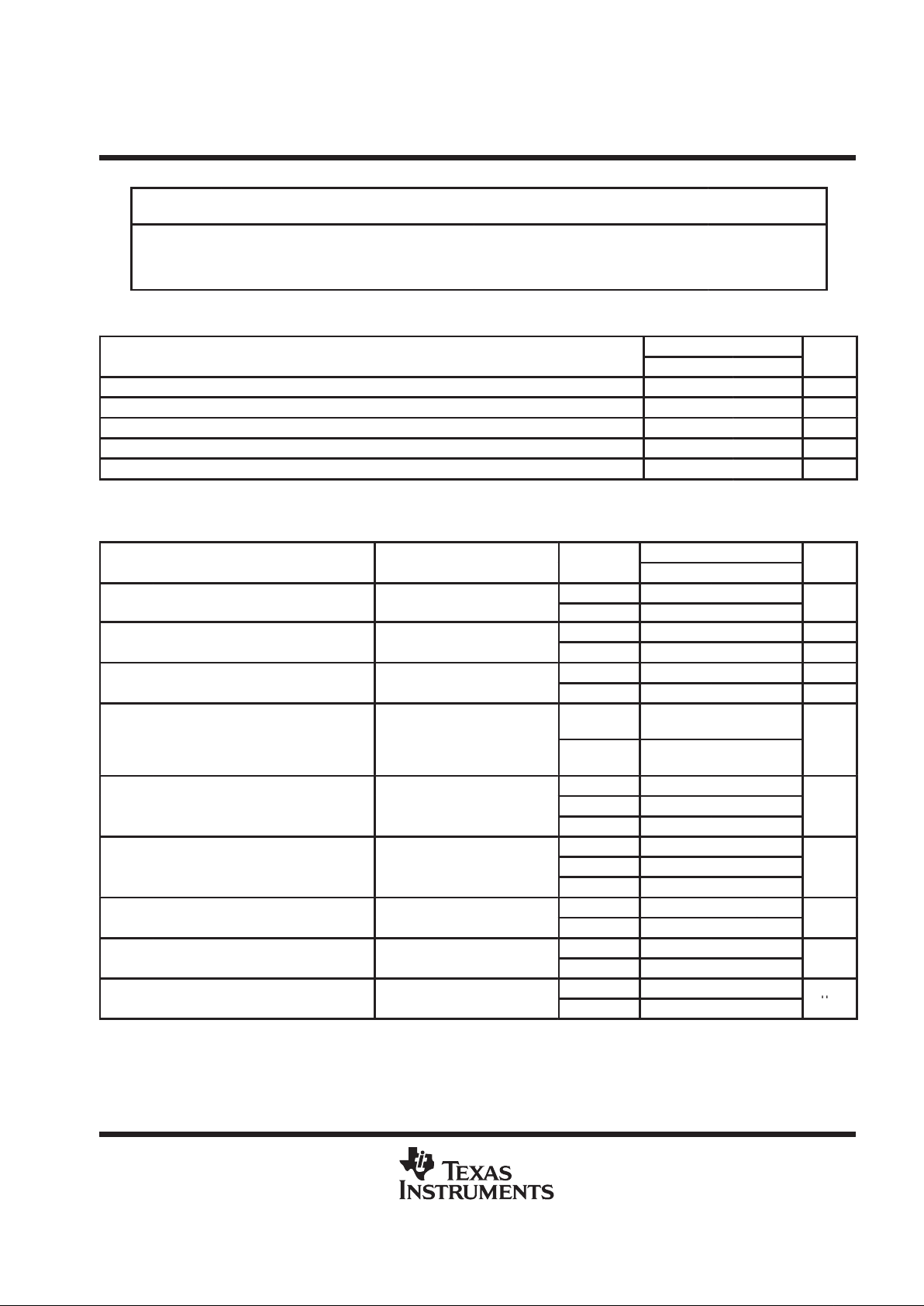

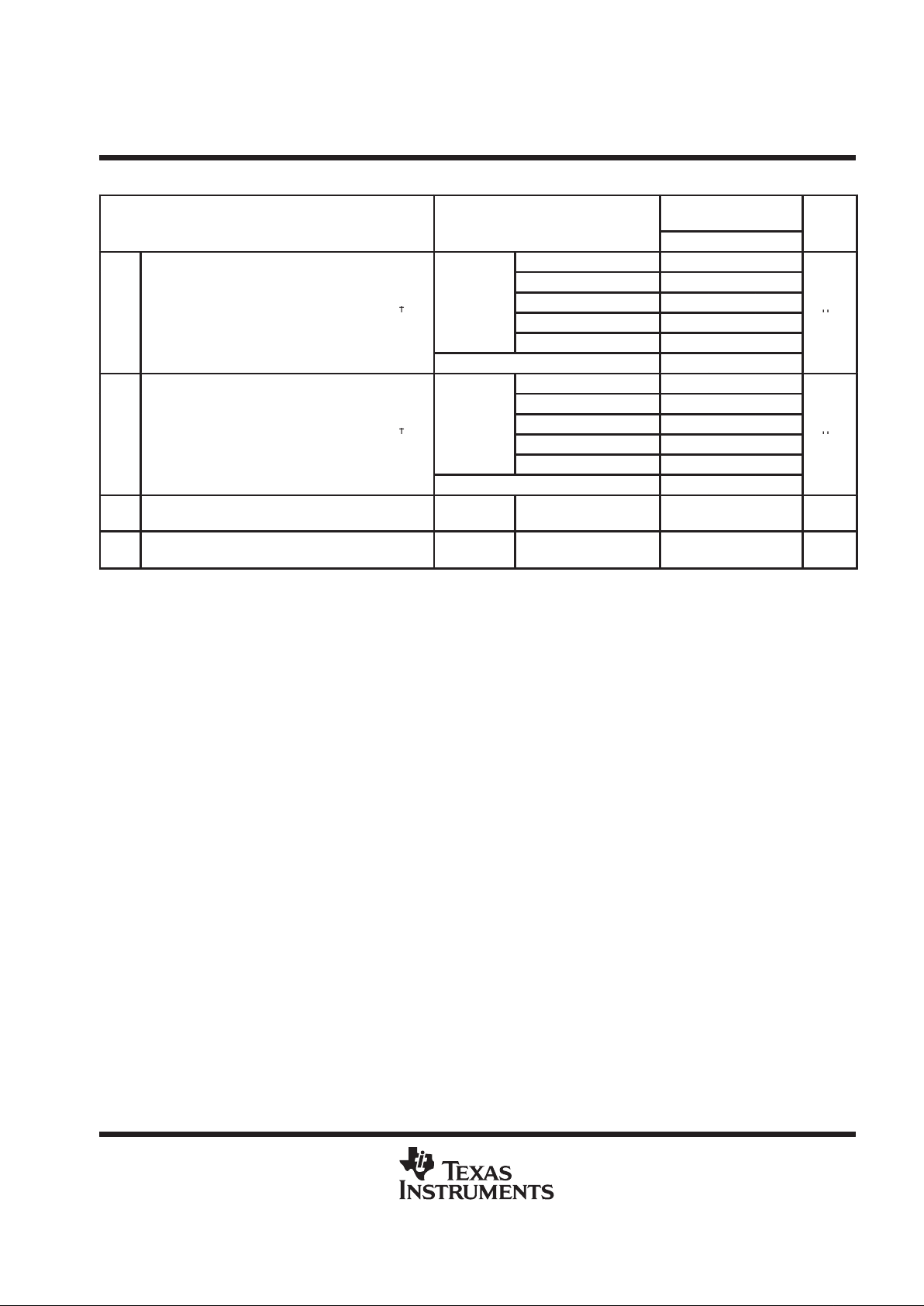

DISSIPATION RATING TABLE

PACKAGE

TA ≤ 25°C

POWER RATING

DERATING FACTOR

ABOVE TA = 25°C

TA = 70°C

POWER RATING

TA = 85°C

POWER RATING

TA = 125°C

POWER RATING

D

FK

J

N

950 mW

1375 mW

1375 mW

1150 mW

7.6 mW/°C

11.0 mW/°C

11.0 mW/°C

9.2 mW/°C

608 mW

880 mW

880 mW

736 mW

494 mW

715 mW

715 mW

598 mW

N/A

275 mW

275 mW

N/A

recommended operating conditions

TLC3704C

MIN NOM MAX

UNIT

Supply voltage, V

DD

3 5 16 V

Common-mode input voltage, V

IC

– 0.2 VDD – 1.5 V

High-level output current, I

OH

– 20 mA

Low-level output current, I

OL

20 mA

Operating free-air temperature, T

A

0 70 °C

electrical characteristics at specified operating free-air temperature, VDD = 5 V

(unless otherwise noted)

TLC3704C

PARAMETER

TEST CONDITIONS

†

T

A

MIN TYP MAX

UNIT

p

VDD = 5 V to 10 V, 25°C 1.2 5

VIOInput offset voltage

VIC = V

ICR

min, See Note 3 0°C to 70°C 6.5

mV

p

25°C 1 pA

IIOInput offset current

V

IC

= 2.5

V

70°C 0.3 nA

p

25°C 5 pA

IIBInput bias current

V

IC

= 2.5

V

70°C 0.6 nA

p

25°C

0 to

VDD – 1

V

ICR

Common-mode input voltage range

0°C to 70°C

0 to

VDD – 1.5

V

25°C 84

CMRR Common-mode rejection ratio VIC = V

ICR

min

70°C 84

dB

0°C 84

25°C 85

k

SVR

Supply-voltage rejection ratio VDD = 5 V to 10 V

70°C 85

dB

0°C 85

p

25°C 4.5 4.7

VOHHigh-level output voltage

V

ID

= 1 V,

I

OH

= –4

mA

70°C 4.3

V

p

25°C 210 300

VOLLow-level output voltage

V

ID

= –1 V,

I

OH

= 4

mA

70°C 375

mV

pp

p

p

25°C 35 80

IDDSupply current (all four comparators)

Outputs lo

w,

No load

0°C to 70°C 100

µ

A

†

All characteristics are measured with zero common-mode voltage unless otherwise noted.

NOTE 3: The offset voltage limits given are the maximum values required to drive the output up to 4.5 V or down to 0.3 V.

TLC3704, TLC3704Q

QUAD MICROPOWER LinCMOS VOLTAGE COMPARATORS

SLCS117A – NOVEMBER 1986 – REVISED OCT OBER 1996

4

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

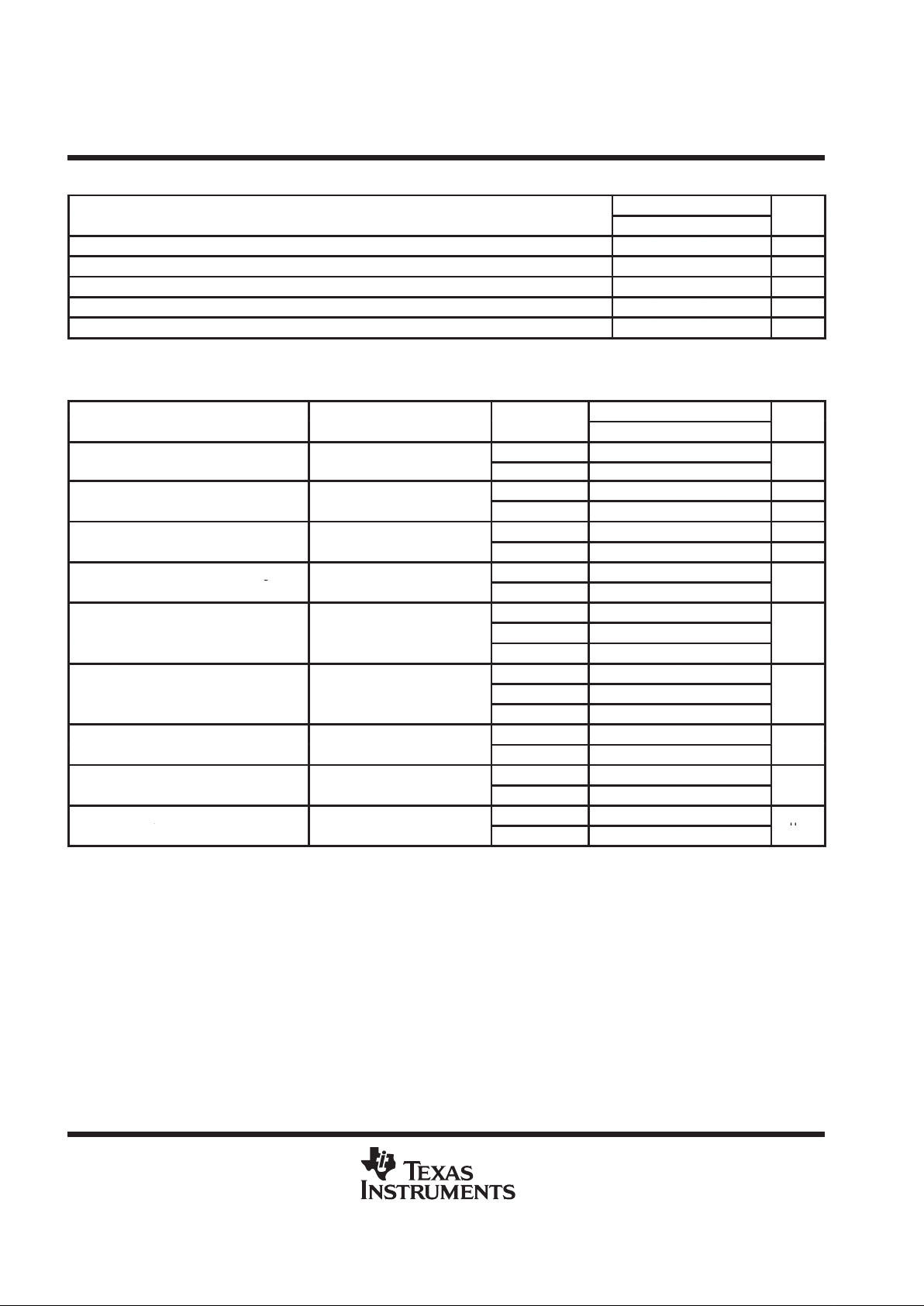

recommended operating conditions

TLC3704I

MIN NOM MAX

UNIT

Supply voltage, V

DD

3 5 16 V

Common-mode input voltage, V

IC

– 0.2 VDD – 1.5 V

High-level output current, I

OH

– 20 mA

Low-level output current, I

OL

20 mA

Operating free-air temperature, T

A

– 40 85 °C

electrical characteristics at specified operating free-air temperature, VDD = 5 V, VIC = 0 (unless

otherwise noted)

TLC3704I

PARAMETER

TEST CONDITIONS

T

A

MIN TYP MAX

UNIT

p

VDD = 5 V to 10 V, 25°C 1.2 5

VIOInput offset voltage

VIC = V

ICR

min, See Note 3 –40°C to 85°C 7

mV

p

25°C 1 pA

IIOInput offset current

V

IC

= 2.5

V

85°C 1 nA

p

25°C 5 pA

IIBInput bias current

V

IC

= 2.5

V

85°C 2 nA

p

25°C

0 to

VDD – 1

V

ICR

Common-mode input voltage range

–40°C to 85°C

0 to

VDD – 1.5

V

25°C 84

CMRR Common-mode rejection ratio VIC = V

ICR

min

85°C 84

dB

–40°C 83

25°C 85

k

SVR

Supply-voltage rejection ratio VDD = 5 V to 10 V

85°C 85

dB

–40°C 83

p

25°C 4.5 4.7

VOHHigh-level output voltage

V

ID

= 1 V,

I

OH

= –4

mA

85°C 4.3

V

p

25°C 210 300

VOLLow-level output voltage

V

ID

= –

1 V

,

I

OH

=

4 mA

85°C 400

mV

pp

p

p

25°C 35 80

IDDSupply current (all four comparators)

Outputs lo

w,

No load

–40°C to 85°C 125

µ

A

NOTE 3: The offset voltage limits given are the maximum values required to drive the output up to 4.5 V or down to 0.3 V.

TLC3704, TLC3704Q

QUAD MICROPOWER LinCMOS VOLTAGE COMPARATORS

SLCS117A – NOVEMBER 1986 – REVISED OCT OBER 1996

5

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

recommended operating conditions

TLC3704M

MIN NOM MAX

UNIT

Supply voltage, V

DD

4 5 16 V

Common-mode input voltage, V

IC

0 VDD – 1.5 V

High-level output current, I

OH

– 20 mA

Low-level output current, I

OL

20 mA

Operating free-air temperature, T

A

– 55 125 °C

electrical characteristics at specified operating free-air temperature, VDD = 5 V, VIC = 0 (unless

otherwise noted)

TLC3704M

PARAMETER

TEST CONDITIONS

T

A

MIN TYP MAX

UNIT

p

VDD = 5 V to 10 V, 25°C 1.2 5

VIOInput offset voltage

VIC = V

ICR

min, See Note 3 –55°C to 125°C 10

mV

p

25°C 1 pA

IIOInput offset current

V

IC

= 2.5

V

125°C 15 nA

p

25°C 5 pA

IIBInput bias current

V

IC

= 2.5

V

125°C 30 nA

p

25°C

0 to

VDD – 1

V

ICR

Common-mode input voltage range

–55°C to 125°C

0 to

VDD – 1.5

V

25°C 84

CMRR Common-mode rejection ratio VIC = V

ICR

min

125°C 83

dB

–55°C 82

25°C 85

k

SVR

Supply-voltage rejection ratio VDD = 5 V to 10 V

125°C 85

dB

–55°C 82

p

25°C 4.5 4.7

VOHHigh-level output voltage

V

ID

= 1 V,

I

OH

= –4

mA

125°C 4.2

V

p

25°C 210 300

VOLLow-level output voltage

V

ID

= –

1 V

,

I

OH

=

4 mA

125°C 500

mV

pp

p

p

25°C 35 80

IDDSupply current (all four comparators)

Outputs lo

w,

No load

–55°C to 125°C 175

µ

A

NOTE 3: The offset voltage limits given are the maximum values required to drive the output up to 4.5 V or down to 0.3 V.

TLC3704, TLC3704Q

QUAD MICROPOWER LinCMOS VOLTAGE COMPARATORS

SLCS117A – NOVEMBER 1986 – REVISED OCT OBER 1996

6

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

recommended operating conditions

TLC3704Q

MIN NOM MAX

UNIT

Supply voltage, V

DD

3 5 16 V

Common-mode input voltage, V

IC

–0.2 VDD – 1.5 V

High-level output current, I

OH

– 20 mA

Low-level output current, I

OL

20 mA

Operating free-air temperature, T

A

– 40 125 °C

electrical characteristics at specified operating free-air temperature, VDD = 5 V, VIC = 0 (unless

otherwise noted)

TLC3704Q

PARAMETER

TEST CONDITIONS

T

A

MIN TYP MAX

UNIT

p

VDD = 5 V to 10 V, 25°C 1.2 5

VIOInput offset voltage

VIC = V

ICR

min, See Note 3 –40°C to 125°C 7

mV

p

25°C 1 pA

IIOInput offset current

V

IC

= 2.5

V

125°C 15 nA

p

25°C 5 pA

IIBInput bias current

V

IC

= 2.5

V

125°C 30 nA

Common-mode input voltage

25°C 0 to VDD – 1

V

ICR

g

range

–40°C to 125°C 0 to VDD – 1.5

V

25°C 84

CMRR Common-mode rejection ratio VIC = V

ICR

min

125°C 83

dB

–40°C 83

25°C 85

k

SVR

Supply-voltage rejection ratio VDD = 5 V to 10 V

125°C 85

dB

–40°C 83

p

25°C 4.5 4.7

VOHHigh-level output voltage

V

ID

=

1 V

,

I

OH

= –

4 mA

125°C 4.2

V

p

25°C 210 300

VOLLow-level output voltage

V

ID

= –1 V,

I

OH

= 4

mA

125°C 500

mV

Supply current (all four

p

25°C 35 80

I

DD

y(

comparators)

Outputs lo

w,

No load

–40°C to 125°C 175

µ

A

NOTE 3: The offset voltage limits given are the maximum values required to drive the output up to 4.5 V or down to 0.3 V.

TLC3704, TLC3704Q

QUAD MICROPOWER LinCMOS VOLTAGE COMPARATORS

SLCS117A – NOVEMBER 1986 – REVISED OCT OBER 1996

7

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

switching characteristics, VDD = 5 V, TA = 25°C

PARAMETER TEST CONDITIONS

TLC3704C, TLC3704I

TLC3704M, TLC3704Q

UNIT

MIN TYP MAX

Overdrive = 2 mV 4.5

Overdrive = 5 mV 2.7

p

p

f = 10 kHz,

p

Overdrive = 10 mV 1.9

t

PLH

Propagation delay time, low-to-high-level output

†

C

L

= 50

F

Overdrive = 20 mV 1.4

µ

s

Overdrive = 40 mV 1.1

VI = 1.4-V step at IN+ 1.1

Overdrive = 2 mV 4

Overdrive = 5 mV 2.3

p

p

f = 10 kHz,

p

Overdrive = 10 mV 1.5

t

PHL

Propagation delay time, high-to-low-level output

†

C

L

= 50

F

Overdrive = 20 mV 0.95

µ

s

Overdrive = 40 mV 0.65

VI = 1.4-V step at IN+ 0.15

t

f

Fall time

f = 10 kHz,

CL = 50 pF

Overdrive = 50 mV 50 ns

t

r

Rise time

f = 10 kHz,

CL = 50 pF

Overdrive = 50 mV 125 ns

†

Simultaneous switching of inputs causes degradation in output response.

TLC3704, TLC3704Q

QUAD MICROPOWER LinCMOS VOLTAGE COMPARATORS

SLCS117A – NOVEMBER 1986 – REVISED OCT OBER 1996

8

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

PRINCIPLES OF OPERATION

LinCMOS process

The LinCMOS process is a linear polysilicon-gate CMOS process. Primarily designed for single-supply

applications, LinCMOS products facilitate the design of a wide range of high-performance analog functions from

operational amplifiers to complex mixed-mode converters.

While digital designers are experienced with CMOS, MOS technologies are relatively new for analog designers.

This short guide is intended to answer the most frequently asked questions related to the quality and reliability

of LinCMOS products. Further questions should be directed to the nearest TI field sales office.

electrostatic discharge

CMOS circuits are prone to gate oxide breakdown when exposed to high voltages even if the exposure is only

for very short periods of time. Electrostatic discharge (ESD) is one of the most common causes of damage to

CMOS devices. It can occur when a device is handled without proper consideration for environmental

electrostatic charges, e.g., during board assembly . If a circuit in which one amplifier from a dual op amp is being

used and the unused pins are left open, high voltages tends to develop. If there is no provision for ESD

protection, these voltages may eventually punch through the gate oxide and cause the device to fail. T o prevent

voltage buildup, each pin is protected by internal circuitry.

Standard ESD-protection circuits safely shunt the ESD current by providing a mechanism whereby one or more

transistors break down at voltages higher than the normal operating voltages but lower than the breakdown

voltage of the input gate. This type of protection scheme is limited by leakage currents which flow through the

shunting transistors during normal operation after an ESD voltage has occurred. Although these currents are

small, on the order of tens of nanoamps, CMOS amplifiers are often specified to draw input currents as low as

tens of picoamps.

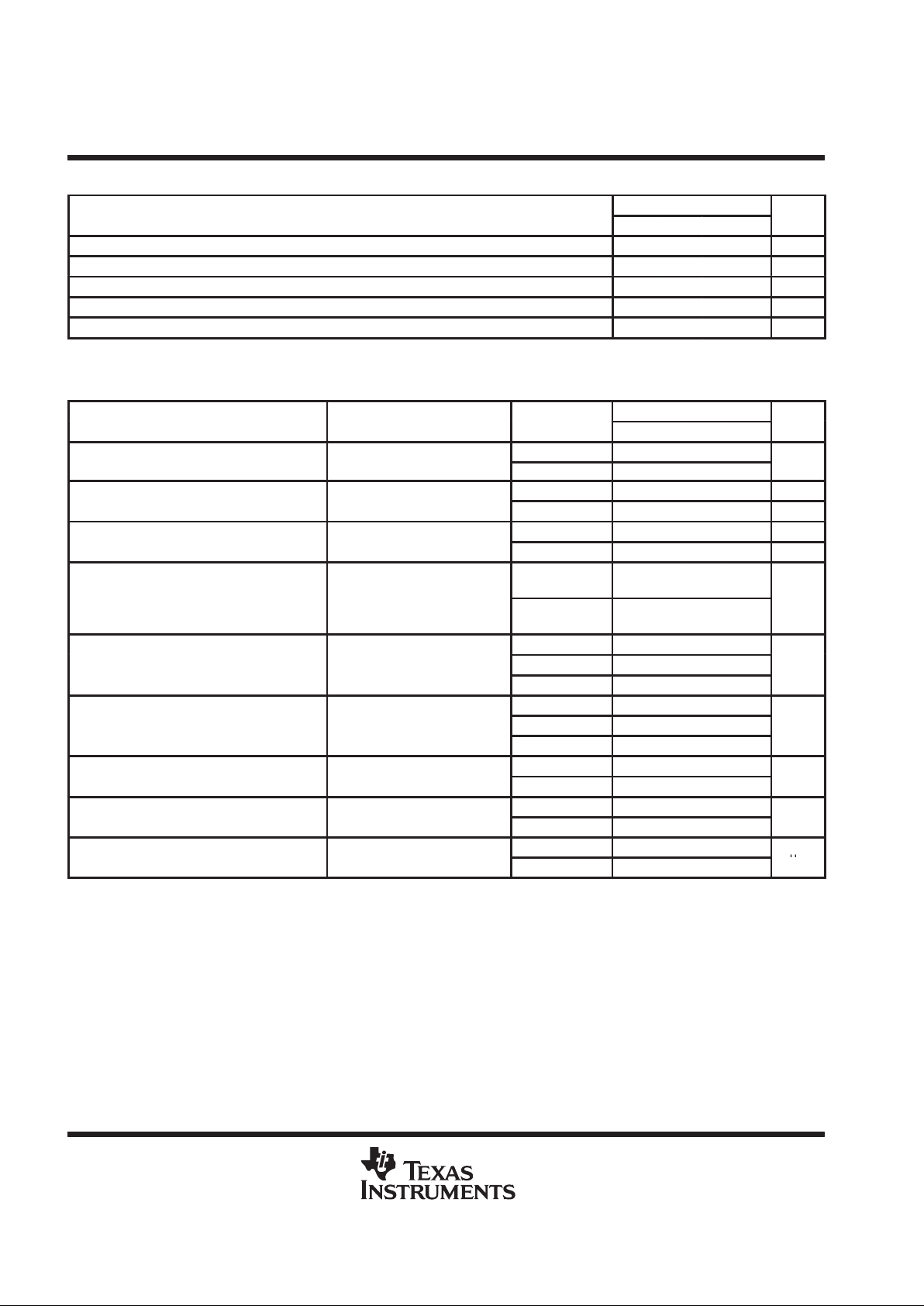

To overcome this limitation, TI design engineers developed the patented ESD-protection circuit shown in

Figure 1. This circuit can withstand several successive 2-kV ESD pulses, while reducing or eliminating leakage

currents that may be drawn through the input pins. A more detailed discussion of the operation of the TI

ESD-protection circuit is presented on the next page.

All input and output pins on LinCMOS and Advanced LinCMOS products have associated ESD-protection

circuitry that undergoes qualification testing to withstand 2000 V discharged from a 100-pF capacitor through

a 1500-Ω resistor (human body model) and 200 V from a 100-pF capacitor with no current-limiting resistor

(charged device model). These tests simulate both operator and machine handling of devices during normal

test and assembly operations.

To Protected Circuit

D3

R2

Q2

D2D1

Q1

Input

GND

R1

V

DD

Figure 1. LinCMOS ESD-Protection Schematic

Loading...

Loading...