查询THS14F01供应商

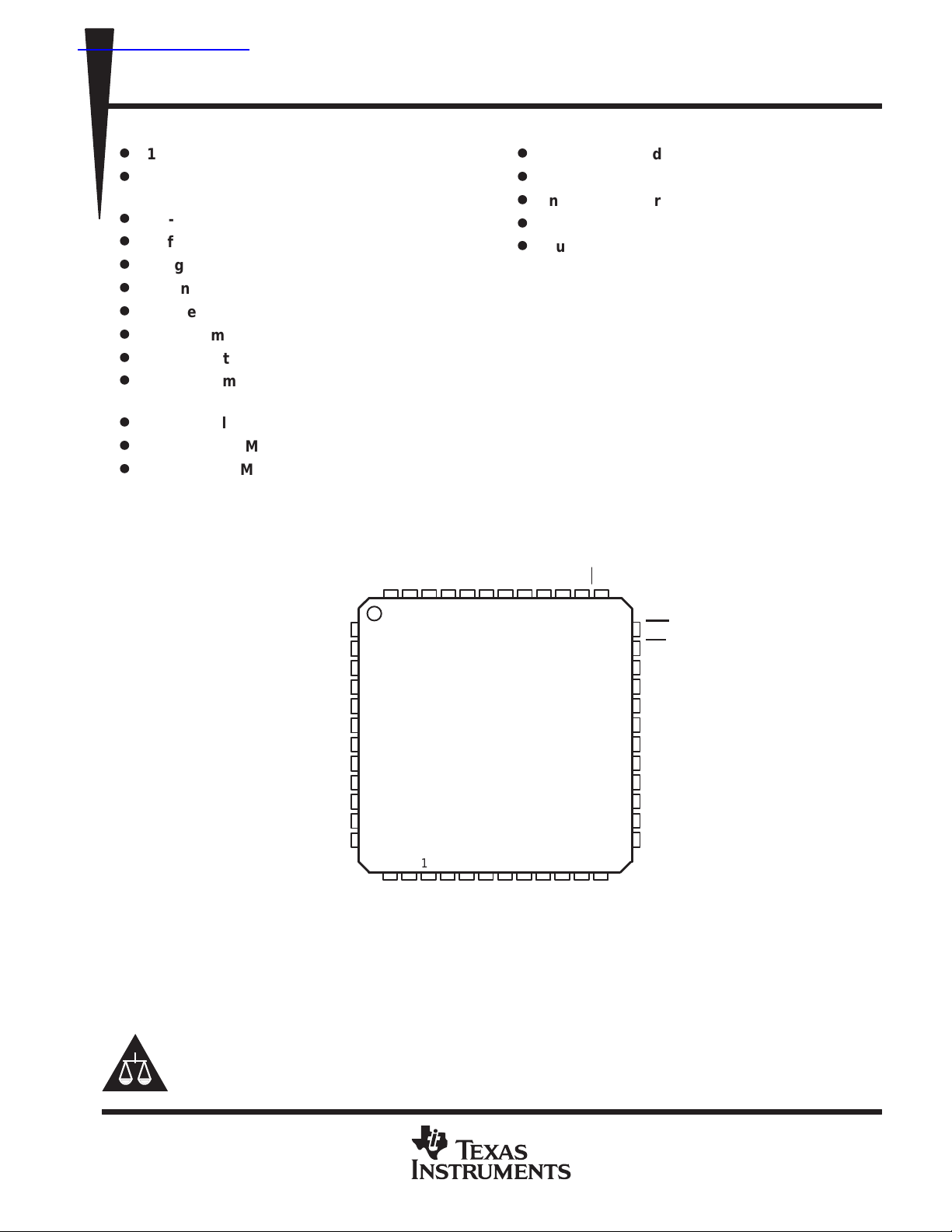

14-BIT, 1 MSPS/ 3 MSPS, DSP COMPATIBLE, ANALOG-TO-DIGITAL CONVERTERS

THS14F01, THS14F03

WITH FIFO INTERNAL REFERENCE AND PGA

SLAS285 – JUNE 2000

features

D

14-Bit Resolution

D

1 MSPS and 3 MSPS Speed Grades

Available

D

On-Chip FIFO For Optimized Data Transfer

D

Differential Nonlinearity (DNL) ±0.6 LSB Typ

D

Integral Nonlinearity (INL) ±1.5 LSB Typ

D

Internal Reference

D

Differential Inputs

D

Programmable Gain Amplifier

D

µP Compatible Parallel Interface

D

Timing Compatible With TI 6000 DSP

Family

D

3.3-V Single Supply

D

Power-Down Mode

D

Monolithic CMOS Design

PFB PACKAGE

DD

IN+AVAGND

AGND

applications

D

D

D

D

D

(TOP VIEW)

DD

DD

AV

AGND

DV

xDSL Front Ends

Communication

Industrial Control

Instrumentation

Automotive

A0A1FOVL

INT

CS

47 46 45 44 4348 42

IN–

1

AV

VBG

CML

REF+

REF–

AGND

AGND

DGND

NC – No internal connection

DD

OV

D13

D12

2

3

4

5

6

7

8

9

10

11

12

13

14 15

D11

DD

DV

16

DGND

17 18 19 20

D9D8D7

D10

40 39 3841

21

DD

DV

22 23 24

D5D4D3

D6

37

36

35

34

33

32

31

30

29

28

27

26

25

WR

OE

DGND

DGND

CLK

DV

DD

DV

DD

D0

D1

D2

DV

DD

DGND

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Copyright 2000, Texas Instruments Incorporated

1

THS14F01, THS14F03

14-BIT, 1 MSPS/ 3 MSPS, DSP COMPATIBLE, ANALOG-TO-DIGITAL CONVERTERS

WITH FIFO INTERNAL REFERENCE AND PGA

SLAS285 – JUNE 2000

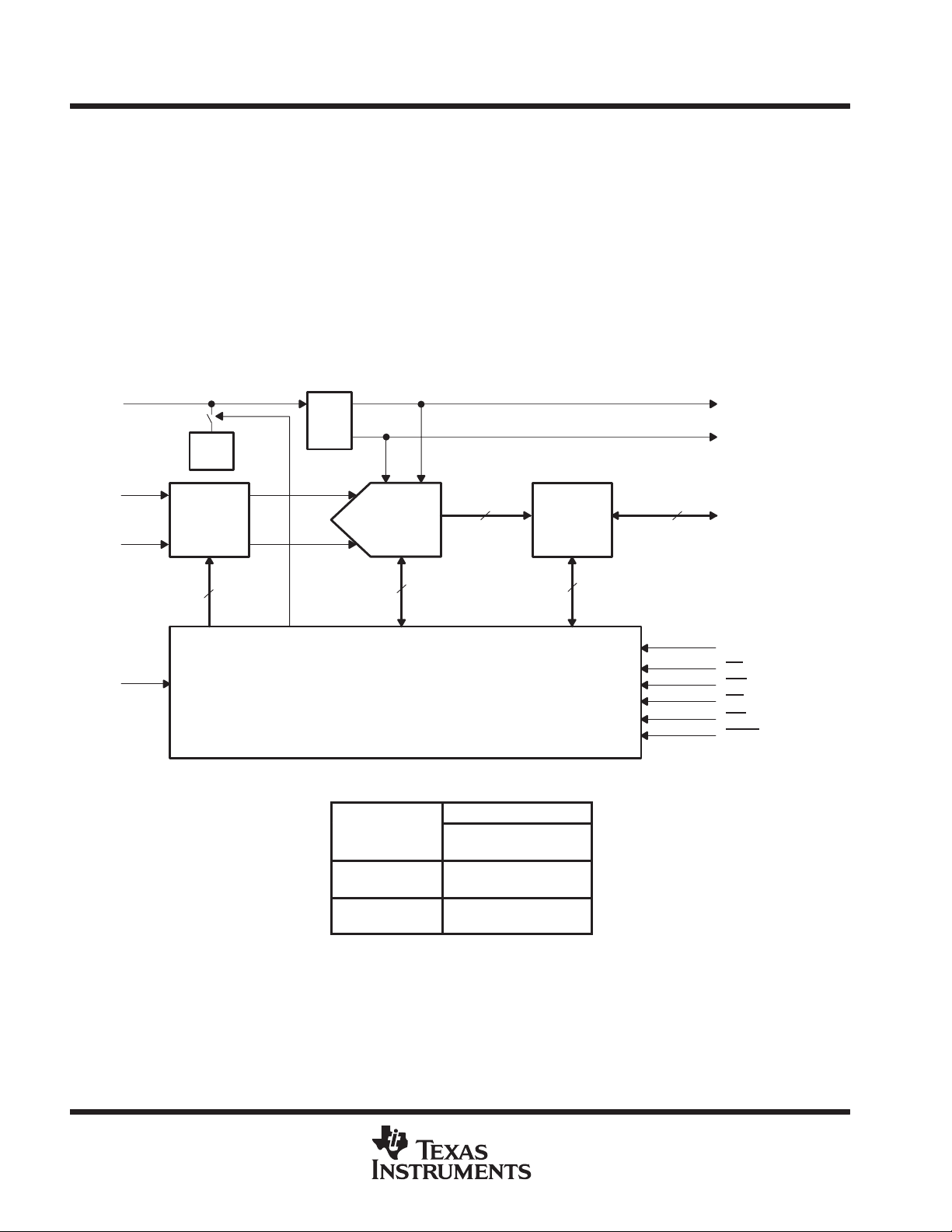

description

The THS14F01 and THS14F03 are 14-bit, 1 MSPS/ 3 MSPS, single supply analog-to-digital converters with

a FIFO, internal reference, differential inputs, programmable input gain, and an on-chip sample and hold

amplifier.

Implemented with a CMOS process, the device has outstanding price/performance and power/speed ratios.

The THS14F01 and THS14F03 are designed for use with 3.3-V systems, and with a high-speed µP compatible

parallel interface, making them the first choice for solutions based on high-performance DSPs like the TI

TMS320C6000 series.

The THS14F01 and THS14F03 are available in a TQFP-48 package in standard commercial and industrial

temperature ranges.

functional block diagram

VBG

IN+

IN–

CLK

1.5 V

BG

PGA

0..7 dB

REF+

REF

14-Bit

ADC

6

CONTROL

LOGIC

AVAILABLE OPTIONS

T

A

0°C to 70°C

–40°C to 85°C

14 15

PACKAGED DEVICE

TQFP

(PFB)

THS14F01CPFB,

THS14F03CPFB

THS14F01IPFB,

THS14F03IPFB

32-Word

FIFO+

Buffer

REF–

D[13:0] + OV bit

A[1:0]

CS

WR

OE

INT

FOVL

2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

I/O

DESCRIPTION

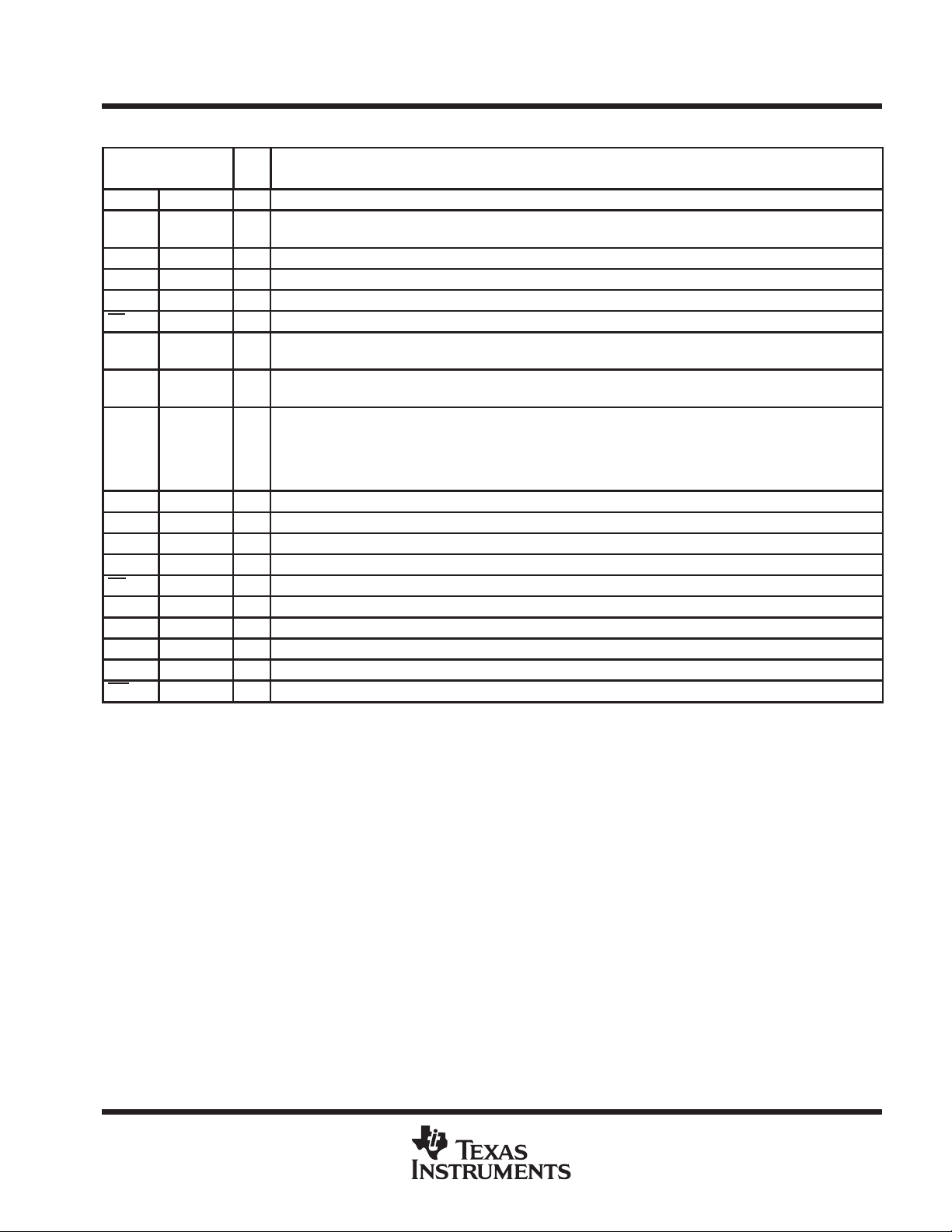

THS14F01, THS14F03

14-BIT, 1 MSPS/ 3 MSPS, DSP COMPATIBLE, ANALOG-TO-DIGITAL CONVERTERS

WITH FIFO INTERNAL REFERENCE AND PGA

Terminal Functions

TERMINAL

NAME NO.

A[1:0] 40, 41 I Address input

AGND 7,8, 44,

AV

DD

CLK 32 I Clock input

CML 4 Reference midpoint. This pin requires a 0.1-µF capacitor to AGND.

CS 37 I Chip select input. Active low

DGND 9, 15, 25,

DV

DD

D[13:0] 11, 12, 13,

FOVL 39 O FIFO Overflow. Asserted when FIFO is full. Programmable polarity

IN+ 48 I Positive differential analog input

IN– 1 I Negative differential analog input

INT 38 O Interrupt output. Asserted when FIFO trigger level is reached. Programmable polarity

OE 35 I Output enable. Active low

OV 10 O Out of range output

REF+ 5 O Positive reference output. This pin requires a 0.1-µF capacitor to AGND.

REF– 6 O Negative reference output. This pin requires a 0.1-µF capacitor to AGND.

VBG 3 I Reference input. This pin requires a 1-µF capacitor to AGND.

WR 36 I Write signal. Active low

45, 46

2, 43, 47 P Analog power supply

33, 34

14, 20, 26,

30, 31, 42

16, 17, 18,

19, 21, 22,

23, 24, 27,

28, 29

P Analog ground

P Digital ground

P Digital power supply

I/O Data inputs/outputs

SLAS285 – JUNE 2000

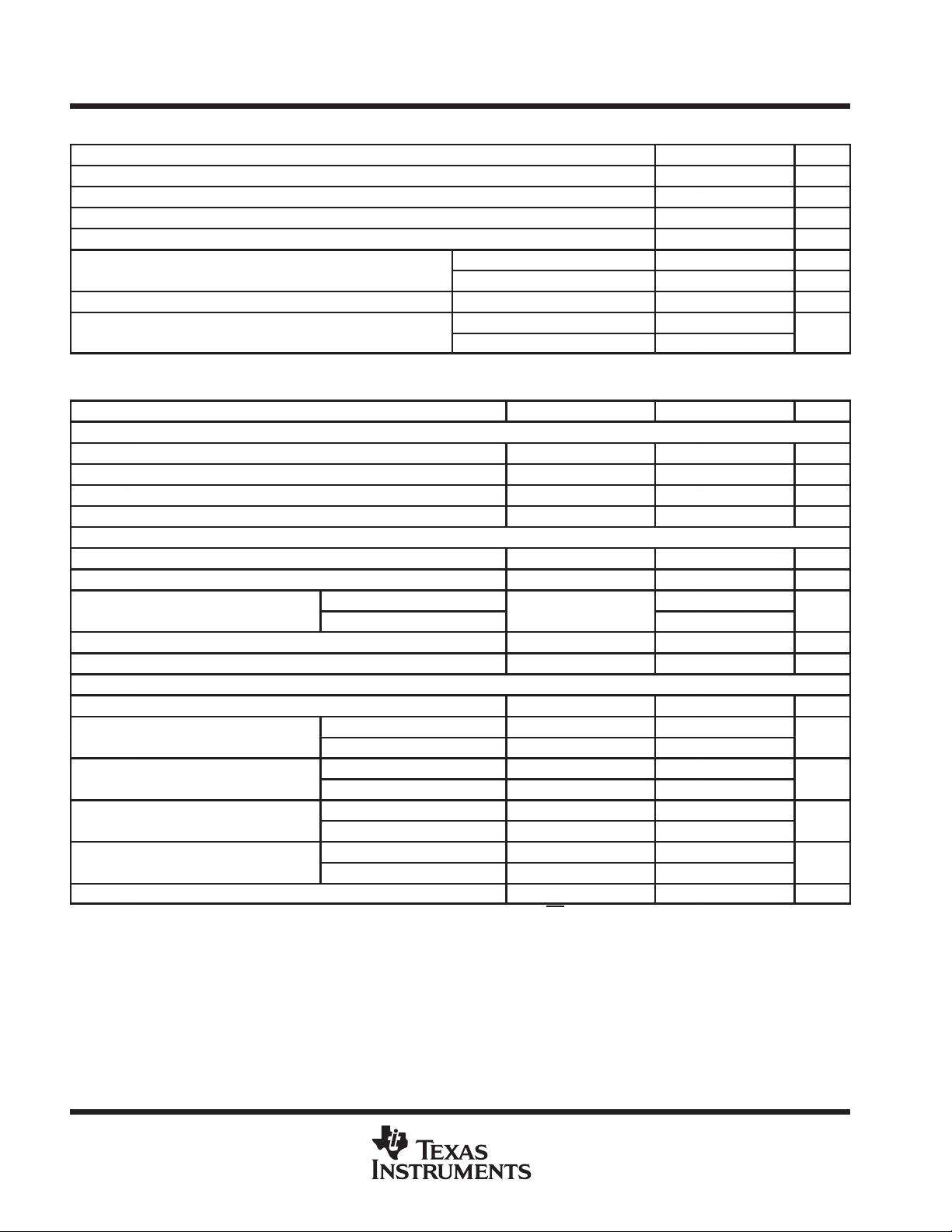

absolute maximum ratings over operating free-air temperature (unless otherwise noted)

†

Supply voltage, (AVDD to AGND) 4V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Supply voltage, (DVDD to DGND) 4V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Reference input voltage range, VBG – 0.3 V to AV

DD

+ 0.3 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Analog input voltage range – 0.3 V to AVDD + 0.3 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Digital input voltage range – 0.3 V to DV

Operating free-air temperature range, T

: C suffix 0°C to 70°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A

DD

+ 0.3 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

I suffix –40°C to 85°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage temperature range, T

stg

–65°C to 150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Lead temperature 1.6 mm (1/16 inch) from case for 10 seconds 260°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

†

Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

3

THS14F01, THS14F03

Clock frequenc

f

Operating free-air temperature

°C

INL

Integral nonlinearit

Best fit

LSB

THD

Total harmonic distortion

dB

SNR

Signal-to-noise ratio

dB

SINAD

Signal-to-noise ratio

distortion

dB

SFDR

Spurious free dynamic range

dB

14-BIT, 1 MSPS/ 3 MSPS, DSP COMPATIBLE, ANALOG-TO-DIGITAL CONVERTERS

WITH FIFO INTERNAL REFERENCE AND PGA

SLAS285 – JUNE 2000

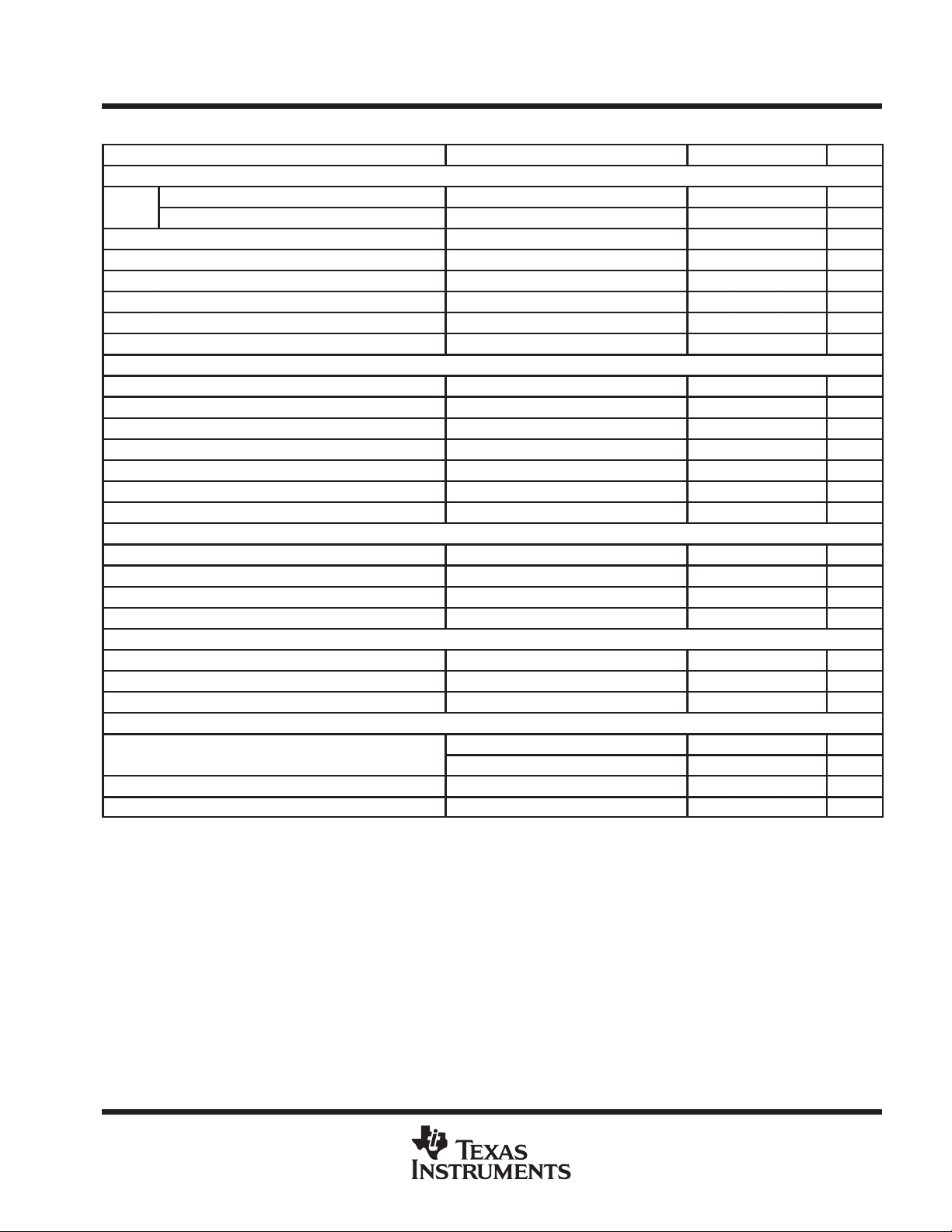

recommended operating conditions

MIN NOM MAX UNIT

Supply voltage, AVDD, DV

High level digital input, V

Low level digital input, V

Load capacitance, C

y,

Clock duty cycle 40% 50% 60%

p

CLK

DD

IH

IL

L

THS14F01 0.1 1 1 MHz

THS14F03 0.1 3 3 MHz

p

C suffix 0 25 70

I suffix –40 25 85

electrical characteristics over recommended operating conditions

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

Power Supply

I

DDA

I

DDD

DC Characteristics

DNL Differential nonlinearity ±0.6 ±1 LSB

AC Characteristics

ENOB Effective number of bits 11.2 1 1.5 Bits

†

FIFO trigger level = 10 samples. Performance is ensured with the output enable signal (OE

on CLK.

Analog supply current 81 90 mA

Digital supply current 5 10 mA

Power 270 360 mW

Power down current 20 µA

†

Resolution 14 Bits

y

Offset error IN+ = IN–, PGA = 0 dB 0.3 %FSR

Gain error PGA = 0 dB 1 %FSR

†

+

p

Analog input bandwidth 140 MHz

THS14F01

THS14F03

THS14F01/3 fi = 100 kHz –81

THS14F03 fi = 1 MHz –78

THS14F01/3 fi = 100 kHz 72

THS14F03 fi = 1 MHz 70 72

THS14F01/3 fi = 100 kHz 70

THS14F03 fi = 1 MHz 69 70

THS14F01/3 fi = 100 kHz 80

THS14F03 fi = 1 MHz 73 80

) being low during no more than one rising clock edge

3 3.3 3.6 V

2 3.3 V

0 0.8 V

5 15 pF

±1.5 ±2.5

±1.5 ±2.5

°

4

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

VBG

f

Clock frequenc

14-BIT, 1 MSPS/ 3 MSPS, DSP COMPATIBLE, ANALOG-TO-DIGITAL CONVERTERS

electrical characteristics (continued)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

Reference Voltage

Bandgap voltage, internal mode 1.425 1.5 1.575 V

Input impedance 40 kΩ

Positive reference voltage, REF+ 2.5 V

Negative reference voltage, REF– 0.5 V

Reference difference, ∆REF, REF+ – REF– 2 V

Accuracy, internal reference 5%

Temperature coefficient 40 ppm/°C

Voltage coefficient 200 ppm/V

Analog Inputs

Positive analog input, IN+ 0 AV

Negative analog input, IN– 0 AV

Analog input voltage difference ∆Ain = IN+ – IN–, V

Input impedance 25 kΩ

PGA range 0 7 dB

PGA step size 1 dB

PGA gain error ±0.25 dB

Digital Inputs

V

IH

V

IL

Digital Outputs

V

OH

V

OL

I

OZ

Clock Timing (CS low)

CLK

t

d

High-level digital input 2 V

Low-level digital input 0.8 V

Input capacitance 5 pF

Input current ±1 µA

High-level digital output IOH = 50 µA 2.6 V

Low-level digital output IOL = 50 µA 0.4 V

Output current, high impedance ±10 µA

y

Output delay time 25 ns

Latency 9.5 Cycles

THS14F01, THS14F03

WITH FIFO INTERNAL REFERENCE AND PGA

SLAS285 – JUNE 2000

ref

V

V

V

DD

DD

= REF+ – REF– –V

ref

THS14F01 0.1 1 1 MHz

THS14F03

ref

0.1 3 3 MHz

V

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

5

THS14F01, THS14F03

14-BIT, 1 MSPS/ 3 MSPS, DSP COMPATIBLE, ANALOG-TO-DIGITAL CONVERTERS

WITH FIFO INTERNAL REFERENCE AND PGA

SLAS285 – JUNE 2000

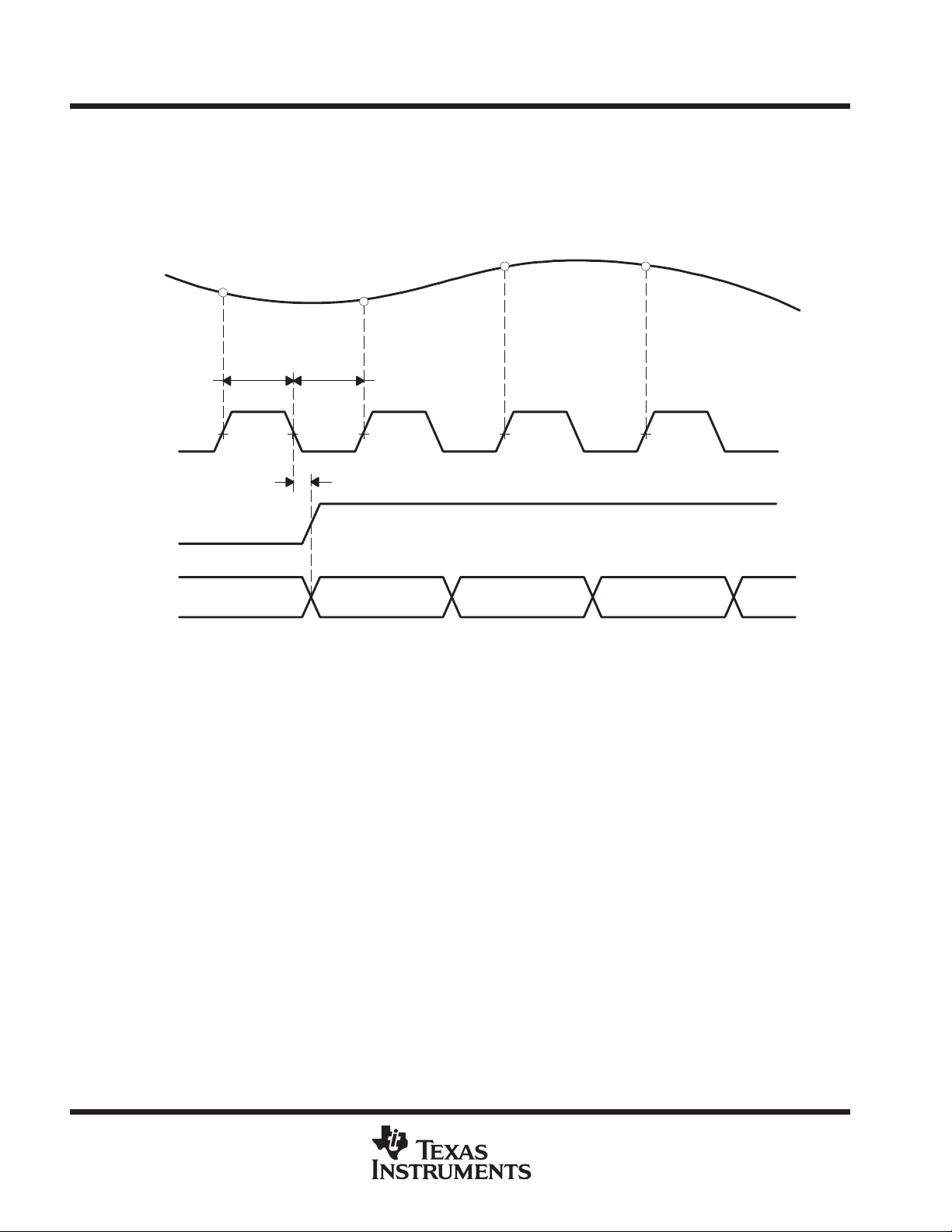

PARAMETER MEASUREMENT INFORMATION

sample timing

The THS14F01/3 core is based on a pipeline architecture with a latency of 9.5 samples. The conversion results

are stored in the FIFO 9.5 clock cycles after the input signal was sampled.

Analog

Input

S9

S11

S10

S12

CLK

INT

Data

to FIFO

t

w(CLK)

t

t

w(CLK)

d

C1 C2

C3

Figure 1. Sample Timing

INT goes active if the programmed FIFO level is reached. INT is either low or high active depending on the

polarity bit (IP) within the control word. This signal is set synchronously to the CLK signal. It is reset by a read

access to the FIFO once the number of samples in the FIFO is below the programmed threshold level.

6

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

THS14F01, THS14F03

14-BIT, 1 MSPS/ 3 MSPS, DSP COMPATIBLE, ANALOG-TO-DIGITAL CONVERTERS

WITH FIFO INTERNAL REFERENCE AND PGA

SLAS285 – JUNE 2000

PARAMETER MEASUREMENT INFORMATION

The parallel interface of the THS14F01/3 ADC features 3-state buffers making it possible to directly connect

it to a data bus. The output buffers are enabled by driving the OE input low.

Besides the sample results, it is also possible to read back the values of the control register, the PGA register,

and the control register. Which register is read is determined by the address inputs A[1,0]. The ADC results are

available at address 0.

The timing of the control signals is described in the following sections.

The FIFO can be disabled by setting FC to 0 (FIFO reset, default at power on). This makes it possible to access

the device synchronously.

In this case the data is updated on every clock cycle.

Analog

Input

S9

S11

S10

S12

CLK

D[13:0]

OV

OE

A[1:0]

CS

t

w(CLK)

C0

t

en

X X

t

su(OE-ACS)

t

w(CLK)

t

d

C1 C2

C3

Figure 2. Sample Timing

t

dis

t

h(A)

t

h(CS)

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

7

THS14F01, THS14F03

14-BIT, 1 MSPS/ 3 MSPS, DSP COMPATIBLE, ANALOG-TO-DIGITAL CONVERTERS

WITH FIFO INTERNAL REFERENCE AND PGA

SLAS285 – JUNE 2000

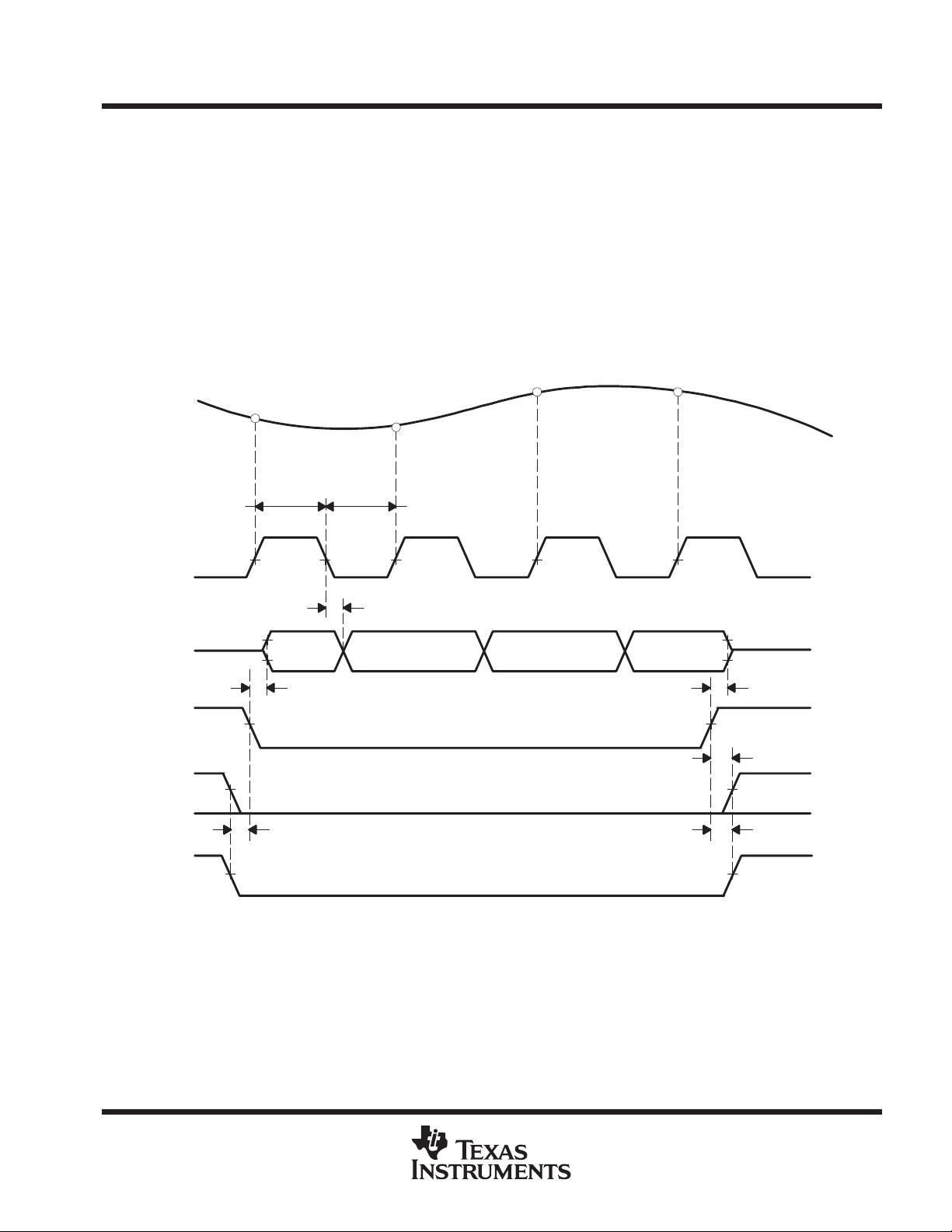

PARAMETER MEASUREMENT INFORMATION

read timing (15-pF load)

PARAMETER MIN TYP MAX UNIT

t

su(OE–ACS)

t

en

t

dis

t

h(A)

t

h(CS)

NOTE: All timing parameters refer to a 50% level.

CS

OE

Address and chip select setup time 4 ns

Output enable 15 ns

Output disable 10 ns

Address hold time 1 15 ns

Chip select hold time 0 ns

t

h(CS)

D[13:0]

O V

A[1:0]

t

su(OE–ACS)

X X

t

en

DATA

ADDRESS

Figure 3. Read Timing

t

h(A)

t

dis

8

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

14-BIT, 1 MSPS/ 3 MSPS, DSP COMPATIBLE, ANALOG-TO-DIGITAL CONVERTERS

PARAMETER MEASUREMENT INFORMATION

write timing (15-pF load)

PARAMETER MIN TYP MAX UNIT

t

su(WE–CS)

t

su(DA)

t

h(DA)

t

h(CS)

t

wH(WE)

NOTE: All timing parameters refer to a 50% level.

CS

WE

Chip select setup time 4 ns

Data and address setup time 29 ns

Data and address hold time 0 ns

Chip select hold time 0 ns

Write pulse duration high 15 ns

t

su(WE–CS)

THS14F01, THS14F03

WITH FIFO INTERNAL REFERENCE AND PGA

SLAS285 – JUNE 2000

t

h(CS)

t

su(DA)

D[13:0]

t

h(DA)

X

X

A

X X

DATA

ADDRESS

Figure 4. Write Timing

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

9

THS14F01, THS14F03

14-BIT, 1 MSPS/ 3 MSPS, DSP COMPATIBLE, ANALOG-TO-DIGITAL CONVERTERS

WITH FIFO INTERNAL REFERENCE AND PGA

SLAS285 – JUNE 2000

TYPICAL CHARACTERISTICS

POWER

vs

FREQUENCY

284

282

280

278

276

Power – mW

274

272

270

268

0.1 1 10

f – Frequency – MHz

Figure 5

0

fs = 1 MSPS,

–20

fI = 100 kHz,

–1 dB

–40

–60

90

80

70

60

50

40

30

– Supply Current – mA

CC

I

20

10

0

0 50 100 150 200 250 300

FAST FOURIER TRANSFORM

SUPPLY CURRENT

vs

TIME

t – Time – ns

Figure 6

10

–80

Output – dB

–100

–120

–140

0 100 200 300

f – Frequency – kHz

Figure 7

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

400 500

THS14F01, THS14F03

14-BIT, 1 MSPS/ 3 MSPS, DSP COMPATIBLE, ANALOG-TO-DIGITAL CONVERTERS

WITH FIFO INTERNAL REFERENCE AND PGA

SLAS285 – JUNE 2000

TYPICAL CHARACTERISTICS

FAST FOURIER TRANSFORM

0

fs = 3 MSPS,

–20

fI = 1 MHz,

–1 dB

–40

–60

–80

Output – dB

–100

–120

–140

0.1 0.4 0.7 1

f – Frequency – MHz

Figure 8

INTEGRAL NONLINEARITY

2

1.5

0.5

–0.5

–1

–1.5

–2

INL – Integral Nonlinearity – LSB

fs = 1 MSPS

1

0

0 2048 4096 6144 8192 10240

Samples

12288 14336 16384

1.3

Figure 9

INTEGRAL NONLINEARITY

2

1.5

1

0.5

0

–0.5

–1

–1.5

–2

INL – Integral Nonlinearity – LSB

0 2048 4096 6144 8192 10240

Samples

Figure 10

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

fs = 3 MSPS

12288 14336 16384

11

THS14F01, THS14F03

14-BIT, 1 MSPS/ 3 MSPS, DSP COMPATIBLE, ANALOG-TO-DIGITAL CONVERTERS

WITH FIFO INTERNAL REFERENCE AND PGA

SLAS285 – JUNE 2000

TYPICAL CHARACTERISTICS

DIFFERENTIAL NONLINEARITY

1

fs = 1 MSPS

0.8

0.6

0.4

0.2

0

–0.2

–0.4

–0.6

–0.8

–1

0 2048 4096 6144 8192 10240

DNL – Differential Nonlinearity – LSB

Samples

Figure 11

DIFFERENTIAL NONLINEARITY

1

0.8

0.6

0.4

0.2

0

–0.2

–0.4

–0.6

–0.8

–1

0 2048 4096 6144 8192 10240

DNL – Differential Nonlinearity – LSB

Samples

12288 14336 16384

fs = 3 MSPS

12288 14336 16384

12

Figure 12

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

THS14F01, THS14F03

14-BIT, 1 MSPS/ 3 MSPS, DSP COMPATIBLE, ANALOG-TO-DIGITAL CONVERTERS

WITH FIFO INTERNAL REFERENCE AND PGA

SLAS285 – JUNE 2000

TYPICAL CHARACTERISTICS

TOTAL HARMONIC DISTORTION

FREQUENCY

–70

fs = 3 MSPS,

–72

fI at –1 dB

–74

–76

–78

–80

–82

–84

–86

THD – Total Harmonic Distortion – dB

–88

–90

10

f – Frequency – Hz

Figure 13 Figure 14

vs

100 1000

1500

SIGNAL-TO-NOISE RATIO

FREQUENCY

80

fs = 3 MSPS,

78

fI at –1 dB

76

74

72

70

68

66

64

SNR – Signal-to-Noise Ratio – dB

62

60

10

100

f – Frequency – Hz

vs

1000

1500

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

13

THS14F01, THS14F03

14-BIT, 1 MSPS/ 3 MSPS, DSP COMPATIBLE, ANALOG-TO-DIGITAL CONVERTERS

WITH FIFO INTERNAL REFERENCE AND PGA

SLAS285 – JUNE 2000

PRINCIPLES OF OPERATION

registers

The device contains several registers. The A register is selected by the values of bits A1 and A0:

A1 A0 Register

0 0 Conversion result

0 1 PGA

1 0 Offset

1 1 Control

T ables 1 and 2 describe how to read the conversion results and how to configure the data converter . The default

values (were applicable) show the state after a power-on reset.

Table 1. Conversion Result Register, Address 0, Read

BIT D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

Function MSB ... … … … … … … … … … … … LSB

The output can be configured for two’s complement or straight binary format (see D11/control register).

The output code is given by:

2s complement: Straight binary:

–8192 at ∆IN = –∆REF 0 at ∆IN = –∆REF

0 at ∆IN = 0 8192 at ∆IN = 0

8191 ∆IN = –∆REF – 1 LSB 16383 at ∆IN = –∆REF – 1 LSB

1LSB

+

2DREF

16384

Table 2. PGA Gain Register, Address 1, Read/Write

BIT D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

Function X X X X X X X X X X X G2 G1 G0

Default 0 0 0 0 0 0 0 0 0 0 0 0 0 0

The PGA gain is determined by writing to G2–0.

Gain (dB) = 1dB × G2–0. max = 7dB. The range of G2–0 is 0 to 7.

Table 3. Offset Register, Address 2, Read/Write

BIT D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

Function X X X X X X MSB … … … … … … LSB

Default 0 0 0 0 0 0 0 0 0 0 0 0 0 0

The offset correction range is from –128 to 127 LSB. This value is added to the conversion results from the ADC.

14

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

THS14F01, THS14F03

14-BIT, 1 MSPS/ 3 MSPS, DSP COMPATIBLE, ANALOG-TO-DIGITAL CONVERTERS

WITH FIFO INTERNAL REFERENCE AND PGA

SLAS285 – JUNE 2000

PRINCIPLES OF OPERATION

Table 4. Control Register, Address 3, Read

BIT D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

Function PWD REF FOR TM2 TM1 TM0 OFF IP FP FC F3 F2 F1 F0

Table 5. Control Register, Address 3, Write

BIT D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

Function PWD REF FOR TM2 TM1 TM0 OFF IP FP FC F3 F2 F1 F0

Default 0 0 0 0 0 0 0 0 0 0 0 0 0 0

PWD: Power down 0 = normal operation 1 = power down

REF: Reference select 0 = internal reference 1 = external reference

FOR: Output format 0 = straight binary 1 = 2s complement

TM2–0: Test mode 000 = normal operation

001 = both inputs = REF–

010 = IN+ at V

011 = IN+ at REF+, IN– at REF–

100 = normal operation

101 = both inputs = REF+

110 = IN+ at REF–, IN– at V

111 = IN+ at REF–, IN– at REF+

OFF: Offset correction 0 = enable 1 = disable

IP: INT polarity 0 = low active 1 = high active

FP: FIFO FOVL polarity 0 = low active 1 = high active

FC: FIFO control 0 = disable FIFO 1 = enable FIFO

F3–0: FIFO threshold Sets the FIFO threshold for the INT signal in steps of 2 ranging from 0 to 30

/2, IN– at REF–

ref

ref

/2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

15

THS14F01, THS14F03

14-BIT, 1 MSPS/ 3 MSPS, DSP COMPATIBLE, ANALOG-TO-DIGITAL CONVERTERS

WITH FIFO INTERNAL REFERENCE AND PGA

SLAS285 – JUNE 2000

APPLICATION INFORMATION

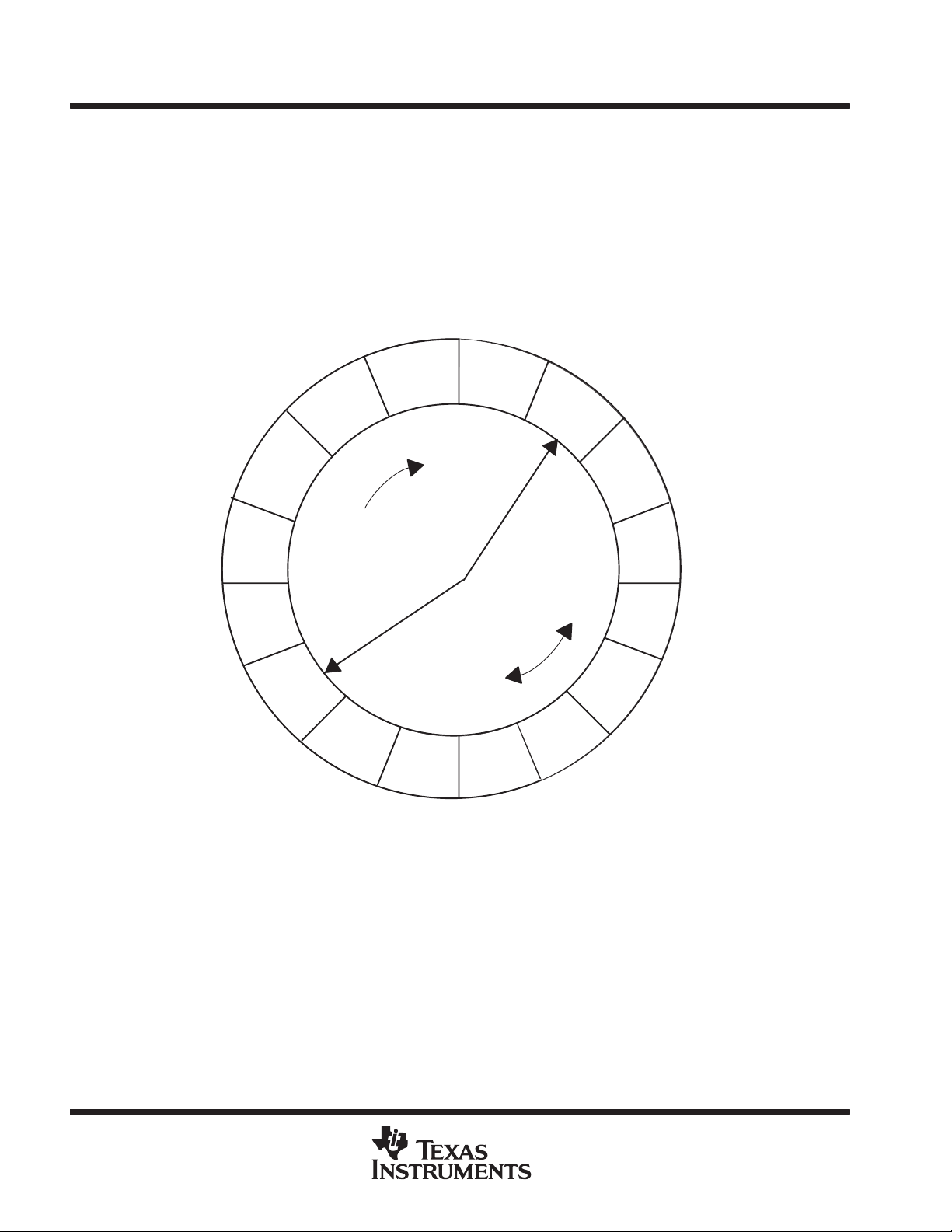

FIFO description

The FIFO is based on a circular buffer (see Figure 15, in this example the FIFO is 16 words long). The buffer is

accessed using two pointers, one for the ADC writing to the FIFO, one for the processor (DSP) reading from the buffer .

Both pointers move in a clockwise direction. If the distance between the ADC write pointer and the DSP read pointer

is greater or equal a programmable threshold, the INT signal is asserted. If this INT signal is connected to an external

interrupt pin of the processor, it is possible to read out the stored values in the FIFO at once during the interrupt service

routine. If the ADC write pointer reaches the position of the DSP read pointer, an overflow occurs. In this case, the

overflow bit in the ADC register is set and the FOVL is asserted.

12

15

14

13

ADC

11

10

9

8

0

1

2

DSP

3

4

T

5

6

7

16

Figure 15. Circular Buffer

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

THS14F01, THS14F03

14-BIT, 1 MSPS/ 3 MSPS, DSP COMPATIBLE, ANALOG-TO-DIGITAL CONVERTERS

WITH FIFO INTERNAL REFERENCE AND PGA

SLAS285 – JUNE 2000

APPLICATION INFORMATION

DMA transfer and FIFO

The FIFO makes it possible to use the available interface bandwidth of the host processor more efficiently . The

following is a description based on the TMS320C6201 DSP from TI.

The TMS320C6201 memory interface has a limited bandwidth, for example 200MWPS at a clock rate of 200

MHz. The THS14F04x interface is asynchronous with a maximum speed of 300MWPS, which is approximately

7 clock cycles.

If the DSP uses the DMA controller to read data from the DSP, the following conditions exist:

D

DMA bus arbitration: 16 clock cycles

D

THS14F0x read access: 7 clock cycles

If, for example, 10 samples need to be read from the ADC without the FIFO, the memory interface will be

allocated for (10 + 7) × 16 = 272 clock cycles in total.

BUSarb R

S

BUSarb R

S

BUSarb R

S

BUSarb R

S

BUSarb R

S

With a FIFO programmed to a 10 sample threshold, the memory interface will be allocated for 16 + 7 × 10 = 86

clock cycles in total.

BUS Available for Other Peripheral

BUSarb R R R R BUSarb R R R R

driving the analog input

The THS14F01/3 ADCs have a fully differential input. A differential input is advantageous with respect to SNR,

SFDR, and THD performance because the signal peak-to-peak level is 50% of a comparable single-ended

input.

There are three basic input configurations:

D

Fully differential

D

Transformer coupled single-ended to differential

D

Single-ended

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

17

THS14F01, THS14F03

14-BIT, 1 MSPS/ 3 MSPS, DSP COMPATIBLE, ANALOG-TO-DIGITAL CONVERTERS

WITH FIFO INTERNAL REFERENCE AND PGA

SLAS285 – JUNE 2000

APPLICATION INFORMATION

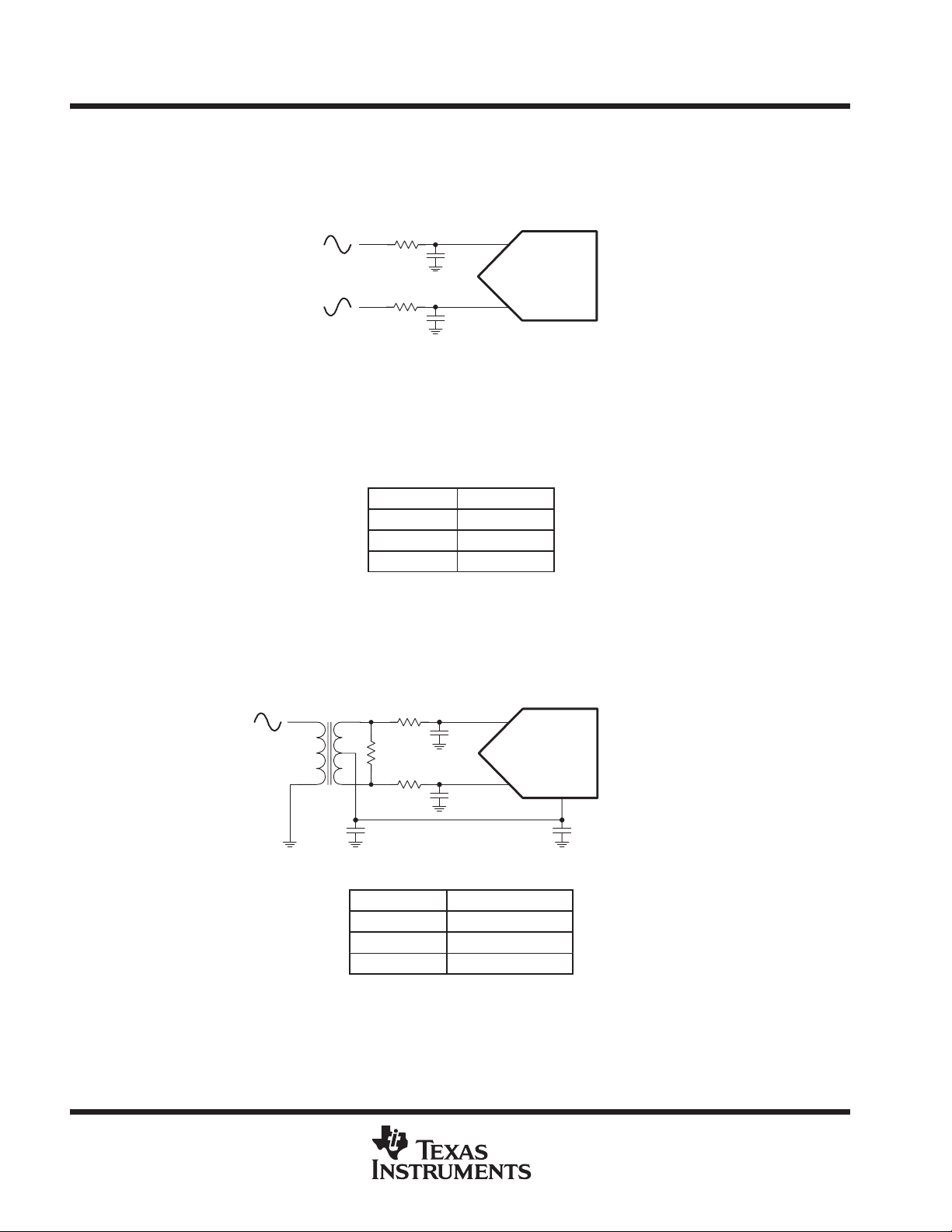

fully differential configuration

In this configuration, the ADC converts the difference (∆IN) of the two input signals on IN+ and IN–.

22 Ω

100 pF

22 Ω

100 pF

Figure 16. Differential Input

The resistors and capacitors on the inputs decouple the driving source output from the ADC input and also serve

as first order low pass filters to attenuate out of band noise.

The input range on both inputs is 0 V to A VDD. The full-scale value is determined by the voltage reference. The

positive full-scale output is reached, if ∆IN equals ∆REF , the negative full-scale output is reached, if ∆IN equals

–∆REF.

∆IN [V] OUTPUT

–∆REF – full scale

0 0

∆REF + full scale

IN+

THS14F01/3

IN–

transformer coupled single-ended to differential configuration

If the application requires the best SNR, SFDR, and THD performance, the input should be transformer coupled.

The signal amplitude on both inputs of the ADC is one half as high as in a single-ended configuration thus

increasing the ADC ac performance.

22 Ω

100 pF

R

22 Ω

100 pF

+

1 µF 0.1 µF

Figure 17. Transformer Coupled

IN [V

–∆REF – full scale

†

n = 1 (winding ratio)

] OUTPUT [

PEAK

0 0

∆REF + full scale

The resistor R of the transformer coupled input configuration must be set to match the signal source impedance

R = n2 Rs, where Rs is the source impedance and n is the transformer winding ratio.

IN+

THS14F01/3

IN–

CML

]

PEAK

†

†

18

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

14-BIT, 1 MSPS/ 3 MSPS, DSP COMPATIBLE, ANALOG-TO-DIGITAL CONVERTERS

APPLICATION INFORMATION

single-ended configuration

In this configuration, the input signal is level shifted by ∆REF/2.

10 kΩ 10 kΩ

–

+

22 Ω

THS14F01, THS14F03

WITH FIFO INTERNAL REFERENCE AND PGA

SLAS285 – JUNE 2000

10 kΩ + 10 kΩ

REF+

100 pF

100 pF

IN+

THS14F01/3

IN–

REF–

10 kΩ

10 kΩ

Figure 18. Single-Ended With Level Shift

The following table shows the input voltages for negative full-scale output, zero output, and positive full-scale

output:

∆IN+ [V] OUTPUT

–∆REF – full scale

0 0

∆REF + full scale

Note that the resistors of the op-amp and the op-amp all introduce gain and offset errors. Those errors can be

trimmed by varying the values of the resistors.

Because of the added offset, the op-amp does not necessarily operate in the best region of its transfer curve

(best linearity around zero) and therefore may introduce unacceptable distortion. For ac signals, an alternative

is described in the following section.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

19

THS14F01, THS14F03

14-BIT, 1 MSPS/ 3 MSPS, DSP COMPATIBLE, ANALOG-TO-DIGITAL CONVERTERS

WITH FIFO INTERNAL REFERENCE AND PGA

SLAS285 – JUNE 2000

APPLICATION INFORMATION

ac-coupled single-ended configuration

If the application does not require the signal bandwidth to include dc, the level shift shown in Figure 4 is not

necessary.

10 kΩ

10 kΩ

REF+

10 kΩ 10 kΩ

–

+

100 pF

10 nF

22 Ω

100 pF

Figure 19. Single-Ended With Level Shift

IN+

THS14F01/3

IN–

10 kΩ

10 kΩ

REF–

Because the signal swing on the op-amp is centered around ground, it is more likely that the signal stays within

the linear region of the op-amp transfer function, thus increasing the overall ac performance.

IN [V

–∆REF – full scale

] OUTPUT [

PEAK

0 0

∆REF + full scale

PEAK

]

Compared to the transformer-coupled configuration, the swing on IN– is twice as big, which can decrease the

ac performance (SNR, SFD, and THD).

20

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

THS14F01, THS14F03

14-BIT, 1 MSPS/ 3 MSPS, DSP COMPATIBLE, ANALOG-TO-DIGITAL CONVERTERS

WITH FIFO INTERNAL REFERENCE AND PGA

SLAS285 – JUNE 2000

APPLICATION INFORMATION

internal/external reference operation

The THS14F01/3 ADC can either be operated using the built-in band gap reference or using an external

precision reference in case very high dc accuracy is needed.

The REF+ and REF+ outputs are given by:

REF

)+

If the built-in reference is used, VBG equals 1.5 V which results in REF+ = 2.5 V, REF– = 0.5 V and ∆REF =

2V.

The internal reference can be disabled by writing 1 to D12 (REF) in the control register (address 3). The band

gap reference is then disconnected and can be substituted by a voltage on the VBG pin.

VBG

ǒ

Ǔ

1

)

and REF–+VBGǒ1–

3

2

2

Ǔ

3

programmable gain amplifier

The on-chip programmable gain amplifier (PGA) has eight gain settings. The gain can be changed by writing

to the PGA gain register (address 1). The range is 0 to 7dB in steps of one dB.

out of range indication

The OV output of the ADC indicates an out of range condition. Every time the difference on the analog inputs

exceeds the differential reference, this signal is asserted. This signal is updated the same way as the digital data

outputs and therefore subject to the same pipeline delay.

offset compensation

With the offset register it is possible to automatically compensate system offset errors, including errors caused

by additional signal conditioning circuitry . If the offset compensation is enabled (D7 (OFF) in the control register),

the value in the offset register (address 2) is automatically subtracted from the output of the ADC.

In order to set the correct value of the offset compensation register , the ADC result when the input signal is 0

must be read by the host processor and written to the offset register (address 2).

test modes

The ADC core operation can be tested by selecting one of the available test modes (see control register

description). The test modes apply various voltages to the differential input depending on the setting in the

control register.

digital I/O

The digital inputs and outputs of the THS14F01/3 ADC are 3-V CMOS compatible. In order to avoid current feed

back errors, the capacitive load on the digital outputs should be as low as possible (50 pF max). Series resistors

(100 Ω) on the digital outputs can improve the performance by limiting the current during output transitions.

The parallel interface of the THS14F01/3 ADC features 3-state buffers, making it possible to directly connect

it to a data bus. The output buffers are enabled by driving the OE input low.

Refer to the read and write timing diagrams in the parameter measurement information section for information

on read and write access.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

21

THS14F01, THS14F03

14-BIT, 1 MSPS/ 3 MSPS, DSP COMPATIBLE, ANALOG-TO-DIGITAL CONVERTERS

WITH FIFO INTERNAL REFERENCE AND PGA

SLAS285 – JUNE 2000

MECHANICAL DATA

PFB (S-PQFP-G48) PLASTIC QUAD FLATPACK

37

48

1,05

0,95

0,50

36

0,27

0,17

25

24

13

1

5,50 TYP

7,20

SQ

6,80

9,20

SQ

8,80

12

M

0,08

0,05 MIN

Seating Plane

0,13 NOM

Gage Plane

0,25

0°–7°

0,75

0,45

1,20 MAX

NOTES: A. All linear dimensions are in millimeters.

22

B. This drawing is subject to change without notice.

C. Falls within JEDEC MS-026

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

0,08

4073176/B 10/96

IMPORTANT NOTICE

T exas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue

any product or service without notice, and advise customers to obtain the latest version of relevant information

to verify, before placing orders, that information being relied on is current and complete. All products are sold

subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those

pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in

accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent

TI deems necessary to support this warranty . Specific testing of all parameters of each device is not necessarily

performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer’s applications, adequate design and operating

safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent

that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other

intellectual property right of TI covering or relating to any combination, machine, or process in which such

semiconductor products or services might be or are used. TI’s publication of information regarding any third

party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.

Copyright 2000, Texas Instruments Incorporated

Loading...

Loading...