PAL16L8AM, PAL16L8A-2M, PAL16R4AM, PAL16R4A-2M

PAL16R6AM, PAL16R6A-2M, PAL16R8AM, PAL16R8A-2M

STANDARD HIGH-SPEED PAL

SRPS016 – D2705, FEBRUARY 1984 – REVISED MARCH 1992

CIRCUITS

• Choice of Operating Speeds

High-Speed, A Devices . . . 25 MHz Min

Half-Power, A-2 Devices . . . 16 MHz Min

• Choice of Input/Output Configuration

• Package Options Include Both Ceramic DIP

and Chip Carrier in Addition to Ceramic

Flat Package

DEVICE

PAL16L8 10 2 0 6

PAL16R4 8 0 4 (3-state buffers) 4

PAL16R6 8 0 6 (3-state buffers) 2

PAL16R8 8 0 8 (3-state buffers) 0

I

INPUTS

description

These programmable array logic devices feature

high speed and a choice of either standard or

half-power devices. They combine Advanced

Low-Power Schottky technology with proven

titanium-tungsten fuses. These devices will

provide reliable, high-performance substitutes for

conventional TTL logic. Their easy

programmability allow for quick design of ”custom”

functions and typically results in a more compact

circuit board. In addition, chip carriers are

available for further reduction in board space.

The Half-Power versions offer a choice of

operating frequency, switching speeds, and

power dissipation. In many cases, these

Half-Power devices can result in significant power

reduction from an overall system level.

3-STATE

O OUTPUTS

REGISTERED

Q OUTPUTS

I/O

PORT

S

PAL16L8’

J OR W PACKAGE

(TOP VIEW)

I

1

I

2

I

3

I

4

I

5

I

6

I

7

I

8

I

9

GND

I

I

I

I

I

10

PAL16L8’

FK PACKAGE

(TOP VIEW)

I

I

3 2 1 20 19

4

5

6

7

8

910111213

I

GND

V

20

CC

O

19

I/O

18

I/O

17

I/O

16

15

I/O

14

I/O

13

I/O

12

O

11

I

CC

I

O

V

I/O

18

I/O

17

I/O

16

I/O

15

I/O

14

I

O

I/O

The PAL16’ M series is characterized for

operation over the full military temperature range

of –55°C to 125°C.

PAL is a registered trademark of Advanced Micro Devices Inc.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Copyright 1992, Texas Instruments Incorporated

1

PAL16R4AM, PAL16R4A-2M, PAL16R6AM, PAL16R6A-2M, PAL16R8AM, PAL16R8A-2M

STANDARD HIGH-SPEED PAL

SRPS016 – D2705, FEBRUARY 1984 – REVISED MARCH 1992

CIRCUITS

PAL16R4’

J OR W PACKAGE

(TOP VIEW)

CLK

1

I

2

I

3

I

4

I

5

I

6

I

7

I

8

I

9

GND

GND

10

PAL16R6’

J OR W PACKAGE

(TOP VIEW)

CLK

1

I

2

I

3

I

4

I

5

I

6

I

7

I

8

I

9

10

20

19

18

17

16

15

14

13

12

11

20

19

18

17

16

15

14

13

12

11

V

I/O

I/O

Q

Q

Q

Q

I/O

I/O

OE

V

I/O

Q

Q

Q

Q

Q

Q

I/O

OE

CC

CC

FK PACKAGE

3 2 1 20 19

I

4

I

5

I

6

I

7

I

8

910111213

FK PACKAGE

3 2 1 20 19

I

4

I

5

I

6

I

7

I

8

910111213

PAL16R4’

(TOP VIEW)

I

I

CLK

I

OE

GND

PAL16R6’

(TOP VIEW)

I

I

CLK

I

OE

GND

CC

V

I/O

CC

V

I/O

I/O

18

17

16

15

14

I/O

I/O

18

17

16

15

14

Q

I/O

Q

Q

Q

Q

Q

Q

Q

Q

Q

PAL16R8’

J OR W PACKAGE

(TOP VIEW)

CLK

1

I

2

I

3

I

4

I

5

I

6

I

7

I

8

I

9

GND

2

10

V

20

CC

Q

19

Q

18

Q

17

Q

16

15

Q

14

Q

13

Q

12

Q

11

OE

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

I

I

I

I

I

PAL16R8’

FK PACKAGE

(TOP VIEW)

I

I

CLK

3 2 1 20 19

4

5

6

7

8

910111213

I

OE

GND

CC

V

Q

Q

18

17

16

15

14

Q

Q

Q

Q

Q

Q

PAL16L8AM, PAL16L8A-2M, PAL16R4AM, PAL16R4A-2M

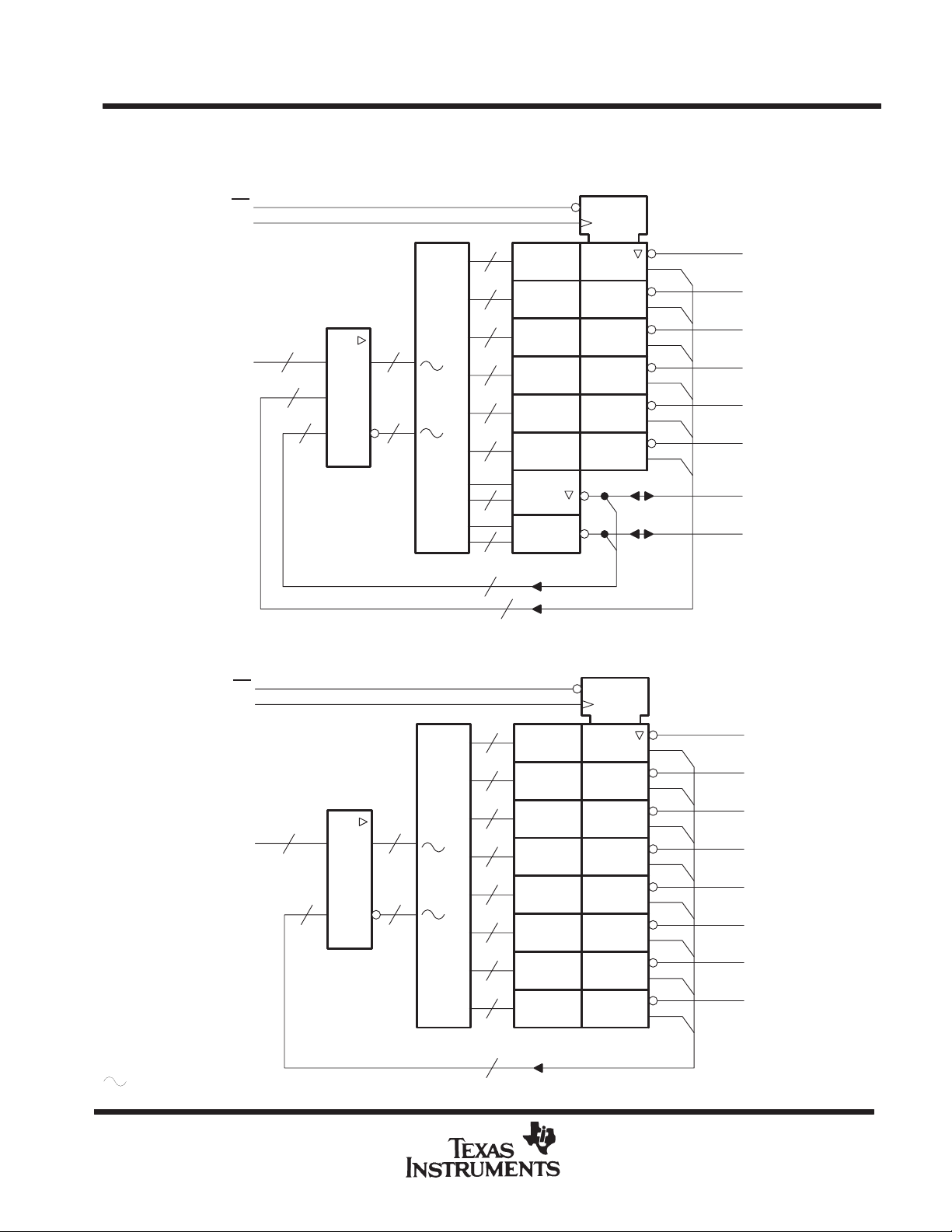

functional block diagrams (positive logic)

PAL16L8AM

PAL16L8A-2M

STANDARD HIGH-SPEED PAL

SRPS016 – D2705, FEBRUARY 1984 – REVISED MARCH 1992

CIRCUITS

OE

CLK

10 16

I

16 x

&

32 X 64

166

PAL16R4AM

PAL16R4A-2M

7

7

7

7

7

7

7

7

6

EN

≥1

O

O

I/O

I/O

I/O

I/O

I/O

I/O

EN 2

C1

denotes fused inputs

816

I

16 x

4

164

&

32 X 64

1D

I = 0

2

Q

Q

Q

Q

I/O

I/O

I/O

I/O

8

8

8

8

7

7

7

7

4

≥1

≥1

EN

4

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

3

PAL16R6AM, PAL16R6A-2M, PAL16R8AM, PAL16R8A-2M

STANDARD HIGH-SPEED PAL

SRPS016 – D2705, FEBRUARY 1984 – REVISED MARCH 1992

functional block diagrams (positive logic)

CIRCUITS

PAL16R6AM

PAL16R6A-2M

OE

CLK

816

I

16 x

6

162

&

32 X 64

PAL16R8AM

PAL16R8A-2M

EN 2

C1

1D

I = 0

2

Q

Q

Q

Q

Q

Q

I/O

I/O

8

8

8

8

8

8

7

7

2

≥1

≥1

EN

6

OE

CLK

denotes fused inputs

816

I

16 x

168

&

32 X 64

EN 2

C1

1D

I = 0

2

Q

Q

Q

Q

Q

Q

Q

Q

8

8

8

8

8

8

8

8

8

≥1

4

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Loading...

Loading...