D

Low Supply Voltage Range 2.5 V – 5.5 V

D

Low Operation Current,

400 mA at 1 MHz, 3 V

D

Ultra-Low Power Consumption

Standby Mode: 2 µA

RAM Retention Off Mode: 0.1 µA

D

Five Power-Saving Modes

D

Wake Up From Standby Mode in 6 µs

D

16-Bit RISC Architecture, 300 ns Instruction

Cycle Time

D

Single Common 32 kHz Crystal, Internal

System Clock up to 3.8 MHz

D

Integrated LCD Driver for up to 120

Segments

D

Integrated Hardware Multiplier Performs

Signed, Unsigned, and MAC Operations for

Operands Up to 16 X 16 Bits

D

Serial Communication Interface (USART),

Select Asynchronous UART or

Synchronous SPI by Software

description

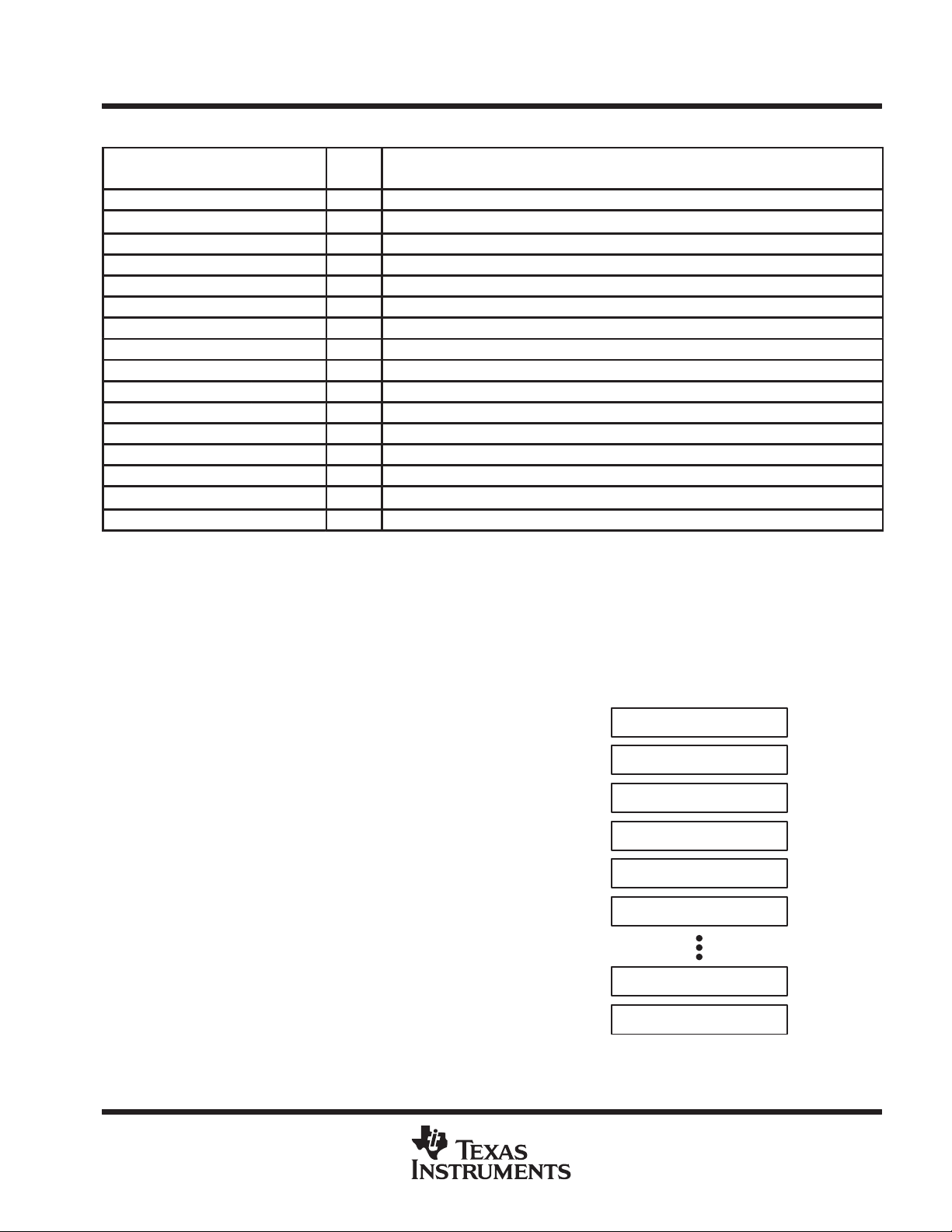

MSP430C33x, MSP430P337A

MIXED SIGNAL MICROCONTROLLERS

SLAS227 – OCTOBER 1999

D

Slope A/D Converter Using External

Components

D

16-Bit Timer With Five Capture/Compare

Registers

D

Serial On-Board Programming

D

Programmable Code Protection by Security

Fuse

D

Family Members Include:

MSP430C336 – 24 KB ROM, 1 KB RAM

MSP430C337 – 32 KB ROM, 1 KB RAM

MSP430P337A – 32 KB OTP, 1 KB RAM

D

EPROM Version Available for Prototyping:

PMS430E337A

D

Available in the following packages:

100 Pin Quad Flat-Pack (QFP),

100 Pin Ceramic Quad Flat-Pack (CFP)

(EPROM Version)

The T exas Instruments MSP430 is an ultra-low power mixed signal microcontroller family consisting of several

devices which features different sets of modules targeted to various applications. The controller is designed to

be battery operated for an extended application lifetime. With the 16-bit RISC architecture, 16 integrated

registers on the CPU, and a constant generator, the MSP430 achieves maximum code efficiency. The

digital-controlled oscillator, together with the frequency lock loop (FLL), provides a wake up from a low-power

mode to an active mode in less than 6 ms. The MSP430x33x series micro-controllers have built in hardware

multiplication and communication capability using asynchronous (UART) and synchronous protocols.

Typical applications of the MSP430 family include electronic gas, water, and electric meters and other sensor

systems that capture analog signals, converts them to digital values, processes, displays, or transmits them to

a host system.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Copyright 1999, Texas Instruments Incorporated

1

MSP430C33x, MSP430P337A

40°C to 85°C

MSP430C337IPJM

25°C

PMS430E337AHFD

MIXED SIGNAL MICROCONTROLLERS

SLAS227 – OCTOBER 1999

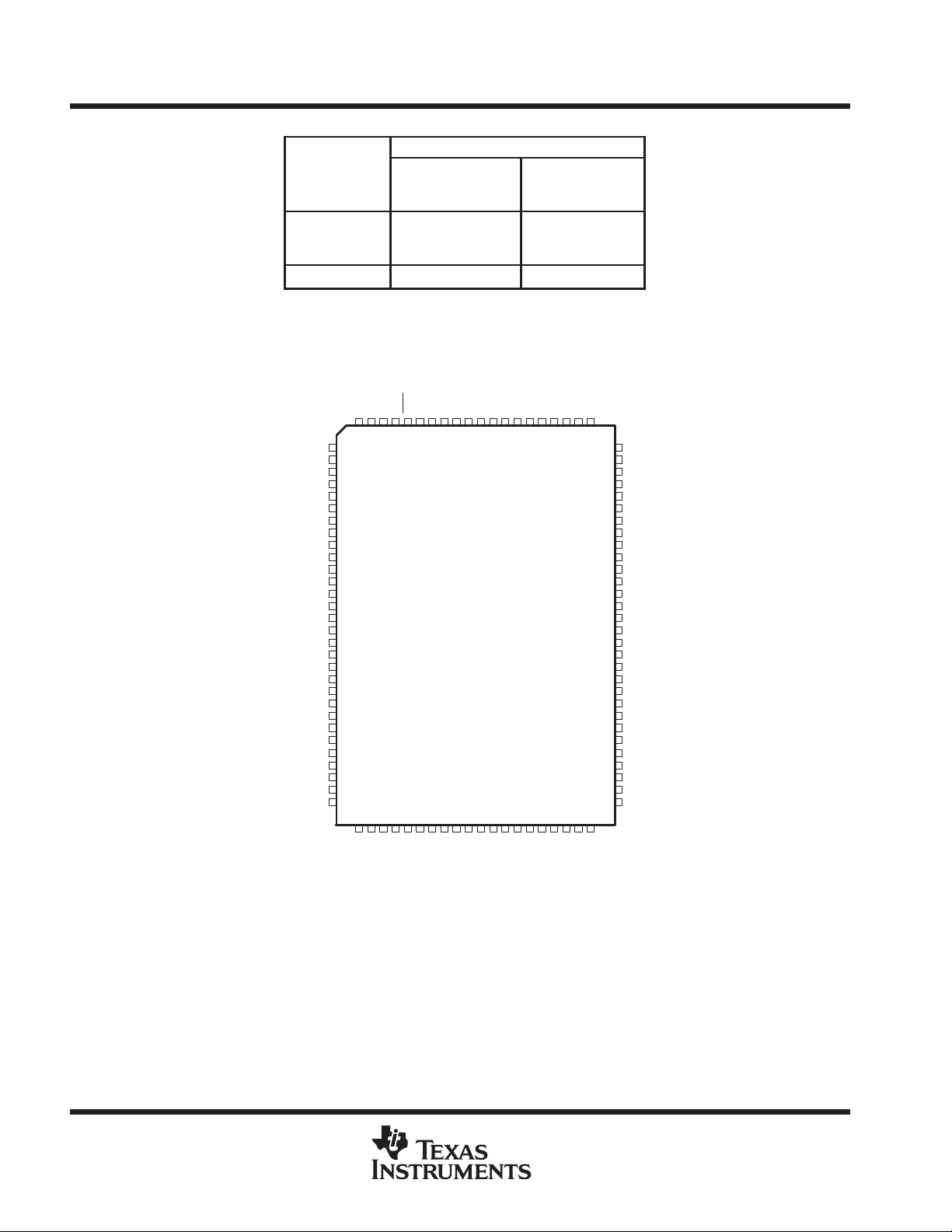

T

A

°

–

°

°

AVAILABLE OPTIONS

PACKAGED DEVICES

PLASTIC

QFP

(PJM)

MSP430C336IPJM

MSP430P337AIPJM

—

PJM or HFD PACKAGE

(TOP VIEW)

CERAMIC

QFP

(HFD)

—

V

CC1

CIN

TP0.0

TP0.1

TP0.2

TP0.3

TP0.4

TP0.5

P0.0

P0.1/RXD

P0.2/TXD

P0.3

P0.4

P0.5

P0.6

P0.7

P1.0

P1.1

P1.2

P1.3

P1.4

P1.5

P1.6

P1.7

P2.0

P2.1

P2.2

V

SS2

V

CC2

NC

SS1

Xin

Xout/TCLK

RST/NMI

TCK

TMS

TDI/VPP

XBUF

V

96

97

98

99

100

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

35

34

33

32

31

TDO/TDI

92

93

94

95

39

38

37

36

R33

91

40

R23

90

41

R13

89

42

R03

S27/O27

S29/O29/CMPI

S28/O28

85

86

87

88

46

45

43

44

S26/O26

S25/O25

S24/O24

82

83

84

49

48

47

S23/O23

81

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

NC

S22/O22

S21/O21

S20/O20

S19/O19

S18/O18

S17/O17

S16/O16

S15/O15

S14/O14

S13/O13

S12/O12

S11/O11

S10/O10

S9/O9

S8/O8

S7/07

S6/O6

S5/O5

S4/O4

S3/O3

S2/O2

S1

S0

COM0

COM1

COM2

COM3

V

SS3

P4.7/URXD

2

P2.3

P2.4

P2.5

P2.6

P2.7

P3.0

P3.1

P3.3/TA0

P3.2/TACLK

NC – No internal connection

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

P3.4/TA1

P3.5/TA2

P3.6/TA3

P3.7/TA4

P4.0

P4.1

P4.2/STE

P4.4/SOMI

P4.3/SIMO

P4.5/UCLK

P4.6/UTXD

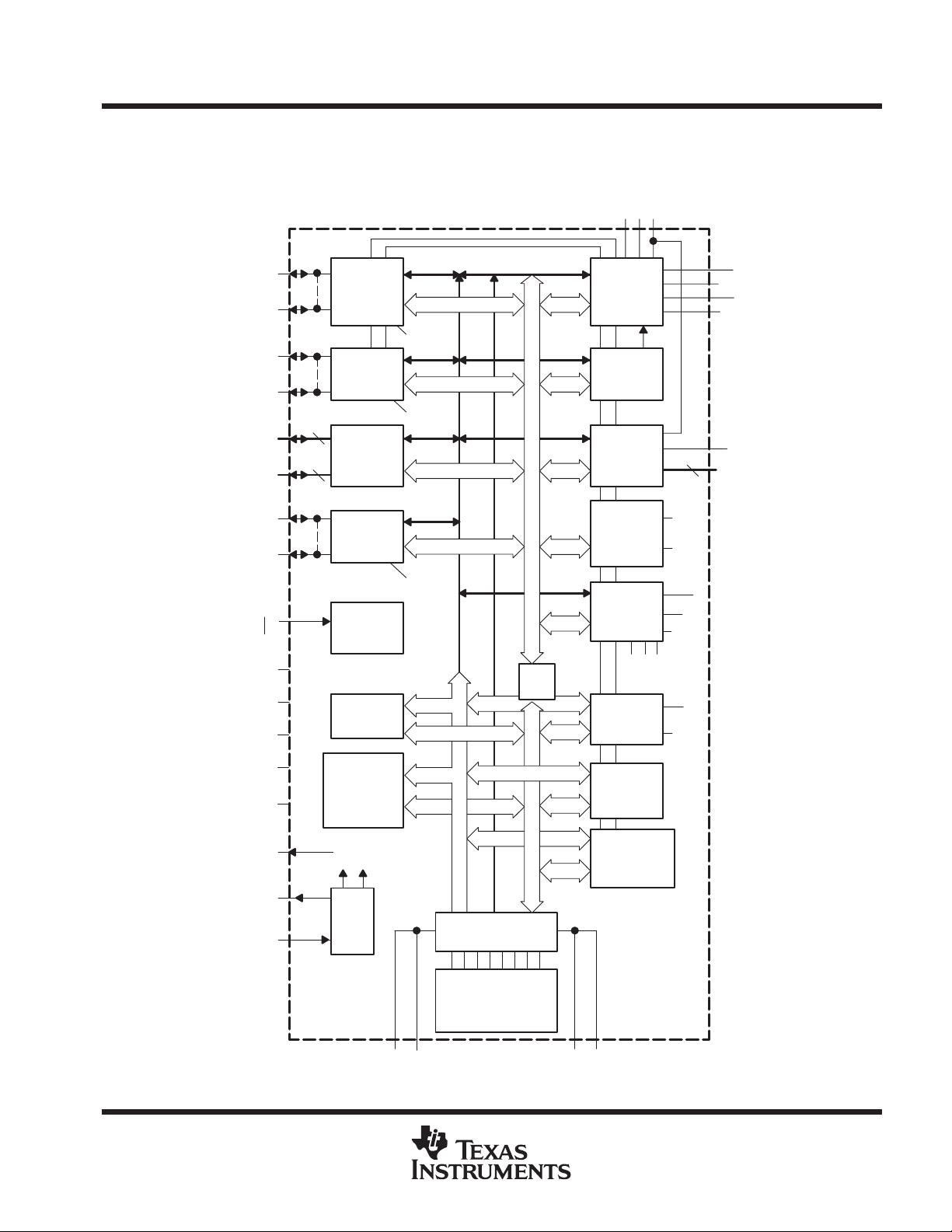

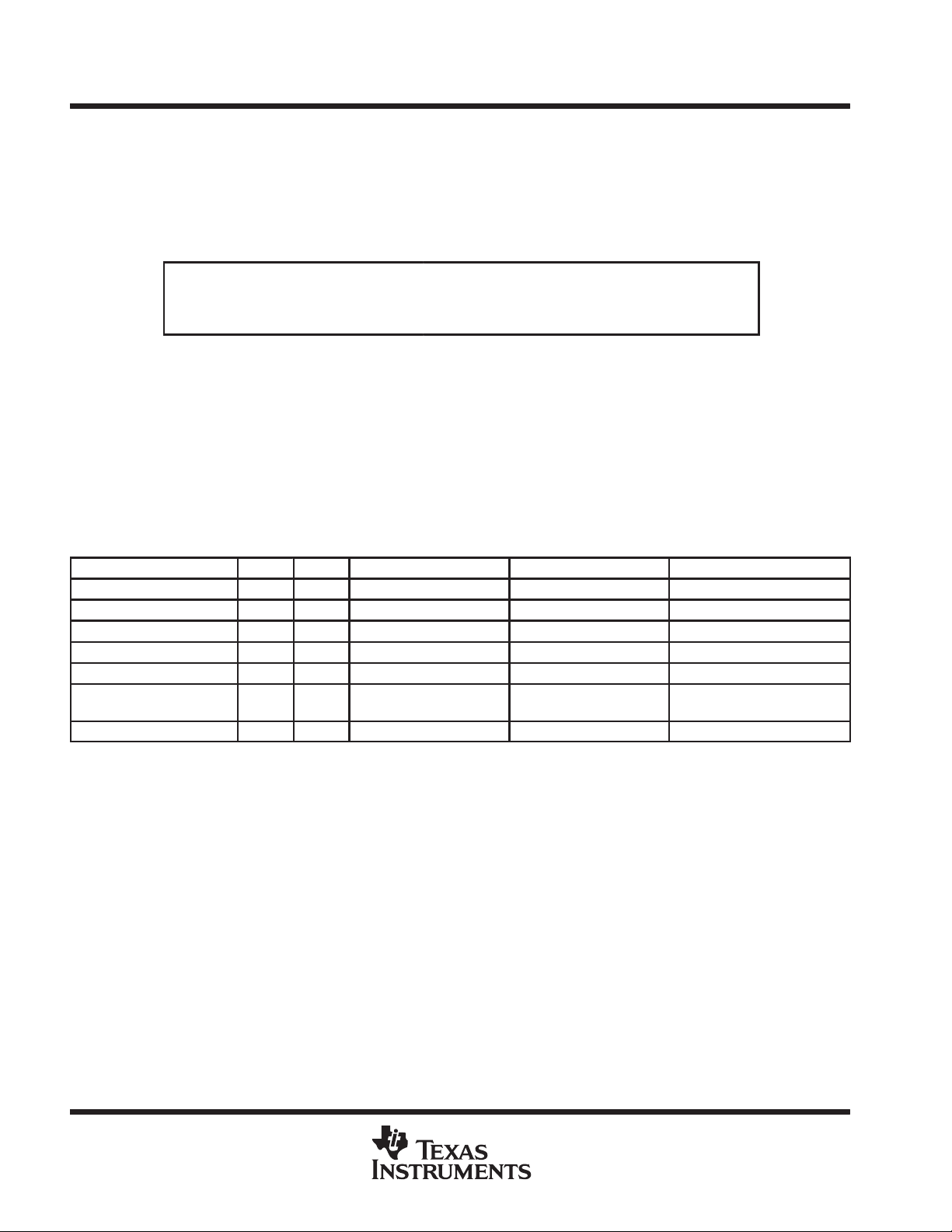

functional block diagram

I/O Port

8 I/O’s, All With

I/O Port

1x8 Digital

Interr. Cap.

I/O’s

3 Int. Vectors

TXD

MSP430C33x, MSP430P337A

MIXED SIGNAL MICROCONTROLLERS

SLAS227 – OCTOBER 1999

Com0–3

S0–28/O2–28

S29/O29/CMPI

R33

LCD

120 Segments

Basic

Timer1

1, 2, 3, 4 MUX

LCD

f

CMPI

R23

R13

R03

V

V

V

V

V

SS3

SS2

SS1

CC2

CC1

XIN Xout XBUF RST/NMI P4.0 P4.7 P2.x P1.x P3.0 P3.7 P0.0 P0.7

I/O Port

8 8

I/O Port

Power-on-

1024B

32 kB OPT or

24/32 kB ROM

ACLK

Oscillator

Interr. Cap.

2x8 I/O’s All

I/O’s

1x8 Digital

Reset

RAM

SRAM

EPROM

C: ROM

P: OTP

MCLK

FLL

System Clock

2 Int. Vectors

E: EPROM

USART TimerA RXD,

MAB, 4 Bit

MAB, 16 Bit

MCB

Test

MDB, 8 Bit

MDB, 16 Bit

JTAG

Bus

Conv

Applications

8 Bit Timer/Port

Timer/Counter

USART

timer

Watchdog TimerA

MPY

Multiplier

A/D Conv.

Timer, O/P

UART or

SPI Function

UTXD

URXD

PWM

16 Bit

15/16 Bit

MAC

MPYS

TXD RXD

STE

UCLK

TACLK

8x8 Bit

16x16 Bit

CIN

6

TP0.0–0.5

SOMI

SIMO

TA0–4

CPU

Incl. 16 Reg.

TDI/VPP

TDO/TDI

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TMS

TCK

3

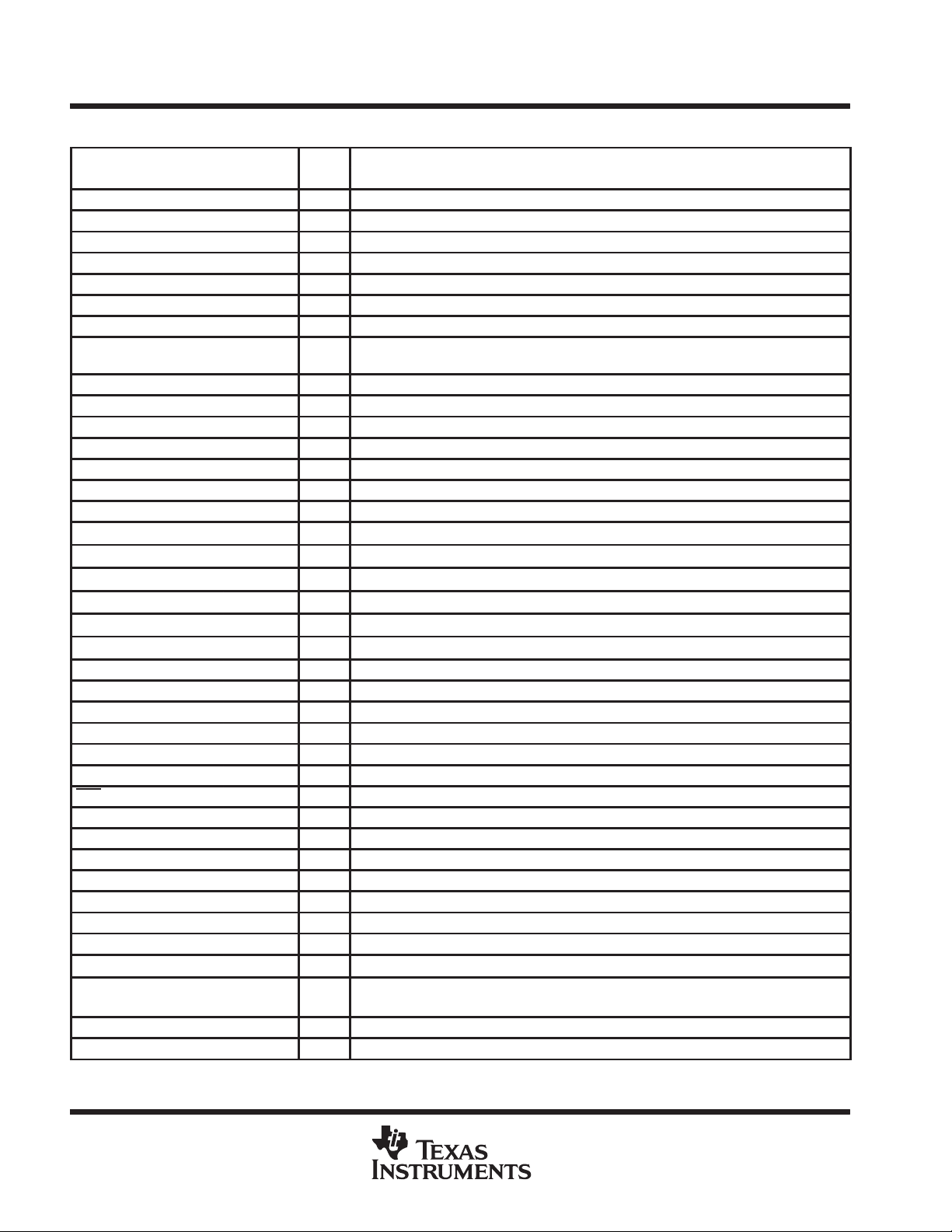

MSP430C33x, MSP430P337A

I/O

DESCRIPTION

MIXED SIGNAL MICROCONTROLLERS

SLAS227 – OCTOBER 1999

Terminal Functions

TERMINAL

NAME NO.

CIN 2 I Input port. CIN is used as an enable for counter TPCNT1 – (Timer/Port).

COM0–3 56–53 O Common outputs. COM0-3 are used for LCD backplanes – LCD

P0.0 9 I/O General-purpose digital I/O

P0.1/RXD 10 I/O General-purpose digital I/O, receive digital Input port – 8-bit Timer/Counter

P0.2/TXD 11 I/O General-purpose digital I/O, transmit data output port – 8-bit Timer/Counter

P0.3–P0.7 12–16 I/O Five general-purpose digital I/Os, bit 3-7

P1.0–P1.7 17–24 I/O Eight general-purpose digital I/Os, bit 0-7

P2.0–P2.7 25–27,

31–35

P3.0, P3.1 36,37 I/O Two general-purpose digital I/Os, bit 0 and bit 1

P3.2/TACLK 38 I/O General-purpose digital I/O, clock input – Timer_A

P3.3/TA0 39 I/O General-purpose digital I/O, capture I/O, or PWM output port – Timer_A CCR0

P3.4/TA1 40 I/O General-purpose digital I/O, capture I/O, or PWM output port – Timer_A CCR1

P3.5/TA2 41 I/O General-purpose digital I/O, capture I/O, or PWM output port – Timer_A CCR2

P3.6/TA3 42 I/O General-purpose digital I/O, capture I/O, or PWM output port – Timer_A CCR3

P3.7/TA4 43 I/O General-purpose digital I/O, capture I/O, or PWM output port – Timer_A CCR4

P4.0 44 I/O General-purpose digital I/O, bit 0

P4.1 45 I/O General-purpose digital I/O, bit 1

P4.2/STE 46 I/O General-purpose digital I/O, slave transmit enable – USART/SPI mode

P4.3/SIMO 47 I/O General-purpose digital I/O, slave in/master out – USART/SPI mode

P4.4/SOMI 48 I/O General-purpose digital I/O, master in/slave out – USART/SPI mode

P4.5/UCLK 49 I/O General-purpose digital I/O, external clock input – USART

P4.6/UTXD 50 I/O General-purpose digital I/O, transmit data out – USART/UART mode

P4.7/URXD 51 I/O General-purpose digital I/O, receive data in – USART/UART mode

R03 88 I Input port of fourth positive (lowest) analog LCD level (V5) – LCD

R13 89 I Input port of third most positive analog LCD level (V3 of V4) – LCD

R23 90 I Input port of second most positive analog LCD level (V2) – LCD

R33 91 O Output of most positive analog LCD level (V1) – LCD

RST/NMI 96 I Reset input or non-maskable interrupt input port

S0 57 O Segment line S0 – LCD

S1 58 O Segment line S1 – LCD

S2/O2–S5/O5 59–62 O Segment lines S2 to S5 or digital output ports, O2-O5, group 1 – LCD

S6/O6–S9/O9 63–66 O Segment lines S6 to S9 or digital output ports O6-O9, group 2 – LCD

S10/O10–S13/O13 67–70 O Segment lines S10 to S13 or digital output ports O10-O13, group 3 – LCD

S14/O14–S17/O17 71–74 O Segment lines S14 to S17 or digital output ports O14-O17, group 4 – LCD

S18/O18–S21/O21 75–78 O Segment lines S18 to S21 or digital output ports O18-O21, group 5 – LCD

S22/O22–S25/O25 79, 81–83 O Segment line S22 to S25 or digital output ports O22-O25, group 6 – LCD

S26/O26–S29/O29/CMPI 84–87 O Segment line S26 to S29 or digital output ports O26-O29, group 7 – LCD. Segment line S29

TCK 95 I Test clock. TCK is the clock input port for device programming and test

TDI/VPP 93 I Test data input. TDI/VPP is used as a data input port or input for programming voltage

I/O Eight general-purpose digital I/Os, bit 0-7

can be used as comparator input port CMPI – Timer/Port

4

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

I/O

DESCRIPTION

MSP430C33x, MSP430P337A

MIXED SIGNAL MICROCONTROLLERS

SLAS227 – OCTOBER 1999

Terminal Functions

TERMINAL

NAME NO.

TMS 94 I Test mode select. TMS is used as an input port for device programming and test

TDO/TDI 92 I/O Test data output port. TDO/TDI data output or programming data input terminal

TP0.0 3 O General-purpose 3-state digital output port, bit 0 – Timer/Port

TP0.1 4 O General-purpose 3-state digital output port, bit 1 – Timer/Port

TP0.2 5 O General-purpose 3-state digital output port, bit 2 – Timer/Port

TP0.3 6 O General-purpose 3-state digital output port, bit 3 – Timer/Port

TP0.4 7 O General-purpose 3-state digital output port, bit 4 – Timer/Port

TP0.5 8 I/O General-purpose 3-state digital input/output port, bit 5 – Timer/Port

VCC1 1 Positive supply voltage

VCC2 29 Positive supply voltage

VSS1 100 Ground reference

VSS2 28 Ground reference

VSS3 52 Ground reference

XBUF 97 O System clock (MCLK) or crystal clock (ACLK) output

Xin 99 I Input port for crystal oscillator

Xout/TCLK 98 I/O Output terminal of crystal oscillator or test clock input

short-form description

processing unit

The processing unit is based on a consistent and orthogonal designed CPU and instruction set. This design

structure results in a RISC-like architecture, highly transparent to the application development and is

distinguished due to ease of programming. All operations, other than program-flow instructions consequently

are performed as register operations in conjunction with seven addressing modes for source and four modes

for destination operand.

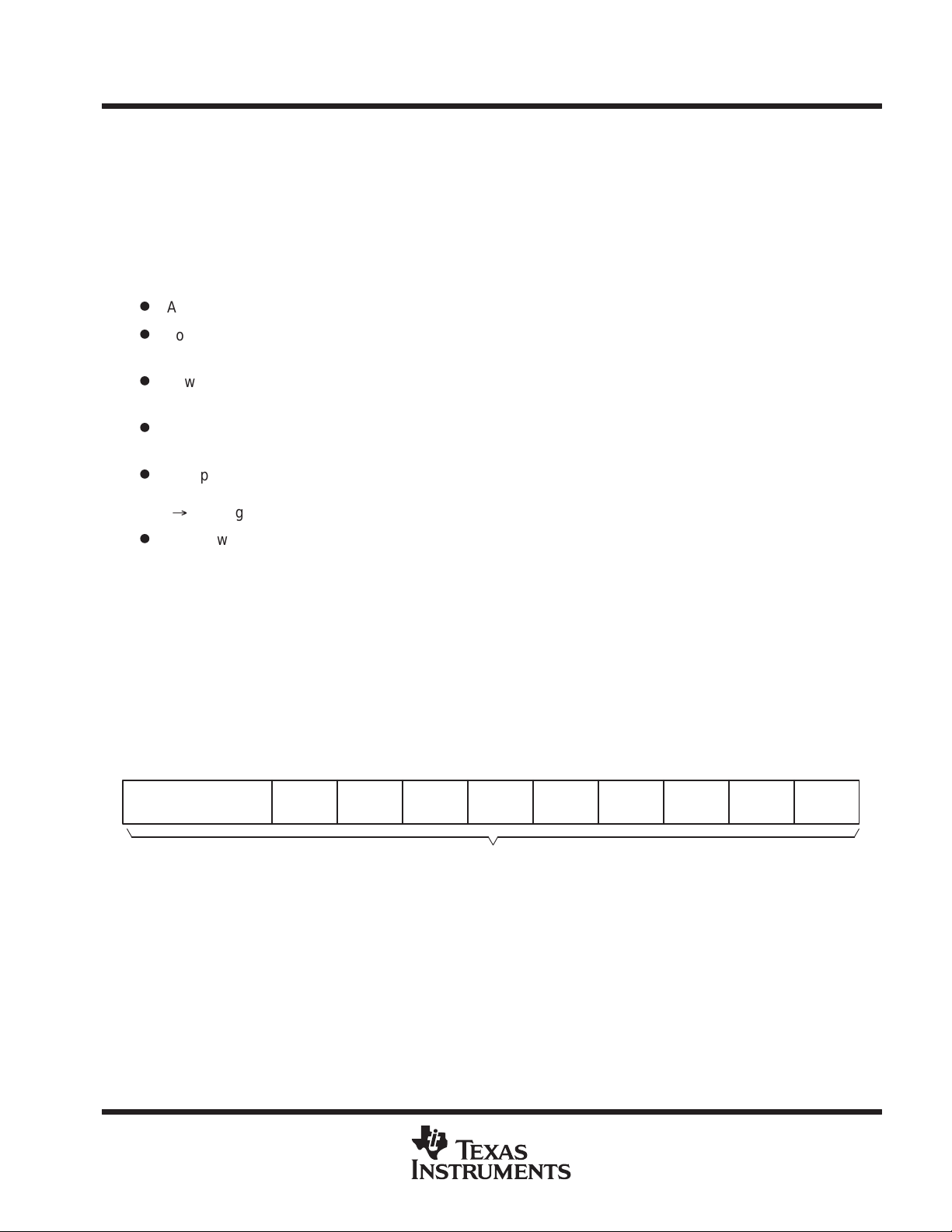

CPU registers

Sixteen registers are located inside the CPU,

providing reduced instruction execution time. This

reduces a register-register operation execution

time to one cycle of the processor frequency.

Four of the registers are reserved for special use

as a program counter, a stack pointer, a status

register and a constant generator. The remaining

registers are available as general purpose

registers.

Peripherals are connected to the CPU using a

data address and control bus and can be handled

easily with all instructions for memory manipulation.

Program Counter

Stack Pointer

Status Register

Constant Generator

General Purpose Register

General Purpose Register

General Purpose Register R14

PC/R0

SP/R1

SR/CG1/R2

CG2/R3

R4

R5

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

General Purpose Register

R15

5

MSP430C33x, MSP430P337A

MIXED SIGNAL MICROCONTROLLERS

SLAS227 – OCTOBER 1999

instruction set

The instruction set for this register-register architecture provides a powerful and easy-to-use assembly

language. The instruction set consists of 51 instructions, with three formats and seven addressing modes.

T able 1 provides a summation and example of the three types of instruction formats; the addressing modes are

listed in Table 2.

Table 1. Instruction Word Formats

Dual operands, source-destination

e.g. ADD R4,R5 R4 + R5 → R5

Single operands, destination only e.g. CALL R8 PC → (TOS), R8→ PC

Relative jump, un–/conditional e.g. JNE Jump-on equal bit = 0

Instructions that can operate on both word and byte data are differentiated by the suffix .B when a byte operation

is required.

Examples: Instructions for word operation: Instructions for byte operation:

MOV EDE,TONI MOV.B EDE,TONI

ADD #235h,&MEM ADD.B #35h,&MEM

PUSH R5 PUSH.B R5

SWPB R5 –––

Table 2. Address Mode Descriptions

ADDRESS MODE S D SYNTAX EXAMPLE OPERATION

Register √ √ MOV Rs,Rd MOV R10,R11 R10 → R11

Indexed √ √ MOV X(Rn),Y(Rm) MOV 2(R5),6(R6) M(2+R5) → M(6+R6)

Symbolic (PC relative) √ √ MOV EDE,TONI M(EDE) → M(TONI)

Absolute √ √ MOV &MEM,&TCDAT M(MEM) → M(TCDAT)

Indirect √ MOV @Rn,Y(Rm) MOV @R10,Tab(R6) M(R10) → M(Tab+R6)

Indirect autoincrement √ MOV @Rn+,Rm MOV @R10+,R11 M(R10) → R11

Immediate √ MOV #X,TONI MOV #45,TONI #45 → M(TONI)

NOTE 1: S = source, D = destination.

R10 + 2

→ R10

Computed branches (BR) and subroutine calls (CALL) instructions use the same addressing modes as the other

instructions. These addressing modes provide

indirect

addressing, ideally suited for computed branches and

calls. The full use of this programming capability permits a program structure different from conventional 8- and

16-bit controllers. For example, numerous routines can easily be designed to deal with pointers and stacks

instead of using flag type programs for flow control.

6

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

MSP430C33x, MSP430P337A

MIXED SIGNAL MICROCONTROLLERS

SLAS227 – OCTOBER 1999

operation modes and interrupts

The MSP430 operating modes support various advanced requirements for ultra-low power and ultra-low energy

consumption. This is achieved by the intelligent management of the operations during the different module

operation modes and CPU states. The requirements are fully supported during interrupt event handling. An

interrupt event awakens the system from each of the various operating modes and returns with the RETI

instruction to the mode that was selected before the interrupt event. The clocks used are ACLK and MCLK.

ACLK is the crystal frequency and MCLK is a multiple of ACLK and is used as the system clock.

The following five operating modes are supported:

D

Active mode (AM). The CPU is enabled with different combinations of active peripheral modules.

D

Low power mode 0 (LPM0). The CPU is disabled, peripheral operation continues, ACLK and MCLK signals

are active, and loop control for MCLK is active.

D

Low power mode 1 (LPM1). The CPU is disabled, peripheral operation continues, ACLK and MCLK signals

are active, and loop control for MCLK is inactive.

D

Low power mode 2 (LMP2). The CPU is disabled, peripheral operation continues, ACLK signal is active,

and MCLK and loop control for MCLK are inactive.

D

Low power mode 3 (LMP3). The CPU is disabled, peripheral operation continues, ACLK signal is active,

MCLK and loop control for MCLK are inactive, and the dc generator for the digital controlled oscillator (DCO)

(³MCLK generator) is switched off.

D

Low power mode 4 (LMP4). The CPU is disabled, peripheral operation continues, ACLK signal is inactive

(crystal oscillator stopped), MCLK and loop control for MCLK are inactive, and the dc generator for the DCO

is switched off.

The special function registers (SFR) include module-enable bits that stop or enable the operation of the specific

peripheral module. All registers of the peripherals may be accessed if the operational function is stopped or

enabled. However, some peripheral current-saving functions are accessed through the state of local register

bits. An example is the enable/disable of the analog voltage generator in the LCD peripheral, which is turned

on or off using one register bit.

The most general bits that influence current consumption and support fast turn-on from low power operating

modes are located in the status register (SR). Four of these bits control the CPU and the system clock generator:

SCG1, SCG0, OscOff, and CPUOff.

15 9 8 7 0

Reserved For Future

Enhancements

interrupts

Software determines the activation of interrupts through the monitoring of hardware set interrupt flag status bits,

the control of specific interrupt enable bits in SRs, the establishment of interrupt vectors, and the programming

of interrupt handlers. The interrupt vectors and the power-up starting address are located in ROM address

locations 0FFFFh through 0FFE0h. Each vector contains the 16-bit address of the appropriate interrupt handler

instruction sequence. Table 3 provides a summation of interrupt functions and addresses.

V SCG1 SCG0 OscOff CPUOff GIE N Z C

rw-0

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

7

MSP430C33x, MSP430P337A

Timer/Port

,,

Maskable

0FFE8h

4

MIXED SIGNAL MICROCONTROLLERS

SLAS227 – OCTOBER 1999

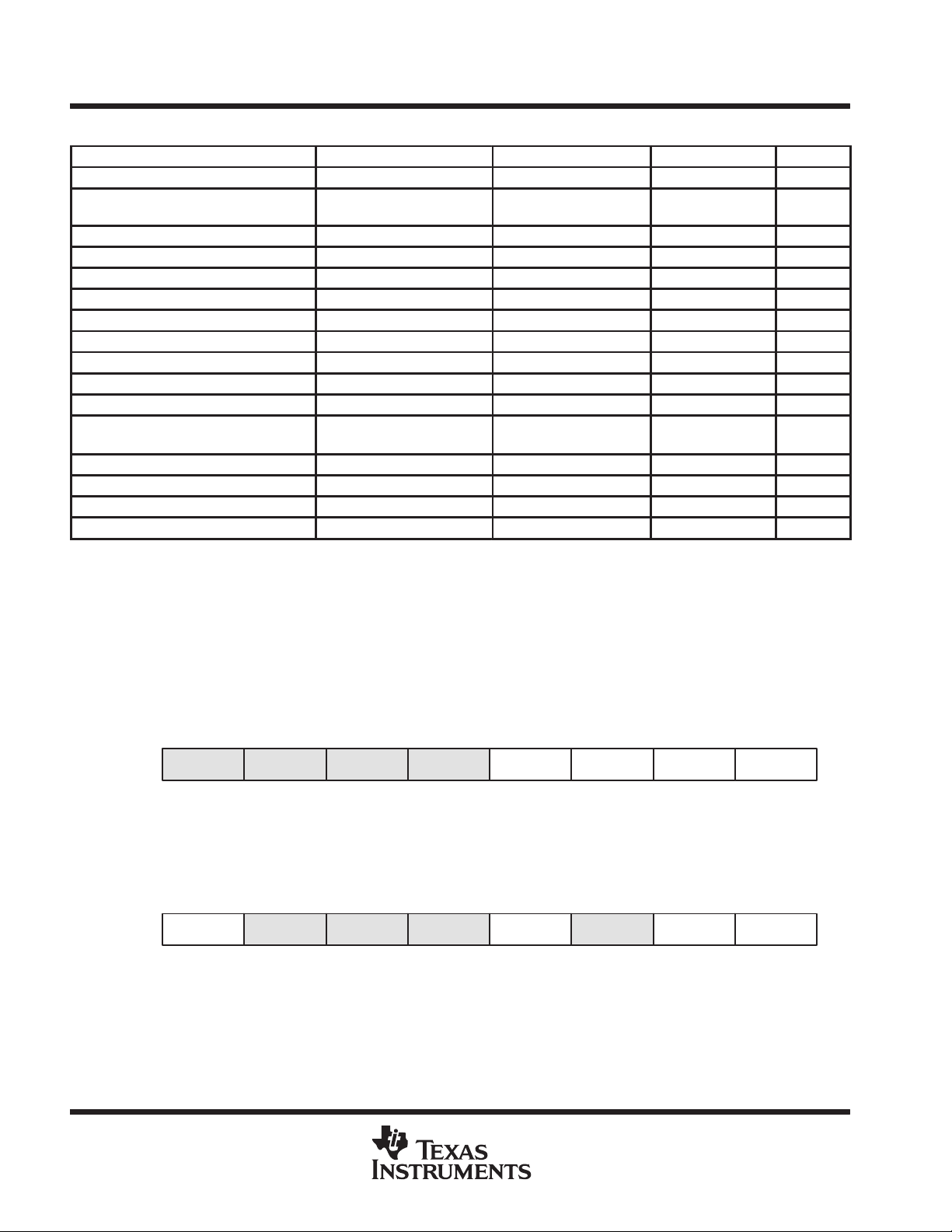

Table 3. Interrupt Functions and Addresses

INTERRUPT SOURCE INTERRUPT FLAG SYSTEM INTERRUPT WORD ADDRESS PRIORITY

Power-up, external reset, Watchdog WDTIFG Reset 0FFFEh 15, highest

NMI,

Oscillator fault

Dedicated I/O P0.0 P0IFG.0 Mmaskable 0FFFAh 13

Dedicated I/O P0.1 or 8-bit Timer/Counter P0IFG.1 Maskable 0FFF8h 12

Watchdog Timer WDTIFG Maskable 0FFF4h 10

Timer_A CCIFG0 (see Note 3) Maskable 0FFF2h 9

Timer_A TAIFG (see Note 3) Maskable 0FFF0h 8

UART receive URXIFG Maskable 0FFEEh 7

UART transmit UTXIFG Maskable 0FFECh 6

I/O port P2 P2IFG.07 (see Note 2) Maskable 0FFE6h 3

I/O port P1 P1IFG.07 (see Note 2) Maskable 0FFE4h 2

Basic Timer1 BTIFG Maskable 0FFE2h 1

I/O port P0.2 – P0.7 P0IFG.27 (see Note 2) Maskable 0FFE0h 0, lowest

NOTES: 2. Multiple source flags

3. Interrupt flags are located in the individual module registers.

4. Non-maskable : neither the individual or the general interrupt enable bit will disable an interrupt event.

5. (Non)-maskable: the individual interrupt enable bit can disable an interrupt event, but the general interrupt enable bit cannot.

NMIIFG (see Notes 2 and 4)

OFIFG (see Notes 2 and 5)

RC1FG, RC2FG, EN1FG

(see Note 3)

Non-maskable

(Non)-maskable

Maskable 0FFF6h 11

0FFFCh 14

0FFEAh 5

special function registers

Most interrupt and module enable bits are collected into the lowest address space. Special function register bits

that are not allocated to a functional purpose are not physically present in the device. Simple software access

is provided with this arrangement.

interrupt enable 1 and 2

Address

0h

7654 0

321

P0IE.1 OFIE WDTIE

rw-0 rw-0 rw-0 rw-0

P0IE.0

WDTIE: Watchdog Timer interrupt enable signal

OFIE: Oscillator fault interrupt enable signal

P0IE.0: Dedicated I/O P0.0 interrupt enable signal

P0IE.1: P0.1 or 8-bit Timer/Counter, RXD interrupt enable signal

Address

01h BTIE

7654 0

rw-0

321

TPIE UTXIE URXIE

rw-0 rw-0 rw-0

URXIE: USART receive interrupt enable signal

UTXIE: USART transmit interrupt enable signal

TPIE: Timer/Port interrupt enable signal

BTIE: Basic Timer1 interrupt enable signal

8

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

MIXED SIGNAL MICROCONTROLLERS

interrupt flag registers 1 and 2

Address

02h NMIIFG P0IFG.0

7654 0

321

P0IFG.1 OFIFG WDTIFG

MSP430C33x, MSP430P337A

SLAS227 – OCTOBER 1999

WDTIFG: Set on overflow or security key violation

or

Reset on VCC1 power-on or reset condition at RST/NMI-pin

OFIFG: Flag set on oscillator fault

P0IFG.0: Dedicated I/O P0.0

P0IFG.1: P0.1 or 8-bit Timer/Counter, RXD

NMIIFG: Signal at RST

Address

03h BTIFG

7654 0

rw

/NMI-pin

URXIFG: USART receive flag

UTXIFG: USART transmit flag

BTIFG: Basic Timer1 flag

module enable registers 1 and 2

Address

04h

Address

05h

7654 0321

7654 0

rw-0 rw-1 rw-0

rw-0 rw-0

321

UTXIFG URXIFG

rw-1 rw-0

321

UTXE URXE

UTXE: USART transmit enable

URXE: USART receive enable

Legend rw:

rw-0:

Bit can be read and written

Bit can be read and written. It is reset by PUC

SFR bit not present in device

rw-0 rw-0

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

9

Loading...

Loading...