Page 1

现货库存、技术资料、百科信息、热点资讯,精彩尽在鼎好!

5-V Low-Drop Fixed Voltage Regulator TLE 4270

Features

• Output voltage tolerance ≤ ± 2 %

• Low-drop voltage

• Integrated overtemperature protection

• Reverse polarity protection

• Input voltage up to 42 V

• Overvoltage protection up to 65 V (≤ 400 ms)

• Short-circuit proof

• Suitable for use in automotive electronics

• Wide temperature range

• Adjustable reset time

• ESD protection > 4000 V

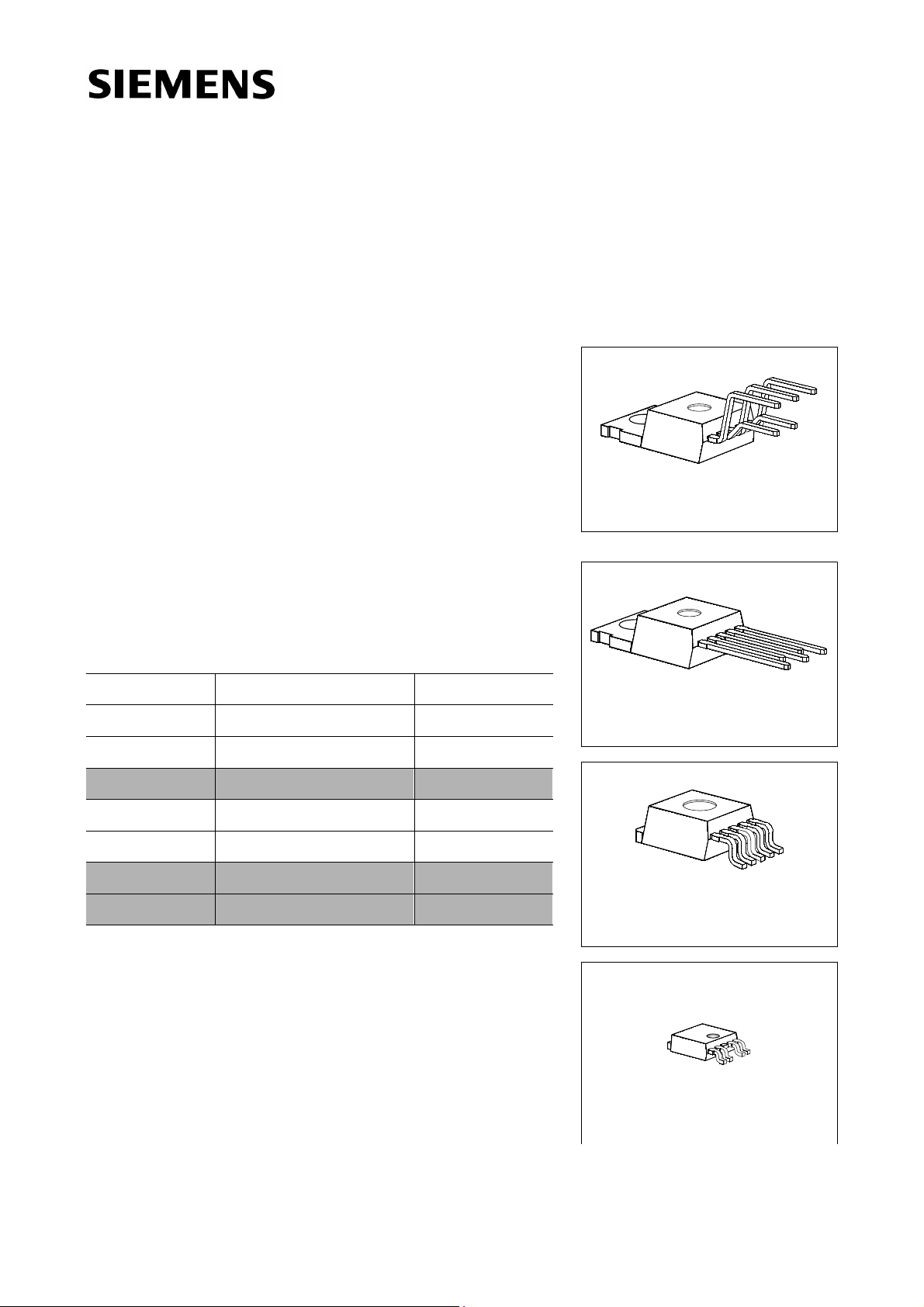

P-TO220-5-11

(P-TO220-5-1)

Type Ordering Code Package

TLE 4270 Q67000-A9209-A903 P-TO220-5-11

P-TO220-5-12

(P-TO220-5-2)

TLE 4270 S Q67000-A9243-A904 P-TO220-5-12

TLE 4270 G Q67006-A9201-A901 P-TO263-5-1

▼ TLE 4270 Q67000-A9209-A801 P-TO220-5-1

▼ TLE 4270 S Q67000-A9243-A802 P-TO220-5-2

TLE 4270 G Q67006-A9201-A802 P-TO220-5-8

▼

P-TO263-5-1

TLE 4270 D Q67006-A9360 P-TO252-5-1

●

(P-TO220-5-8)

▼ Not for new design ● New type

Functional Description

This device is a 5-V low-drop fixed-voltage regula tor.

The maximum input voltage is 42 V (65 V, ≤ 400 ms).

Up to an input voltage of 26 V and for an output current

up to 550 mA it regulates the output volta ge within a

2 % accuracy. The short circuit protection limits the

P-TO252-5-1 (D-PAK)

output current of more than 650 mA. Th e device incorporates overvoltage protection

and temperature protection that disables the circuit at unpermissibly high temperatures.

Semiconductor Group 1 1998-11-01

Page 2

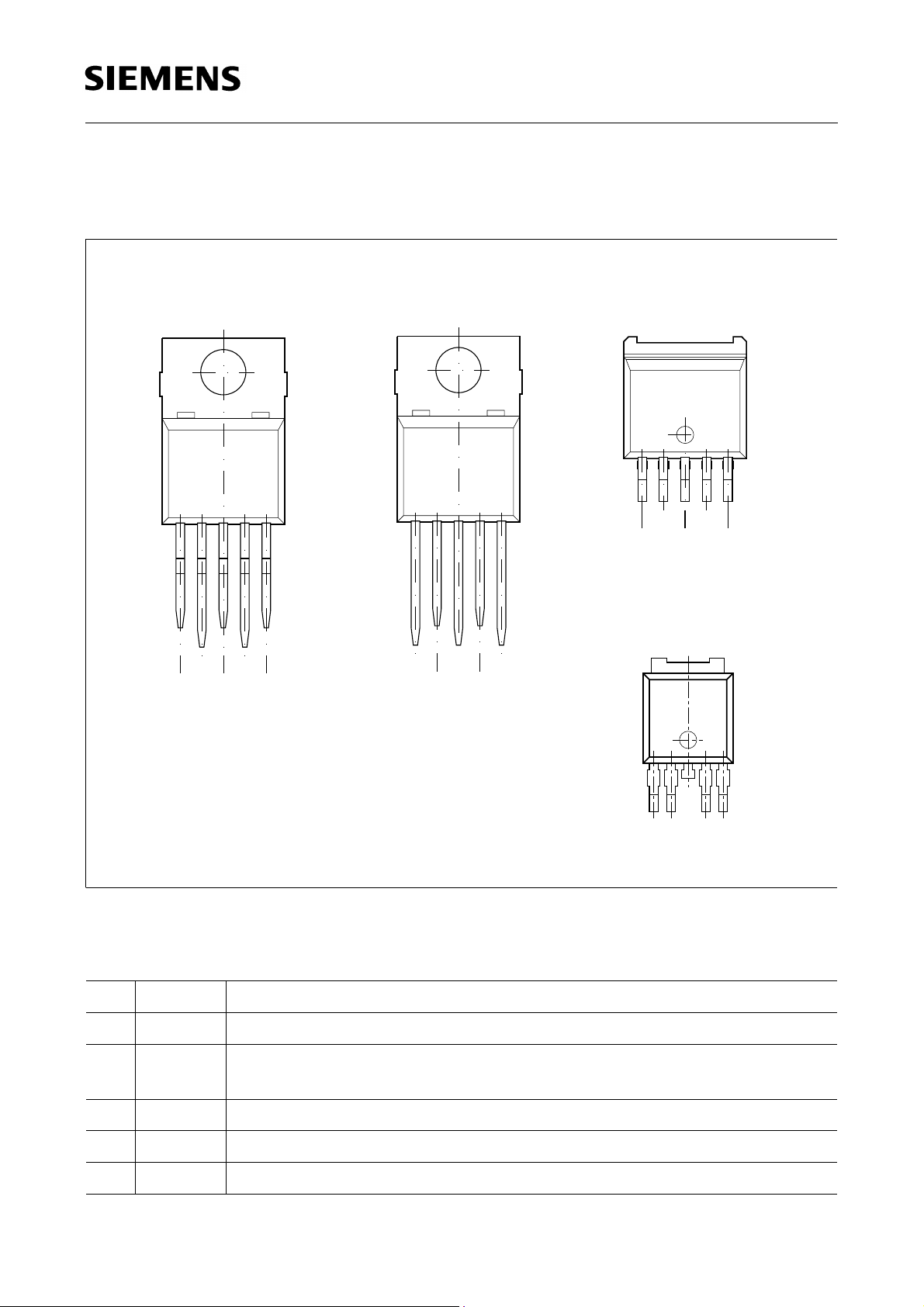

Pin Configuration

AEP01923

ΙROGNDDQ

51

(top view)

TLE 4270

P-TO220-5-11

(P-TO220-5-1)

P-TO220-5-12

(P-TO220-5-2)

Ι

GNDDQ

RO

AEP02172

P-TO263-5-1

(P-TO220-5-8)

15

RO

51

Ι

GNDDQ

AEP01922

P-TO252-5-1 (D-PAK)

GND

15

ROΙ DQ

AEP02580

Figure 1

Pin Definitions and Functions

Pin Symbol Function

1 I Input; block to ground directly on the IC with ceramic capacitor

2RO Reset Output; the open collector output is connected to the 5 V output

via an integrated resistor of 30 kΩ.

3GNDGround; internally connected to heatsink.

4D Reset Delay; connect a capacitor to ground for delay time adjustment.

5Q 5-V Output; block to ground with 22 µF capacitor, ESR < 3 Ω.

Semiconductor Group 2 1998-11-01

Page 3

TLE 4270

Application Description

V

The IC regulates an in put vol tage in the rang e of 5.5 V <

< 36 V to V

I

to 26 V it produces a regulated output current of more than 550 mA. Above 26 V the

save-operating-area protection allows operation up to 36 V with a regulated output

current of more than 300 mA. Overvoltage protection limits operation at 42 V. The

overvoltage protection hysteresis restores operation if the input voltage has dropped

V

below 36 V. A reset signal is generated for an output voltage of

< 4.5 V . The dela y for

Q

power-on reset can be set externally with a capacitor.

Design Notes for External Components

C

An input capacitor

is necessary for compensation of lin e influences. The resonant

I

circuit consisting of lead inductance and input capacitance can be damped by a resistor

C

of approx. 1 Ω in series with

the regulating circuit. Stability is guaranteed at values of

. An output capacitor CQ is necessary for the stability of

I

C

≥ 22 µF and an ESR of

Q

< 3 Ω.

=5.0V. Up

Qnom

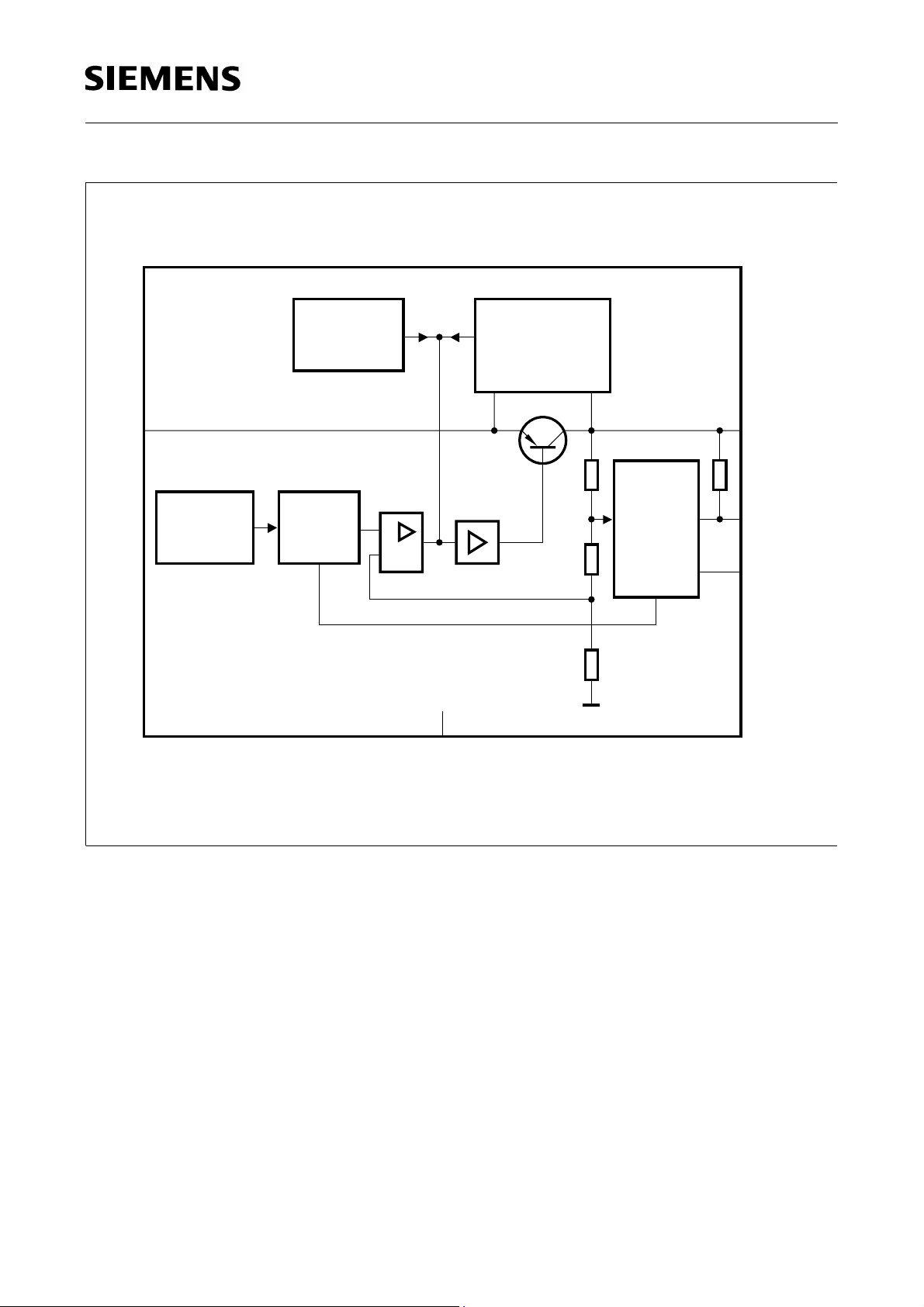

Circuit Description

The control amplifier compares a reference voltage, which is kept highly accurate by

resistance adjustment, to a volt age that is proportion al to the output voltag e and drives

the base of a series transistor via a buffer. Saturation control as a function of the load

current prevents any over-saturation of the power element.

C

If the output voltage decreases below 4.5 V, an external capacitor

discharged by the reset generator. If the volt age on this capacitor drops below

on pin 4 (D) will be

D

V

DRL

, a

reset signal is generated o n pin 2 (R O), i. e. res et ou tput i s se t low . If t he ou tput voltage

C

rises above 4.5 V,

the voltage on the capacitor reaches

will be charged with constant current. After the power-on-reset time

D

V

and the reset output will be set high again. The

DU

value of the power-on-reset time can be set within a wide range depending of the

C

capacitance of

.

D

The IC also incorporates a number of internal circuits for protection against:

• Overload

• Overvoltage

• Overtemperature

• Reverse polarity

Semiconductor Group 3 1998-11-01

Page 4

TLE 4270

Input

1

Adjustment

Temperature

Sensor

Bandgap

Reference

Control

Amplifier

+

-

3

GND

Buffer

Saturation

Control and

Protection

Circuit

Reset

Generator

5

Output

2

Reset

Output

4

Reset

Delay

AEB01924

Figure 2

Block Diagram

Semiconductor Group 4 1998-11-01

Page 5

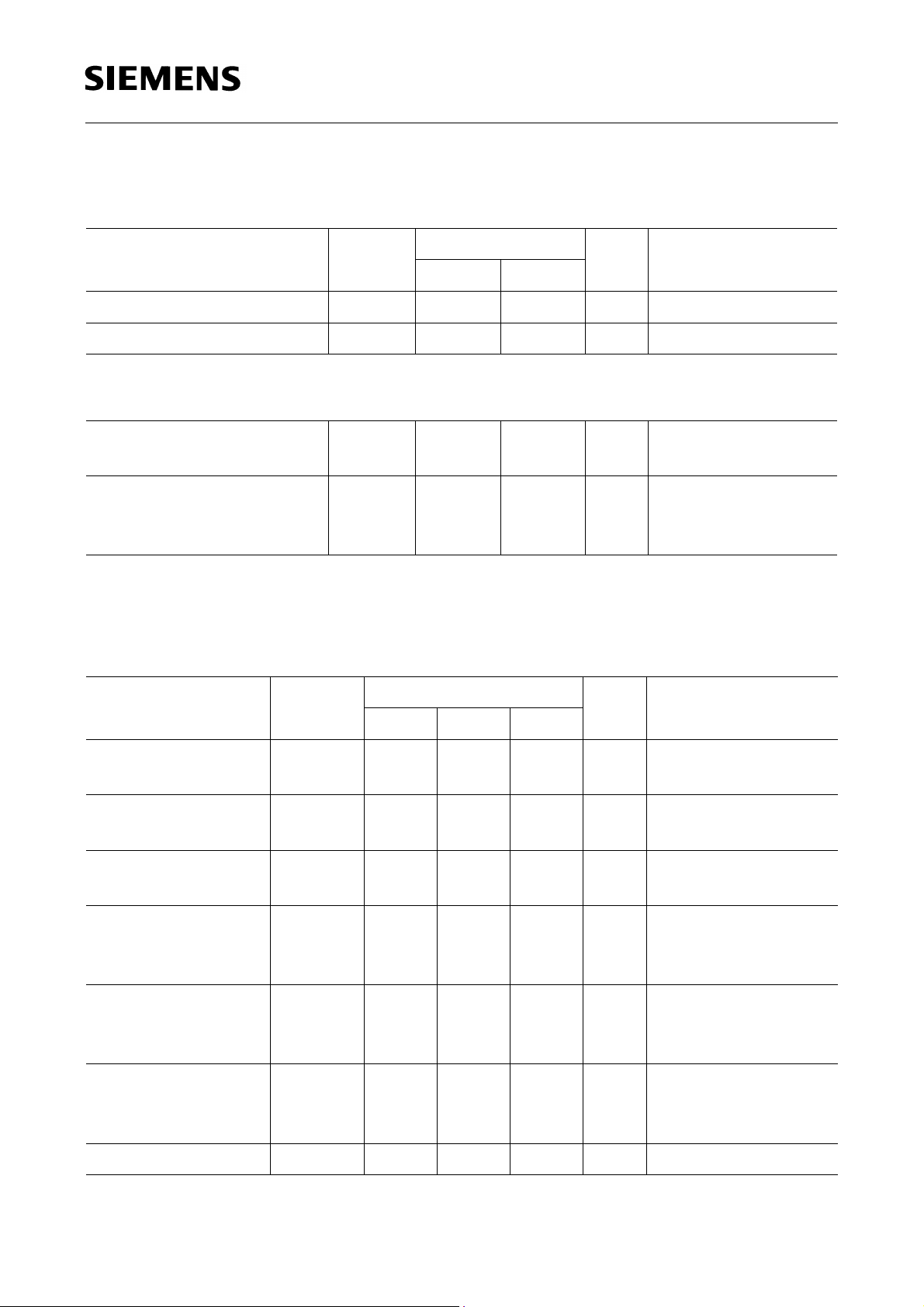

Absolute Maximum Ratings

T

= – 40 to 150 °C

j

Parameter Symbol Limit Values Unit Notes

min. max.

Input

TLE 4270

Voltage

Voltage

Current

Reset Output

Voltage

Current

Reset Delay

Voltage

Current

Output

Voltage

Current

V

V

I

V

I

V

I

V

I

I

I

I

R

R

D

D

Q

Q

– 42 42

65

– 0.3 7 V

– 0.3 7 V

– 1.0 16 V

V

V

t ≤ 400 ms

internally limited

Internally limited

Internally limited

Internally limited

Ground

Current

I

GND

– 0.5 – A –

Temperat ures

Junction temperature

Storage temperature

T

j

T

stg

– 50

150

150

°C

°C

–

Optimum reliability and life time are guaranteed if the junction temperature does not

exceed 125 °C in operating mode. Operation at up to the maximum junction temperature

of 150 °C is possible in principle. Note, however, that operation at the maximum

permitted ratings could affect the reliability of the device.

Semiconductor Group 5 1998-11-01

Page 6

Operating Range

Parameter Symbol Limit Values Unit Notes

min. max.

TLE 4270

Input voltage

Junction temperature

V

T

I

j

642V–

– 40 150 °C–

Thermal Resistance

Junction ambient

R

thja

–6570K/W

K/W TO263, TO252

Junction case R

Z

thjc

thjc

–32K/W

K/W

t < 1ms

(TO-220/263

Packages)

1)

Soldered in, min. footprint

Characteristics

V

= 13.5 V; – 40 °C ≤ Tj= ≤ 125 °C (unless otherwise specified)

I

Parameter Symbol Limit Values Unit Test Condition

min. typ. max.

Output voltage

V

Q

4.90 5.00 5.10 V 5 mA≤ IQ≤ 550 mA;

V

6 V ≤

≤ 26 V

I

1)

Output voltage

Output current

V

I

Qmax

Q

4.90 5.00 5.10 V 26 V ≤ VI≤ 36 V;

I

≤ 300 mA

Q

650 850 – mA VQ = 0 V

limiting

Current

I

q

–11.5mAIQ = 5 mA

consumption

I

= II − I

q

Current

Q

I

q

–5575mAIQ = 550 mA

consumption

I

= II– I

q

Current

Q

I

q

–7090mAIQ = 550 mA; VI = 5 V

consumption

I

= II– I

q

Drop voltage

Semiconductor Group 6 1998-11-01

Q

V

dr

– 350 700 mV IQ = 550 mA

1)

Page 7

TLE 4270

Characteristics (cont’d)

V

= 13.5 V; – 40 °C ≤ Tj= ≤ 125 °C (unless otherwise specified)

I

Parameter Symbol Limit Values Unit Test Condition

min. typ. max.

Load regulation ∆V

Supply voltage

∆V

regulation

Power supply

PSRR –54–dBf

Ripple rejection

Reset Generator

Switching threshold

Reset High voltage

Reset low voltage

Reset low voltage

Reset pull-up

Lower reset timing

V

V

V

V

R

V

RT

ROH

ROL

ROL

DRL

threshold

Q

Q

–2550mVIQ = 5 to 550 mA;

V

= 6 V

I

–1225mVVI = 6 to 26 V

I

= 5 mA

Q

=100Hz;

r

V

=0.5V

r

SS

4.5 4.65 4.8 V –

4.5 – – V –

–60–mVR

1.0 V ≤

=30 kΩ2);

intern

V

Q

≤ 4.5 V

– 200 400 mV IR = 3 mA, VQ = 4.4 V

18 30 46 kΩ internally connected

to Q

0.2 0.45 0.8 V VQ< V

RT

Charge current I

Upper timing

V

d

DU

81425µA VD = 1.0 V

1.4 1.8 2.3 V –

threshold

Delay time

Reset reaction time

t

d

t

RR

–13–msCD = 100 nF

––3µs CD = 100 nF

Overvoltage Protection

Turn-Off voltage

1)

Drop voltage = VI– VQ (measured when the output voltage has dropped 100 mV from the nominal value

obtained at 13.5 V input)

2)

Reset peak is always lower tha n 1. 0 V.

Semiconductor Group 7 1998-11-01

V

I, ov

42 44 46 V –

Page 8

TLE 4270

Figure 3

Test Circuit

V

Ι

Ι

Ι

µ

1000 F

Ι

15

470 nF

Q

µ

22 F

TLE 4270G

Ι

R

2

V

4

Ι

D

V

D

C

D

3

Ι

V

GND

Q

R

AES01925

Input

Reset

470 nF

1

TLE 4270

2

5

5 V-Output

22 F

µ

4

to MC

3

100 nF

AES01926

Figure 4

Application Circuit

Semiconductor Group 8 1998-11-01

Page 9

TLE 4270

V

Ι

t

<

RR

V

Q

V

RT

d

Ι

V

d

=

d

C

V

V

DU

D

V

DRL

tt

d

V

R

RR

t

d

Power-on-Reset

Figure 5

Time Response

Thermal

Voltage Drop Undervoltage

Shutdown at Input

Secondary Load

Spike

Bounce

AES01927

Semiconductor Group 9 1998-11-01

Page 10

TLE 4270

Output Voltage VQ versus

Temperature

5.20

V

V

Q

5.10

5.00

4.90

4.80

4.70

4.60

T

= 13.5 V

V

Ι

j

40-40 0

80 120

AED01928

160

C

T

j

Output Voltage VQ versus

Input Voltage

12

V

V

Q

10

8

6

4

2

0

0

V

I

R

= 25

Ω

L

2

4

68

AED01929

10

V

V

Ι

Output Current IQ versus

Temperature

1200

mA

Ι

Q

1000

800

600

400

200

0

T

j

40-40 0

AED01930

80 120

T

C

160

Output Current IQ versus

Input Voltage

1.2

A

Ι

Q

1.0

0.8

0.6

0.4

0.2

0

V

T

= 125 C

j

20010

I

T

30

AED01931

= 25 C

j

40

V

Ι

50

V

Semiconductor Group 10 1998-11-01

Page 11

TLE 4270

Current Consumption I

versus Output Current I

6

mA

Ι

q

5

4

3

V

= 13.5 V

Ι

2

1

0020 1206040

q

Q

AED01932

Current Consumption I

versus Output Current I

q

Q

AED01933

80

mA

Ι

q

70

60

50

V

= 13.5 V

Ι

40

30

20

10

0

80

mA

Ι

Q

1000 200

400 600

300

mA

Ι

Q

Current Consumption I

versus Input Voltage V

120

mA

Ι

q

100

80

60

R

40

= 20

R

20

0

Ω

L

20010

q

I

= 10

L

30

R

L

AED01934

Ω

= 50

40

V

Ω

Ι

Drop Voltage Vdr versus

Output Current

800

mV

V

Dr

700

600

500

T

= 125 C

j

400

300

200

100

0

50

V

2000 400

I

Q

AED01935

T

=25

C

j

600 1000

mA

Ι

Q

Semiconductor Group 11 1998-11-01

Page 12

TLE 4270

V

j

Charge Current Id

versus Temperature

8

A

µ

Ι

d

7

Ι

d

6

5

4

3

2

1

0

0-40 40

T

j

V

V

AED01936

= 13.5 V

Ι

= 1 V

D

12080 160

C

T

j

Delay Switching threshold V

versus Temperature T

4.0

V

dT

3.5

3.0

2.5

2.0

1.5

1.0

0.5

0

0-40 40

V

= 13.5 V

Ι

V

j

DU

12080 160

DU

AED01937

C

T

Semiconductor Group 12 1998-11-01

Page 13

Package Outlines

P-TO220-5-1

(Plastic Transistor Single Outline)

+0.4

10

10.2

-0.2

+0.1

3.75

TLE 4270

2.8

4.6

+0.1

1.27

±0.4

19.5 max

16

-0.2

1x45˚

-0.2

8.8

±0.3

15.4

±0.3

2.6

15

±0.4

0.4

+0.1

1.7

+0.1

1)

0.8

0.6

M

5x

1) 1 at dam bar (max 1.8 from body)

-0.15

1) 1 im Dichtstegbereich (max 1.8 vom Körper)

-0.15

4.5

±0.4

8.4

8.6

±0.3

10.2

GPT05107

Sorts of Packing

Package outlines for tubes, trays etc. are contained in our

Data Book “Package Information”.

Dimensions in mm

Semiconductor Group 13 1998-11-01

Page 14

P-TO220-5-2

(Plastic Transistor Single Outline)

+0.4

10

10.2

-0.2

+0.1

3.75

15

2.8

±0.2

10.9

±0.2

12.9

1.27

+0.1

4.6

-0.2

1x45˚

-0.2

8.8

TLE 4270

±0.3

15.4

1.7

0.8

+0.1

1)

M

0.6

0.4

2.6

+0.1

±0.15

5x

1) 1 at dam bar (max 1.8 from body)

-0.15

1) 1 im Dichtstegbereich (max 1.8 vom Körper)

-0.15

GPT05256

Sorts of Packing

Package outlines for tubes, trays etc. are contained in our

Data Book “Package Information”.

Dimensions in mm

Semiconductor Group 14 1998-11-01

Page 15

P-TO220-5-11

(Plastic Transistor Single Outline)

±0.2

10

±0.15

9.8

1)

8.5

3.7

-0.15

1)

±0.3

±0.3

17

13.4

15.65

C

0...0.15

1.7

0.8

±0.2

2.8

±0.3

8.6

±0.1

A

±0.3

10.2

TLE 4270

4.4

±0.1

1.27

0.05

±0.3

3.7

2.4

M

A0.25

C

8.4

±0.4

±0.2

9.25

0.5

3.9

±0.1

±0.4

1)

Typical

All metal surfaces tin plated, except area of cut.

GPT09064

Sorts of Packing

Package outlines for tubes, trays etc. are contained in our

Data Book “Package Information”.

Dimensions in mm

Semiconductor Group 15 1998-11-01

Page 16

P-TO220-5-12

(Plastic Transistor Single Outline)

±0.2

10

±0.15

9.8

1)

8.5

3.7

-0.15

1)

±0.3

±0.3

17

13.4

15.65

C

A

±0.2

2.8

±0.5

11

±0.5

13

1.27

0.05

TLE 4270

B

4.4

±0.1

±0.2

9.25

0...0.15

1.7

6x

0.8

±0.1

2.4

M

BA0.25

C

Typical

1)

All metal surfaces tin plated, except area of cut.

±0.1

0.5

GPT09065

Sorts of Packing

Package outlines for tubes, trays etc. are contained in our

Data Book “Package Information”.

Dimensions in mm

Semiconductor Group 16 1998-11-01

Page 17

P-TO263-5-1

(Plastic Transistor Single Outline)

±0.2

10

±0.15

9.8

8.5

±0.3

1

±0.2

9.25

(15)

±0.1

5x0.8

1)

A

1)

8

0...0.15

4x1.7

TLE 4270

4.4

±0.1

1.27

B

0.1

2.4

±0.3

±0.5

2.7

4.7

0.5

8˚ max.

M

BA0.25

0.05

±0.1

0.1

1)

Typical

All metal surfaces tin plated, except area of cut.

GPT09113

Sorts of Packing

Package outlines for tubes, trays etc. are contained in our

Data Book “Package Information”.

SMD = Surface Mounted Device

Dimensions in mm

Semiconductor Group 17 1998-11-01

Page 18

P-TO220-5-8

(Plastic Transistor Single Outline)

10.2

8.0

10.1

1.7

0.8

TLE 4270

4.6

1.27

0.2

2.6

1)

8.8

3.5

1.5

0.4

4 x 1.7 = 6.8

1) shear and punch direction burr free surface

GPT05873

Sorts of Packing

Package outlines for tubes, trays etc. are contained in our

Data Book “Package Information”.

SMD = Surface Mounted Device

Dimensions in mm

Semiconductor Group 18 1998-11-01

Page 19

P-TO252-5-1

(Plastic Transistor Single Outline)

TLE 4270

+0.15

6.5

-0.10

B

±0.1

1

0...0.15

0.51 min

-0.2

±0.5

6.22

9.9

0.15 max

per side

±0.1

1

(4.17)

5.4

±0.1

±0.15

0.8

5x0.6

A

±0.1

1.14

4.56

M

B

A0.25

All metal surfaces tin plated, except area of cut.

2.3

+0.05

-0.10

0.9

0.5

GPT09161

+0.08

-0.04

+0.08

-0.04

0.1

Sorts of Packing

Package outlines for tubes, trays etc. are contained in our

Data Book “Package Information”.

SMD = Surface Mounted Device

Dimensions in mm

Semiconductor Group 19 1998-11-01

Loading...

Loading...