Siemens HYB3116405BJ-50, HYB3116405BT-50, HYB3116405BT-60, HYB3116405BTL-50, HYB3116405BTL-60 Datasheet

...

4M × 4-Bit Dynamic RAM

2k & 4k Refresh

(Hyper Page Mode - EDO)

Advanced Information

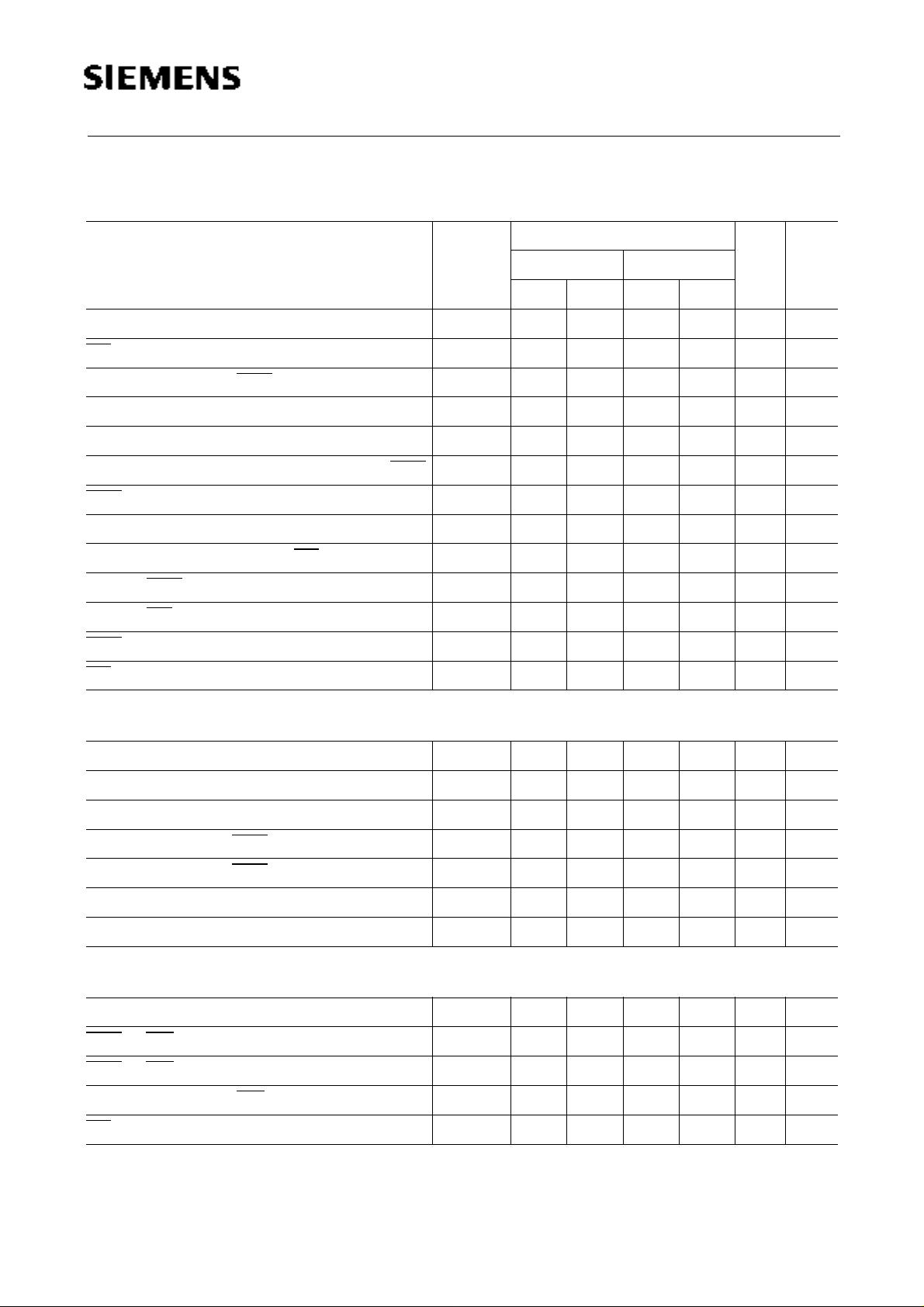

• 4 194 304 words by 4-bit organization

• 0 to 70 °C operating temperature

• Hyper Page Mode - EDO - operation

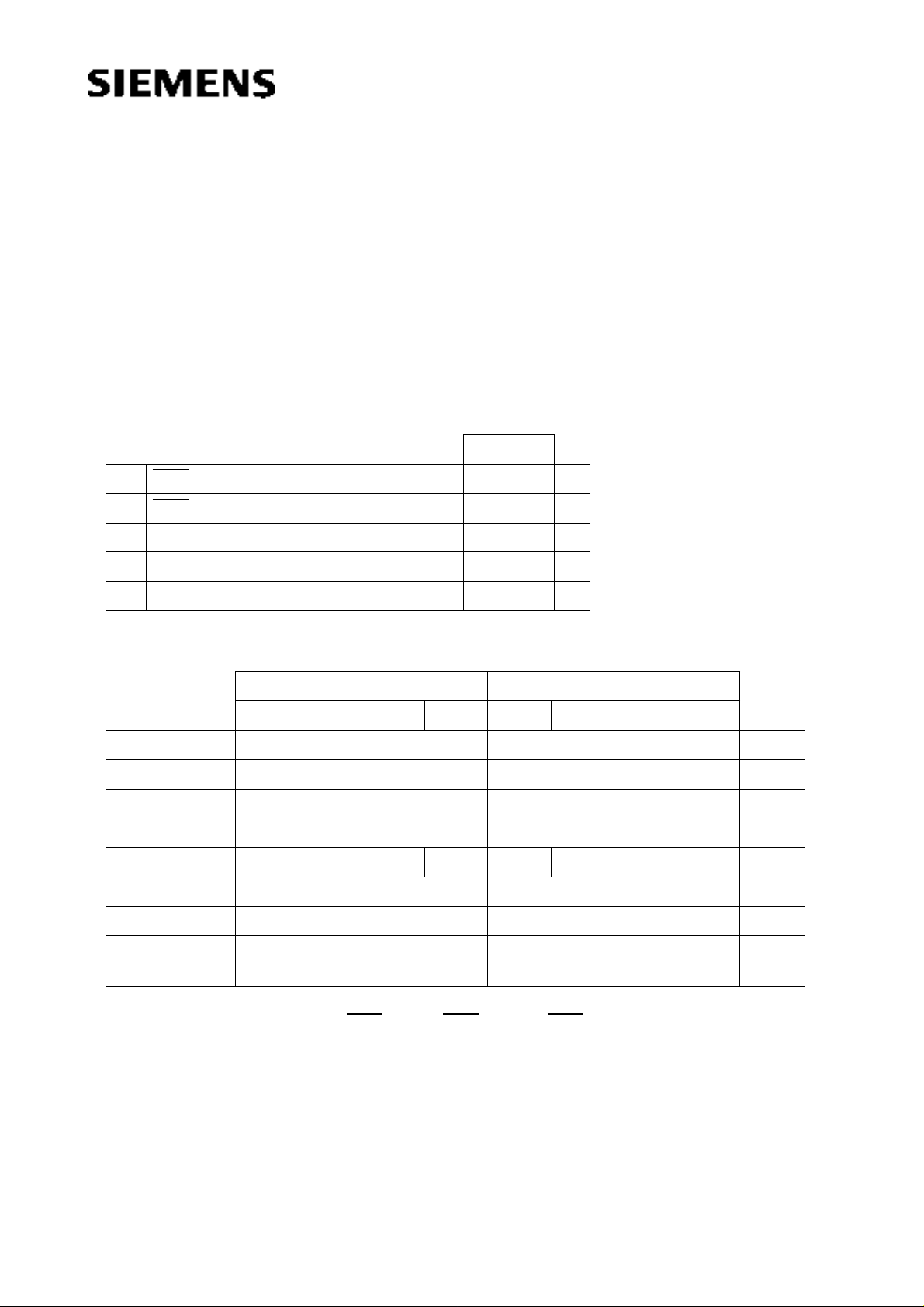

• Performance:

HYB 5116405BJ-50/-60

HYB 5117405BJ-50/-60

HYB 3116405BJ/BT(L)-50/-60

HYB 3117405BJ/BT-50/-60

-50 -60

t

t

t

t

t

• Power dissipation, refresh & addressing:

Power supply 5 V ± 10% 3.3 V ± 0.3 V 5 V ± 10% 3.3 V ± 0.3 V

Addressing 12/10 12/10 11/11 11/11

Refresh 4096 cylces / 64 ms 2048 cycles / 32 ms

L-version 4096 cycles / 128 ms –

Active 275 220 180 144 440 385 288 252 mW

TTL Standby 11 7.2 11 7.2 mW

CMOS Standby 5.5 3.6 5.5 3.6 mW

RAS access time 50 60 ns

RAC

CAS access time 13 15 ns

CAC

Access time from address 25 30 ns

AA

Read/Write cycle time 84 104 ns

RC

Hyper page mode (EDO) cycle time 20 25 ns

HPC

HYB 5116405 HYB 3116405 HYB 5117405 HYB 3117405

-50 -60 -50 -60 -50 -60 -50 -60

CMOS Standby

(L-version)

• Read, write, read-modify-write, CAS-before-RAS refresh, RAS-only refresh, hidden refresh,

test mode and Self Refresh (on L-versions only)

• All inputs, outputs and clocks fully TTL (5 V versions) and LV-TTL (3.3 V version)-compatible

• Plastic Package: P-SOJ-26/24-1 300 mil

Semiconductor Group 1 1998-10-01

– 0.72 – – mW

P-TSOPII-26/24-1 300 mil

HYB 5116(7)405BJ-50/-60

HYB 3116(7)405BJ/BT(L)-50/-60

4M × 4 EDO-DRAM

The HYB 5(3)116(7)405 are 16 MBit dynamic RAMs based on die revisions “G” & “F” and organized

as 4 194 304 words by 4-bits. The HYB 5(3)116(7)405BJ/BT(L) utilizes a submicron CMOS silicon

gate process technology, as well as advanced circuit techniques to provide wide operating margins,

both internally and for the system user. Multiplexed address inputs permit the HYB 5(3)116(7)405

to be packaged in a standard SOJ-26/24 and TSOPII-26/24 plastic package with 300 mil width.

These packages provide high system bit densities and are compatible with commonly used

automatic testing and insertion equipment. The HYB 3116(7)405BTL have a very low power “sleep

mode” supported by Self Refresh.

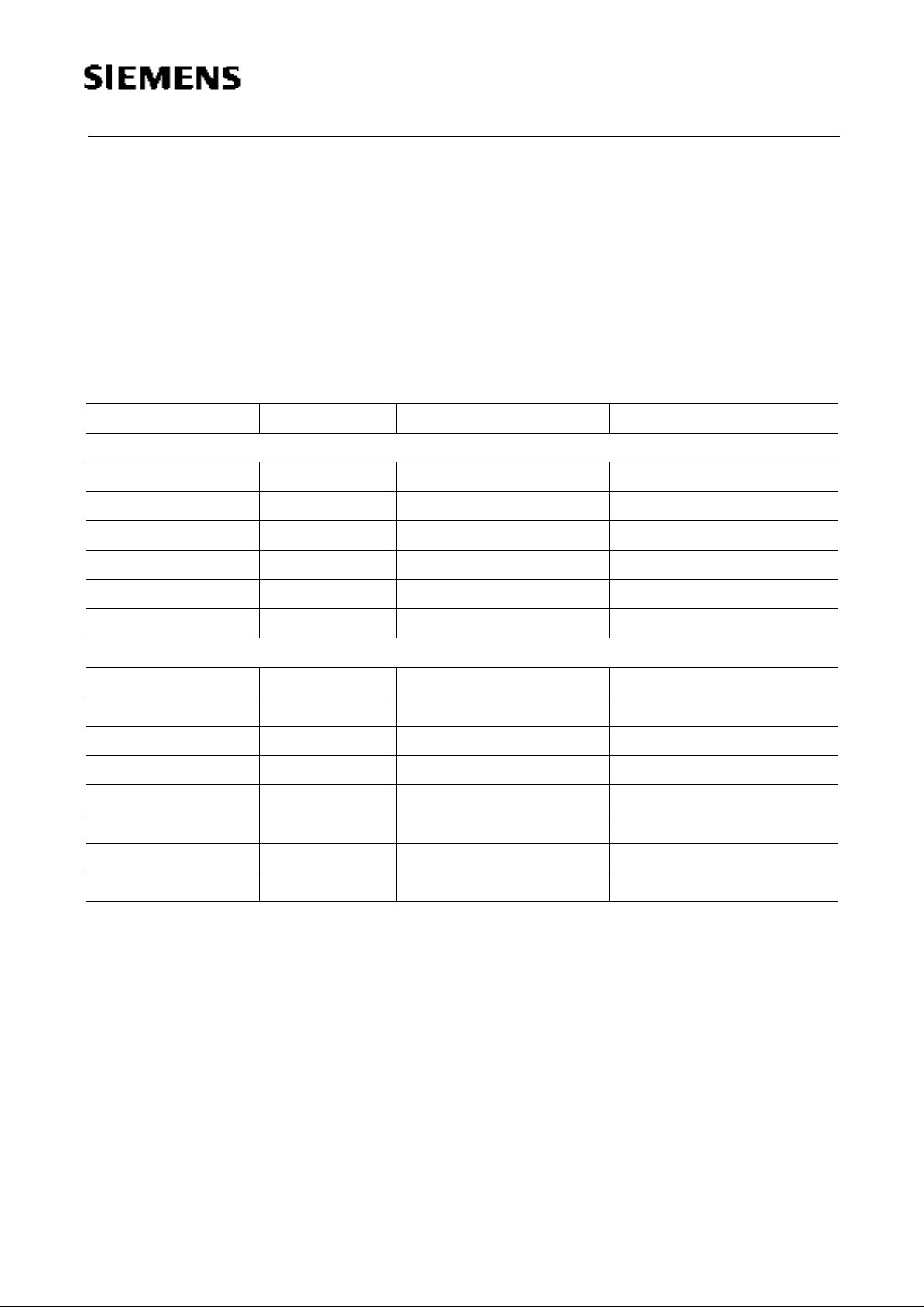

Ordering Information

Type Ordering Code Package Descriptions

2k-Refresh Versions:

HYB 5117405BJ-50 Q67100-Q1101 P-SOJ-26/24-1 300 mil 5 V 50 ns EDO-DRAM

HYB 5117405BJ-60 Q67100-Q1102 P-SOJ-26/24-1 300 mil 5 V 60 ns EDO-DRAM

HYB 3117405BJ-50 on request P-SOJ-26/24-1 300 mil 3.3 V 50 ns EDO-DRAM

HYB 3117405BJ-60 on request P-SOJ-26/24-1 300 mil 3.3 V 60 ns EDO-DRAM

HYB 3117405BT-50 on request P-TSOPII-26/24-1 300 mil 3.3 V 50 ns EDO-DRAM

HYB 3117405BT-60 on request P-TSOPII-26/24-1 300 mil 3.3 V 60 ns EDO-DRAM

4k-Refresh Versions:

HYB 5116405BJ-50 Q67100-Q1098 P-SOJ-26/24-1 300 mil 5 V 50 ns EDO-DRAM

HYB 5116405BJ-60 Q67100-Q1099 P-SOJ-26/24-1 300 mil 5 V 60 ns EDO-DRAM

HYB 3116405BJ-50 on request P-SOJ-26/24-1 300 mil 3.3 V 50 ns EDO-DRAM

HYB 3116405BJ-60 on request P-SOJ-26/24-1 300 mil 3.3 V 60 ns EDO-DRAM

HYB 3116405BT-50 on request P-TSOPII-26/24-1 300 mil 3.3 V 50 ns EDO-DRAM

HYB 3116405BT-60 on request P-TSOPII-26/24-1 300 mil 3.3 V 60 ns EDO-DRAM

HYB 3116405BTL-50 on request P-TSOPII-26/24-1 300 mil 3.3 V 50 ns LP-EDO-DRAM

HYB 3116405BTL-60 on request P-TSOPII-26/24-1 300 mil 3.3 V 60 ns LP-EDO-DRAM

Semiconductor Group 2 1998-10-01

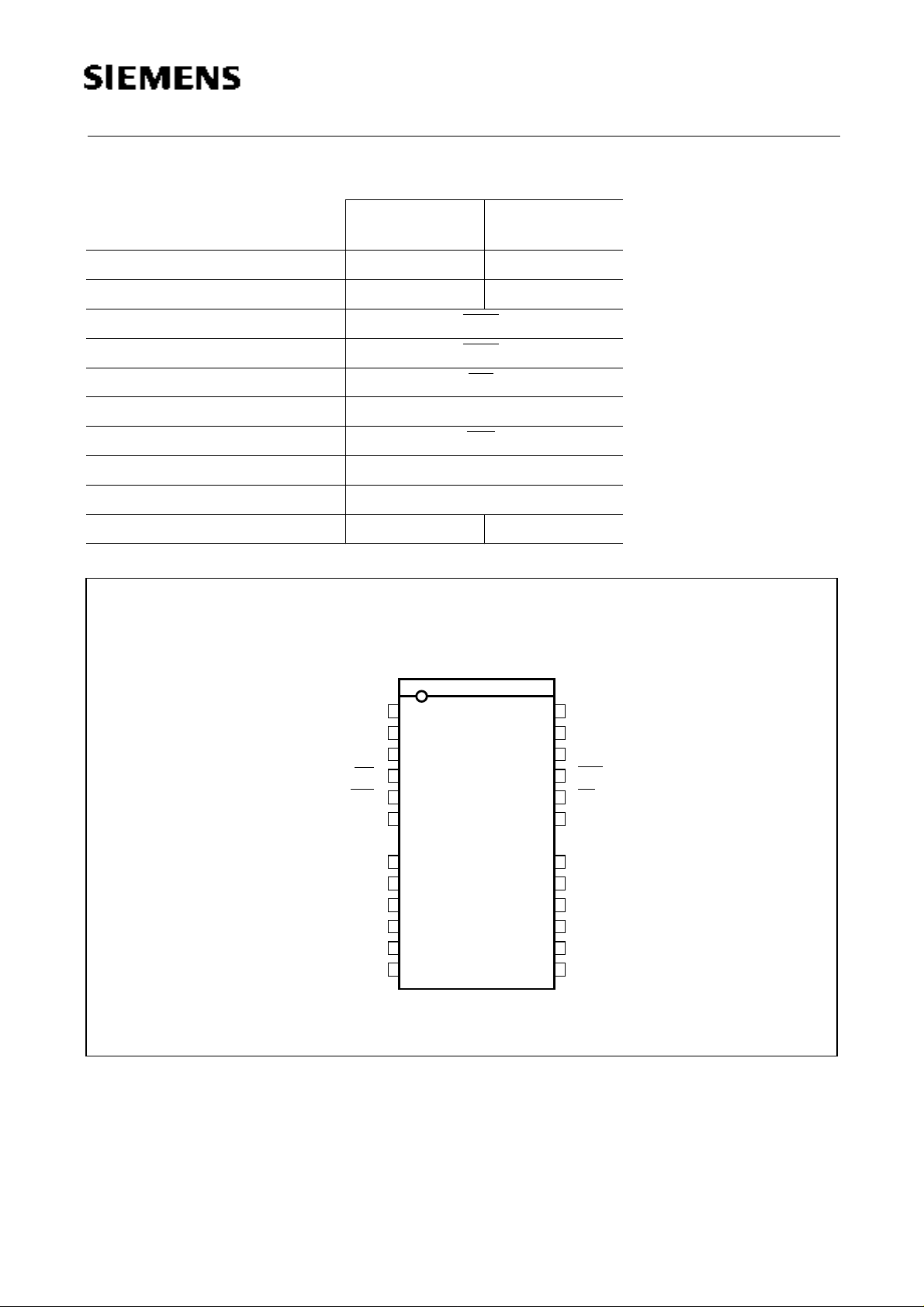

Pin Names

HYB 5116(7)405BJ-50/-60

HYB 3116(7)405BJ/BT(L)-50/-60

4M × 4 EDO-DRAM

HYB 5(3)16405

4k-Refresh

HYB 5(3)17405

2k-Refresh

Row Address Inputs A0 - A11 A0 - A10

Column Address Inputs A0 - A9 A0 - A10

Row Address Strobe RAS

Column Address Strobe CAS

Output Enable OE

Data Input/Output I/O1 - I/O4

Read/Write Input WE

Power Supply V

Ground (0 V) V

CC

SS

Not Connected – N.C.

P-SOJ-26/24-1 300 mil

P-TSOPII-26/24-1 300 mil

Pin Configuration

(top view)

V

CC

I/O1

I/O2

WE

RAS

A11 / N.C.

A10

A0 9

A1

A2

A3

V

CC

1

2

3

4

5

6

819

10

11

12

13 14

SPP03454

26

25

24

23

22

21

18

17

16

15

V

SS

I/O4

I/O3

CAS

OE

A9

A8

A7

A6

A5

A4

V

SS

Semiconductor Group 3 1998-10-01

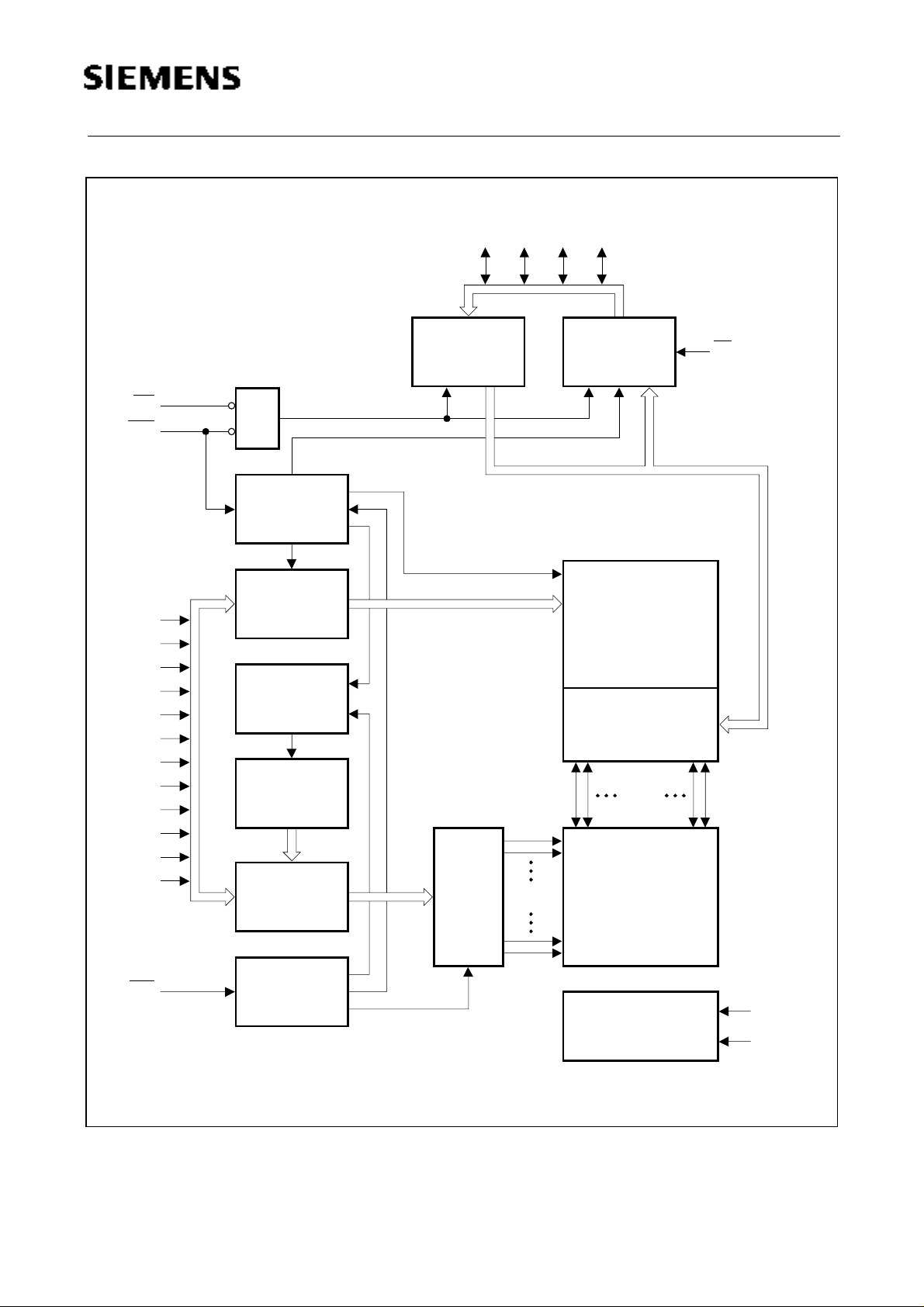

HYB 5116(7)405BJ-50/-60

HYB 3116(7)405BJ/BT(L)-50/-60

4M × 4 EDO-DRAM

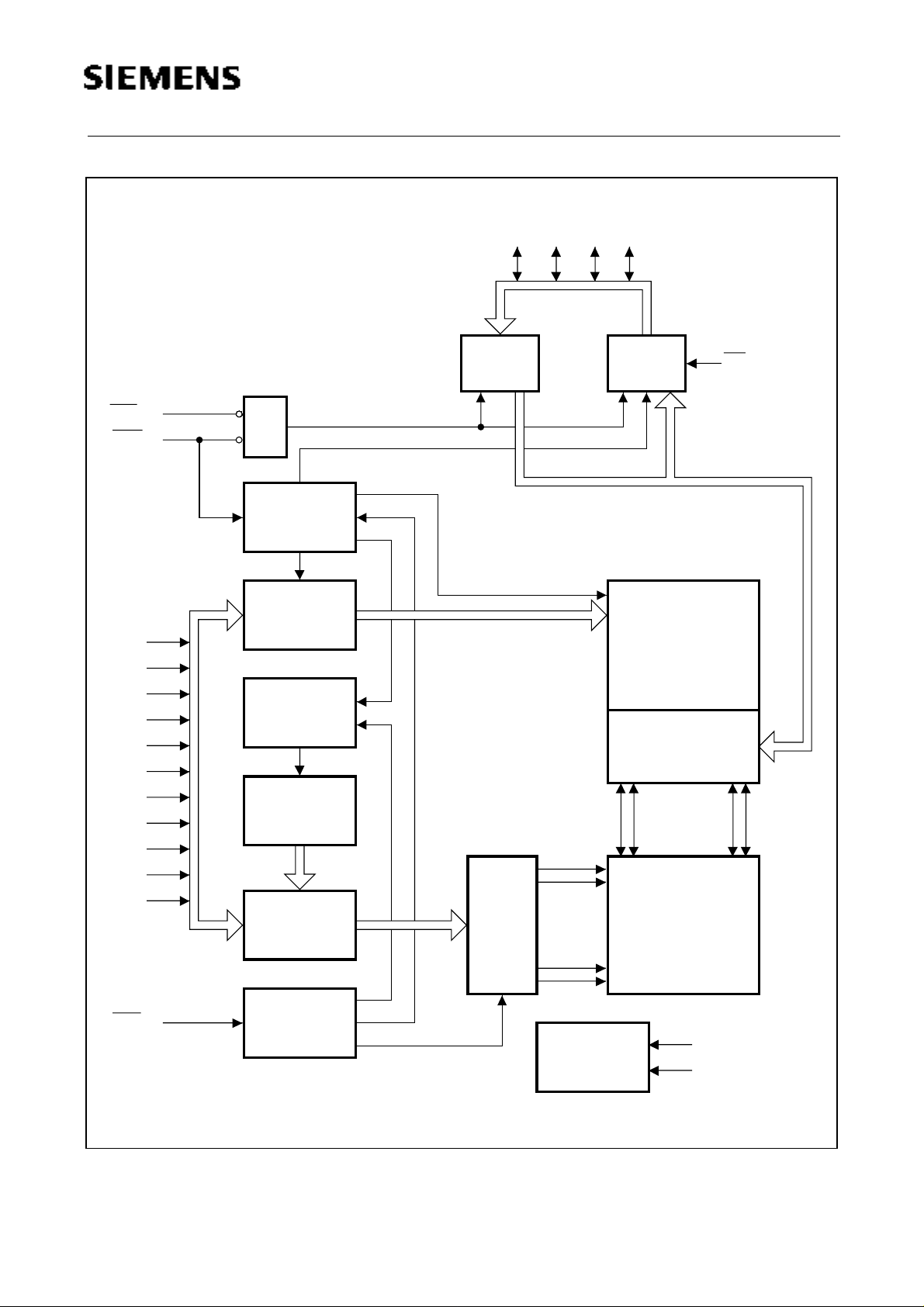

I/O2

I/O1

I/O3 I/O4

WE

CAS

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

10

12

&

No.2 Clock

Generator

Column

Address

Buffers (10)

Refresh

Controller

Refresh

Counter (12)

12

Row

Address

Buffers (12)

12

Data IN

Buffer

10

Row

Decoder

4

4096

Data OUT

Buffer

4

Column

Decoder

Sense Amplifier

I/O Gating

1024

x 4

Memory Array

4096 x 1024 x 4

OE

4

RAS

No.1 Clock

Generator

Voltage Down

Generator

SPB03455

V

CC

V

CC

(internal)

Block Diagram for HYB 5(3)116405 (4k-refresh)

Semiconductor Group 4 1998-10-01

HYB 5116(7)405BJ-50/-60

HYB 3116(7)405BJ/BT(L)-50/-60

4M × 4 EDO-DRAM

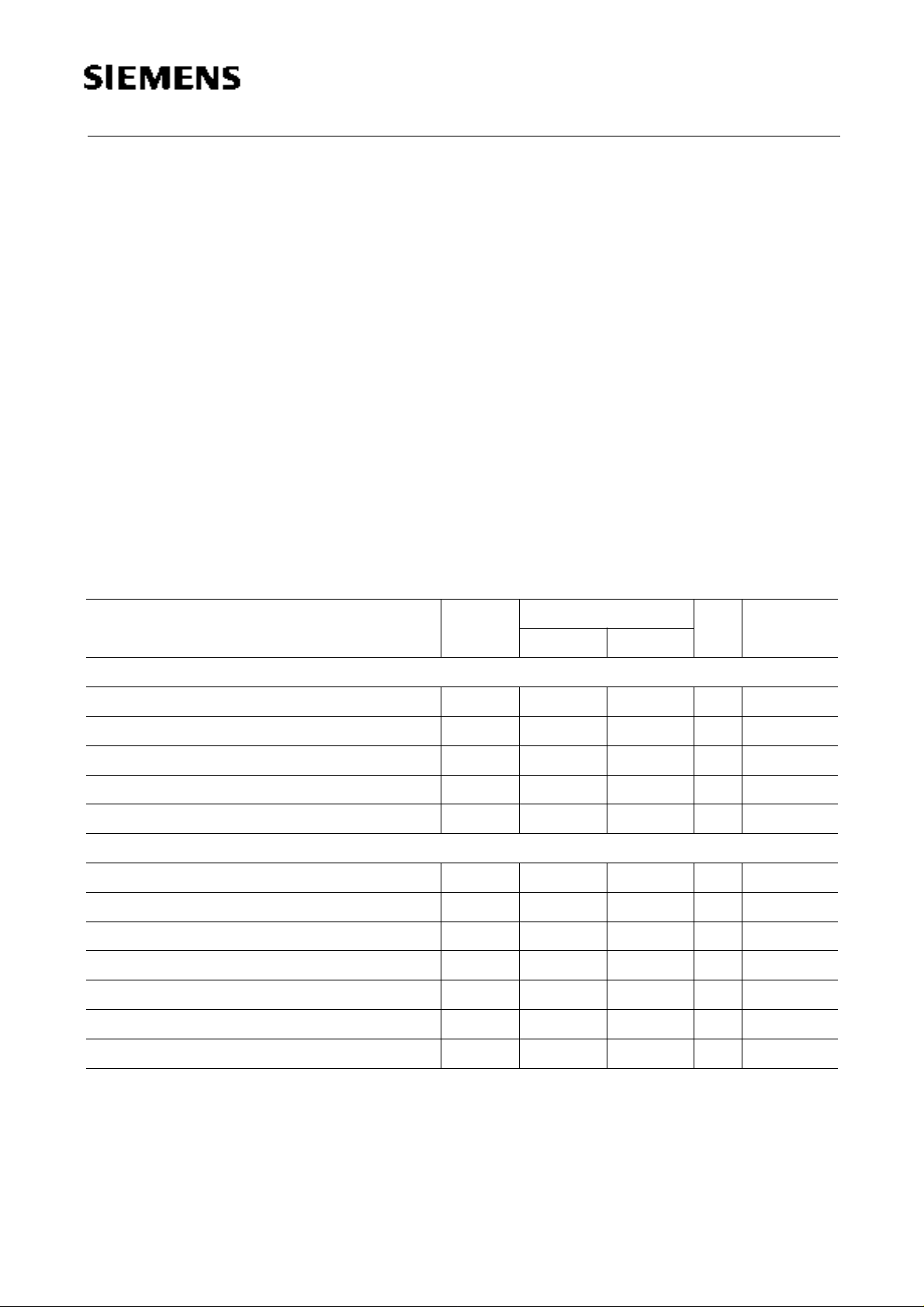

WE

CAS

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

11

11

&

No.2 Clock

Generator

Column

Address

Buffers (11)

Refresh

Controller

Refresh

Counter (11)

11

Row

Address

Buffers (11)

11

I/O1 I/O2 I/O4

Data In

Buffer

4

11

.

.

Row

Decoder

.

2048

.

.

.

I/O3

Data Out

Buffer

4

Column

Decoder

Sense Amplifier

I/O Gating

2048

...

x4

Memory Array

2048 2048x

...

x

OE

4

4

RAS

No.1 Clock

Generator

Voltage Down

Generator

V

CC

V

CC

(internal)

SPB02823

Block Diagram for HYB 5(3)117405 (2k-refresh)

Semiconductor Group 5 1998-10-01

HYB 5116(7)405BJ-50/-60

HYB 3116(7)405BJ/BT(L)-50/-60

4M × 4 EDO-DRAM

Absolute Maximum Ratings

Operating temperature range ........................................................................................... 0 to 70 ˚C

Storage temperature range........................................................................................ – 55 to 150 ˚C

Input/output voltage (5 V versions)................................................... – 0.5 to min (VCC+ 0.5, 7.0) V

Input/output voltage (3.3 V versions)................................................ – 0.5 to min (VCC+ 0.5, 4.6) V

Power supply voltage (5 V versions) ....................................................................... – 1.0 V to 7.0 V

Power supply voltage (3.3 V versions) .................................................................... – 1.0 V to 4.6 V

Power dissipation (5 V versions) ............................................................................................ 1.0 W

Power dissipation (3.3 V versions) ......................................................................................... 0.5 W

Data out current (short circuit) ............................................................................................... 50 mA

Note: Stresses above those listed under “Absolute Maximum Ratings” may cause permanent

damage of the device. Exposure to absolute maximum rating conditions for extended periods

may affect device reliability.

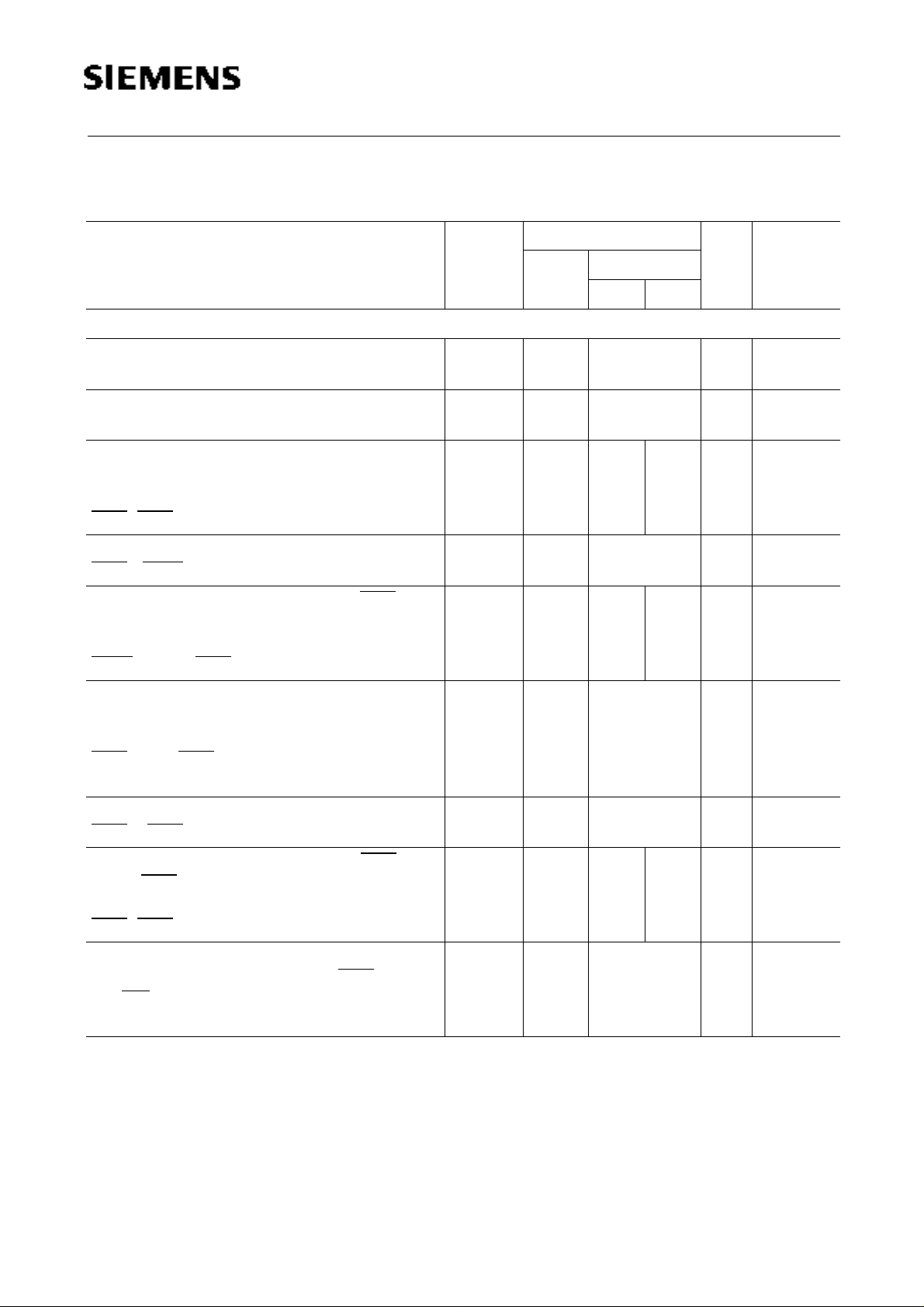

DC Characteristics

T

= 0 to 70 °C, VSS = 0 V, tT = 2 ns

A

Parameter Symbol Limit Values Unit Test

min. max.

Condition

5 V Versions

Power supply voltage V

Input high voltage V

Input low voltage V

Output high voltage (I

Output low voltage (I

= – 5 mA) V

OUT

= 4.2 mA) V

OUT

CC

IH

IL

OH

OL

4.5 5.5 V

2.4 VCC+ 0.5 V

– 0.5 0.8 V

2.4 – V

– 0.4 V

1

1

1

1

3.3 V Versions

Power supply voltage V

Input high voltage V

Input low voltage V

TTL Output high voltage (I

TTL Output low voltage (I

CMOS Output high voltage (I

CMOS Output low voltage (I

= – 2 mA) V

OUT

= 2 mA) V

OUT

= – 100 µA) V

OUT

= 100 µA) V

OUT

CC

IH

IL

OH

OL

OH

OL

3.0 3.6 V

2.0 VCC+ 0.5 V

– 0.5 0.8 V

2.4 – V

– 0.4 V

V

– 0.2 – V

CC

– 0.2 V

1

1

1

1

Semiconductor Group 6 1998-10-01

HYB 5116(7)405BJ-50/-60

HYB 3116(7)405BJ/BT(L)-50/-60

4M × 4 EDO-DRAM

DC Characteristics (cont’d)

T

= 0 to 70 °C, VSS = 0 V, tT = 2 ns

A

Parameter Symbol Limit Values Unit Notes

min. max.

2k 4k

Common Parameters

Input leakage current

(0 V ≤ VIH≤ VCC + 0.3 V, all other pins = 0 V)

Output leakage current

(DO is disabled, 0 V ≤ V

≤ VCC + 0.3 V)

OUT

Average VCC supply current

-50 version

-60 version

(RAS, CAS, address cycling: tRC = t

RC MIN.

)

Standby VCC supply current

(RAS = CAS = VIH)

I

I

I

I

I(L)

O(L)

CC1

CC2

– 10 10 µA

– 10 10 µA

–

–

80

70

50

40

mA

mA

– 2 mA –

1

1

2, 3, 4

2, 3, 4

Average VCC supply current, during RAS-only

refresh cycles -50 version

-60 version

(RAS cycling, CAS = VIH, tRC = t

RC MIN.

)

AverageVCC supply current,during hyper page

mode (EDO) -50 version

-60 version

(RAS = VIL, CAS, address cycling:

t

PC

= t

PC MIN.

)

Standby VCC supply current

(RAS = CAS = VCC – 0.2 V)

Average VCC supply current, during CASbefore-RAS refresh mode -50 version

-60 version

(RAS, CAS cycling: tRC = t

RC MIN.

)

Average Self Refresh current

(CBR cycle with t

RAS

> t

RASS MIN.

, CAS held

low, WE = VCC– 0.2 V, Address and

Din = VCC– 0.2 V or 0.2 V)

I

I

I

I

I

CC3

CC4

CC5

CC6

CC7

–

–

–

–

–1

–

–

80

70

80

70

35

30

200

50

40

50

40

mA

mA

mA

mA

mA

µA1L-version

mA

mA

2, 4

2, 4

2, 3, 4

2, 3, 4

2, 4

2, 4

– 250 µAL-

version

only

Semiconductor Group 7 1998-10-01

HYB 5116(7)405BJ-50/-60

HYB 3116(7)405BJ/BT(L)-50/-60

4M × 4 EDO-DRAM

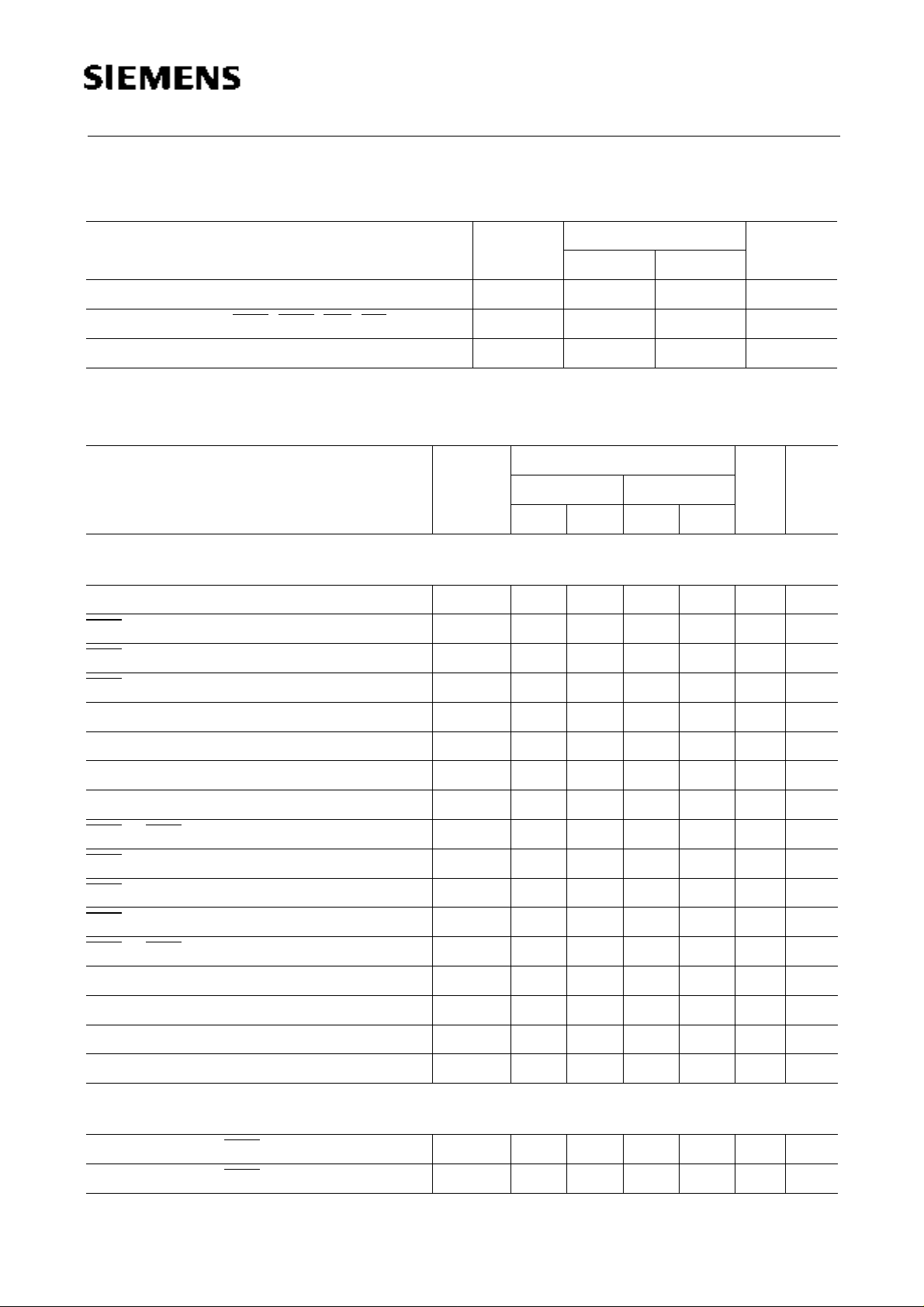

Capacitance

T

= 0 to 70 °C, f = 1 MHz

A

Parameter Symbol Limit Values Unit

min. max.

Input capacitance (A0 to A11) C

Input capacitance (RAS, CAS, WE, OE) C

I/O capacitance (I/O1 to I/O4) C

AC Characteristics

T

= 0 to 70 °C, VCC = 5 V ± 10 % / VCC = 3.3 V ± 0.3 V, tT = 2 ns

A

5, 6

I1

I2

IO

–5pF

–7pF

–7pF

Parameter Symbol Limit Values Unit Note

-50 -60

min. max. min. max.

Common Parameters

Random read or write cycle time t

RAS precharge time t

RAS pulse width t

CAS pulse width t

Row address setup time t

Row address hold time t

Column address setup time t

Column address hold time t

RAS to CAS delay time t

RAS to column address delay t

RAS hold time t

CAS hold time t

CAS to RAS precharge time t

Transition time (rise and fall) t

Refresh period for 2k-refresh version t

Refresh period for 4k-refresh version t

Refresh period for Low Power Version t

RC

RP

RAS

CAS

ASR

RAH

ASC

CAH

RCD

RAD

RSH

CSH

CRP

T

REF

REF

REF

84 – 104 – ns

30 – 40 – ns

50 10k 60 10k ns

8 10k 10 10k ns

0–0–ns

8–10–ns

0–0–ns

8–10–ns

12 37 14 45 ns

10 25 12 30 ns

13 – 15 – ns

40 – 50 – ns

5–5–ns

1 50 1 50 ns

7

– 32 – 32 ms

– 64 – 64 ms

– 128 – 128 ms

Read Cycle

Access time from RAS t

Access time from CAS t

RAC

CAC

– 50 – 60 ns

– 13 – 15 ns

8, 9

8, 9

Semiconductor Group 8 1998-10-01

HYB 5116(7)405BJ-50/-60

HYB 3116(7)405BJ/BT(L)-50/-60

4M × 4 EDO-DRAM

AC Characteristics (cont’d)

T

= 0 to 70 °C, VCC = 5 V ± 10 % / VCC = 3.3 V ± 0.3 V, tT = 2 ns

A

5, 6

Parameter Symbol Limit Values Unit Note

-50 -60

min. max. min. max.

Access time from column address t

OE access time t

Column address to RAS lead time t

Read command setup time t

Read command hold time t

Read command hold time referenced to RAS t

CAS to output in low-Z t

Output buffer turn-off delay t

Output turn-off delay from OE t

Data to CAS low delay t

Data to OE low delay t

CAS high to data delay t

OE high to data delay t

AA

OEA

RAL

RCS

RCH

RRH

CLZ

OFF

OEZ

DZC

DZO

CDD

ODD

– 25 – 30 ns

– 13 – 15 ns

25 – 30 – ns

0–0–ns

0–0–ns

0–0–ns

0–0–ns

0 13 0 15 ns

0 13 0 15 ns

0–0–ns

0–0–ns

10 – 13 – ns

10 – 13 – ns

8, 10

11

11

8

12

12

13

13

14

14

Write Cycle

Write command hold time t

Write command pulse width t

Write command setup time t

Write command to RAS lead time t

Write command to CAS lead time t

Data setup time t

Data hold time t

Read-Modify-Write Cycle

Read-write cycle time t

RAS to WE delay time t

CAS to WE delay time t

Column address to WE delay time t

OE command hold time t

WCH

WP

WCS

RWL

CWL

DS

DH

RWC

RWD

CWD

AWD

OEH

8–10–ns

8–10–ns

0–0–ns

15

8–10–ns

8–10–ns

0–0–ns

8–10–ns

16

16

113 – 138 – ns

64 – 77 – ns

27 – 32 – ns

39 – 47 – ns

15

15

15

10 – 13 – ns

Semiconductor Group 9 1998-10-01

Loading...

Loading...