Page 1

INTEGRATED CIRCUITS

DATA SH EET

TEA1533P; TEA1533AP

GreenChip

Product specification

Supersedes data of 2002 May 31

TM

II SMPS control IC

2002 Aug 23

Page 2

Philips Semiconductors Product specification

GreenChipTMII SMPS control IC

FEATURES

Distinctive features

• Universal mains supply operation (70 to 276 V AC)

• High level of integration, giving a very low external

component count.

Green features

• Valley or zero voltage switching for minimum switching

losses

• Efficient quasi-resonant operation at high power levels

• Frequency reductionat low power standby for improved

system efficiency (<3 W)

• Cycle skipping mode at very low loads. Pi <300 mW at

no-load operation for a typical adapter application

• On-chip start-up current source.

Protection features

• Safe restart mode for system fault conditions

• Continuous mode protection by means of

demagnetization detection (zero switch-on current)

• Accurateand adjustable overvoltage protection(latched

in TEA1533P, safe restart in TEA1533AP)

• Short winding protection

• Undervoltage protection (foldback during overload)

• Overtemperatureprotection (latched in TEA1533P,safe

restart in TEA1533AP)

• Low and adjustable overcurrent protection trip level

• Soft (re)start

• Mains voltage-dependent operation enabling level.

TEA1533P; TEA1533AP

APPLICATIONS

Besides typical application areas, i.e. adapters and

chargers, the device can be used in TV and monitor

supplies and all applications that demand an efficient and

cost-effective solution up to 250 W.

1

2

TEA1533P

TEA1533AP

3

4

8

7

6

5

MGU505

2002 Aug 23 2

Fig.1 Basic application diagram.

Page 3

Philips Semiconductors Product specification

GreenChipTMII SMPS control IC

GENERAL DESCRIPTION

The GreenChip

Switched Mode Power Supply (SMPS) control ICs

operatingdirectly from the rectified universalmains.A high

level of integration leads to a cost effective power supply

with a very low number of external components.

The special built-in green functions allow the efficiency to

be optimum at all power levels. This holds for

quasi-resonant operation at high power levels, as well as

fixed frequency operation with valley switching at medium

power levels. At low power (standby) levels, the system

operates at a reduced frequency and with valley detection.

(1) GreenChip is a trademark of Koninklijke Philips

Electronics N.V.

ORDERING INFORMATION

TYPE NUMBER

TEA1533P DIP8 plastic dual in-line package; 8 leads (300 mil) SOT97-1

TEA1533AP

(1)

II is the second generation of green

NAME DESCRIPTION VERSION

The proprietary high voltage BCD800 process makes

direct start-up possible from the rectified mains voltage in

an effective and green way. A second low voltage

BICMOS IC is used for accurate, high-speed protection

functions and control.

Highly efficient and reliable supplies can easily be

designed using the GreenChipII control IC.

PACKAGE

TEA1533P; TEA1533AP

2002 Aug 23 3

Page 4

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

b

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

2002 Aug 23 4

ook, full pagewidth

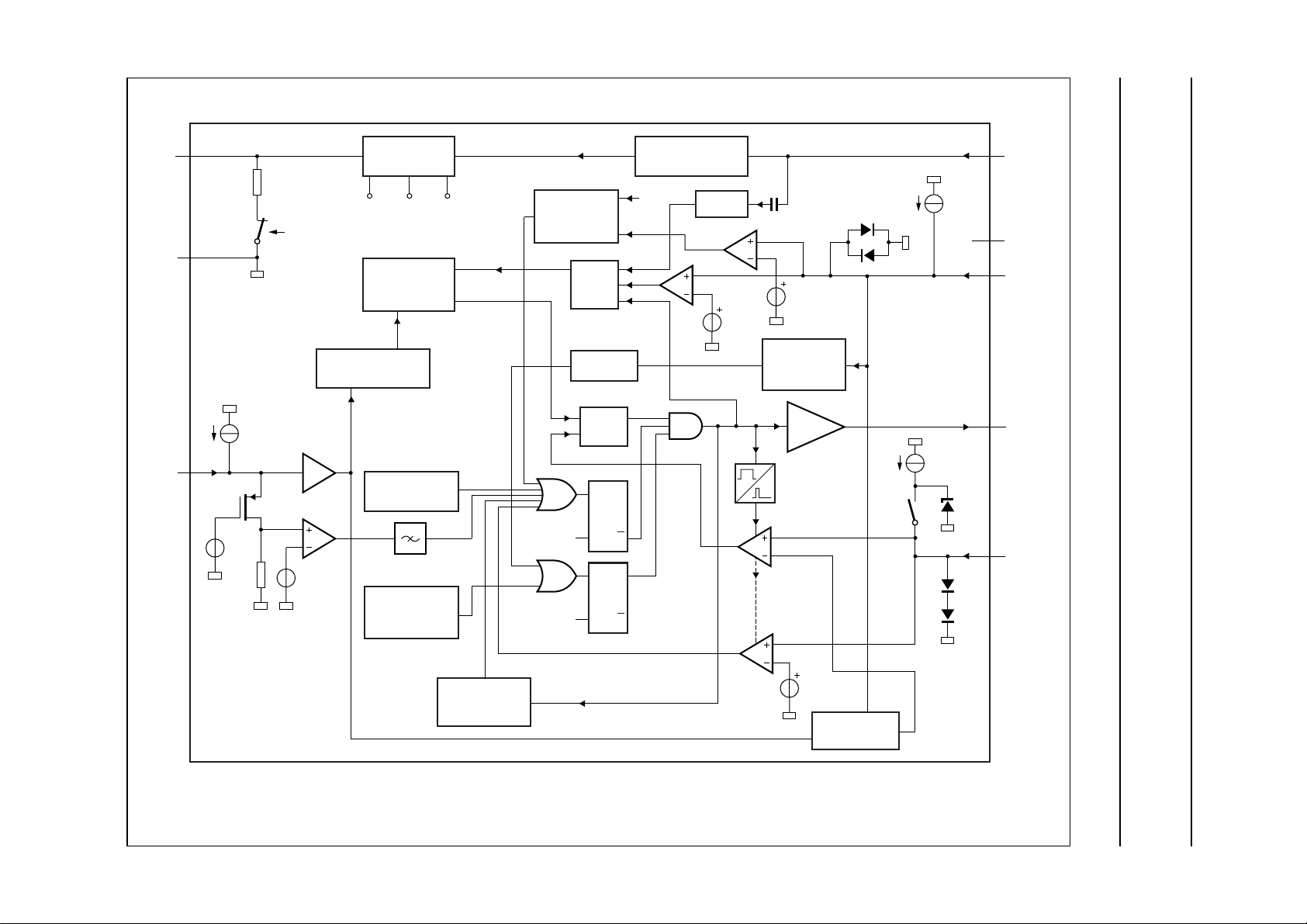

BLOCK DIAGRAM

Philips Semiconductors Product specification

GreenChip

V

CC

GND

CTRL

1

I

prot(CTRL)

M-level

−1

burst

detect

S1

2

3

2.5 V

SUPPLY

MANAGEMENT

internal

FREQUENCY

UVLO start

supply

VOLTAGE

CONTROLLED

OSCILLATOR

CONTROL

POWER-ON

RESET

OVER-

TEMPERATURE

PROTECTION

DEMAG

SHORT

PROTECTION

UVLO

V

< 4.5 V

CC

or UVLO

(TEA1533AP)

LOGIC

UP/DOWN

COUNTER

LOGIC

SQ

R

Q

SQ

R

Q

START-UP

CURRENT SOURCE

OCP

VALLEY

100

mV

50

mV

VOLTAGE

PROTECTION

LEB

blank

OCP

OVER-

DRIVER

I

prot(DEM)

clamp

soft

start

S2

8

DRAIN

TM

HVS

7

n.c.

4

DEM

6

DRIVER

I

ss

0.5 V

5

I

sense

II SMPS control IC

TEA1533P; TEA1533AP

TEA1533P

TEA1533AP

MAXIMUM

ON-TIME

PROTECTION

Fig.2 Block diagram.

short

winding

0.88 V

OVERPOWER

PROTECTION

MGU506

Page 5

Philips Semiconductors Product specification

GreenChipTMII SMPS control IC

TEA1533P; TEA1533AP

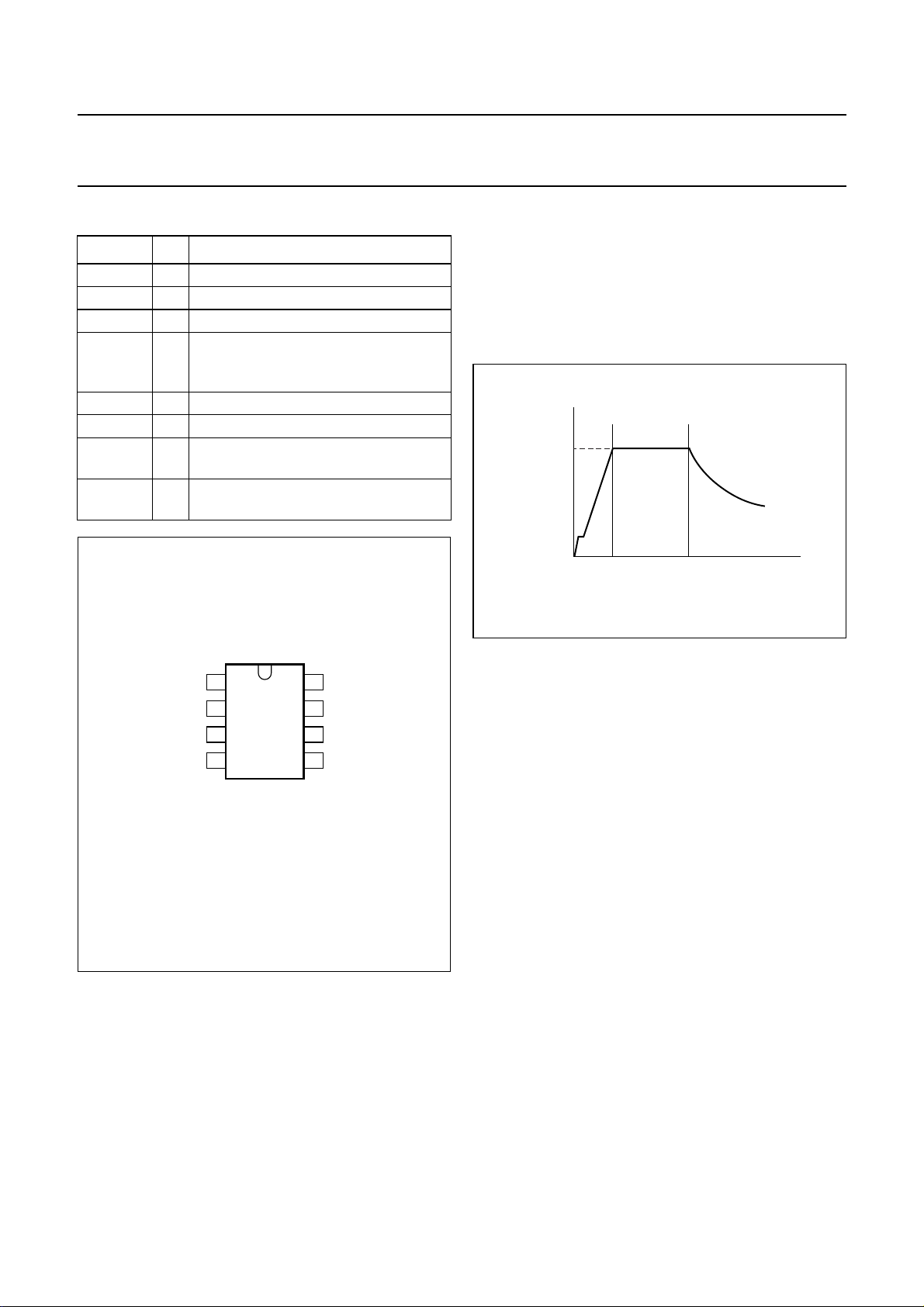

PINNING FUNCTIONAL DESCRIPTION

SYMBOL PIN DESCRIPTION

V

CC

1 supply voltage

GND 2 ground

CTRL 3 control input

The TEA1533 is the controller of a compact flyback

converter, and is situated at the primary side. An auxiliary

winding of the transformer provides demagnetization

detection and powers the IC after start-up.

The TEA1533 can operate in multi modes (see Fig.4).

DEM 4 input from auxiliary winding for

demagnetization timing, overvoltage

and overpower protection

I

sense

DRIVER 6 gate driver output

HVS 7 high voltage safety spacer, not

5 programmable current sense input

handbook, halfpage

(kHz)

f

VCO fixed quasi resonant

175

connected

DRAIN 8 drain of external MOS switch, input for

start-up current and valley sensing

25

MGU508

P (W)

handbook, halfpage

V

1

CC

GND

2

TEA1533P

CTRL

DEM

TEA1533AP

3

4

MGU507

Fig.3 Pin configuration.

8

7

6

5

DRAIN

HVS

DRIVER

I

sense

Fig.4 Multi modes operation.

The next converter stroke is started only after

demagnetization of the transformer current (zero current

switching), while the drain voltage has reached the lowest

voltage to prevent switching losses (green function). The

primary resonant circuit of the primary inductance and

draincapacitorensuresthis quasi-resonant operation. The

design can be optimized in such a way that zero voltage

switching can be reached over almost the universal mains

range.

To prevent very high frequency operation at lower loads,

the quasi-resonant operation changes smoothly in fixed

frequency PWM control.

At very low power (standby) levels, the frequency is

controlled down, via the VCO, to a minimum frequency of

approximately 25 kHz.

Start-up, mains enabling operation level and

undervoltage lock-out

Initially, the IC is self supplying from the rectified mains

voltage via pin DRAIN (see Figs 11 and 12). Supply

capacitor C

is charged by the internal start-up current

VCC

source to approximately 4 V or higher, depending on the

voltage on pin DRAIN.

2002 Aug 23 5

Page 6

Philips Semiconductors Product specification

GreenChipTMII SMPS control IC

Once the drain voltage exceeds the M-level

(mains-dependent operation-enabling level), the start-up

current source will continue charging capacitor C

(switch S1 will be opened); see Fig.2. The IC will activate

the converter as soon as the voltage on pin VCC passes

the V

CC(start)

level.

The IC supply is taken over by the auxiliary winding as

soon as the output voltage reaches its intended level and

the IC supply from the mains voltage is subsequently

stopped for high efficiency operation (green function).

The moment the voltage on pin VCC drops below the

undervoltage lock-out level, the IC stops switching and

enters a safe restart from the rectified mains voltage.

Inhibiting the auxiliary supply by external means causes

the converter to operate in a stable, well defined burst

mode.

Supply management

All (internal) reference voltages are derived from a

temperature compensated, on-chip band gap circuit.

VCC

V

handbook, halfpage

sense(max)

Fig.5 V

handbook, halfpage

(kHz)

TEA1533P; TEA1533AP

0.52 V

sense(max)

f

175

1 V

(typ)

voltage as function of V

1.5 V

(typ)

175 kHz

V

MGU509

MGU233

CTRL

CTRL

.

Current mode control

Current mode control is used for its good line regulation

behaviour.

The ‘on-time’ iscontrolled by theinternally inverted control

voltage, which is compared with the primary current

information. The primary current is sensed across an

external resistor. The driver output is latched in the logic,

preventing multiple switch-on.

The internal control voltage is inverselyproportional to the

external control pin voltage, with an offset of 1.5 V. This

means that a voltage range from 1 to 1.5 V on pin CTRL

will result in an internal control voltage range from

0.5 to 0 V (a high external control voltage results in a low

duty cycle).

Oscillator

The maximum fixed frequency of the oscillator isset by an

internal current source and capacitor. The maximum

frequency is reduced once the control voltage enters the

VCO control window. Then, the maximum frequency

changeslinearly with thecontrol voltage untilthe minimum

frequency is reached (see Figs 5 and 6).

25

V

VCO

VCO

2

level

Fig.6 VCO frequency as function of V

level

sense(max) (V)

1

sense(max)

Cycle skipping

At very low power levels, a cycle skipping mode will be

activated. A high control voltage will reduce the switching

frequency to a minimum of 25 kHz. If the voltage on the

control pin is raised even more, switch-on of the external

power MOSFET will be inhibited until the voltage on the

control pin has dropped to a lower value again (see Fig.7).

For system accuracy, it is not the absolute voltage on the

control pin that will trigger the cycle skipping mode, but a

signal derived from the internal VCO will be used.

Remark 1:If the no-loadrequirementof the systemissuch

that the output voltage can be regulated to its intended

level at a switching frequency of 25 kHz or above, the

cycle skipping mode will not be activated.

Remark 2: As switching will stop when the voltage on the

control pin is raised above a certain level, the burst mode

has to beactivated by amicrocontroller or any other circuit

sending a 30 µs, 16 mA pulse to the control input

(pin CTRL) of the IC.

2002 Aug 23 6

Page 7

Philips Semiconductors Product specification

GreenChipTMII SMPS control IC

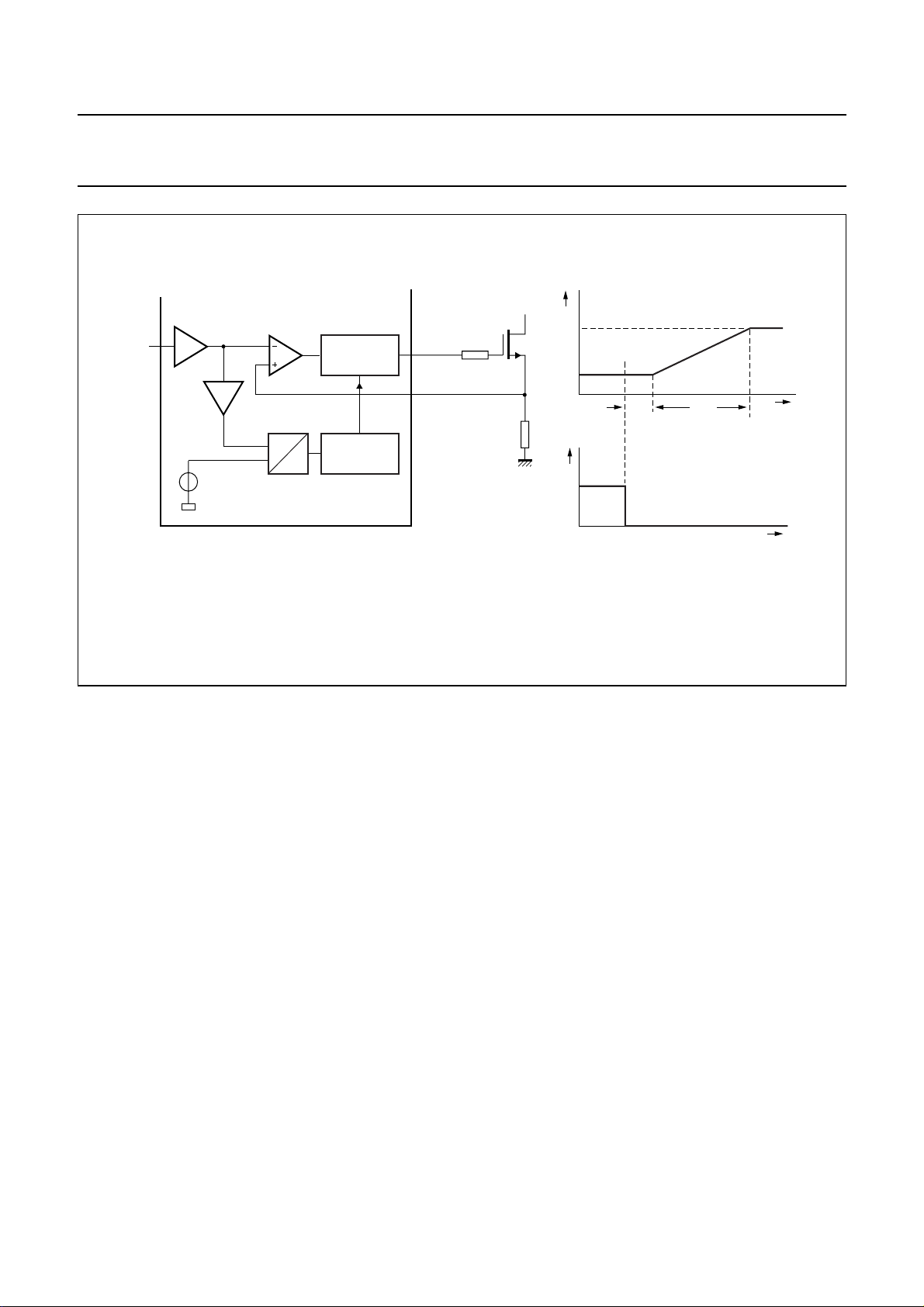

handbook, full pagewidth

CTRL

1.5 V − V

CTRL

X2

V

x

150 mV

current

comparator

V

I

DRIVER

OSCILLATOR

DRIVER

I

sense

TEA1533P; TEA1533AP

f

osc

f

max

f

min

cycle

skipping

1

0

dV

2

dV

1

150

Vx (mV)

MGU510

Vx (mV)

The voltage levels dV1 and dV2 are fixed in the IC to 50 mV (typical) and 18 mV (typical) respectively.

Fig.7 The cycle skipping circuitry.

Demagnetization

The system will be in discontinuous conduction mode all

the time. The oscillator will not start a new primary stroke

until the secondary stroke has ended.

Demagnetization features a cycle-by-cycle output

short-circuit protection by immediately lowering the

frequency (longer off-time), thereby reducing the power

Minimum and maximum ‘on-time’

The minimum ‘on-time’ of the SMPS is determined by the

Leading Edge Blanking (LEB) time. The IC limits the

‘on-time’ to 50 µs. When the system desires an ‘on-time’

longer than 50 µs, a fault condition is assumed (e.g.

removed Ciin Fig.11), the IC will stop switching and enter

the safe restart mode.

level.

Demagnetizationrecognition is suppressedduringthe first

t

time. This suppression may be necessary in

suppr

applications where the transformer has a large leakage

inductance, at low output voltages and at start-up.

If pin DEM is open-circuit or not connected, a fault

condition is assumed and the converter will stop operating

immediately. Operation will recommence as soon as the

fault condition is removed.

If pin DEM is shorted to ground, again a fault condition is

assumed and the converter will stop operating after the

first stroke. The converter will subsequently enter the safe

restart mode. This situation will persist until the

short-circuit is removed.

2002 Aug 23 7

Page 8

Philips Semiconductors Product specification

GreenChipTMII SMPS control IC

OverVoltage Protection (OVP)

An OVP mode is implemented in the GreenChip series.

This works for the TEA1533 by sensing the auxiliary

voltage via the current flowing into pin DEM during the

secondary stroke. The auxiliary winding voltage is a

well-defined replica of the output voltage. Any voltage

spikes are averaged by an internal filter.

Ifthe output voltage exceedstheOVP trip level, aninternal

counter starts counting subsequent OVP events. The

counter has been added to prevent incorrect OVP

detections which might occur during ESD or lightning

events. If the output voltage exceeds the OVP trip level a

fewtimes and notagain in asubsequent cycle, theinternal

counter will count down with twice the speed compared

with counting-up. However, when typical 10 cycles of

subsequent OVP events are detected, the IC assumes a

true OVP and the OVP circuit switches the power

MOSFET off. Next, the controller waits until the UVLO

level is reached on pin VCC. When VCC drops to UVLO,

capacitor C

Regarding the TEA1533P, this IC will not start switching

again. Subsequently, VCC will drop again to the UVLO

level, etc. Operation only recommences when the V

voltage drops below a level of approximately 4.5 V

(practically when V

period).

will be recharged to the V

VCC

has been disconnectedfor a short

mains

start

level.

CC

TEA1533P; TEA1533AP

Valley switching

A new cycle starts when the power MOSFET is switched

on (see Fig.8). After the ‘on-time’ (which is determined by

the ‘sense’ voltage and the internal control voltage), the

switchis opened andthesecondary stroke starts.Afterthe

secondary stroke, the drain voltage shows an oscillation

with a frequency of approximately

----------------------------------------------2π×L

where L

is the primary self inductance of the transformer

p

and Cd is the capacitance on the drain node.

As soon as the oscillator voltage is high again and the

secondary stroke has ended, the circuit waits for the

lowest drain voltage before starting a new primary stroke.

This method is called valley detection. Figure 8 shows the

drain voltage together with the valley signal, the signal

indicating the secondary stroke and the oscillator signal.

In an optimum design, the reflected secondary voltage on

the primary side will force the drain voltage to zero. Thus,

zero voltage switching is very possible, preventing large

1

capacitive switching losses and

P

-- -

2

allowing high frequency operation, which results in small

and cost effective inductors.

1

C

×()×

p

d

2

CV

× f××=

Regarding the TEA1533AP, switching starts again (safe

restart mode) when the V

level is reached. This

start

process is repeated as long as the OVP condition exists.

Theoutput voltage V

can be set by the demagnetization resistor, R

V

N

----------N

=

o OVP()

s

I

(OVP)(DEM)RDEM

aux

× V

where Nsis the number of secondary turnsand N

atwhich the OVPfunctiontrips,

o(OVP)

:

DEM

+{}

clamp(DEM)(pos)

is the

aux

number of auxiliary turns of the transformer.

Current I

(OVP)(DEM)

The value of R

is internally trimmed.

can be adjusted to the turns ratio of the

DEM

transformer, thus making an accurate OVP possible.

2002 Aug 23 8

Page 9

Philips Semiconductors Product specification

GreenChipTMII SMPS control IC

handbook, full pagewidth

drain

valley

secondary

stroke

primary

stroke

secondary

stroke

TEA1533P; TEA1533AP

secondary

ringing

oscillator

A: Start of new cycle at lowest drain voltage.

B: Start of new cycle in a classical PWM system at high drain voltage.

Fig.8 Signals for valley switching.

OverCurrent Protection (OCP)

The cycle-by-cycle peak drain current limit circuit uses the

externalsource resistor to measurethecurrent accurately.

This allows optimum size determination of the transformer

core (cost issue). The circuit is activated after the leading

edge blanking time, t

. The OCP circuit limits the ‘sense’

leb

voltage to an internal level.

OverPower Protection (OPP)

Duringthe primary stroke,the rectified mainsinput voltage

is measured by sensing the current drawn from pin DEM.

This current is dependent on the mains voltage, according

to the following formula:

I

DEM

V

≈≈

-------------- R

DEM

aux

×

NV

mains

-------------------------R

DEM

BA

MGU235

N

where:

N

=

-----------N

aux

p

The current information is used to adjust the peak drain

current, which is measured via pin I

. The internal

sense

compensation is such that an almost mains independent

maximum output power can be realized.

The OPP curve is given in Fig.9.

2002 Aug 23 9

Page 10

Philips Semiconductors Product specification

GreenChipTMII SMPS control IC

MGU236

handbook, halfpage

−100 µA

(typ)

I

DEM

−24 µA

(typ)

Fig.9 OPP correction curve.

Short winding protection

After the leading edge blanking time, the short winding

protection circuit is activated. If the ‘sense’ voltage

exceeds the short winding protection voltage V

converter will stop switching. Once VCC drops below the

UVLO level, capacitor C

will be recharged and the

VCC

supply will restart again. This cycle will be repeated until

the short-circuit is removed (safe restart mode).

The short winding protection will also protect in case of a

secondary diode short-circuit.

OverTemperature Protection (OTP)

An accurate temperature protection is provided in the

circuit. When the junction temperature exceeds the

thermal shutdown temperature, the IC will stop switching.

When VCC drops to UVLO, capacitor C

recharged to the V

start

level.

Regarding the TEA1533P, this IC will not start switching

again. Subsequently, VCC will drop again to the UVLO

level, etc. Operation only recommences when the V

voltage drops below a level of approximately 4.5 V

(practically when the V

has been disconnected for a

mains

short period).

V

sense(max)

0.52 V

(typ)

0.3 V

(typ)

will be

VCC

swp

, the

CC

TEA1533P; TEA1533AP

Control pin protection

If pin CTRL is open-circuit or not connected, a fault

conditionis assumed and theconverter will stop switching.

Operation will recommence as soon as the fault condition

is removed.

Burst mode standby

Pin CTRL is also used to implement the burst mode

standby. In burst mode standby, the power supply enters

a special low dissipation state. Figure 11 shows a flyback

converter using the burst mode standby function. The

system enters burst mode standby when the

microcontroller activates NPN transistor T1 on the

secondary side.

When the voltage on C

measured by the microcontroller, the opto-coupler is

activated by T1, sending a large current signal to

pin CTRL. In response to this signal, the IC stops

switching and entersa ‘hiccup’ mode.This burst activation

signal should be present for longer than the ‘burst blank’

period (typically 30 µs): the blanking time prevents false

burst triggering due to spikes. Figure 12 shows the burst

mode standby signals. The hiccup mode during burst

mode standby operation does not differ from the hiccup

mode at safe restart during a system fault condition (e.g.

output short-circuit). The power is reduced during soft

restart mode.

Burst mode standby operation continues until the

microcontroller stops activating transistor T1. The system

then enters the start-up sequence and begins normal

switching behaviour.

V

I

burstmode

th

--------------- R

CTRL

+=

exceeds a certain voltage

micro

I

th(on)

Regarding the TEA1533AP, when the V

start

level is

reached, switching starts again (safe restart mode). This

process is repeated as long as the OTP condition exists.

2002 Aug 23 10

Page 11

Philips Semiconductors Product specification

GreenChipTMII SMPS control IC

Soft start-up

To prevent transformer rattle during hiccup, the

transformer peak current is slowly increased by the soft

start function. This can be achieved by inserting a resistor

and a capacitor between pin I

(see Fig.10). An internal current source charges the

capacitor to V = ISS× RSS, with a maximum of

approximately 0.5 V.

The start level and the time constant of the increasing

primary current level can be adjusted externally by

changing the values of RSS and CSS.

V

I

primary(max)

τ R

SSCSS

ocpISSRSS

=

---------------------------------------------- -

×=

The charging currentI

pin I

pin I

is below approximately 0.5 V. If the voltage on

sense

exceeds 0.5 V, the soft start current source will

sense

×()–

R

sense

will flow aslong as the voltage on

SS

start limiting the current ISS. At the V

current source is completely switched off.

and the sense resistor

sense

level, the I

CC(start)

SS

TEA1533P; TEA1533AP

Driver

The driver circuit to the gate of the power MOSFET has a

current sourcing capabilityof 170 mA typical and a current

sink capability of 700 mA typical. This permits fast turn-on

and turn-off of the power MOSFET for efficient operation.

A low driver source current has been chosen to limit the

∆V/∆t at switch-on. This reduces Electro Magnetic

Interference (EMI) and also limits the current spikes

across R

sense

.

Since the soft start current ISS is subtracted from pin V

CC

chargingcurrent, the RSSvaluewill affect the VCCcharging

current level by a maximum of 60 µA (typical value).

handbook, halfpage

I

SS

0.5 V

start-up

V

ocp

R

I

5

sense

SS

C

SS

R

sense

MGU237

Fig.10 Soft start.

2002 Aug 23 11

Page 12

Philips Semiconductors Product specification

GreenChipTMII SMPS control IC

TEA1533P; TEA1533AP

LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 60134); note 1.

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

Voltages

V

CC

V

CTRL

V

DEM

V

sense

V

DRAIN

supply voltage continuous −0.4 +20 V

voltage on pin CTRL −0.4 +5 V

voltage on pin DEM current limited −0.4 − V

voltage on pin I

sense

current limited −0.4 − V

voltage on pin DRAIN −0.4 +650 V

Currents

I

CTRL

I

DEM

I

sense

I

DRIVER

I

DRAIN

current on pin CTRL d < 10% − 50 mA

current on pin DEM −250 +250 µA

current on pin I

sense

−1 +10 mA

current on pin DRIVER d < 10% −0.8 +2 A

current on pin DRAIN − 5mA

General

P

tot

T

stg

T

j

V

esd

total power dissipation T

<70°C − 0.75 W

amb

storage temperature −55 +150 °C

operating junction temperature −20 +145 °C

electrostatic discharge voltage

pins 1 to 6 HBM class 1; note 2 − 2000 V

pin DRAIN HBM class 1; note 2 − 1500 V

any pin note 3 − 400 V

Notes

1. All voltages are measured with respect to ground; positive currents flow into the IC; pin VCC may not be current

driven. The voltage ratings are valid provided other ratings are not violated; current ratings are valid provided the

maximum power rating is not violated.

2. Equivalent to discharging a 100 pF capacitor through a 1.5 kΩ resistor.

3. Equivalent to discharging a 200 pF capacitor through a 0.75 µH coil and a 10 Ω resistor.

THERMAL CHARACTERISTICS

SYMBOL PARAMETER CONDITIONS VALUE UNIT

R

th(j-a)

thermal resistance from junction to ambient in free air; note 1 100 K/W

Note

1. With pin GND connected to sufficient copper area on the printed-circuit board.

QUALITY SPECIFICATION

In accordance with ‘SNW-FQ-611-D’.

2002 Aug 23 12

Page 13

Philips Semiconductors Product specification

GreenChipTMII SMPS control IC

TEA1533P; TEA1533AP

CHARACTERISTICS

T

=25°C; VCC= 15 V; all voltages are measured with respect to ground; currents are positive when flowing into

amb

the IC; unless otherwise specified.

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Start-up current source (pin DRAIN)

I

DRAIN

BV

DSS

M-level mains-dependent operation

supply current drawn from

pin DRAIN

VCC=0V; V

> 100 V 1.0 1.2 1.4 mA

DRAIN

with auxiliary supply;

V

DRAIN

> 100 V

− 100 300 µA

breakdown voltage 650 −−V

60 − 100 V

enabling level

Supply voltage management (pin V

V

CC(start)

V

CC(UVLO)

V

CC(hys)

I

CC(h)

I

CC(l)

I

CC(restart)

I

CC(oper)

start-up voltage on V

undervoltage lock-out on V

hysteresis voltage on V

pin VCC charging current, high V

pin VCC charging current, low V

pin VCC restart current V

supply current under normal

CC

CC

)

CC

CC

10.3 11 11.7 V

8.1 8.7 9.3 V

V

CC(start)

DRAIN

DRAIN

3V<VCC<V

DRAIN

V

CC(UVLO)<VCC

− V

CC(UVLO)

2.0 2.3 2.6 V

> 100 V; VCC<3V −1.2 −1 −0.8 mA

> 100 V;

> 100 V;

CC(UVLO)

<V

CC(start)

−1.2 −0.75 −0.45 mA

−650 −550 −450 µA

no load on pin DRIVER 1.1 1.3 1.5 mA

operation

I

CC(burstmode)

supply current while not switching − 0.85 − mA

Demagnetization management (pin DEM)

V

th(DEM)

demagnetization comparator

50 100 150 mV

threshold voltage on pin DEM

I

prot(DEM)

V

clamp(DEM)(neg)

protection current on pin DEM V

negative clamp voltage on

=50mV −50

DEM

I

= −150 µA −0.5 −0.25 −0.05 V

DEM

(1)

−−10 nA

pin DEM

V

clamp(DEM)(pos)

positive clamp voltage on

I

= 250 µA 0.5 0.7 0.9 V

DEM

pin DEM

t

suppr

suppression of transformer

1.1 1.5 1.9 µs

ringing at start of secondary

stroke

Pulse width modulator

t

on(min)

t

on(max)

minimum on-time − t

leb

− ns

maximum on-time latched 40 50 60 µs

Oscillator

f

osc(l)

f

osc(h)

V

vco(start)

oscillator low fixed frequency V

oscillator high fixed frequency V

peak voltage on pin I

sense

, where

> 1.5 V 20 25 30 kHz

CTRL

< 1 V 145 175 205 kHz

CTRL

see Figs 6 and 7 − VCO

1

− mV

frequency reduction starts

2002 Aug 23 13

Page 14

Philips Semiconductors Product specification

GreenChipTMII SMPS control IC

TEA1533P; TEA1533AP

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

V

vco(max)

peak voltage on pin I

sense

the frequency is equal to f

, where

osc(l)

− VCO1− 25 − mV

Duty cycle control (pin CTRL)

V

CTRL(min)

minimum voltage on pin CTRL for

− 1.0 − V

maximum duty cycle

V

CTRL(max)

maximumvoltageonpin CTRL for

− 1.5 − V

minimum duty cycle

I

prot(CTRL)

protection current on pin CTRL V

= 1.5 V −1

CTRL

(1)

−0.8 −0.5 µA

Burst mode standby (pin CTRL)

V

th(burst)(on)

burst mode standby active

I

= 6 mA 3.3 3.8 4.3 V

burst

threshold voltage

I

th(burst)(on)

I

th(burst)(off)

burst mode standby active current 16 −−mA

burst mode standby inactive

−− 6mA

current

t

(burst-blank)

burst mode standby blanking time 25 30 35 µs

Valley switch (pin DRAIN)

∆V/∆t

valley

t

valley-swon

valley recognition voltage change −85 −+85 V/µs

delay from valley recognition to

− 150

(1)

− ns

switch-on

Overcurrent and short winding protection (pin I

V

sense(max)

t

PD

V

swp

t

leb

maximum source voltage OCP ∆V/∆t = 0.1 V/µs 0.48 0.52 0.56 V

propagating delay from detecting

V

sense(max)

to switch-off

short winding protection voltage 0.83 0.88 0.96 V

blanking time for current and

)

sense

∆V/∆t = 0.5 V/µs − 140 185 ns

300 370 440 ns

short winding protection

I

SS

soft start current V

< 0.5 V 45 60 75 µA

sense

Overvoltage protection (pin DEM)

I

OVP(DEM)

OVP level on pin DEM set by resistor R

DEM

, see

54 60 66 µA

Section “OverVoltage

Protection (OVP)”

Overpower protection (pin DEM)

I

OPP(DEM)

OPP current on pin DEM to start

OPP correction

set by resistor R

DEM

Section “OverPower

, see

−−24 −µA

Protection (OPP)”

I

OPP50%(DEM)

OPP current on pin DEM, where

−−100 −µA

maximum source voltage is

limited to 0.3 V

2002 Aug 23 14

Page 15

Philips Semiconductors Product specification

GreenChipTMII SMPS control IC

TEA1533P; TEA1533AP

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Driver (pin DRIVER)

I

source

I

sink

V

o(max)

source current capability of driver VCC= 9.5 V; V

sink current capability of driver VCC= 9.5 V; V

V

= 9.5 V;

CC

maximum output voltage of the

V

VCC>12V − 11.5 12 V

DRIVER

= 9.5 V

DRIVER

=2V −−170 −88 mA

DRIVER

=2V − 300 − mA

400 700 − mA

driver

Temperature protection

T

prot(max)

maximum temperature protection

130 140 150 °C

level

T

prot(hys)

hysteresis for the temperature

− 8

(1)

−°C

protection level

Note

1. Guaranteed by design.

2002 Aug 23 15

Page 16

Philips Semiconductors Product specification

GreenChipTMII SMPS control IC

TEA1533P; TEA1533AP

APPLICATION INFORMATION

A converterwith the TEA1533consists of aninput filter, atransformer with athird winding (auxiliary), and an output stage

with a feedback circuit.

Capacitor C

(at pin VCC) buffers the supply voltage of the IC, which is powered via the high voltage rectified mains

VCC

during start-up and via the auxiliary winding during operation.

A sense resistor converts the primary current into a voltage at pin I

. The value of this sense resistor defines the

sense

maximum primary peak current.

V

handbook, full pagewidth

mains

C

C

CTRL

R

CTRL

VCC

V

CC

GND

CTRL

DEM

1

2

TEA1533P

TEA1533AP

3

4

R

DEM

D

D

N

s

micro

o

C

i

C

i

N

p

DRAIN

8

HVS

7

6

5

DRIVER

I

sense

n.c.

power

MOSFET

R

SS

C

SS

R

sense

N

aux

C

o

V

µC

micro

V

oV

MICRO-

CONTROLLER

standby

pulse

Fig.11 Flyback configuration with secondary sensing using the burst mode standby.

2002 Aug 23 16

R

R

reg1

reg2

T

MGU511

1

Page 17

Philips Semiconductors Product specification

GreenChipTMII SMPS control IC

handbook, full pagewidth

V

i

V

D

(power

MOSFET)

V

i

V

o

TEA1533P; TEA1533AP

V

CC

V

gate

M-level

burst mode

V

µC

start-up

sequence

normal

operation

overvoltage

protection

(TEA1533AP)

output

short-circuit

burst mode standby

normal

operation

MGU512

Fig.12 Typical waveforms.

2002 Aug 23 17

Page 18

Philips Semiconductors Product specification

GreenChipTMII SMPS control IC

PACKAGE OUTLINE

DIP8: plastic dual in-line package; 8 leads (300 mil)

D

seating plane

A

L

Z

e

b

8

1

w M

b

1

b

2

5

TEA1533P; TEA1533AP

SOT97-1

M

E

A

2

A

c

(e )

1

M

H

pin 1 index

E

1

DIMENSIONS (inch dimensions are derived from the original mm dimensions)

A

A

A

UNIT

max.

mm

inches

Note

1. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

OUTLINE

VERSION

SOT97-1

12

min.

max.

050G01 MO-001 SC-504-8

b

1.73

0.53

1.14

0.38

0.068

0.021

0.045

0.015

IEC JEDEC EIAJ

b

1

1.07

0.89

0.042

0.035

4

0 5 10 mm

scale

b

2

0.36

0.23

0.014

0.009

REFERENCES

(1) (1)

cD E e M

9.8

9.2

0.39

0.36

6.48

6.20

0.26

0.24

L

e

1

M

3.60

8.25

3.05

7.80

0.14

0.32

0.12

0.31

EUROPEAN

PROJECTION

E

10.0

0.39

0.33

H

8.3

w

max.

0.2542.54 7.62

ISSUE DATE

0.010.10 0.30

95-02-04

99-12-27

1.154.2 0.51 3.2

0.0450.17 0.020 0.13

(1)

Z

2002 Aug 23 18

Page 19

Philips Semiconductors Product specification

GreenChipTMII SMPS control IC

SOLDERING

Introduction to soldering through-hole mount

packages

This text gives a brief insight to wave, dip and manual

soldering.A more in-depth accountofsoldering ICs can be

found in our

Packages”

Wave soldering is the preferred method for mounting of

through-hole mount IC packages on a printed-circuit

board.

Soldering by dipping or by solder wave

The maximum permissible temperature of the solder is

260 °C; solder at this temperature must not be in contact

with the joints for more than 5 seconds.

Thetotalcontact time of successive solderwavesmustnot

exceed 5 seconds.

Suitability of through-hole mount IC packages for dipping and wave soldering methods

“Data Handbook IC26; Integrated Circuit

(document order number 9398 652 90011).

The device may be mounted up to the seating plane, but

the temperature of the plastic body must not exceed the

specified maximum storage temperature (T

printed-circuit board has been pre-heated, forced cooling

may be necessary immediately after soldering to keep the

temperature within the permissible limit.

Manual soldering

Apply the soldering iron (24 V or less) to the lead(s) of the

package, either below the seating plane or not more than

2 mm above it. If the temperature of the soldering iron bit

is less than 300 °C it may remain in contact for up to

10 seconds. If the bit temperature is between

300 and 400 °C, contact may be up to 5 seconds.

TEA1533P; TEA1533AP

stg(max)

). If the

PACKAGE

DIPPING WAVE

DBS, DIP, HDIP, SDIP, SIL suitable suitable

Note

1. For SDIP packages, the longitudinal axis must be parallel to the transport direction of the printed-circuit board.

SOLDERING METHOD

(1)

2002 Aug 23 19

Page 20

Philips Semiconductors Product specification

GreenChipTMII SMPS control IC

DATA SHEET STATUS

PRODUCT

DATA SHEET STATUS

Objective data Development This data sheet contains data from the objective specification for product

Preliminary data Qualification This data sheet contains data from the preliminary specification.

Product data Production This data sheet contains data from the product specification. Philips

Notes

1. Please consult the most recently issued data sheet before initiating or completing a design.

2. The product status of the device(s) described in this data sheet may have changed since this data sheet was

published. The latest information is available on the Internet at URL http://www.semiconductors.philips.com.

(1)

STATUS

(2)

development. Philips Semiconductors reserves the right to change the

specification in any manner without notice.

Supplementary data will be published at a later date. Philips

Semiconductors reserves the right to change the specification without

notice, in order to improve the design and supply the best possible

product.

Semiconductors reserves the right to make changes at any time in order

to improve the design, manufacturing and supply. Changes will be

communicated according to the Customer Product/Process Change

Notification (CPCN) procedure SNW-SQ-650A.

TEA1533P; TEA1533AP

DEFINITIONS

DEFINITIONS

Short-form specification The data in a short-form

specification is extracted from a full data sheet with the

same type number and title. For detailed information see

the relevant data sheet or data handbook.

Limiting values definition Limiting values given are in

accordance with the Absolute Maximum Rating System

(IEC 60134). Stress above one or more of the limiting

values may cause permanent damage to the device.

These are stress ratings only and operation of the device

atthese or at anyotherconditionsabove those given inthe

Characteristics sections of the specification is not implied.

Exposure to limiting values for extended periods may

affect device reliability.

Application information Applications that are

described herein for any of these products are for

illustrative purposes only. Philips Semiconductors make

norepresentationorwarranty that such applications willbe

suitable for the specified use without further testing or

modification.

DISCLAIMERS

Life support applications These products are not

designed for use in life support appliances, devices, or

systems where malfunction of these products can

reasonably be expected to result inpersonal injury. Philips

Semiconductorscustomersusingor selling these products

for use in such applications do so at their own risk and

agree to fully indemnify Philips Semiconductors for any

damages resulting from such application.

Right to make changes Philips Semiconductors

reserves the right to make changes, without notice, in the

products, including circuits, standard cells, and/or

software, described or contained herein in order to

improve design and/or performance. Philips

Semiconductors assumes no responsibility or liability for

theuseof any of these products,conveysnolicence or title

under any patent, copyright, or mask work right to these

products,and makes no representationsorwarranties that

these products are free from patent, copyright, or mask

work right infringement, unless otherwise specified.

2002 Aug 23 20

Page 21

Philips Semiconductors Product specification

GreenChipTMII SMPS control IC

TEA1533P; TEA1533AP

NOTES

2002 Aug 23 21

Page 22

Philips Semiconductors Product specification

GreenChipTMII SMPS control IC

TEA1533P; TEA1533AP

NOTES

2002 Aug 23 22

Page 23

Philips Semiconductors Product specification

GreenChipTMII SMPS control IC

TEA1533P; TEA1533AP

NOTES

2002 Aug 23 23

Page 24

Philips Semiconductors – a w orldwide compan y

Contact information

For additional information please visit http://www.semiconductors.philips.com. Fax: +31 40 27 24825

For sales offices addresses send e-mail to: sales.addresses@www.semiconductors.philips.com.

© Koninklijke Philips Electronics N.V. 2002

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner.

The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed

without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license

under patent- or other industrial or intellectual property rights.

Printed in The Netherlands 613502/02/pp24 Date of release: 2002 Aug 23 Document order number: 9397750 10261

SCA74

Loading...

Loading...