Philips NE56625-20 Datasheet

NE56625-20

System reset with Watchdog timer

Product data 2002 Mar 25

INTEGRATED CIRCUITS

Philips Semiconductors Product data

NE56625-20System reset with watchdog timer

2

2002 Mar 25 853–2327 27919

GENERAL DESCRIPTION

The NE56625-20 is comprised of a power-on reset, a watchdog

timer and low battery detection circuit. The NE56625 is designed to

generate an Active-LOW reset signal for a variety of microprocessor

and logic systems. Accurate reset signals are generated during

momentary power interruptions or whenever power supply voltages

sag to intolerable levels. The built-in watchdog timer monitors the

microprocessor and ensures it is operating properly. Any abnormal

system operations due to microprocessor malfunctions are

terminated by a system reset generated by the watchdog. To

accommodate a wide range of system requirements, the Watchdog

Monitoring Time and power-on reset delay time are programmable

from 10 ms to 10 sec.

The NE56625-20 is designed for low voltage battery powered

applications with low battery detection threshold at 2.2 V . It is offered

in the SO8 surface mount package.

FEA TURES

•Accurate threshold detection voltages:

– Low battery: 2.2 V ±3%

– Power-on reset: 2.0 V ±3%

•Low hysteresis voltage (both low battery check and power-on

reset): 50 mV typ.

•Low supply current: 150 µA typ.

•Programmable power-on reset detection voltage

•Programmable power-on reset delay: 10 ms to 10 s

•Internal watchdog timer programmable with external resistor and

capacitor: 10 ms to 10 s

•Reset assertion with V

CC

down to 0.8 VDC (typical)

•Few external components required

APPLICA TIONS

•Microcomputer systems and logic systems

•2 V cordless phones

•Various portable, battery operated equipment

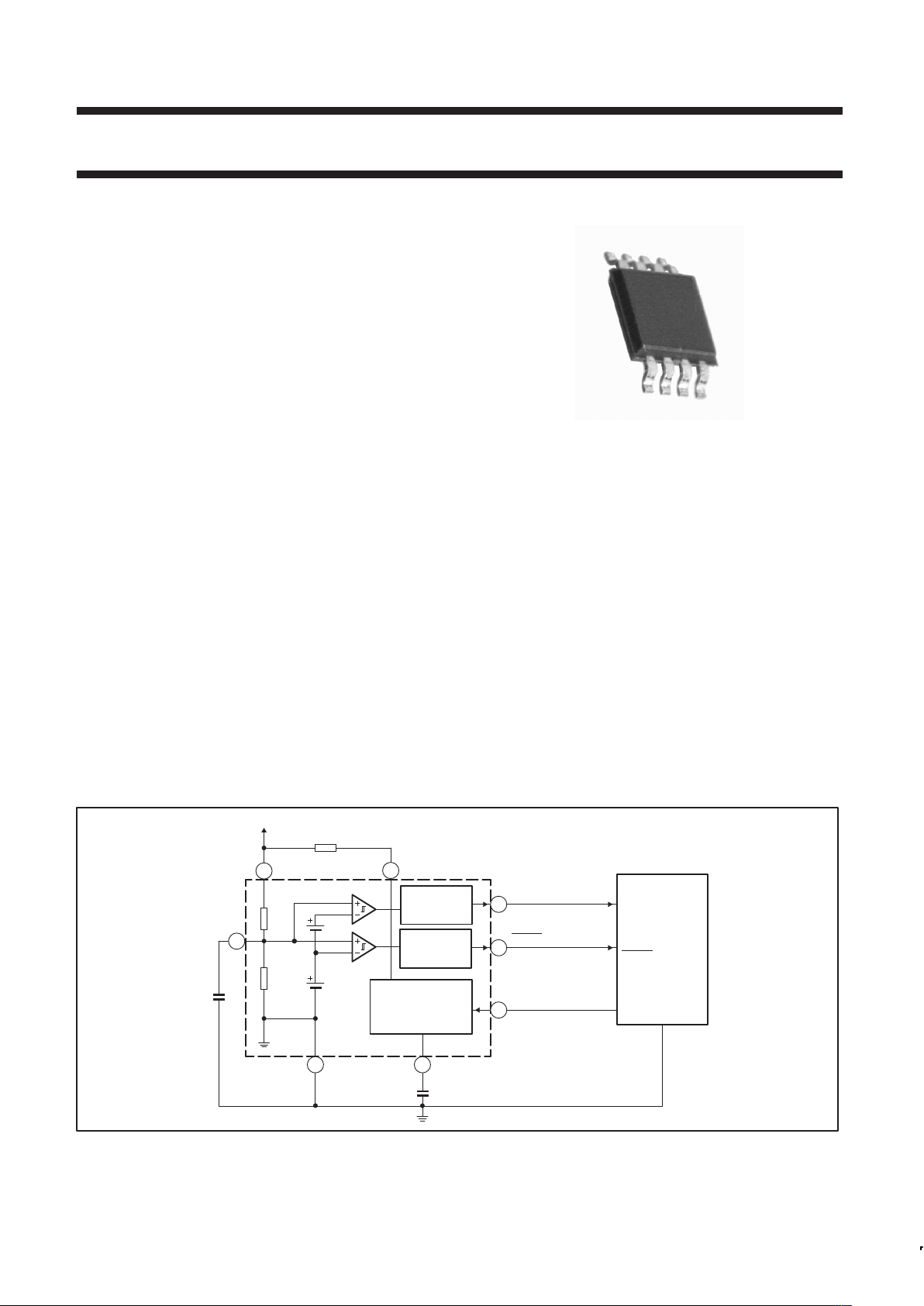

SIMPLIFIED SYSTEM DIAGRAM

1

RESET

CLK

GND

C

R

CT

V

REF

8

3

V

CC

6

NE56625-20

4

BC

RESET

CLK

GND

R

CT

2

NMI

LOGIC SYSTEM

BATTERY

CHECK

RESET

GENERATOR

PROGRAMMABLE

WATCHDOG

TIMER

C

T

7

5

V

S

SL01593

Figure 1. Simplified system diagram.

Philips Semiconductors Product data

NE56625-20System reset with watchdog timer

2002 Mar 25

3

ORDERING INFORMATION

PACKAGE

TEMPERATURE

TYPE NUMBER

NAME DESCRIPTION

RANGE

NE56625-20D SO8 plastic small outline package; 8 leads; body width 3.9 mm –20 to +75 °C

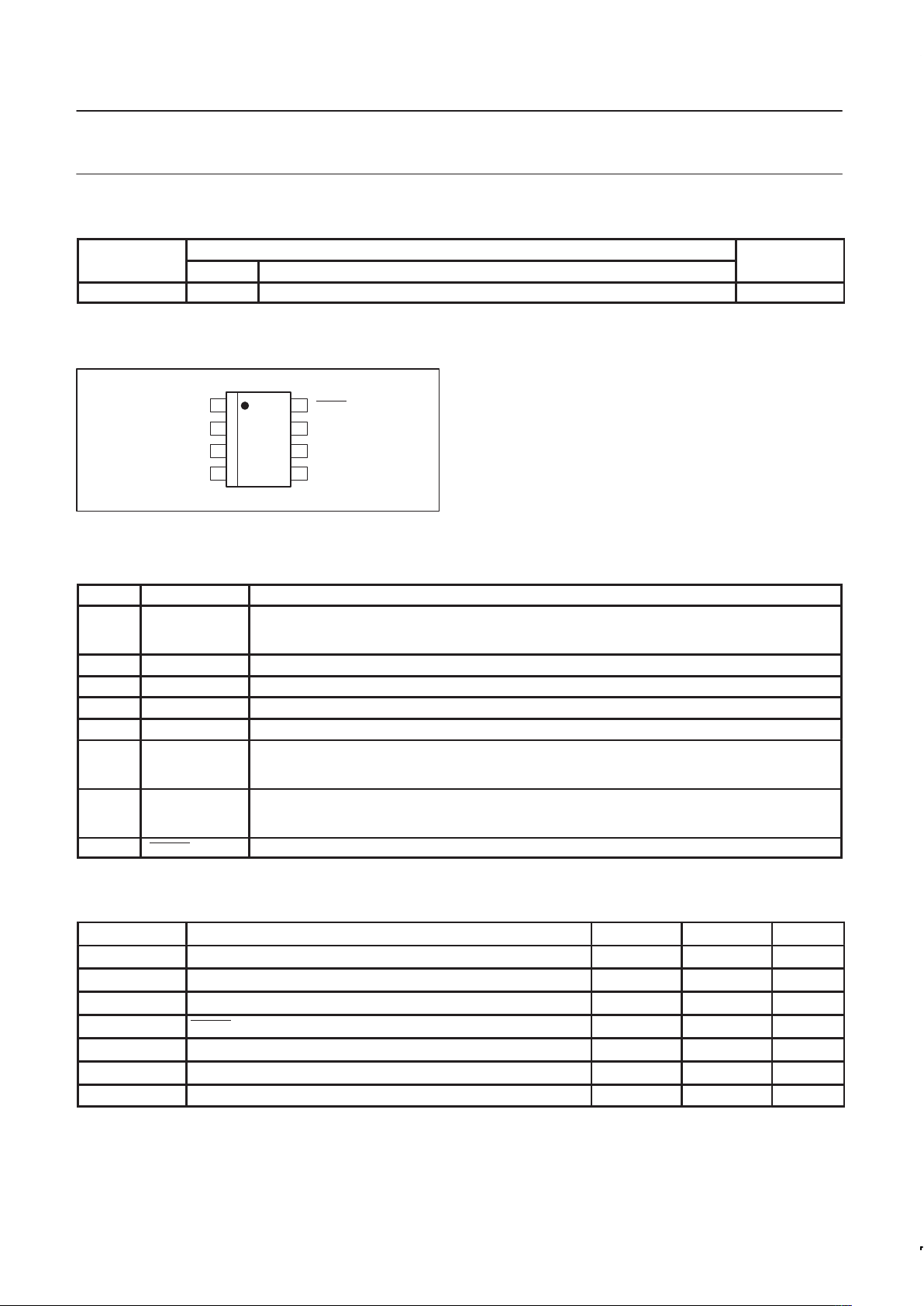

PIN CONFIGURATION

SL01586

1

2

3

4

8

7

6

5

TOP VIEW

SO8

C

T

BC

CLK

GND

RESET

V

S

R

CT

V

CC

Figure 2. Pin configuration.

PIN DESCRIPTION

PIN SYMBOL DESCRIPTION

1 C

T

t

WDM

, t

WDR

, tPR adjustment pin.

t

WDM

, t

WDR

, tPR times are dependent on the value of external CT capacitor used. See Figure 17 (Timing

Diagram) for definition of t

WDM

, t

WDR

, tPR times.

2 BC Battery check Active-LOW output.

3 CLK Clock input pin from logic system for watchdog timer.

4 GND Circuit ground.

5 V

CC

Positive supply voltage.

6 R

CT

Watchdog timer control pin.

The watchdog timer is enabled when this pin is pulled-up to VCC with a resistor, and disabled when this pin

is connected to ground.

7 V

S

Detection threshold adjustment pin.

The detection threshold can be decreased by connecting this pin to VCC with a pull-up resistor. The

detection threshold can be increased by connecting this pin to ground with a pull-down resistor.

8 RESET Reset Active-LOW output.

MAXIMUM RATINGS

SYMBOL PARAMETER MIN. MAX. UNIT

V

CC

Power supply voltage –0.3 7 V

V

VS

VS pin voltage –0.3 7 V

V

CLK

CLK pin voltage –0.3 7 V

V

OH

RESET and BC pin voltage –0.3 7 V

T

oper

Operating temperature –20 +75 °C

T

stg

Storage temperature –40 +125 °C

P Power dissipation – 300 mW

Philips Semiconductors Product data

NE56625-20System reset with watchdog timer

2002 Mar 25

4

RECOMMENDED OPERATING CONDITIONS

SYMBOL PARAMETER RATING UNIT

V

CC

Power supply voltage 1.9 to 6.5 V

I

OLR

RESET sink current 0 to 500 µA

I

OLC

BC sink current 0 to 5.0 mA

V

CKH

HIGH-level clock input voltage < 1.0 V

V

CKL

LOW-level clock input voltage < 0.2 V

t

WD

Clock monitoring time 1 to 10,000 ms

t

r(CLK)

, t

f(CLK)

Clock rise and fall times < 100 µs

t

r(VCC)

Power supply voltage rise time < 100 µs

t

f(VCC)

Power supply voltage fall time < 50 µs

T

amb

Operating ambient temperature –20 to +70 °C

C

T

TC capacitance 0.0022 to 2.2 µF

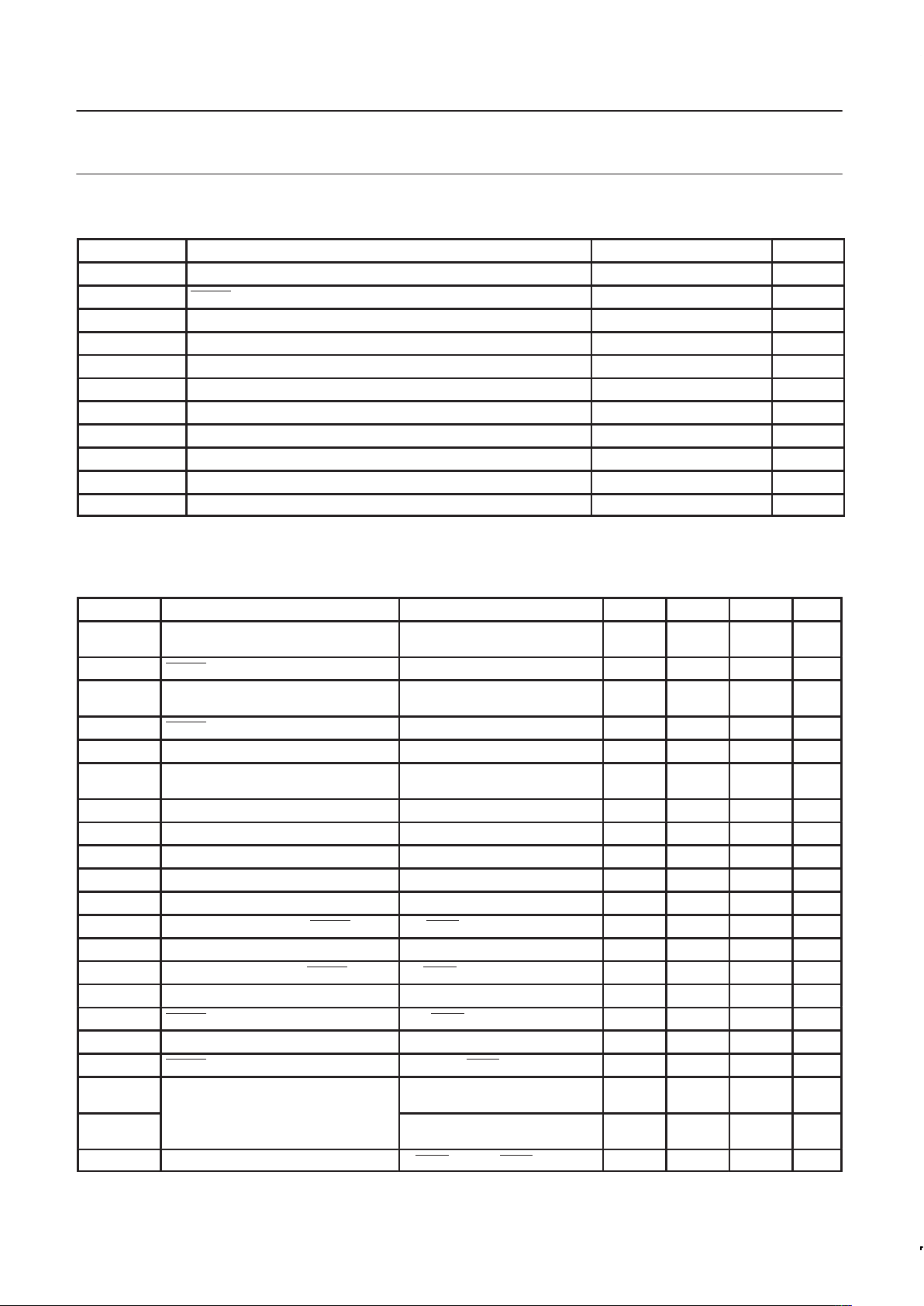

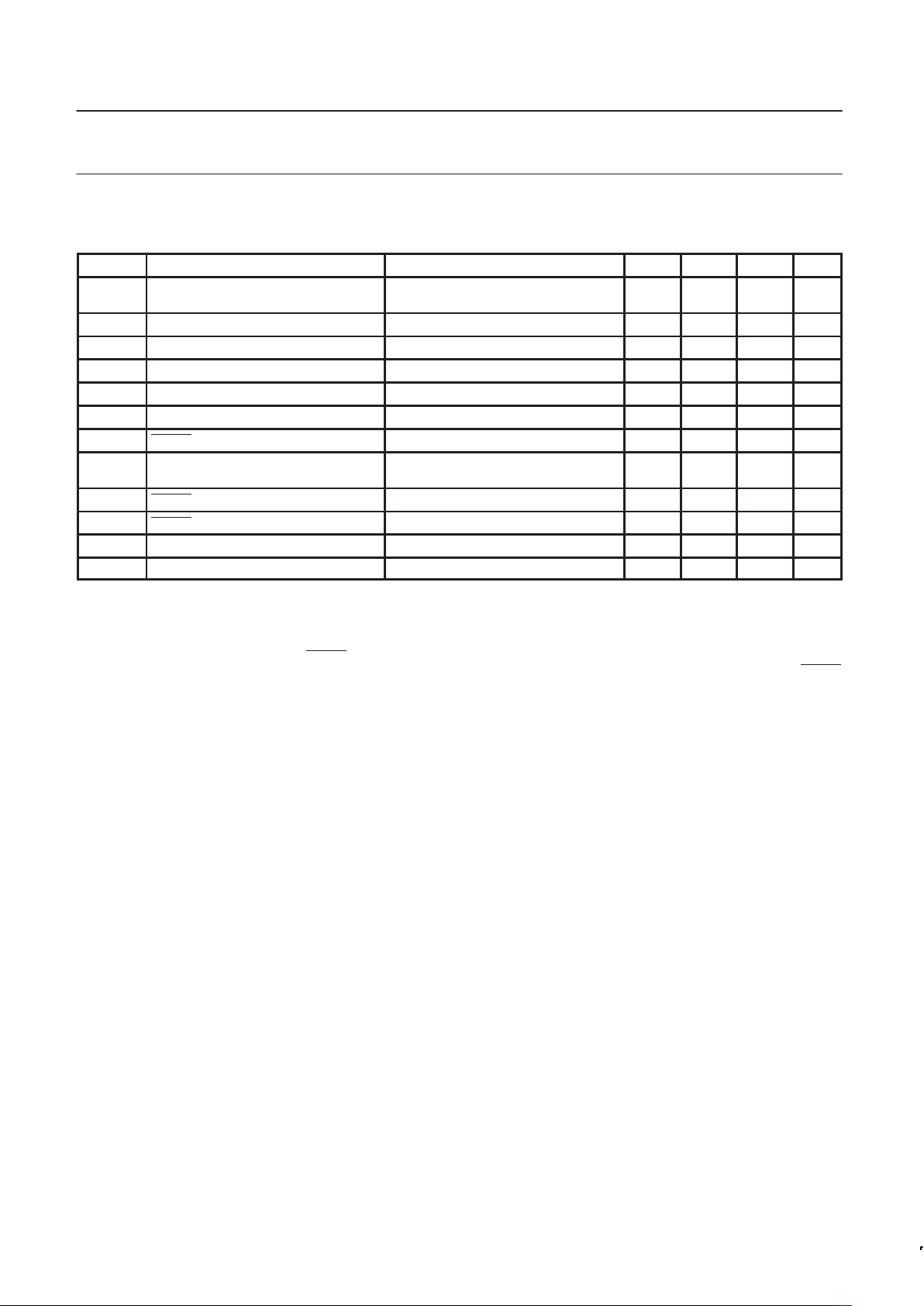

DC ELECTRICAL CHARACTERISTICS

T

amb

= 25 °C, VCC = 2.6 V, unless otherwise specified.

SYMBOL

PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

I

CC

Supply current during watchdog timer

operation

no load – 0.7 1.0 mA

V

SLR

RESET detection threshold VCC = falling; RCT: GND; VS = open 1.94 2.0 2.06 V

∆VSR/∆T

amb

Temperature coefficient of reset detection

voltage

–20 °C ≤ T

amb

≤ 70 °C – ±0.01 ±0.05 %/°C

V

hysR

RESET threshold hysteresis VCC = falling; RCT: GND; VS = open 25 50 100 mV

V

SLB

Battery detection voltage VCC = falling; RLB = 10 kΩ 2.13 2.20 2.27 V

∆VSB/∆T

amb

Temperature coefficient of battery

detection voltage

– ±0.01 ±0.05 %/°C

V

hysB

Battery hysteresis voltage VCC = falling; RLB = 10 kΩ 25 50 100 mV

∆V

SL

Detection voltage difference ∆VSL = V

SLB

– V

SLR

175 200 225 mV

V

TH

CLK input threshold 0.8 1.2 2.0 V

I

IH

HIGH-level CLK input current V

CLK

= 2.6 V – 0 1 µA

I

IL

LOW-level CLK input current V

CLK

= 0 V –15 –6 –2 µA

V

OHR

HIGH-level output voltage, RESET I

RESET

= –1.0 µA; VS = open 2.0 2.2 – V

V

OHB

HIGH-level output voltage, BC RLB = 10 kΩ 2.0 2.2 – V

V

OLR

LOW-level output voltage, RESET I

RESET

= 500 µA; VCC = 1.8 V – 0.3 0.5 V

V

OLB

LOW-level output voltage, BC IBC = 5 mA; VCC = 1.8 V – 0.3 0.5 V

I

OLR

RESET output sink current V

RESET

= 0.5 V; VCC = 1.8 V 500 700 – µA

I

OLB

Battery Check output sink current VBC = 0.5 V; VCC = 1.8 V 5 7 – mA

I

OHR

RESET output source current V

RESET

= 2.0 V 2 4 – µA

I

CT1

CT charge current

VCT = 0.5 V;

during watchdog operation

–0.3 –0.15 –0.075 µA

I

CT2

VCT = 0.5 V;

during power-on reset operation

–0.3 –0.15 –0.075 µA

V

CCL

Supply voltage to assert reset operation V

RESET

= 0.4 V; I

RESET

= 0.05 mA – 0.8 1.0 V

Philips Semiconductors Product data

NE56625-20System reset with watchdog timer

2002 Mar 25

5

AC ELECTRICAL CHARACTERISTICS

Characteristics measured with VCC = 2.6 V, and T

amb

= 25 °C, unless otherwise specified.

SYMBOL

PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

t

P1

Minimum power supply pulse width for

detection

4.0 V ≤ negative-going VCC pulse ≤ 5.0 V 8.0 – – µs

t

CLKW

Clock input pulse width 3.0 – – µs

t

CLK

Clock input cycle 20 – – µs

t

WDM

Watchdog monitoring time (Notes 1, 6) CT = 0.022 µF; RCT = open 50 100 150 ms

t

WDR

Watchdog reset time (Notes 2, 6) CT = 0.022 µF 1.0 2.0 3.0 ms

t

PR

Power-on reset delay time (Notes 3, 6) VCC = rising from 0 V; CT = 0.022 µF 50 100 150 ms

t

PDR

RESET propagation delay time (Note 4) VCC = falling; RLR = 100 kΩ; CLR = 15 pF – 10 – µs

t

PDB

Battery Check propagation delay time

(Note 4)

VCC = falling; RLB = 10 kΩ; CLB = 15 pF – 10 – µs

t

RR

RESET rise time (Note 5) RLR = 100 kΩ; CLR = 15 pF – 10 – µs

t

FR

RESET fall time (Note 5) RLR = 100 kΩ; CLR = 15 pF – 2 – µs

t

RB

Battery Check rise time (Note 5) RLB = 10 kΩ; CLB = 15 pF – 10 – µs

t

FB

Battery Check fall time (Note 5) RLB = 10 kΩ; CLB = 15 pF – 2 – µs

NOTES:

1. ‘Watchdog monitoring time’ (t

WDM

) is the duration from the last pulse (negative-going edge) of the timer clear clock pulse until reset output

pulse occurs (see Figure 17). A reset signal is output if a clock pulse is not input during this time.

2. ‘Watchdog reset time’ (t

WDR

) is the reset pulse width. Do not confuse this with the power-on reset delay time (tPR).

3. The power-on reset delay or hold time is the duration measured from the time V

CC

exceeds the upper detection threshold (V

SHR

) and

power-on reset release is experienced (RESET

output HIGH).

4. ‘Reset response time’ is the duration from when the supply voltage sags below the lower detection threshold (V

SL

) and reset occurs (RESET

output LOW).

5. Reset rise and fall times and Battery Check rise and fall times are measured at 10% and 90% output levels.

6. Watchdog monitoring time (t

WDM

), watchdog reset time (t

WDR

), and power-on reset delay time (tPR) during power-on can be modified by

varying the C

T

capacitance. The times can be approximated by applying the following formula. The recommended range for CT is 0.0022 µF

to 2.2 µF.

Formula 1. Calculation for approximate t

PR

, t

WDM

, and t

WDR

values:

t

PR

(ms) ≈ 4500 × CT (µF)

t

WDM

(ms) ≈ 4500 × CT (µF)

t

WDR

(ms) ≈ 90 × CT (µF)

Example: When C

T

= 0.022 µF and RCT = open:

t

PR

≈ 100 ms

t

WDM

≈ 100 ms

t

WDR

≈ 2.0 ms

Loading...

Loading...