Philips NE56604-42D Datasheet

INTEGRATED CIRCUITS

NE56604-42

System reset with built-in watchdog timer

Product data

Supersedes data of 2001 Jun 19

File under Integrated Circuits, Standard Analog

2001 Aug 22

Philips Semiconductors Product data

TYPE NUMBER

NE56604-42System reset with built-in watchdog timer

GENERAL DESCRIPTION

The NE56604-42 is designed to generate a reset signal at a

threshold voltage of 4.2 V for a variety of microprocessor and logic

systems. Accurate reset signals are generated during momentary

power interruptions, or whenever power supply voltages sag to

intolerable levels. The NE56604-42 has a built-in Watchdog Timer to

monitor the microprocessor and ensure it is operating properly. Any

abnormal system operations due to microprocessor malfunctions

are terminated by a system reset generated by the watchdog. The

NE56604-42 has a watchdog monitoring time of 100 ms (typical).

The NE56604-42 is offered in the SO8 surface mount package.

FEATURES

•Both positive and negative logic reset output signals are available

•Accurate threshold detection

•Internal power-on reset delay

•Internal watchdog timer programmable with external resistor

•Watchdog monitoring time of 100 ms (typical)

•Reset assertion with V

•Few external components required.

down to 0.8 VDC (typical)

CC

APPLICA TIONS

•Microcomputer systems

•Logic systems.

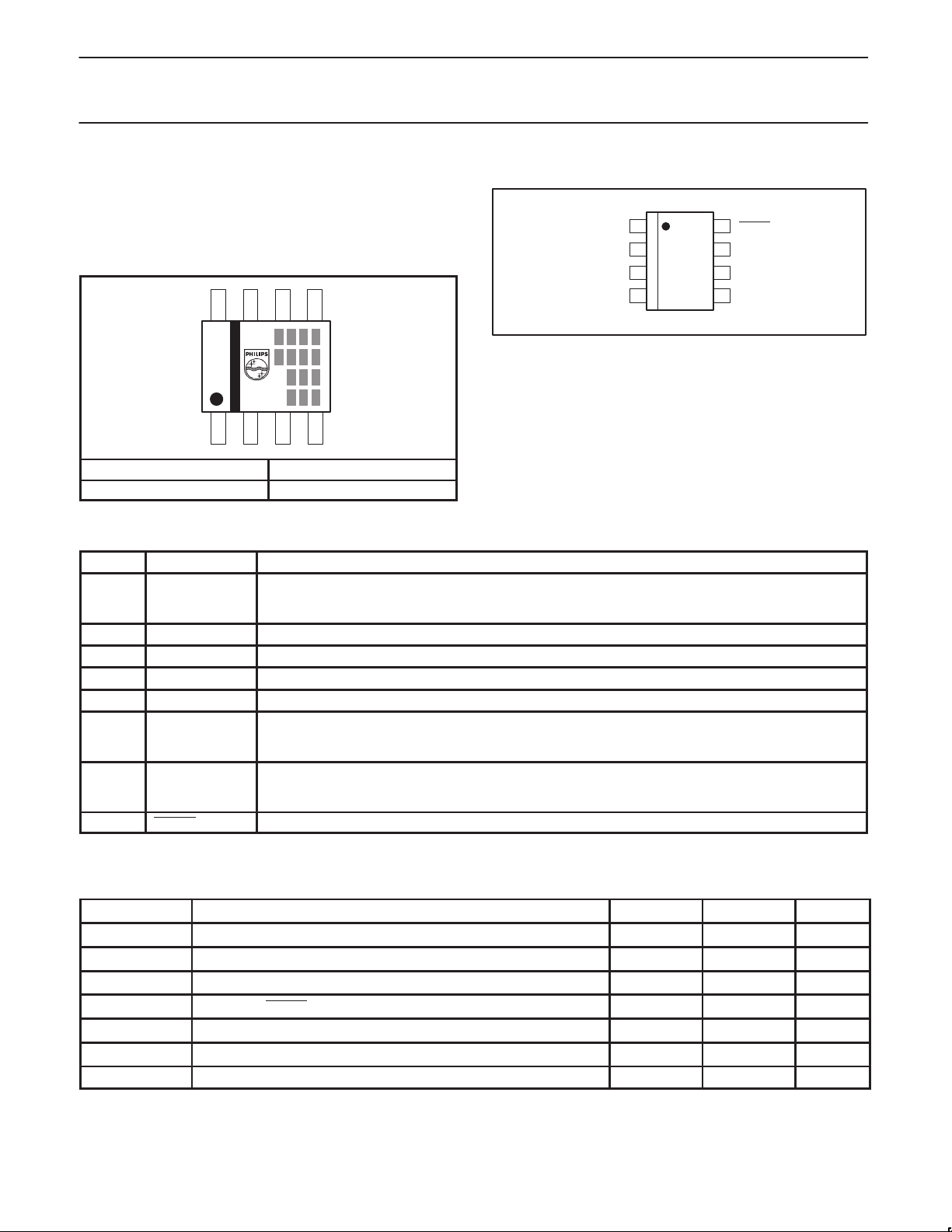

SIMPLIFIED SYSTEM DIAGRAM

V

CC

5

V

C

R

S

7

R

R

CT

R

6

CT

NE56604-42

RESET

GENERATOR

V

REF

4

GND

PROGRAMMABLE

WATCHDOG TIMER

1

C

T

Figure 1. Simplified system diagram.

8

2

3

RESET

RESET

CLK

LOGIC

SYSTEM

RESET

RESET

CLK

GND

SL01281

ORDERING INFORMATION

PACKAGE

NAME DESCRIPTION

TEMPERATURE

RANGE

NE56604-42D SO8 plastic small outline package; 8 leads; body width 3.9 mm –20 to +70 °C

2001 Aug 22 853–2250 26949

2

Philips Semiconductors Product data

NE56604-42System reset with built-in watchdog timer

Part number marking

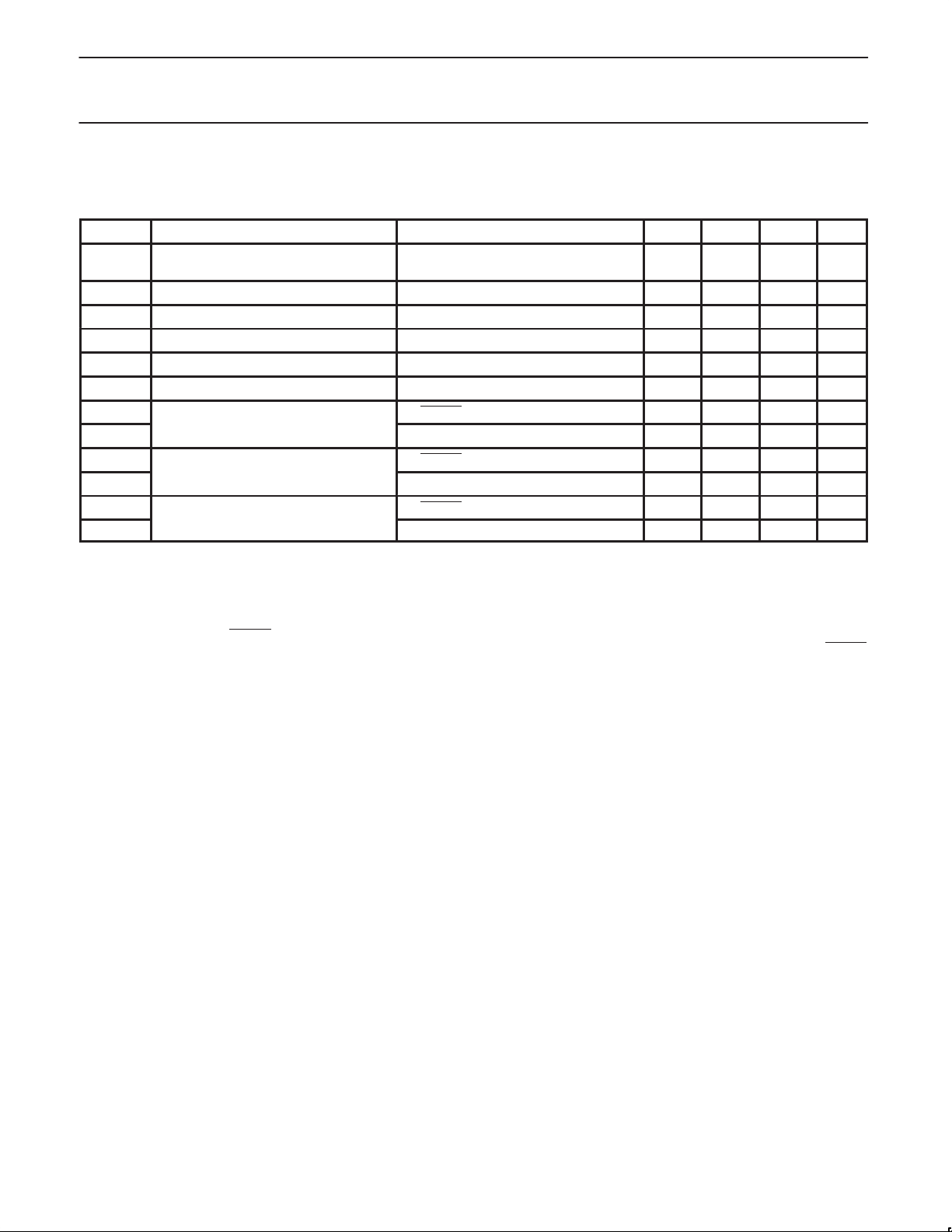

PIN CONFIGURATION

The package is marked with a four letter code in the first line to the

right of the logo. The first three letters designate the product. The

fourth letter, represented by ‘x’, is a date tracking code. The

remaining two or three lines of characters are internal manufacturing

codes.

5

6

7

8

2

1

3

4

Part number Marking

NE56604-42 A A D x

PIN DESCRIPTION

PIN SYMBOL DESCRIPTION

1 C

T

2 RESET Reset HIGH output pin.

3 CLK Clock input pin from logic system for watchdog timer.

4 GND Circuit ground.

5 V

6 R

7 V

CC

CT

S

8 RESET Reset LOW output pin.

t

, t

WDM

t

WDM

Diagram) for definition of t

, tPR adjustment pin.

WDR

, t

, tPR times are dependent on the value of external CT capacitor used. See Figure 20 (Timing

WDR

WDM

, t

WDR

, tPR times.

Power supply pin for circuit.

Watchdog timer control and program pin.

Serves to ENABLE the watchdog function when connected to pull-up resistor (RCT) to VCC, and DISABLE

the watchdog when connected to ground. Used in conjunction with C

Detection threshold adjustment pin.

The detection threshold can be increased by connecting this pin to VCC with a pull-up resistor. The detection

threshold can be decreased by connecting this pin to ground with a pull-down resistor.

TOP VIEW

8

7

6

5

SL01280

RESET

CLK

GND

1

C

T

2

SO8

3

4

Figure 2. Pin configuration.

pin to program t

T

RESET

V

S

R

CT

V

CC

WDM

time.

MAXIMUM RATINGS

SYMBOL PARAMETER MIN. MAX. UNIT

V

CC

V

VS

V

CLK

V

OH

T

oper

T

stg

P Power dissipation – 250 mW

2001 Aug 22

Power supply voltage –0.3 10 V

VS pin voltage –0.3 10 V

CLK pin voltage –0.3 10 V

RESET and RESET pin voltage –0.3 10 V

Operating temperature –20 70 °C

Storage temperature –40 125 °C

3

Philips Semiconductors Product data

NE56604-42System reset with built-in watchdog timer

DC ELECTRICAL CHARACTERISTICS

Characteristics measured with VCC = 5.0 V, and T

See Figure 26 (Test circuit 1) for test configuration used for DC parameters.

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

I

CC

V

SL

V

SH

∆VS/∆T

V

hys

V

TH

I

IH

I

IL

V

OH1

V

OH2

V

OL1

V

OL2

V

OL3

V

OL4

I

OL1

I

OL2

I

CT1

I

CT2

V

CCL1

V

CCL2

Supply current during watchdog timer

operation

Reset detection threshold

Temperature coefficient of reset threshold –20 °C ≤ T

amb

Threshold hysteresis V

CLK input threshold 0.8 1.2 2.0 V

CLK input current, HIGH-level V

CLK input current, LOW-level V

Output voltage, HIGH-level

Output voltage, LOW-level

Output sink current

CT charge current (Note 1)

Supply voltage to assert reset operation

NOTE:

1. I

source current is determined by the value of the RCT pull-up resistor to VCC.

CT

= 25 °C, unless otherwise specified.

amb

VS = open; VCC = falling 4.05 4.20 4.35 V

VS = open; VCC = rising 4.15 4.30 4.45 V

amb

= VSH (rising VCC) – V

hys

(falling VCC)

= 5.0 V – 0 1.0 µA

CLK

= 0 V –20 –10 –3.0 µA

CLK

I

= –5.0 µA; VS = open 4.5 4.8 – V

RESET

I

current = –5.0 mA; VS = 0 V 4.5 4.8 – V

RESET

I

= 3.0 mA; VS = 0 V – 0.2 0.4 V

RESET

I

= 10 mA; VS = 0 V – 0.3 0.5 V

RESET

I

= 0.5 mA; VS = open – 0.2 0.4 V

RESET

I

= 1.0 mA; VS = open – 0.3 0.5 V

RESET

V

= 1.0 V; VS = 0 V 10 16 – mA

RESET

V

= 1.0 V; VS = open 1.0 2.0 – mA

RESET

VCT = 1.0 V; RCT = open during

watchdog operation

VCT = 1.0 V;

during power-on reset operation

V

= 0.4 V; I

RESET

V

RESET

1 MΩ resistor (pin 2 to GND)

RESET

= VCC – 0.1 V;

– 0.7 1.0 mA

≤ 70 °C – ±0.01 – %/°C

SL

50 100 150 mV

–0.8 –1.2 –2.4 µA

–0.8 –1.2 –2.4 µA

= 0.2 mA – 0.8 1.0 V

– 0.8 1.0 V

2001 Aug 22

4

Philips Semiconductors Product data

NE56604-42System reset with built-in watchdog timer

AC ELECTRICAL CHARACTERISTICS

Characteristics measured with VCC = 5.0 V, and T

See Figure 27 (Test circuit 2) for test configuration used for AC parameters.

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

t

P1

t

CLKW

t

CLK

t

WDM

t

WDR

t

PR

t

PD1

t

PD2

t

R1

t

R2

t

F1

t

F2

Minimum power supply pulse width for

detection

Clock input pulse width 3.0 – – µs

Clock input cycle 20 – – µs

Watchdog monitoring time (Notes 1, 6) CT = 0.1 µF; RCT = open 50 100 150 ms

Watchdog reset time (Notes 2, 6) CT = 0.1 µF 1.0 2.0 3.0 ms

Power-on reset delay time (Notes 3, 6) VCC = rising from 0 V; CT = 0.1 µF 50 100 150 ms

Reset propagation delay time (Note 4)

Reset rise time (Note 5)

Reset fall time (Note 5)

NOTES:

1. ‘Watchdog monitoring time’ is the duration from the last pulse (negative-going edge) of the timer clear clock pulse until reset output pulse

occurs (see Figure 20). A reset signal is output if a clock pulse is not input during this time. Watchdog monitoring time can be modified by

changing the value of the R

2. ‘Watchdog reset time’ is the reset pulse width (see Figure 20).

pull-up resistor. Monitoring time adjustments are shown in Figure 25.

CT

3. ‘Power-on reset delay time’ is the duration measured from the time V

release is experienced (RESET

output HIGH; RESET output LOW).

4. ‘Reset response time’ is the duration from when the supply voltage sags below the lower detection threshold (V

output LOW, RESET output HIGH).

5. Reset rise and fall times are measured at 10% and 90% output levels.

6. Watchdog monitoring time (t

varying the C

to 10 µF.

capacitance. The times can be approximated by applying the following formula. The recommended range for CT is 0.001 µF

T

), watchdog reset time (t

WDM

Formula 1. Calculation for approximate t

(ms) ≈ 1000 × CT (µF)

t

PR

t

(ms) ≈ 1000 × CT (µF)

WDM

t

(ms) ≈ 20 × CT (µF)

WDR

Example: When CT = 0.1 µF and RCT = open:

t

≈ 100 ms

PR

t

≈ 100 ms

WDM

t

≈ 2.0 ms

WDR

= 25 °C, unless otherwise specified.

amb

4.0 V ≤ negative-going VCC pulse ≤ 5.0 V 8.0 – – µs

RESET: RL1 = 2.2 kΩ; CL1 = 100 pF – 2.0 10 µs

RESET: RL2 = 10 kΩ; CL2 = 20 pF – 3.0 10 µs

RESET: RL1 = 2.2 kΩ; CL1 = 100 pF – 1.0 1.5 µs

RESET: RL2 = 10 kΩ; CL2 = 20 pF – 1.0 1.5 µs

RESET: RL1 = 2.2 kΩ; CL1 = 100 pF – 0.1 0.5 µs

RESET: RL2 = 10 kΩ; CL2 = 20 pF – 0.5 1.0 µs

CC

), and power-on reset delay time (tPR) during power-on can be modified by

WDR

, t

PR

WDM

, and t

WDR

values:

exceeds the upper detection threshold (VSH) and power-on reset

) and reset occurs (RESET

SL

2001 Aug 22

5

Philips Semiconductors Product data

NE56604-42System reset with built-in watchdog timer

TYPICAL PERFORMANCE CURVES

1.4

T

= 35 °C

amb

1.2

1.0

0.8

0.6

0.4

POWER SUPPLY CURRENT (mA)

CC

0.2

I

0

0 1.0 2.0 3.0 4.0 5.0 6.0 7.0 8.0 9.0 10.0

WITHOUT

CLOCK SIGNALS

TO WATCHDOG

WITH

CLOCK SIGNALS

TO WATCHDOG

VCC, POWER SUPPLY VOLTAGE (V)

Figure 3. Power supply current vs. voltage.

6.0

RESET PULL-UP R = 2.2 kΩ

5.0

4.0

3.0

2.0

, RESET OUTPUT VOLTAGE (V)

RST

1.0

V

0

0 1.0 2.0 3.0 4.0 5.0 6.0

T

= –25 °C

amb

T

= 25 °C

amb

T

= 75 °C

amb

VCC POWER SUPPLY VOLTAGE (V)

V

SL

V

OL

Figure 5. RESET output voltage vs. supply voltage.

6.0

RESET PULL-UP R = 10 kΩ

SL01303

5.0

4.0

3.0

2.0

, RESET OUTPUT VOLTAGE (V)

1.0

RST

V

0

0 1.0 2.0 3.0 4.0 5.0 6.0 7.0 8.0

VCC, POWER SUPPLY VOLTAGE (V)

T

= –25 °C, 25 °C, 75 °C

amb

V

SL

V

SH

V

OL

SL01304

Figure 4. RESET output voltage vs. supply voltage.

4.5

VCC = RISING (VSH)

VCC = FALLING (VSL)

4.4

V

4.3

V

SH

4.2

, DETECTION THRESHOLD (V)

SH

4.1

, V

SL

V

4.0

–40 –20 0 20 40 60 80 100

T

, AMBIENT TEMPERATURE (°C)

amb

SL01302

SH

V

SL

SL01301

Figure 6. Detection threshold vs. temperature.

600

500

400

300

200

100

, RESET OUTPUT SATURATION (mV)

OL

V

0

0 –0.6 –0.8 –1.0 –1.2 –1.4 –1.6 –1.8

Figure 7. RESET saturation vs. sink current.

2001 Aug 22

VCC = 5.0 V

RESET PULL-UP R = 10 kΩ

T

amb

–0.2 –0.4

IOL, RESET OUTPUT SINK CURRENT (mA)

= 25 °C

T

amb

= 75 °C

T

amb

= –25 °C

SL01300

600

500

400

300

200

100

, RESET OUTPUT SATURATION (mV)

OL

V

0

0 –6 –8 –10 –12 –14 –16 –18

VCC = 5.0 V

RESET

PULL-UP R = 2.2 kΩ

T

= 75 °C

amb

–2 –4

IOL, RESET OUTPUT SINK CURRENT (mA)

T

amb

T

= –25 °C

amb

= 25 °C

SL01299

Figure 8. RESET saturation vs. sink current.

6

Loading...

Loading...