Philips 74HCT221N, 74HCT221DB, 74HCT221D, 74HC221N, 74HC221DB Datasheet

...

DATA SH EET

Product specification

Supersedes data of April 1988

File under Integrated Circuits, IC06

December 1990

INTEGRATED CIRCUITS

74HC/HCT221

Dual non-retriggerable monostable

multivibrator with reset

For a complete data sheet, please also download:

•The IC06 74HC/HCT/HCU/HCMOS Logic Family Specifications

•The IC06 74HC/HCT/HCU/HCMOS Logic Package Information

•The IC06 74HC/HCT/HCU/HCMOS Logic Package Outlines

December 1990 2

Philips Semiconductors Product specification

Dual non-retriggerable monostable

multivibrator with reset

74HC/HCT221

FEATURES

• Pulse width variance is typically less than ±5%

• Pin-out identical to “123”

• Overriding reset terminates output pulse

• nB inputs have hysteresis for improved noise immunity

• Output capability: standard (except for nR

EXT/CEXT

)

• ICC category: MSI

GENERAL DESCRIPTION

The 74HC/HCT221 are high-speed Si-gate CMOS devices

and are pin compatible with low power Schottky TTL

(LSTTL). They are specified in compliance with JEDEC

standard no. 7A.

The 74HC/HCT221 are dual non-retriggerable monostable

multivibrators. Each multivibrator features an active

LOW-going edge input (n

A) and an active HIGH-going

edge input (nB), either of which can be used as an enable

input.

Pulse triggering occurs at a particular voltage level and is

not directly related to the transition time of the input pulse.

Schmitt-trigger input circuitry for the nB inputs allow

jitter-free triggering from inputs with slow transition rates,

providing the circuit with excellent noise immunity.

Once triggered, the outputs (nQ, nQ) are independent of

further transitions of nA and nB inputs and are a function

of the timing components. The output pulses can be

terminated by the overriding active LOW reset inputs

(nRD). Input pulses may be of any duration relative to the

output pulse.

Pulse width stability is achieved through internal

compensation and is virtually independent of VCC and

temperature. In most applications pulse stability will only

be limited by the accuracy of the external timing

components.

The output pulse width is defined by the following

relationship:

tW=C

EXTREXTIn2

tW= 0.7C

EXTREXT

Pin assignments for the “221” are identical to those of the

“123” so that the “221” can be substituted for those

products in systems not using the retrigger by merely

changing the value of R

EXT

and/or C

EXT

.

QUICK REFERENCE DATA

GND = 0 V; T

amb

=25°C; tr=tf= 6 ns

Notes

1. C

PD

is used to determine the dynamic power dissipation (PD in µW):

PD=CPD× V

CC

2

× fi+∑(CL× V

CC

2

× fo) + 0.33 × C

EXT

× V

CC

2

× fo+ D × 28 × VCCwhere:

fi= input frequency in MHz; fo= output frequency in MHz

∑ (CL× V

CC

2

× fo) = sum of outputs

C

EXT

= timing capacitance in pF; CL= output load capacitance in pF

VCC= supply voltage in V; D = duty factor in %

2. For HC the condition is VI= GND to V

CC

For HCT the condition is VI= GND to VCC− 1.5 V

SYMBOL PARAMETER CONDITIONS

TYPICAL

UNIT

HC HCT

propagation delay C

L

= 15 pF; VCC=5 V;

R

EXT

=5 kΩ; C

EXT

= 0 pF

t

PHL

nA, nB, nRD to nQ, nQ 2932ns

t

PLH

nA, nB, nRD to nQ, nQ 3536ns

C

I

input capacitance 3.5 3.5 pF

C

PD

power dissipation capacitance per package notes 1 and 2 90 96 pF

December 1990 3

Philips Semiconductors Product specification

Dual non-retriggerable monostable

multivibrator with reset

74HC/HCT221

ORDERING INFORMATION

See

“74HC/HCT/HCU/HCMOS Logic Package Information”

.

PIN DESCRIPTION

PIN NO. SYMBOL NAME AND FUNCTION

1, 9 1

A, 2A trigger inputs (negative-edge triggered)

2, 10 1B, 2B trigger inputs (positive-edge triggered)

3, 11 1

RD, 2R

D

direct reset inputs (active LOW)

4, 12 1

Q, 2Q outputs (active LOW)

72R

EXT/CEXT

external resistor/capacitor connection

8 GND ground (0 V)

13, 5 1Q, 2Q outputs (active HIGH)

14, 6 1C

EXT

, 2C

EXT

external capacitor connection

15 1R

EXT/CEXT

external resistor/capacitor connection

16 V

CC

positive supply voltage

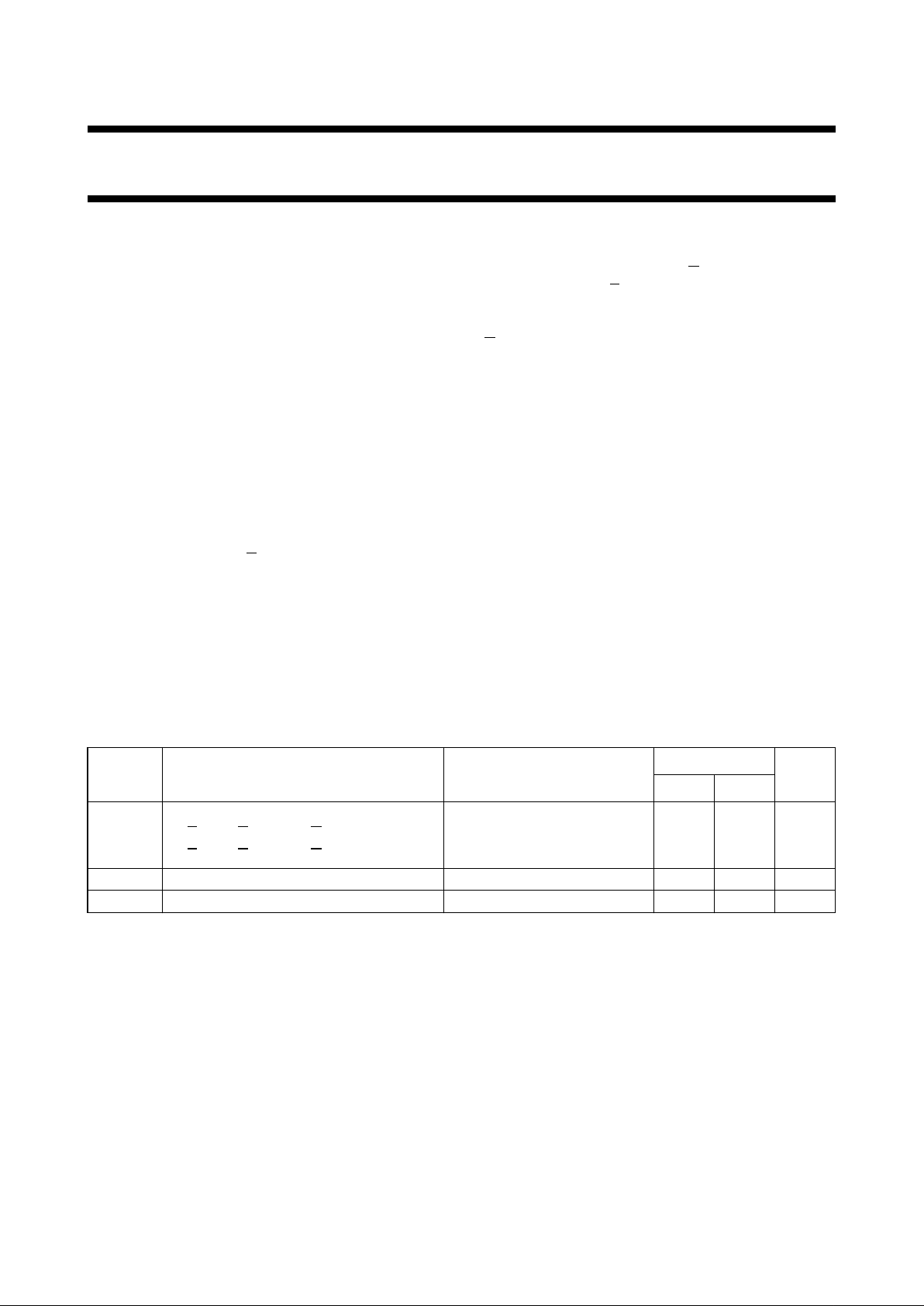

Fig.1 Pin configuration. Fig.2 Logic symbol. Fig.3 IEC logic symbol.

December 1990 4

Philips Semiconductors Product specification

Dual non-retriggerable monostable

multivibrator with reset

74HC/HCT221

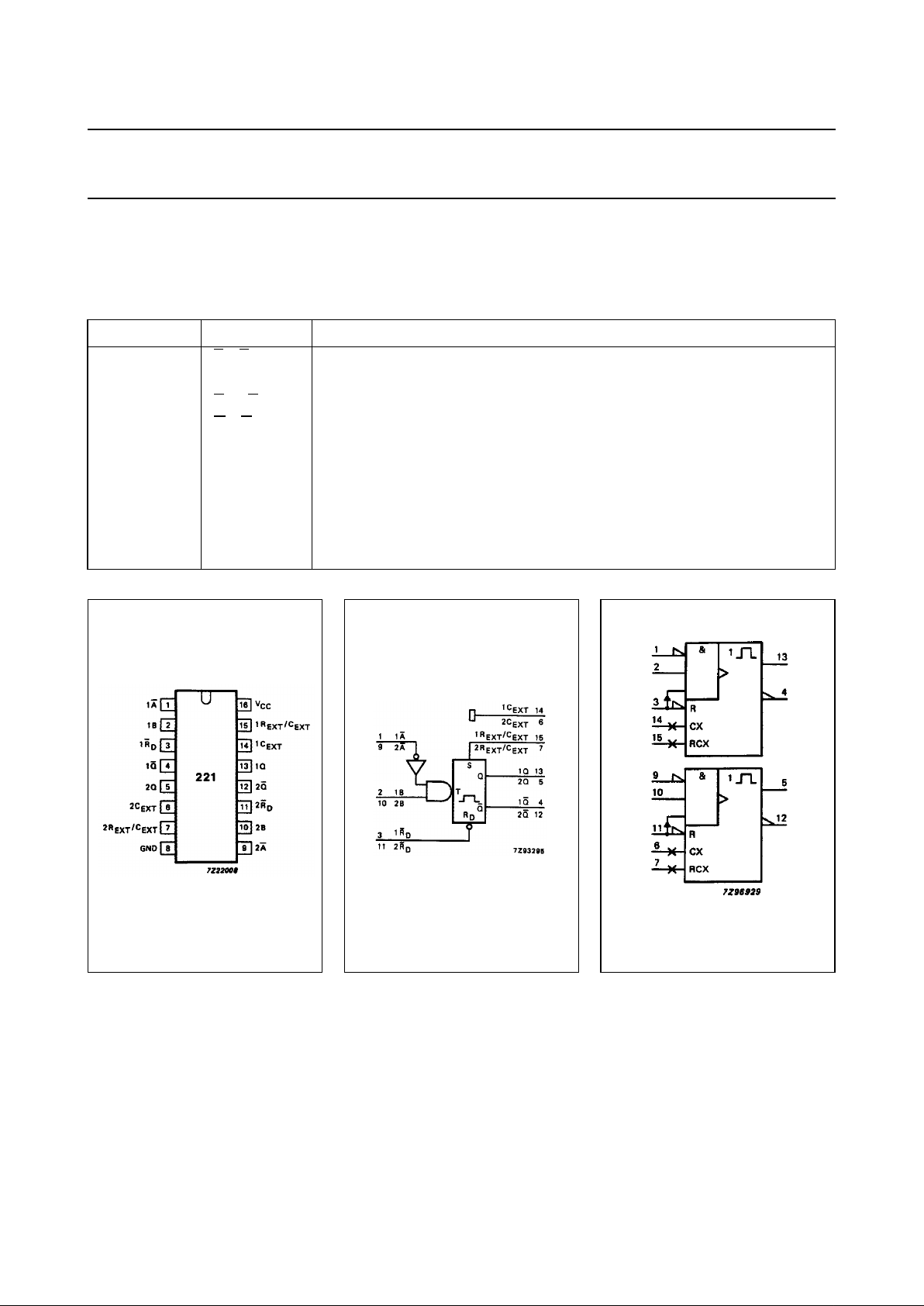

Fig.4 Functional diagram.

FUNCTION TABLE

Notes

1. H = HIGH voltage level

L = LOW voltage level

X = don’t care

↑ = LOW-to-HIGH level

↓ = HIGH-to-LOW level

= one HIGH-level output pulse

= one LOW-level output pulse

2. If the monostable was triggered before this condition

was established the pulse will continue as

programmed.

3. For this combination the reset input must be LOW and

the following sequence must be used:

pin 1 (or 9) must be set HIGH or pin 2 (or 10) set LOW;

then pin 1 (or 9) must be LOW and pin 2 (or 10) set

HIGH. Now the reset input goes from LOW-to-HIGH

and the device will be triggered.

INPUTS OUTPUTS

nR

D

nAnBnQnQ

LXXLH

XHXL

(2)

H

(2)

XXLL

(2)

H

(2)

HL↑

H↓H

↑LH

(3) (3)

December 1990 5

Philips Semiconductors Product specification

Dual non-retriggerable monostable

multivibrator with reset

74HC/HCT221

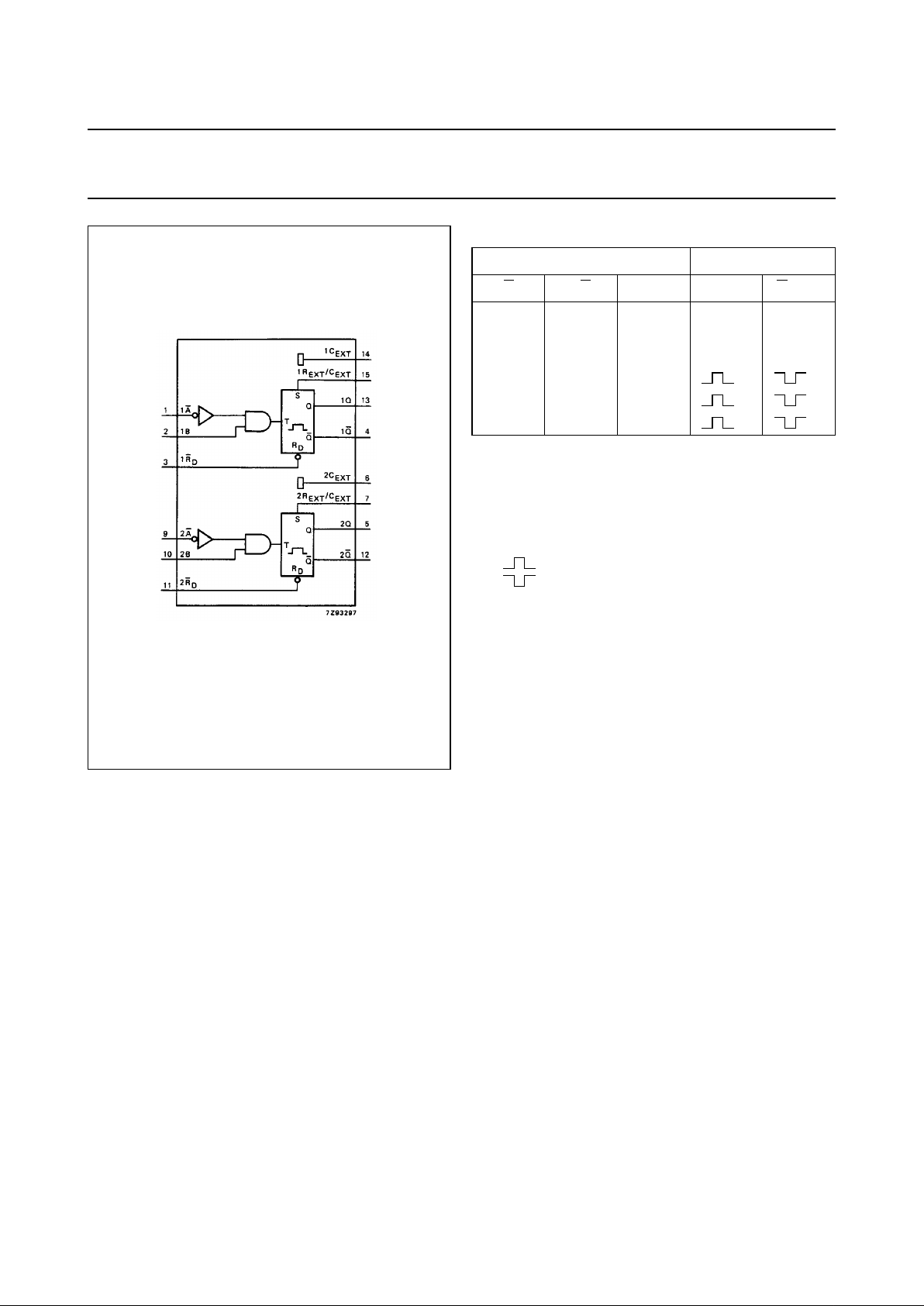

Note

It is recommended to ground pins 6 (2C

EXT

) and 14 (1C

EXT

) externally to pin 8 (GND).

Fig.5 Logic diagram.

Fig.6 Timing component connections.

Loading...

Loading...