NEC UPD98404GJ-KEU Datasheet

DATA SHEET

MOS INTEGRATED CIRCUIT

µµµµ

PD98404

ADVANCED ATM SONET FRAMER

DESCRIPTION

The µPD98404 NEASCOT-P30TM is an LSI for ATM applications, which can be used in ATM adapter boards for

connecting PCs or workstations to an ATM network and can also be used in ATM hubs and ATM switches. This LSI

provides the TC sub-layer functions in the SONET/SDH-base physical layer within the ATM protocol defined by the

ATM Forum’s UNI3.1 recommendations.

This product’s main functions include transmission functions such as mapping of ATM cells sent from the ATM

layer to the payload field in a 155 Mbps SONET STS-3c/SDH STM-1 frame and transmission to PMD (Physical Media

Dependent) sub-layer in the physical layer. Its reception functions include separation of the overhead from the ATM

cells in data streams received from PMD sub-layer and transmission of the ATM cells to the ATM layer. In addition,

this LSI includes a clock recovery function that extracts a reception sync clock from bit streams in received data and

a clock synthesis function that generates a clock for transmissions.

Detailed function descriptions are provided in the following user’s manuals. Be sure to read them before

designing.

µµµµ

PD98404 User’s Manual: S11821E

FEATURES

• On-chip clock recovery/clock synthesis functions

• Provides TC sub-layer function for the ATM protocol’s physical layer

• Supported frame formats include 155 Mbps SONET STS-3c/SDH STM-1

• Conforms to ATM Forum UTOPIA interface Level 2 V1.0 (af-phy-0039.000 June 1995)

Supports three UTOPIA interfaces:

•

Single PHY octet-level handshaking

•

Single PHY cell-level handshaking

•

Multi PHY mode

• Selectable to drop/bypass unassigned cells

• On-chip internal loopback functions for PMD layer loopback and ATM layer loopback

• Supports two PMD interfaces: serial and parallel

•

155.52 Mbps serial interface

•

19.44 MHz parallel interface

• Provides registers for writing/reading overhead information

SOH (section overhead) :J0 byte, Z0 (first and second) bytes, F1 byte

LOH (line overhead) :K1 byte, K2 byte

POH (path overhead) :F2 byte, C2 byte, H4 byte

• Provides pseudo error frame transmit function for various errors

• Supports JTAG boundary scan test function (IEEE 1149.1)

• CMOS technology

• +3.3 V single power supply

The information in this document is subject to change without notice. Before using this document, please

confirm that this is the latest version.

Not all devices/types available in every country. Please check with local NEC representative for

availability and additional information.

Document No. S11822EJ4V0DS00 (4th edition)

Date Published May 2000 N CP(K)

Printed in Japan

The mark shows major revised points.

©

1997, 1999

µµµµ

• Provides abundant OAM (Operation and Maintenance) functions

Transmit side

• Transmission of various alarm data

* Source-triggered automatic loopback transmission

Line RDI, Path RDI

Line REI, Path REI

* Command-specified transmission

Line AIS, Path AIS

• Pseudo error generation frame transmit functions

LOS generated frame

OOF, LOF generated frame

LOP generated frame

OCD, LCD generated frame

B1 error generated frame

B2 error generated frame

B3 error generated frame

Receive side

• Detection of alarm and fault signals

LOS (Loss Of Signal)

OOF (Out Of Frame)

LOF (Loss Of Frame)

LOP (Loss Of Pointer)

OCD (Out of Cell Delineation)

LOC (Loss Of Cell delineation)

Line RDI, Path RDI

Line AIS, Path AIS

• Detection and display of quality loss sources

B1 error, B2 error, B3 error,

Line REI, Path-REI

• On-chip error counters

B1 byte error counter (16-bit)

B2 byte error counter (20-bit)

B3 byte error counter (16-bit)

Line REI error counter (20-bit)

Path REI error counter (16-bit)

Rx Frequency justification processing counter (12-bit)

HEC error drop cell counter (20-bit)

FIFO overflow drop cell counter (20-bit)

Idle cell counter (20-bit)

PD98404

ORDERING INFORMATION

Part number Package

PD98404GJ-KEU 144-pin plastic QFP (fine pitch) (20 × 20 mm)

µ

2

Data Sheet S11822EJ4V0DS00

µµµµ

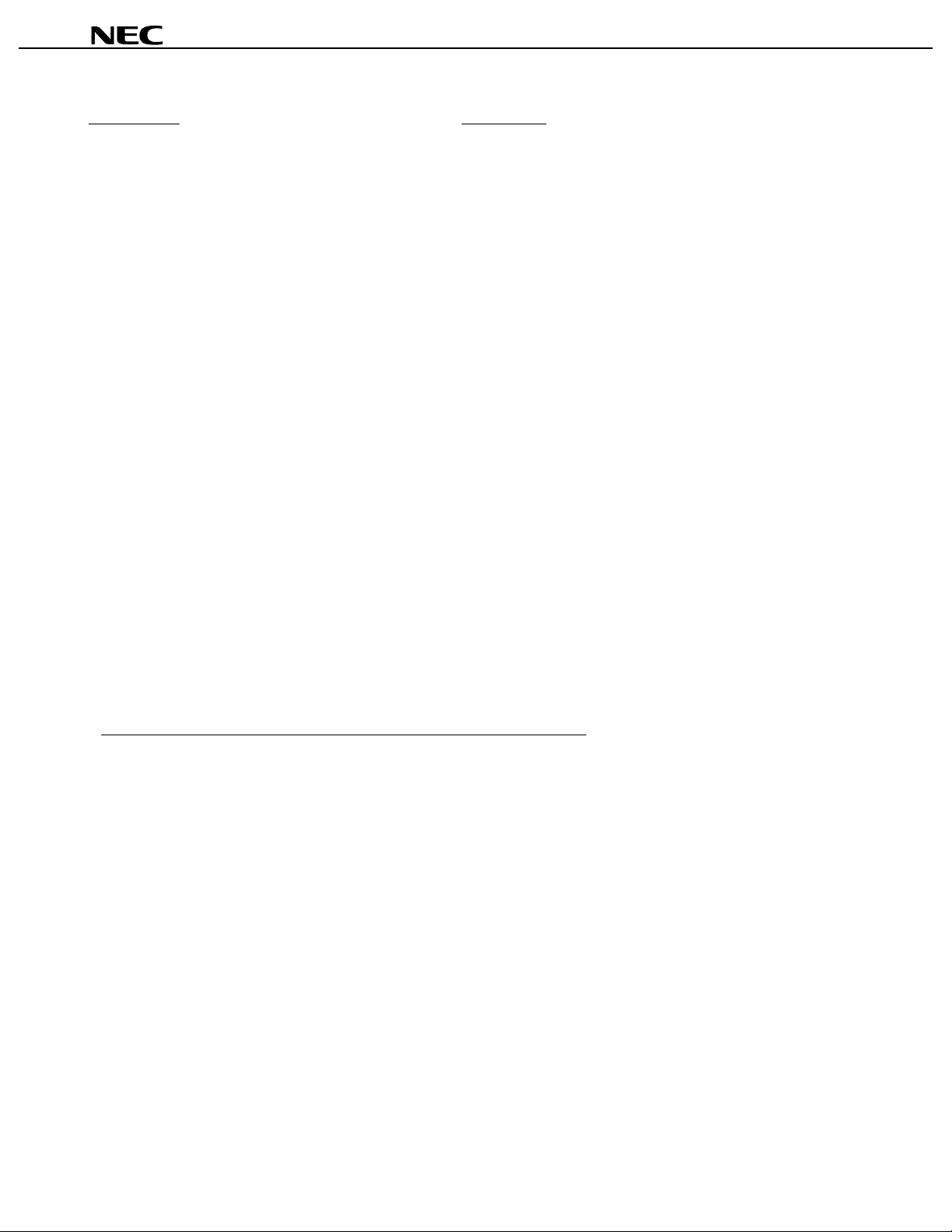

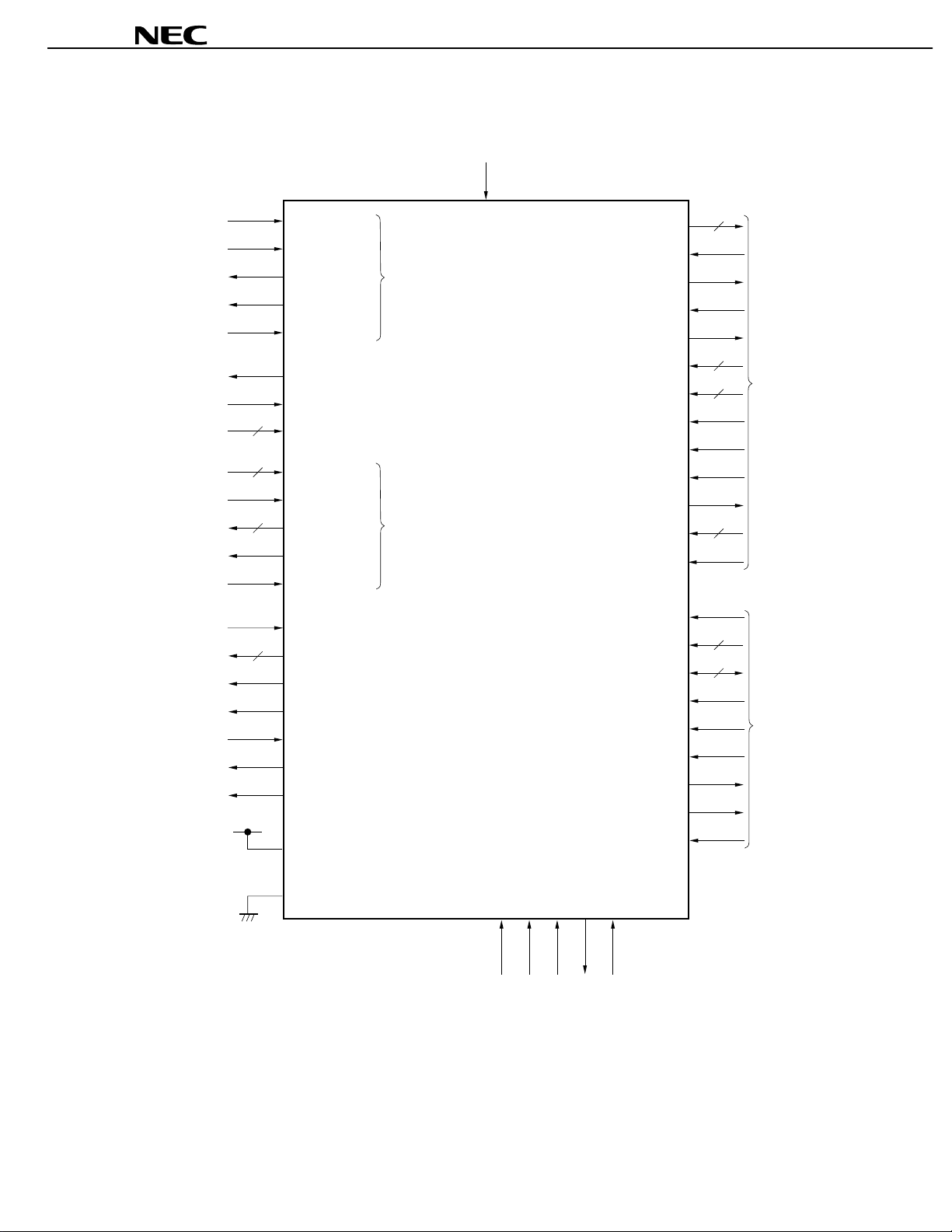

SYSTEM CONFIGURATION EXAMPLE

The following is an example of a system configuration using the µPD98404.

ATM adapter card application

PD98404

Control

memory

Microprocessor

SAR chip

µ

PD98401A

NEASCOT-S15

Bus bridge

Hub (terminal side) application

PHY chip

µ

TM

PD98404

NEASCOT-P30

Oscillator

Oscillator

Optical fiber

transceiver

/receiver

19.44 MHz

Switch device

µ

PD98412

NEASCOT-X15

µ

PD98404

NEASCOT-P30

TM

µ

PD98404

NEASCOT-P30

UTOPIA Level2

Data Sheet S11822EJ4V0DS00

Optical fiber

transceiver

/receiver

Optical fiber

transceiver

/receiver

3

4

µ

µµ

µ

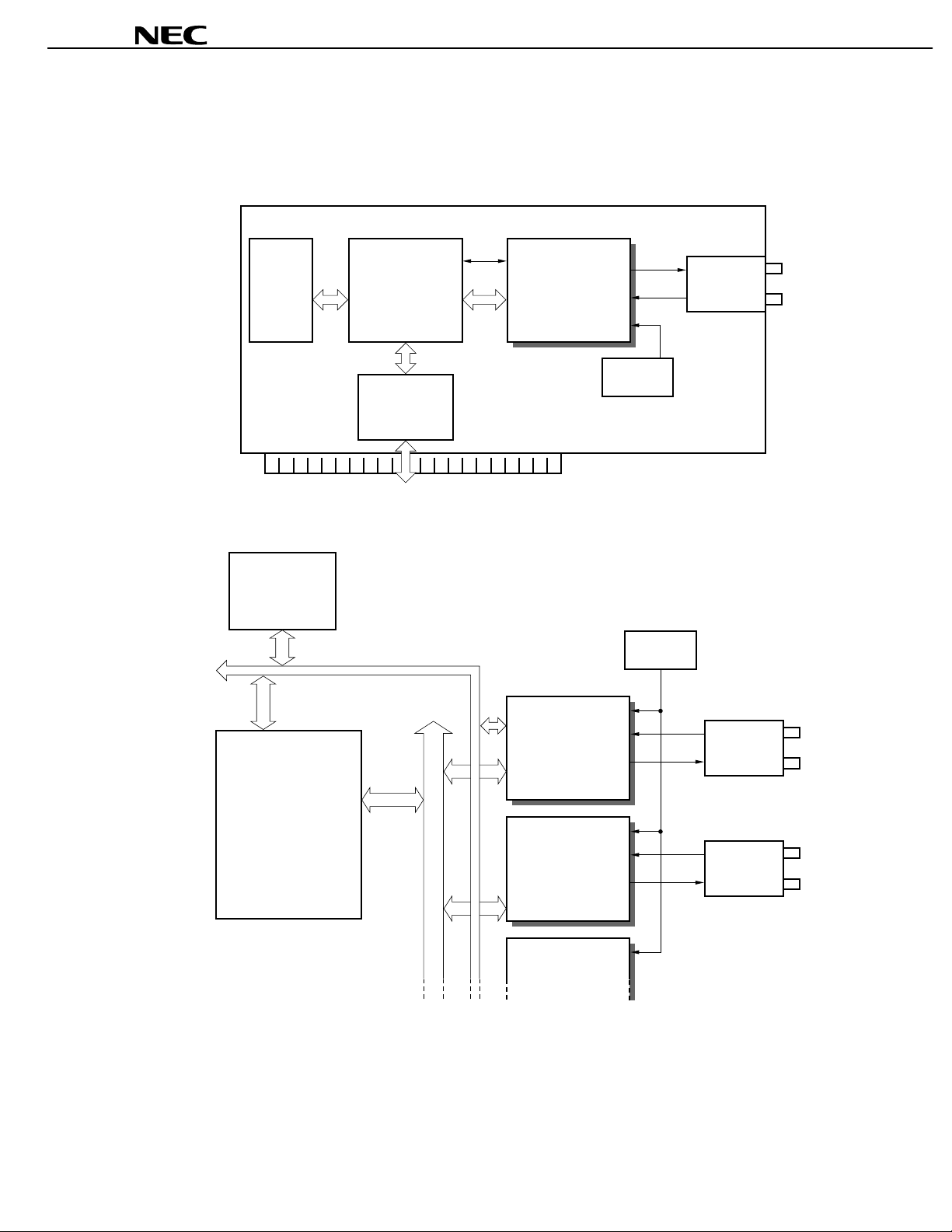

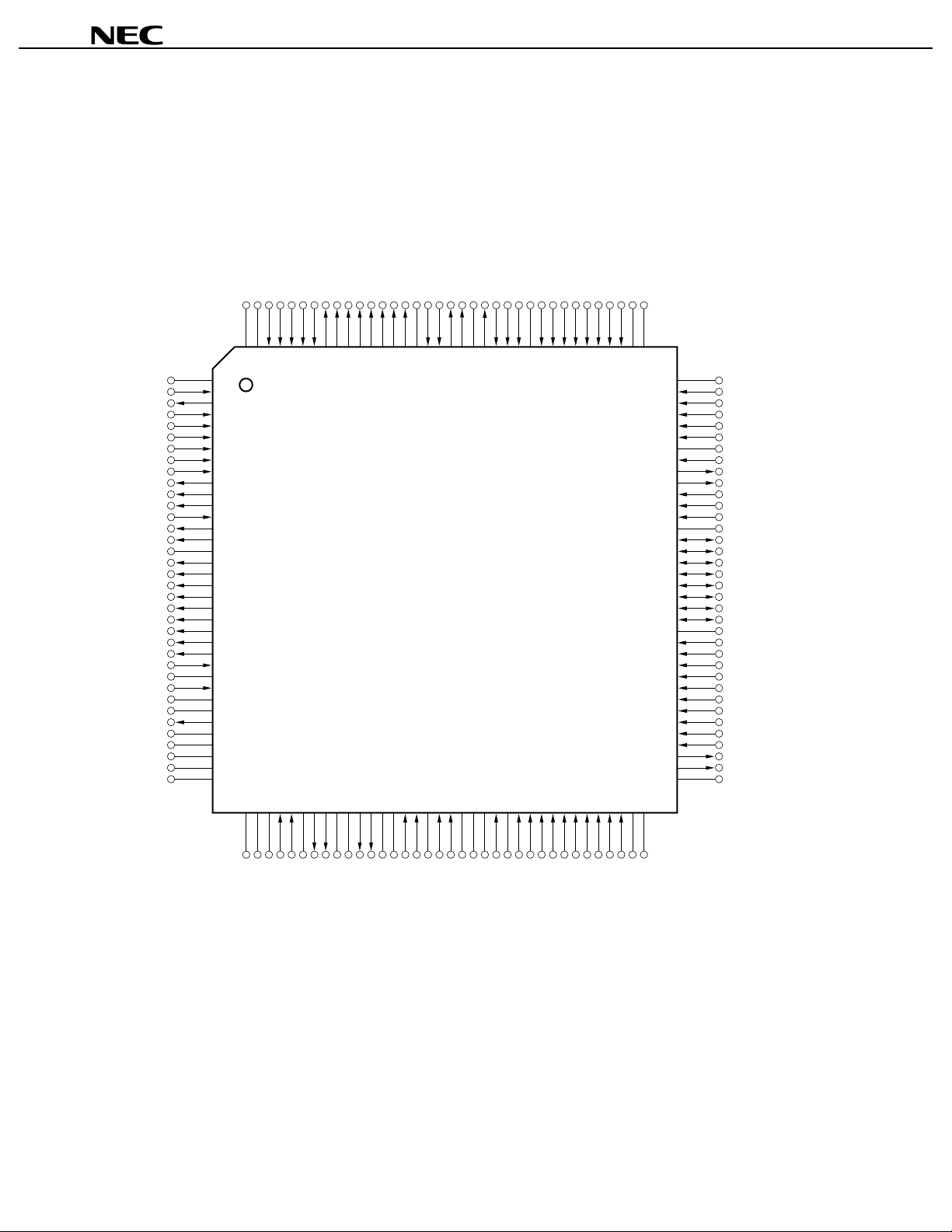

BLOCK DIAGRAM

PMD interface signal

Data Sheet S11822EJ4V0DS00

Clock recovery

& clock synthesizer

& PMD layer interface

Serial to

parallel

Parallel to

serial

BIP generator

(transmit side)

BIP generator

(receive side)

Frame

synchronization

(A1, A2)

+

Transmission overhead

processor

(A1, A2, K2, Z2,

G1, H1, H2, H3)

Transmission

timing generator

Pointer processor

Descrambler

Scrambler

+

Reception overhead

processor

(K2, Z2, G1, H1, H2, H3)

OAM controller

(performance register, etc.)

Cell

synchronization

HEC verification

HEC correction

Cell

scrambler

Cell

descrambler

HEC

generator

Transmission

overhead registers

(J0, Z0, C2, K2,etc.)

Reception

overhead registers

(J0, Z0, C2, K2, etc.)

Interrupt source

register

Mode register

Rx FIFO,

7 cells

Tx FIFO,

7 cells

ATM layer interface

Controller interface

UTOPIA interface signal

Management interface signal

PD98404

µµµµ

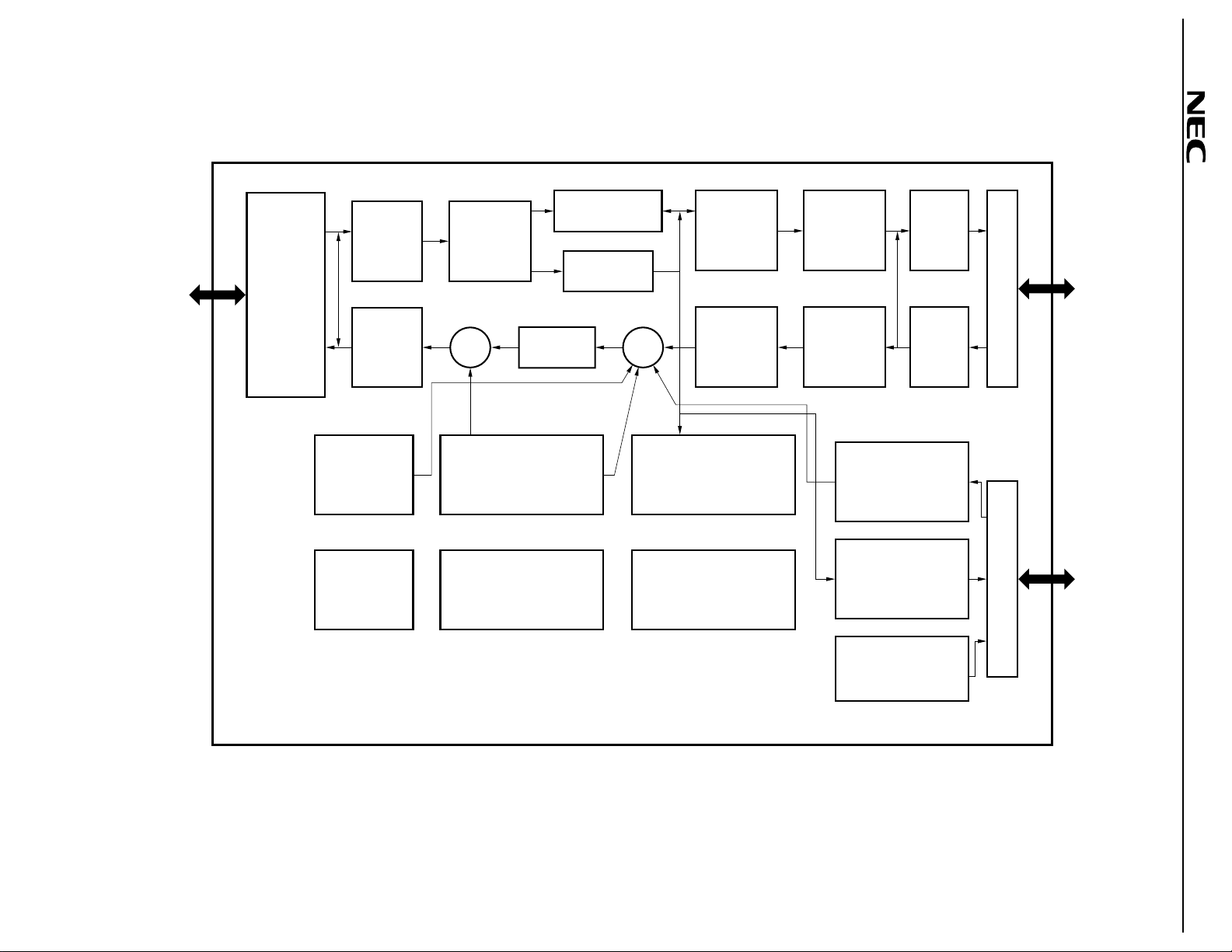

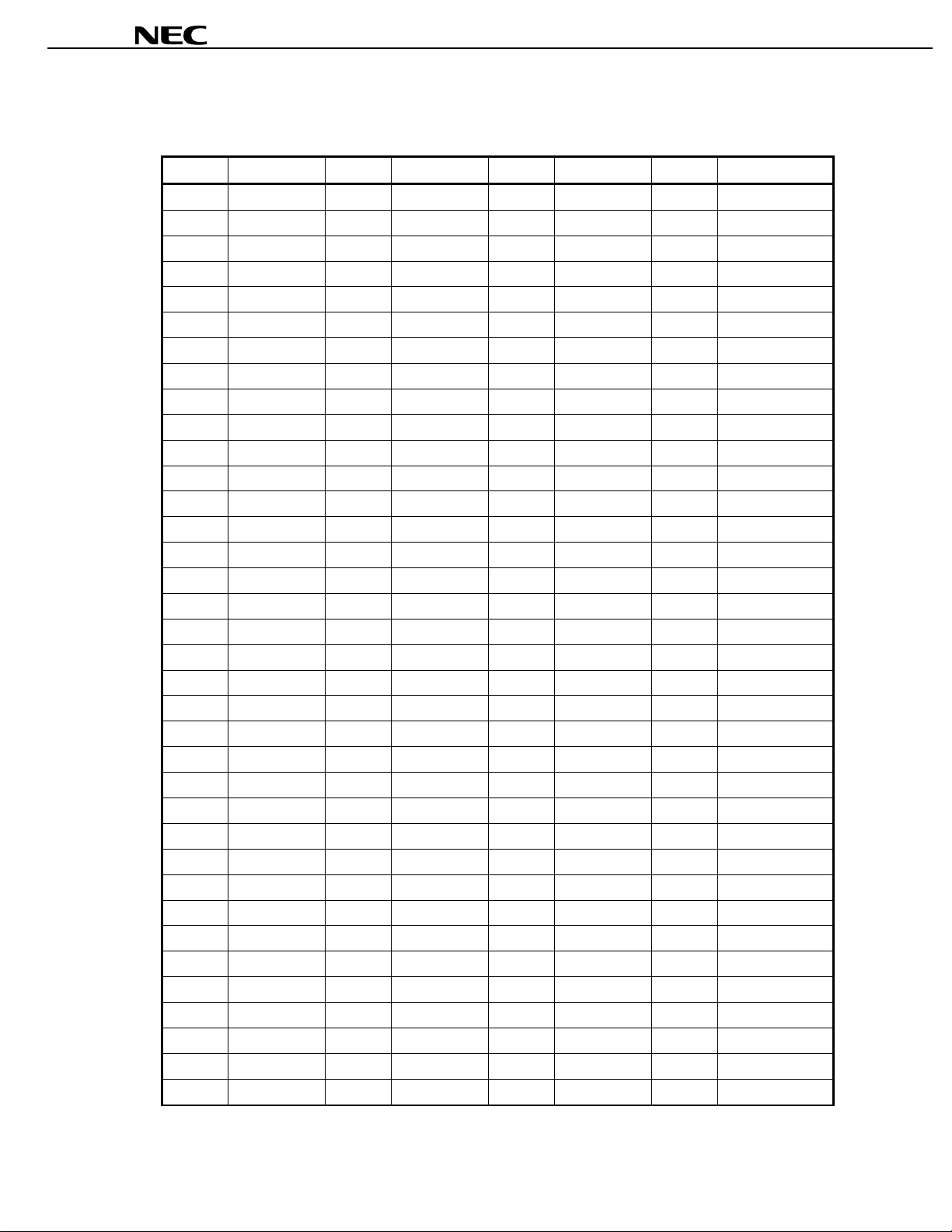

PIN CONFIGURATION

PMD interface

PD98404

Test interface

Power

supply, GND

RDIT, RDIC

RCIT, RCIC

TDOT, TDOC

TCOT, TCOC

TFKT, TFKC

AIN1

REFCLK

PSEL0, PSEL1

2

RPD0 - RPD7

8

RPC

TPD0 - TPD7

8

TPC

TFC

PMDALM

PHYALM0 - PHYALM2

3

RxFP

TxFP

TFSS

RCL

TCL

VDD, VDD-TPE, VDD-RPE

VDD-SP, VDD-CS, VDD-CR

GND, GND-TPE, GND-RPE

GND-SP, GND-CS, GND-CR

Serial

Parallel

TEST0 - TEST2

JRST_B

JMS

JCK

RDO0 - RDO7

RCLK

RSOC

RENBL_B

EMPTY_B/RCLAV

RADD0-RADD4

TDI0 - TDI7

TCLK

TSOC

TENBL_B

FULL_B/TCLAV

TADD0 - TADD4

UMPSEL

MSEL

MADD0 - MADD6

MD0 - MD7

CS_B

DS_B/RD_B

R/W_B/WR_B

ACK_B/RDY_B

PHINT_B

RESET_B

JDO

JDI

8

5

8

5

7

8

ATM

layer interface

Management

interface

Remark

JTAG boundary scan interface

Active low pins are indicated with the suffix “_B” in this document.

Data Sheet S11822EJ4V0DS00

5

µµµµ

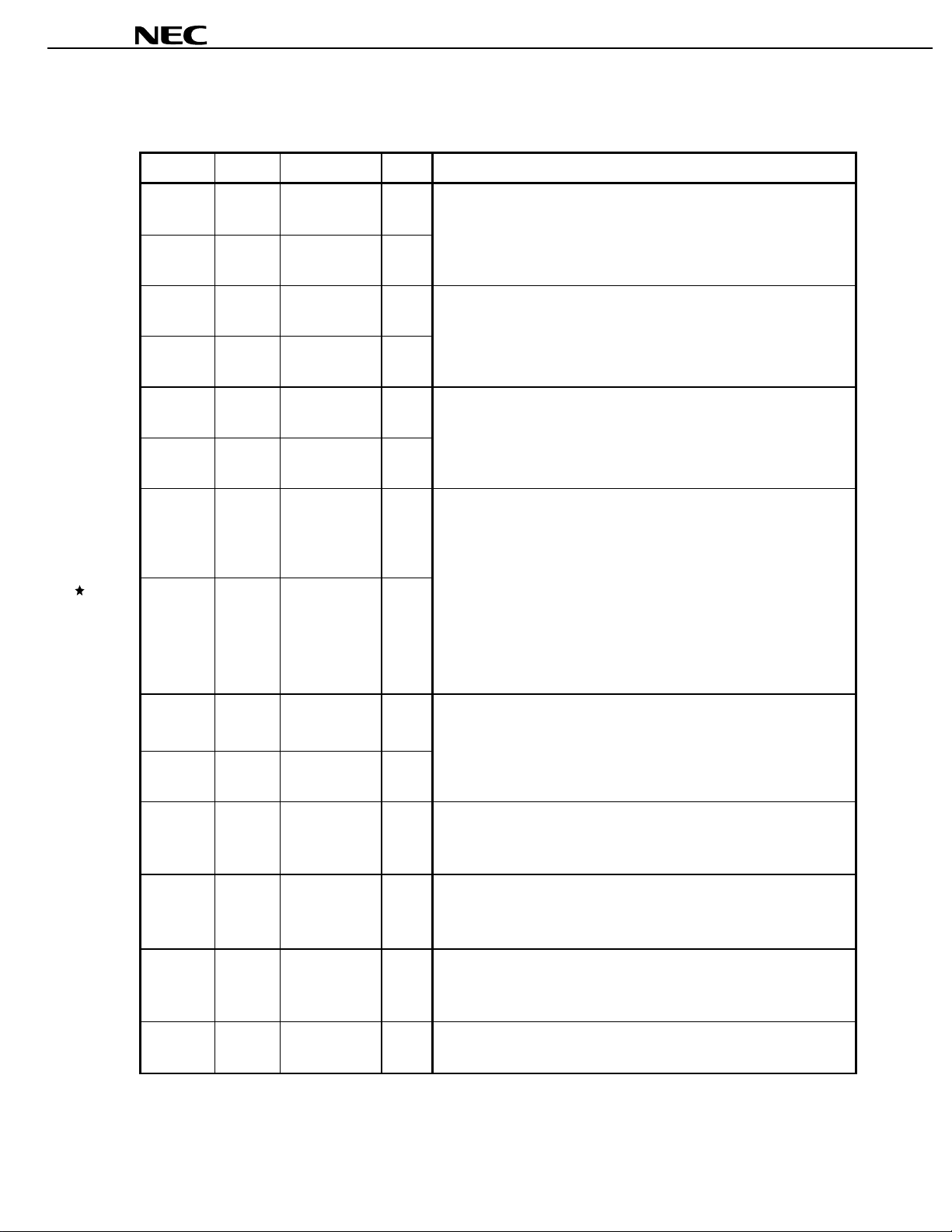

PIN CONFIGURATION (TOP VIEW)

PD98404

144-pin plastic QFP (fine pitch) (20

GND

GND

RADD4

RADD3

RADD2

RADD1

144

143

142

141

140

VDD

JCK

JDO

JDI

JMS

JRST_B

TEST0

TEST1

TEST2

PHYALM0

PHYALM1

PHYALM2

TFSS

TxFP

TCL

GND

TPD0

TPD1

TPD2

TPD3

TPD4

TPD5

TPD6

TPD7

TPC

TFC

VDD

REFCLK

GND-CS

GND-CS

AIN1

VDD-CS

VDD-CS

GND-CS

VDD-SP

VDD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

3738394041424344454647484950515253545556575859606162636465666768697071

139

20 mm)

××××

RADD0

RDO7

RDO6

138

137

136

RDO5

RDO4

135

134

RDO3

RDO2

133

132

RDO1

RDO0

131

130

VDD

129

RCLK

128

RENBL_B

RSOC

EMPTY_B/RCLAV

GND

127

126

125

124

FULL_B/TCLAV

TSOC

TENBL_B

TCLK

VDD

123

122

121

120

119

TDI7

118

TDI6

117

TDI5

116

TDI4

115

TDI3

114

TDI2

113

TDI1

112

TDI0

111

GND

110

GND

109

72

108

107

106

105

104

103

102

101

100

VDD

TADD4

TADD3

TADD2

TADD1

TADD0

GND

RESET_B

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

PHINT_B

ACK/RDY_B

R/W_B/WR_B

DS_B/RD_B

CS_B

VDD

MD7

MD6

MD5

MD4

MD3

MD2

MD1

MD0

GND

UMPSEL

MADD6

MADD5

MADD4

MADD3

MADD2

MADD1

MADD0

MSEL

PMDALM

RCL

RxFP

VDD

RPC

VDD-CR

GND-CR

GND-RPE

VDD

RPD0

RPD1

RPD2

RPD3

RPD4

RPD5

RPD6

RPD7

PSEL0

PSEL1

GND

GND

GND

TFKT

TFKC

TCOT

GND-SP

VDD-TPE

TCOC

GND-TPE

VDD-TPE

GND-TPE

6

RCIT

RDIT

RCIC

TDOT

TDOC

VDD-TPE

GND-RPE

RDIC

VDD-RPE

Data Sheet S11822EJ4V0DS00

µµµµ

PIN ALLOCATION

Number Pin name Number Pin name Number Pin name Number Pin name

1 VDD 37 GND 73 VDD 109 GND

2 JCK 38 GND-SP 74 RxFP 110 GND

3 JDO 39 VDD-TPE 75 RCL 111 TDI0

4 JDI 40 TFKT 76 PMDALM 112 TDI1

5 JMS 41 TFKC 77 MSEL 113 TDI2

6 JRST_B 42 GND-TPE 78 MADD0 114 TDI3

7 TEST0 43 TCOT 79 MADD1 115 TDI4

8 TEST1 44 TCOC 80 MADD2 116 TDI5

9 TEST2 45 VDD-TPE 81 MADD3 117 TDI6

10 PHYALM0 46 GND-TPE 82 MADD4 118 TDI7

11 PHYALM1 47 TDOT 83 MADD5 119 VDD

12 PHYALM2 48 TDOC 84 MADD6 120 TCLK

13 TFSS 49 VDD-TPE 85 UMPSEL 121 TENBL_B

14 TxFP 50 GND-RPE 86 GND 122 TSOC

15 TCL 51 RCIT 87 MD0 123 FULL_B/TCLAV

16 GND 52 RCIC 88 MD1 124 GND

17 TPD0 53 VDD-RPE 89 MD2 125 EMPTY_B/RCLAV

18 TPD1 54 RDIT 90 MD3 126 RSOC

19 TPD2 55 RDI C 91 MD4 127 RENBL_B

20 TPD3 56 GND-RPE 92 MD5 128 RCLK

21 TPD4 57 GND-CR 93 MD6 129 VDD

22 TPD5 58 VDD-CR 94 MD7 130 RDO0

23 TPD6 59 RPC 95 VDD 131 RDO1

24 TPD7 60 VDD 96 CS_B 132 RDO2

25 TPC 61 RPD0 97 DS_B/RD_B 133 RDO3

26 TFC 62 RPD1 98 R/W_B/WR_B 134 RDO4

27 VDD 63 RPD2 99 ACK_B/RDY_B 135 RDO5

28 REFCLK 64 RPD3 100 PHINT_B 136 RDO6

29 GND-CS 65 RPD4 101 RESET_B 137 RDO7

30 GND-CS 66 RPD5 102 GND 138 RADD0

31 AIN1 67 RPD6 103 TADD0 139 RADD1

32 VDD-CS 68 RPD7 104 TADD1 140 RADD2

33 VDD-CS 69 PSEL0 105 TADD2 141 RADD3

34 GND-CS 70 PSEL1 106 TADD3 142 RADD4

35 VDD-SP 71 GND 107 TADD4 143 GND

36 VDD 72 GND 108 VDD 144 GND

PD98404

Data Sheet S11822EJ4V0DS00

7

µµµµ

PIN NAMES

PD98404

ACK_B : Read/write Cycle Receive Acknowledge

AIN1 : External Filt er Connection

CS : Chip Select

DS_B : Data Strobe

EMPTY_B : Output Buffer Empty

FULL_B : Buffer Full

GND : Ground

GND-RPE : Ground for Receive PECL Buffer

GND-CR : Ground for Clock Recovery Circuit

GND-CS : Ground for Cloc k Synthesis

GND-SP : Ground for Serial/Parallel Circuit

GND-TPE : Ground for Transmit PECL Buffer

JCK : JTAG Clock

JDI : JTAG Data Input

JDO : JTAG Data Output

JMS : JTAG Mode Selec t

JRST_B : JTAG Reset

MADD0-MADD6 : Management Interface Address Bus

MD0-MD7 : Management Int erface Data Bus

MSEL : Management Int erface Mode Select

PHINT_B : Physical Interrupt

PH Y A L M 0 - : PHY Alarm Detection

PHYALM2

PMDALM : PMD Device Al arm

PSEL0, PSEL1 : PMD Mode Select

RADD0-RADD4 : R eceive PHY Device Address

RCIC : Receive Cl ock Input Complement

RCIT : Receive Clock Input True

RCL : Internal Receive System Clock

RCLAV : Receive Cell Available

RCLK : Receive Data Transferring Clock

RD_B : Read Select

RDIC : Receive Dat a Input Complement

RDIT : Receive Data Input True

RDO0-RDO7 : Receive Data Output

REFCLK : System Cl ock

RENBL_B : Receive Data Enable

RESET_B : Sys tem Reset

RPC : Receive Parallel Data Clock

RPD0-RPD7 : Receive Parallel Data

RSOC : Receive Start Address of ATM Cell

RxFP : Receive Frame Pulse

R/W_B : Read/write Control

TADD0-TADD4 : Transmit PHY Devic e Address

TCL : Internal Transmit System Clock

TCLAV : Transmit Cell Available

TCLK : Tr ansmit Data Transferring Clock

TCOC : Transmit Clock Output Complement

TCOT : Transmit Clock Output True

TDI0-TDI7 : Transmit Data Input from the ATM Layer

TDOC : Transmit Data Output Complement

TDOT : Transmit Data Output True

TENBL_B : Transmit Data Enable

TEST0-TEST2 : Test Mode Pin

TFC : Transmit Reference Clock

TFKC : Transmit Referenc e Clock Complement

TFKT : Transmit Reference Cloc k True

TFSS : Tr ansmit Frame Set Signal

TPC : Transmit Parallel Data Clock

TPD0-TPD7 : Transmit Parallel Data

TSOC : Transmit Start Address of ATM Cell

TxFP : Transmit Frame Pulse

UMPSEL : Utopi a Multi-PHY Mode Select

VDD : Supply Voltage for Logi c Circuit

VDD-RPE : Voltage Supply for Receive PECL Buffer

VDD-CR : Voltage Supply for Clock Recovery Cir cuit

VDD-CS : Voltage Supply for Clock Sy nthesis

VDD-SP : Voltage Supply for Serial/Parallel Circ uit

VDD-TPE : Voltage Supply for Transmit PECL Buffer

WR_B : Write Select

RDY_B : Ready Si gnal

8

Data Sheet S11822EJ4V0DS00

µµµµ

1. PIN FUNCTIONS

PD98404

1.1 PMD Interface

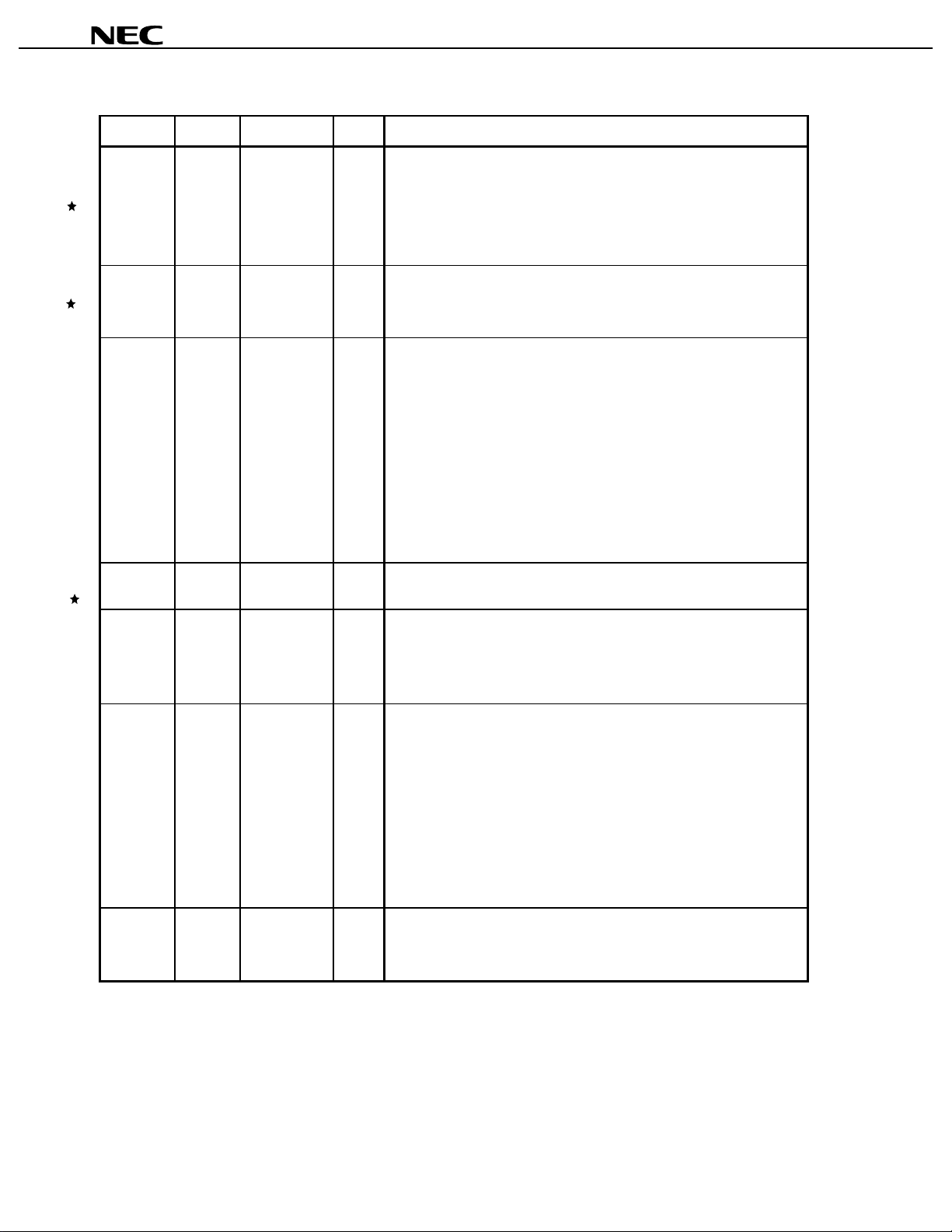

Pin name Pin No. I/O level I/O Function

RDIT 5 4 P-ECL

True(+)

RDIC 55 P-ECL

Complement(-)

RCIT 51 P-ECL

True(+)

RCIC 52 P-ECL

Complement(-)

TDOT 47 P-ECL

True(+)

TDOC 48 P-ECL

Complement(-)

TCOT 43 P-ECL

True(+)

TCOC 44 P-ECL

Complement(-)

I

Serial receiv e data input. When PSEL [1:0] is set to 00, the data is

sampled on a clock recovered by the internal clock recovery PLL.

When PSEL [1:0] is set to 01, the data is sampled on the cloc k input

I

to RCIT/RCIC.

I

Serial receiv e clock input (155.52 MHz).

When PSEL [1:0] is set to 01, the input is used as a receive c lock.

I

O

Serial transmit data output . The data is output i n sync wit h the risi ng

edge of the serial clock TCOT.

O

O

Serial transmit clock output (155. 52 MHz).

When PSEL [1:0] is set to 00, the clock generated by the internal

synthesizer PLL is output as the t ransmit cloc k. When PSEL [1:0] is

set to 01, the clock supplied to TFKT/TFKC is output.

O

Depending on the mode selected, t he transmit data may be l atched

by the receive cl ock for output. Ev en in suc h a case, t his pin out puts

the clock of the internal synthesizer or the clock input to the

TFKT/TFKC pin in accordance wi th the setti ng of the PSEL[1:0] pins .

It does not output t he receive recov ery clock.

(1/2)

TFKT 40 P-ECL

True(+)

TFKC 41 P-ECL

Complement(-)

RPD0RPD7

RPC 59 TTL* I Parall el receive clock input (19.44 MHz).

TPD0TPD7

TPC 25 TTL* O Parallel transmit clock output . When PSEL [1:0] is set to 1X, thi s pin

61-68 TTL* I Parallel receive data i nput. When PSEL [ 1:0] i s set to 1X, thes e pins

17-24 TTL* O Parallel transmi t data output. When PSEL [ 1:0] is set to 1X t o select

Serial transmit clock input (155. 52 MHz).

I

When PSEL [1:0] is set to 01, the input is used as the transmit clock.

I

input receive dat a. The data is sampled i n sync wi th the ris ing edge

of parallel receive clock RPC.

When PSEL [1:0] is set t o 1X to s elec t paral lel mode, t his pin i nputs a

19.44 MHz receive c lock.

parallel mode, these pi ns output transmit dat a in sync with t he rising

edge of PC.

outputs the clock (19.44 MHz) suppli ed to TFC.

Data Sheet S11822EJ4V0DS00

9

µµµµ

PD98404

(2/3)

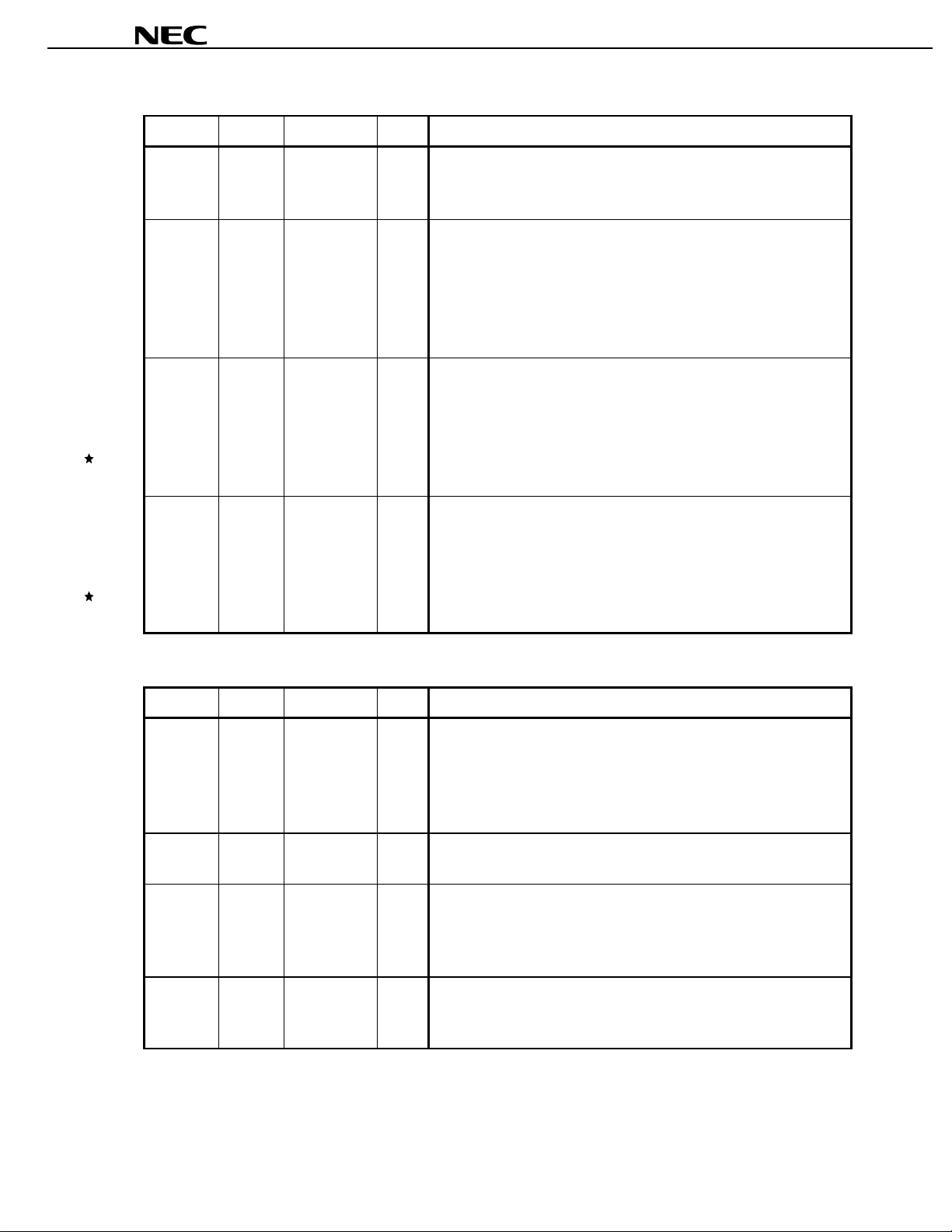

Pin name Pin No. I/O level I/O Function

TFC 26 TTL* I Parallel transmit clock input. When PSEL [1:0] is set to 1X to sel ect

parallel mode, this pin inputs a parallel t ransmit clock of 19.44 MHz.

If the TxCL bits [ 1:0] of the MDR1 register are set to 10 in the ser ial

mode with PSEL[1:0] = “00”, input the 19.44 MHz s ource cloc k of the

internal cloc k synthesiz er PLL.

REFCLK 28 TTL* I Reference clock input. This pin supplies a system clock of 19.44

MHz to the internal clock recovery/synthesizer. Always input this

clock.

PSEL0,

PSEL1

AIN1 31 Analog O

PMDALM 76 TTL* I PMD layer alarm signal input. The si gnal level of t his pin is r eflected

PHYALM0PHYALM2

69, 70 TTL* I PMD interface mode select input. These pins select the interface

mode of the PMD layer to be used.

PSEL [1:0] = 00 :Serial mode. The cl ock generated by the internal

clock recovery/synthesizer PLL is used for

transmission and reception.

PSEL [1:0] = 01 :Serial mode. The clock input of the external

RCIT/RCIC and TFKT/TFKC is used for

transmission and reception.

PSEL [1:0] = 1x:Parall el mode. The clock input of RPC and TFC is

used.

This pin connects the loop filter of the internal synthesizer PLL.

Leave open.

in the state bit of an internal r egister. The transit ion of the bit c an be

used as an interrupt source. The state signal from a peripheral

device is input.

10-12 TTL* O PHY layer alar m detection signal out put. These pins output a signal

indicating that an internally monitored error state (PMDALM,

CMDARM, LOS, OOF, LOF, LOP, OCD, LCD, Line AIS, Path AIS,

Line RDI, or Path RDI) has been detected. The pins c an output an

error either singly or in combination. The type of the error to be

indicated is sel ected by s etting the i nternal AMPR, AMR1, and AMR2

registers.

For details on use, refer to

(PHYALM[2:0], PMDALM)

(S11821E)

.

in

3.5 Alarm Report Pins

µµµµ

PD98404 User’s Manual

RxFP 74 TTL* O Frame pulse output for the recei ve side (8 kHz). This pin outputs a

pulse signal at one-clock intervals in sync with the RCL clock in the

frame synchronization state.

10

Data Sheet S11822EJ4V0DS00

µµµµ

PD98404

(3/3)

Pin name Pin No. I/O level I/O Function

TxFP 14 TTL* O Frame pulse signal output for the transmit side (8 kHz). This pin

outputs a pulse signal at one-clock intervals in sync with the TCL

clock.

TFSS 13 TTL* I Transmit frame output di sable signal input. W hen the signal i s high,

the transmit fr ame output s tops . W hen the s ignal is low, t r ansmi s si on

starts fr om the beginning of a frame. The

signal at the ris ing edge of the TCL cloc k. The tr ansmit frame out put

is resumed at the ninth rising edge of the TCL c lock after the ris ing

edge at which the high lev el of this signal was last detected.

RCL 75 TTL* O Internal system clock output for the receive side (19.44 MHz). This

pin outputs the receive c lock divided by 8. The source r eceive cloc k

depends on the selected mode, which is ei ther t he cl oc k generat ed by

the internal clock recovery PLL or the clock supplied from the

RCIT/RCIC and RFC pins. Cloc k output from t his pi n is s topped whil e

the device is being reset.

PD98404 samples this

µ

TCL 15 TTL* O

1.2

ATM layer interface

Pin name Pin No. I/O level I/O Function

RDO0RDO7

RCLK 128 TTL* I Receive clock input. This pin supplies a clock of up to 40 MHz f or

RSOC 126 TTL* O

130-137 TTL* O

(2 or 3-

state)

(2 or 3-

state)

Internal system clock output of the transmit side (19.44 MHz).

This pin outputs the t ransmit clock divided by 8. The sour ce tr ansmit

clock depends on the selected mode, which is either the clock

generated by the internal sy nthesizer or the cloc k supplied from the

TCIT/TCIC and TFC pins. Cloc k output fr om this pin is stopped whi le

the device is being reset.

(1/2)

Receive data output.

These pins form an 8-bit data bus that output s receive data to an ATM

layer device. The data is out put in sync with the ris ing edge of the

RCLK clock. These pi ns operat e i n two or thr ee s tat es , dependi ng on

the UTOPIA interface mode.

receive data transfer.

Receive cell start position signal output.

This pin outputs a s ignal indicating the posit ion of the first by te of a

receive cell. This pin operates in two or three s tates, depending on

the UTOPIA interface mode.

RENBL_B 127 TTL* I

Receive enable signal input.

This pin inputs a signal indicating that the ATM layer is ready to

receive data.

Data Sheet S11822EJ4V0DS00

11

Loading...

Loading...