DATA SHEET

MOS INTEGRATED CIRCUIT

µ

PD78P4916

16-BIT SINGLE-CHIP MICROCONTROLLER

The µPD78P4916 is one of the µPD784915 subseries in the 78K/IV Series microcontrollers which incorporate

a high-speed and high-performance 16-bit CPU.

The µPD78P4916 replaces mask ROM with one-time PROM and increases on-chip ROM and RAM capacity

µ

compared to the

It is suitable for evaluation at system development and for small quantity production.

Detailed descriptions of functions are provided in the following user's manuals. Be sure to read these

documents when designing.

PD784915.

µ

PD784915 Subseries User’s Manual – Hardware : U10444E

78K/IV Series User's Manual – Instruction : U10905E

FEATURES

High-speed instruction execution using 16-bit CPU core

• Minimum instruction execution time: 250 ns (at 8-MHz internal clock)

On-chip high capacity memory

• PROM : 62 Kbytes

• RAM : 2048 bytes

Note It is possible to change the capacity of the internal PROM and the internal RAM by specifying the internal

memory capacity select (IMS) register.

ORDERING INFORMATION

Part Number Package

µ

PD78P4916GF-3BA 100-pin plastic QFP (14 × 20 mm)

Note

Note

The information in this document is subject to change without notice.

Document No. U11045EJ1V0DS00 (1st edition)

Date Published April 1996 P

Printed in Japan

The mark * shows major revised points.

©

1996

78K/IV Series Products

µ

PD78138

Subseries

78K/I Series

µ

PD78148

Subseries

Enhanced peripheral

hardware

78K/IV Series

µ

PD78P4916

PD784915

m

PD784915

µ

Subseries

Subseries

High-performance 16-bit CPU core

High-speed operation

On-chip analog circuit for VCR

2

µ

PD78P4916

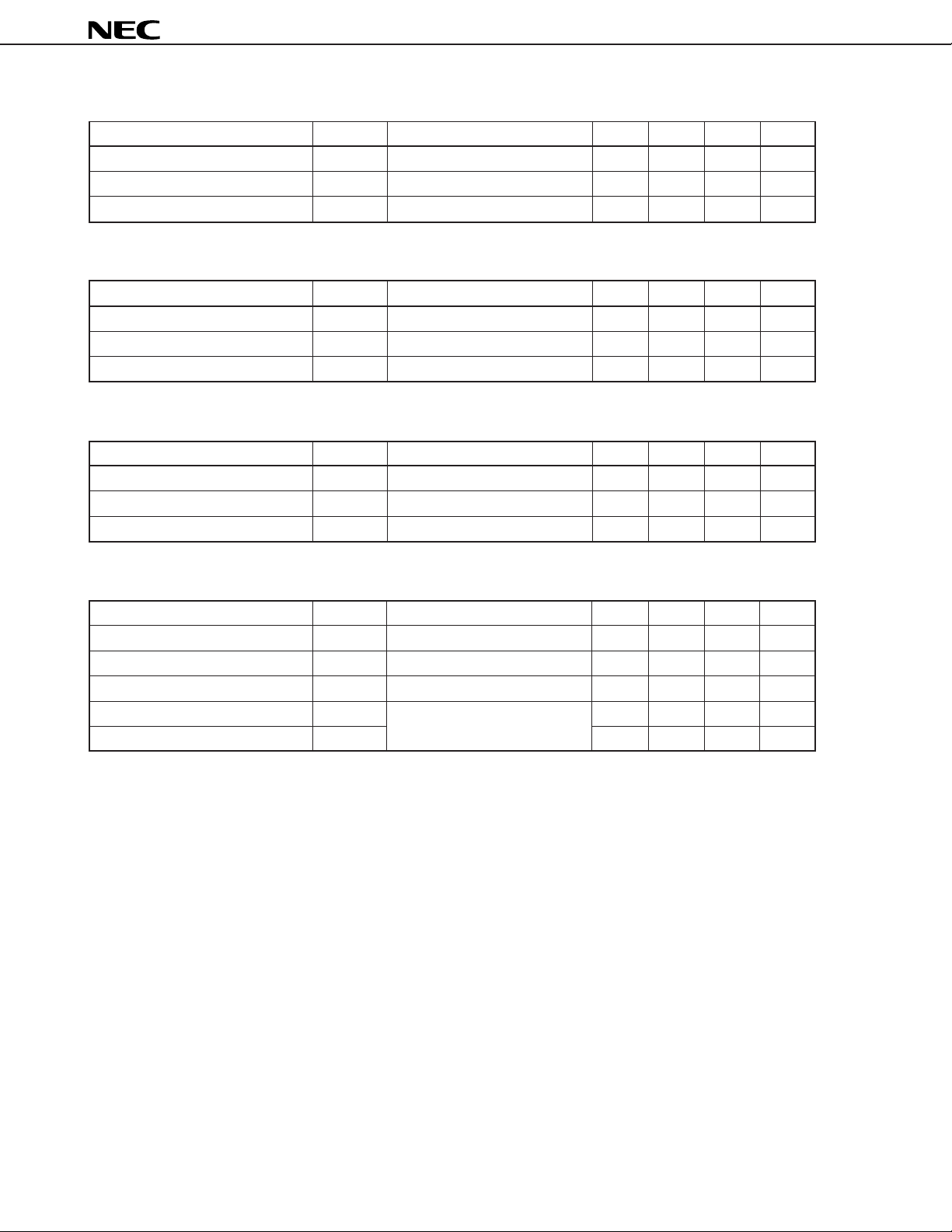

Function List (1/2)

Item Function

Internal PROM capacity 62 Kbytes

Internal RAM capacity 2048 bytes

Operation clock 16 MHz (Internal clock: 8 MHz)

Low frequency oscillation mode: 8 MHz (Internal clock: 8 MHz)

Low power consumption mode: 32.768 kHz (Subsystem clock)

Minimum instruction execution time

I/O ports Total: 54 Input: 8

Real-time output port 11 (including 3 outputs each for Pseudo-VSYNC, Head amplifier switch, and Chromi-

Super Timer/counter Timer/counter Compare register Capture register Remark

timer

unit

Capture register Input signal Number of bits Measurement cycle Operation edge

Special circuit for VCR • VSYNC separator, HSYNC separator

General purpose timer Timer Compare register Capture register

PWM output • 16-bit precision: 3 channels (Carrier frequency: 62.5 kHz)

Serial interface 3-wire serial I/O: 2 channels

A/D converter 8-bit resolution × 12 channels, conversion time: 10 µs

250 ns (at 8-MHz internal clock)

nance rotate)

TM0 (16-bit) 3 –

TM1 (16-bit) 3 1

FRC (22-bit) – 6

TM3 (16-bit) 2 1

• VISS detector, Wide-aspect detector

• Field identifier

• Head amplifier switch/chrominance rotate output circuit

TM2 (16-bit) 1 –

TM4 (16-bit) 1 (Capture/compare) 1

TM5 (16-bit) 1 –

• 8-bit precision: 3 channels (Carrier frequency: 62.5 kHz)

• BUSY/STRB control available (only 1 channel)

Note

Note

I/O: 46

UDC (5-bit) 1 –

EC (8-bit) 4 –

EDV (8-bit) 1 –

CFG 22 125 ns to 524 ms ↑↓

DFG 22 125 ns to 524 ms ↑

HSW 16 1 µs to 65.5 ms ↑↓

VSYNC 22 125 ns to 524 ms ↑

CTL 16 1 µs to 65.5 ms ↑↓

TREEL 22 125 ns to 524 ms ↑↓

SREEL 22 125 ns to 524 ms ↑↓

Generates HSW signal

Divides CFG signal

Note It is possible to change the capacity of the internal PROM and the internal RAM by specifying the internal

memory capacity select (IMS) register.

3

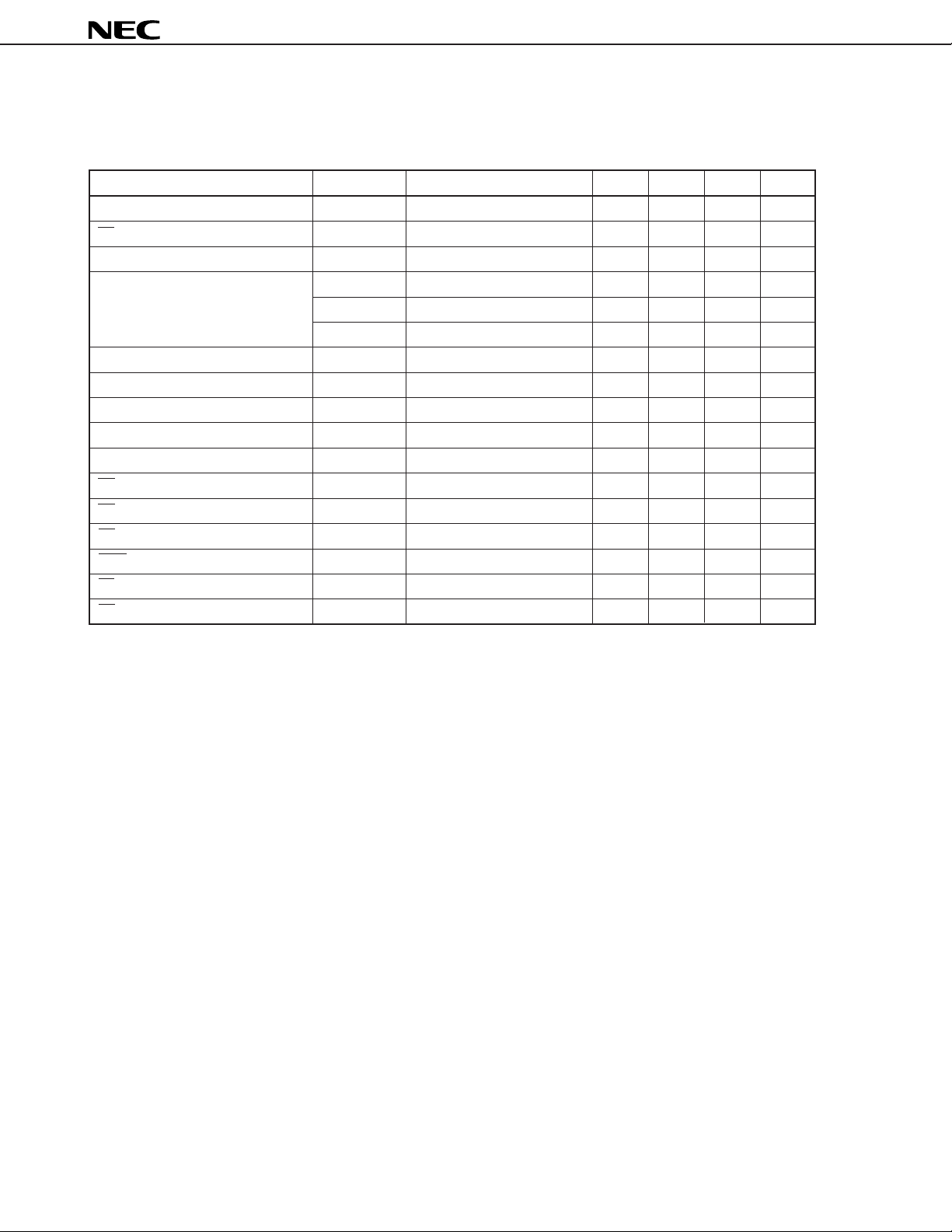

Function List (2/2)

Item Function

Analog unit • CTL amplifier

• RECCTL driver (supports re-write operation)

• DFG amplifier, DPG comparator, CFG amplifier

• DPFG separator (Three-value)

• Reel FG comparator (2 channels)

• CSYNC comparator

Interrupt Programmable 4 levels, vectored interrupt, macro service, context switching

External 9 (including NMI)

Internal 19 (including software interrupt)

*

Standby function HALT mode/STOP mode

Low-power consumption mode: HALT mode

Release from STOP mode by NMI pin’s active edge, Watch interrupt (INTW), or

INTP1/INTP2/KEY0-KEY4 pins’ input.

Watch function 0.5-sec interval, capable of low-voltage operation (VDD = 2.7 V)

*

Power supply voltage VDD = 2.7 to 5.5 V

Package 100-pin plastic QFP (14 × 20 mm)

µ

PD78P4916

4

Pin Configuration (Top View)

(1) Normal Operation Mode

• 100-pin plastic QFP (14 × 20 mm)

µ

PD78P4916GF-3BA

µ

PD78P4916

P64

P65/HWIN

P66/PWM4

P67/PWM5

P60/STRB/CLO

P61/SCK1/BUZ

P62/SO1

P63/SI1

PWM0

PWM1

SCK2

SO2

SI2/BUSY

V

XT1

XT2

V

X2

X1

RESET

IC

PTO02

PTO01

PTO00

P87/PTO11

P86/PTO10

P85/PWM3

P84/PWM2

P83/ROTC

P82/HASW

DD1AVSS1

CSYNCIN

REEL0IN/INTP3

REEL1IN

DFGIN

DPGIN

CFGCPIN

CFGAMPO

CFGIN

AV

VREFC

CTLOUT2

CTLOUT1

CTLIN

RECTTL–

100

1

2

3

4

5

6

7

8

9

10

11

12

13

14

DD

15

16

17

SS

18

19

20

21

22

23

24

25

26

27

28

29

30

SS2

RECTTL+

CTLDLY

AV

ANI11

ANI10

81828384858687888990919293949596979899

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

5049484746454443424140393837363534333231

ANI9

ANI8

P77/ANI7

P76/ANI6

P75/ANI5

P74/ANI4

P73/ANI3

P72/ANI2

P71/ANI1

P70/ANI0

REF

AV

AV

DD2

P96

P95/KEY4

P94/KEY3

P93/KEY2

P92/KEY1

P91/KEY0

P90/ENV

NMI

INTP0

INTP1

INTP2

P00

P01

P02

P03

P04

P05

P06

SS

DD

V

P80

P57

P56

P55

P54

P53

P52

P51

P50

V

P47

P46

Caution Connect the IC (Internally Connected) pin to V

P45

P44

P43

P42

SS directly.

P41

P40

P07

5

µ

PD78P4916

ANI0-ANI11 : Analog Input P00-P07 : Port0

AV

DD1, AVDD2 : Analog Power Supply P40-P47 : Port4

SS1, AVSS2 : Analog Ground P50-P57 : Port5

AV

REF : Analog Reference Voltage P60-P67 : Port6

AV

BUSY : Serial Busy P70-P77 : Port7

BUZ : Buzzer Output P80, P82-P87 : Port8

CFGAMPO : Capstan FG Amplifier Output P90-P96 : Port9

CFGCPIN : Capstan FG Capacitor Input PTO00-PTO02, : Programmable Timer Output

CFGIN : Analog Unit Input PTO10, PTO11

CLO : Clock Output

CSYNCIN : Analog Unit Input

CTLDLY : Control Delay Input

PWM0 - PWM5 : Pulse Width Modulation Output

RECCTL+, RECCTL–

REEL0IN, REEL1IN

: RECCTL Output/PBCLT Input

: Analog Unit Input

CTLIN : CTL Amplifier Input Capacitor RESET : Reset

CTLOUT1, CTLOUT2

: CTL Amplifier Output ROTC : Chrominance Rotate Output

DFGIN : Analog Unit Input SCK1, SCK2 : Serial Clock

DPGIN : Analog Unit Input SI1, SI2 : Serial Input

ENV : Envelope Input SO1, SO2 : Serial Output

HASW : Head Amplifier Switch Output STRB : Serial Strobe

HWIN : Hardware Timer External Input V

DD : Power Supply

IC : Internally Connected VREFC : Reference Amplifier Capacitor

INTP0-INTP3 : Interrupt From Peripherals Vss : Ground

KEY0-KEY4 : Key Return X1, X2 : Crystal (Main System Clock)

NMI : Nonmaskable Interrupt XT1, XT2 : Crystal (Subsystem Clock)

6

(2) PROM Programming Mode

• 100-pin plastic QFP (14 × 20 mm)

µ

PD78P4916GF-3BA

µ

PD78P4916

PGM

(L)

OPEN

(L)

V

OPEN

OPEN

RESET

IC/V

OPEN

(L)

OE

CE

V

V

V

SS

DD

(L)

100

99 9897 96959493 92919089 8887 86858483 8281

1

(L)

OPEN

(L)

OPEN

OPEN

V

V

2

3

4

5

6

7

8

9

10

11

12

13

14

DD

15

SS

16

17

SS

18

19

SS

20

21

PP

22

23

24

25

26

27

28

29

30

31 3233 34353637 3839 40 4142 4344 4546 4748 4950

(L)

SS

V

OPEN

(L)

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

V

D0

D1

D2

D3

D4

D5

D6

(L)

DD

(L)

A9

(L)

(L)

A15

A14

A13

A12

A11

A10

A16

A7A6A5A4A3A2A1

A8

V

V

A0

D7

SS

DD

Cautions (L) : Connect to VSS via pull-down resistors individually.

V

SS : Connect to ground.

OPEN : Leave this pin unconnected.

RESET : Apply low level.

A0 - A16 : Address Bus RESET : Reset

D0 - D7 : Data Bus V

CE : Chip Enable V

OE : Output Enable V

DD : Power Supply

PP : Programming Power Supply

SS : Ground

PGM : Program

7

Internal Block Diagram

µ

PD78P4916

NMI

INTP0 -

INTP3

PWM0 -

PWM5

PTO00 -

PTO02

PTO10,

PTO11

VREFC

REEL0IN

REEL1IN

CSYNCIN

DFGIN

DPGIN

CFGIN

CFGAMPO

CFGCPIN

CTLOUT1

CTLOUT2

CTLIN

RECCTL+

RECCTL–

CTLDLY

AV

DD1, AVDD2

AVSS1, AVSS2

AVREF

ANI0 - ANI11

Interrupt

Control

Super Timer

Unit

Analog Unit

&

A/D Converter

78K/IV

16-bit CPU Core

(RAM 512 bytes)

System

Control

Clock Output

Buzzer Output

Key Input

Real-Time

Output Port

VDD

VSS

X1

X2

XT1

XT2

RESET

D0 - D7

A0 - A16

CE

OE

PGM

VPP

CLO

BUZ

KEY0 - KEY4

P00 - P07

P80, P82, P83

Used in PROM

programming

mode

SI1

SO1

SCK1

SI2/BUSY

SO2

SCK2

STRB

Serial

Interface 1

Serial

Interface 2

RAM

1536

bytes

62

ROM

Kbytes

Port0

Port4

Port5

Port6

Port7

Port8

Port9

P00 - P07

P40 - P47

P50 - P57

P60 - P67

P70 - P77

P80, P82 - P87

P90 - P96

8

System Configuration Example

• Camcorder

Drum motor

Capstan motor

M

M

Driver

Driver

DFG

DPG

CFG

DFGIN

DPGIN

PWM0

CFGIN

PWM1

µ

PD78P4916

PORT

PORT

PORT

SCK1

SI1

SO1

INTP0

µ

PD78P4916

Key matrix

INTP0

Microcontroller

SCK

SO

SI

PORT

for camera

control

µ

PD78356

CTL head

Loading motor

Audio-video

signal

processor

Signals from

remote controller

Driver

Composite sync signal

Video head switch

Audio head switch

Pseudo-vertical sync signal

Remote control

receive signal

PC2800A

µ

RECCTL+

RECCTL–

PWM2M

PORT

CSYNCIN

PTO00

PTO01

P80

INTP2

X1 X2 XT1 XT2

16 MHz 32.768 kHz

PORT

SCK2

SO2

BUSY

PORT

STRB

PORT

Camera block

CS

CLK

DATA

BUSY

LCD display panel

CS

CLK

DATA

BUSY

STB

Mechanical block

LCD C/D

PD7225

µ

OSD

PD6456

µ

9

• Deck-type VCR

Drum

motor

µ

PD78P4916

PD78P4916

µ

DFG

DPG

M

Driver

DFGIN

DPGIN

PWM0

PORT

SCK1

SI1

SO1

STB

CLK

DOUT

DIN

TM

FIP C/D

PD16311

µ

Capstan

motor

CTL

head

Loading

motor

Reel

motors

CFG

M

M

M

M

Driver

Driver

Reel FG0

Driver

Driver

Reel FG1

CFGIN

PWM1

RECCTL+

RECCTL–

PWM2

REEL0IN

PWM3

PWM4

REEL1IN

Low-frequency

oscillation mode

X1 X2

PORT

SCK2

PORT

CSYNCIN

PTO00

PTO01

PWM5

PORT

PORT

INTP2

XT1

SO2

Composite

synchronous signal

Video head switch

Audio head switch

Pseudo-vertical

synchronous signal

P80

XT2

CS

CLK

DATA

Remote control

receive signal

FIP

Key matrix

OSD

PD6454

µ

PC2800A

µ

Audio-video

signal

processor unit

Tuner unit

Mechanical block

Signals from

remote controller

10

8 MHz 32.768 kHz

µ

PD78P4916

CONTENTS

1. DIFFERENCES BETWEEN µPD78P4916 AND µPD784915, µPD784916A ································· 12

2. PIN FUNCTION ································································································································· 13

2.1 Normal Operation Mode ····························································································································· 13

2.2 PROM Programming Mode (V

2.3 Pin I/O Circuits and Recommended Connection of Unused Pins ························································· 16

3. INTERNAL MEMORY CAPACITY SELECT REGISTER (IMS) ··················································· 20

4. PROM PROGRAMMING ··················································································································· 21

4.1 Operation Mode ·········································································································································· 21

4.2 PROM Write Procedure ······························································································································ 23

4.3 PROM Read Procedure ······························································································································ 27

4.4 Screening One-time PROM Versions ······································································································· 27

PP ≥ 5 V, RESET = L) ·················································································· 15

*

5. ELECTRICAL SPECIFICATIONS ····································································································· 28

6. PACKAGE DRAWING ······················································································································ 46

7. RECOMMENDED SOLDERING CONDITIONS ················································································· 47

APPENDIX A. DEVELOPMENT TOOLS ····························································································· 48

APPENDIX B. SOCKET DRAWING AND RECOMMENDED FOOTPRINT ········································ 50

APPENDIX C. RELATED DOCUMENTS ···························································································· 52

*

*

*

11

µ

1. DIFFERENCES BETWEEN µPD78P4916 AND µPD784915, µPD784916A

*

Other than the memory types, their capacities, and memory-related points, the functions of the three devices are

µ

identical: the

784916A contain mask ROMs.

Table 1-1 shows the differences among these devices. Be sure to keep in mind these differences especially when

debugging and pre-producing the application system with the PROM version and then mass-producing it with the

mask-ROM version.

For the details about the CPU functions and on-chip hardware, refer to the

Manual—Hardware (U10444E).

PD78P4916 incorporates a one-time PROM that is rewritable by users, while the µPD784915 and

µ

PD784915 Subseries User’s

µ

Table 1-1. Differences among

PD784915 Subseries Devices

PD78P4916

Parameters

Internal ROM One-time PROM Mask ROM Mask ROM

Internal RAM 2048 bytes

Internal memory size select register (IMS) Provided Not provided Not provided

Pinouts Pins related to PROM writing and reading are provided on the µPD78P4916.

Other There are differences in noise immunity, noise radiation, and some electrical

Note The internal PROM and RAM capacities of the

size select register (IMS).

Caution There are differences in noise immunity and noise radiation between the PROM and mask-ROM

versions. When pre-producing the application set with the PROM version and then massproducing it with the mask-ROM version, be sure to conduct sufficient evaluations for the set

using consumer samples (not engineering samples) of the mask-ROM version.

µ

PD78P4916

62 Kbytes

specifications, because of the differences in circuit complexity and mask

layout.

Note

Note

µ

PD78P4916 can be changed through its internal memory

µ

PD784915

48 Kbytes 62 Kbytes

1280 bytes 1280 bytes

µ

PD784916A

12

2. PIN FUNCTION

2.1 Normal Operation Mode

(1) Port Pins

µ

PD78P4916

Pin Name Input/Output

P00 - P07 I/O Real-time 8-bit input/output port (Port0)

P40 - P47 I/O – 8-bit input/output port (Port4)

P50 - P57 I/O – 8-bit input/output port (Port5)

P60 I/O STRB/CLO 8-bit input/output port (Port6)

P61 SCK1/BUZ

P62 SO1

P63 SI1

P64 –

P65 HWIN

P66 PWM4

P67 PWM5

P70 - P77 Input ANI0 - ANI7 8-bit input port (Port7)

P80 I/O Real-time for Pseudo-VSYNC output 7-bit input/output port (Port8)

P82

P83 for ROTC output

P84 PWM2

P85 PWM3

P86 PTO10

P87 PTO11

P90 I/O ENV 7-bit input/output port (Port9)

P91 - P95 KEY0 - KEY4

P96 –

Alternate function

output port • Specifiable to input or output mode bitwise.

• With software-specifiable on-chip pull-up resistors

(P00 - P07).

• Specifiable to input or output mode bitwise.

• With software-specifiable on-chip pull-up resistors

(P40 - P47).

• Specifiable to input or output mode bitwise.

• With software-specifiable on-chip pull-up resistors

(P50 - P57).

• Specifiable to input or output mode bitwise.

• With software-specifiable on-chip pull-up resistors

(P60 - P67).

output port

for HASW output

• Specifiable to input or output mode bitwise.

• With software-specifiable on-chip pull-up resistors

(P90 - P96).

Description

• Specifiable to input or output

mode bitwise.

• With software-specifiable on-chip

pull-up resistors (P80, P82 - P87)

13

(2) Non-Port Pins (1/2)

µ

PD78P4916

Pin Name Input/Output

REEL0IN Input INTP3 Reel FG inputs

REEL1IN –

DFGIN – Drum FG, PFG input (Three-value)

DPGIN – Drum PG input

CFGIN – Capstan FG input

CSYNCIN – Composite SYNC input

CFGCPIN – CFG comparator input

CFGAMPO Output – CFG amplifier output

PTO00 Output – Programmable timer outputs of super timer unit

PTO01 –

PTO02 –

PTO10 P86

PTO11 P87

PWM0 Output – PWM outputs of super timer unit

PWM1 –

PWM2 P84

PWM3 P85

PWM4 P66

PWM5 P67

HASW Output P82 Head amplifier switch output

ROTC Output P83 Chrominance rotate output

ENV Input P90 Envelope input

SI1 Input P63 Serial data input (Serial interface channel 1)

SO1 Output P62 Serial data output (Serial interface channel 1)

SCK1 I/O P61/BUZ Serial clock input/output (Serial interface channel 1)

SI2 Input BUSY Serial data input (Serial interface channel 2)

SO2 Output – Serial data output (Serial interface channel 2)

SCK2 I/O – Serial clock input/output (Serial interface channel 2)

BUSY Input SI2 Serial busy input (Serial interface channel 2)

STRB Output P60/CLO Serial strobe output (Serial interface channel 2)

ANI0 - ANI7 Analog inputs P70 - P77 Analog inputs for A/D converter

ANI8 - ANI11 –

CTLIN – – CTL amplifier input capacitor

CTLOUT1 Output – CTL amplifier output

CTLOUT2 I/O – Logic input/CTL amplifier output

RECCTL+, RECCTL–

CTLDLY – – External time-constant connection (to rewrite RECCTL)

VREFC – – AC ground for VREF amplifier

NMI Input – Non-maskable interrupt request input

I/O – RECCTL output/PBCTL input

Alternate function

Description

14

(2) Non-Port Pins (2/2)

µ

PD78P4916

Pin Name Input/Output

INTP0 - INTP2 Input – External interrupt request input

INTP3 Input REEL0IN

KEY0 - KEY4 Input P91 - P95 Key input signal

CLO Output P60/STRB Clock output

BUZ Output P61/SCK1 Buzzer output

HWIN Input P65 Hardware timer external input

RESET Input – Reset input

X1 Input – Crystal resonator connection for main system clock oscillation

X2 –

XT1 Input – Crystal resonator connection for subsystem clock oscillation

XT2 –

AVDD1, AVDD2 – – Positive power supply for analog unit

AVSS1, AVSS2 – – GND for analog unit

AVREF – – Reference voltage input to A/D converter

VDD – – Positive power supply to digital unit

VSS – – GND of digital unit

IC – – Internally connected. Connect directly to V SS.

Alternate function

Description

Crystal resonator connection for clock oscillation of watch

2.2 PROM Programming Mode (VPP ≥ 5 V, RESET = L)

Pin name Input/output Function

VPP – Set PROM programming mode

High voltage applied at program write/verify operation

RESET Input Low level input for setting PROM programming mode

A0 - A16 Address input

D0 - D7 I/O Data input/output

PGM Input Program inhibit input in PROM programming mode

CE PROM enable input / programming pulse input

OE Read strobe input to PROM

VDD – Positive power supply

VSS GND potential

15

µ

2.3 Pin I/O Circuits and Recommended Connection of Unused Pins

*

Table 2-1 shows the input/output circuit types of the device’s pins and the recommended connection

of the pins which are unnecessary to the user’s application. The circuit diagrams for the I/O circuits are

shown in Figure 2-1.

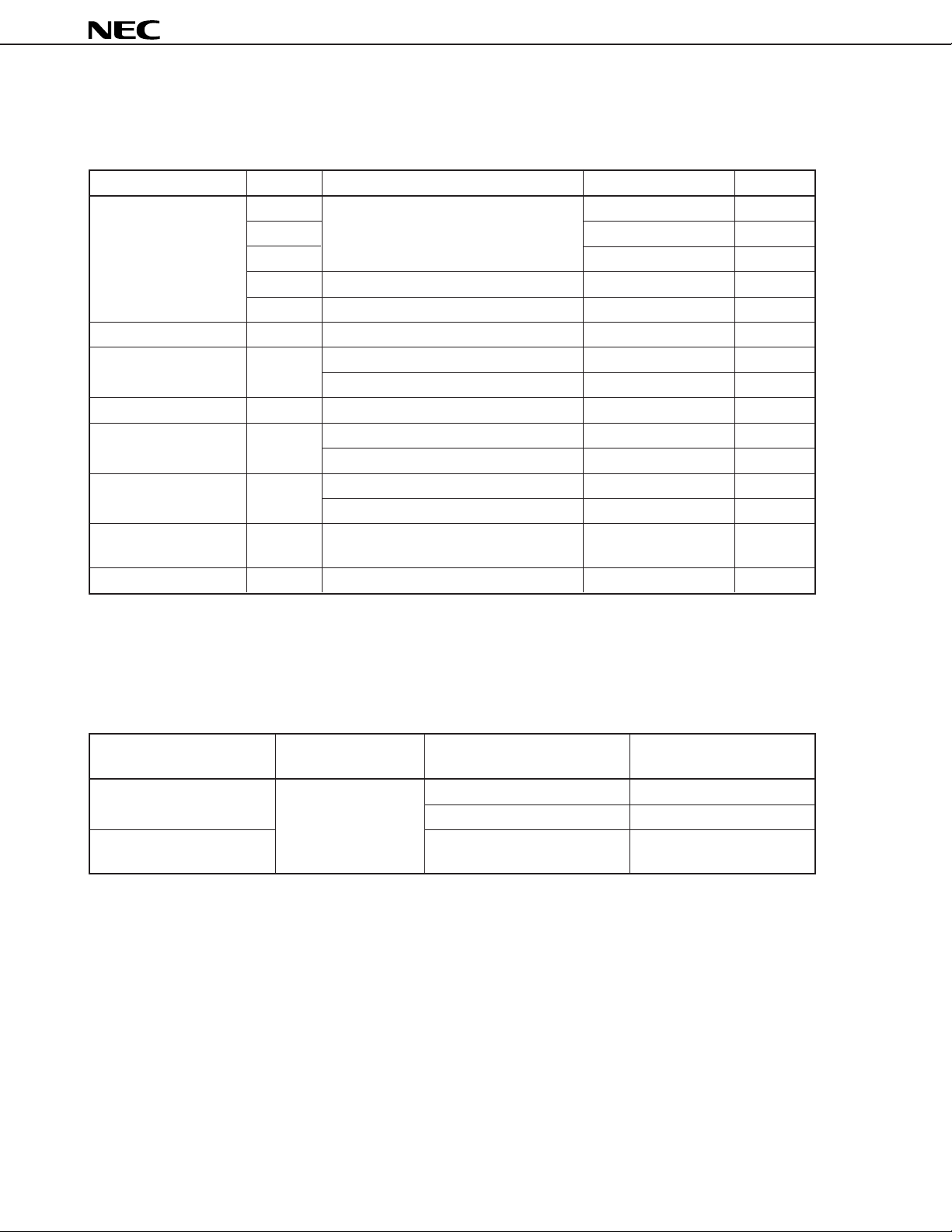

Table 2-1. Pin I/O Circuits and Recommended Connection of Unused Pins (1/2)

Pins I/O circuit types Direction Recommended connection of unused pins

P00-P07 5-A I/O Input mode: Connect to VDD.

P40-P47 Output mode: Leave unconnected.

P50-P57

P60/STRB/CLO

P61/SCK1/BUZ

P62/SO1 5-A

P63/SI1 8-A

P64 5-A

P65/HWIN 8-A

P66/PWM4 5-A

P67/PWM5

P70/ANI0-P77/ANI7 9 Input Connect to VSS.

P80 5-A I/O Input mode: Connect to VDD.

P82/HASW Output mode: Leave unconnected.

P83/ROTC

P84/PWM2

P85/PWM3

P86/PTO10

P87/PTO11

P90/ENV

P91/KEY0-P95/KEY4 8-A

P96 5-A

SI2/BUSY 2-A Input Connect to VDD.

SO2 4 Output High-impedance mode: Connect to VSS via a pull-down resistor.

SCK2

ANI8-ANI11 7 Input Connect to VSS.

RECCTL+, RECCTL– — I/O When ENCTL = 0 and ENREC = 0: Connect to VSS.

8-A

Otherwise: Leave unconnected.

8-A I/O Input mode: Connect to VDD.

Output mode: Leave unconnected.

PD78P4916

Remark ENCTL: Bit 1 of the amplifier control register (AMPC)

ENREC: Bit 7 of the amplifier mode register 0 (AMPM0)

16

µ

PD78P4916

Table 2-1. Pin I/O Circuits and Recommended Connection of Unused Pins (2/2)

Pins I/O circuit types Direction Recommended connection of unused pins

DFGIN — Input ENDRUM = 0: Connect to VSS.

DPGIN ENDRUM = 0, or ENDRUM = 1 and SELPGSEPA = 0:

Connect to VSS.

CFGIN, CFGCPIN ENCAP = 0: Connect to VSS.

CSYNCIN ENCSYN = 0: Connect to VSS.

REEL0IN/INTP3, REEL1IN

CTLOUT1 — Output Leave unconnected.

CTLOUT2 — I/O When ENCTL and ENCOMP = 0 and 0: Connect to VSS.

CFGAMPO — Output Leave unconnected.

CTLIN — — When ENCTL = 0: Leave unconnected.

VREFC When ENCTL, ENCAP, and ENCOMP = 0, 0, and 0:

CTLDLY Leave unconnected.

PWM0, PWM1 3 Output Leave unconnected.

PTO00-PTO02

NMI 2 Input Connect to VDD.

INTP0 Connect to VDD or VSS.

INTP1, INTP2 2-A Input Connect to VDD.

AVDD1, AVDD2 — — Connect to VDD.

AVREF, AVSS1, AVSS2 Connect to VSS.

RESET

XT1 — — Connect to VSS.

XT2 Leave unconnected.

IC Connect directly to VSS.

2——

ENREEL = 0: Connect to VSS.

ENCTL = 1: Leave unconnected.

Leave unconnected.

Remark ENDRUM: Bit 2 of the amplifier control register (AMPC)

SELPGSEPA: Bit 2 of the amplifier mode register 0 (AMPM0)

ENCAP: Bit 3 of the amplifier control register (AMPC)

ENCSYN: Bit 5 of the amplifier control register (AMPC)

ENREEL: Bit 6 of the amplifier control register (AMPC)

ENCTL: Bit 1 of the amplifier control register (AMPC)

ENCOMP: Bit 4 of the amplifier control register (AMPC)

17

Figure 2-1. Pin I/O Circuit Diagrams (1/2)

µ

PD78P4916

Type 2

IN

Schmitt triggered input with hysteresis characteristics.

Type 2-A

V

DD

P-ch

pullup

enable

IN

Schmitt triggered input with hysteresis characteristics.

Type 3

DD

V

P-ch

Type 5-A

pullup

enable

data

output

disable

input

enable

Type 7

IN

P-ch

N-ch

V

DD

P-ch

N-ch

Comparator

V

P-ch

DD

IN/

OUT

data

OUT

N-ch

Type 4

V

DD

data

output

P-ch

N-ch

disable

Push-pull output that can also set the output to the

high-impedance state

(both P-ch and N-ch transistors are turned off.)

OUT

Type 8-A

pullup

enable

data

output

disable

V

REF

(Threshold voltage)

V

DD

P-ch

N-ch

P-ch

V

DD

IN/

OUT

18

Type 9

Figure 2-1. Pin I/O Circuit Diagrams (2/2)

µ

PD78P4916

IN

P-ch

N-ch

Comparator

V

REF

(Threshold voltage)

input enable

19

µ

PD78P4916

3. INTERNAL MEMORY CAPACITY SELECT REGISTER (IMS)

Internal memory capacity select register (IMS) specifies the effective area of on-chip memory (PROM, RAM) of

µ

PD78P4916. Setting this register is required when the capacity of the ROM or RAM in the mask version is

the

smaller than that of the

this register, bugs in application programs due to accessing an address beyond the memory capacity of the actual

chip can be avoided.

The IMS register is write-only register. To write this register, use the 8-bit manipulation instruction.

The register is initialized to FFH by RESET input (ROM: 62 Kbytes, RAM: 2048 bytes).

µ

PD78P4916. If the memory capacity of the µPD78P4916 is appropriately defined using

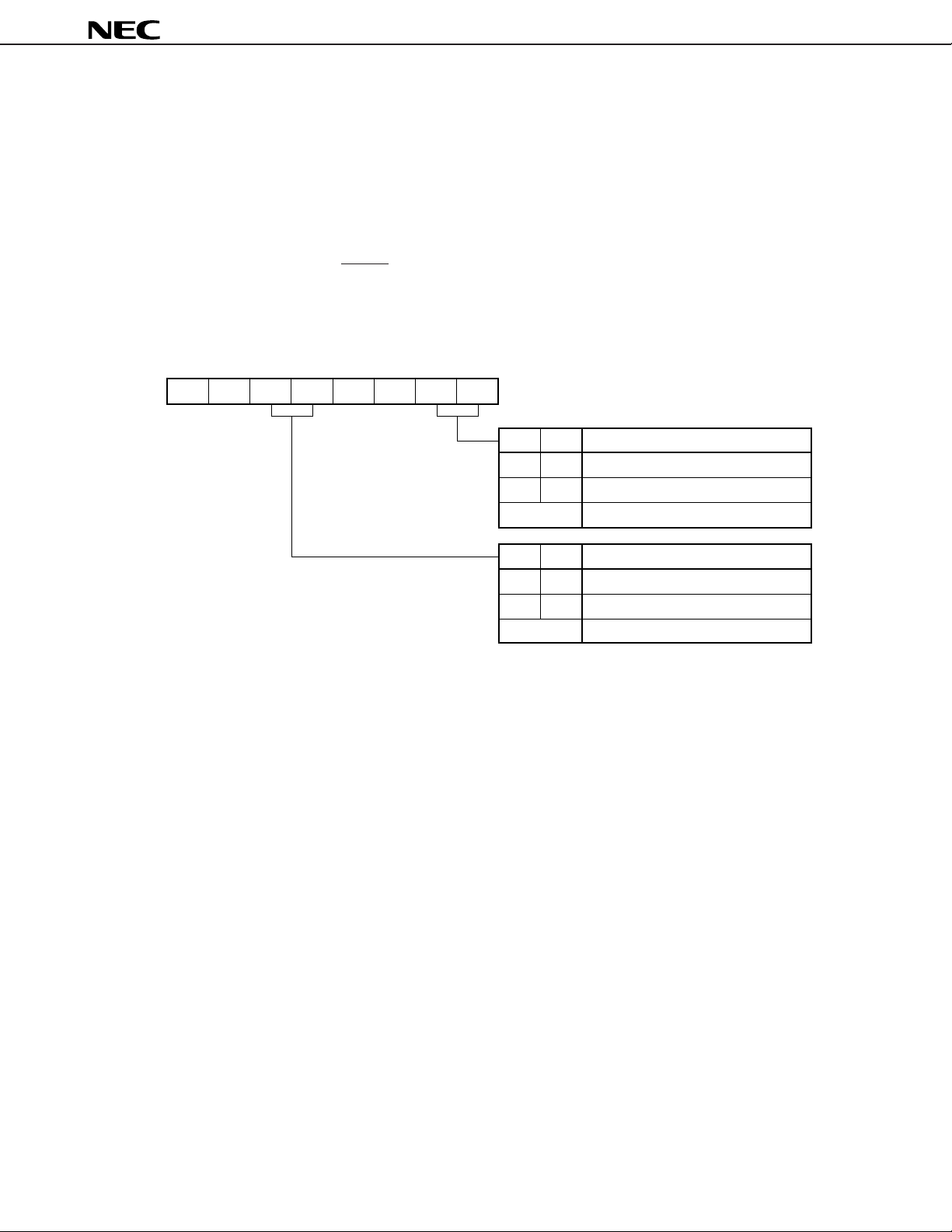

*

7654 2310

11 1ROM1 ROM0 1 RAM1 RAM0IMS FFFCH

Caution The

write instruction to IMS is executed in the

or malfunctions.

Figure 3-1. Internal Memory Capacity Select Register (IMS) Format

R/WState at resetAddress

FFH

RAM1 RAM0

0

1

Other

ROM1 ROM0

1

1

Other

µ

PD78P4916 has the IMS and the µPD784915 and 784916A do not have it. However, if a

µ

PD784915 or 784916A, it does not cause conflicts

Specification of internal RAM capacity

1

1280 bytes

1

2048 bytes

Setting prohibited

Specification of internal ROM capacity

0

48 Kbytes

1

62 Kbytes

Setting prohibited

W

20

µ

PD78P4916

4. PROM PROGRAMMING

The µPD78P4916 has on-chip 62-Kbyte PROM as the program memory. The PROM programming mode is

entered by setting V

DD, IC/VPP, and RESET pins as specified. For the settings of the unused pins in this mode,

refer to the drawing of “(2) PROM Programming Mode” in the section “Pin Configuration (Top View)”.

4.1 Operation Mode

The PROM programming mode is entered by applying +5 V or +12 V to the IC/VPP pin, +5 V or +6.5 V to the VDD

pins, and low-level voltage to the RESET pin. Table 4-1 shows the operation mode specified by the CE, OE, and

PGM pins.

It is possible to read the contents of PROM by setting up read operation mode.

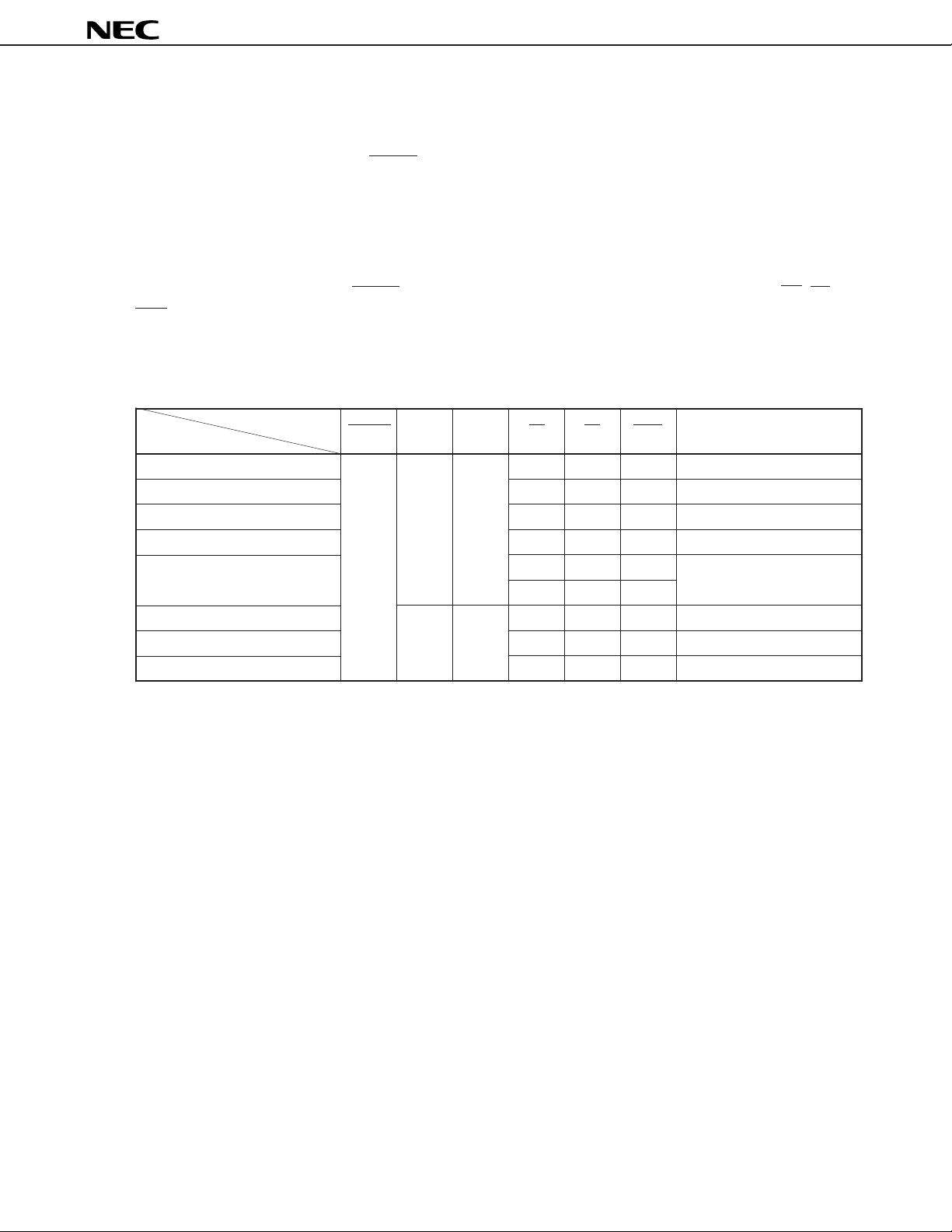

Table 4-1. Operation Mode of PROM Programming

Pins

Operation mode

Page data latch L +12.5 V +6.5 V H L H Data input

Page write H H L High impedance

Byte write L H L Data input

Program verify L L H Data output

Program inhibit × H H High impedance

Read +5 V +5 V L L H Data output

Output disable L H × High impedance

Standby H ××High impedance

RESET IC/V

V

PP

DD

CE OE PGM D0 - D7

× LL

Remark × : Low or high level

21

µ

PD78P4916

(1) Read mode

By setting CE = L and OE = L, the device enters the read mode.

(2) Output disable mode

By setting OE = H, the device enters the output disable mode, where data output pins go to high impedance

state.

Therefore it is possible to read data from a specified device by enabling only the OE pin of the device to be

read, if two or more

(3) Standby mode

By setting CE = H, the device enters the Standby mode.

In this mode, data output pins go to high impedance state regardless of the OE pin condition.

(4) Page data latch mode

By setting CE = H, PGM = H, and OE = L at the beginning of page programming mode, the device enters the

page data latch mode.

In this mode, 4-byte data are latched in page units (consisting of 4 bytes) to internal address/data latch circuit.

µ

PD78P4916s are connected to a data bus.

(5) Page programming mode

After one-page data (consisting of 4 bytes) and their address are latched in the page data latch mode, the page

programming operation is executed by applying 0.1-ms programming pulse (active low) to the PGM pin under

CE = H, OE = H conditions. Following that operation, the programming data is verified by setting CE = L and

OE = L.

When data is not programmed by one programming pulse, the write and verify operations are repeated X times

(X ≤ 10).

(6) Byte programming mode

Applying 0.1-ms programming pulse (active low) to the PGM pin under CE = L and OE = H condition, byte

programming operation is executed. Next, the programming data is verified by setting OE = L.

When data is not programmed by one programming pulse, the write and verify operations are repeated X times

(X ≤ 10).

(7) Program verify mode

By setting CE = L, PGM = H, and OE = L, the device enters the program verify mode. Check whether data

is programmed correctly or not in this mode after write operation.

(8) Program inhibit mode

When the OE pins, V

program inhibit mode to write data to one of those devices.

Programming is executed in the page programming mode or byte programming mode as mentioned above. At

that time, data is not programmed to a device for which high level voltage is applied to the PGM pin.

PP pins, and D0-D7 pins of two or more

µ

PD78P4916s are connected in parallel, use

22

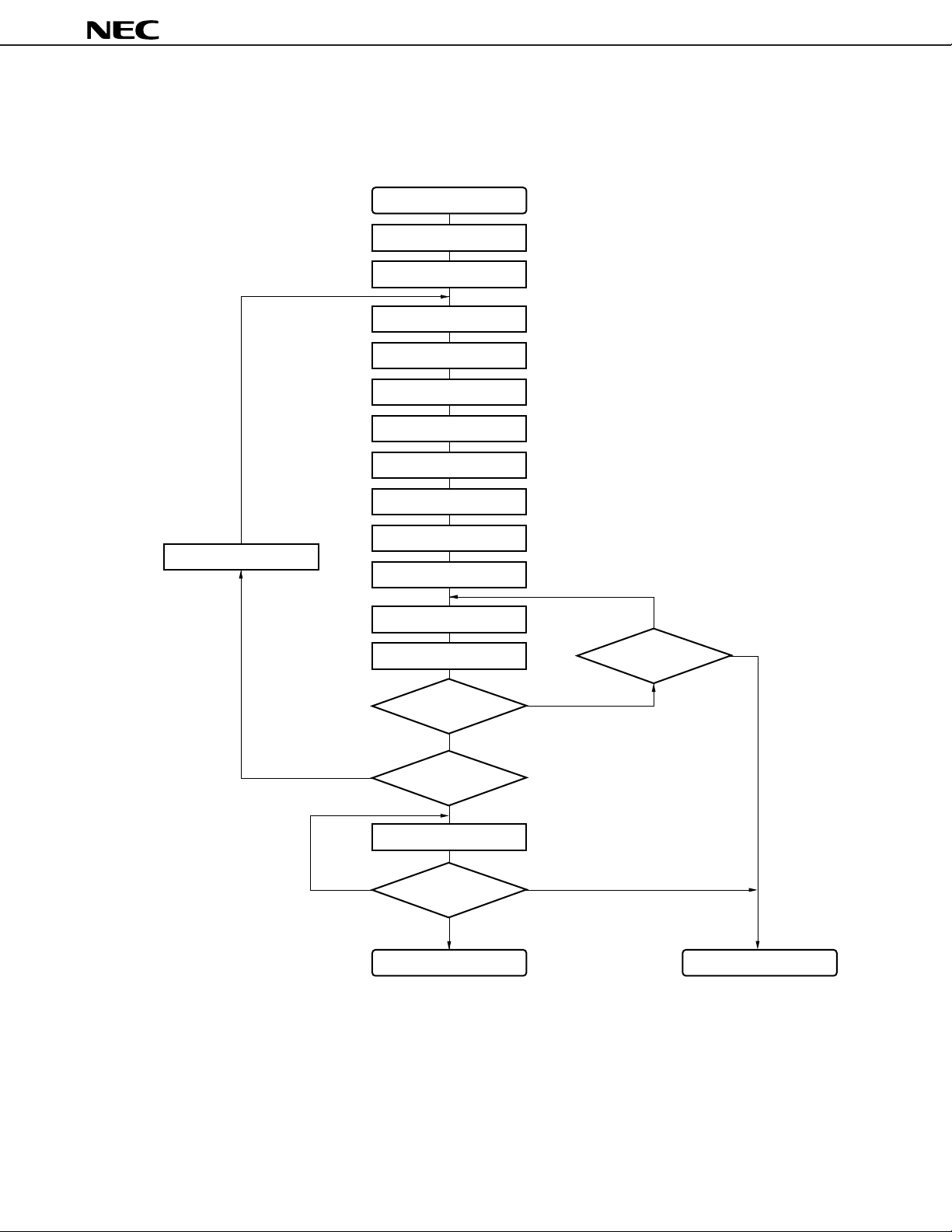

4.2 PROM Write Procedure

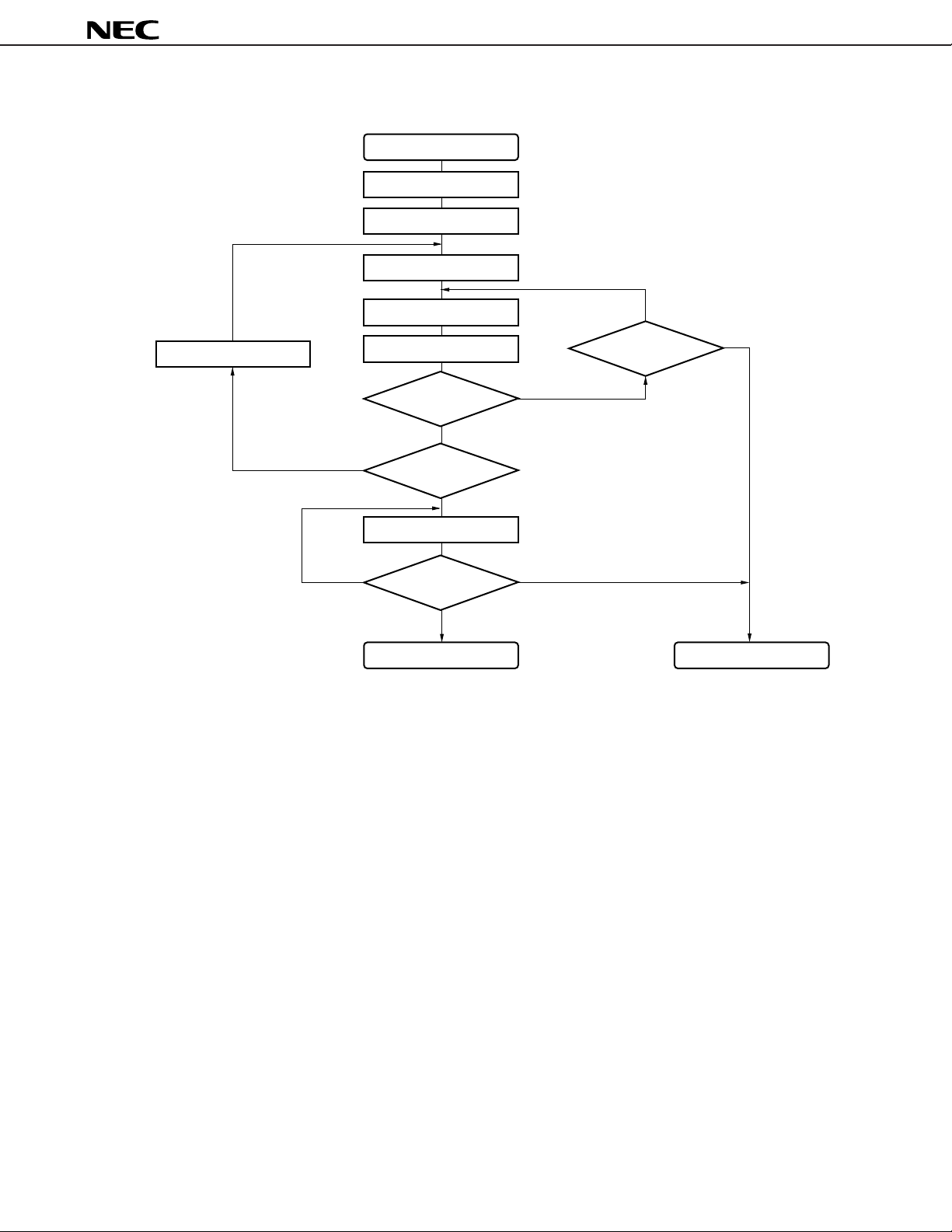

Figure 4-1. Flowchart in Page Programming Mode

Start

Address = G

DD

= 6.5 V, VPP = 12.5 V

V

X = 0

Latch

Address = Address + 1

Latch

Address = Address + 1

µ

PD78P4916

Address = Address + 1

Latch

Address = Address + 1

Latch

X = X+1

0.1-ms programming pulse

Verify 4 bytes

Pass

No

Pass

Address = N ?

Yes

VDD = 4.5 to 5.5 V, VPP = V

Verify all bytes

All Pass

No

X = 10?

Fail

DD

Fail

Yes

Remarks 1. G = Start address

2. N = End address of the program

Write operation end

Defective

23

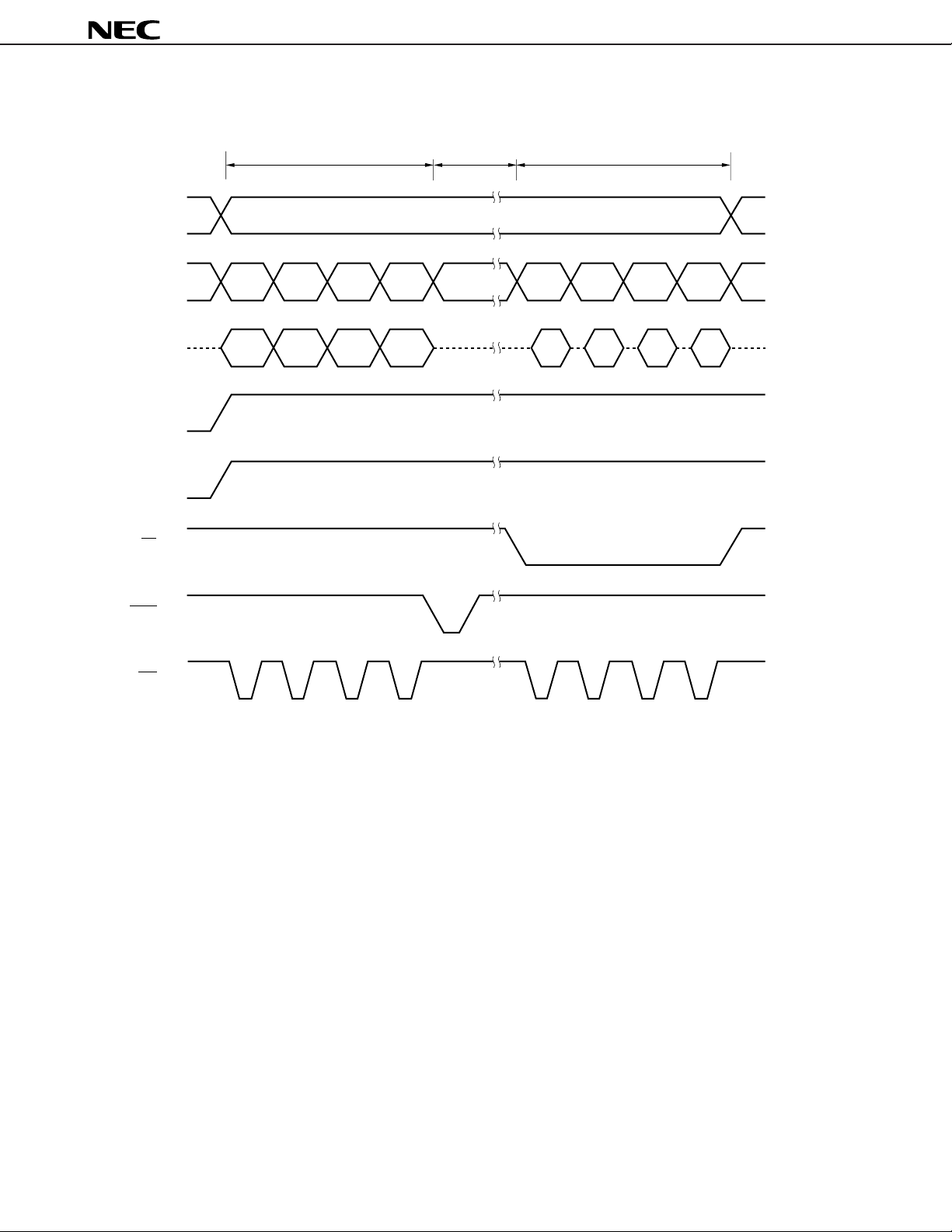

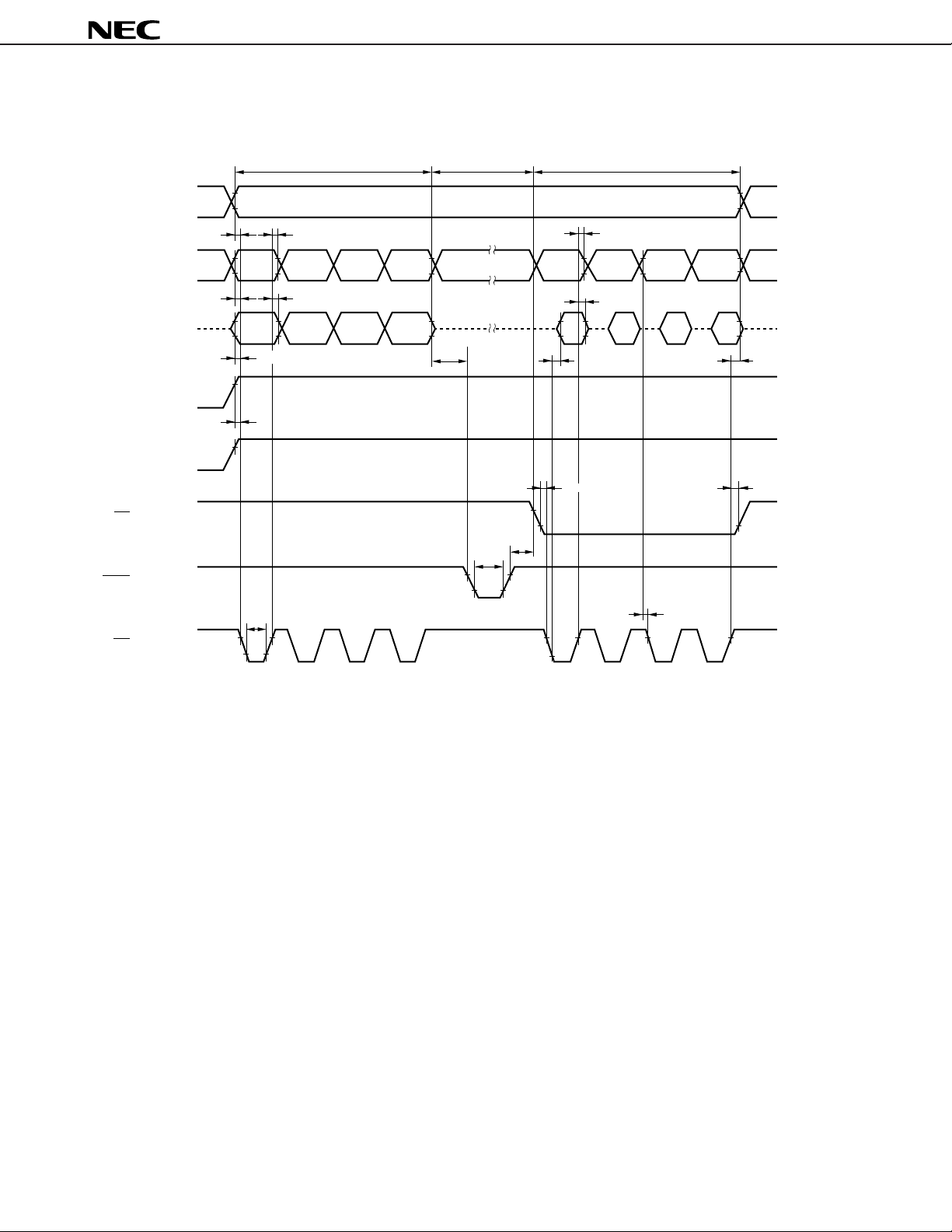

Figure 4-2. Operation Timing in Page Programming Mode

Page data latch Page programming Program verify

µ

PD78P4916

A2 - A16

A0, A1

D0 - D7

V

PP

V

DD

CE

PGM

OE

V

PP

V

DD

VDD+1.5

V

DD

V

IH

V

IL

V

IH

V

IL

V

IH

V

IL

Address input

Address input

Hi-Z

Data input Data output

Hi-ZHi-Z

24

Figure 4-3. Flowchart in Byte Programming Mode

Start

Address = G

VDD = 6.5 V, VPP = 12.5 V

X = 0

µ

PD78P4916

Address = Address + 1

Pass

Remarks 1. G = Start address

2. N = End address of the program

X = X+1

0.1-ms programming pulse

Verify

Pass

No

Address = N ?

Yes

VDD = 4.5 to 5.5 V, VPP = V

Verify all bytes

All Pass

Write operation end

No

X = 10?

Fail

DD

Fail

Yes

Defective

25

Figure 4-4. Operation Timing in Byte Programming Mode

Programming Program verify

µ

PD78P4916

A0 - A16

D0 - D7

V

PP

V

DD

CE

PGM

OE

V

PP

V

DD

VDD+1.5

V

DD

V

IH

V

IL

V

IH

V

IL

V

IH

V

IL

Address input

Data input Data output

Hi-Z

Hi-ZHi-Z

Cautions 1. Apply voltage to V

is cut off.

2. The voltage including overshoot applied to VPP pin must be kept less than +13.5 V.

3. If a device is inserted or removed while +12.5 V is applied to V

affected in reliability.

DD before applying voltage to VPP, and cut off VDD voltage after VPP voltage

PP pin, it may be adversely

26

µ

PD78P4916

4.3 PROM Read Procedure

The contents of PROM can be read onto external data bus (D0-D7) as described below:

(1) Fix RESET pin to low and supply +5 V to VPP pin. Connect other unused pins as specified in “(2) PROM

Programming Mode” in section “Pin Configuration (Top View)."

(2) Supply +5 V to the V

(3) Input the address of the data to be read to the A0-A16 pins.

(4) Enter the read mode (CE = L, OE = L).

(5) Output data to D0-D7 pins.

The above operation timing from (2) to (5) is shown in Figure 4-5.

DD and VPP pins.

Figure 4-5. PROM Read Timing

A0 - A16

CE (Input)

OE (Input)

D0 - D7

Hi-Z

Address input

Data output

Hi-Z

4.4 Screening One-time PROM Versions

The one-time PROM version (µPD78P4916GF-3BA) cannot be completely tested by NEC for shipment because

of its structure. For screening, it is recommended to verify PROM after storing the necessary data under the following

conditions:

Storage Temperature Storage Time

125 ˚C 24 hours

27

5. ELECTRICAL SPECIFICATIONS

*

Absolute Maximum Ratings (TA = 25 ˚C)

Parameter Symbol Conditions Ratings Unit

Supply voltage VDD VDD – AVDD1 ≤ 0.5 V –0.5 to +7.0 V

AVDD1 VDD – AVDD2 ≤ 0.5 V –0.5 to +7.0 V

AVDD2 AVDD1 – AVDD2 ≤ 0.5 V –0.5 to +7.0 V

AVSS1 –0.5 to +0.5 V

AVSS2 –0.5 to +0.5 V

Input voltage VI –0.5 to VDD+0.5 V

Analog input voltage VIAN VDD ≥ AVDD2 –0.5 to AVDD2+0.5 V

(ANI0-ANI11)

Output voltage VO –0.5 to VDD+0.5 V

Output current, low

Output current, high

Operating ambient TA –10 to +70 ˚C

temperature

Storage temperature T stg –65 to +150 ˚C

IOL Per pin 15 mA

IOH Per pin –10 mA

VDD < AVDD2 –0.5 to VDD+0.5 V

Total of all output pins 100 mA

Total of all output pins –50 mA

µ

PD78P4916

Caution If any of the above parameters exceeds the absolute maximum ratings, even momentarily,

device reliability may be impaired. The absolute maximum ratings are values that may

physically damage the product. Be sure to use the product within the ratings.

Operating Conditions

Clock frequency

4 MHz ≤ fXX ≤ 16 MHz –10 to +70 ˚C All functions +4.5 to +5.5 V

32 kHz ≤ fXT ≤ 35 kHz Subclock operation (CPU, watch, +2.7 to +5.5 V

Operating ambient

temperature (TA)

Operating condition Supply voltage (VDD)

CPU function only +4.0 to +5.5 V

and Port functions only)

28

µ

PD78P4916

Oscillator Characteristics (Main Clock) (TA = –10 to +70 ˚C, VDD = AVDD = 4.0 to 5.5 V, VSS = AVSS = 0 V)

Resonator Recommended circuit Item MIN. MAX. Unit

Crystal resonator Oscillation frequency (fXX) 4 16 MHz

X1 X2 V

C1 C2

SS

Oscillator Characteristics (Subclock) (TA = –10 to +70 ˚C, VDD = AVDD = 2.7 to 5.5 V, VSS = AVSS = 0 V)

Resonator Recommended circuit Item MIN. MAX. Unit

Crystal resonator Oscillation frequency (fXT) 32 35 kHz

XT1 XT2 V

C1 C2

SS

Caution When using the main system clock and subsystem clock oscillators, wiring in the area enclosed

with the dotted lines should be carried out as follows to avoid an adverse effect from wiring

capacitance:

• Wiring should be as short as possible.

• Wiring should not cross other signal lines.

Wiring should not be placed close to a varying high current.

• The potential of the oscillator capacitor ground should be the same as V

SS.

Do not ground wiring to a ground pattern in which high current flows.

• Do not fetch a signal from the oscillator.

As the amplification degree of the subsystem clock oscillator is low to reduce current

consumption, pay particular attention to the wiring method.

29

µ

PD78P4916

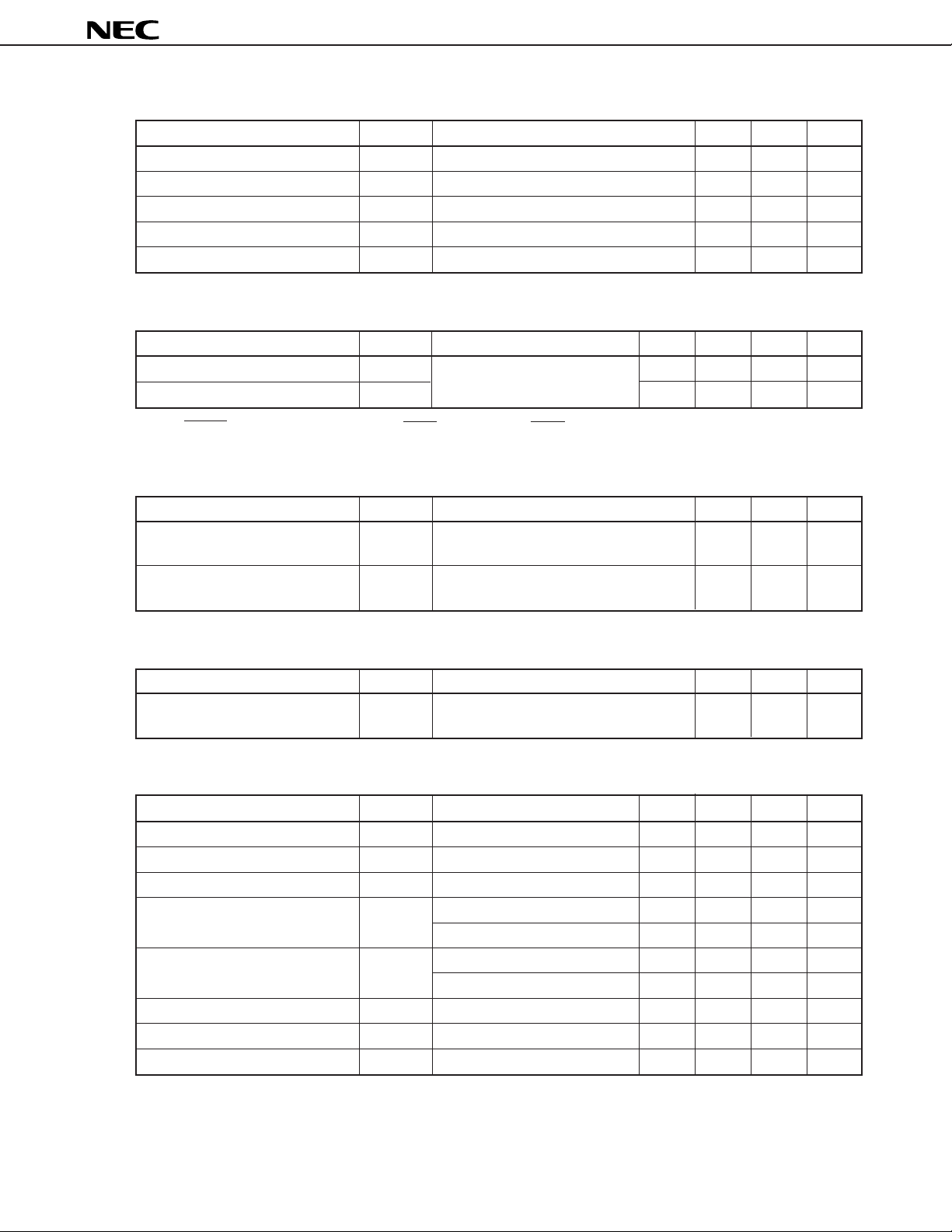

DC Characteristics (TA = –10 to +70 ˚C, VDD = AVDD = 4.5 to 5.5 V, VSS = AVSS = 0 V)

Parameter Symbol Conditions MIN. TYP. MAX. Unit

Input voltage, low VIL1 Other than pins indicated in Note 1 below 0 0.3VDD V

VIL2 Pins indicated in Note 1 below 0 0.2VDD V

VIL3 X1, X2 0 0.4 V

Input voltage, high VIH1 Other than pins indicated in Note 1 below 0.7VDD VDD V

VIH2 Pins indicated in Note 1 below 0.8VDD VDD V

VIH3 X1, X2 VDD–0.5 VDD V

Output voltage, low VOL1 IOL = 5.0 mA (Pins listed in Note 2 below) 0.6 V

VOL2 IOL = 2.0 mA 0.45 V

VOL3 IOL = 100 µA 0.25 V

Output voltage, VOH1 IOH = –1.0 mA VDD–1.0 V

high VOH2 IOH = –100 µAVDD–0.4 V

Input leakage current

Output leakage ILO 0 ≤ VO ≤ VDD ±10

current

VDD power supply IDD1 Operation mode fXX = 16 MHz 35 55 mA

current

Data retention voltage

Data retention IDDDR STOP mode Subclock oscillation 36 75

Note 3

current

Pull-up resistor RL VI = 0 V 25 55 110 kΩ

ILI 0 ≤ VI ≤ VDD ±10

fXX = 8 MHz (Low frequency

oscillation mode)

Internal main clock operation

at 8 MHz

fXT = 32.768 kHz 0.9 1.2 mA

Subclock operation

(CPU, Watch, Port)

VDD = 2.7 V

IDD2 HALT mode fXX = 16 MHz 15 27.5 mA

fXX = 8 MHz (Low frequency

oscillation mode)

Internal main clock operation

at 8 MHz

fXT = 32.768 kHz 30 60

Subclock operation

(CPU, Watch, Port)

VDD = 2.7 V

VDDDR STOP mode 2.5 V

VDDDR = 5.0 V

STOP mode Subclock oscillation 3.5 15

VDDDR = 2.7 V

STOP mode Subclock suspended 1.5 10

VDDDR = 2.5 V

µ

A

µ

A

µ

A

µ

A

µ

A

µ

A

Notes 1. RESET, IC, NMI, INTP0-INTP2, P61/SCK1/BUZ, P63/SI1, SCK2, SI2/BUSY, P65/HWIN,

P91/KEY0-P95/KEY4.

2. P46, P47

3. When subclock is suspended at STOP mode, disconnect feedback resistor and connect XT1 pin to

the VDD potential.

30

µ

PD78P4916

AC Characteristics

CPU and peripheral unit operation clocks (TA = –10 to +70 ˚C, VDD = AVDD = 4.5 to 5.5 V, VSS = AVSS = 0 V)

Parameter Symbol Conditions TYP. Unit

CPU operation clock cycle time

Peripheral unit operation clock

cycle time

tCLK fXX = 16 MHz V DD = AVDD = 4.0 to 5.5 V 125 ns

CPU function only

fXX = 16 MHz

fXX = 8 MHz, Low frequency oscillation mode (CC bit7 = 1)

tCLK1 fXX = 16 MHz 125 ns

fXX = 8 MHz, Low frequency oscillation mode (CC bit7 = 1)

Serial interface

(1) SIOn: n = 1, 2 (TA = –10 to +70 ˚C, VDD = AVDD = 4.5 to 5.5 V, VSS = AVSS = 0 V)

Parameter Symbol Conditions MIN. MAX. Unit

Serial clock cycle time tCYSK Input External clock 1.0

Output fCLK1/8 1.0

fCLK1/16 2.0

fCLK1/32 4.0

fCLK1/64 8.0

fCLK1/128 16

fCLK1/256 32

Serial clock high/low level width tWSKH Input External clock 420 ns

tWSKL Output Internal clock

SIn set-up time (to SCKn ↑)tSSSK 100 ns

SIn hold time (from SCKn ↑)tHSSK 400 ns

SOn output delay time (from SCKn ↓)

tDSSK 0 300 ns

tCYSK/2–50

µ

µ

µ

µ

µ

µ

µ

ns

s

s

s

s

s

s

s

Remarks 1. fCLK1: Operation clock for peripheral unit (8 MHz)

2. n = 1, 2

(2) Only SIO2 (T

SCK2(8) ↑ → STRB ↑ tDSTRB tWSKH tCYSK

Strobe high level width tWSTRB tCYSK–30 tCYSK+30 ns

BUSY setup time (to BUSY detection timing)

BUSY hold time (from BUSY detection timing)

Busy inactive → SCK2(1) ↓ tLBUSY

A= –10 to +70 ˚C, VDD = AVDD = 4.5 to 5.5 V, VSS = AVSS = 0 V)

Parameter Symbol Conditions MIN. MAX. Unit

tSBUSY 100 ns

tHBUSY 100 ns

tCYSK+tWSKH

Remarks 1. The value in the parentheses following SCK2 indicates the sequential number of the SCK2.

2. BUSY detection timing is (n + 2) × t

CYSK (n = 0, 1,...) after SCK2(8) ↑.

3. BUSY inactive → SCK2(1) ↓ is a value at the time data is already written in SIO2.

31

µ

PD78P4916

Other Operations (TA = –10 to +70 ˚C, VDD = AVDD = 4.5 to 5.5 V, VSS = AVSS = 0 V)

Parameter Symbol Conditions MIN. MAX. Unit

Timer unit input low level width tWCTL at DFGIN, CFGIN, DPGIN, REEL0IN, tCLK1 ns

REEL1IN logic level input

Timer unit input high level width tWCTH at DFGIN, CFGIN, DPGIN, REEL0IN, tCLK1 ns

REEL1IN logic level input

Timer unit input signal valid edge tPERIN DFGIN, CFGIN and DPGIN input 2

input cycle

CSYNCIN low level width tWCR1L Digital noise eliminator not used 8tCLK1 ns

Digital noise eliminator used 108t CLK1 ns

(INTM2 bit 4 = 0)

Digital noise eliminator used 180t CLK1 ns

(INTM2 bit 4 = 1)

CSYNCIN high level width tWCR1H Digital noise eliminator not used 8tCLK1 ns

Digital noise eliminator used 108t CLK1 ns

(INTM2 bit 4 = 0)

Digital noise eliminator used 180t CLK1 ns

(INTM2 bit 4 = 1)

Digital noise Eliminated pulse tWSEP INTM2 bit 4 = 0 104tCLK1 ns

eliminator width

Passed pulse width INTM2 bit 4 = 0 108tCLK1 ns

NMI low level width tWNIL VDD = AVDD = 2.7 to 5.5 V 10

NMI high level width tWNIH VDD = AVDD = 2.7 to 5.5 V 10

INTP0 and INTP3 low level width

INTP0 and INTP3 high level width

INTP1, KEY0 - KEY4 low level tWIPL1 Other than in STOP mode 2tCLK1 ns

width

INTP1, KEY0 - KEY4 high level tWIPH1 Other than in STOP mode 2tCLK1 ns

width

INTP2 low level width tWIPL2

INTP2 high level width tWIPH2

RESET low level width tWRSL 10

tWIPL0 2tCLK1 ns

tWIPH0 2tCLK1 ns

INTM2 bit 4 = 1 176tCLK1 ns

INTM2 bit 4 = 1 180tCLK1 ns

When cancelling STOP mode 10

When cancelling STOP mode 10

Main clock opera

in normal mode

Subclock operation Sampled at fCLK 61

in normal mode

When cancelling STOP mode 10

Main clock operation

in normal mode

Subclock operation Sampled at fCLK 61

in normal mode

When cancelling STOP mode 10

tion Sampled at fCLK 2tCLK1 ns

Sampled at fCLK/128 32

Sampled at fCLK/128 7.9

Sampled at fCLK 2tCLK1 ns

Sampled at fCLK/128 32

Sampled at fCLK/128 7.9

Note

Note

Note

Note

µ

µ

µ

µ

µ

µ

µ

ms

µ

µ

µ

ms

µ

µ

s

s

s

s

s

s

s

s

s

s

s

s

Note If a high level or low level is input two times in succession during the sampling period, high level or low

level is detected.

Remark t

CLK1: Operation clock cycle time for peripheral unit (125 ns).

32

µ

PD78P4916

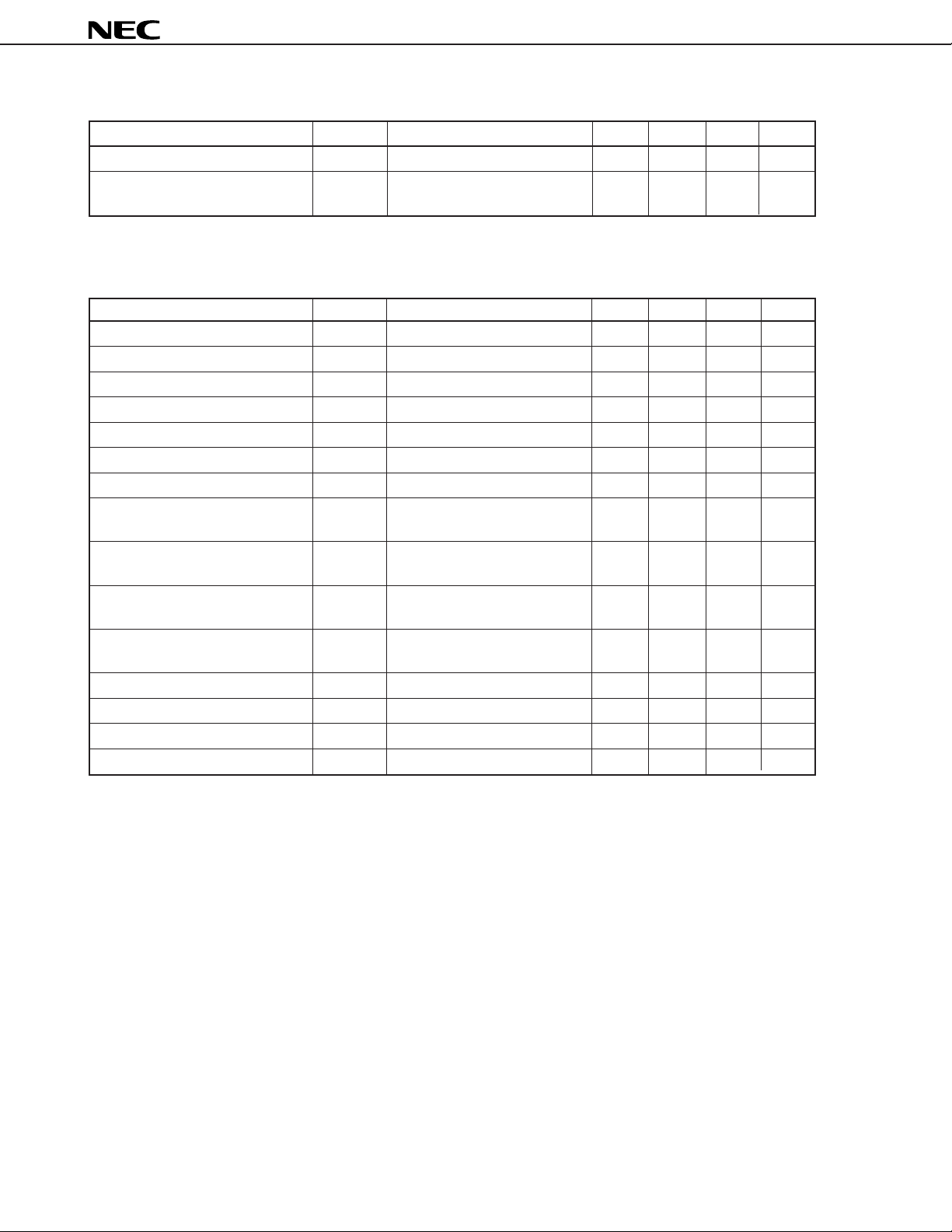

Clock Output Operation (TA = –10 to +70 ˚C, VDD = AVDD = 4.5 to 5.5 V, VSS = AVSS = 0 V)

Parameter Symbol Expression MIN. MAX. Unit

CLO cycle time tCYCL 250 2000 ns

CLO low level width tCLL tCYCL/2 ± 50 75 1050 ns

CLO high level width tCLH tCYCL/2 ± 50 75 1050 ns

CLO rising time tCLR 50 ns

CLO falling time tCLF 50 ns

Data Retention Characteristics (TA = –10 to +70 ˚C, VDD = AVDD = 2.5 to 5.5 V, VSS = AVSS = 0 V)

Parameter Symbol Conditions MIN. TYP. MAX. Unit

Input voltage, low VIL Pins listed in Note below 0 0.1VDDDR V

Input voltage, high VIH 0.9VDDDR VDDDR V

Note

RESET, IC, NMI, INTP0-INTP2, P61/SCK1/BUZ, P63/SI1, SCK2, SI2/BUSY, P65/HWIN, P91/KEY0-P95/KEY4

Watch Function (TA = –10 to +70 ˚C, VDD = AVDD = 2.7 to 5.5 V, VSS = AVSS = 0 V)

Parameter Symbol Conditions MIN. MAX. Unit

Subclock oscillation retention VDDXT 2.7 V

voltage

Hardware watch function operation VDDW 2.7 V

voltage

Subclock Oscillation Suspension Detection Flag (TA = –10 to +70 ˚C, VDD = AVDD = 4.5 to 5.5 V, VSS = AVSS = 0 V)

Parameter Symbol Conditions MIN. MAX. Unit

Oscillation suspension detection tOSCF 45

width

µ

s

A/D Converter Characteristics (TA = –10 to +70 ˚C, VDD = AVDD = AVREF = 4.5 to 5.5 V, VSS = AVSS = 0 V)

Parameter Symbol Conditions MIN. TYP. MAX. Unit

Resolution 8 bit

Total error AVREF = VDD 2.0 %

Quantization error ±1/2 LSB

Conversion time tCONV ADM bit 4 = 0 160tCLK1

ADM bit 4 = 1 80tCLK1

Sampling time tSAMP ADM bit 4 = 0 32tCLK1

ADM bit 4 = 1 16tCLK1

Analog input voltage VIAN 0AVREF V

Analog input impedance ZAN 1000 MΩ

AVREF current AIREF 0.4 1.2 mA

µ

s

µ

s

µ

s

µ

s

33

µ

PD78P4916

VREF Amplifier (TA = 25 ˚C, VDD = AVDD = 5 V, VSS = AVSS = 0 V)

Parameter Symbol Conditions MIN. TYP. MAX. Unit

Reference voltage VREF 2.35 2.50 2.65 V

Charge current ICHG AMPM0.0 is set to 1 300

for pins listed in Note below.

µ

A

Note RECCTL+, RECCTL–, CFGIN, CFGCPIN, DFGIN, DPGIN, CSYNCIN, REEL0IN, REEL1IN

CTL Amplifier (TA = 25 ˚C, VDD = AVDD = 5 V, VSS = AVSS = 0 V)

Parameter Symbol Conditions MIN. TYP. MAX. Unit

CTL+, – input resistance RICTL 2510kΩ

Feedback resistance RFCTL 20 50 100 kΩ

Bias resistance RBCTL 20 50 100 kΩ

Minimum voltage gain GCTLMIN 17 20 22 dB

Maximum voltage gain GCTLMAX 71 75 dB

Gain switching step SGAIN 1.77 dB

Common mode signal rejection CMR DC, Voltage gain: 20 dB 50 dB

Comparator set voltage for VPBCTLHS

waveform regulation, high

Comparator reset voltage for VPBCTLHR

waveform regulation, high

Comparator set voltage for VPBCTLLS

waveform regulation, low

Comparator reset voltage for VPBCTLLR

waveform regulation, low

Comparator high voltage for CLT flag S

Comparator low voltage for CLT flag S

Comparator high voltage for CLT flag L

Comparator low voltage for CLT flag L

VFSH

VFSL

VFLH

VFLL

VREF+0.47 VREF+0.50 VREF+0.53

VREF+0.27 VREF+0.30 VREF+0.33

VREF–0.53 VREF–0.50 VREF –0.47

VREF–0.33 VREF–0.30 VREF –0.27

VREF+1.00 VREF+1.05 VREF+1.10

VREF–1.10 VREF–1.05 VREF –1.00

VREF+1.40 VREF+1.45 VREF+1.50

VREF–1.50 VREF–1.45 VREF –1.40

V

V

V

V

V

V

V

V

34

µ

PD78P4916

CFG Amplifier (AC Coupling) (TA = 25 ˚C, VDD = AVDD = 5 V, VSS = AVSS = 0 V)

Parameter Symbol Conditions MIN. TYP. MAX. Unit

Voltage gain 1 GCFG1 fi = 2 kHz, open loop 50 dB

Voltage gain 2 GCFG2 fi = 2 kHz, open loop 34 dB

CFGAMPO output current, high IOHCFG DC –1 mA

CFGAMPO output current, low IOLCFG DC 0.4 mA

Comparator high voltage V CFGH

Comparator low voltage VCFGL

Duty precision PDUTY See Note below. 49.7 50.0 50.3 %

VREF+0.09 VREF+0.12

VREF–0.15 VREF–0.12

VREF+0.15

VREF–0.09

Note The following circuit and input signal conditions are assumed.

µ

• Input signal: sine wave input (5 mV

p-p), fi = 1 kHz

1 kΩ

PD78P4916

• Voltage gain: 50 dB

22 µF

330 kΩ

0.01 µF

CFGIN

CFGAMPO

V

V

CFGCPIN

DFG Amplifier (AC Coupling) (TA = 25 ˚C, VDD = AVDD = 5 V, VSS = AVSS = 0 V)

Parameter Symbol Conditions MIN. TYP. MAX. Unit

Voltage gain GDFG fi = 900 Hz, open loop 50 dB

Feedback resistance RFDFG 160 400 640 kΩ

Input protect resistance RIDFG 150 Ω

Comparator high voltage V DFGH

Comparator low voltage VDFGL

VREF+0.07 VREF+0.10 VREF+0.14

VREF–0.14 VREF–0.10 VREF –0.07

V

V

Caution The resistance of the pin to be connected to the DFGIN pin must be below 16 kΩ . If the resistance

is higher than the limit, the DFG amplifier may oscillate.

DPG Comparator (AC Coupling) (T

Parameter Symbol Conditions MIN. TYP. MAX. Unit

Input impedance ZIDPG 20 50 100 kΩ

Comparator high voltage VDPGH

Comparator low voltage VDPGL

A = 25 ˚C, VDD = AVDD = 5 V, VSS = AVSS = 0 V)

VREF+0.02 VREF+0.05 VREF+0.08

VREF–0.08 VREF–0.05 VREF –0.02

V

V

35

µ

PD78P4916

Three-value divider (TA = 25 ˚C, VDD = AVDD = 5 V, VSS = AVSS = 0 V)

Parameter Symbol Conditions MIN. TYP. MAX. Unit

Input impedance ZIPFG 20 50 100 kΩ

Comparator high voltage VPFGH VREF+0.5 VREF+0.7 VREF +0.9 V

Comparator low voltage VPFGL VREF–1.4 VREF–1.2 VREF–1.0 V

CSYNC Comparator (AC Coupling) (TA = 25 ˚C, VDD = AVDD = 5 V, VSS = AVSS = 0 V)

Parameter Symbol Conditions MIN. TYP. MAX. Unit

Input impedance ZICSYN 20 50 100 kΩ

Comparator high voltage VCSYNH

Comparator low voltage VCSYNL

VREF+0.07 VREF+0.10 VREF+0.13

VREF–0.13 VREF–0.10 VREF –0.07

Reel FG Comparator (AC Coupling) (TA = 25 ˚C, VDD = AVDD = 5 V, VSS = AVSS = 0 V)

Parameter Symbol Conditions MIN. TYP. MAX. Unit

Input impedance ZIRLFG 20 50 100 kΩ

Comparator high voltage VRLFGH

Comparator low voltage VRLFGL

VREF+0.02 VREF+0.05 VREF+0.08

VREF–0.08 VREF–0.05 VREF –0.02

V

V

V

V

RECCTL Driver (TA = 25 ˚C, VDD = AVDD = 5 V, VSS = AVSS = 0 V)

Parameter Symbol Conditions MIN. TYP. MAX. Unit

RECCTL+, – high level output voltage

RECCTL+, – low level output voltage

CTLDLY on-chip resistor RCTL 40 70 140 kΩ

CTLDLY charge current IOHCTL On-chip resistor disabled –3 mA

CTLDLY discharge current IOLCTL –3 mA

VOHREC IOH = –4 mA

VOLREC IOL = 4 mA

VDD–0.8 V

0.8 V

36

Timing Waveform

AC timing test point

µ

PD78P4916

0.8 VDD or 2.2 V

0.8 V

Serial Transfer Timing (SIOn: n = 1, 2)

WSKL

t

SCKn

t

CYSK

SIn

SOn

t

WSKH

Test points

t

DSSK

Output data

0.8 VDD or 2.2 V

0.8 V

t

SSSKtHSSK

Input data

37

Serial Transfer Timing (Only SIO2)

No busy processing

t

WSKL

t

WSKH

µ

PD78P4916

SCK2

BUSY

78

t

CYSK

At active-high

STRB

Continue busy processing

t

WSKL

SCK2

BUSY

STRB

78

t

CYSK

At active-high

t

WSKH

t

DSTRB

t

DSTRB

9101

Invalid busy

t

WSTRB

9 10 10+n

t

SBUSY

t

WSTRB

t

HBUSY

2

Terminate busy processing

SCK2

BUSY

WSKL

t

78

t

WSKH

t

CYSK

At active-high

9 11+n

10+n

t

HBUSY

t

LBUSY

Caution Do not use busy control and strobe control whenever the external clock is selected as a serial

clock.

1

38

Super timer unit input timing

At DFGIN, CFGIN, DPGIN, REEL0IN

and REEL1IN logic level input

At CSYNCIN logic level input

Interrupt input timing

0.8 V

0.8 V

µ

PD78P4916

t

WCTH

DD

t

WCTL

0.8 V

t

WCR1H

DD

t

WCR1L

0.8 V

NMI

INTP0, INTP3

INTP1, KEY0 - KEY4

INTP2

0.8 V

0.8 V

0.8 V

0.8 V

t

WNIH

DD

t

WNIL

0.8 V

t

WIPH0

DD

t

WIPL0

0.8 V

t

WIPH1

DD

t

WIPL1

0.8 V

t

WIPH2

DD

t

WIPL2

0.8 V

Reset input timing

RESET

0.8 V

t

WRSL

39

Clock output timing

CLO

0.8 V

0.8 V

µ

PD78P4916

t

CLH

DD

t

CLR

t

CYCL

t

CLF

t

CLL

40

DC Programming Characteristics (TA = +25 ± 5 ˚C, VSS = AVSS = 0 V)

µ

PD78P4916

Parameter

Input voltage, high VIH VIH 2.4 VDDP+0.3 V

Input voltage, low VIL VIL –0.3 0.8 V

Input leakage current ILIP ILI 0 ≤ VI ≤ VDDP

Output voltage, high VOH1 VOH1 IOH = –400 µA 2.4 V

Output voltage, low VOL VOL IOL = 2.1 mA 0.45 V

Output leakage current ILO 0 ≤ VO ≤ VDDP, OE = VIH ±10

VDD supply voltage VDDP VDD Program memory write 6.25 6.5 6.75 V

VPP supply voltage VPP VPP Program memory write 12.2 12.5 12.8 V

VDD supply current IDD IDD Program memory write 50 mA

VPP supply current IPP IPP Program memory write 50 mA

Symbol Symbol

VOH2 VOH2 IOH = –100 µAVDDP–0.7 V

Note 1

Conditions MIN. TYP. MAX. Unit

Note 2

mode

Program memory read 4.50 5.0 5.50 V

mode

mode

Program memory read VPP = VDDP V

mode

mode

Program memory read 30 mA

mode

mode

Program memory read 1 100

mode

±10

µ

µ

µ

A

A

A

Notes 1. Corresponding symbols of the µPD27C1001A.

2. V

DDP is a VDD pin during programming.

41

AC Programming Characteristics (TA = +25 ± 5 ˚C, VSS = AVSS = 0 V)

PROM Write Operation Mode (Page Programming Mode)

µ

PD78P4916

Parameter

Address setup time tAS 2

CE set time tCES 2

Input data setup time tDS 2

Address hold time tAH 2

Input data hold time tDH 2

Output data hold time tDF 0 230 ns

VPP setup time tVPS 2

VDDP setup time tVDS

Initial programming pulse width tPW 0.095 0.1 0.105 ms

OE set time tOES 2

OE → valid data delay time tOE 1

OE pulse width during data latch tLW 1

PGM set-up time tPGMS 2

CE hold time tCEH 2

OE hold time tOEH 2

Note 1

Symbol

tAHL 2

tAHV 0

Note 2

Conditions MIN. TYP. MAX. Unit

µ

µ

µ

µ

µ

µ

µ

µ

2

µ

µ

µ

µ

µ

µ

µ

s

s

s

s

s

s

s

s

s

s

s

s

s

s

s

Notes 1. Correspond to symbols of the µPD27C1001A (except tVDS).

VDS corresponds to tVCS of the

2. t

µ

PD27C1001A.

42

PROM Write Mode (Byte Programming Mode)

µ

PD78P4916

Parameter

Address setup time tAS 2

CE set time tCES 2

Input data setup time tDS 2

Address hold time tAH 2

Input data hold time tDH 2

Output data hold time tDF 0 130 ns

VPP setup time tVPS 2

VDDP setup time tVDS

Initial programming pulse width tPW 0.095 0.1 0.105 ms

OE set time tOES 2

OE → valid data delay time tOE 150 ns

Symbol

Note 1

Note 2

Conditions MIN. TYP. MAX. Unit

2

Notes 1. Correspond to symbols of the µPD27C1001A (except tVDS).

2. t

VDS corresponds to tVCS of the

µ

PD27C1001A.

PROM Read Mode

Parameter

Address → data output time tACC CE = OE = VIL 200 ns

CE ↓ → data output time tCE OE = VIL 200 ns

OE ↓ → data output time tOE CE = VIL 75 ns

Data hold time (from OE ↑, CE ↑)

Data hold time (

from

address) tOH CE = OE = VIL 0ns

Note 2

Note 1

Symbol

tDF CE = VIL or OE = VIL 060ns

Conditions MIN. TYP. MAX. Unit

µ

s

µ

s

µ

s

µ

s

µ

s

µ

s

µ

s

µ

s

Notes 1. Correspond to symbols of the µPD27C1001A.

2. t

DF is a time after either OE or CE rose to VIH first.

43

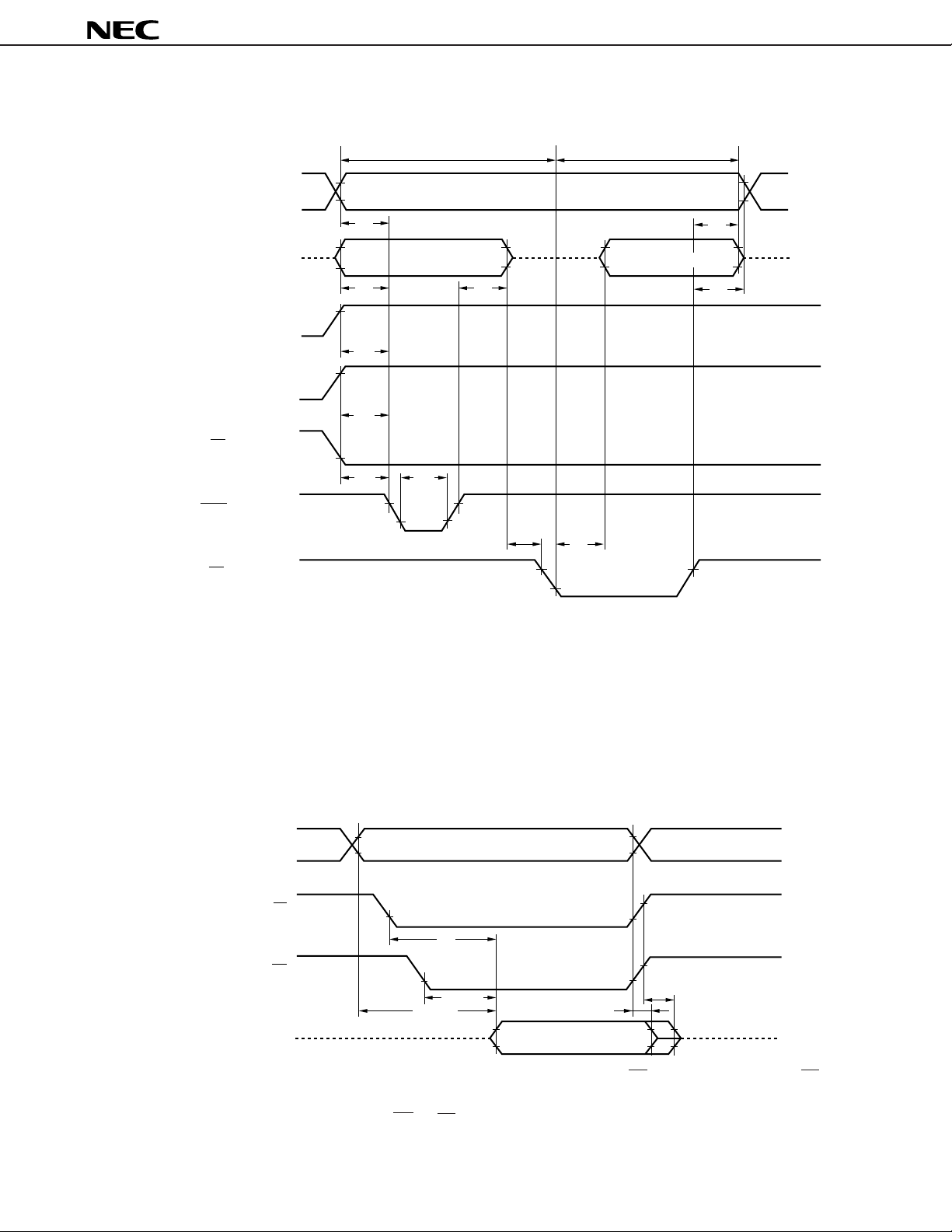

PROM Write Mode Timing (Page Programming Mode)

Page data latch Page programming Program verify

A2 - A16

t

AS

A0, A1

t

AHL

µ

PD78P4916

t

AHV

V

V

DDP

CE

PGM

OE

PP

D0 - D7

V

DDP

V

V

DDP

+1.5

V

DDP

V

V

V

V

V

V

DS

t

Hi-Z

t

VPS

PP

t

VDS

IH

IL

IH

IL

IH

IL

t

Data input

LW

t

DH

Hi-Z

t

t

OE

CEH

t

PGMS

t

PW

t

CES

t

DH

Data

output

t

OES

t

OEH

Hi-Z

t

AH

44

PROM Write Mode Timing (Byte Programming Mode)

Programming Program verify

A0 - A16

t

AS

V

V

DDP

CE

PGM

OE

PP

D0 - D7

V

V

DDP

VDD+1.5

V

DDP

V

V

V

V

V

V

PP

IH

IL

IH

IL

IH

IL

Data input Data output

t

t

t

t

DS

VPS

VDS

CES

t

PW

t

DH

µ

PD78P4916

t

DF

Hi-Z

t

OES

t

OE

Hi-ZHi-Z

t

AH

Cautions1. Apply voltage to V

DDP before applying voltage to VPP, and cut off VDDP voltage after VPP voltage

is cut off.

2. The voltage, including overshoot, applied to V

3. If a device is inserted or removed while +12.5 V is applied to V

affected in reliability.

PROM Read Mode Timing

A0 - A16

CE

OE

D0 - D7

Hi-Z

Notes 1. If data need to be read within t

should be t

DF is the time after either OE or CE first rose to VIH.

2. t

ACC – tOE.

PP pin must be kept less than +13.5 V.

PP pin, it may be adversely

Valid address

t

CE

Note 2

t

Note 1

t

OE

Note 1

t

ACC

t

OH

Data output

ACC, the maximum delay time of OE active level input from CE falling

DF

Hi-Z

45

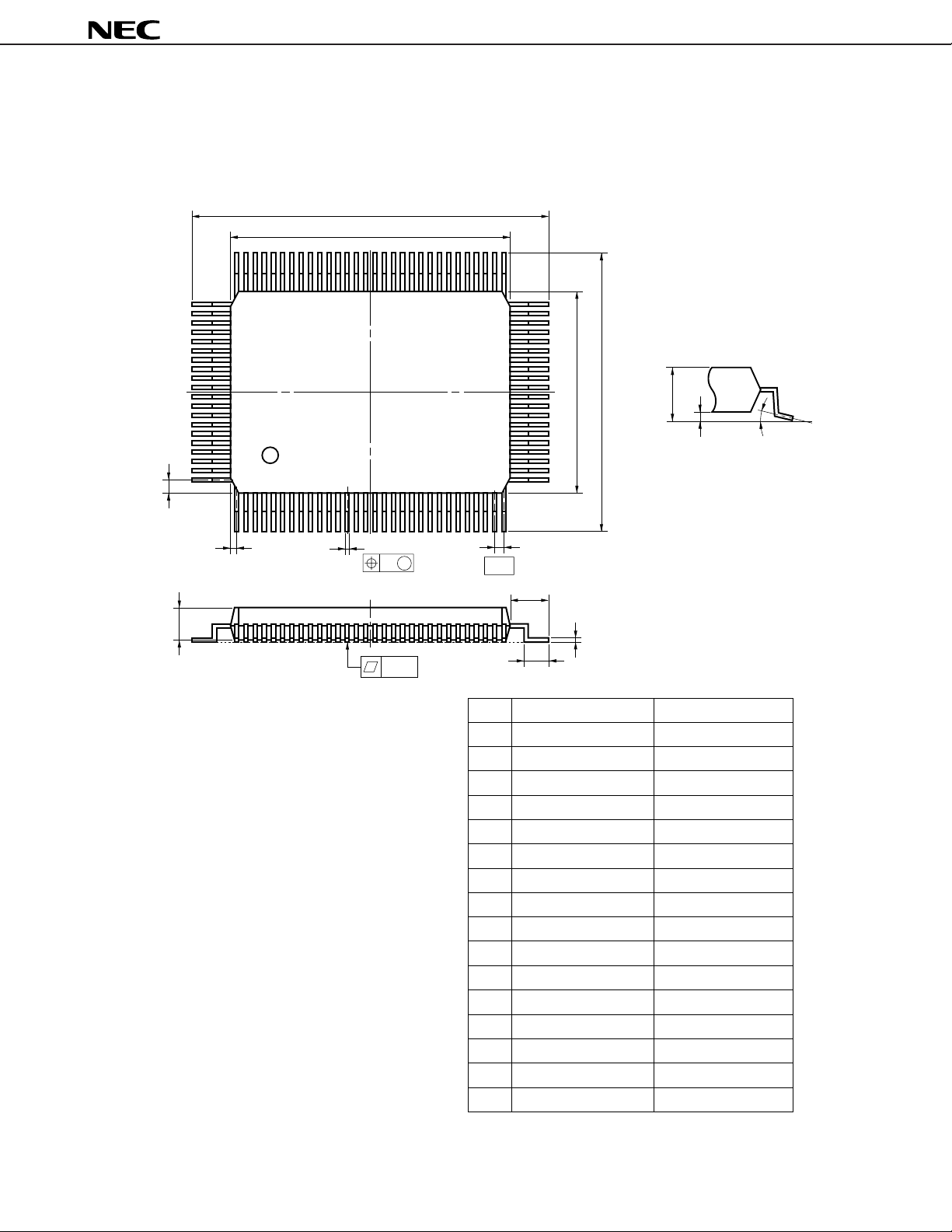

6. PACKAGE DRAWING

100 PIN PLASTIC QFP (14 × 20)

µ

PD78P4916

A

B

80

81

100

F

1

G

H

M

I

P

N

NOTE

Each lead centerline is located within 0.15

mm (0.006 inch) of its true position (T.P.) at

maximum material condition.

51

50

C

D

detail of lead end

S

Q

31

30

J

K

M

L

P100GF-65-3BA1-2

ITEM MILLIMETERS INCHES

A

B

C

D

F

G

H

I

J

K

L

M

N

23.6±0.4

20.0±0.2

14.0±0.2

17.6±0.4

0.8

0.6

0.30±0.10

0.15

0.65 (T.P.)

1.8±0.2

0.8±0.2

+0.10

0.15

–0.05

0.10

0.929±0.016

+0.009

0.795

–0.008

+0.009

0.551

–0.008

0.693±0.016

0.031

0.024

+0.004

0.012

–0.005

0.006

0.026 (T.P.)

+0.008

0.071

–0.009

+0.009

0.031

–0.008

+0.004

0.006

–0.003

0.004

P 2.7 0.106

Q

0.1±0.1

0.004±0.004

S 3.0 MAX. 0.119 MAX.

5°

±

5°

46

µ

PD78P4916

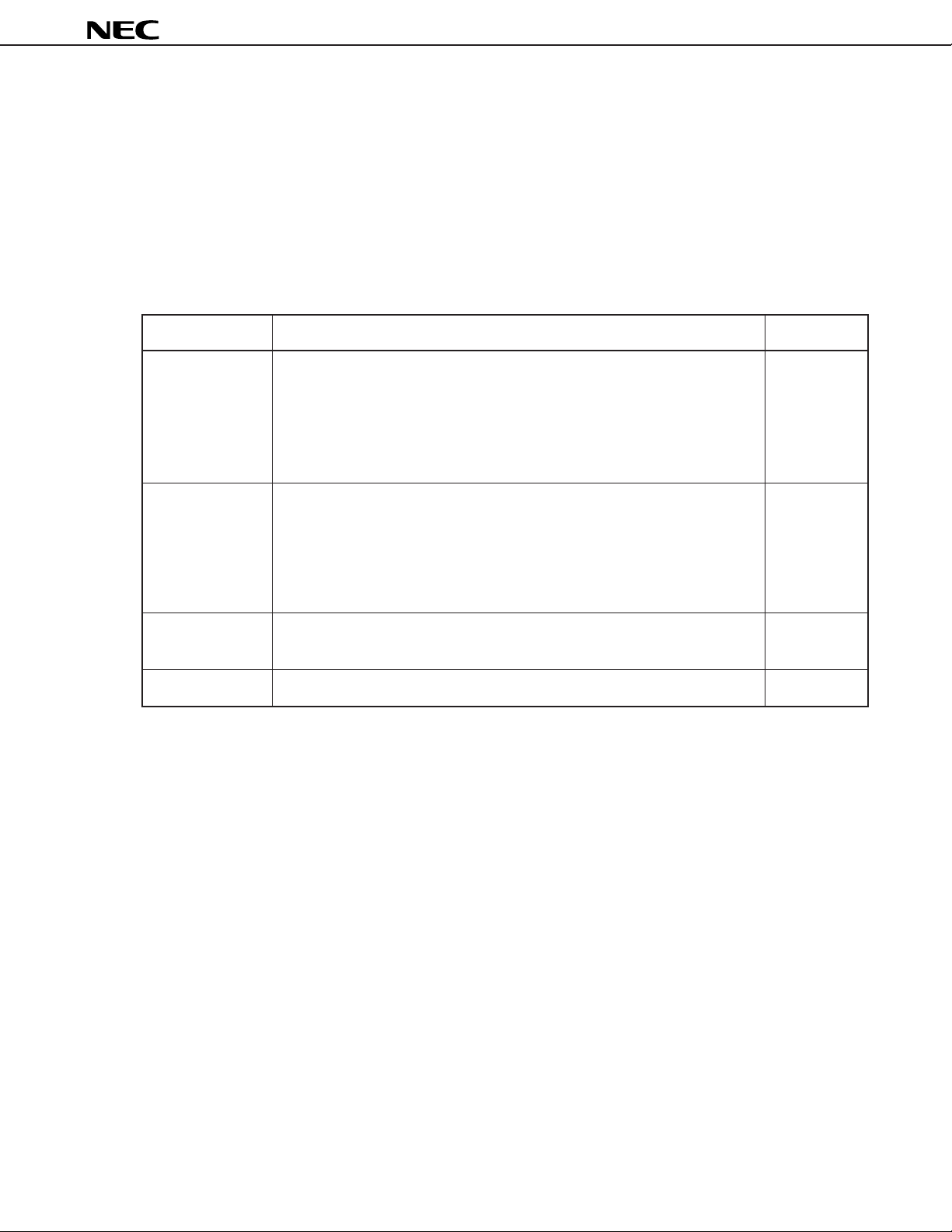

7. RECOMMENDED SOLDERING CONDITIONS

This device should be soldered and mounted under the following conditions.

For details about the recommended conditions, refer to the document “Semiconductor Device Mounting

Technology Manual” (C10535E). For soldering methods and conditions other than those recommended below,

contact your NEC sales representative.

Table 7-1. Surface Mounting Type Soldering Conditions

µ

PD78P4916GF-3BA: 100-pin plastic QFP (14 x 20 mm)

Soldering Method Soldering Conditions Symbol

Infrared rays reflow Peak package's surface temperature: 235 ˚C, Reflow time: 30 seconds or less IR35-00-2

(at 210 ˚C or higher), Number of reflow processes: 2 or less

<Attention>

(1) Wait for the device temperature to come down to room temperature

after the first reflow before starting the second reflow.

(2) Do not perform flux cleaning of the soldered portion after the first reflow.

*

VPS Peak package's surface temperature: 215 ˚C, Reflow time: 40 seconds or less VP15-00-2

(at 200 ˚C or higher), Number of reflow processes: 2 or less

<Attention>

(1) Wait for the device temperature to come down to room temperature

after the first reflow before starting the second reflow.

(2) Do not perform flux cleaning of the soldered portion after the first reflow.

Wave soldering

Partial heating Pin temperature: 300 ˚C or below, Time: 3 seconds or less (per pin row) —

Caution Do not use different soldering methods together (except for partial heating).

Solder temperature: 260 ˚C or below, Flow time: 10 seconds or less, Number of flow

process: 1, Preheating temperature; 120 ˚C max. (package surface temperature)

WS60-00-1

47

APPENDIX A. DEVELOPMENT TOOLS

*

The following development tools are prepared for system development using the µPD78P4916.

Language Software

µ

PD78P4916

RA78K4

CC78K4

CC78K4-L

Note 1

Note 1

Note 1

Assembler package common to the 78K/IV Series

C compiler package common to the 78K/IV Series

C compiler library source file common to the 78K/IV Series

PROM Writing Tool

PG-1500 PROM programmer

PA-78P4916GF Programmer adapter connected to the PG-1500

PG-1500 Controller

Note 2

Control program for PG-1500

Debugging Tool

IE-784000-R In-circuit emulator common to the 78K/IV Series

IE-784000-R-BK Break board common to the 78K/IV Series

IE-784000-R-EM Emulation board common to the 78K/IV Series

IE-784915-R-EM1 Emulation board for evaluation of the µPD784915 Subseries

IE-78000-R-SV3 Interface adapter when using EWS as a host machine

IE-70000-98-IF-B Interface adapter when using PC-9800 series (except notebook type) as a host

machine

IE-70000-98N-IF Interface adapter and cable when using notebook type PC-9800 series as a host

machine

IE-70000-PC-IF-B Interface adapter when using IBM PC/ATTM as a host machine

EP-784915GF-R Emulation probe common to the µPD784915 subseries

EV-9200GF-100 Conversion socket for 100-pin plastic QFP to mount a device on a target system

SM78K4

ID78K4

DF784915

Note 3

Note 3

Note 4

System emulator for all 78K/IV series devices

Integrated debugger for IE-784000-R

Device file common to the µPD784915 subseries

Real-time OS

*

RX78K/IV

MX78K4

48

Note 4

Note 2

Real-time OS common to the 78K/IV series

OS common to the 78K/IV series

µ

PD78P4916

Notes 1. • PC-9800 series (for MS-DOSTM) based

• IBM PC/AT and compatibles (for PC DOS

TM

• HP9000 series 700

• SPARCstation

• NEWS

2. • PC-9800 series (for MS-DOS) based

• IBM PC/AT and its compatibles (for PC DOS, Windows, MS-DOS, and IBM DOS) based

3. • PC-9800 series (for Windows on MS-DOS) based

• IBM PC/AT and its compatibles (for PC DOS, Windows, MS-DOS, and IBM DOS) based

• HP9000 series 700 (for HP-UX) based

• SPARCstation (for SunOS) based

4. • PC-9800 series (for MS-DOS) based

• IBM PC/AT and compatibles (for PC DOS, Windows, MS-DOS, and IBM DOS) based

• HP9000 series 700 (for HP-UX) based

• SPARCstation (for SunOS) based

Remark The RA78K4, CC78K4, SM78K4, and ID78K4 should be used in combination with the DF784915.

TM

(NEWS-OSTM) based

(for HP-UXTM) based

TM

(for SunOSTM) based

TM

, WindowsTM, MS-DOS, and IBM DOSTM) based

*

49

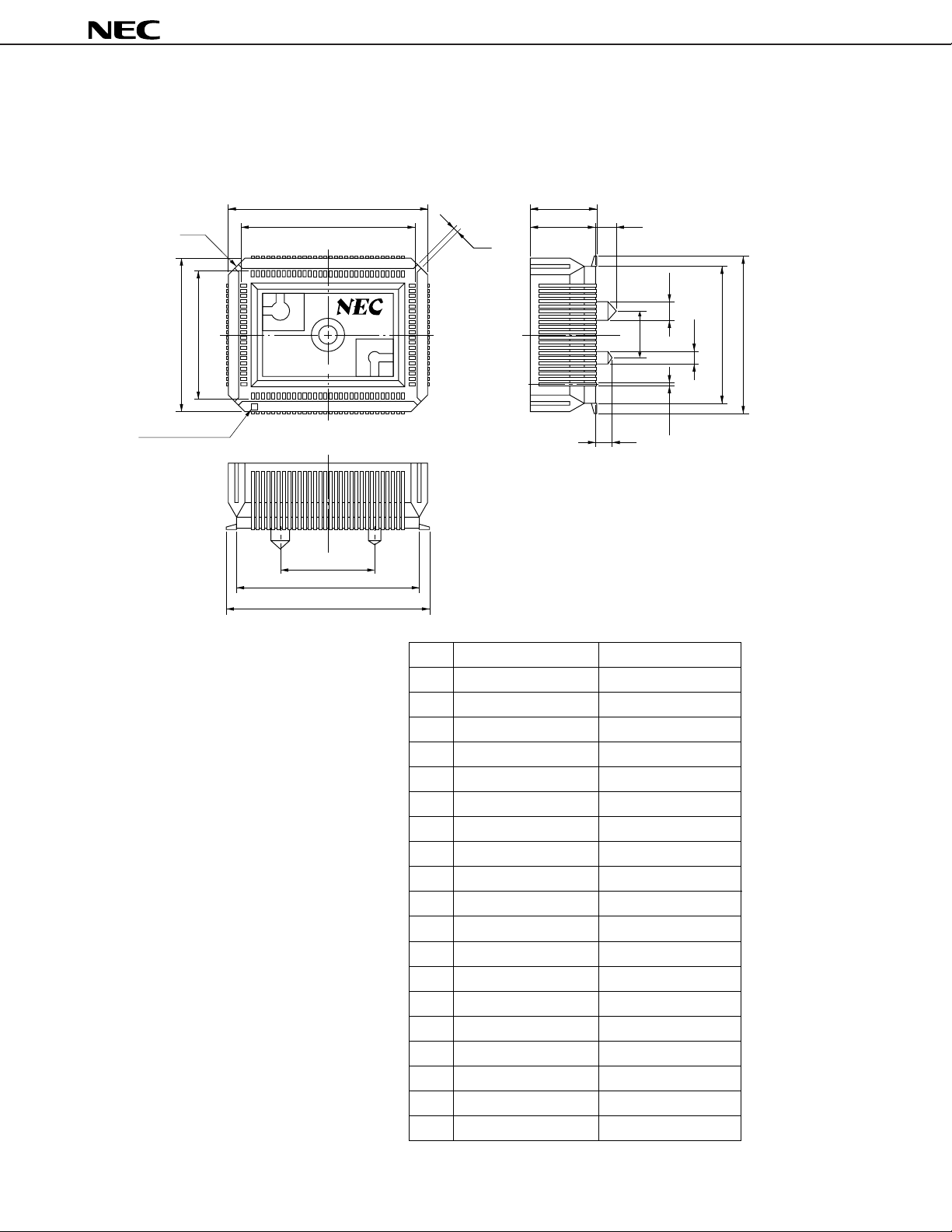

APPENDIX B. SOCKET DRAWING AND RECOMMENDED FOOTPRINT

*

Figure B-1. EV-9200GF-100 Drawing

(For reference purpose only)

µ

PD78P4916

E

D

C

No.1 pin index

EV-9200GF-100

1

A

B

F

G

H

I

ITEM MILLIMETERS INCHES

A

B

C

D

E

F

G

H

I

J

K

L

M

N

O

P

Q

R

S

24.6

21

15

18.6

4-C 2

0.8

12.0

22.6

25.3

6.0

16.6

19.3

8.2

8.0

2.5

2.0

0.35

φ

2.3

φ

1.5

M

N O

EV-9200GF-100-G0

J

P

0.969

0.827

0.591

0.732

4-C 0.079

0.031

0.472

0.89

0.996

0.236

0.654

076

0.323

0.315

0.098

0.079

0.014

φ

0.091

φ

0.059

R

S

Q

L

K

50

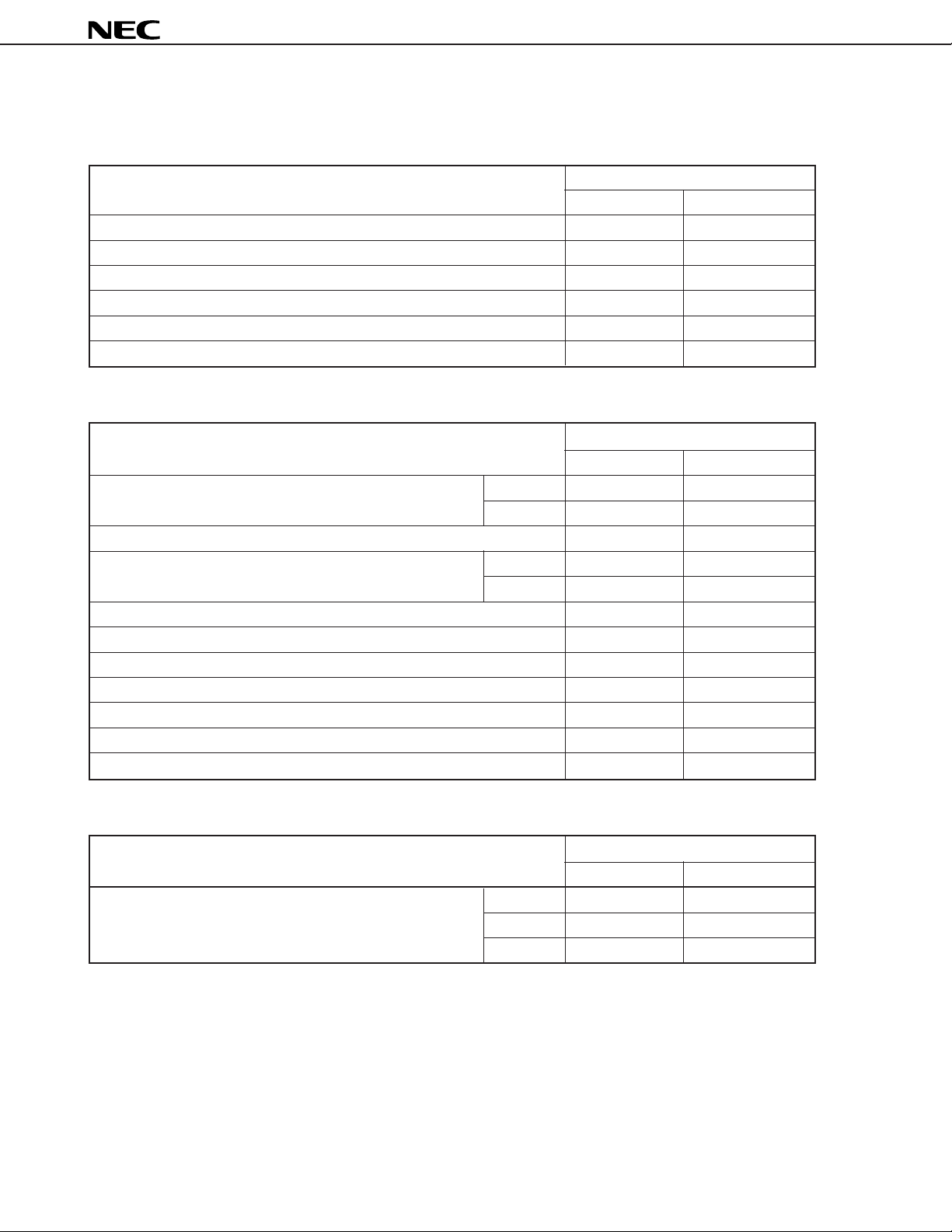

Figure B-2. Recommended EV-9200GF-100 Footprint

(For reference purpose only)

G

J

K

F

E

D

L

C

B

A

µ

PD78P4916

H

I

EV-9200GF-100-P1

ITEM MILLIMETERS INCHES

+0.001

–0.002

+0.001

–0.002

1.035

0.85

0.614

0.799

0.472

0.236

0.014

φ

0.093

φ

0.091

φ

0.062

×

0.748=0.486

+0.003

–0.002

+0.003

–0.002

+0.001

–0.001

+0.001

–0.002

+0.001

–0.002

A

B

C

D

E

F

G

H

I

J

K

L

Caution

26.3

21.6

0.65±0.02 × 29=18.85±0.05

0.65±0.02 × 19=12.35±0.05

15.6

20.3

12±0.05

6±0.05

0.35±0.02

φ

2.36±0.03

φ

2.3

φ

1.57±0.03

Dimensions of mount pad for EV-9200 and that for

0.026 × 1.142=0.742

0.026

target device (QFP) may be different in some parts.

For the recommended mount pad dimensions for

QFP, refer to "SEMICONDUCTOR DEVICE MOUNTING

TECHNOLOGY MANUAL" (C10535E).

+0.002

–0.002

+0.003

–0.002

51

APPENDIX C. RELATED DOCUMENTS

*

Document related to device

Title Document No.

Japanese English

µ

PD784915 Subseries User’s Manual – Hardware U10444J U10444E

µ

PD784915 Subseries Special Function Register Table U10976J —

78K/IV Series User’s Manual – Instructions U10905J U10905E

78K/IV Series Instruction Table U10594J —

78K/IV Series Instruction Set U10595J —

78K/IV Series Application Note – Software Basics U10095J —

Development tool documents (User’s Manual)

Title Document No.

Japanese English

RA78K Series Assembler Package Language EEU-809 EEU-1399

Operation EEU-815 EEU-1404

RA78K Series Structured Assembler Preprocessor EEU-817 EEU-1402

CC78K Series C Compiler Language EEU-656 EEU-1280

Operation EEU-655 EEU-1284

CC78K Series Library Source File EEU-777 —

PG-1500 PROM Programmer EEU-651 EEU-1335

PG-1500 Controller PC-9800 series – MS-DOS base EEU-704 EEU-1291

PG-1500 Controller IBM PC series – PC DOS base EEU-5008 U10540E

IE-784000-R EEU-5004 EEU-1534

IE-784915-R-EM1 EP-784915GF-R U10931J —

ID78K4 Integrated Debugger – Reference U10440J IEU-1412

µ

PD78P4916

Embedded-software documents (User’s Manual)

Title Document No.

Japanese English

RX78K/IV Series Real-time OS Basics U10604J —

Installation U10603J —

Debugger U10364J —

Caution The contents of the documents listed above are subject to change without prior notice to users.

Be sure to use the latest edition when starting design.

52

µ

PD78P4916

Other documents

Title Document No.

Japanese English

Semiconductor Device Package Manual IEI-635 IEI-1213

Semiconductor Device Mounting Technology Manual C10535J C10535E

Quality Grades on NEC Semiconductor Devices IEI-620 IEI-1209

NEC Semiconductor Device Reliability/Quality Control System IEM-5068 —

Electrostatic Discharge (ESD) Test MEM-539 —

Guide to Quality Assurance for Semiconductor Devices MEI-603 MEI-1202

Microcontroller-Related Product Guide - Third Party Products MEI-604 —

Caution The contents of the documents listed above are subject to change without prior notice to users.

Be sure to use the latest edition when starting design.

*

53

[MEMO]

µ

PD78P4916

54

µ

PD78P4916

NOTES FOR CMOS DEVICES

1 PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

Note: Strong electric field, when exposed to a MOS device, can cause destruction of

the gate oxide and ultimately degrade the device operation. Steps must be

taken to stop generation of static electricity as much as possible, and quickly

dissipate it once, when it has occurred. Environmental control must be

adequate. When it is dry, humidifier should be used. It is recommended to avoid

using insulators that easily build static electricity. Semiconductor devices

must be stored and transported in an anti-static container, static shielding bag

or conductive material. All test and measurement tools including work bench

and floor should be grounded. The operator should be grounded using wrist

strap. Semiconductor devices must not be touched with bare hands. Similar

precautions need to be taken for PW boards with semiconductor devices on it.

2 HANDLING OF UNUSED INPUT PINS FOR CMOS

Note: No connection for CMOS device inputs can be cause of malfunction. If no

connection is provided to the input pins, it is possible that an internal input level

may be generated due to noise, etc., hence causing malfunction. CMOS devices

behave differently than Bipolar or NMOS devices. Input levels of CMOS devices

must be fixed high or low by using a pull-up or pull-down circuitry. Each unused

pin should be connected to VDD or GND with a resistor, if it is considered to have

a possibility of being an output pin. All handling related to the unused pins must

be judged device by device and related specifications governing the devices.

3 STATUS BEFORE INITIALIZATION OF MOS DEVICES

Note: Power-on does not necessarily define initial status of MOS device. Production

process of MOS does not define the initial operation status of the device.

Immediately after the power source is turned ON, the devices with reset function

have not yet been initialized. Hence, power-on does not guarantee out-pin

levels, I/O settings or contents of registers. Device is not initialized until the

reset signal is received. Reset operation must be executed immediately after

power-on for devices having reset function.

55

µ

PD78P4916

FIP is a trademark of NEC Corporation.

MS-DOS and Windows are trademarks of Microsoft Corporation.

IBM DOS, PC/AT, and PC DOS are trademarks of International Business Machines Corporation.

HP9000 Series 700 and HP-UX are trademarks of Hewlett-Packard Company.

SPARCstation is a trademark of SPARC International, Inc.

SunOS is a trademark of Sun Microsystems, Inc.

NEWS and NEWS-OS are trademarks of Sony Corporation.

The related documents indicated in this publication may include preliminary versions. However, preliminary

versions are not marked as such.

The export of this product from Japan is regulated by the Japanese government. To export this product may be prohibited

without governmental license, the need for which must be judged by the customer. The export or re-export of this product

from a country other than Japan may also be prohibited without a license from that country. Please call an NEC sales

representative.

The application circuits and their parameters are for reference only and are not intended for use in actual design-in's.

No part of this document may be copied or reproduced in any form or by any means without the prior written

consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this

document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual

property rights of third parties by or arising from use of a device described herein or any other liability arising

from use of such device. No license, either express, implied or otherwise, is granted under any patents,

copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices,

the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or

property arising from a defect in an NEC semiconductor device, customer must incorporate sufficient safety

measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

“Standard“, “Special“, and “Specific“. The Specific quality grade applies only to devices developed based on