NEC UPD30500S2-200, UPD30500S2-180, UPD30500S2-150, UPD30500RJ-200, UPD30500RJ-180 Datasheet

...

DATA SHEET

MOS INTEGRATED CIRCUIT

µ

PD30500, 30500A, 30500B

VR5000TM, VR5000ATM, VR5000B

TM

64-BIT MICROPROCESSOR

DESCRIPTION

The µPD30500 (VR5000), µPD30500A (VR5000A), and µPD30500B

bit RISC (Reduced Instruction Set Computer) type microprocessors employing the RISC architecture developed by

TM

MIPS

VR4000TM Series and higher, and completely compatible with those of the VR10000TM. Therefore, present

applications can be used as they are.

Technologies Inc.

The instructions of the VR5000, VR5000A, and VR5000B are compatible with those of the VR3000TM Series and

Note Under development

Detailed functions are described in the following manual. Be sure to read the manual when

designing your system.

R5000, VR5000A, VR5000B User’s Manual (U11761E)

• V

FEATURES

• Employs 64-bit MIPS-based RISC architecture

• High-speed processing

• 2-way super scalar 5-stage pipeline

µ

• 5.5 SPECint95, 5.5 SPECfp95, 278 MIPS (

6.6 SPECint95, 6.6 SPECfp95, 353 MIPS (µPD30500A)

8 SPECint95, 8 SPECfp95, 423 MIPS (µPD30500B)

• High-speed translation buffer mechanism (TLB) (48 entries)

• Address space Physical: 36 bits, Virtual: 40 bits

• Floating-point unit (FPU)

• Sum-of-products operation instruction supported

• Primary cache memory (instruction/data: 32 Kbytes each)

• Secondary cache controller

• Maximum operating frequency Internal: 200 MHz (

External: 100 MHz

• Selectable external/internal multiple rate from twice to eight times

• Instruction set compatible with V

• Supply voltage: 3.3 V ±5% (µPD30500)

Core: 2.5 V ±5%, I/O: 3.3 V ±5% (µPD30500A)

Core: 1.8 V ±0.1 V, I/O: 3.3 V ±5% (

R3000 and VR4000 Series and higher (conforms to MIPS I, II, III, and IV)

PD30500)

µ

PD30500), 250 MHz (µPD30500A), 300 MHz (µPD30500B)

µ

PD30500B)

Note

(VR5000B) are a high-performance, 64-

Unless otherwise specified, the VR5000 (µPD30500) is treated as the representative model throughout this

document.

The information in this document is subject to change without notice. Before using this document, please

confirm that this is the latest version.

Not all devices/types available in every country. Please check with local NEC representative for availability

and additional information.

Document No. U12031EJ4V0DS00 (4th edition)

Date Published May 2000 N CP(K)

Printed in Japan

The mark shows major revised points.

©

MIPS Technologies Inc.

©

1997,1999

1997

µ

PD30500, 30500A, 30500B

APPLICATIONS

• High-performance embedded systems

• Multimedia systems

• Entry-class computers

• Image processing systems

ORDERING INFORMATION

Part number Package Maximum operating frequency (MHz)

µ

PD30500RJ-150 223-pin ceramic PGA (48 × 48) 150

µ

PD30500RJ-180 223-pin ceramic PGA (48 × 48) 180

µ

PD30500RJ-200 223-pin ceramic PGA (48 × 48) 200

µ

PD30500S2-150 272-pin plastic BGA (C/D advanced type) (29 × 29) 150

µ

PD30500S2-180 272-pin plastic BGA (C/D advanced type) (29 × 29) 180

µ

PD30500S2-200 272-pin plastic BGA (C/D advanced type) (29 × 29) 200

µ

PD30500AS2-250 272-pin plastic BGA (C/D advanced type) (29 × 29) 250

µ

PD30500BS2-300

Note

272-pin plastic BGA (C/D advanced type) (29 × 29) 300

Note Under development

MAIN DIFFERENCES BETWEEN VR5000, VR5000A, AND VR5000B

Parameter VR5000 VR5000A VR5000B

Maximum internal operating frequency

Internal multiplication ratio for clock 2, 3, 4, 5, 6, 7, 8 2, 2.5

interface input

Supply voltage 3.3 V ±5% Core: 2.5 V ±5% Core: 1.8 V ±0.1 V

Package • 223-pin ceramic PGA • 272-pin plastic BGA (C/D advanced type)

Notes 1. Under development

2. Selectable only when SysClock = 100 MHz

150/180/200 MHz 250 MHz 300 MHz

Note 2

, 3, 4, 5, 6, 7, 8

I/O: 3.3 V ±5% I/O: 3.3 V ±5%

• 272-pin plastic BGA

(C/D advanced type)

Note 1

2

Data Sheet U12031EJ4V0DS00

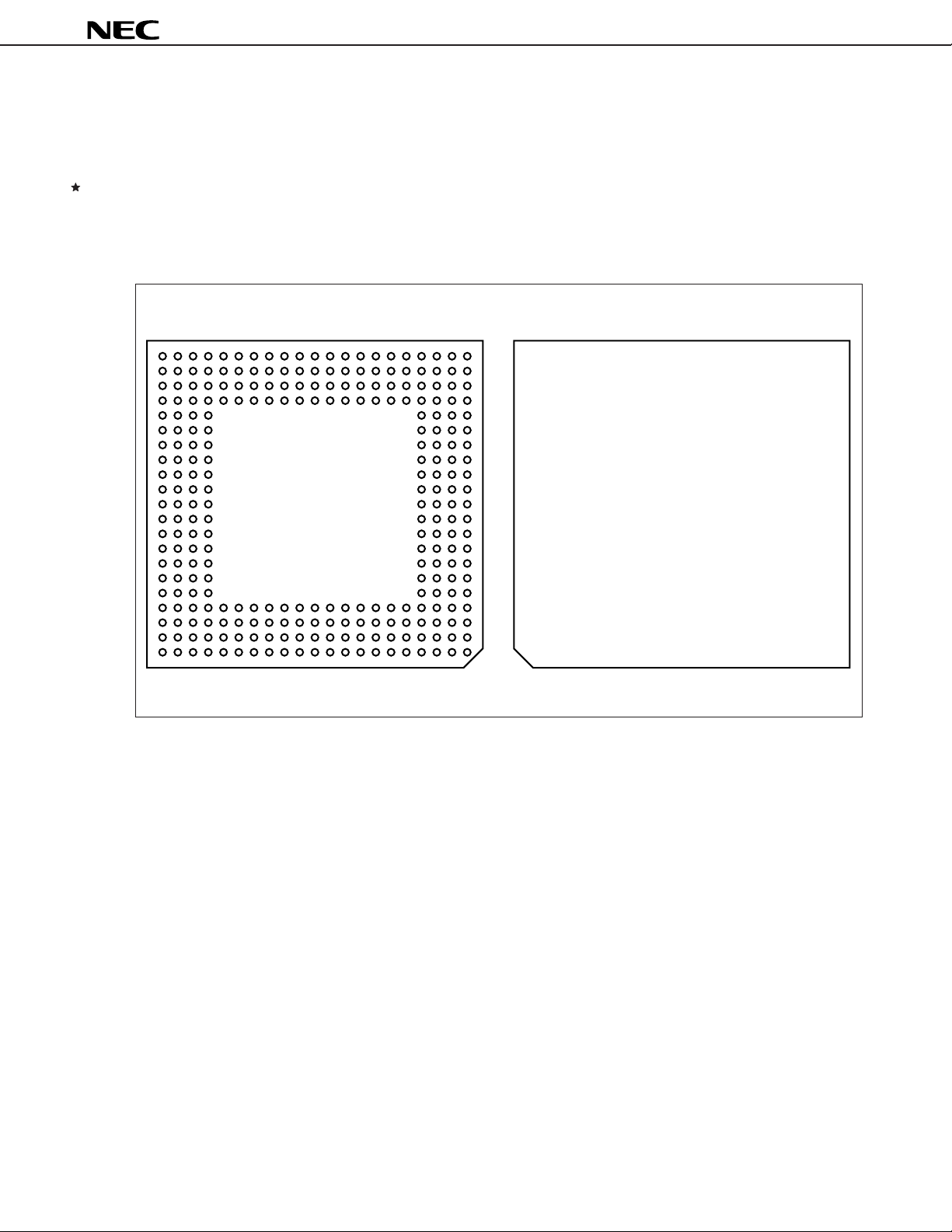

PIN CONFIGURATION

• 223-pin ceramic PGA (48 × 48)

µ

PD30500RJ-150

µ

PD30500RJ-180

µ

PD30500RJ-200

Bottom View Top View

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

µ

PD30500, 30500A, 30500B

ABCDEFGHJKLMNPRTUV

Index mark

VUTRPNMLKJHGFEDCBA

Data Sheet U12031EJ4V0DS00

3

µ

PD30500, 30500A, 30500B

No. Name No. Name No. Name No. Name No. Name No. Name

A2 VDD

A3 GND

A4 VDD

A5 GND

A6 GND

A7 VDD

A8 GND

A9 VDD

A10 GND

A11 VDD

A12 GND

A13 VDD

A14 GND

A15 GND

A16 VDD

A17 GND

A18 GND

B1 GND

B2 GND

B3 VDD

B4 SysADC4

B5 SysADC0

B6 SysAD18

B7 SysAD20

B8 SysAD54

B9 SysAD26

B10 SysAD58

B11 SysAD30

B12 SysAD46

B13 SysAD12

B14 SysAD40

B15 SysAD6

B16 GND

B17 VDD

B18 VDD

C1 VDD

C2 VDD

C3 ValidOut

C4 NMI

C5 SysADC6

C6 SysAD16

C7 SysAD50

C8 SysAD22

C9 SysAD24

C10 SysAD28

C11 SysAD62

C12 SysAD44

C13 SysAD10

C14 SysAD38

C15 SysAD4

C16 SysAD34

C17 SysAD2

C18 GND

D1 GND

D2 Int3

D3 Int5

D4 Release

D5 VDD

D6 SysADC2

D7 SysAD48

D8 SysAD52

D9 SysAD56

D10 SysAD60

D11 SysAD14

D12 SysAD42

D13 SysAD8

D14 SysAD36

D15 ColdReset

D16 SysAD0

D17 ScTOE

D18 VDD

E1 GND

E2 Int0

E3 Int2

E4 Int4

E15 SysAD32

E16 ScDCE1

E17 ScCWE1

E18 VDD

F1 VDD

F2 Reserved

F3 ScValid

F4 Int1

F15 ScDCE0

F16 ScCWE0

F17 ScTDE

F18 GND

G1 GND

G2 Reserved

G3 Reserved

G4 Reserved

G15 ScCLR

G16 ScTCE

G17 Modeln

G18 VDD

H1 VDD

H2 Reserved

H3 Reserved

H4 Reserved

H15 VDDOk

H16 ModeClock

H17 SysClock

H18 GND

J1 GND

J2 WrRdy

J3 Validln

J4 ExtRqst

J15 Reserved

J16 Reserved

J17 Reserved

J18 VDD

K1 VDD

K2 ScMatch

K3 RdRdy

K4 ScDOE

K15 Reserved

K16 VDDP

K17 GNDP

K18 GND

L1 GND

L2 SysCmd8

L3 SysCmd7

L4 SysCmd5

L15 ScLine12

L16 ScLine14

L17 ScLine15

L18 VDD

M1 VDD

M2 SysCmd6

M3 SysCmd4

M4 SysCmd1

M15 ScLine8

M16 ScLine10

M17 ScLine13

M18 GND

N1 GND

N2 SysCmd3

N3 SysCmd2

N4 SysADC7

N15 ScLine5

N16 ScLine7

N17 ScLine11

N18 VDD

P1 VDD

P2 SysCmd0

P3 SysCmdP

P4 SysADC1

P15 ScLine2

P16 ScLine4

P17 ScLine9

P18 GND

R1 VDD

R2 SysADC5

R3 SysADC3

R4 BigEndian

R5 SysAD49

R6 SysAD51

R7 SysAD55

R8 SysAD27

R9 SysAD31

R10 SysAD43

R11 SysAD39

R12 SysAD35

R13 SysAD1

R14 ScWord1

R15 ScLine0

R16 ScLine3

R17 ScLine6

R18 GND

T1 GND

T2 SysAD15

T3 SysAD47

T4 SysAD17

T5 SysAD19

T6 SysAD23

T7 SysAD57

T8 SysAD29

T9 VDD

T10 SysAD45

T11 SysAD41

T12 SysAD7

T13 SysAD5

T14 SysAD33

T15 Reset

T16 ScLine1

T17 VDD

T18 VDD

U1 VDD

U2 VDD

U3 GND

U4 SysAD21

U5 SysAD53

U6 SysAD25

U7 SysAD59

U8 SysAD61

U9 SysAD63

U10 SysAD13

U11 SysAD11

U12 SysAD9

U13 SysAD37

U14 SysAD3

U15 ScWord0

U16 VDD

U17 GND

U18 GND

V1 GND

V2 GND

V3 VDD

V4 GND

V5 GND

V6 VDD

V7 GND

V8 VDD

V9 GND

V10 VDD

V11 GND

V12 VDD

V13 GND

V14 VDD

V15 GND

V16 GND

V17 VDD

V18 GND

4

Data Sheet U12031EJ4V0DS00

• 272-pin plastic BGA (C/D advanced type) (29 × 29)

µ

PD30500S2-150

µ

PD30500S2-180

µ

PD30500S2-200

µ

PD30500AS2-250

µ

PD30500BS2-300

Note

Bottom View Top View

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

µ

PD30500, 30500A, 30500B

AAYWVUTRPNMLKJHGFEDCBA ABCDEFGHJKLMNPRTUVWYAA

Note Under development

Data Sheet U12031EJ4V0DS00

5

µ

PD30500, 30500A, 30500B

(1)µPD30500

No. Name No. Name No. Name No. Name No. Name No. Name

A1 GND

A2 VDD

A3 GND

A4 SysAD32

A5 GND

A6 ScCWE1

A7 GND

A8 VDDOk

A9 GND

A10 SysClock

A11 GND

A12 ScLine15

A13 GND

A14 ScLine12

A15 GND

A16 ScLine7

A17 GND

A18 ScLine2

A19 GND

A20 VDD

A21 GND

B1 VDD

B2 VDD

B3 VDD

B4 SysAD2

B5 SysAD0

B6 ScTOE

B7 ScCLR

B8 ScTDE

B9 ModeClock

B10 Reserved

B11 Reserved

B12 NC

B13 ScLine14

B14 ScLine10

B15 ScLine9

B16 ScLine6

B17 ScLine3

B18 ScLine1

B19 VDD

B20 VDD

B21 VDD

C1 GND

C2 VDD

C3 ColdReset

C4 SysAD34

C5 ScDCE1

C6 ScDCE0

C7 ScCWE0

C8 ScTCE

C9 Modeln

C10 Reserved

C11 GNDP

C12 Reserved

C13 ScLine13

C14 ScLine11

C15 ScLine8

C16 ScLine5

C17 ScLine4

C18 ScLine0

C19 Reset

C20 VDD

C21 GND

D1 VDD

D2 VDD

D3 VDD

D4 GND

D5 VDD

D6 GND

D7 VDD

D8 VDD

D9 GND

D10 VDD

D11 VDDP

D12 VDD

D13 GND

D14 VDD

D15 VDD

D16 GND

D17 VDD

D18 GND

D19 VDD

D20 VDD

D21 VDD

E1 GND

E2 SysAD36

E3 SysAD4

E4 VDD

E18 VDD

E19 ScWord1

E20 ScWord0

E21 GND

F1 SysAD8

F2 SysAD38

F3 SysAD6

F4 GND

F18 GND

F19 SysAD1

F20 SysAD33

F21 SysAD3

G1 GND

G2 SysAD10

G3 SysAD40

G4 VDD

G18 VDD

G19 SysAD35

G20 SysAD5

G21 GND

H1 SysAD42

H2 SysAD44

H3 SysAD12

H4 VDD

H18 VDD

H19 SysAD7

H20 SysAD39

H21 SysAD37

J1 GND

J2 SysAD46

J3 SysAD14

J4 GND

J18 GND

J19 SysAD9

J20 SysAD41

J21 GND

K1 SysAD60

K2 SysAD30

K3 SysAD62

K4 VDD

K18 VDD

K19 SysAD11

K20 SysAD43

K21 SysAD13

L1 GND

L2 SysAD58

L3 SysAD28

L4 VDD

L18 VDD

L19 SysAD45

L20 SysAD63

L21 GND

M1 SysAD26

M2 SysAD56

M3 SysAD24

M4 VDD

M18 VDD

M19 SysAD29

M20 SysAD61

M21 SysAD31

N1 GND

N2 SysAD54

N3 SysAD22

N4 GND

N18 GND

N19 SysAD27

N20 SysAD59

N21 GND

P1 SysAD50

P2 SysAD52

P3 SysAD20

P4 VDD

P18 VDD

P19 SysAD25

P20 SysAD57

P21 SysAD55

R1 GND

R2 SysAD18

R3 SysAD48

R4 VDD

R18 VDD

R19 SysAD53

R20 SysAD23

R21 GND

T1 SysAD16

T2 SysADC0

T3 SysADC2

T4 GND

T18 GND

T19 SysAD19

T20 SysAD51

T21 SysAD21

U1 GND

U2 SysADC4

U3 SysADC6

U4 VDD

U18 VDD

U19 SysAD17

U20 SysAD49

U21 GND

V1 VDD

V2 VDD

V3 VDD

V4 GND

V5 NMI

V6 GND

V7 VDD

V8 VDD

V9 GND

V10 VDD

V11 VDD

V12 VDD

V13 GND

V14 VDD

V15 VDD

V16 GND

V17 VDD

V18 GND

V19 VDD

V20 VDD

V21 VDD

W1 GND

W2 VDD

W3 VDD

W4 VDD

W5 Int5

W6 Int4

W7 Int1

W8 Reserved

W9 Reserved

W10 Reserved

W11 Validln

W12 ScDOE

W13 SysCmd7

W14 SysCmd4

W15 SysCmd1

W16 SysADC7

W17 SysADC5

W18 SysAD47

W19 BigEndian

W20 VDD

W21 GND

Y1 VDD

Y2 VDD

Y3 VDD

Y4 Release

Y5 Int3

Y6 Int2

Y7 ScValid

Y8 Reserved

Y9 Reserved

Y10 Reserved

Y11 ExtRqst

Y12 RdRdy

Y13 SysCmd8

Y14 SysCmd5

Y15 SysCmd3

Y16 SysCmd0

Y17 SysCmdP

Y18 SysADC1

Y19 SysAD15

Y20 VDD

Y21 VDD

AA1 GND

AA2 VDD

AA3 GND

AA4 ValidOut

AA5 GND

AA6 Int0

AA7 GND

AA8 Reserved

AA9 GND

AA10 WrRdy

AA11 GND

AA12 ScMatch

AA13 GND

AA14 SysCmd6

AA15 GND

AA16 SysCmd2

AA17 GND

AA18 SysADC3

AA19 GND

AA20 VDD

AA21 GND

6

Data Sheet U12031EJ4V0DS00

µ

PD30500, 30500A, 30500B

(2)µPD30500A, 30500B

No. Name No. Name No. Name No. Name No. Name No. Name

A1 GND

A2 VDDIO

A3 GND

A4 SysAD32

A5 GND

A6 ScCWE1

A7 GND

A8 VDDOk

A9 GND

A10 SysClock

A11 GND

A12 ScLine15

A13 GND

A14 ScLine12

A15 GND

A16 ScLine7

A17 GND

A18 ScLine2

A19 GND

A20 VDDIO

A21 GND

B1 VDDIO

B2 VDDIO

B3 VDDIO

B4 SysAD2

B5 SysAD0

B6 ScTOE

B7 ScCLR

B8 ScTDE

B9 ModeClock

B10 GND

B11 GND

B12 GND

B13 ScLine14

B14 ScLine10

B15 ScLine9

B16 ScLine6

B17 ScLine3

B18 ScLine1

B19 VDDIO

B20 VDDIO

B21 VDDIO

C1 GND

C2 VDDIO

C3 ColdReset

C4 SysAD34

C5 ScDCE1

C6 ScDCE0

C7 ScCWE0

C8 ScTCE

C9 Modeln

C10 NC

C11 GNDP

C12 GND

C13 ScLine13

C14 ScLine11

C15 ScLine8

C16 ScLine5

C17 ScLine4

C18 ScLine0

C19 Reset

C20 VDDIO

C21 GND

D1 VDD

D2 VDD

D3 VDD

D4 GND

D5 VDD

D6 GND

D7 VDDIO

D8 VDD

D9 GND

D10 VDDIO

D11 VDDP

D12 VDD

D13 GND

D14 VDDIO

D15 VDD

D16 GND

D17 VDDIO

D18 GND

D19 VDD

D20 VDD

D21 VDD

E1 GND

E2 SysAD36

E3 SysAD4

E4 VDD

E18 VDD

E19 ScWord1

E20 ScWord0

E21 GND

F1 SysAD8

F2 SysAD38

F3 SysAD6

F4 GND

F18 GND

F19 SysAD1

F20 SysAD33

F21 SysAD3

G1 GND

G2 SysAD10

G3 SysAD40

G4 VDDIO

G18 VDDIO

G19 SysAD35

G20 SysAD5

G21 GND

H1 SysAD42

H2 SysAD44

H3 SysAD12

H4 VDD

H18 VDD

H19 SysAD7

H20 SysAD39

H21 SysAD37

J1 GND

J2 SysAD46

J3 SysAD14

J4 GND

J18 GND

J19 SysAD9

J20 SysAD41

J21 GND

K1 SysAD60

K2 SysAD30

K3 SysAD62

K4 VDDIO

K18 VDDIO

K19 SysAD11

K20 SysAD43

K21 SysAD13

L1 GND

L2 SysAD58

L3 SysAD28

L4 VDD

L18 VDD

L19 SysAD45

L20 SysAD63

L21 GND

M1 SysAD26

M2 SysAD56

M3 SysAD24

M4 VDDIO

M18 VDDIO

M19 SysAD29

M20 SysAD61

M21 SysAD31

N1 GND

N2 SysAD54

N3 SysAD22

N4 GND

N18 GND

N19 SysAD27

N20 SysAD59

N21 GND

P1 SysAD50

P2 SysAD52

P3 SysAD20

P4 VDD

P18 VDD

P19 SysAD25

P20 SysAD57

P21 SysAD55

R1 GND

R2 SysAD18

R3 SysAD48

R4 VDDIO

R18 VDDIO

R19 SysAD53

R20 SysAD23

R21 GND

T1 SysAD16

T2 SysADC0

T3 SysADC2

T4 GND

T18 GND

T19 SysAD19

T20 SysAD51

T21 SysAD21

U1 GND

U2 SysADC4

U3 SysADC6

U4 VDD

U18 VDD

U19 SysAD17

U20 SysAD49

U21 GND

V1 VDD

V2 VDD

V3 VDD

V4 GND

V5 NMI

V6 GND

V7 VDD

V8 VDDIO

V9 GND

V10 VDD

V11 VDDIO

V12 VDD

V13 GND

V14 VDDIO

V15 VDD

V16 GND

V17 VDDIO

V18 GND

V19 VDD

V20 VDD

V21 VDD

W1 GND

W2 VDDIO

W3 VDDIO

W4 VDDIO

W5 Int5

W6 Int4

W7 Int1

W8 GND

W9 GND

W10 VDD

W11 Validln

W12 ScDOE

W13 SysCmd7

W14 SysCmd4

W15 SysCmd1

W16 SysADC7

W17 SysADC5

W18 SysAD47

W19 BigEndian

W20 VDDIO

W21 GND

Y1 VDDIO

Y2 VDDIO

Y3 VDDIO

Y4 Release

Y5 Int3

Y6 Int2

Y7 ScValid

Y8 GND

Y9 GND

Y10 GND

Y11 ExtRqst

Y12 RdRdy

Y13 SysCmd8

Y14 SysCmd5

Y15 SysCmd3

Y16 SysCmd0

Y17 SysCmdP

Y18 SysADC1

Y19 SysAD15

Y20 VDDIO

Y21 VDDIO

AA1 GND

AA2 VDDIO

AA3 GND

AA4 ValidOut

AA5 GND

AA6 Int0

AA7 GND

AA8 GND

AA9 GND

AA10 WrRdy

AA11 GND

AA12 ScMatch

AA13 GND

AA14 SysCmd6

AA15 GND

AA16 SysCmd2

AA17 GND

AA18 SysADC3

AA19 GND

AA20 VDDIO

AA21 GND

Data Sheet U12031EJ4V0DS00

7

PIN NAMES

BigEndian: Endian Mode Select

ColdReset: Cold Reset

ExtRqst: External Request

GND: Ground

GNDP: Quiet GND for PLL

Int (0:5): Interrupt Request

ModeClock: Boot Mode Clock

Modeln: Boot Mode Data In

NC: No Connection

NMI: Non-maskable Interrupt Request

RdRdy: Read Ready

Release: Release Interface

Reset: Reset

ScCLR: Secondary Cache Block Clear

ScCWE (0:1): Secondary Cache Write Enable

ScDCE (0:1): Data RAM Chip Enable

ScDOE: Data RAM Output Enable

ScLine (0:15): Secondary Cache Line Index

ScMatch: Secondary Cache Tag Match

ScTCE: Secondary Cache Tag RAM Chip Enable

ScTDE: Secondary Cache Tag RAM Data Enable

ScTOE: Secondary Cache Tag RAM Output Enable

ScValid: Secondary Cache Valid

ScWord (0:1): Secondary Cache Word Index

SysAD (0:63): System Address/Data Bus

SysADC (0:7): System Address/Data Check Bus

SysClock: System Clock

SysCmd (0:8): System Command/Data Identifier

SysCmdP: System Command/Data Identifier Bus Parity

Validln: Valid Input

ValidOut: Valid Output

DD: Power Supply (

V

VDD: Power Supply for Processor Core (µPD30500A, 30500B)

DDIO: Power Supply for Processor I/O (

V

VDDOk: VDD is OK

VDDP: Quiet VDD for PLL

WrRdy: Write Ready

µ

PD30500)

µ

PD30500A, 30500B only)

µ

PD30500, 30500A, 30500B

8

Data Sheet U12031EJ4V0DS00

INTERNAL BLOCK DIAGRAM

µ

PD30500, 30500A, 30500B

Data, address

System interface

Instruction cache Data cache

Instruction address

Control

SysClock

Clock

generator

CP0

TLB

Execution unit

Floating-point unit

Pipeline control

Data Sheet U12031EJ4V0DS00

9

µ

PD30500, 30500A, 30500B

CONTENTS

1. PIN FUNCTIONS ................................................................................................................................ 11

2. ELECTRICAL SPECIFICATIONS ......................................................................................................13

2.1µPD30500 ....................................................................................................................................................13

2.2µPD30500A..................................................................................................................................................16

2.3µPD30500B (Preliminary) ..........................................................................................................................19

2.4 Test Condition ............................................................................................................................................ 22

2.5 Timing Chart ............................................................................................................................................... 22

3. PACKAGE DRAWING........................................................................................................................27

4. RECOMMENDED SOLDERING CONDITIONS ................................................................................. 29

APPENDIX DIFFERENCES BETWEEN THE VR5000 AND VR4310TM.................................................... 30

10

Data Sheet U12031EJ4V0DS00

1. PIN FUNCTIONS

Pin Name I/O Function

SysAD (0:63) I/O System address/data bus.

64-bit bus for communication between processor, secondary cache and external agent.

SysADC (0:7) I/O System address/data check bus.

8-bit bus including check bits for the SysAD bus.

SysCmd (0:8) I/O System command/data ID bus.

9-bit bus for communication of commands and data identifiers between processor

and external agent.

SysCmdP I/O System command/data ID bus parity.

1-bit even number parity bit for the SysCmd bus.

ValidIn Input Valid in.

Signal indicating that external agent has transmitted valid address or data onto

SysAD bus and valid command or data identifier onto SysCmd bus.

ValidOut Output Valid out.

Signal indicating that processor has transmitted valid address or data onto SysAD

bus and valid command or data identifier onto SysCmd bus.

ExtRqst Input External request.

Signal used by external agent to request for its use by system interface.

Release Output Interface release.

Signal indicating that the processor has released the system interface to the slave state.

WrRdy Output Write ready.

Signal indicating that the external agent can accept a processor write request.

RdRdy Input Read ready.

Signal indicating that external agent can accept a processor read request.

ScCLR Output Secondary cache block clear.

Clears all the valid bits of the tag RAM.

ScCWE (0:1) Output Secondary cache write enable.

Write enable signal for the secondary cache RAM.

ScDCE (0:1) Output Data RAM chip select.

Chip select signal for secondary cache RAM.

ScDOE Input Data RAM output enable.

Data output enable signal from the external agent.

ScLine (0:15) Output Secondary cache line index.

Cache line index output of the secondary cache.

ScMatch Input Secondary cache tag match.

Tag match signal from secondary cache tag RAM.

ScTCE Output Secondary cache tag RAM chip select.

Chip select signal of the secondary cache tag RAM.

ScTDE Output Secondary cache tag RAM data enable.

Data enable signal from the secondary cache tag RAM.

ScTOE Output Secondary cache tag RAM output enable.

Output enable signal from the secondary cache tag RAM.

ScWord (0:1) I/O Secondary cache word index.

Signal indicating that the double word of the secondary cache index is correct.

ScValid I/O Secondary cache valid.

Signal indicating that the data of the secondary cache is valid.

µ

PD30500, 30500A, 30500B

Data Sheet U12031EJ4V0DS00

11

Loading...

Loading...