NEC UPD2845GR, UPD2845GR-E2, UPD2845GR-E1 Datasheet

DATA SHEET

DATA SHEET

CMOS DIGITAL INTEGRATED CIRCUITS

PPPP

PD2845GR

1 V, 1.3 mA, 94MHz PLL SYNTHESIZER LSI

FOR PAGER SYSTEM

DESCRIPTION

PD2845GR is a PLL synthesizer LSI for pager system. This LSI is manufactured using low voltage CMOS

P

process and therefore realized the low power consumption PLL operated on 1 V, 1.3 mA. This LSI is packaged in 16

pin plastic SSOP suitable for high-density surface mounting. So, this product contributes to produce a long-lifebattery and physically-small pager system.

FEATURES

• Operating frequency : · Input frequency : fin = 10 MHz to 94 MHz

· Reference oscillating frequency : f

• Low Supply voltage : · PLL block : V

· Charge pump block: V

• Low power consumption • I

• Equipped with power-save function • Serial data can be received in power-save mode.

• Packaged in 16 pin plastic SSOP suitable for high-density surface mounting.

DD

= 1.3 mA TYP. @ fin = 70 MHz, f

DD1

= 1.00 V to 1.15 V @ fin = 10 MHz to 70 MHz

DD1

V

= 1.05 V to 1.15 V @ fin = 10 MHz to 94 MHz

DD2

= 3.0 V ± 300 mV

x’tal

= 12.8 MHz

x’tal

= 12.8 MHz

ORDERING INFORMATION

PART NUMBER PACKAGE SUPPLYING FORM

P

PD2845GR-E1 16 pin plastic SSOP

(225 mil)

P

PD2845GR-E2 16 pin plastic SSOP

(225 mil)

* To order evaluation samples, please contact your local NEC sales office (Order number : PPD2845GR).

Embossed tape 12 mm wide. QTY 2.5 k/reel

Pin 1 is in tape pull-out direction.

Embossed tape 12 mm wide. QTY 2.5 k/reel

Pin 1 is in tape roll-in direction.

PIN ASSIGNMENT

(Top View)

V

DD1

F

GND

FR

RESET

EO

IN

XI

XO

LE

CLK

DATA

PS

EOP

EON

Document No. P12150EJ2V0DS00 (2nd edition)

(Previous No. IC-3291)

Date Published February 1997 N

NC

V

DD2

Caution Electro-static sensitive devices

1994©

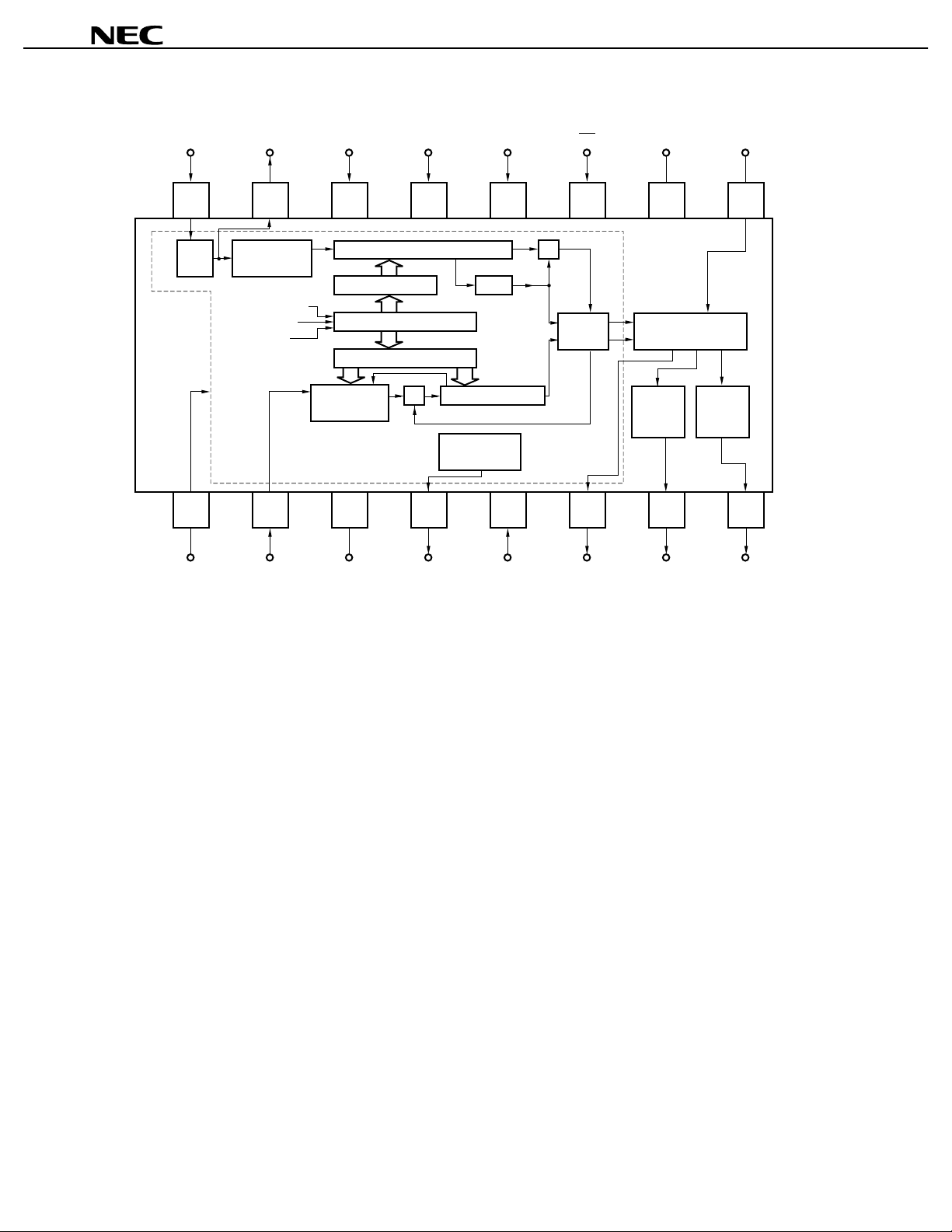

INTERNAL BLOCK DIAGRAM

PPPP

PD2845GR

XI XO LE

16 15 14 13 12 11 10 9

IN

AMP

1 2 3 4 5 6 7 8

V

DD1

1/2

PRESCALER

DATA

CLK

LE

F

IN

5 BIT

reference divider 13 BIT

latch 13 BIT

Shift register 23 BIT

32/33

PRESCALER

GND FR RESET EO EOP EON

CLK

latch 18 BIT

gate

DATA

gate

timer

divider 13 BIT

TEST CIRCUIT

FV

PS NC V

FR

Phase

comparator

Phase detector

error out

Pch

open

drain

Nch

open

drain

DD2

2

PPPP

PD2845GR

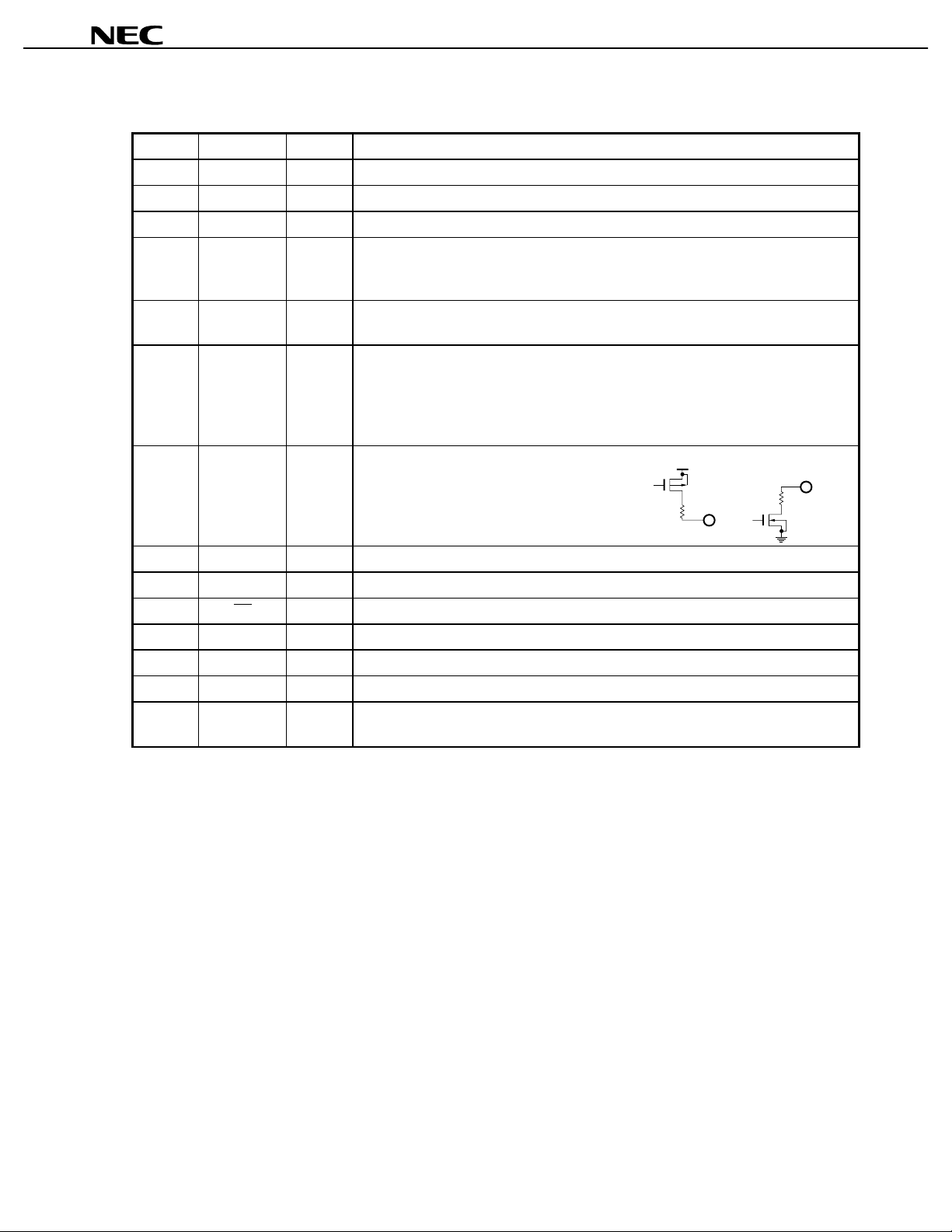

PIN EXPLANATION

PIN No. PIN NAME I/O EXPLANATION FOR FUNCTION

1V

2FINI Frequency Input

3 GND

4 FR O Test pin for monitor.

5 RESET I Test pin for monitor reset. (Refer to RESET on 12 page)

6 EO O Internal charge pump output. In the case of passive filter, this output should be used.

7

8

DD1

EOP

EON

•

•

O

O

Supply voltage to PLL block

Ground

Normally used as PLL, output L should be selected by test bit and this pin should be

opened. (Refer to setting for reference counter on 11 page)

Normally used as PLL, this pin should be grounded.

p

Input signal phase f

fp > fr : Low output

p

< fr : High output

f

p

= fr : High-impedance

f

Outputs for external charge pump. In the case of active filter, this outputs should be used.

EOP : PCH open drain

EON : NCH open drain

vs. reference signal f

r

EON

EOP

9V

10 NC

11 PS I Control bias input for power-save (Refer to Power-save on 12 page).

12 DATA I Data input for divided ratio.

13 CLK I Clock input for shift register.

14 LE I Latch enable input.

15

16

DD2

XO

XI

•

•

O

Supply voltage to charge pump.

Non Connection.

X’tal oscillator connection pin.

I

3

PPPP

PD2845GR

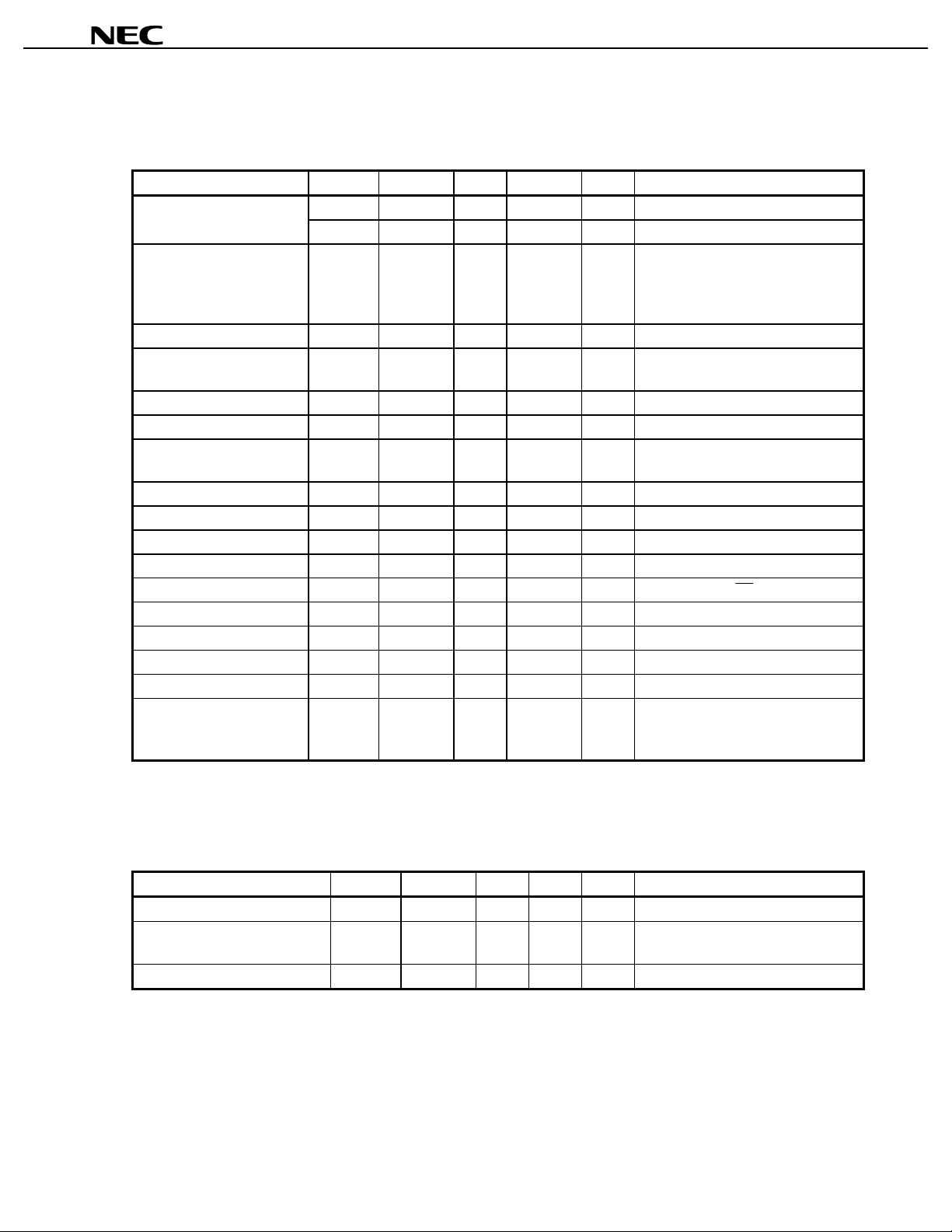

ABSOLUTE MAXIMUM RATINGS (UNLESS OTHERWISE SPECIFIED, TA = +25 °C

Supply Voltage V

Input Voltage V

Output Voltage V

Output Current I

Operating Ambient Temperature T

Storage Temperature T

DD1

DD2

V

I1

I2

V

O1

O2

V

O

A

stg

0.3 to 2.0 V

ð

0.3 to 6.0 V

ð

0.3 to V

ð

0.3 to 6.0 (DATA, CLK, LE, PS) V

ð

0.3 to V

ð

0.3 to V

ð

DD1

+0.3 (Except for DATA, CLK, LE, PS pin) V

DD1

+0.3 (XO, FR) V

DD2

+0.3 (EO, EOP, EON) V

10 mA

10 to +50 °C

ð

55 to +125 °C

ð

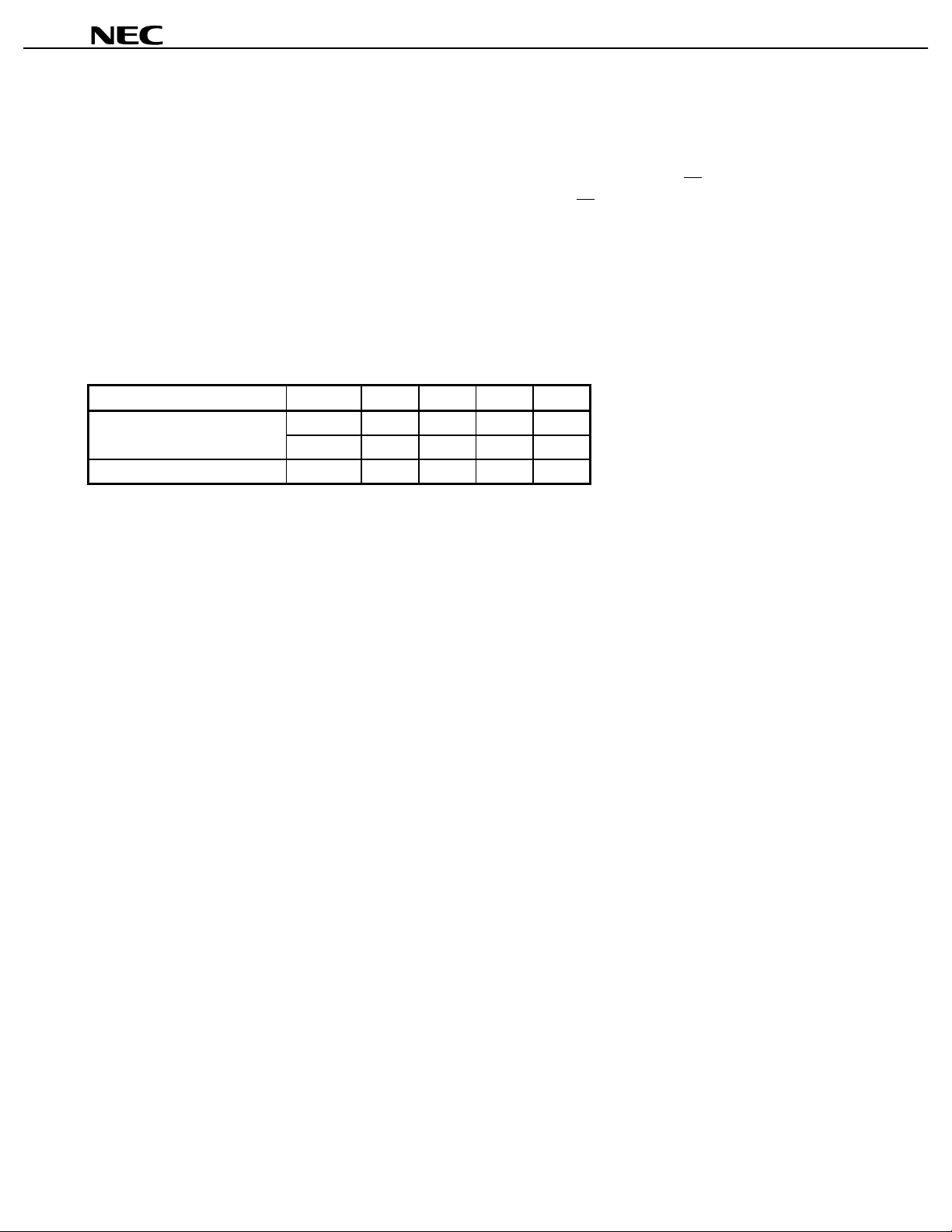

RECOMMENDED OPERATING RANGE

PARAMETER SYMBOL MIN. TYP. MAX. UNIT

DD1

Supply Voltage

Operating Ambient Temperature T

V

V

DD2

A

1.0 1.05 1.1 V

2.85 3.0 3.15 V

10 +25 +50 °C

ð

)

4

ELECTRICAL CHARACTERISTICS

PPPP

PD2845GR

DC PERFORMANCE (Unless otherwise specified, V

PARAMETER SYMBOL MIN. TYP. MAX. UNIT CONDITIONS

Supply Voltage V

Circuit Current I

Data Retain Current I

High Level Output Current1

High Level Output Current2

High Level Output Current3

Low Level Output Current1

Low Level Output Current2

Low Level Output Current3

High Level Input Current1

Low Level Input Current1

High Level Input Current2

*1

*1

*1

*2

*2

*2

*2

*1

*2

High Level Input Voltage1 V

Low Level Input Voltage1 V

High Level Input Voltage2 V

Low Level Input Voltage2 V

Output Leak Current I

DD1

DD2

V

DD1

DR

OH1

I

OH2

I

OH3

I

OL1

I

OL2

I

OL3

I

IH1

I

IL1

I

IH2

I

IH1

IL1

IH2

IL2

L

1.00 1.05 1.15 V PLL Operation

2.70 3.0 3.30 V P/D Charge pump block

1.0 mA EO, EOP pin. V

ð

0.5 mA XO pin. V

ð

0.1 mA FR pin. V

ð

1.0 mA EO, EON pin. V

0.4 mA XO pin. VOL = 0.5 V

0.4 mA FR pin. VOL = 0.5 V

0.4

0.4

ð

DD1

0.8 u V

0 0.2 u V

DD1

0.8 u V

0 0.2 u V

DD1

= 1.00 V to 1.15 V, V

DD2

= 2.70 to 3.30 V, TA =

1.3 2.2 mA fin = 70 MHz, 0.2 V

fx’tal = 12.8 MHz X’tal OSC IN.

DD1

= 1.0 V to 1.1 V

V

DD2

= 2.85 V to 3.15 V

V

1.0 10

1.0

A No Input Signal, V

P

OH

DD2

= V

= 0.5 V

ð0.5 V

OH

= V

OH

= V

V

OL

V

AFIN, XI pin. VIH = V

P

AFIN, XI pin. VIL = 0 V, V

P

A DATA, CLK, LE, PS pin. V

P

4.0 V DATA, CLK, LE, PS pin.

10

DD1

DD1

V

DD1

4

ð

1.0

r

V DATA, CLK, LE, PS pin.

V RESET pin.

V RESET pin.

A EO, EOP, EON pin.

P

DD1

= 1.0 V to 1.1 V

V

DD2

= 2.85 V to 3.15 V

V

DD2

DD1

DD1

DD2

P-P

DD1

ð0.5 V

ð0.5 V

DD1

10 to +50 °C)

ðððð

.

= 1.1 V

= 2.85 V

= 2.85 V

1.0 V

DD1

1.0 V

IH1

= 3.85 V

Current from IC

*1

Current into IC

*2

AC PERFORMANCE (Unless otherwise specified, V

PARAMETER SYMBOL MIN. TYP. MAX. UNIT CONDITIONS

Input frequency 1 f

Input frequency 2 f

Reference Oscillating Frequency f

in1

in2

x’tal

10 70 MHz FIN pin, Vin = 0.2 V

10 94 MHz FIN pin, Vin = 0.2 V

DD1

= 1.00 V to 1.15 V, V

DD2

= 2.70 to 3.30 V, TA =

12.8 MHz XI, XO pin

DD1

= 1.05 V to 1.15 V

V

P-P

P-P

,

10 to +50

ðððð

C)

qqqq

5

Loading...

Loading...