Page 1

DATA SHEET

MOS INTEGRATED CIRCUIT

µ

PD7564A, 7564A(A)

4-BIT SINGLE-CHIP MICROCOMPUTER

DESCRIPTION

The µPD7564A is a 4-bit single-chip microcomputer with a small number of ports in a small package, which is

of low-order models,

forms efficient dispersion processing of a system as a sub-CPU for the 75X series or 78k series.

The µPD7564A has outputs to directly drive a triac and LEDs and allows selection among many types of input/

output circuits using their respective mask options, sharply reducing the number of external circuits required.

Details of functions are described in the User’s Manual shown below. Be sure to read in design.

µ

PD7554 and 7564 sub-series in the µPD7500 series. With an on-chip serial interface, it per-

µ

PD7554, 7564 User’s Manual: IEM-1111D

FEATURES

• 47 types of instructions

µ

(Subset of

• Instruction cycle

Ceramic oscillation : 2.86 µs

• Program memory (ROM) capacity: 1024 × 8 bits

• Data memory (RAM) capacity: 64 × 4 bits

• Test source: One external source and two internal

sources

• 8-bit timer/event counter

• 15 I/O lines (Total output current of all pins: 100 mA)

• Can directly drive a triac and a LED: P80 to P82

• Can directly drive LEDs: P100 to P103 and P110 to

P113

• Mask option function provided for every port

PD7500H SET B)

(in operation at 700 kHz, 5 V)

APPLICATIONS

µ

PD7564A : PPCs, printers, VCRs, audio equipments,

etc.

µ

PD7564A(A) : Automotive and transportation equip-

ments, etc.

• 8-bit serial interface

• Standby (STOP/HALT) function

• Low supply voltage data retaining function for data

memory

• Built-in ceramic oscillator for system clock

• Low power dissipation

• Single power supply (2.7 to 6.0 V)

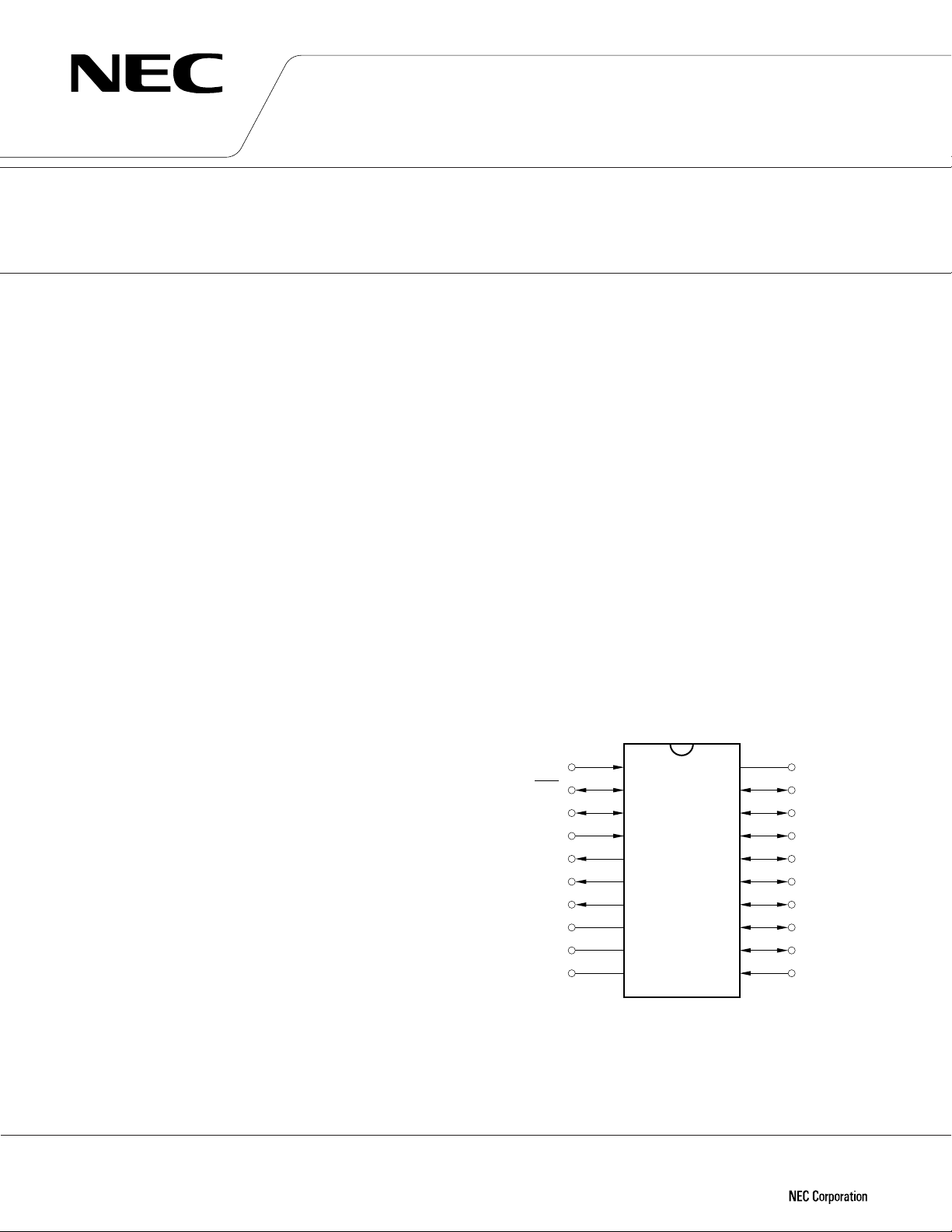

PIN CONFIGURATION (TOP VIEW)

P00/INT0

P01/SCK

P02/SO

P03/SI

P80

P81

P82

CL2

CL1

V

µ

PD7564A

20

19

18

17

16

15

14

13

12

11

1

2

3

4

5

6

7

8

9

DD

10

V

SS

P113

P112

P111

P110

P103

P102

P101

P100

RESET

★

The quality grade and absolute maximum ratings of the

Except where specifically noted, explanations here concern the

If you are using the

tional differences.

Document No. IC-2401C

(O. D. No. IC-7834C)

Date Published December 1994 P

Printed in Japan

µ

PD7564A and the µPD7564A(A) differ.

µ

PD7564A as a representative product.

µ

PD7564A(A), use the information presented here after the checking the func-

The information in this document is subject to change without notice.

The mark ★ shows major revised points.

©

1994

Page 2

µ

PD7564A, 7564A(A)

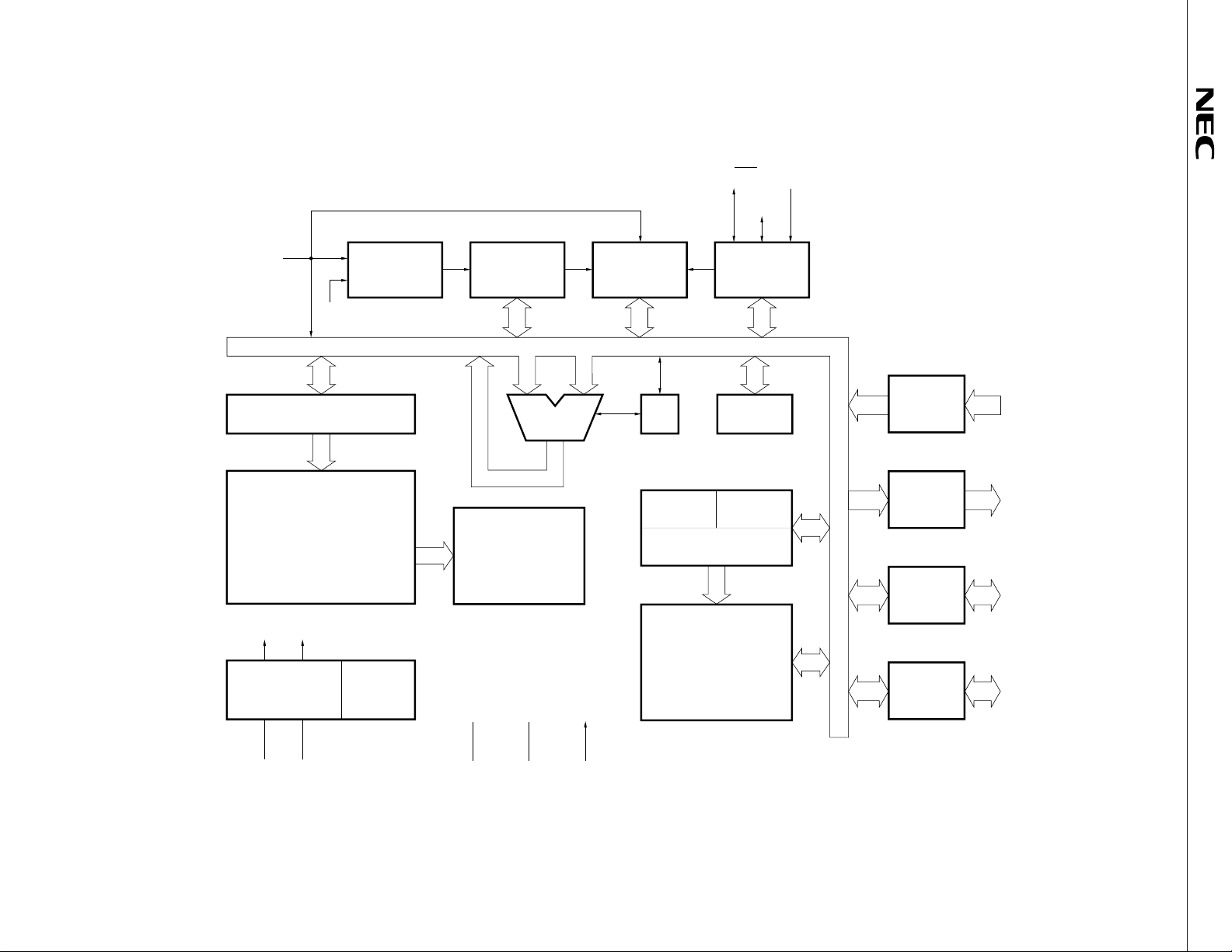

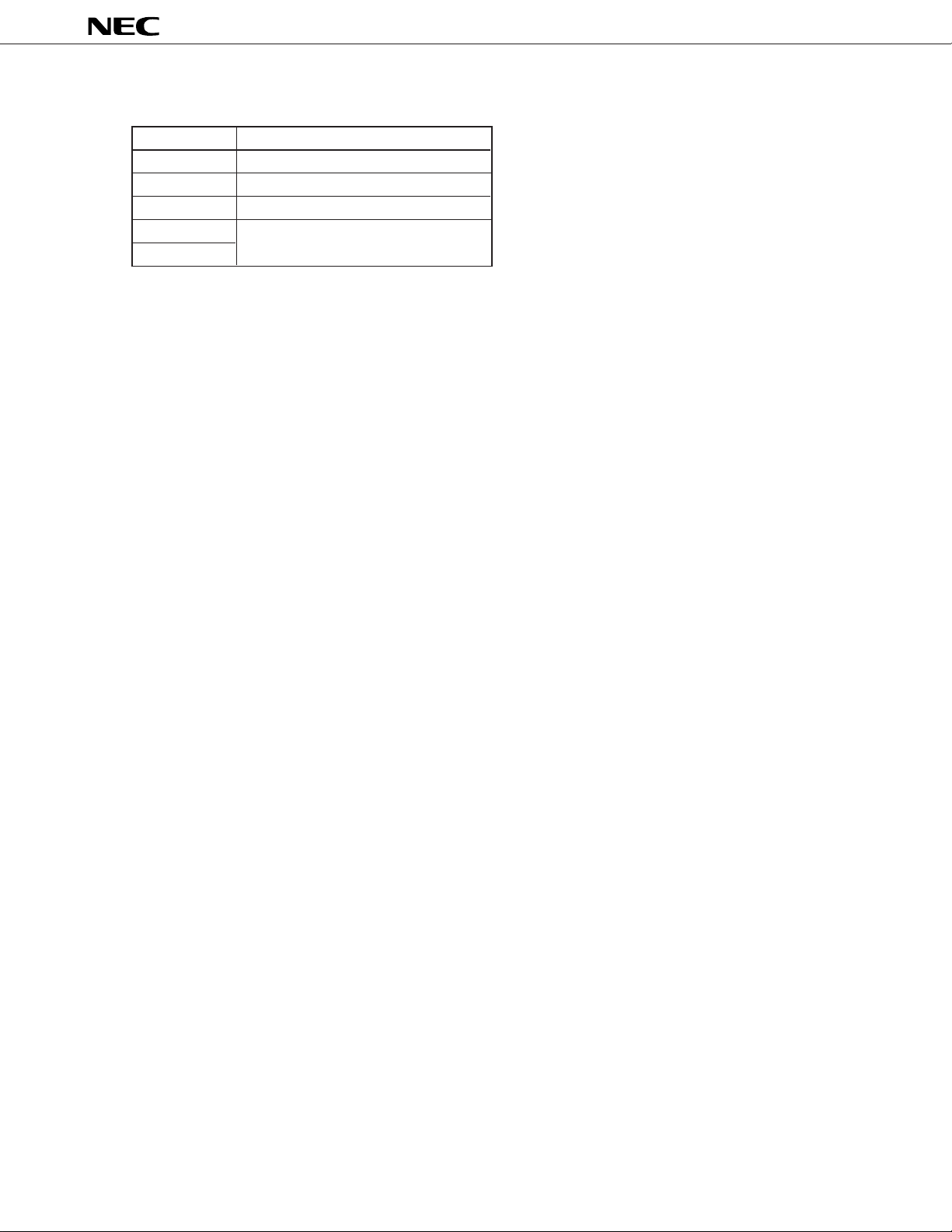

ORDERING INFORMATION

Ordering Code Package Quality Grade

µ

PD7564ACS-××× 20-pin plastic shrink DIP (300 mil) Standard

µ

PD7564AG-××× 20-pin plastic SOP (300 mil) Standard

µ

★

★

PD7564ACS(A)-××× 20-pin plastic shrink DIP (300 mil) Special

µ

PD7564AG(A)-××× 20-pin plastic SOP (300 mil) Special

Caution Be sure to specify a mask option when ordering this device.

Remarks "×××" is a ROM code number.

Please refer to “Quality grade on NEC Semiconductor Devices” (Document number IEI-1209) published by

NEC Corporation to know the specification of quality grade on the devices and its recommended applications.

2

Page 3

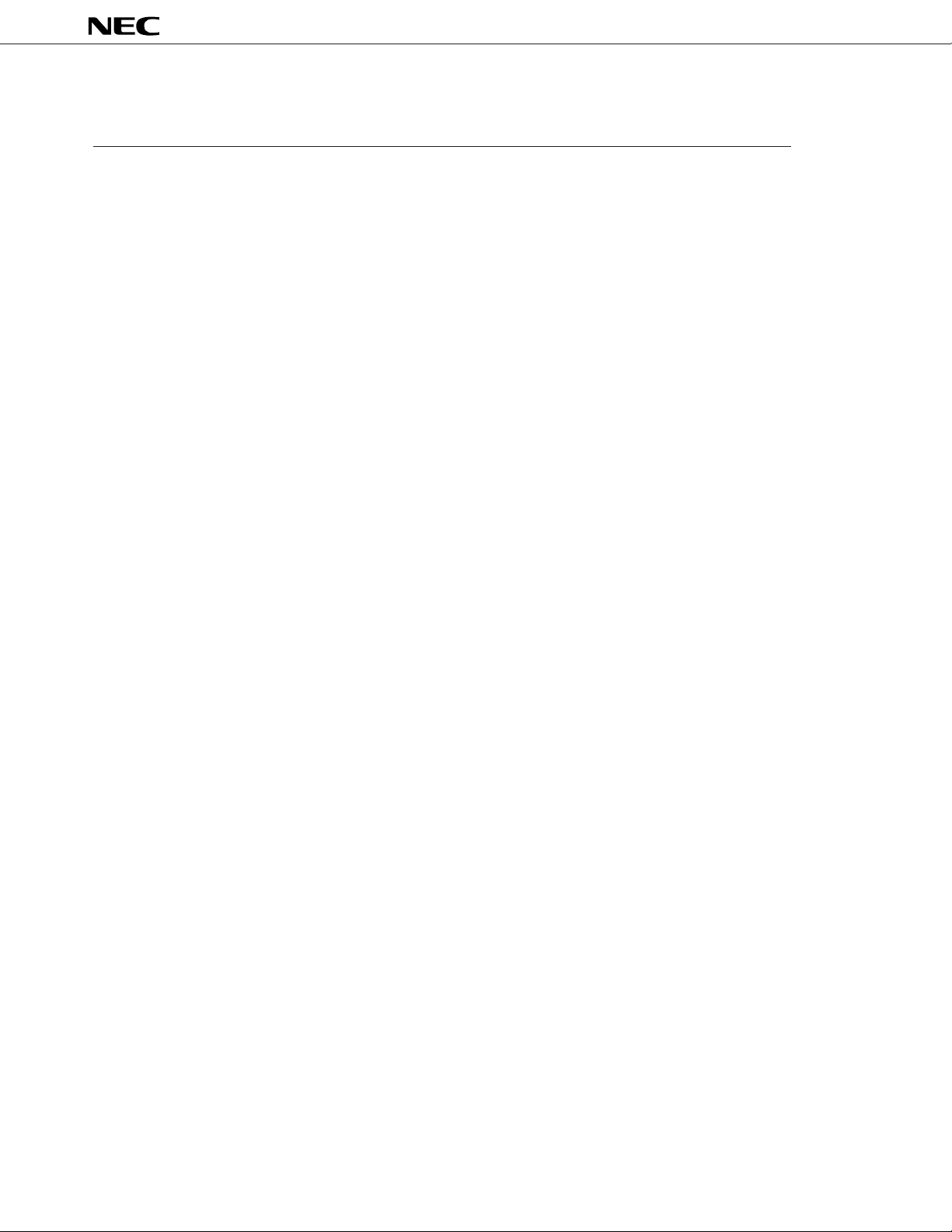

INT0

BLOCK DIAGRAM OF

P01/SCK P03/SI

P02/SO

P00/INT0

CL

PROGRAM COUNTER (10)

PROGRAM MEMORY

1024 × 8 BITS

φ

CL

SYSTEM

CLOCK

GENERATOR

CLOCK

CONTROL

STANDBY

CONTROL

CP

TIMER/EVENT

COUNTER

INSTRUCTION

DECODER

ALU

TEST

CONTROL

GENERAL REGISTERS

H (2) L (4)

STACK POINTER (6)

DATA MEMORY

SERIAL

INTERFACE

64 × 4 BITS

µ

PD7564A

PORT0

A (4)C

BUFFER

PORT8

LATCH

BUFFER

PORT10

LATCH

BUFFER

PORT11

LATCH

BUFFER

4 P00–P03

3 P80–P82

4 P100–P103

4 P110–P113

µ

PD7564A, 7564A(A)

CL1 CL2

DD

RESETV

V

SS

3

Page 4

µ

PD7564A, 7564A(A)

CONTENTS

1. PIN FUNCTIONS ......................................................................................................................................... 6

1.1 PORT FUNCTIONS ............................................................................................................................................... 6

1.2 OTHER THAN PORTS .......................................................................................................................................... 6

1.3 PIN MASK OPTION .............................................................................................................................................. 7

1.4 CAUTION ON USE OF P00/INT0 PIN AND RESET PIN ................................................................................... 7

1.5 PIN INPUT/OUTPUT CIRCUITS .......................................................................................................................... 8

1.6 RECOMMENDED CONNECTION OF UNUSED

1.7 OPERATION OF INPUT/OUTPUT PORTS ....................................................................................................... 11

µ

PD7564A PINS .................................................................. 11

2. INTERNAL BLOCK FUNCTIONS ............................................................................................................ 13

2.1 PROGRAM COUNTER (PC): 10 BITS ................................................................................................................ 13

2.2 STACK POINTER (SP): 6 BITS .......................................................................................................................... 14

2.3 PROGRAM MEMORY (ROM): 1024 WORDS × 8 BITS ................................................................................... 15

2.4 GENERAL REGISTER ......................................................................................................................................... 15

2.5 DATA MEMORY (RAM): 64 × 4 BITS ............................................................................................................... 16

2.6 ACCUMULATOR (A): 4 BITS ............................................................................................................................. 17

2.7 ARITHMETIC LOGIC UNIT (ALU): 4 BITS ........................................................................................................ 17

2.8 PROGRAM STATUS WORD (PSW): 4 BITS .................................................................................................... 17

2.9 SYSTEM CLOCK GENERATOR ......................................................................................................................... 18

2.10 CLOCK CONTROL CIRCUIT ............................................................................................................................... 19

2.11 TIMER/EVENT COUNTER ................................................................................................................................. 20

2.12 SERIAL INTERFACE ........................................................................................................................................... 21

2.13 TEST CONTROL CIRCUIT .................................................................................................................................. 23

3. STANDBY FUNCTIONS ........................................................................................................................... 25

3.1 STOP MODE ........................................................................................................................................................ 25

3.2 CANCELLING THE HALT MODE ....................................................................................................................... 25

3.3 CANCELLING STOP MODE BY RESET INPUT ................................................................................................ 26

3.4 CANCELLING HALT MODE BY TEST REQUEST FLAG ................................................................................. 26

3.5 CANCELLING HALT MODE BY RESET INPUT ................................................................................................ 26

4. RESET FUNCTIONS ................................................................................................................................. 27

4.1 DETAILS OF INITIALIZATION ........................................................................................................................... 27

5.µPD7564A INSTRUCTION SET............................................................................................................... 28

6. ELECTRICAL SPECIFICATIONS .............................................................................................................. 33

7. CHARACTERISTICS CURVES .................................................................................................................. 40

8.µPD7564A APPLIED CIRCUITS ............................................................................................................... 43

9. PACKAGE INFORMATION ....................................................................................................................... 45

4

Page 5

µ

PD7564A, 7564A(A)

10. RECOMMENDED PACKAGING PATTERN OF SOP (REFERENCE) ..................................................... 49

11. RECOMMENDED SOLDERING CONDITIONS....................................................................................... 50

APPENDIX A. COMPARISON BETWEEN SUB-SERIES PRODUCT FUNCTIONS..................................... 51

APPENDIX B. DEVELOPMENT TOOLS ........................................................................................................ 52

APPENDIX C. RELATED DOCUMENTS.......................................................................................................... 54

★

5

Page 6

1. PIN FUNCTIONS

1.1 PORT FUNCTIONS

µ

PD7564A, 7564A(A)

Pin Name Input/Output

P00 Input INT0 S

P01

P02 SO W

P03 Input SI S

P80 to P82 Output –– O

P100 to P103 Input/output ––

P110 to P113 Input/output ––

Input/output

Dual-Function

Pin Circuit

SCK

4-bit input port (Port 0)

P00 serves also as a count clock (event pulse)

input.

3-bit output port (Port 8)

High current (15 mA), middle-high voltage (9 V)

output

4-bit I/O port (Port 10)

Middle-high current (10 mA), middle-high voltage

(9 V) input/output

4-bit I/O port (Port 11)

Middle-high current (10 mA), middle-high voltage

(9 V) input/output

Function After RESET

Input

High

impedance

High

impedance

or

high-level

output

Input/Output

1.2 OTHER THAN PORTS

Pin Name Input/Output

INT0 Input P00 Edge detection testable input pin (Rising edge) S

SCK Input/output P01 Serial clock Input/output pin Input X

SO Output P02 Serial data output pin Input W

SI Input P03 Serial data input pin Input S

CL1

CL2

Dual-Function

Pin Circuit

Connection pin for ceramic oscillation ceramic

resonator

Function After RESET

Input/Output

X

P

––

System reset input pin (high-level active)

RESET R

VDD Positive power supply pin

VSS GND potential pin

A pull-down resistor can be incorporated using

the mask option.

6

Page 7

µ

PD7564A, 7564A(A)

1.3 PIN MASK OPTION

Each pin is provided with the following mask options which can be selected for each bit according to the purpose:

Pin Name Mask Options

P00 ➀ No internally provided resistor ➁ Pull-down resistor internally provided ➂ Pull-up resistor internally provided

P01 ➀ No internally provided resistor ➁ Pull-down resistor internally provided ➂ Pull-up resistor internally provided

P02 ➀ No internally provided resistor ➁ Pull-down resistor internally provided ➂ Pull-up resistor internally provided

P03 ➀ No internally provided resistor ➁ Pull-down resistor internally provided ➂ Pull-up resistor internally provided

P80 ➀ N-ch open-drain output ➁ CMOS (push-pull) output

P81 ➀ N-ch open-drain output ➁ CMOS (push-pull) output

P82 ➀ N-ch open-drain output ➁ CMOS (push-pull) output

P100 ➀ N-ch open-drain input/output ➁ Push-pull input/output

➂ N-ch open-drain + pull-up resistor built-in input/output

P101 ➀ N-ch open-drain input/output ➁ Push-pull input/output

➂ N-ch open-drain + pull-up resistor built-in input/output

P102 ➀ N-ch open-drain input/output ➁ Push-pull input/output

➂ N-ch open-drain + pull-up resistor built-in input/output

P103 ➀ N-ch open-drain input/output ➁ Push-pull input/output

➂ N-ch open-drain + pull-up resistor built-in input/output

P110 ➀ N-ch open-drain input/output ➁ Push-pull input/output

➂ N-ch open-drain + pull-up resistor built-in input/output

P111 ➀ N-ch open-drain input/output ➁ Push-pull input/output

➂ N-ch open-drain + pull-up resistor built-in input/output

P112 ➀ N-ch open-drain input/output ➁ Push-pull input/output

➂ N-ch open-drain + pull-up resistor built-in input/output

P113 ➀ N-ch open-drain input/output ➁ Push-pull input/output

➂ N-ch open-drain + pull-up resistor built-in input/output

RESET ➀ Incorporating no pull-down resistor ➁ Incorporating a pull-down resistor

★

There is no mask option for PROM products. For more information, see the µPD75P64 Data Sheet (IC-2838).

1.4 CAUTION ON USE OF P00/INT0 PIN AND RESET PIN

In addition to the functions shown in 1.1, 1.2 and 1.3, the P00/INT0 pin and RESET pin have a function for setting

the test mode in which the internal operation of the

When a potential greater than V

exceeding V

SS is applied during normal operation, the test mode will be entered and normal operation may be

SS is applied to either of these pins, the test mode is set. As a result, if noise

µ

PD7564A is tested (IC test only).

impeded.

If, for example, the routing of the wiring between the P00/INT0 pin and RESET pin is long, the above problem

may occur as the result of inter-wiring noise between these pins.

Therefore, wiring should be carried out so as to suppress inter-wiring noise as far as possible. If it is not possible

to suppress noise, anti-noise measures should be taken using external parts as shown in the figures below.

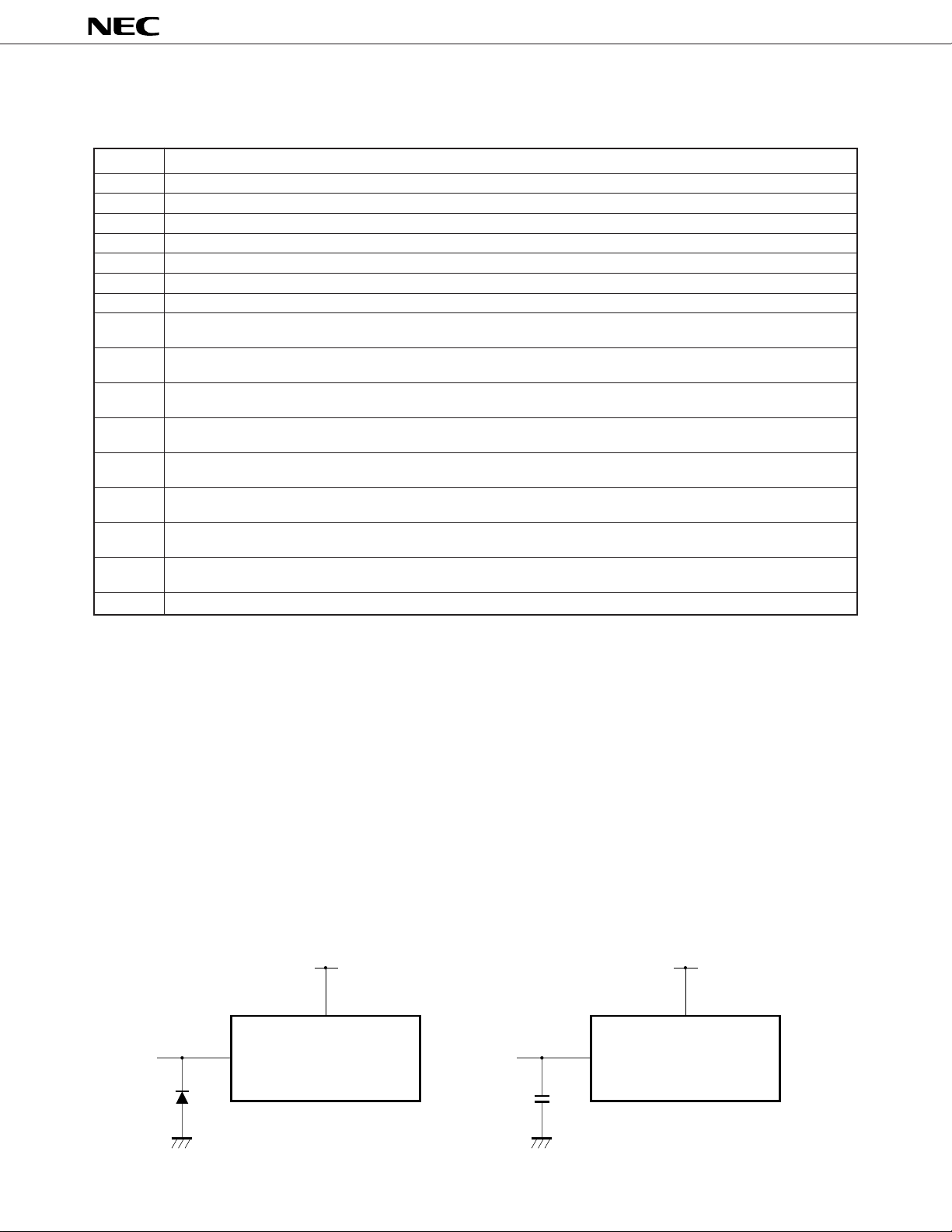

• Connection of diode with small VF between P00/

INT4/RESET pin and V

Diode

with

F

Small V

SS

V

P00/INT0, RESET

V

DD

DD

• Connection of capacitor between P00/INT0/

RESET pin and V

SS

V

P00/INT0, RESET

V

DD

DD

V

SS

V

SS

7

Page 8

1.5 PIN INPUT/OUTPUT CIRCUITS

This section presents the input/output circuit for each pin of the

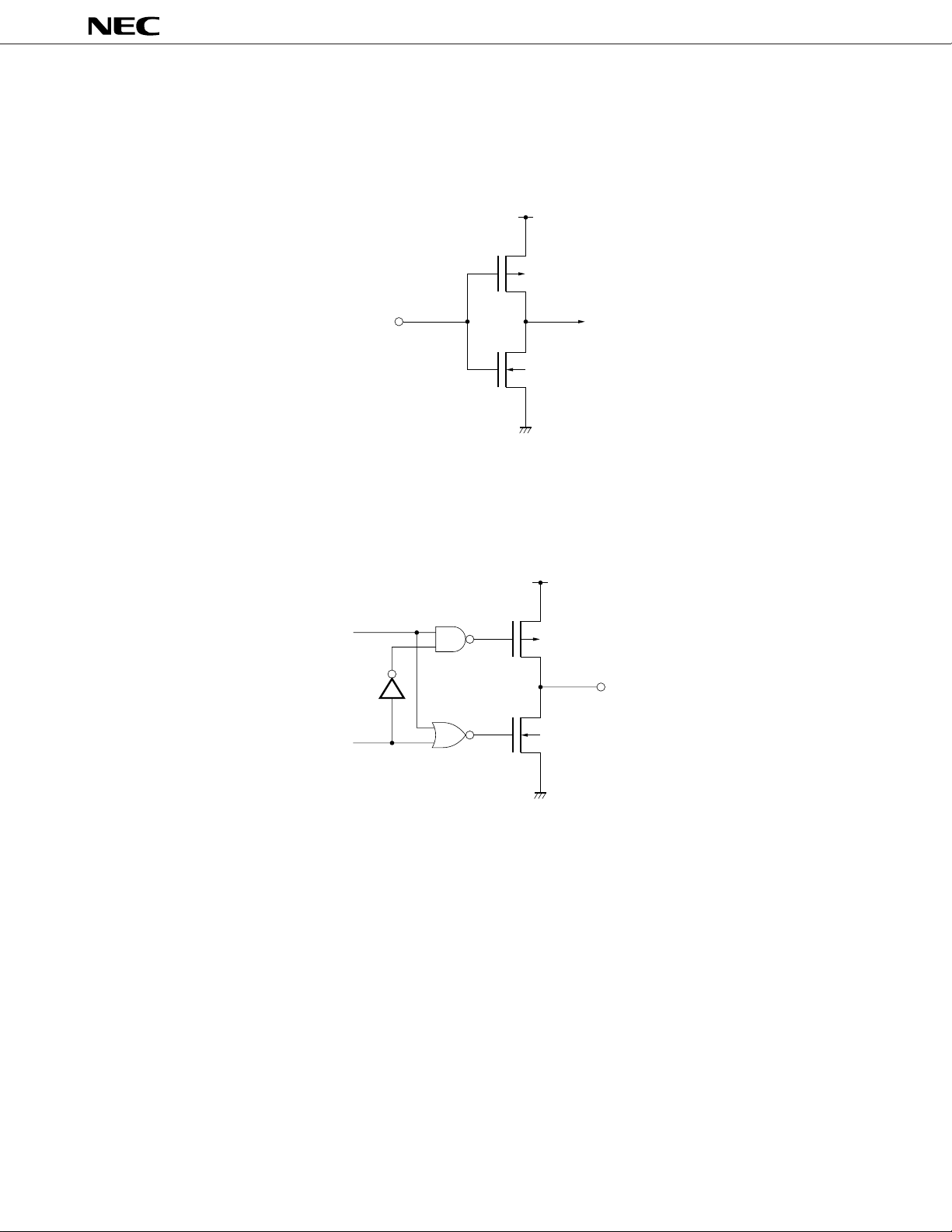

(1) Type A (for Type W)

IN

µ

PD7564A, 7564A(A)

µ

PD7564A in a partly simplified format:

VDD

P–ch

N–ch

Forming an input buffer conformable to the CMOS specification

(2) Type D (for Types W and X)

V

DD

data

output

disable

P–ch

OUT

N–ch

Forming a push-pull output which becomes high impedance (with both P-ch and N-ch off) in response to

RESET input

8

Page 9

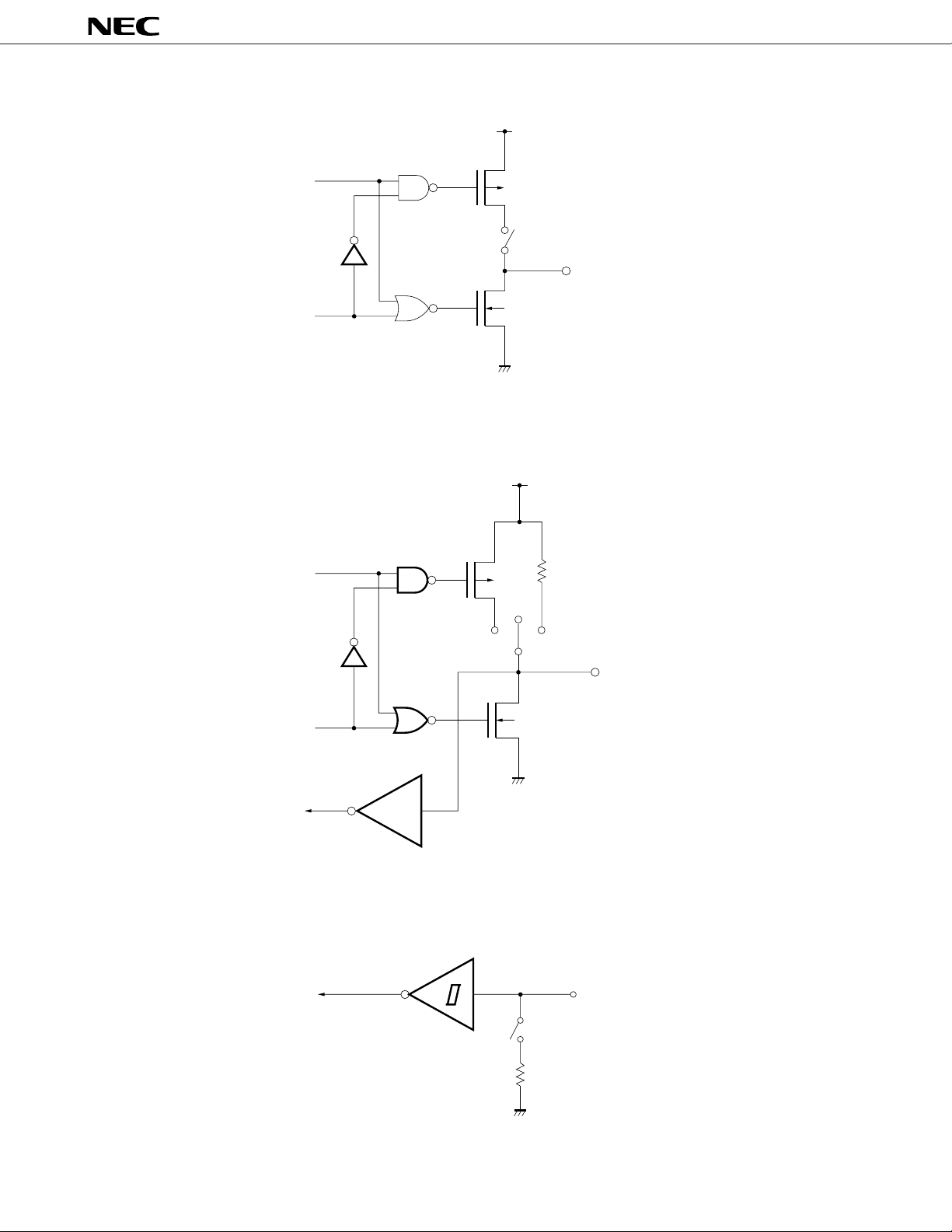

(3) Type O

µ

PD7564A, 7564A(A)

V

DD

(4) Type P

data

output

disable

data

P–ch

Mask Option

N–ch

V

DD

P–ch

OUT

(Middle-High Voltage,

High-Current)

Mask Option

(5) Type R

output

disable

Middle-High Input Buffer

(Middle-High Voltage,

N–ch

High-Current)

Mask Option

IN/OUT

9

Page 10

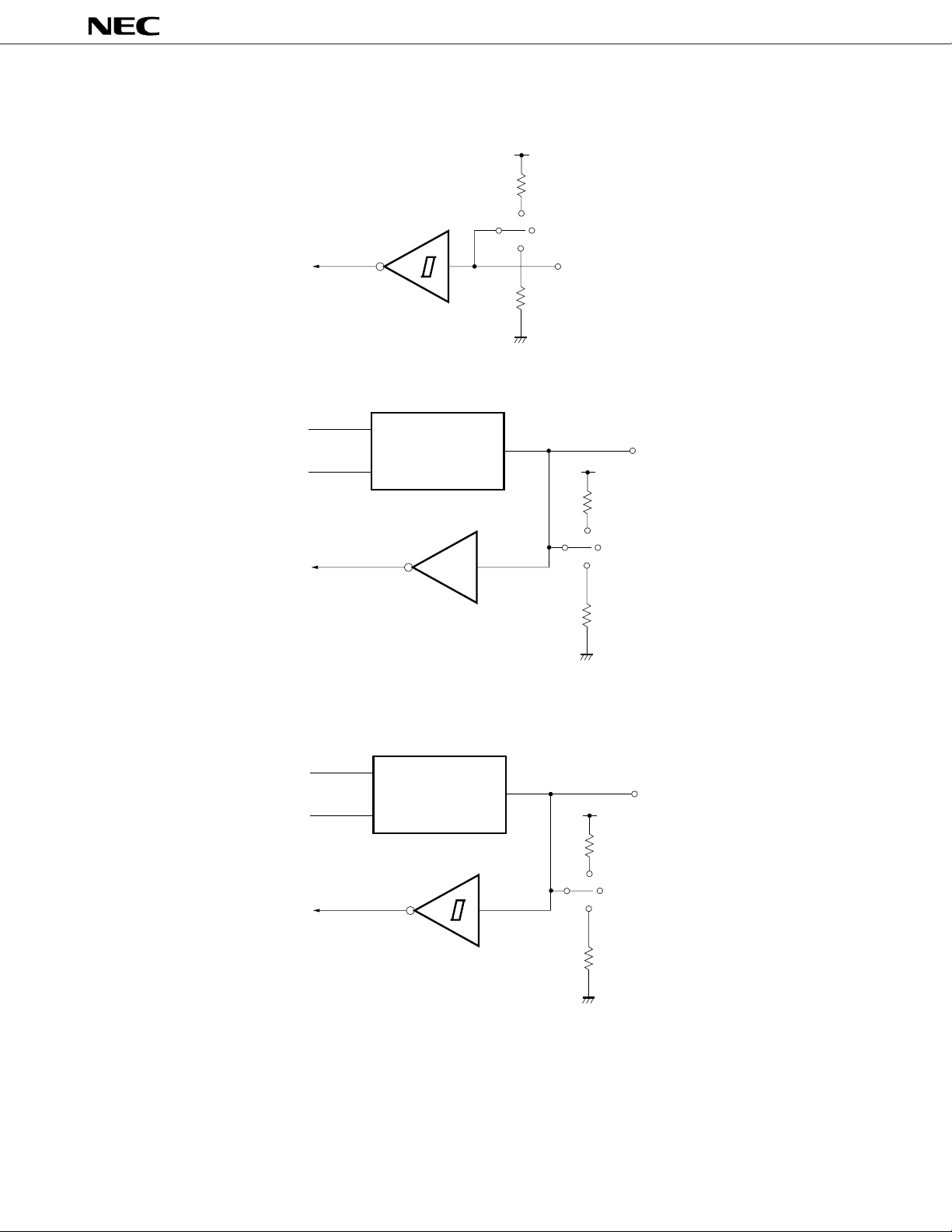

(6) Type S

(7) Type W

data

output

disable

Type D

DD

V

Mask Option

IN

V

DD

µ

PD7564A, 7564A(A)

IN/OUT

(8) Type X

data

output

disable

Type A

Type D

V

DD

Mask Option

IN/OUT

Mask Option

10

Page 11

µ

PD7564A, 7564A(A)

1.6 RECOMMENDED CONNECTION OF UNUSED µPD7564A PINS

Pin Recommended Connection

P00/INT0 Connect to VSS.

P01 to P03 Connect to VSS or VDD.

P80 to P82 Leave open.

P100 to P103

P110 to P113

1.7 OPERATION OF INPUT/OUTPUT PORTS

(1) P00 to P03 (Port 0)

The port 0 is a 4-bit input port consisting of 4-bit input pins P00 to P03. In addition to being used for port input,

P00 serves as a count clock input or testable input (INT0), each of P01 to P03 serves as a serial interface input/output.

To use P00 as a count clock input, set bits 2 (CM2) and 1 (CM1) of the clock mode register to 01. (See 2.10 “CLOCK

CONTROL CIRCUIT” for details.)

To use P00 as a INT0, set bit 3 (SM3) of the shift mode register to 1.

The serial interface function to use P01 to P03 as a serial interface I/O port is determined by bits 2 and 1 (SM2

and SM1) of the shift mode register. See 2.12 “SERIAL INTERFACE” for details.

Even though this port operates using any function other than the port function, execution of the port input

instruction (IPL) permits loading data on the P00 to P03 line to the accumulator (A0 to A3) at any time.

Input state : Connect to VSS or VDD.

Output state: Leave open.

(2) P80 to P83 (Port 8)

The port 8 is a 4-bit output port with an output latch, which consists of 4-bit output pin.

The port output instruction (OPL) latches the content of the accumulator (A0 to A3) to the output latch and outputs

it to pins P80 to P83.

The SPBL and RPBL instructions allow bit-by-bit setting and resetting of pins P80 to P82.

For these ports, mask options for the output format are available to select CMOS (push-pull) output or N-ch open-

drain output.

The port specified as a N-ch open-drain output and provides an efficient interface to the circuit operating at a

different supply voltage because the output buffer has a dielectric strength of 9 V.

11

Page 12

µ

PD7564A, 7564A(A)

(3) P100 to P103 (Port 10) and P110 to P113 (Port 11): Quasi-bidirectional input/output

P100 to P103 are 4-bit I/O pins which form the port 10 (4-bit I/O port with an output latch). P110 to P113 are 4-

bit I/O pins which form the port 11 (4-bit I/O port with an output latch).

The port output instruction (OPL) latches the content of the accumulator to the output latch and outputs it to the

4-bit pins.

The data written once in the output latch and the output buffer state are retained until the output instruction to

operate the port 10 or 11 is executed or the RESET signal is input. Even though an input instruction is executed for

the port 10 or 11, the states of both the output latch and output buffer do not change.

The SPBL and RPBL instructions allow bit-by-bit setting and resetting of pins P100 to P103 and P110 to P113.

The input/output format of each of the ports 10 and 11 can be selected from among the N-ch open-drain input/

output, N-ch open-drain + pull-up resistor built-in input/output, and CMOS (push-pull) input/output by their

respective mask options.

When the CMOS (push-pull) input/output is selected, the port cannot return to the input mode once the output

instruction is executed. However, the states of the pins of the port can be checked by reading via the port input

instruction (IPL).

When one of the other two formats is selected, the port can enter the input mode to load the data on the 4-bit

line to the accumulator (as a quasi-bidirectional port) when the port receives high level output. Select each type of

the input/output format to meet the use of the port:

➀ CMOS input/output

i) Uses all 4 bits of the port as input ports.

ii) Uses pins of the port as output pins not requiring middle withstand voltage output.

➁ N-ch open-drain input/output

i) Uses pins of the port as I/O pins requiring a middle withstand voltage dielectric strength.

ii) Uses input pins of the port which also has output pins.

iii) Uses each pin of the port for both input and output by switching them over.

➂ N-ch open-drain + pull-up resistor built-in input/output

i) Uses input pins of the port which also has output pins, that require a pull-up resistor.

ii) Uses each pin of the port for both input and output by switching them over. This requires a pull-up resistor.

Caution Before using input pins in the case of ➁ or ➂ , write 1 in the output latch to turn the N-ch transistor

off.

12

Page 13

µ

PD7564A, 7564A(A)

2. INTERNAL BLOCK FUNCTIONS

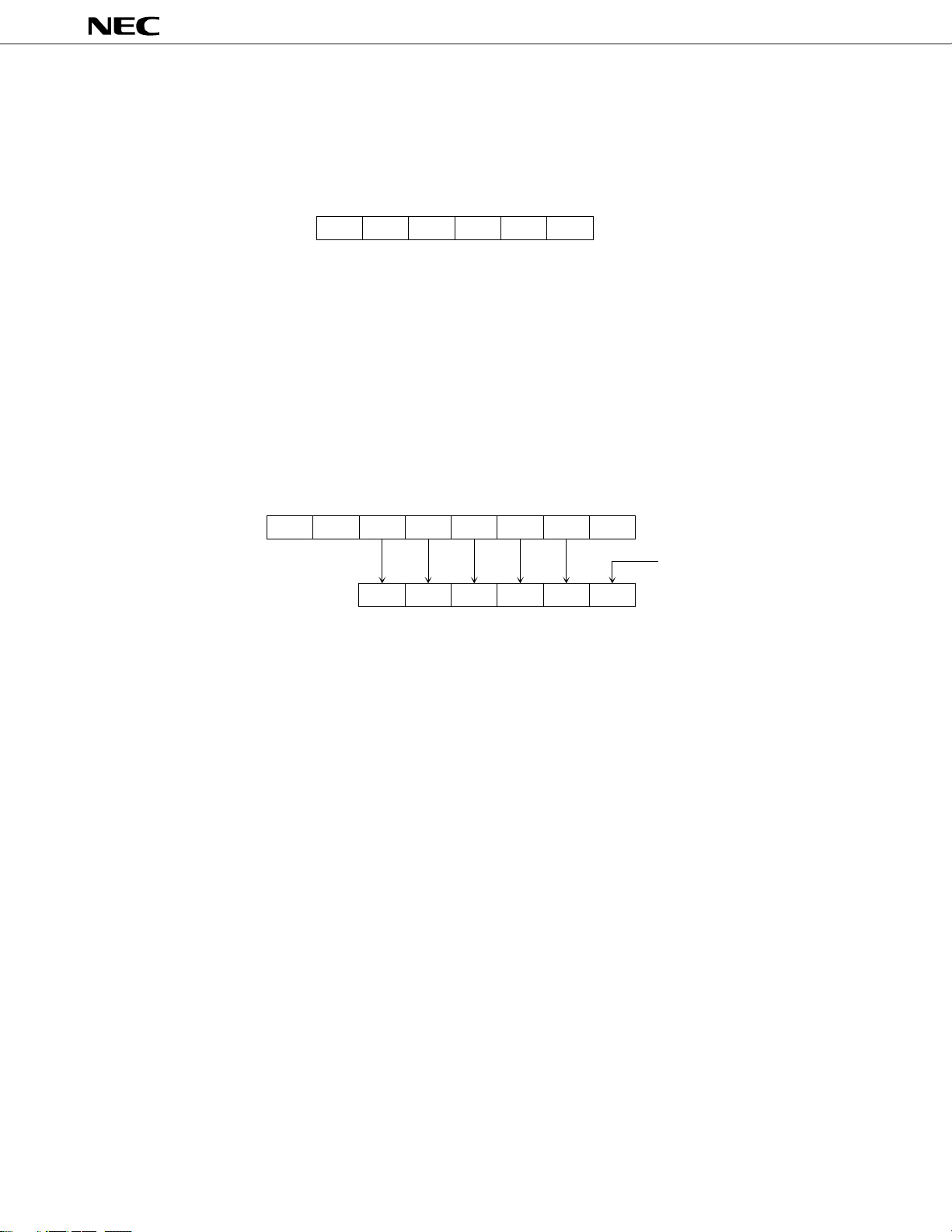

2.1 PROGRAM COUNTER (PC): 10 BITS

The program counter is a 10-bit binaryc ounter to retain program memory (ROM) address information.

Fig. 2-1 Program Counter Configuration

PC9 PC8 PC7 PC6 PC5 PC4 PC3 PC2 PC1 PC0 PC

When one instruction is executed, usually the program counter is incremented by the number of bytes of the

instruction.

When the call instruction is executed, the PC is loaded with a nkew call address after the stack memory saves

the current contents (return address) of the PC. When the return instruction is executed, the content (return address)

of the stack memory is loaded onto the PC. When the jump instruction is executed, the immediate data identifying

the destination of the jump is loaded to all or some of bits of the PC.

When a skip occurs, the PC is incremented by 2 or 3 during the machine cycle depending on the number of bytes

in the next instruction.

When the RESET signal is input, all the bits of the PC are cleared to zero.

13

Page 14

µ

PD7564A, 7564A(A)

2.2 STACK POINTER (SP): 6 BITS

The stack pointer is a 6-bit register which retains head address information of the stack memory (LIFO type) which

is a part of the data memory.

Fig. 2-2 Stack Pointer Configuration

SP5 SP4 SP3 SP2 SP1 SP0 SP

The stack pointer is decremented when the call instruction is executed. It is incremented when the return

instruction is executed.

To determine the stack area, initialize the SP using the TAMSP instruction. Note that bit SP0 is loaded with 0

unconditionally when the TAMSP instruction is executed. Set the SP to the value of “the highest address of the stack

area + 1” because the stack operation starts with decrementation of the SP.

When the highest address of the stack area is 3FH which is the highest address of the data memory, the initial

µ

value of SP5-0 must be 00H. For emulation using the

when executing the TAMSP instruction.

Fig. 2-3 In Execution of TAMSP Instruction

PD7500H (EVAKIT-7500B), set the data to be used for AM

A3 A2 A1 A0 (HL)3(HL)2(HL)1(HL)

SP5 SP4 SP3 SP2 SP1 SP0

Note that the contents of the SP cannot be read.

Caution Be sure to set the SP at the initial stage of the program execution because the SP becomes undefined

when the RESET signal is input.

Example LHLI 00H

LAI 0

ST

LAI 4

TAMSP ;SP = 40H

0

0

14

Page 15

µ

PD7564A, 7564A(A)

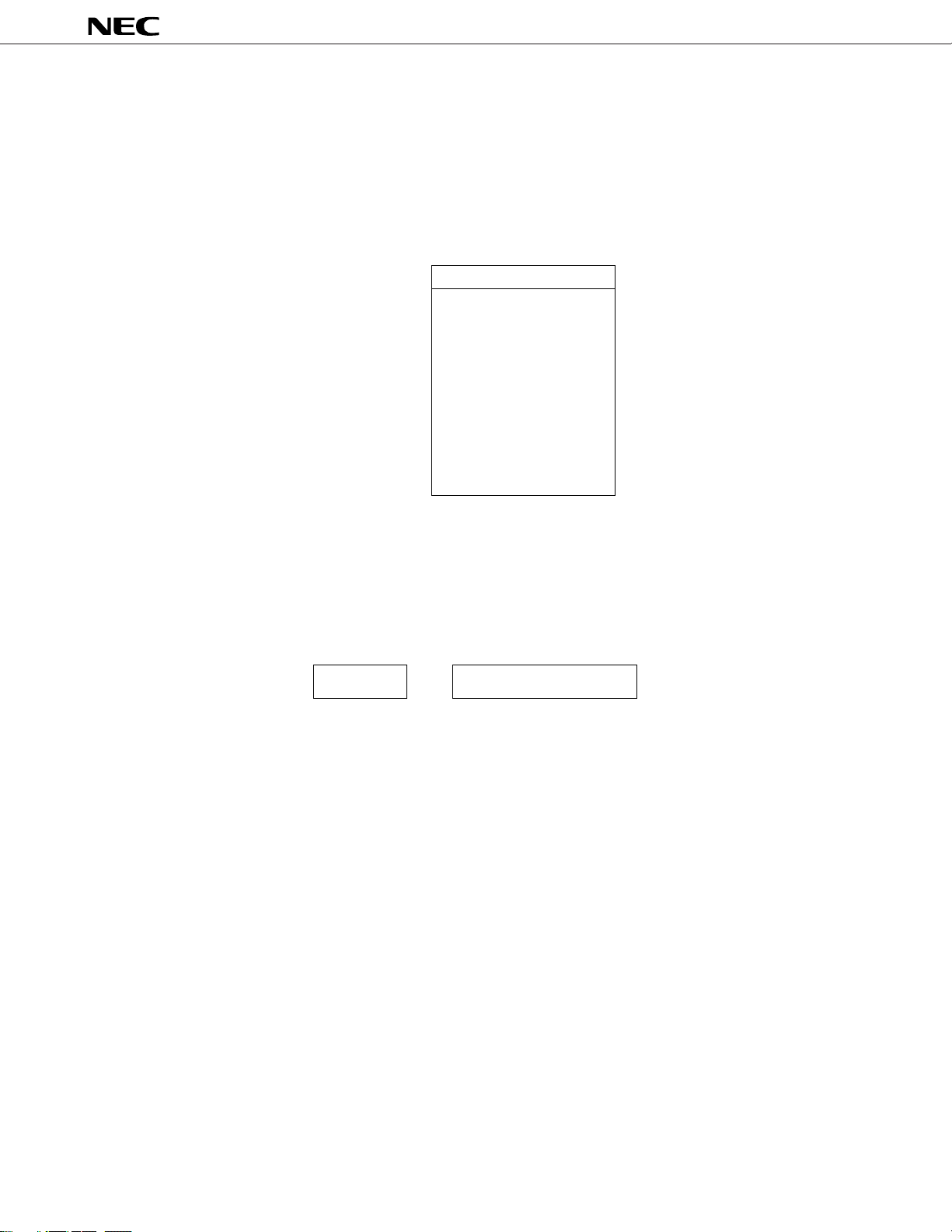

2.3 PROGRAM MEMORY (ROM): 1024 WORDS × 8 BITS

The program memory is a mask programmable ROM of 1024 word × 8 bits configuration. It is addressed by the

program counter.

The program memory stores programs.

Address 000H is the reset start address.

Fig. 2-4 Program Memory Map

(0) 000H

(1023) 3FFH

2.4 GENERAL REGISTER

General registers H (with two bits) and L (with four bits) operate individually. They also form a pair register HL

(H: high order and L: low order) to serve as a data pointer for addressing the data memory.

Fig. 2-5 General Register Configuration

10

HL

Reset Start

30

The L register is also used to specify I/O ports and the mode register when an input/output instruction (IPL or

OPL) is executed. It also used to specify the bits of a port when the SPBL or RPBL instruction is executed.

15

Page 16

µ

PD7564A, 7564A(A)

2.5 DATA MEMORY (RAM): 64 × 4 BITS

The data memory is a static RAM of 64 word × 4 bits configuration. It is used as the area to store or stack processed

data. The data memory may be processed in 8-bit units when paired with the accumulator.

Fig. 2-6 Data Memory Map

( 0 ) 00H

64 Words × 4 Bits

(63) 3FH

The data memory is addressed in the following three ways:

• Direct: Direct addressing based on immediate data of an instruction

• Register indirect: Indirect addressing according to the contents of the pair register HL (including automatic

incrementation and decrementation)

• Stack: Indirect addressing according to the contents of the stack pointer (SP)

An arbitrary space of the data memory is available as stack memory. The boundary of the stack area is specified

when the TAMSP instruction initializes the SP. After that, the stack area is accessed automatically by the call or return

instruction.

After the call instruction is executed, the content of the PC and PSW is stored in the order shown in the following

diagram:

Stack Area

30

SP – 4

SP – 3

SP – 2

SP – 1

0 0 PC9 PC8

PSW*

PC3 – PC0

PC7 – PC4

* Bit 1 is fixed at 0.

When the return instruction is executed, the content of the PSW is not restored while those of the PC are restored.

Data in the data memory is retained at a low supply voltage in the STOP mode.

16

Page 17

µ

PD7564A, 7564A(A)

2.6 ACCUMULATOR (A): 4 BITS

The accumulator is a 4-bit register which plays a major role in many types of arithmetic operations. The

accumulator may be processed in 8-bit units when paired with the data memory addressed by the pair register HL.

Fig. 2-7 Accumulator Configuration

A3 A2 A1 A0 A

2.7 ARITHMETIC LOGIC UNIT (ALU): 4 BITS

The arithmetic logic unit is a 4-bit arithmetic circuit to perform arithmetic and bit processing such as binary

addition, logical operation, incrementation, decrementation, and comparison.

2.8 PROGRAM STATUS WORD (PSW): 4 BITS

The program status word consists of skip flags (SK1 and SK0) and a carry flag (C). Bit 1 of the PSW is fixed at 0.

Fig. 2-8 Program Status Word Configuration

3210

SK1 SK0 0 C PSW

(1) Skip flags (SK1 and SK0)

Skip flags store the following skip status:

• Stacking by the LAI instruction

• Stacking by the LHLI instruction

• Skip condition establishment by any instruction other than stack instructions

The skip flags are set and reset automatically when respective instructions are executed.

(2) Carry flag (C)

The carry flag is set to 1 when a carry from bit 3 of the ALU occurs when the add instruction (ACSC) is executed.

The flag is reset to 0 when the carry does not occur. The SC and RC instructions respectively set and reset the carry

flag. The SKC instruction tests the contents of the flag.

The content of the PSW are automatically stored in the stack area when the call instruction is executed. It cannot

be restored by the return inhstruction.

When the RESET signal is input, SK1 and SK0 are both cleared to zero and C becomes undefined.

17

Page 18

µ

PD7564A, 7564A(A)

2.9 SYSTEM CLOCK GENERATOR

The system clock generator contains an ceramic oscillator, 1/2 divider, and standby (STOP/HALT) mode control

circuit.

Fig. 2-9 System Clock Generator

STOP F/F

STOP*

HALT*

RESET (High)

HALT RELEASE

RESET ( )

RESET ( )

(To CPU)

φ

CL (System Clock)

CL1

CL2

Oscillator

Stop

Ceramic

Oscillator

QS

R

* Instruction execution

HALT F/F

QS

R

1/2

The ceramic oscillator oscillates with a ceramic resonator R connected to pins CL1 and CL2.

φ

The ceramic oscillator outputs the system clock (CL) which is 1/2 divided to the CPU clock (

).

The control circuit in the standby mode consists mainly of STOP F/F and HALT F/F.

The STOP F/F is set by the STOP instruction to stop ceramic oscillation, blocking every clock from being supplied

(STOP mode). The STOP F/F is reset by the RESET input (high level) to restart ceramic oscillation. When the RESET

input returns to the low level after that, the oscillator once more supplys each clock.

The HALT F/F is set by the HALT instruction to disable the input to the 1/2 divider which generates the CPU clock

φ

, stopping only the CPU clock φ (HALT mode).

The HALT F/F is reset at the fall of the HALT RELEASE signal (which goes active when even one test request flag

is set) or the RESET input signal, causing the oscillator to start supplying the CPU clock φ.

The HALT F/F remains on for the same function of the HALT mode even while the RESET input is active (high).

When a power-on reset occurs, ceramic oscillation starts at rise of the RESET input signal. However, it takes a

certain time for the oscillation output level to be stabilized after the start of oscillation. To prevent the CPU from

malfunctioning by unstable clock pulses, the standby mode control circuit sets the HALT F/F while the RESET input

remains high to suppress the CPU clock

φ

. Thus the high-level duration of the RESET input must be set so that it

exceeds the stabilizing time required for the ceramic resonator to be used.

18

Page 19

µ

PD7564A, 7564A(A)

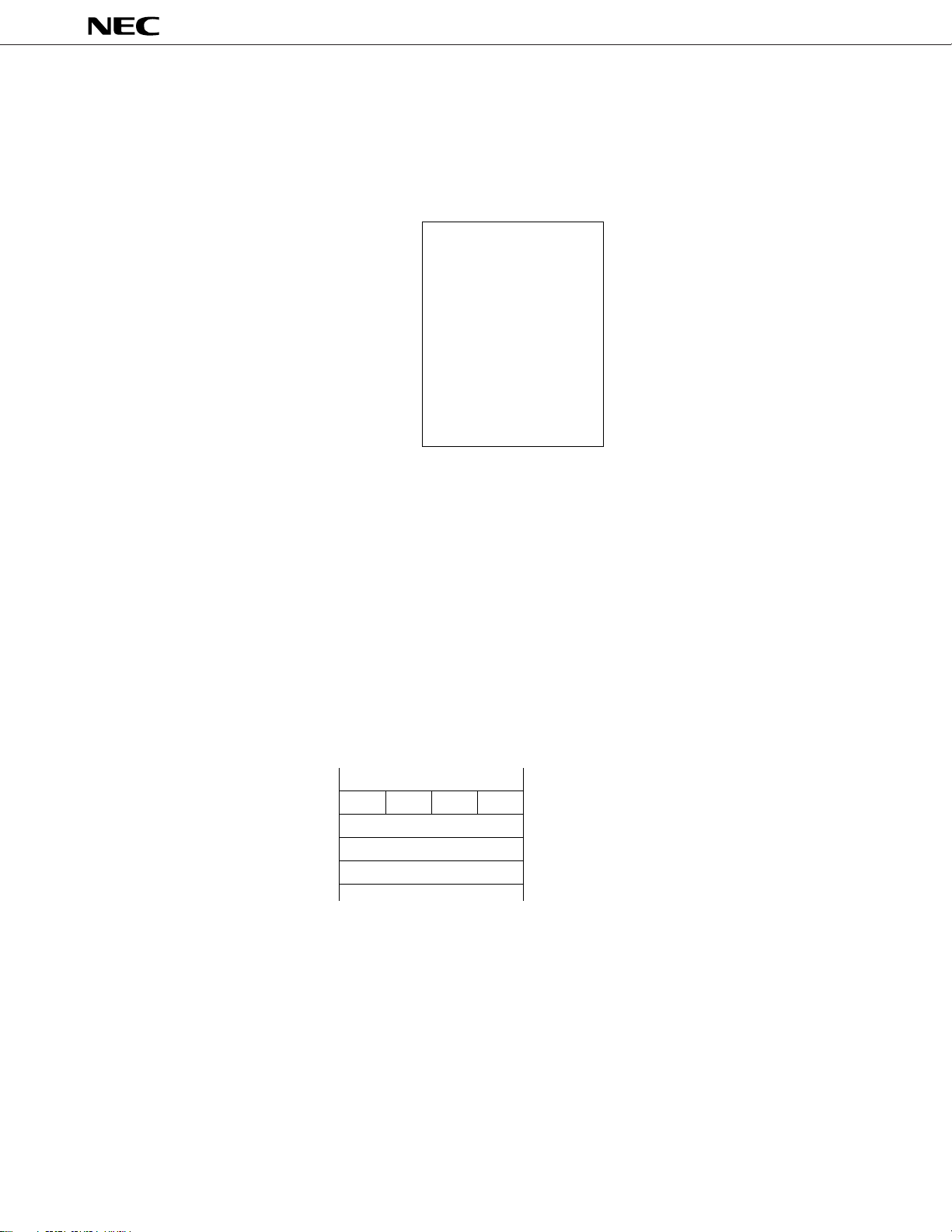

2.10 CLOCK CONTROL CIRCUIT

The clock control circuit consists of 2-bit clock mode registers (CM2 and CM1), prescalers 1, 2 and 3, and a

multiplexer. The circuit inputs the system clock generator output (CL) and the event pulse (P00). It also selects a

clock source and a prescaler according to the specifications of clock mode register and supplies a count pulse (CP)

to the timer/event counter.

Fig. 2-10 Clock Control Circuit

Internal Bus

OPL*

CM2 CM1

CL

P00

PRESCALER 1

(1/4)

* Instruction execution

Use the OPL instruction to set codes in the clock mode registers.

Fig. 2-11 Clock Mode Register Format

CM2 CM1

Clock Mode Register

PRESCALER 2

(1/8)

PRESCALER 3

(1/8)

CP

CM2 CM1 Count Pulse Frequency (CP)

0 0 CL ×

0 1 P00

1 0 CL ×

1 1 CL ×

256

1

1

32

1

4

Caution When setting codes in the clock mode registers using the OPL instruction, be sure to set bit 0 of the

µ

accumulator to 0. (Bit 0 corresponds to CM0 of the

PD7500 of EVAKIT-7500B in emulation.)

19

Page 20

2.11 TIMER/EVENT COUNTER

The timer/event counter is based on an 8-bit count register as shown in Fig. 2-12.

Fig. 2-12 Timer/Event Counter

Internal Bus

µ

PD7564A, 7564A(A)

*

TIMER

RESET

8

INTT

(To Test Control Circuit)

CLR

*TCNTAM

CP

Count

Holding

Circuit

8-BIT COUNT REG

* Instruction execution

The 8-bit count register is a binary 8-bit up-counter which is incremented whenever a count pulse (CP) is input.

The register is cleared to 00H when the TIMER instruction is executed, RESET signal is input, or an overflow occurs

(FFH to 00H).

As the count pulse, the clock mode register can select one of the following four. See 2.10 “CLOCK CONTROL

CIRCUIT”.

CP : CL × ––, CL × –––, CL × ––––, P00

11 1

4 32 256

The count register continues to be incremented as long as count pulses are input. The TIMER instruction clears

the count register to 00H and triggers the timer operation.

The count register is incremented in synchronization with the CP (or the rise of the P00 input when an external

clock is used). On the count reaches 256, the register returns the count value to 00H from FFH, generates the overflow

signal INTT, and sets the INTT test flag INTT RQF.

In this way, the count register counts over from 00H.

To recognize the overflow, test the flag INTT RQF using the SKI instruction.

When the timer/event counter serves as a timer, the reference tiome is determined by the CP frequency. The

precision is determined by the system clock oscillator frequency when the system clock system is selected and by

the P00 input frequency when the P00 input is selected.

The content of the count register can be read at any time by the TCNTAM instruction. This function allows

checking the current time of the timer and counting event pulses input to the P00 input. This enables the number

of even pulses that have been generated so far (event counter function).

The count holding circuit ignores the change of the count pulse (CP) during execution of the TCNTAM instruction.

This is to prevent reading undefined data in the count register using the TCNTAM instruction while the counter is

being updated.

Since the timer/event counter operates the system clock system (CL) or the P00 input for count pulses, it is used

to cancel the HALT mode which stops the CPU clock

φ

as well as the STOP mode which stops the system clock CL.

(See 3. “STANDBY FUNCTIONS”.)

20

Page 21

µ

PD7564A, 7564A(A)

2.12 SERIAL INTERFACE

The serial interface consists of an 8-bit shift register, 3-bit shift mode register, and 3-bit counter. It is used for

input/output of serial data.

Fig. 2-13 Serial Interface Block Diagram

Internal Bus

*IPL *TSIOAM TAMSIO*

48

8

OPL*

P03/SI

P02/SO

LSB

8–BIT SHIFT REG

MSB

SHIFT MODE REG

SM3

3–BIT CNT

P01/SCK

φ

INT0P00/INT0

R

RS F/F

SQ

INTS

SIO*

* Instruction execution

Remarks 1.φ indicates the internal clock signal (system clock).

2. SM3 and INT0 go to the test control circuit.

Input/output of serial data is controlled by the serial clock. The highest bit (bit 7) of the shift register is output

from the SO line at rise of the serial clock (SCK pin signal). At its fall, the contents of the shift register is shifted by

one bit (bit n → bit n+1) and data on the SI line is loaded to the lowest bit (bit 0) of the shift register.

The 3-bit counter (octal counter) counts serial clock pulses. Wthenever it counts eight clock pulses (on completion

of 1-byte serial data transfer), the counter generates an internal test request signal INTS to set the test request flag

(INT0/S RQF).

SCK

SI

DI

7

MSB

DO

SO

7

Remarks 1. DI: Serial data input

2. DO: Serial data output

Fig. 2-14 Shift Timing

DI

6

DI

5

DI

4

DI

3

DI

6

DO5DO4DO3DO2DO1DO

DO

INTS RQF

Setting Timing

2

DI

1

DI

0

LSB

0

21

Page 22

µ

PD7564A, 7564A(A)

The serial interface sets serial data for transmission in the shift register using the TAMSIO instruction and starts

the transfer using the SIO instruction. To recognize the termination of one-byte transfer, check the test request flag

INT0/S RQF using the corresponding instruction.

The serial interface starts serial data reception, using the SIO instruction, checks the termination of one-byte

transfer using the instruction, and then receives data from the shift register by executing the TSIOAM instruction.

Two types of serial clock sources are available: one is the system clock

input). They are selected respectively by bits 2 and 1 (SM2 and SM1) of the shift mode register.

When the system clock φ is selected and the SIO instruction is executed, the clock pulse is supplied to the serial

interface as a serial clock to control serial data input/output and is output from the SCK pin.

When the system clock φ pulse is supplied eight times, the supply to the serial interface is automatically stopped

and the SCK output remains high. Since serial data input/output stops automatically after transfer of one byte. The

programmer does not need to control the serial clock. In this case, the transfer speed is determined by the system

clock frequency.

In this mode, it is possible to read receive data (by the TSIOAM instruction) and write data (by the TAMSIO

instruction) from and to the shift register only by waiting for 6 machine cycles after execution of the SIO instrucction

on the program without waiting until the INT0/S RQF is set.

Fig. 2-15 TAMSIO/TSIOAM Instruction Execution Timing

φ

and the other is the external clock (SCK

SIO

Machine Cycle

SCK

When the external clock (SCK input) is selected, the interface inputs serial clock pulses from the SCK input. When

an external serial clock pulse is input eight times, the INT0/S RQF is set and the termination of one-byte transfer

can be recognized. However, the eight serial clocks to be input must be counted on the side of the external clock

source because serial clock disable control is not performed internally. The transfer speed is determined by the

external serial clock within the range from DC to the maximum value limited by the standard.

When the external clock is used, the SIO, TAMSIO, or TSIOAM instruction the execution must be executed while

the serial clock pulse SCK is high. If such an instruction is executed while the SCK is rising or falling or is low, the

function of the instruction is not guaranteed.

Wait (6 Machine Cycle)Instruction Execution

TAMSIO

TSIOAM

22

Page 23

Fig. 2-16 Shift Mode Register Format

µ

PD7564A, 7564A(A)

SM3 SM2 SM1

Shift Mode Register

Settings for serial interface operation and the associated mode of the port 0

SM2 SM1 P03/SI P02/SO P01/SCK Serial Operation

00

01

10

1 1 SCK output (

Port input Port input

SI input SO output

Port input

φ

continuous output

SCK input Operation based on external clock

φ

Stop

× 8) Operation based on

φ

INT0/INTS selection

SM3 Test Sources

0 INTS

1 INT0

Caution When setting a code in the shift mode register using the OPL instruction, be sure to set bit 0 of the

accumulator to 0 (Bit 0 corresponds to CM0 of the

µ

PD7500H of EVAKIT-7500B in emulation).

In the system which does not require serial interface, the 8-bit shift register can be used as a simple register and

data can be read or writtene by the TSIOAM or TAMSIO instruction when serial operation is off.

2.13 TEST CONTROL CIRCUIT

The µPD7564A is provided with the following three types of test sources (one external source and two internal

sources):

Test Sources Internal/External Request Flag

INTT (Overflow from timer/event counter) Internal INTT RQF

INT0 (Test request signal from P00 pin) External

INTS (Transfer end signal from serial interface) Internal

INT 0/S RQF

The test control circuit checks consist mainly of test request flags (INTT RQF and INT0/S RQF) which are set by

three different test sources and the test request flag control circuit which checks the content of test request flags

using the SKI instruction and controls resetting the checked flags.

The INT0 and INTS are common in the request flag. Which one is selected is determined by bit 3 (SM3) of the

shift mode register.

SM3 Test Sources

0 INTS

1 INT0

23

Page 24

µ

PD7564A, 7564A(A)

The INTT RQF is set when a timer overflow occurs and is reset by the SKI or TIMER instruction.

The INT0/S request flag functions in the following two ways according to the setting of the SM3:

(1) SM3 = 0

The INTS is validated. The request flag INT0/S RQF is set when the INTS signal to indicate the termination of 8-

bit serial data transfer is issued. The flag is reset when the SKI or SIO instruction is executed.

(2) SM3 = 1

The IN0 is validated. The request flag INT0/S RQF is set when the leading edge signal enters the INT0/P00 pin.

The flag is reset when the SKI instruction is executed.

The OR output of each test request flag is used to cancel the HALT mode. If one or more request flags are set

in the HALT mode, the standby mode is cancelled.

The RESET signal cancels every request flag and the SM3. In the reset initial status, the INTS is selected and the

INT0 input is disabled.

Fig. 2-17 Test Control Circuit Block Diagram

Internal Bus

OPL*

SM3

INTT

INTS

INT0

*SIO

NONSYNC

EDGE GATE

NONSYNC

EDGE GATE

* Instruction execution

Remarks SM3 is bit 3 of the shift mode register.

TEST RQF

CONTROL

TIMER*

S

R

S

R

SKI*

INTT

RQF

INT0/S

RQF

Q

Q

HALT

RELEASE

24

Page 25

µ

PD7564A, 7564A(A)

3. STANDBY FUNCTIONS

The µPD7564A provides two types of standby modes (STOP and HALT modes) to save power while the program

is on standby. The STOP and HALT modes are set by the STOP and HALT instructions, respectively. The STOP mode

stops every clock and the HALT mode stops only the CPU clock φ. The HALT mode halts program execution, however,

it holds the contents of all the internal registers and data memory that have been stored.

The serial interface and timer/event counter can operate even in the HALT mode.

The STOP mode is cancelled only by RESET input. The HALT mode is cancelled when the test request flag (INTT

RQF or INT0/S RQF) is set or by RESET input. Note that if even one test request flag is set, the device cannot enter

either the STOP or HALT mode even though the STOP or HALT instruction is executed. Before setting the STOP

or HALT mode at a point where a test request flag may be set, execute the SKI instruction to reset the test request

flag.

3.1 STOP MODE

When the STOP instruction is executed, the device can enter the STOP mode at any time unless any request flag

is set.

In the STOP mode, the contents of the data memory are retained and the RESET input used to cancel the STOP

mode is valid. In the STOP mode, however, any other functions are turned off to minimize power consumption.

Caution In the STOP mode, the CL1 input is internally connected to V

ceramic oscillator.

3.2 CANCELLING THE HALT MODE

The HALT mode stops only the 1/2 divider in the system clock generator (allowing operation of the system clock

CL and stopping the CPU clock

φ

using

generator and the event pulse from the (P00) pin to supply the count pulses (CP) for both subsystems selectively

to the timer event counter. Thus, the timer event counter can operate depending on the both-system count pulses

and continue counting time.

as a serial clock are stopped in the HALT mode.

Since the HALT mode allows operation of the clock control circuit, the circuit inputs the CL signal from the clock

The serial interface operates in this mode when the external clock (SCK input) is selected as a serial clock.

φ

). Therefore, the operations of the CPU requiring the φ signal and the serial interface

DD (high level) to prevent a leak in the

25

Page 26

µ

g

PD7564A, 7564A(A)

3.3 CANCELLING STOP MODE BY RESET INPUT

When the RESET input goes high from low in the STOP mode, the standby mode returns to the HALT mode to

start ceramic oscillation.

When the RESET input returns to low, the HALT mode is cancelled and the CPU starts the program from address

0 after normal reset operation. The STOP mode is cancelled in this way.

Note that the content of the data memory is retained even during the cancelling operation, however, the content

of the other registers becomes undefined on cancellation.

Fig. 3-1 STOP Mode Cancel Timing

STOP

instruction

RESET Input

STOP Mode

HALT Mode

(Oscillation stabilizing time)

Starting Clock Oscillation

Cancellation

Normal Resetting Operation

(Starting from address 0)

Caution The STOP mode does not result from setting the test request flag.

3.4 CANCELLING HALT MODE BY TEST REQUEST FLAG

When the test request flat (INTT RQF or INT0/S RQF) is set in the HALT mode, the mode is cancelled and the

program stars executing the instruction that follows the HALT instruction.

Cancellation of the HALT mode does not affect the content of any register or the data memory, that is retained

in the mode.

3.5 CANCELLING HALT MODE BY RESET INPUT

RESET input cancels the HALT mode unconditionally.

Fig. 3-2 shows the HALT mode unconditionally.

Fig. 3-2 HALT mode cancel timing by RESET input

RESET

HALT Mode Cancellation

Normal Resetting Operation

(Startin

from address 0)

The HALT mode is maintained while the RESET input is being active (high). When the RESET input goes low, the

HALT mode is cancelled and the CPU starts to execute the program from address 0 after a normal reset operation.

Note that RESET input does not affect the content of the data memory that is retained in the HALT mode, however,

the contents of the other registers become undefined on cancellation of the mode.

26

Page 27

µ

PD7564A, 7564A(A)

4. RESET FUNCTIONS

The µPD7564A is reset and initialized when the RESET pin inputs a high or active RESET signal as follows:

4.1 DETAILS OF INITIALIZATION

(1) The program counter (PC9-PC0) is cleared to zero.

(2) The skip flags (SK1 and SK0) in the program status word are reset to zero.

(3) The count register in the timer-event counter is cleared to 00H.

(4) The clock control circuit becomes as follows:

• Clock mode registers (CM2 and CM1) = 0

➞ CP = CL × –––––

• Prescalers 1, 2, and 3 = 0

(5) The shift mode register (SM3 to SM1) is cleared to zero.

→ Shifting of the serial interface is stopped.

→ The port 0 enters the input mode (high impedance).

→ INT0/S, INTS is selected.

(6) The test request flag (INTT RQF or INT0/S RQF) is reset to zero.

(7) The contents of the data memory and the following registers become undefined:

Stack pointer (SP)

Accumulator (A)

Carry flag (C)

General registers (H and L)

Output latch of each port

(8) The output buffer of every port goes off and has high impedance. The I/O port enters the input mode.

Caution When the STANDBY mode is cancelled by the RESET signal, the content of the data memory is retained

without becoming undefined.

When the RESET input is cancelled, the program is executed starting with address 000H. The content of each

register shall either be initialized in the process of the program or reinitialized depending on conditions.

1

256

27

Page 28

5.µPD7564A INSTRUCTION SET

(1) Operand representation and description

addr 10-bit immediate data or label

caddr 10-bit immediate data or label

caddr1 100H to 107H, 140H to 147H, 180H to 187H,

IC0H to IC7H immediate data or label

mem 6-bit immediate data or label

n5 5-bit immediate data or label

n4 4-bit immediate data or label

n2 2-bit immediate data or label

bit 2-bit immediate data or label

pr HL-, HL+, HL

(2) Mnemonics for operation descriptions

A : Accumulator

H : H register

L : L register

HL : Pair register HL

pr : Pair register HL-, HL+, or HL

SP : Stack pointer

PC : Program counter

C : Carry flag

PSW : Program status word

SIO : Shift register

CT : Count register

In : Immediate data to n5, n4 or n2

Pn : Immediate data to addr, caddr, or caddr1

Bn : Immediate data to bit

Dn : Immediate data to mem

Rn : Immediate data to pr

(××) : Content addressed by ××

×H : Hexadecimal data

µ

PD7564A, 7564A(A)

28

Page 29

(3) Port/mode register selection

IPL Instruction

L Port

0 Port 0

AH Port 10

BH Port 11

OPL Instruction

L Port/mode register

8 Port 8

AH Port 10

BH Port 11

CH Clock mode register

FH Shift mode register

µ

PD7564A, 7564A(A)

RPBL/SPBL Instruction

LFHEHDHCHBHAH98210

Bit32103210210

Port Port 11 Port 10 Port 8

(4) Selection of pair register addressing

pr R1 R0

HL– 0 0

HL+ 0 1

HL 1 0

29

Page 30

30

Mne- Ope- Operation Code

Note

monic rands B1 B2 Condition

LAI n4 0001I

LHI n2 001010I

LAM pr 010100R

LHLI n5 1 1 0 I

3 I2

4 I3 I2

I1 I0

1 I0

1R0

I1 I0

A←n4 Loads n4 to the accumulator. Stack LAI

H←n2 Loads n2 to H register.

A←(pr) pr = HL –, HL +, HL

H←0I4, L←I3–0

ST 01010111 (HL)←A

3 I2

3 I2

I1 I0

1R0

I1 I0

STII n4 0100I

Load/store instructions

XAL 01111011 A↔L

XAM pr 010101R

AISC n4 0000I

(HL)←n4, L←L+1

A↔(pr) pr = HL – , HL + , HL

A←A + n4 Adds the accumulator to n4. Carry

ASC 01111101 A←A + (HL)

Operation

Loads the contents of the memory L = FH(HL –)

address by pr to the accumulator. L = 0 (HL +)

Loads n5 to the pair register HL. Stack LHLI

Stores the contents of the accumulator

in the memory addressed by HL.

Stores n4 in the memory addressed by

HL and increments the L register.

Exchanges the contents of the accumu-

lator and the L register.

Exchanges the contents of the accumu- L = FH (HL–)

lator and the memory addressed by pr. L = 0 (HL+)

Adds the contents of the accumulator

and the memory addressed by HL.

Adds the contents of the accumulator,

ACSC 01111100 A, C←A + (HL) + C the memory addressed by HL, and of Carry

the carry flag.

Calculate the exclusive OR of the

EXL 01111110 A←A ∀ (HL) contents of the accumulator and the

Operation instructions

memory addressed by HL.

CMA 01111111 A←A

––

Complements the accumulator.

RC 01111000 C←0 Resets the carry flag.

SC 01111001 C←1 Sets the carry flag.

Accumulator &

carry flag

manipulation

instructions

ILS 01011001 L←L + 1 Increments the L register. L = 0

IDRS mem 0011110100D

5

D4D3D2D1D

0 (mem)←(mem) + 1

Increments the contents of the memory

addressed by mem.

DLS 01011000 L←L – 1 Decrements the L register. L = FH

DDRS mem 0011110000D

Increment/decre-

ment instructions

RMB bit 011010B

SMB bit 011011B

Memory bit

manipulation

Iistructions

1B0

1B0

5

D4D3D2D1D

0 (mem)←(mem) – 1

(HL)bit←0

(HL)bit←1

Decrements the contents of the memory

addressed by mem.

Resets the bits specified by B

1–0, of the

memory addressed by HL.

Sets the bits specified by B

1–0, of the

memory addressed by HL.

Skip

Carry

(mem) = 0

(mem) = FH

µ

PD7564A, 7564A(A)

Note Instruction Group

Page 31

Mne- Ope- Operation Code

Note

monic rands B1 B2 Condition

JMP addr 001000P

Jump

JCP addr 1 0 P

instructions

5 P4 P3

9P8 P7P6

P2 P1 P0

P5P4P3P2P

1P0 PC9–0←P9–0

PC5–0←P5–0

(SP–1)(SP–2)(SP–4)←PC

CALL caddr 001100P

9P8 P7P6

P5P4P3P2P

1P0 (SP–3)←PSW, SP←SP – 4 stacxk memory, decrements SP by 4, and

PC9–0←P9–0

(SP–1)(SP–2)(SP–4)←PC

4 P3

CAL caddr1 1 1 1 P

P2 P1 P0

RT 01010011

(SP–3)←PSW, SP←SP – 4 stacxk memory, decrements SP by 4, and

PC9–0←0 1 P

9–0←(SP)(SP+2)(SP+3) Restores the contents of the stack

PC

4 P3 0 0 0 P2 P1 P

SP←SP + 4 memory to PC, and increments SP by 4.

Operation

Jumps to the address specified by P

Jumps to the address specified by

replacing PC5–0

9–0

Saves the contents of PC and PSW to the

with P5–0.

calls the address specified by caddr.

9–0

Saves the contents of PC and PSW to the

0 calls the address specified by caddr1.

9–0.

PC9–0←(SP)(SP+2)(SP+3) Restores the contents of the stack

RTS 01011011 SP←SP + 4 memory to PC, increments SP by 4,

then skip unconditionally and causes unconditional skipping.

Transfers the two low-order bits of the

Subroutine/stack control instructions

TAMSP 0011111100110001

PC5–4←A1–0

3–1←(HL)

SP

3–1, SP0←0 order bits of the memory addressed by

accumulator to SP

HL to SP

3–1.

5–4 and the three high-

SKC 01011010 Skip if C = 1 Causes skipping if the carry flag is 1. C = 1

SKABT bit 011101B

1B0

Skip if Abit

= 1

Causes skipping of the bit of the accumu-

lator, which is specified by B

1-0 is 1.

Causes skipping of the bit of the memory

SKMBT bit 011001B

1B0

Skip if (HL)

bit = 1 addressed by HL, which is specified by (HL)

B1–0 is 1.

Causes skipping of the bit of the memory

SKMBF bit 011000B

1B0

Skip if (HL)

bit = 0 addressed by HL, which is specified by (HL)

B1–0 is 0.

Skip instructions

Causes skipping if the contents are the

SKAEM 01011111 Skip if A = (HL) same between the accumulator and the A = (HL)

memory addressed by HL.

SKAEI n4 001111110110I

SKI n2 00111111010000I1I0

3 I2 I

1 I0 Skip if A = n4 Skips if the accumulator is equal to n4. A = n4

Skip if INT RQF = 1 Skips if INT RQF is 1, and then sets

Then reset INT RQF INT RQF to 0.

Skip

Uncondition-

ally

A

bit = 1

bit

= 1

bit

= 0

INT RQF = 1

µ

PD7564A, 7564A(A)

31

Note Instruction Group

Page 32

32

Mne- Ope- Operation Code

Note

monic rands B1 B2 Condition

Operation

Transfers the contents of the accumulator

SIO

TAMSIO 0011111100111110

7–4←A to the four high-order bits of the shift

SIO3–0←(HL) register and the contents of the memory

addressed by HL to the four low-order bits.

Transfers the four high-order bits of the

TSIOAM 0011111100111010

SIO control instructions

A←SIO

(HL)←SIO

3–0

shift register to the accumulator and the

four low-order bits to the memory

addressed by HL.

7–4

SIO 0011111100110011 Start SIO Starts shifting.

TIMER 0011111100110010 Start Timer Starts timer operation.

Transfers the four high-order bits of

TCNTAM 0011111100111011

instructions

Timer control

IPL 01110000 A←Port (L)

7–4

(HL)←CT

3–0

the count register to the accumulator

and the four low-order bits to the

memory addressed by HL.

Loads the contents of the port specified

by the L register to the accumulator.

A←CT

Outputs the contents of the accumu-

OPL 01110010 Port/Mode reg. (L)←A lator to the port specified by the L

register or the mode register.

RPBL* 01011100 Port bit (L)←0

SPBL* 01011101 Port bit (L)←1

Input/output instructions

Resets the bits of ports 8, 10, and 11,

that are specified by the L register.

Sets the bits of ports 8, 10, and 11,

that are specified by the L register.

HALT 0011111100110110 Set Halt Mode Sets the HALT mode.

STOP 0011111100110111 Set Stop Mode Sets the STOP mode.

NOP 00000000 No operation

instructions

CPU control

Performs no operation for one

machine cycle.

Skip

µ

PD7564A, 7564A(A)

* SPBL and RPBL are bit-wise set/reset instructions. They perform output to each 4-bit port including the specified bits as well as set and reset operation

(They output the contents of the output latch to bits other than the specified bits.). Before executing these instructions, intialize the contents of the output

latch using the OPL instruction.

Note Instruction Group

Page 33

µ

PD7564A, 7564A(A)

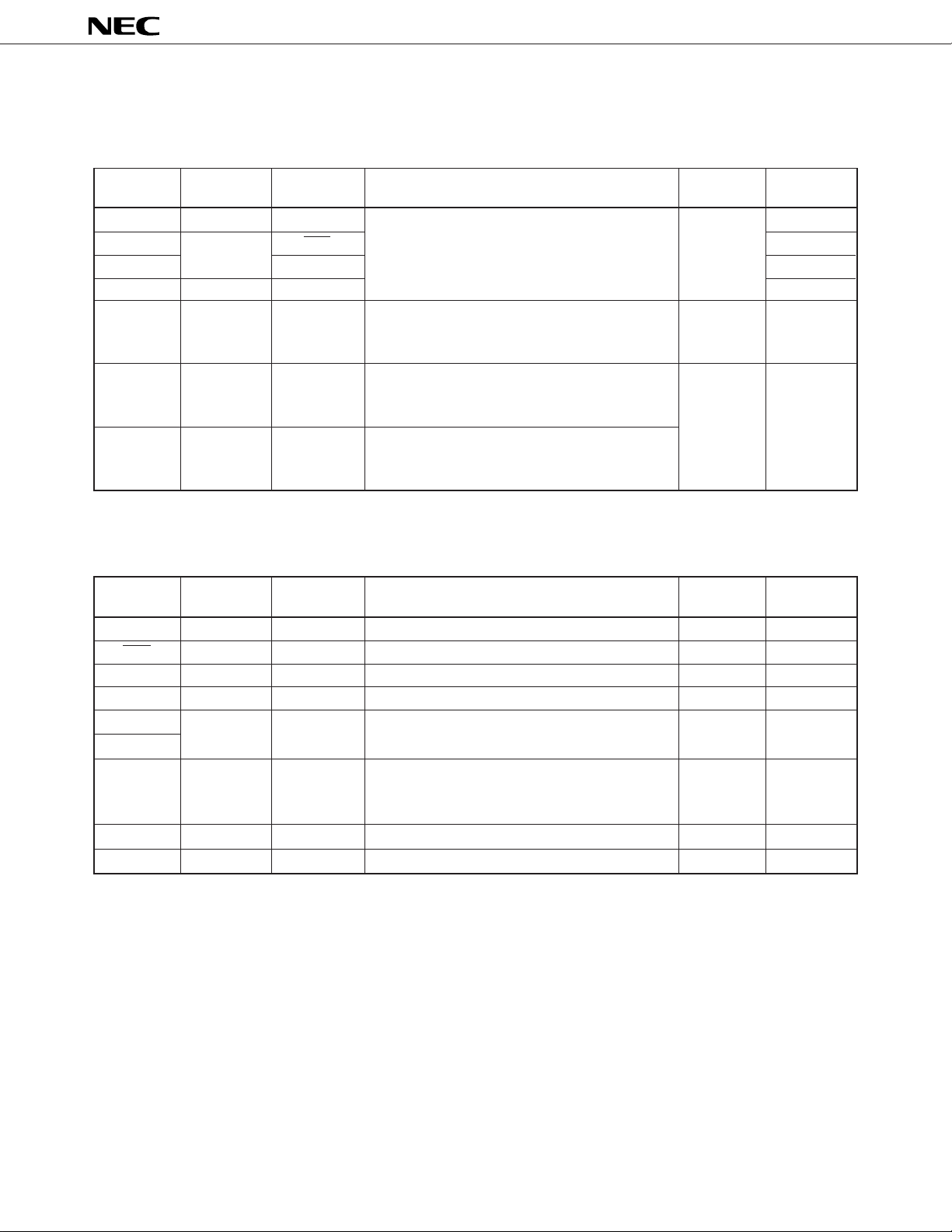

6. ELECTRICAL SPECIFICATIONS

µ

PD7564A: ABSOLUTE MAXIMUM RATINGS (Ta = 25°C)

Parameter Symbol Test Conditions Rating Unit

Supply voltage VDD –0.3 to +7.0 V

Except ports 10 and 11 –0.3 to VDD + 0.3 V

Input voltage VI

Output voltage VO

Output current high IOH

Output current low IOL

Operating temperature Topt –10 to +70 °C

Storage temperature Tstg –65 to +150 °C

Power consumption Pd Ta = 70 °C

Ports 10 and 11

Except ports 8, 10, 11 –0.3 to VDD + 0.3 V

Ports 8, 10 and 11

1 pin –5 mA

All pins in total –15 mA

1 pin Port 8 30 mA

All pins in total 100 mA

*1 –0.3 to VDD + 0.3 V

*2 –0.3 to +11 V

*1 –0.3 to VDD + 0.3 V

*2 –0.3 to +11 V

P01, P02 5 mA

Others 15 mA

Shrink DIP 480

Mini flat 250

mW

*1.CMOS input/output or N-ch open-drain output + pull-up resistor built-in input/output

2. N-ch open-drain input/output

Caution Even if one of the parameters exceeds its absolute maximum rating even momentarily, the quality of

the product may be degraded. The absolute maximum rating therefore specifies the upper or lower

limit of the value at which the product can be used without physical damages. Be sure not to exceed

or fall below this value when using the product.

★

33

Page 34

µ

PD7564A, 7564A(A)

µ

★

PD7564A(A): ABSOLUTE MAXIMUM RATINGS (Ta = 25°C)

Parameter Symbol Test Conditions Rating Unit

Supply voltage VDD –0.3 to +7.0 V

Except ports 10 and 11 –0.3 to VDD + 0.3 V

Input voltage VI

Output voltage VO

Output current high IOH

Output current low IOL

Operating temperature Topt –40 to +85 °C

Storage temperature Tstg –65 to +150 °C

Power consumption Pd Ta = 85°C

Ports 10 and 11

Except ports 8, 10, 11 –0.3 to VDD + 0.3 V

Ports 8, 10 and 11

1 pin –5 mA

All pins in total –15 mA

1 pin Port 8 30 mA

All pins in total 100 mA

*1 –0.3 to VDD + 0.3 V

*2 –0.3 to +11 V

*1 –0.3 to VDD + 0.3 V

*2 –0.3 to +11 V

P01, P02 5 mA

Others 15 mA

Shrink DIP 350

Mini flat 195

mW

*1.CMOS input/output or N-ch open-drain output + pull-up resistor built-in input/output

2. N-ch open-drain input/output

Caution Even if one of the parameters exceeds its absolute maximum rating even momentarily, the quality of

the product may be degraded. The absolute maximum rating therefore specifies the upper or lower

limit of the value at which the product can be used without physical damages. Be sure not to exceed

or fall below this value when using the product.

CAPACITY (T

Parameter Symbol Test Conditions MN. TYP. MAX. Unit

Input capacity CIN P00, P03 15 pF

Output capacity COUT Port 8 35 pF

I/O capacity CIO

a = 25 °C, VDD = 0 V)

f = 1 MHz

Unmeasured pins

returned to 0 V.

P01, P02 15 pF

Ports 10 and 11 35 pF

34

Page 35

µ

PD7564A, 7564A(A)

RESONATOR CHARACTERISTICS

Resonator External Circuit Parameter Test Conditions MIN. TYP. MAX. Unit

CL1 CL2

Ceramic

resonator *

µ

PD7564A : Ta = –10 to +70°C, VDD = 2.7 to 6.0 V

µ

PD7564A(A) : Ta = –40 to +85°C, VDD = 2.7 to 6.0 V

VDD = 4.5 to 6.0 V 290 700 710 kHz

R2

C2C1

Oscillator

frequency

(fCC)

Oscillation

stabilization

time (tOS)

VDD = 4.0 to 6.0 V 290 500 510 kHz

VDD = 3.5 to 6.0 V 290 400 410 kHz

VDD = 2.7 to 6.0 V 290 300 310 kHz

After reaching MIN.

of operating voltage

range

20 ms

* The following ceramic resonators are recommended.

Manufacturer Product Name Range [V]

CSB300D 330 330 6.8 2.7 6.0

Murata Mfg.

Kyocera

Toko CRK-500 100 100 12 4.0 6.0

CSB400P 220 220 6.8 3.5 6.0

CSB500E 100 100 6.8 4.0 6.0

CSB700A 100 100 6.8 4.5 6.0

KBR-300B 470 470 0 2.7 6.0

KBR-400B 330 330 0 3.5 6.0

KBR-500B 220 220 0 4.0 6.0

KBR-680B 220 220 0 4.5 6.0

CRK-400 120 120 12 3.5 6.0

CRK-680 82 82 12 4.5 6.0

Recommended Constant

C1 [pF] C2 [pF] R2 [kΩ] MIN. MAX.

Operating Voltage

Caution 1. Install the oscillation circuit as close to CL1 and CL2 pins as possible.

2. Do not allow other signal lines to pass through the area enclosed by dotted lines.

35

Page 36

µ

PD7564A, 7564A(A)

DC CHARACTERISTICS

Parameter Symbol Test Conditions MIN. TYP. MAX. Unit

Input voltage high

Input voltage low VIL 0 0.3VDD V

Output voltage high VOH

Output voltage low VOL Ports 10 and 11 VDD = 4.5 to 6.0 V

Input leak current high

Input leak current low ILIL VIN = 0 V –3

Output leak current high

Output leak current low ILOL VOUT = 0 V –3

Input pin built-in resistor

(pull-up/down resistor)

Output pin built-in resistor

(pull-up resistor)

Supply current *2

µ

PD7564A : Ta = –10 to +70°C, VDD = 2.7 to 6.0 V

µ

PD7564A(A) : Ta = –40 to +85°C, VDD = 2.7 to 6.0 V

VIH1 Except ports 10 and 11 0.7VDD VDD V

VIH2 Ports 10 and 11 *1 0.7VDD 9V

VDD = 4.5 to 6.0 V

IOH = –1 mA

IOH = –100 µAVDD – 1.0 V

VDD = 4.5 to 6.0 V

P01, P02

Port 8 IOL = 15 mA

ILIH1 VIN = VDD 3

ILIH2 VIN = 9 V, ports 10 and 11 *1 10

ILOH1 VOUT = VDD 3

ILOH2 VOUT = 9 V, ports 8, 10, and 11 *1 10

Port 0, RESET 23.5 47 70.5 KΩ

Ports 10 and 11 7.5 15 22.5 KΩ

IDD1 Operating mode

IDD2 HALT mode

IDD3 STOP mode

IOL = 1.6 mA

IOL = 400 µA 0.5 V

VDD = 4.5 to 6.0 V

IOL = 1.6 mA

IOL = 10 mA

IOL = 400 µA 0.5 V

VDD = 4.5 to 6.0 V

IOL = 600 µA 0.5 V

VDD = 5 V ± 10 %

fCC = 700 kHz

VDD = 3 V ± 10 %

fCC = 300 kHz

VDD = 5 V ± 10 %

fCC = 700 kHz

VDD = 3 V ± 10 %

fCC = 300 kHz

VDD = 5 V ± 10 % 0.1 10

VDD = 3 V ± 10 % 0.1 5

VDD – 2.0 V

0.4 V

0.4 V

2.0 V

2.0 V

650 2200

120 360

450 1500

65 200

µ

A

µ

A

µ

A

µ

A

µ

A

µ

A

µ

A

µ

A

µ

A

µ

A

µ

A

µ

A

*1.For N-ch open-drain input/output selection

2. The current flowing in built-in pull-up and pull-down resistors is excluded.

36

Page 37

µ

PD7564A, 7564A(A)

AC CHARACTERISTICS

Parameter Symbol Test Conditions MIN. TYP. MAX. Unit

Internal clock cycle time tCY *

P00 event input frequency fPO Duty = 50%

P00 input rise/fall time tPOR, tPOF 0.2

P00 input high/low level

width

SCK cycle time tKCY

SCK high/low level width tKH, tKL

SI setup time (to SCK↑)tSIK 100 ns

SI hold time (from SCK↑)tKSI 100 ns

SCK↓→ SO output delay time tKSO

INT0 high/low level width tIOH, tIOL 10

RESET high/low level

width

µ

PD7564A : Ta = –10 to +70°C, VDD = 2.7 to 6.0 V

µ

PD7564A(A) : Ta = –40 to +85°C, VDD = 2.7 to 6.0 V

VDD = 4.5 to 6.0 V 2.8 6.9

VDD = 4.5 to 6.0 V 0 710 kHz

tPOH, tPOL

tRSH, tRSL 10

VDD = 4.5 to 6.0 V 0.7

Input

Output 2.5

Input 5.0

Output 5.7

Input

Output 1.25

Input 2.5

Output 2.85

VDD = 4.5 to 6.0 V 850 ns

VDD = 4.5 to 6.0 V

VDD = 4.5 to 6.0 V

6.4 6.9

0 350 kHz

1.45

2.0

1.0

1200 ns

µ

s

µ

s

µ

s

µ

s

µ

s

µ

s

µ

s

µ

s

µ

s

µ

s

µ

s

µ

s

µ

s

µ

s

µ

s

* tCY = 2/fCC (See the characteristics curves for the power supply conditions specified above.)

AC Timing Test Point (Except CL1 Input)

0.7 V

0.3 V

DD

DD

Test

Points

0.7 V

0.3 V

DD

DD

37

Page 38

µ

PD7564A, 7564A(A)

CHARACTERISTICS OF DATA MEMORY DATA RETENTION AT LOW SUPPLY VOLTAGE IN STOP MODE

µ

PD7564A : Ta = –10 to +70°C

µ

PD7564A(A) : Ta = –40 to +85°C

Parameter Symbol Test Conditions MIN. TYP. MAX. Unit

Data retention supply voltage VDDDR 2.0 6.0 V

Data retention supply current IDDDR VDDDR = 2.0 V 0.1 5

RESET setup time tSRS 0

Oscillation stabilization time tOS After VDD reaches 4.5 V 20 ms

µ

A

µ

s

Data Retention Timing

HALT

STOP Mode

mode

Operating Mode

V

DD

STOP Instruction

Execution

RESET

Data Retention Mode

V

DDDR

t

SRS

OS

t

38

Page 39

P00 Input Timing

P00 Input

µ

PD7564A, 7564A(A)

1/f

P0

t

POL

t

POH

Serial Transfer Timing

SCK

SI

SO

POR

t

tKL tKH

tSIK tKSI

Input Data

tKSO

tKCY

Output Data

t

POF

Test Input Timing

RESET Input Timing

INT0

RESET

t

IOL

t

RSL

t

IOH

t

RSH

39

Page 40

7. CHARACTERISTIC CURVES

pply

µ

PD7564A, 7564A(A)

fCC (Ceramic Oscillation) vs. V

µ

PD7564A

PD7564A(A)

µ

[kHz]P00 Event Input Frequency f

CC

1000

CL1 CL2

R2

C2C1

500

100

System Clock Oscillator Frequency f

0123456

Supply Voltage VDD [V]

PO

vs. VDD Operating Guarantee Range

f

µ

PD7564A

PD7564A(A)

µ

DD

: Ta = –10 to +70˚C

: T

= –40 to +85˚C

a

Operating

Guarantee

Range

: T

= –10 to +70˚C

a

= –40 to +85˚C

: T

a

[kHz]

PO

1000

t1t

2

CL1

: fX =

1

2t

2

1

2t

1

1>t2

t

t1<t2 : fX =

500

Operating

Guarantee

Range

100

10

0123456

Voltage VDD [V]

Su

40

Page 41

IDD vs. VDD Characteristic Example

(Reference Value)

a

(T

= 25°C)

µ

PD7564A, 7564A(A)

330

µ

1000

[A]

DD

pF

500

fCC = 300 kHz

Operating mode

100

Supply Current I

50

10

0123456

I

OL

30

25

[mA]

OL

20

6.8 kΩ

330

pF

CL1 CL2

100

pF

6.8 kΩ

f

100

700 kHz

pF

CC

=

CL1 CL2

CSB300D CSB700A

HALT mode

DD

Supply Voltage V

[V]

vs. VOL Characteristic Example (Port 8)

(Reference Value)

(Ta = 25°C)

V

DD

= 5 V

Operating mode

HALT mode

15

DD

= 3 V

V

10

Output Current Low I

5

0

0123456

Output Voltage Low VOL [V]

Caution The absolute maximum rating is 30

mA per pin.

41

Page 42

I

OL

vs. VOL Characteristic Example (Port 10, 11)

(Reference Value)

30

25

[mA]

OL

20

V

DD

= 5 V

15

(Ta = 25°C)

µ

PD7564A, 7564A(A)

10

Output Current Low I

5

0

0123456

V

DD

= 3 V

Output Voltage Low VOL [V]

OH

vs. VOH Characteristic Example

I

(Reference Value)

–5

[mA]

OH

–4

–3

–2

DD

= 3 V

V

–1

Output Current High I

0

0123456

VDD – VOH [V]

(Ta = 25°C)

DD

= 5 V

V

Caution The absolute maximum rating is 15 mA per

pin.

Caution The absolute maximum rating is -5 mA

per pin.

42

Page 43

8.µPD7564A APPLIED CIRCUITS

(1) Remote control reception + key entry + LED display

µ

PD7564A, 7564A(A)

Remote

Control

Signal

Master

Microcomputer

SCK

SO

SI

µ

PD75008

PD75108

µ

etc.

Amplifier

Circuit

PC2800AHA(MS) etc.

µ

PD7564A

µ

SCK

SI

SO

P113

RES

INT0

P110

P111

CMOS Output

(Chip

Selector

Transfer

Request)

P80

P81

P82

P112

Open-Drain Output

P100

P101

P102

P103

On-Chip Pull-Up

Resistor Input

LED 8

Driver

PA80C

µ

CL1 CL2

Key Input 4 × 4

43

Page 44

(2) Remote control transmission

PD7564A

µ

P80

(CMOS Output)

RESET

On-Chip Pull-Down

Resistor

On-Chip

Pull-Up

Resistor

Input

P00

P01

P02

P03

P100

µ

PD7564A, 7564A(A)

2SA733 MAX. 40 Keys

N-ch

Open-Drain

Output

CL1 CL2

P101

P102

P103

P82

P110

P111

P112

P113

P81

Ceramic Resonator

2SA952

304 kHz

Infrared Light

Emitting Diode

SE307-C

44

Page 45

9. PACKAGE INFORMATION

DRAWINGS OF MASS-PRODUCTION PRODUCT PACKAGES

µ

PD7564A, 7564A(A)

Caution Dimensions of ES products are different from those of mass-production products. Refer to DRAWINGS

OF ES PRODUCT PACKAGES (1/2).

★

45

Page 46

DRAWINGS OF MASS-PRODUCTION PRODUCT PACKAGES (2/2)

20 PIN PLASTIC SOP (300 mil)

1120

110

µ

PD7564A, 7564A(A)

detail of lead end

P

A

G

F

E

C

D

NOTE

Each lead centerline is located within 0.12 mm (0.005 inch) of

its true position (T.P.) at maximum material condition.

N

M

M

H

I

J

K

B

L

ITEM MILLIMETERS INCHES

A

13.00 MAX.

B

0.78 MAX.

C

1.27 (T.P.)

D 0.40 0.016

E

F

G

H

I

J

K 0.20

L 0.6±0.2 0.024

M

N

P3° 3°

+0.10

–0.05

0.1±0.1

1.8 MAX.

1.55

7.7±0.3

5.6

1.1

+0.10

–0.05

0.12

0.10

+7°

–3°

0.512 MAX.

0.031 MAX.

0.050 (T.P.)

+0.004

–0.003

0.004±0.004

0.071 MAX.

0.061

0.303±0.012

0.220

0.043

+0.004

0.008

–0.002

+0.008

–0.009

0.005

0.004

+7°

–3°

P20GM-50-300B, C-4

★

Caution Dimensions of ES products are different from those of mass-production products. Refer to DRAWINGS

OF ES PRODUCT PACKAGES (2/2).

46

Page 47

DRAWINGS OF ES PRODUCT PACKAGES (1/2)

20-Pin Shrink DIP for ES (Reference) (Unit: mm)

µ

PD7564A, 7564A(A)

47

Page 48

DRAWINGS OF ES PRODUCT PACKAGES (2/2)

20-Pin Ceramic SOP for ES (Reference) (Unit: mm)

µ

PD7564A, 7564A(A)

48

Page 49

µ

PD7564A, 7564A(A)

10. RECOMMENDED PACKAGING PATTERN OF SOP (REFERENCE) (UNIT: mm)

7.62

1.270.76

0.51

1.27

• This recommended pattern conforms to the General Rules for Integrated Citrcuit Outer Shape (IC-74-2) specified

by the Electronic Industries Association of Japan (EIAJ).

• The above pattern dimensions are applicable to all the products designated as EIAJ flat DIP (mini flat) of “Form

A 300 mil type”.

• If there is any possibility of causing a solder bridge, adjust the width (0.76) of each pad while maintaining the

same length (1.27).

49

Page 50

★

11. RECOMMENDED SOLDERING CONDITIONS

Solder µPD7564A on the following recommended conditions.

For details of recommended soldering conditions, refer to the information document “Surface Mount Tech-

nology Manual” (IE-1207).

For details on the soldering method and soldering conditions other than the recommended conditions, call the

NEC salesman.

Table 11-1 Surface Mounting Type Conditions

µ

PD7564AG-×××: 20-pin plastic SOP (300 mil)

µ

PD7564AG(A)-×××: 20-pin plastic SOP (300 mil)

µ

PD7564A, 7564A(A)

Soldering Method Soldering Conditions

Infrared reflow IR30-00-1

VPS VP15-00-1

Wave soldering Number of times: Once, Preheat temperature: 120˚C max. WS60-00-1

Pin part heating Pin temperature: 300°C or below, Duration: 3 sec. max. (per device side) ––

Package peak temperature: 230°C, Duration: 30 sec. max. (at 210°C or above),

Number of times: Once

Package peak temperature: 215°C, Duration: 40 sec. max. (at 200°C or above),

Number of times: Once

Solder both temperature: 260˚C or below, Duration: 10 sec. max.,

(Package surface temperature)

Recommended

Condition Symbol

Caution Use of more than one soldering method should be avoided (except in the case of pin part heating).

Table 11-2 Insertion Type Soldering Conditions

µ

PD7564ACS-×××: 20-pin plastic shrink DIP (300 mil)

µ

PD7564ACS(A)-×××: 20-pin plastic shrink SOP (300 mil)

Soldering Method Soldering Conditions

Wave soldering

(Pin only)

Pin part heating Pin temperature: 300°C or below, Duration: 3 sec. max. (per pin)

Solder bath temperatures: 260°C or below, Duration: 10 sec. max.

Caution Ensure that the application of wave soldering is limited to the pins and no solder touches the main unit

directly.

50

Page 51

µ

PD7564A, 7564A(A)

★APPENDIX A. COMPARISON BETWEEN SUB-SERIES PRODUCT FUNCTIONS

Product Name

Item

Instruction cycle/system

clock (5 V)

Instruction set 47 types (SET B)

ROM 1024 × 8

RAM 64 × 4

Total number 16 15

Port 0 P00 to P03

I/O Port 8 P80 to P82, P83 (CL2) P80 to P82

port Withstand voltage 12 V 9 V 12 V 9 V

Ports 10 and 11 P100 to P103, P110 to P113

Withstand voltage 12 V 9 V 12 V 9 V

Timer/event counter 8 bits

Serial interface 8 bits

Power voltage range 2.5 to 6.0 V 4.5 to 6.0 V 2.0 to 6.0 V 2.7 to 6.0 V 2.7 to 6.0 V 4.5 to 6.0 V 2.7 to 6.0 V 2.7 to 6.0 V

Package

Outside 2.86

Ceramic –––– 2.86

µ

PD7554µPD75P54µPD7554AµPD7554A(A)µPD7564µPD75P64µPD7564AµPD7564A(A)

RC 4 µs/500 kHz ––––

µ

s/700 kHz ––––

µ

s/700 kHz

20-pin plastic shrink DIP

20-pin plastic SOP

51

Page 52

µ

PD7564A, 7564A(A)

APPENDIX B. DEVELOPMENT TOOLS

The following development tools are available for developing systems that use µPD7564A.

Language Processor

This program is used to convert the program written with mnemonic codes to the

program written with object codes so that the program can be executed by the

microcomputer.