Page 1

User’s Manual

µ

PD754144, 754244

4-Bit Single-Chip Microcontrollers

µ

PD754144

µ

PD754244

Document No. U10676EJ3V0UM00 (3rd edition)

Date Published November 2002 N CP(K)

Printed in Japan

1997

Page 2

[MEMO]

2 User’s Manual U10676EJ3V0UM

Page 3

NOTES FOR CMOS DEVICES

1 PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and

ultimately degrade the device operation. Steps must be taken to stop generation of static electricity

as much as possible, and quickly dissipate it once, when it has occurred. Environmental control

must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using

insulators that easily build static electricity. Semiconductor devices must be stored and transported

in an anti-static container, static shielding bag or conductive material. All test and measurement

tools including work bench and floor should be grounded. The operator should be grounded using

wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need

to be taken for PW boards with semiconductor devices on it.

2 HANDLING OF UNUSED INPUT PINS FOR CMOS

Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided

to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence

causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels

of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused

pin should be connected to V

DD

or GND with a resistor, if it is considered to have a possibility of

being an output pin. All handling related to the unused pins must be judged device by device and

related specifications governing the devices.

3 STATUS BEFORE INITIALIZATION OF MOS DEVICES

Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS

does not define the initial operation status of the device. Immediately after the power source is

turned ON, the devices with reset function have not yet been initialized. Hence, power-on does

not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the

reset signal is received. Reset operation must be executed immediately after power-on for devices

having reset function.

This product cannot be used for an IC card (SMART CARD).

EEPROM is a trademark of NEC Electronics Corporation.

MS-DOS is either a registered trademark or a trademark of Microsoft Corporation in the United

States and/or other countries.

IBM DOS, PC/AT, and PC DOS are trademarks of International Business Machines Corporation.

User’s Manual U10676EJ3V0UM

3

Page 4

These commodities, technology or software, must be exported in accordance

with the export administration regulations of the exporting country.

Diversion contrary to the law of that country is prohibited.

•

The information in this document is current as of July, 2002. The information is subject to change

without notice. For actual design-in, refer to the latest publications of NEC Electronics data sheets or

data books, etc., for the most up-to-date specifications of NEC Electronics products. Not all

products and/or types are available in every country. Please check with NEC Electronics sales

representative for availability and additional information.

No part of this document may be copied or reproduced in any form or by any means without prior

•

written consent of NEC Electronics. NEC Electronics assumes no responsibility for any errors that may

appear in this document.

•

NEC Electronics does not assume any liability for infringement of patents, copyrights or other intellectual

property rights of third parties by or arising from the use of NEC Electronics products listed in this document

or any other liability arising from the use of such NEC Electronics products. No license, express, implied or

otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Electronics or

others.

•

Descriptions of circuits, software and other related information in this document are provided for illustrative

purposes in semiconductor product operation and application examples. The incorporation of these

circuits, software and information in the design of customer's equipment shall be done under the full

responsibility of customer. NEC Electronics assumes no responsibility for any losses incurred by customers

or third parties arising from the use of these circuits, software and information.

•

While NEC Electronics endeavors to enhance the quality, reliability and safety of NEC Electronics products,

customers agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To

minimize risks of damage to property or injury (including death) to persons arising from defects in NEC

Electronics products, customers must incorporate sufficient safety measures in their design, such as

redundancy, fire-containment and anti-failure features.

•

NEC Electronics products are classified into the following three quality grades: "Standard", "Special" and

"Specific".

The "Specific" quality grade applies only to NEC Electronics products developed based on a customerdesignated "quality assurance program" for a specific application. The recommended applications of NEC

Electronics product depend on its quality grade, as indicated below. Customers must check the quality grade of

each NEC Electronics product before using it in a particular application.

"Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio

and visual equipment, home electronic appliances, machine tools, personal electronic equipment

and industrial robots.

"Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster

systems, anti-crime systems, safety equipment and medical equipment (not specifically designed

for life support).

"Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life

support systems and medical equipment for life support, etc.

The quality grade of NEC Electronics products is "Standard" unless otherwise expressly specified in NEC

Electronics data sheets or data books, etc. If customers wish to use NEC Electronics products in applications

not intended by NEC Electronics, they must contact NEC Electronics sales representative in advance to

determine NEC Electronics's willingness to support a given application.

(Note)

(1) "NEC Electronics" as used in this statement means NEC Electronics Corporation and also includes its

majority-owned subsidiaries.

(2) "NEC Electronics products" means any product developed or manufactured by or for NEC Electronics

(as defined above).

M8E 02. 11

4 User’s Manual U10676EJ3V0UM

Page 5

Regional Information

Some information contained in this document may vary from country to country. Before using any NEC

Electronics product in your application, pIease contact the NEC Electronics office in your country to

obtain a list of authorized representatives and distributors. They will verify:

•

Device availability

•

Ordering information

•

Product release schedule

•

Availability of related technical literature

•

Development environment specifications (for example, specifications for third-party tools and

components, host computers, power plugs, AC supply voltages, and so forth)

•

Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary

from country to country.

NEC Electronics America, Inc. (U.S.)

Santa Clara, California

Tel: 408-588-6000

800-366-9782

Fax: 408-588-6130

800-729-9288

NEC Electronics (Europe) GmbH

Duesseldorf, Germany

Tel: 0211-65 03 01

Fax: 0211-65 03 327

• Sucursal en España

Madrid, Spain

Tel: 091-504 27 87

Fax: 091-504 28 60

• Succursale Française

Vélizy-Villacoublay, France

Tel: 01-30-67 58 00

Fax: 01-30-67 58 99

• Filiale Italiana

Milano, Italy

Tel: 02-66 75 41

Fax: 02-66 75 42 99

• Branch The Netherlands

Eindhoven, The Netherlands

Tel: 040-244 58 45

Fax: 040-244 45 80

• Tyskland Filial

Taeby, Sweden

Tel: 08-63 80 820

Fax: 08-63 80 388

• United Kingdom Branch

Milton Keynes, UK

Tel: 01908-691-133

Fax: 01908-670-290

NEC Electronics Hong Kong Ltd.

Hong Kong

Tel: 2886-9318

Fax: 2886-9022/9044

NEC Electronics Hong Kong Ltd.

Seoul Branch

Seoul, Korea

Tel: 02-528-0303

Fax: 02-528-4411

NEC Electronics Shanghai, Ltd.

Shanghai, P.R. China

Tel: 021-6841-1138

Fax: 021-6841-1137

NEC Electronics Taiwan Ltd.

Taipei, Taiwan

Tel: 02-2719-2377

Fax: 02-2719-5951

NEC Electronics Singapore Pte. Ltd.

Novena Square, Singapore

Tel: 6253-8311

Fax: 6250-3583

User’s Manual U10676EJ3V0UM

J02.11

5

Page 6

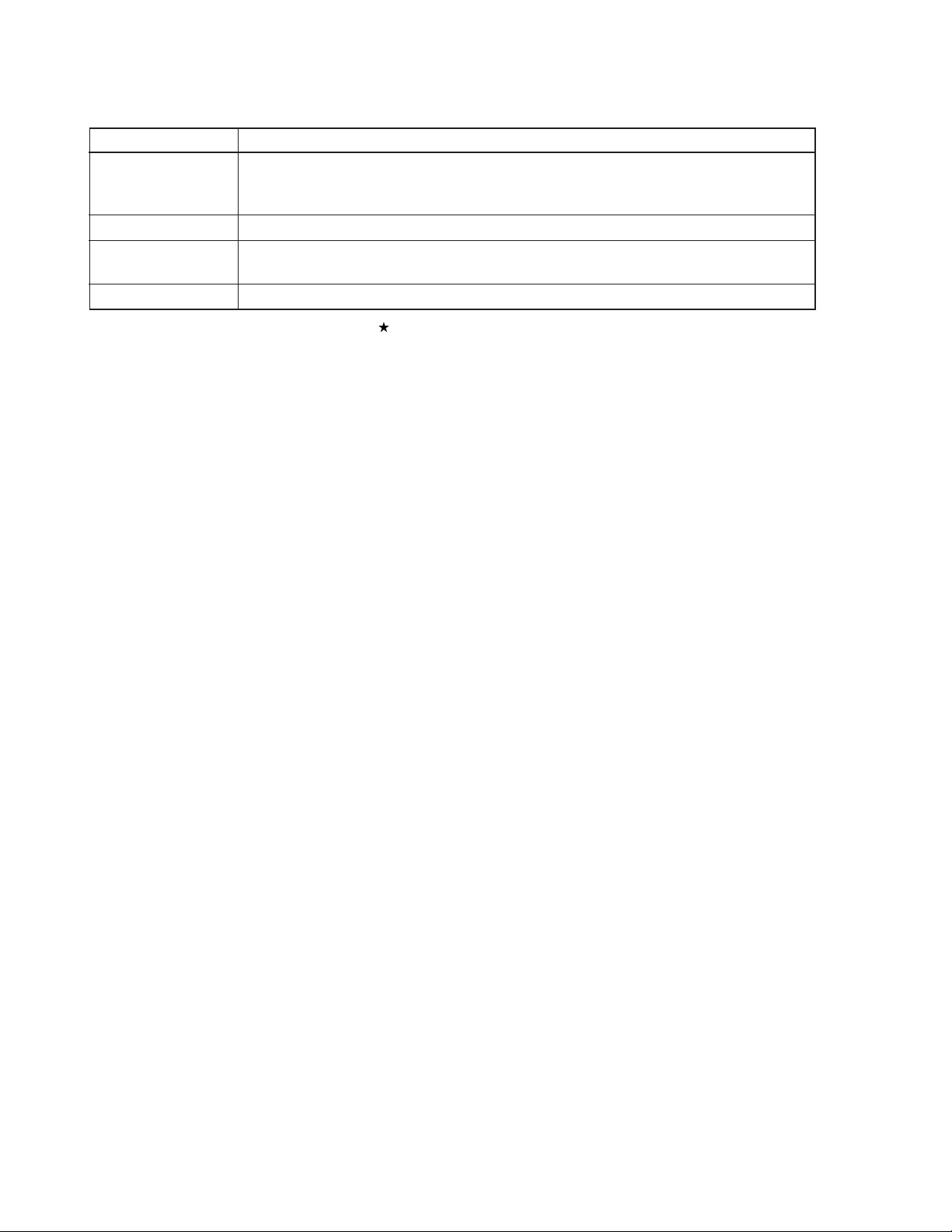

Major Revisions in This Edition

Pages Description

p.210 Correction of description in figure in 7.9 Application of Interrupt (6) Executing pending

interrupt - interrupt occurs during interrupt service (INTBT has higher priority and INTT0

and INTT2 have lower priority)

p.253 Correction of instruction code of “BR BCDE” in 11.3 Opcode of Each Instruction

p.296 Deletion of flash-related products in configuration diagram in APPENDIX A DEVELOPMENT

TOOLS

µ

p.297 in 2nd edition Deletion of APPENDIX A LIST OF FUNCTIONS OF

The mark shows major revised points.

PD754144, 754244, AND 75F4264

6 User’s Manual U10676EJ3V0UM

Page 7

INTRODUCTION

Readers This manual is intended for user engineers who wish to understand the functions of

the µPD754144 and 754244 and design application systems using these microcontrollers.

Purpose This manual is intended to give users an understanding of the hardware functions of

µ

PD754144 and 754244 described in the Organization below.

the

Organization This manual contains the following information.

• General

• Pin Functions

• Features of Architecture and Memory Map

• Internal CPU Functions

• EEPROM

• Peripheral Hardware Functions

• Interrupt Functions and Test Functions

• Standby Functions

• Reset Functions

• Mask option

• Instruction Set

How to Read This Manual It is assumed that the readers of this manual have general knowledge of electrical

engineering, logic circuits, and microcontrollers.

µ

• To users who use this manual as a manual for

µ

→ Unless otherwise specified, the

treated as the representative model in this manual. Check the functional

differences between the µPD754144 and µPD754244 by referring to 1.3

µ

Differences Between

µ

PD754144 and fX as fCC.

• To check the functions of an instruction whose mnemonic is known,

→ Refer to APPENDIX C INSTRUCTION INDEX.

• To check the functions of a specific internal circuit,

→ Refer to APPENDIX D HARDWARE INDEX.

• To understand the overall functions of the

→ Read this manual in the order of the CONTENTS.

Conventions Data significance: Higher digits on the left and lower digits on the right

Active low representations: ××× (overscore over pin and signal name)

Note: Footnote for item marked with Note in the text.

Caution: Information requiring particular attention

Remark: Supplementary information

Numerical representations: Binary ... ×××× or ××××B

PD754144 and 754244, and take the µPD754244 as

Decimal ... ××××

Hexadecimal ... ××××H

PD754244 (crystal/ceramic oscillation, fX) is

PD754144 (RC oscillation, fCC)

µ

PD754144 and 754244,

User’s Manual U10676EJ3V0UM

7

Page 8

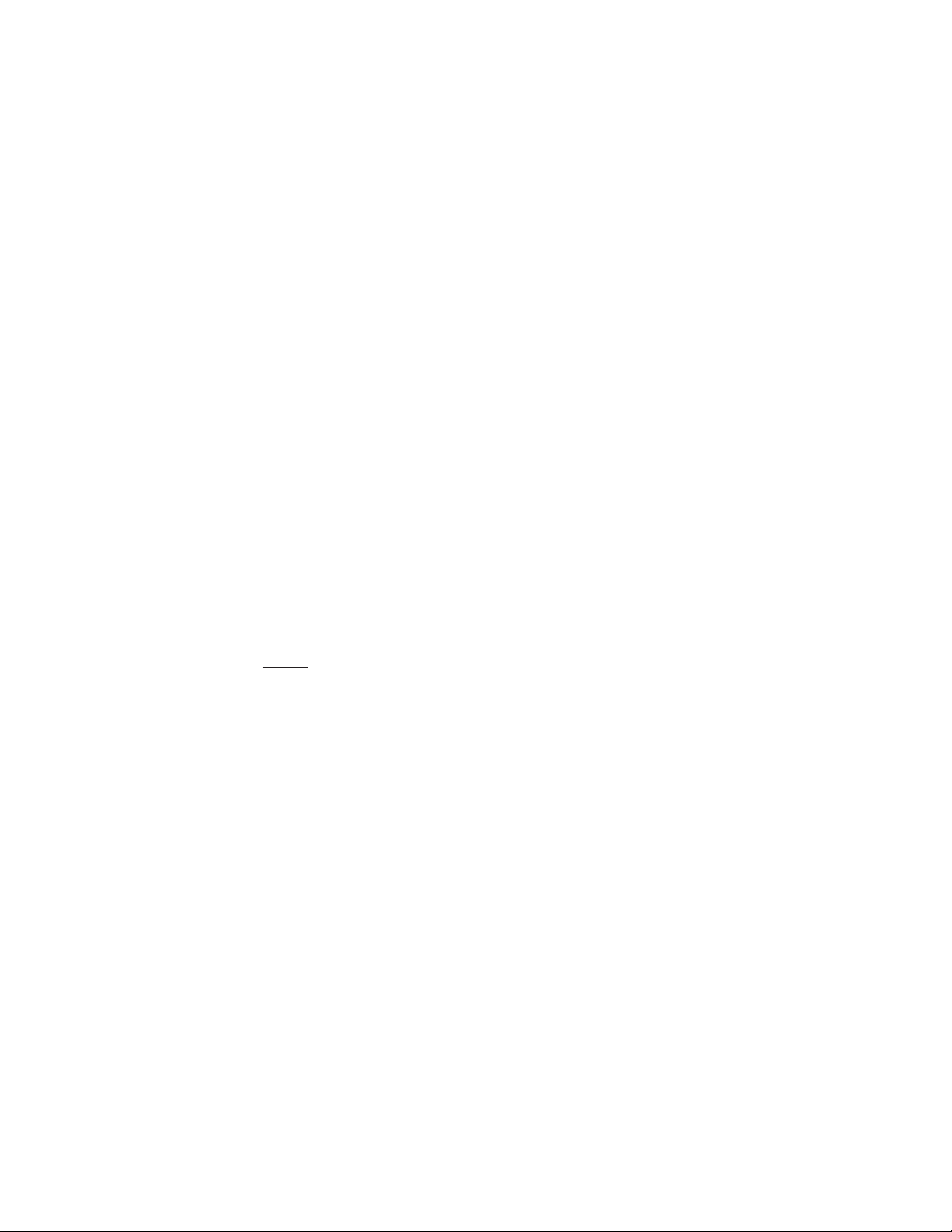

Related Documents The related documents indicated in this publication may include preliminary versions.

However, preliminary versions are not marked as such.

Documents related to devices

Document Name Document No.

µ

PD754144, 754244 Data Sheet U10040E

µ

PD754144, 754244 User’s Manual This manual

75XL Series Selection Guide U10453E

Documents related to development tools (software) (user’s manuals)

Document Name Document No.

RA75X Assembler Package Operation U12622E

Language U12385E

Structured Assembler Preprocessor U12598E

Documents related to development tools (hardware) (user’s manuals)

Document Name Document No.

IE-75000-R/IE-75001-R In-Circuit Emulator EEU-1455

IE-75300-R-EM Emulation Board U11354E

EP-754144GS-R Emulation Probe U10695E

Other documents

Document Name Document No.

SEMICONDUCTOR SELECTION GUIDE - Products & Packages - X13769E

Semiconductor Device Mounting Technology Manual C10535E

Quality Grades on NEC Semiconductor Devices C11531E

NEC Semiconductor Device Reliability/Quality Control System C10983E

Guide to Prevent Damage for Semiconductor Devices by Electrostatic Discharge (ESD) C11892E

Caution The related documents listed above are subject to change without notice. Be sure to use the latest

version of each document for designing.

8 User’s Manual U10676EJ3V0UM

Page 9

TABLE OF CONTENTS

CHAPTER 1 GENERAL ..................................................................................................................... 17

1.1 Functional Outline ............................................................................................................. 18

1.2 Ordering Information ......................................................................................................... 19

1.3 Differences Between Series Products ............................................................................ 19

1.4 Block Diagram .................................................................................................................... 20

1.5 Pin Configuration (Top View)............................................................................................ 21

CHAPTER 2 PIN FUNCTIONS .......................................................................................................... 24

2.1 Pin Functions of µPD754244 ............................................................................................ 24

2.2 Description of Pin Functions ........................................................................................... 26

2.2.1 P30 to P33 (Port 3), P60 to P63 (Port 6), P80 (Port 8) ....................................................... 26

2.2.2 P70 to P73 (Port 7) ................................................................................................................ 26

2.2.3 PTO0 to PTO2 ....................................................................................................................... 26

2.2.4 INT0 ........................................................................................................................................ 27

2.2.5 KR4 to KR7 ............................................................................................................................ 27

2.2.6 KRREN ................................................................................................................................... 27

2.2.7 TH00 and TH01 ..................................................................................................................... 27

2.2.8 AV

2.2.9 CL1 and CL2 (µPD754144 only) ........................................................................................... 28

2.2.10 X1 and X2 (µPD754244 only) ............................................................................................... 28

2.2.11 RESET.................................................................................................................................... 28

2.2.12 IC ............................................................................................................................................ 29

2.2.13 V

2.2.14 V

REF ...................................................................................................................................... 28

DD .......................................................................................................................................... 29

SS .......................................................................................................................................... 29

2.3 Pin I/O Circuits ................................................................................................................... 30

2.4 Processing of Unused Pins .............................................................................................. 31

CHAPTER 3 FEATURES OF ARCHITECTURE AND MEMORY MAP ........................................... 32

3.1 Bank Configuration of Data Memory and Addressing Modes ..................................... 32

3.1.1 Bank configuration of data memory ...................................................................................... 32

3.1.2 Addressing mode of data memory ........................................................................................ 34

3.2 Bank Configuration of General-Purpose Registers ...................................................... 45

3.3 Memory-Mapped I/O ........................................................................................................... 50

CHAPTER 4 INTERNAL CPU FUNCTION ....................................................................................... 60

4.1 Function to Select MkI and MkII Modes.......................................................................... 60

4.1.1 Difference between MkI and MkII modes ............................................................................. 60

4.1.2 Setting stack bank select register (SBS) .............................................................................. 61

4.2 Program Counter (PC) ....................................................................................................... 62

4.3 Program Memory (ROM).................................................................................................... 63

4.4 Data Memory (RAM) ........................................................................................................... 65

4.4.1 Configuration of data memory ............................................................................................... 65

4.4.2 Specifying bank of data memory .......................................................................................... 66

4.5 General-Purpose Registers .............................................................................................. 69

User’s Manual U10676EJ3V0UM

9

Page 10

4.6 Accumulator........................................................................................................................ 70

4.7 Stack Pointer (SP) and Stack Bank Select Register (SBS) .......................................... 70

4.8 Program Status Word (PSW)............................................................................................. 74

4.9 Bank Select Register (BS) ................................................................................................ 78

CHAPTER 5 EEPROM ....................................................................................................................... 80

5.1 EEPROM Configuration ..................................................................................................... 80

5.2 EEPROM Features.............................................................................................................. 80

5.3 EEPROM Write Control Register (EWC).......................................................................... 81

5.4 Interrupt Related to EEPROM Control ............................................................................ 82

5.5 EEPROM Manipulation Method ........................................................................................ 83

5.5.1 EEPROM manipulation instructions ...................................................................................... 83

5.5.2 Read manipulation ................................................................................................................. 84

5.5.3 Write manipulation ................................................................................................................. 85

5.6 Cautions on EEPROM Writing .......................................................................................... 87

CHAPTER 6 PERIPHERAL HARDWARE FUNCTION..................................................................... 88

6.1 Digital I/O Ports .................................................................................................................. 88

6.1.1 Types, features, and configurations of digital I/O ports ....................................................... 89

6.1.2 Setting I/O mode .................................................................................................................... 94

6.1.3 Digital I/O port manipulation instruction ............................................................................... 96

6.1.4 Operation of digital I/O port ................................................................................................... 98

6.1.5 Connecting pull-up resistor ................................................................................................... 100

6.1.6 I/O timing of digital I/O port ................................................................................................... 101

6.2 Clock Generator ................................................................................................................. 103

6.2.1 Configuration of clock generator ........................................................................................... 103

6.2.2 Function and operation of clock generator ........................................................................... 105

6.2.3 Setting CPU clock .................................................................................................................. 112

6.3 Basic Interval Timer/Watchdog Timer ............................................................................. 114

6.3.1 Configuration of basic interval timer/watchdog timer ........................................................... 114

6.3.2 Basic interval timer mode register (BTM) ............................................................................. 115

6.3.3 Watchdog timer enable flag (WDTM).................................................................................... 117

6.3.4 Operation as basic interval timer .......................................................................................... 118

6.3.5 Operation as watchdog timer ................................................................................................ 119

6.3.6 Other functions....................................................................................................................... 121

6.4 Timer Counter ..................................................................................................................... 122

6.4.1 Configuration of timer counter............................................................................................... 122

6.4.2 Operation in 8-bit timer counter mode .................................................................................. 134

6.4.3 Operation in PWM pulse generator mode (PWM mode) ..................................................... 145

6.4.4 Operation in 16-bit timer counter mode ................................................................................ 151

6.4.5 Operation in carrier generator mode (CG mode) ................................................................. 160

6.4.6 Notes on using timer counter ................................................................................................ 173

6.5 Programmable Threshold Port (Analog Input Port) ...................................................... 180

6.5.1 Configuration and operation of programmable threshold port ............................................. 180

6.5.2 Programmable threshold port mode (PTHM) register .......................................................... 182

6.5.3 Programmable threshold port application ............................................................................. 183

6.6 Bit Sequential Buffer ......................................................................................................... 184

10 User’s Manual U10676EJ3V0UM

Page 11

CHAPTER 7 INTERRUPT AND TEST FUNCTIONS ........................................................................ 186

7.1 Configuration of Interrupt Controller .............................................................................. 186

7.2 Types of Interrupt Sources and Vector Table ................................................................. 188

7.3 Hardware Controlling Interrupt Function ....................................................................... 190

7.4 Interrupt Sequence ............................................................................................................ 197

7.5 Nesting Control of Interrupts ........................................................................................... 198

7.6 Servicing of Interrupts Sharing Vector Address ........................................................... 200

7.7 Machine Cycles Until Interrupt Servicing....................................................................... 202

7.8 Effective Usage of Interrupts ........................................................................................... 204

7.9 Application of Interrupt ..................................................................................................... 204

7.10 Test Function ...................................................................................................................... 212

7.10.1 Types of test sources............................................................................................................. 212

7.10.2 Hardware controlling test function ........................................................................................ 212

CHAPTER 8 STANDBY FUNCTION ................................................................................................. 215

8.1 Settings and Operating Statuses of Standby Mode...................................................... 216

8.2 Releasing Standby Mode .................................................................................................. 218

8.3 Operation After Release of Standby Mode..................................................................... 222

8.4 Application of Standby Mode ........................................................................................... 222

CHAPTER 9 RESET FUNCTION....................................................................................................... 227

9.1 Configuration and Operation of Reset Function ........................................................... 227

9.2 Watchdog Flag (WDF), Key Return Flag (KRF) .............................................................. 231

CHAPTER 10 MASK OPTIONS ........................................................................................................ 233

10.1 Pin Mask Options ............................................................................................................... 233

10.1.1 Mask option of P70/KR4 to P73/KR7 ................................................................................... 233

10.1.2 RESET pin mask option ........................................................................................................ 233

10.2 Oscillation Stabilization Wait Time Mask Option........................................................... 233

CHAPTER 11 INSTRUCTION SET.................................................................................................... 234

11.1 Unique Instructions ........................................................................................................... 234

11.1.1 GETI instruction ..................................................................................................................... 234

11.1.2 Bit manipulation instruction ................................................................................................... 235

11.1.3 String-effect instruction .......................................................................................................... 235

11.1.4 Base number adjustment instruction .................................................................................... 236

11.1.5 Skip instruction and number of machine cycles required for skipping ................................ 237

11.2 Instruction Set and Operation .......................................................................................... 237

11.3 Opcode of Each Instruction ............................................................................................. 248

11.4 Instruction Function and Application ............................................................................. 254

11.4.1 Transfer instructions............................................................................................................... 255

11.4.2 Table reference instructions .................................................................................................. 261

11.4.3 Bit transfer instructions .......................................................................................................... 265

11.4.4 Operation instructions ............................................................................................................ 266

11.4.5 Accumulator manipulation instructions ................................................................................. 272

11.4.6 Increment/decrement instructions ......................................................................................... 273

11.4.7 Compare instructions ............................................................................................................. 274

11.4.8 Carry flag manipulation instructions ..................................................................................... 275

11.4.9 Memory bit manipulation instructions ................................................................................... 276

User’s Manual U10676EJ3V0UM

11

Page 12

11.4.10 Branch instructions ................................................................................................................ 279

11.4.11 Subroutine/stack control instructions .................................................................................... 283

11.4.12 Interrupt control instructions.................................................................................................. 287

11.4.13 Input/output instructions ........................................................................................................ 288

11.4.14 CPU control instruction .......................................................................................................... 289

11.4.15 Special instructions ................................................................................................................ 290

APPENDIX A DEVELOPMENT TOOLS ............................................................................................ 293

APPENDIX B ORDERING MASK ROM ............................................................................................ 297

APPENDIX C INSTRUCTION INDEX ................................................................................................ 298

C.1 Instruction Index (By Function) ....................................................................................... 298

C.2 Instruction Index (Alphabetical Order) ........................................................................... 301

APPENDIX D HARDWARE INDEX ................................................................................................... 304

APPENDIX E REVISION HISTORY ................................................................................................... 306

12 User’s Manual U10676EJ3V0UM

Page 13

LIST OF FIGURES (1/3)

Figure No. Title Page

3-1 Selecting MBE = 0 Mode and MBE = 1 Mode .................................................................................. 33

3-2 Data Memory Configuration and Addressing Range for Each Addressing Mode............................ 35

3-3 Updating Address of Static RAM ....................................................................................................... 39

3-4 Example of Using Register Banks ..................................................................................................... 46

3-5 Configuration of General-Purpose Registers (4-Bit Processing) ...................................................... 48

3-6 Configuration of General-Purpose Registers (8-Bit Processing) ...................................................... 49

µ

3-7

4-1 Format of Stack Bank Select Register ............................................................................................... 61

4-2 Configuration of Program Counter ..................................................................................................... 62

4-3 Program Memory Map ........................................................................................................................ 64

4-4 Data Memory Map .............................................................................................................................. 67

4-5 Configuration of General-Purpose Register Area ............................................................................. 69

4-6 Configuration of Register Pair ............................................................................................................ 69

4-7 Accumulator ........................................................................................................................................ 70

4-8 Stack Pointer and Stack Bank Selection Register Configuration ..................................................... 71

4-9 Data Saved to Stack Memory (MkI Mode) ......................................................................................... 72

4-10 Data Restored from Stack Memory (MkI Mode) ................................................................................ 72

4-11 Data Saved to Stack Memory (MkII Mode)........................................................................................ 73

4-12 Data Restored from Stack Memory (MkII Mode) ............................................................................... 73

4-13 Configuration of Program Status Word .............................................................................................. 74

4-14 Configuration of Bank Select Register ............................................................................................... 78

PD754244 I/O Map ........................................................................................................................... 52

5-1 Format of EEPROM Write Control Register ...................................................................................... 81

5-2 EEPROM Write Control Register in EEPROM Read Manipulation .................................................. 84

5-3 EEPROM Write Control Register in EEPROM Write Manipulation................................................... 85

6-1 Data Memory Address of Digital Ports .............................................................................................. 88

6-2 P3n Configuration (n = 0 to 2) ............................................................................................................ 90

6-3 P33 Configuration ............................................................................................................................... 90

6-4 P60 Configuration ............................................................................................................................... 91

6-5 P61 Configuration ............................................................................................................................... 91

6-6 P62 Configuration ............................................................................................................................... 92

6-7 P63 Configuration ............................................................................................................................... 92

6-8 P7n Configuration (n = 0 to 3) ............................................................................................................ 93

6-9 P80 Configuration ............................................................................................................................... 93

6-10 Format of Each Port Mode Register .................................................................................................. 95

6-11 Format of Pull-up Resistor Specification Register ............................................................................ 100

6-12 I/O Timing of Digital I/O Port .............................................................................................................. 101

6-13 ON Timing of Internal Pull-up Resistor Connected via Software ..................................................... 102

6-14 Block Diagram of Clock Generator ..................................................................................................... 103

6-15 Format of Processor Clock Control Register ..................................................................................... 107

6-16 RC Oscillation External Circuit ........................................................................................................... 108

6-17 Crystal/Ceramic Oscillation External Circuit ...................................................................................... 108

User’s Manual U10676EJ3V0UM

13

Page 14

LIST OF FIGURES (2/3)

Figure No. Title Page

6-18 Example of Incorrect Resonator Connection ..................................................................................... 109

6-19 CPU Clock Switching Example .......................................................................................................... 113

6-20 Block Diagram of Basic Interval Timer/Watchdog Timer ................................................................... 114

6-21 Format of Basic Interval Timer Mode Register.................................................................................. 116

6-22 Format of Watchdog Timer Enable Flag (WDTM) ............................................................................. 117

6-23 Block Diagram of Timer Counter (Channel 0) ................................................................................... 123

6-24 Block Diagram of Timer Counter (Channel 1) ................................................................................... 124

6-25 Block Diagram of Timer Counter (Channel 2) ................................................................................... 125

6-26 Format of Timer Counter Mode Register (Channel 0) ...................................................................... 127

6-27 Format of Timer Counter Mode Register (Channel 1) ...................................................................... 128

6-28 Format of Timer Counter Mode Register (Channel 2) ...................................................................... 130

6-29 Format of Timer Counter Output Enable Flag ................................................................................... 132

6-30 Format of Timer Counter Control Register ........................................................................................ 133

6-31 Setting of Timer Counter Mode Register ........................................................................................... 135

6-32 Setting of Timer Counter Control Register ........................................................................................ 138

6-33 Setting of Timer Counter Output Enable Flag ................................................................................... 138

6-34 Configuration When Timer Counter Operates ................................................................................... 143

6-35 Count Operation Timing...................................................................................................................... 143

6-36 Setting of Timer Counter Mode Register ........................................................................................... 146

6-37 Setting of Timer Counter Control Register ........................................................................................ 147

6-38 PWM Pulse Generator Operating Configuration ............................................................................... 149

6-39 PWM Pulse Generator Operating Timing .......................................................................................... 149

6-40 Setting of Timer Counter Mode Registers ......................................................................................... 152

6-41 Setting of Timer Counter Control Register ........................................................................................ 153

6-42 Configuration When Timer Counter Operates ................................................................................... 157

6-43 Timing of Count Operation ................................................................................................................. 158

6-44 Setting of Timer Counter Mode Register (n = 1, 2)........................................................................... 161

6-45 Setting of Timer Counter Output Enable Flag ................................................................................... 162

6-46 Setting of Timer Counter Control Register ........................................................................................ 162

6-47 Configuration in Carrier Generator Mode .......................................................................................... 165

6-48 Carrier Generator Operation Timing .................................................................................................. 166

6-49 Block Diagram of Programmable Threshold Port .............................................................................. 181

6-50 Format of Programmable Threshold Port Mode (PTHM) Register ................................................... 182

6-51 Application Example of Programmable Threshold Port..................................................................... 183

6-52 Format of Bit Sequential Buffer .......................................................................................................... 184

7-1 Block Diagram of Interrupt Controller ................................................................................................ 187

7-2 Interrupt Vector Table .......................................................................................................................... 189

7-3 Interrupt Priority Select Register ........................................................................................................ 192

7-4 Configuration of INT0.......................................................................................................................... 194

7-5 I/O Timing of Noise Eliminator ........................................................................................................... 194

7-6 Format of INT0 Edge Detection Mode Register (IM0) ...................................................................... 195

7-7 Interrupt Servicing Sequence ............................................................................................................. 197

7-8 Nesting of Interrupt with High Priority ................................................................................................ 198

14 User’s Manual U10676EJ3V0UM

Page 15

LIST OF FIGURES (3/3)

Figure No. Title Page

7-9 Interrupt Nesting by Changing Interrupt Status Flag ........................................................................ 199

7-10 Block Diagram of KR4 to KR7 ............................................................................................................ 213

7-11 Format of INT2 Edge Detection Mode Register (IM2) ...................................................................... 214

8-1 Releasing Standby Mode.................................................................................................................... 218

8-2 Wait Time After Releasing STOP Mode............................................................................................. 220

8-3 STOP Mode Release by Key Return Reset or RESET Input ........................................................... 221

9-1 Configuration of Reset Circuit ............................................................................................................ 227

9-2 Reset Operation by RESET Signal .................................................................................................... 228

9-3 WDF Operation in Generating Each Signal ....................................................................................... 231

9-4 KRF Operation in Generating Each Signal ........................................................................................ 232

User’s Manual U10676EJ3V0UM

15

Page 16

LIST OF TABLES

Table No. Title Page

2-1 Pin Functions of Digital I/O Ports ....................................................................................................... 24

2-2 Functions of Non-Port Pins ................................................................................................................ 25

2-3 Recommended Connection of Unused Pins ...................................................................................... 31

3-1 Addressing Modes .............................................................................................................................. 36

3-2 Register Bank Selected by RBE and RBS ........................................................................................ 45

3-3 Example of Using Different Register Banks for Normal Routine and Interrupt Routine .................. 45

3-4 Addressing Modes Applicable to Peripheral Hardware Unit Manipulation ....................................... 50

4-1 Differences Between MkI and MkII Modes ........................................................................................ 60

4-2 Stack Area Selected by SBS .............................................................................................................. 70

4-3 PSW Flags Saved/Restored to/from Stack ........................................................................................ 74

4-4 Carry Flag Manipulation Instruction ................................................................................................... 75

4-5 Contents of Interrupt Status Flags ..................................................................................................... 76

4-6 MBE, MBS, and Memory Bank Selected ........................................................................................... 78

4-7 RBE, RBS, and Register Bank Selected ........................................................................................... 79

5-1 Interrupt Related to EEPROM Control ............................................................................................... 82

6-1 Types and Features of Digital Ports ................................................................................................... 89

6-2 I/O Pin Manipulation Instructions ....................................................................................................... 97

6-3 Operation When I/O Port Is Manipulated ........................................................................................... 99

6-4 Specifying Connection of Pull-up Resistor ........................................................................................ 100

6-5 Maximum Time Required for CPU Clock Switching .......................................................................... 112

6-6 Mode List............................................................................................................................................. 122

6-7 Resolution and Longest Set Time (8-Bit Timer Counter Mode) ........................................................ 139

6-8 Resolution and Longest Set Time (16-Bit Timer Counter Mode) ...................................................... 154

7-1 Types of Interrupt Sources ................................................................................................................. 188

7-2 Signals Setting Interrupt Request Flags ............................................................................................ 191

7-3 IST1 and IST0 and Interrupt Servicing Status .................................................................................. 196

7-4 Identifying Interrupt Sharing Vector Address ..................................................................................... 200

7-5 Types of Test Sources ......................................................................................................................... 212

7-6 Test Request Flag Setting Signals ..................................................................................................... 212

7-7 KR4 to KR7 Pins, KRREN Pin and Test Function ............................................................................. 214

8-1 Operating Statuses in Standby Mode ................................................................................................ 216

8-2 Selecting Wait Time by BTM .............................................................................................................. 220

9-1 Status of Each Hardware Unit After Reset ........................................................................................ 229

9-2 WDF and KRF Contents Corresponding to Each Signal .................................................................. 231

10-1 Selection of Mask Options .................................................................................................................. 233

11-1 Types of Bit Manipulation Addressing Modes and Specification Range .......................................... 235

16 User’s Manual U10676EJ3V0UM

Page 17

CHAPTER 1 GENERAL

The µPD754144 and 754244 are 4-bit single-chip microcontrollers in the NEC 75XL Series, the successor to the

75X Series that boasts a wealth of variations.

µ

PD754144 and 754244 have extended CPU functions compared to the µPD75048, a 75X Series product

The

with on-chip EEPROM, enabling high-speed and low voltage (1.8 V) operation.

This model is available in a small plastic SSOP (7.62 mm (300)).

µ

The features of the

PD754144 are as follows:

• Low-voltage operation: V

DD = 1.8 to 6.0 V

128-bit (16 × 8 bits) EEPROM capable of low voltage (1.8 V) operation on chip

• Variable instruction execution time useful for high-speed operation and power saving

µ

PD754144: RC oscillator (resistors and capacitors are externally provided)

4, 8, 16, 64 µs (at fCC = 1.0 MHz)

µ

PD754244: Crystal/ceramic oscillator

0.95 µs, 1.91 µs, 3.81 µs, 15.3 µs (at fX = 4.19 MHz)

0.67 µs, 1.33 µs, 2.67 µs, 10.7 µs (at fX = 6.0 MHz)

• Four timer channels

• Key return reset function for key-less entry

• Small package (20-pin plastic SSOP (7.62 mm (300))

APPLICATIONS

• Automotive appliances such as keyless entry, small data carriers, etc.

µ

Remark Unless otherwise specified, the

tive model in this manual. When you use this manual for the

µ

PD754244 as the µPD754144 and fX as fCC.

PD754244 (crystal/ceramic oscillation, fX) is treated as the representa-

µ

PD754144 (RC oscillation, fCC), take the

User’s Manual U10676EJ3V0UM

17

Page 18

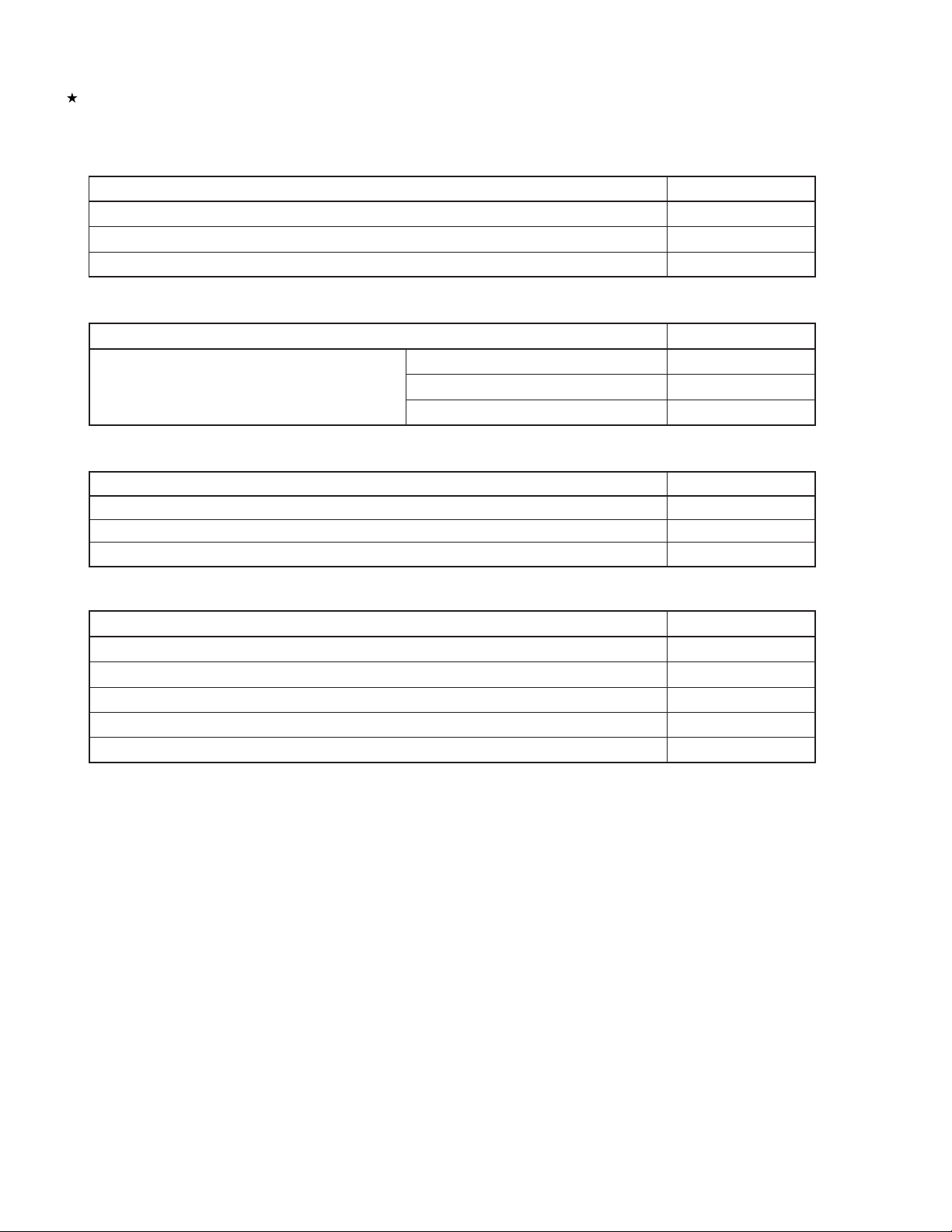

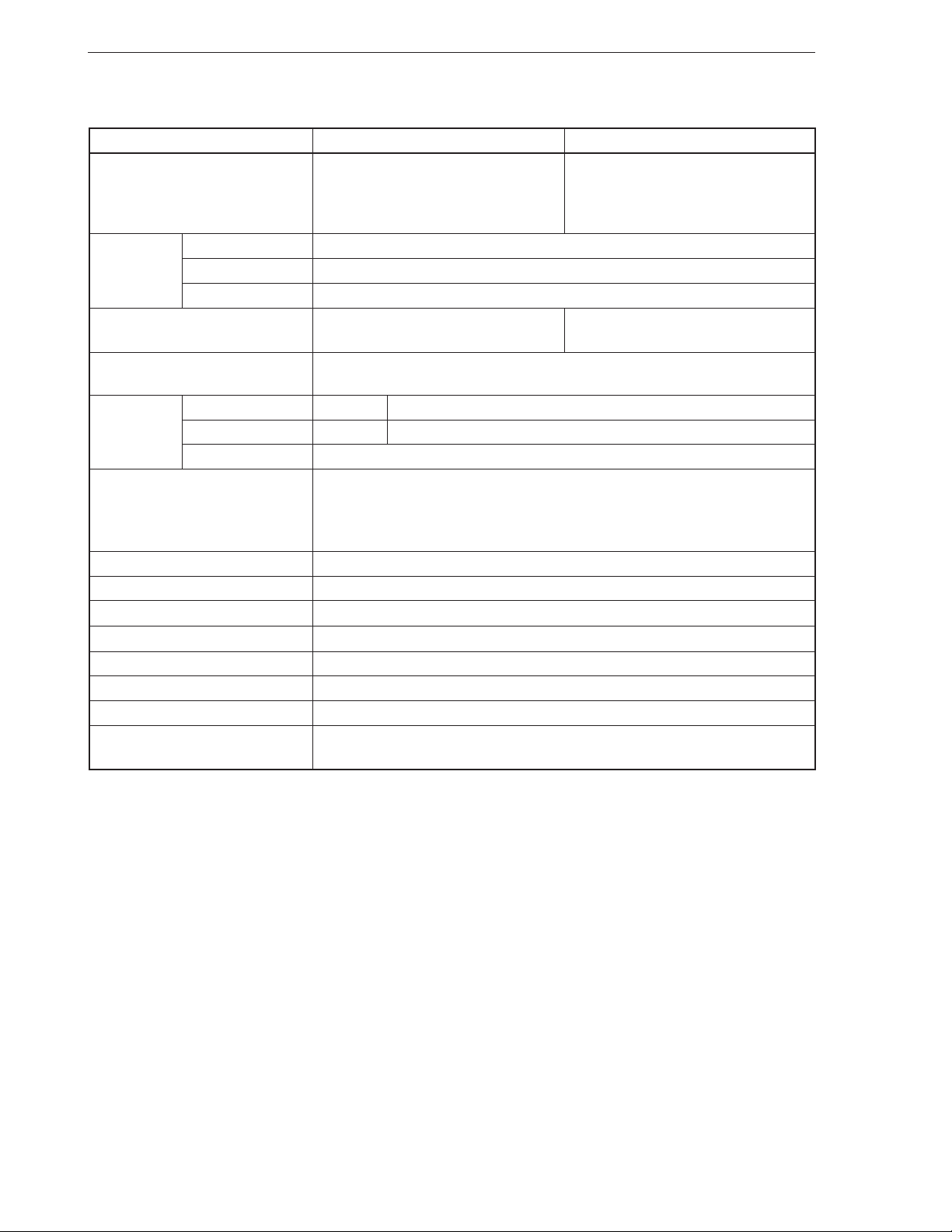

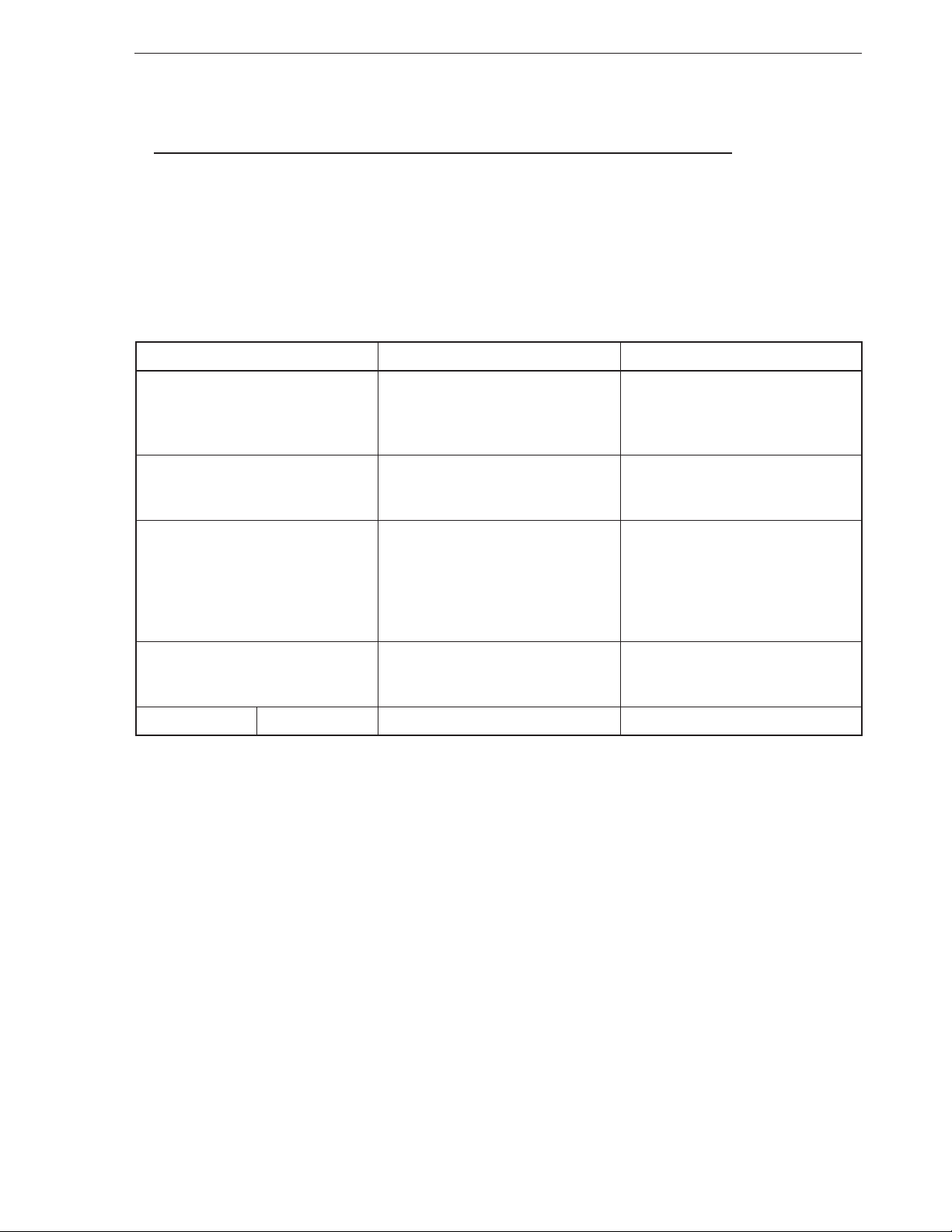

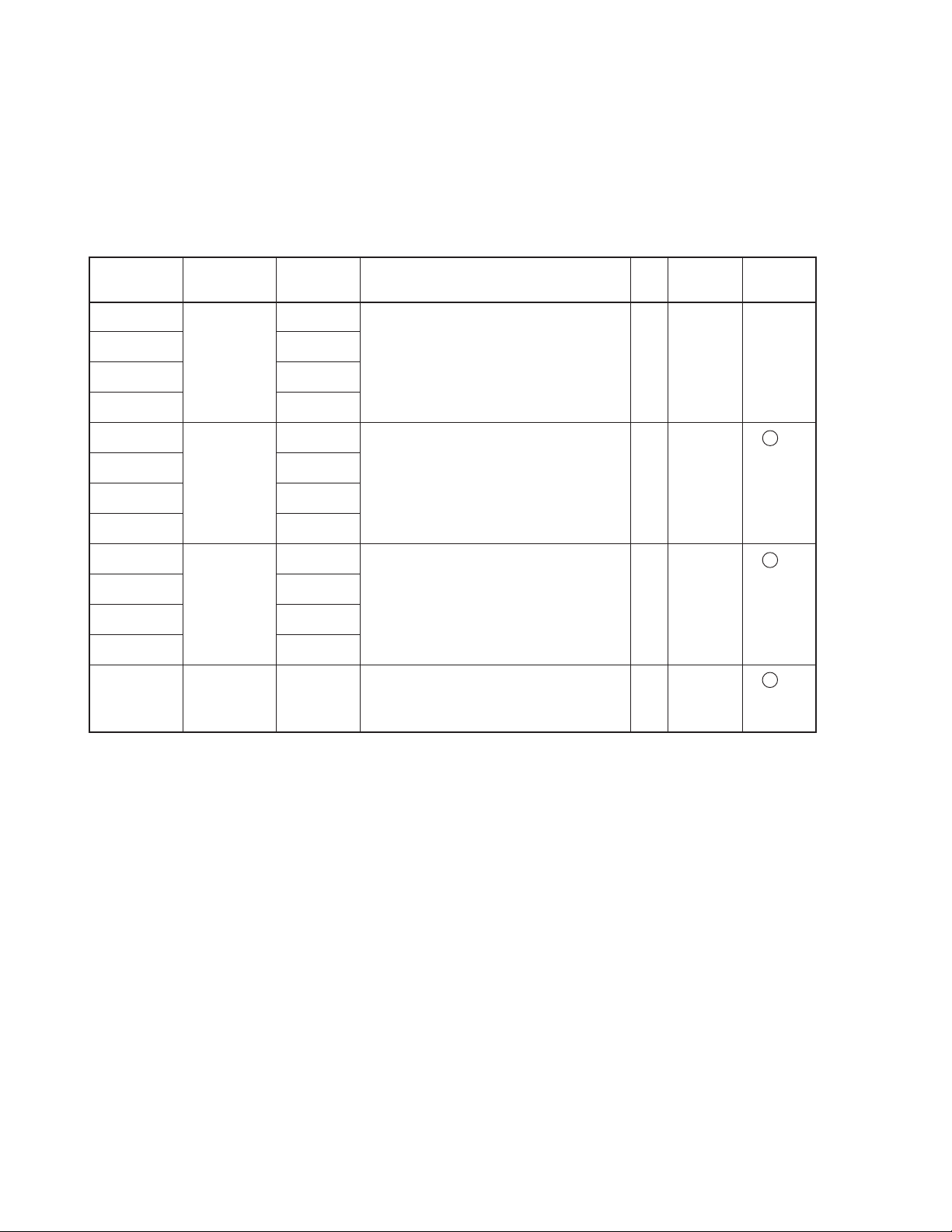

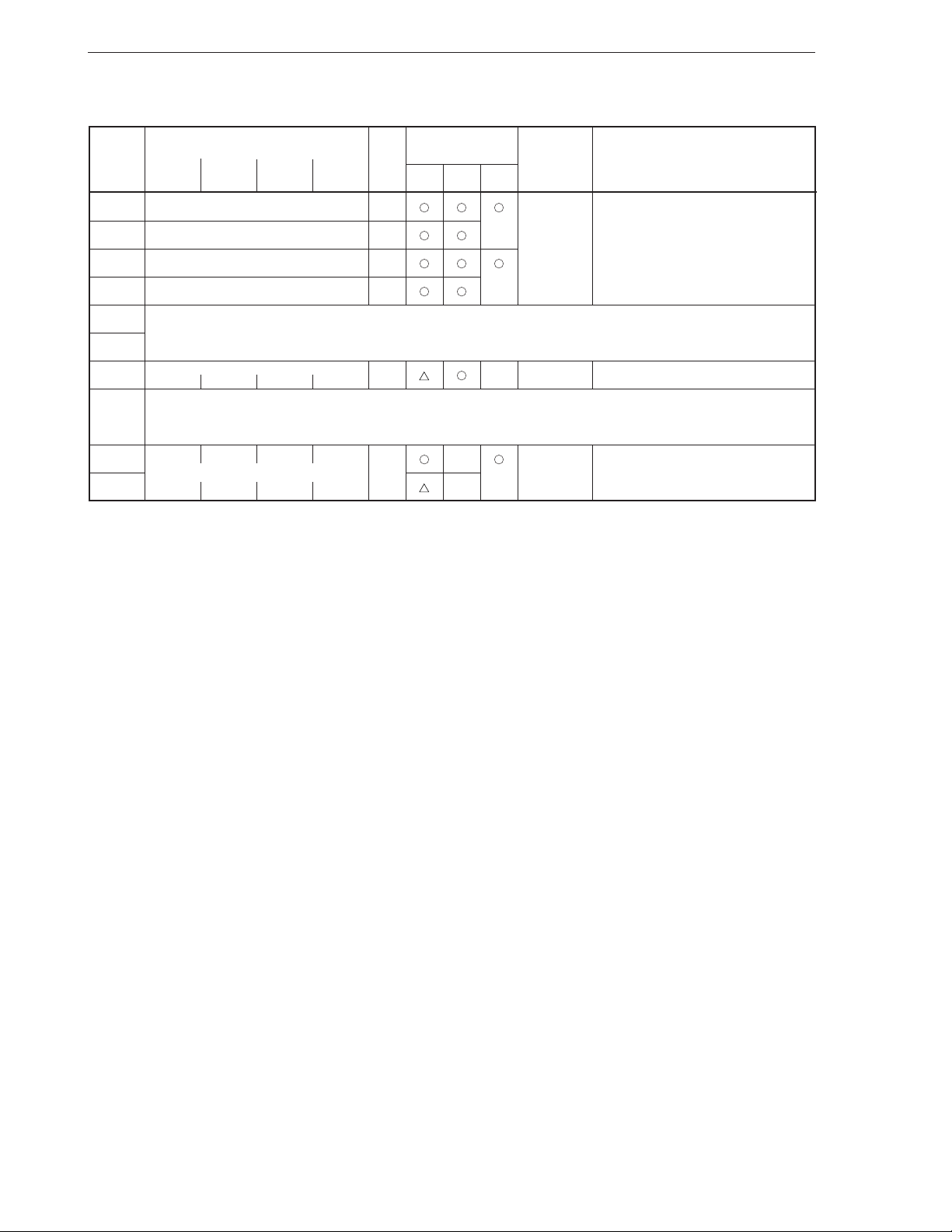

1.1 Functional Outline

CHAPTER 1 GENERAL

Item

Instruction execution time • 4, 8, 16, 64 µs (at fCC = 1.0 MHz) • 0.95, 1.91, 3.81, 15.3 µs

On-chip Mask ROM 4096 × 8 bits (0000H to 0FFFH)

memory RAM 128 × 4 bits (000H to 07FH)

EEPROM 16 × 8 bits (400H to 41FH)

System clock oscillator RC oscillator Crystal/ceramic oscillator

(External resistor and capacitor)

General-purpose registers • 4-bit operation: 8 × 4 banks

• 8-bit operation: 4 × 4 banks

I/O ports CMOS input 4 Pull-up resistors can be incorporated by mask option

CMOS I/O 9 On-chip pull-up resistors can be specified by software

Total 13

Timers 4 channels

• 8-bit timer counter: 3 channels

(can be used as 16-bit timer counter)

• Basic interval/watchdog timer: 1 channel

Programmable threshold port 2 channels

Bit sequential buffer 16 bits

Vectored interrupt External: 1, Internal: 5

Test input External: 1 (with key return reset function)

Standby function STOP/HALT mode

Operating ambient temperature TA = –40 to +85°C

Power supply voltage VDD = 1.8 to 6.0 V

Package • 20-pin plastic SOP (7.62 mm (300))

• 20-pin plastic SSOP (7.62 mm (300))

µ

PD754144

µ

PD754244

(at fX = 4.19 MHz)

• 0.67, 1.33, 2.67, 10.7 µs

(at fX = 6.00 MHz)

18 User’s Manual U10676EJ3V0UM

Page 19

CHAPTER 1 GENERAL

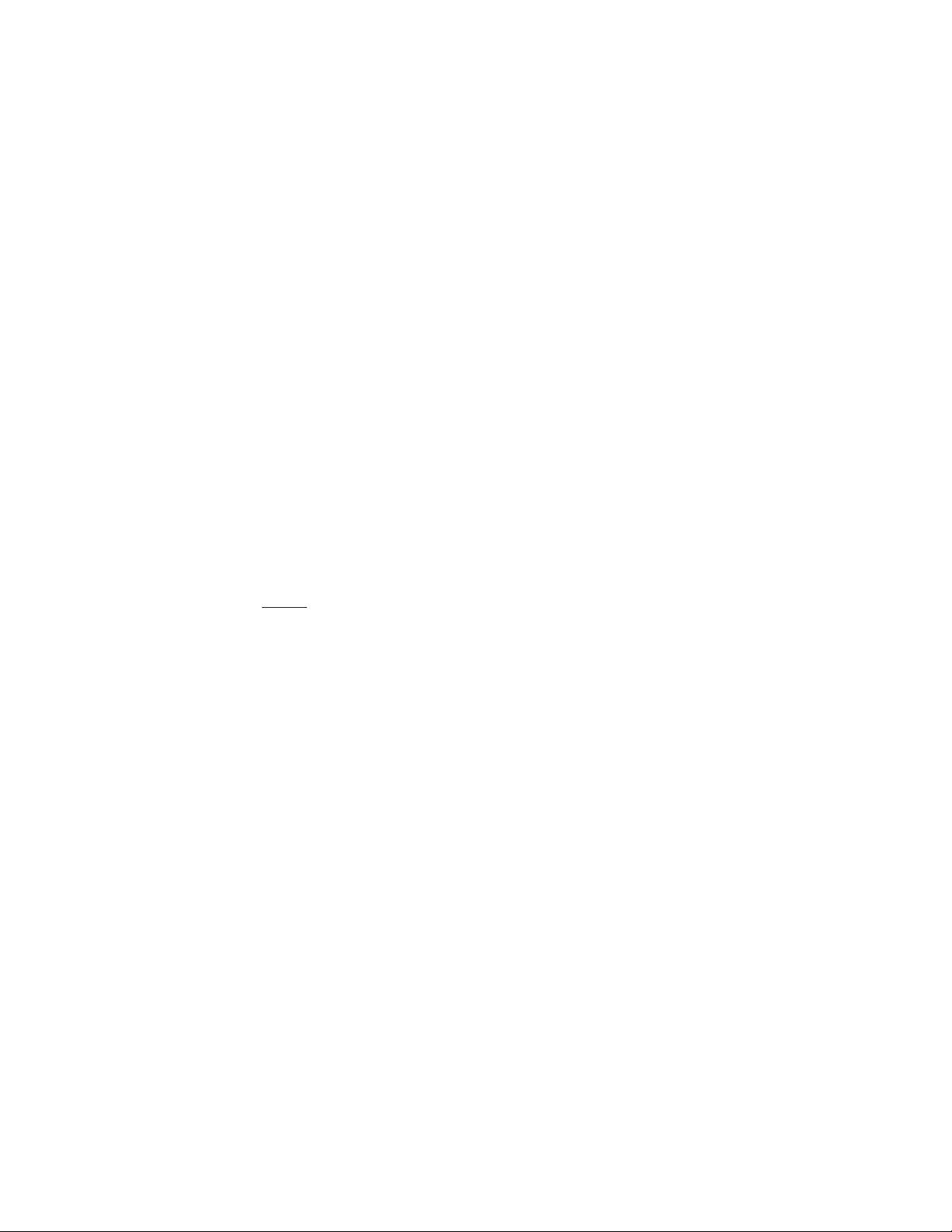

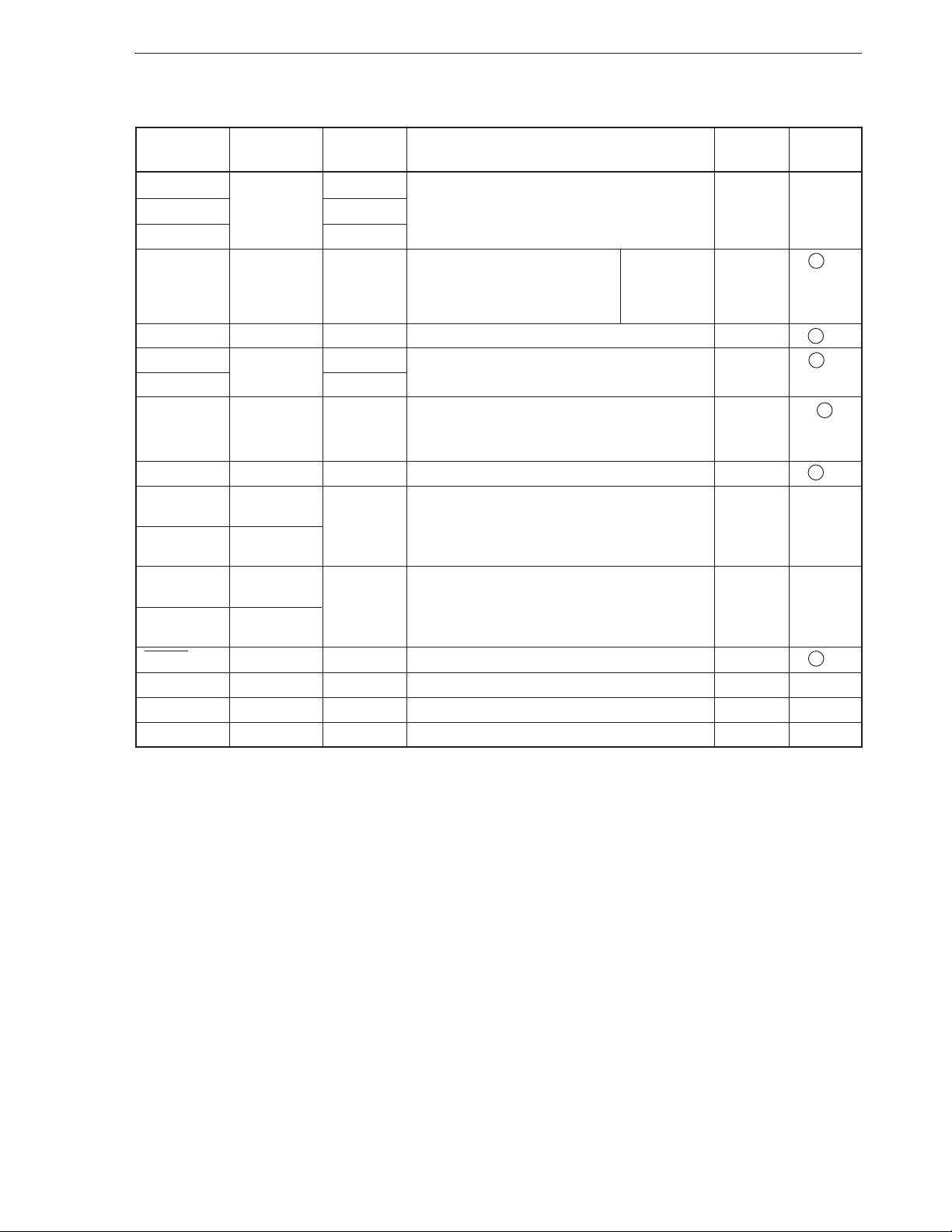

1.2 Ordering Information

Part Number Package

µ

PD754141GS-×××-BA5 20-pin plastic SOP (7.62 mm (300))

µ

PD754141GS-×××-GJG 20-pin plastic SSOP (7.62 mm (300))

µ

PD754244GS-×××-BA5 20-pin plastic SOP (7.62 mm (300))

µ

PD754244GS-×××-GJG 20-pin plastic SSOP (7.62 mm (300))

Remark ××× indicates ROM code suffix.

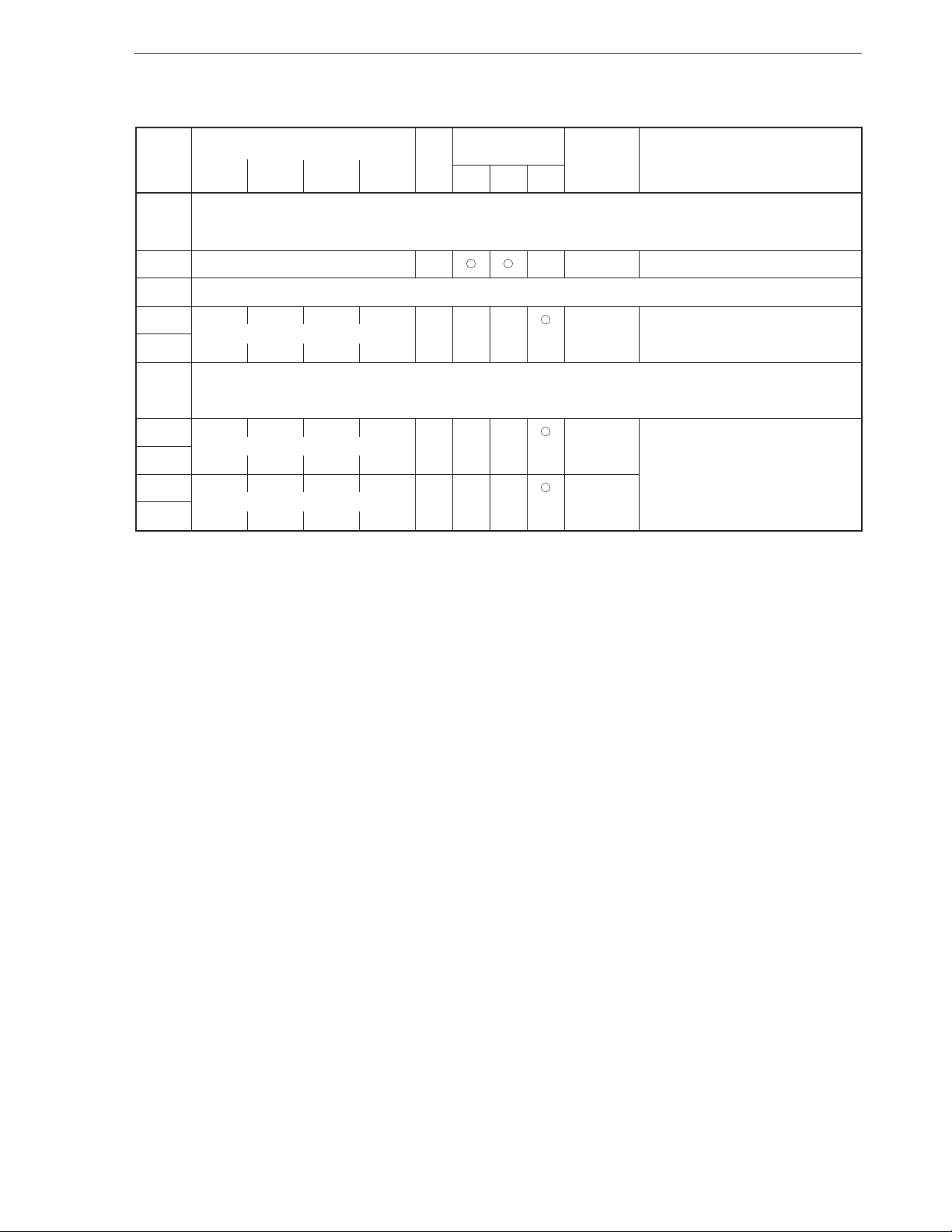

1.3 Differences Between Series Products

Item

Instruction execution time 4, 8, 16, 64 µs (at fCC = 1.0 MHz) • 0.95, 1.91, 3.81, 15.3 µs

System clock oscillator RC oscillator Crystal/ceramic oscillator

(resistors and capacitors are externally

provided)

Startup time after reset Fixed to 56 µs (at 1 MHz) Can be selected by mask option from

Standby mode release time 29/fCC Can be selected by BTM setting from

Pin connection pin 2, pin 3 CL1, CL2 X1, X2

µ

PD754144

µ

PD754244

(at fX = 4.19 MHz)

• 0.67, 1.33, 2.67, 10.7 µs

(at fX = 6.0 MHz)

the following two:

•217/fX (31.3 ms: at 4.19 MHz,

21.8 ms: at 6.0 MHz)

•215/fX (7.81 ms: at 4.19 MHz,

5.46 ms: at 6.0 MHz)

the following four:

220/fX, 217/fX, 215/fX, 213/fX

User’s Manual U10676EJ3V0UM

19

Page 20

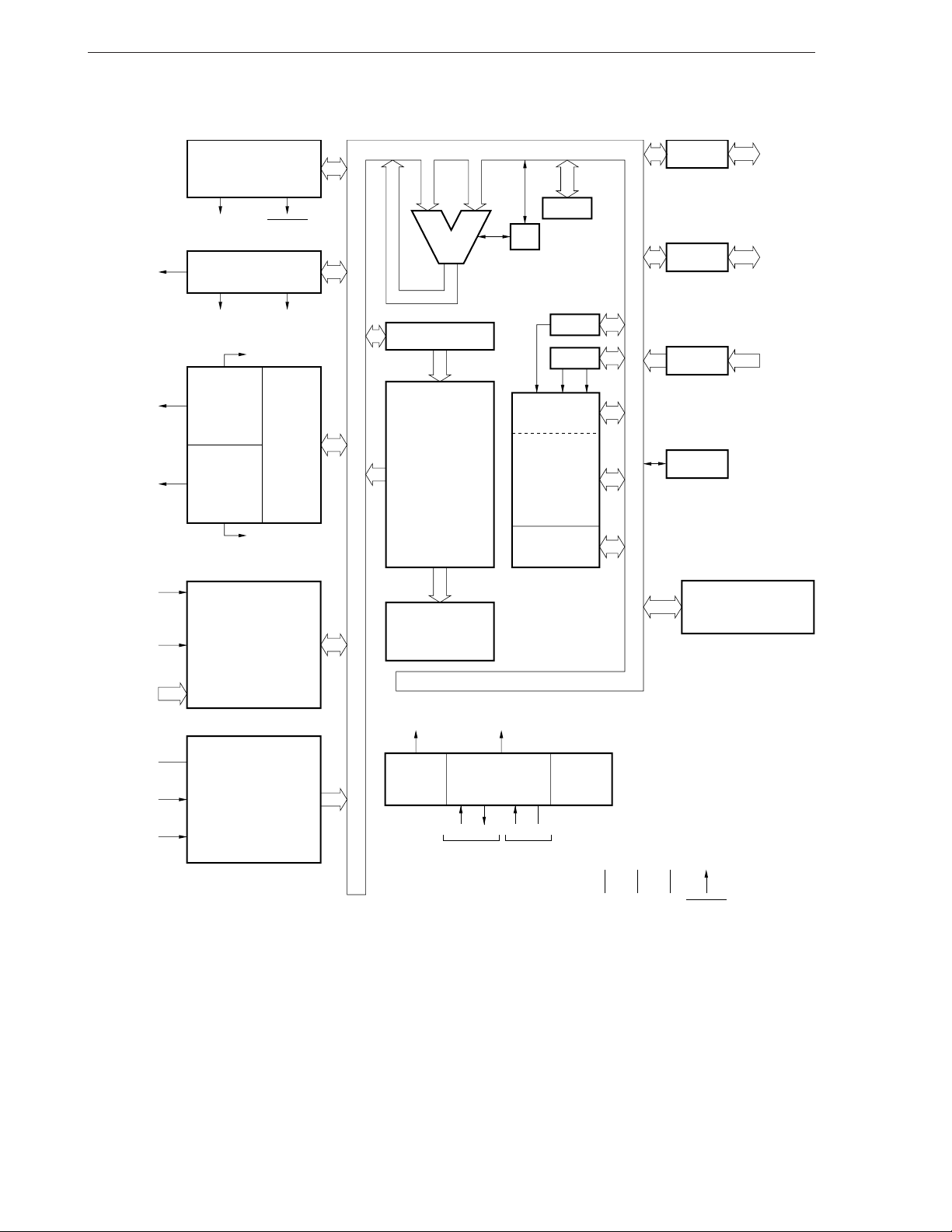

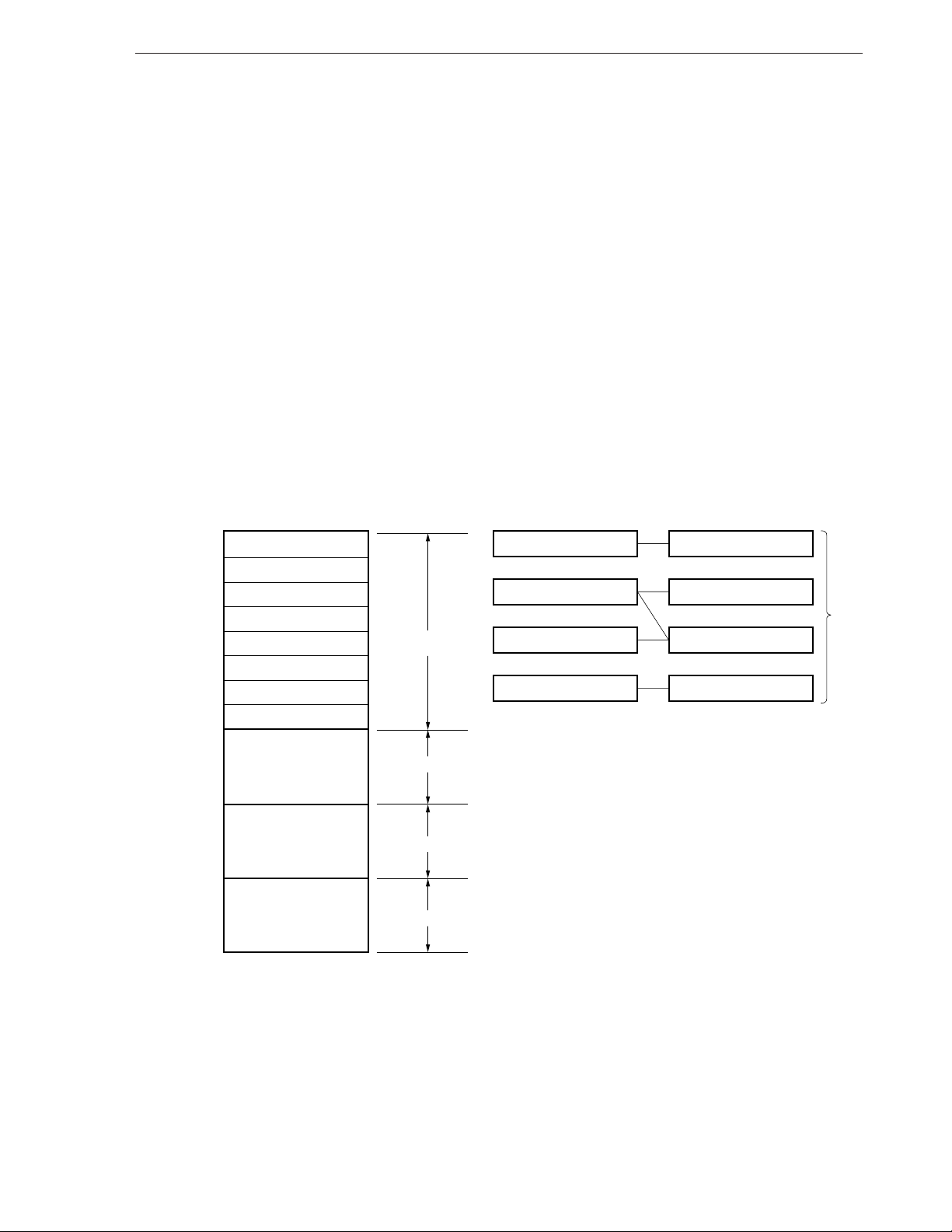

1.4 Block Diagram

CHAPTER 1 GENERAL

PTO0/P30

PTO1/P31

PTO2/P32

INT0/P61

KRREN

Basic interval

timer/watchdog timer

INTBT RESET

8-bit timer counter #0

INTT0 TOUT

INTT1

8-bit timer

counter #1

Cascaded

16-bit

timer

8-bit timer

counter

counter #2

INTT2

Interrupt control

ALU

Program counter

Program memory

(ROM)

4096 × 8 bits

Decode and

control

SP (8)

CY

SBS

Bank

General reg.

Data memory

(RAM)

128 × 4 bits

EEPROM

16 × 8 bits

Port 3 4

Port 6 4

Port 7 4

Port 8

P80

Bit seq. buffer (16)

P30 to P33

P60 to P63

P70 to P73

KR4/P70KR7/P73

REF

/P60

AV

PTH00/P62

PTH01/P63

4

φ

Standby

control

Programmable

f

Clock

divider

N

X

/2

CPU clock

System clock

generator

threshold port

CL1 CL2 X1 X2

In the case of

µ

PD754144

In the case of

µ

PD754244

IC V

DDVSS

RESET

20 User’s Manual U10676EJ3V0UM

Page 21

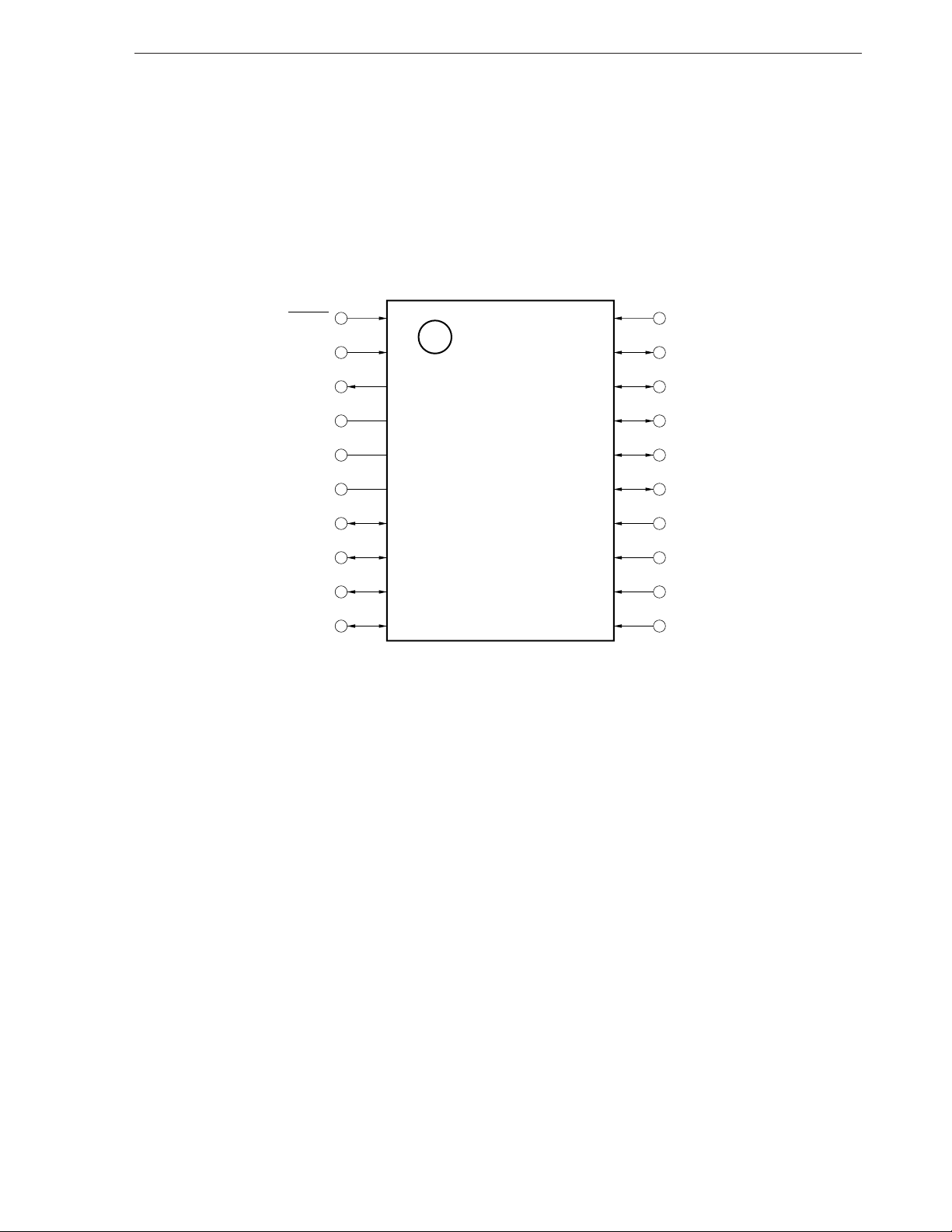

1.5 Pin Configuration (Top View)

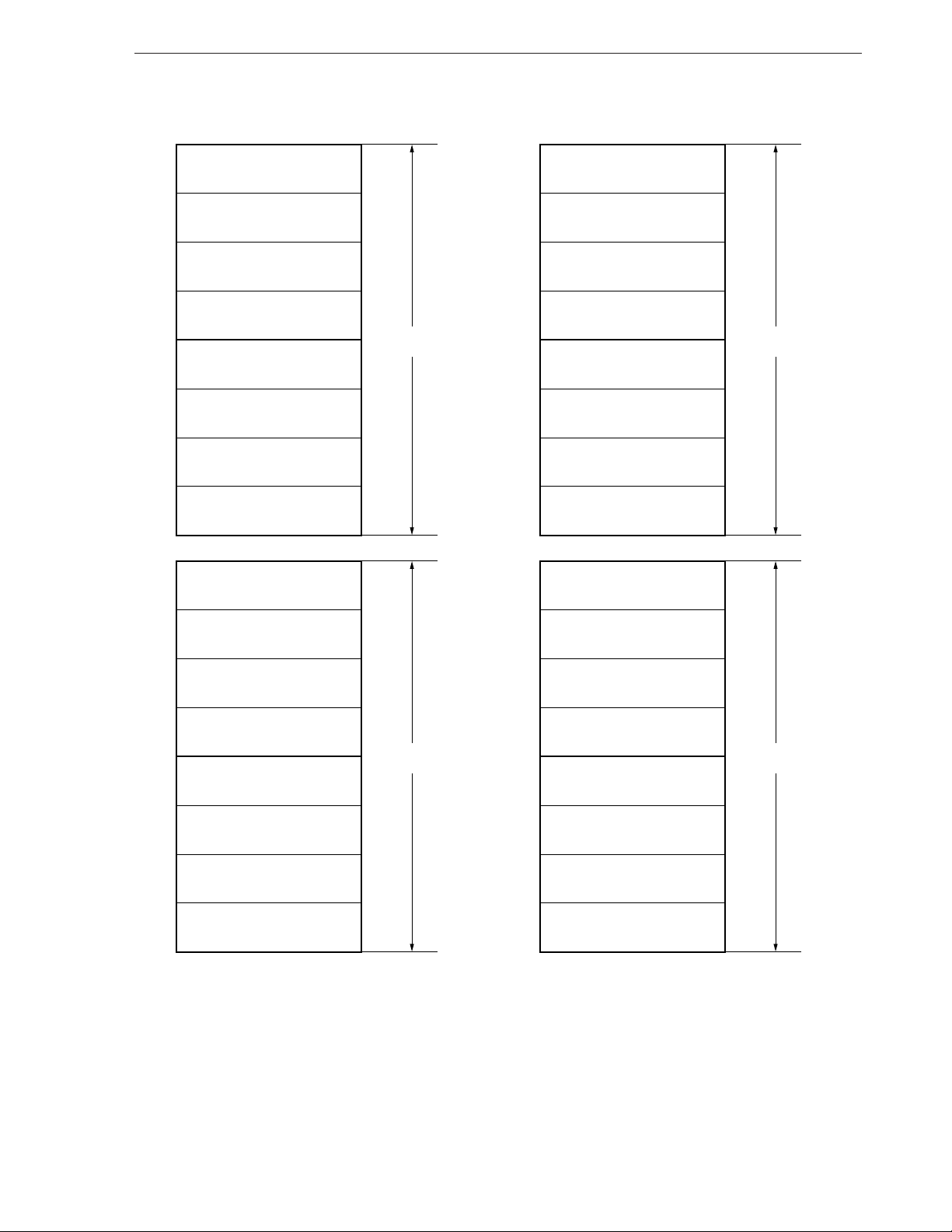

• Pin configuration of µPD754144

• 20-pin plastic SOP (7.62 mm (300))

µ

PD754144GS-×××-BA5

• 20-pin plastic SSOP (7.62 mm (300))

µ

PD754144GS-×××-GJG

CHAPTER 1 GENERAL

RESET

CL1

CL2

V

IC

V

P60/AV

REF

P61/INT0

P62/PTH00

P63/PTH01

SS

DD

1

2

3

4

5

6

7

8

9

10

IC: Internally Connected (Directly connect to VDD.)

20

19

18

17

16

15

14

13

12

11

KRREN

P80

P30/PTO0

P31/PTO1

P32/PTO2

P33

P70/KR4

P71/KR5

P72/KR6

P73/KR7

User’s Manual U10676EJ3V0UM

21

Page 22

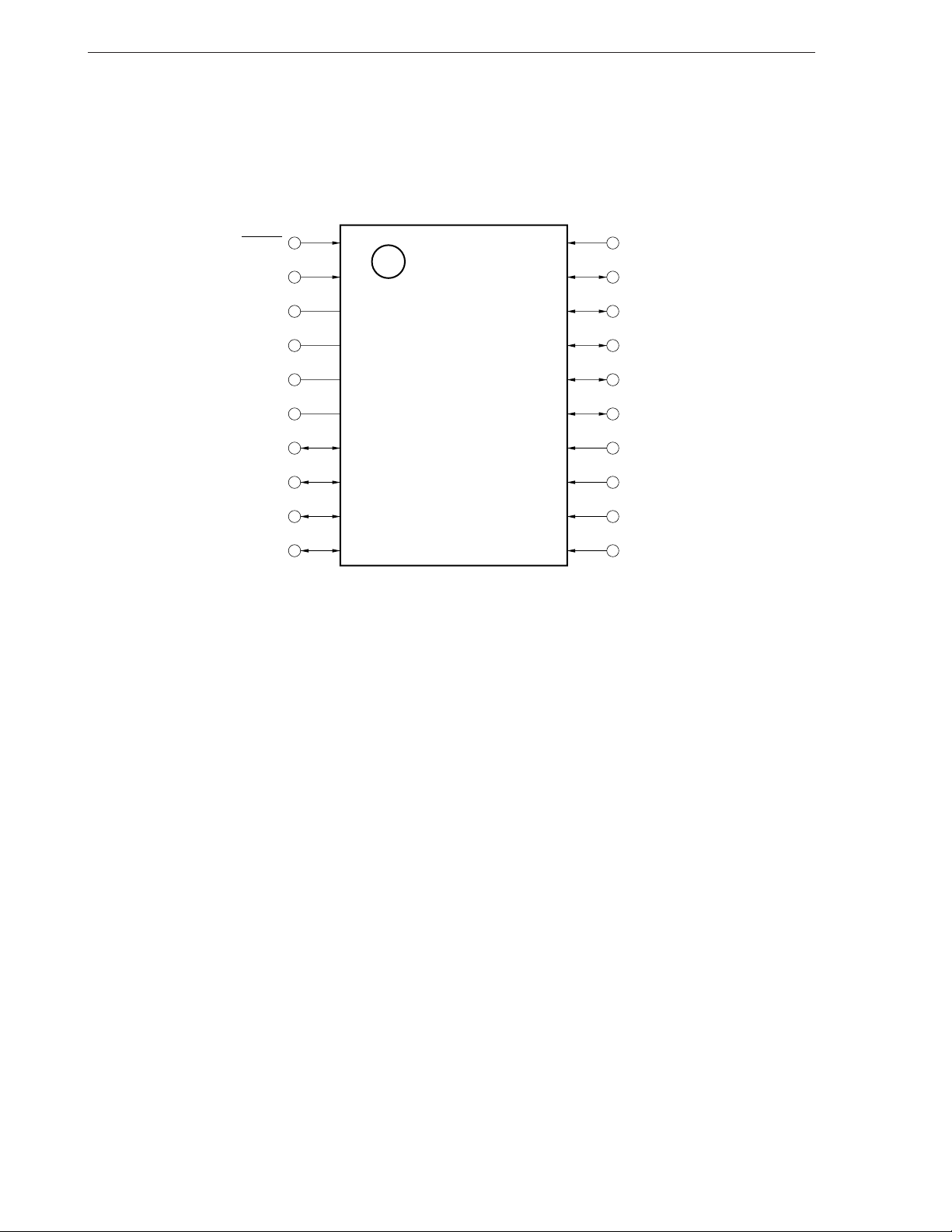

• Pin configuration of µPD754244

• 20-pin plastic SOP (7.62 mm (300))

µ

PD754244GS-×××-BA5

• 20-pin plastic SSOP (7.62 mm (300))

µ

PD754244GS-×××-GJG

CHAPTER 1 GENERAL

RESET

X1

X2

V

IC

V

P60/AV

REF

P61/INT0

P62/PTH00

P63/PTH01

SS

DD

1

2

3

4

5

6

7

8

9

10

IC: Internally Connected (Directly connect to V

DD.)

20

19

18

17

16

15

14

13

12

11

KRREN

P80

P30/PTO0

P31/PTO1

P32/PTO2

P33

P70/KR4

P71/KR5

P72/KR6

P73/KR7

22 User’s Manual U10676EJ3V0UM

Page 23

CHAPTER 1 GENERAL

Pin Name

P30 to P33: Port 3

P60 to P63: Port 6

P70 to P73: Port 7

P80: Port 8

KR4 to KR7: Key return 4 to 7

INT0: External vectored interrupt 0

PTH00, PTH01: Programmable threshold port analog input 0, 1

PTO0 to PTO2: Programmable timer output 0 to 2

KRREN: Key return reset enable

CL1, CL2: RC oscillator

X1, X2: Crystal/ceramic oscillator

IC: Internally connected

RESET: Reset

REF: Analog reference

AV

V

SS: Ground

VDD: Positive power supply

User’s Manual U10676EJ3V0UM

23

Page 24

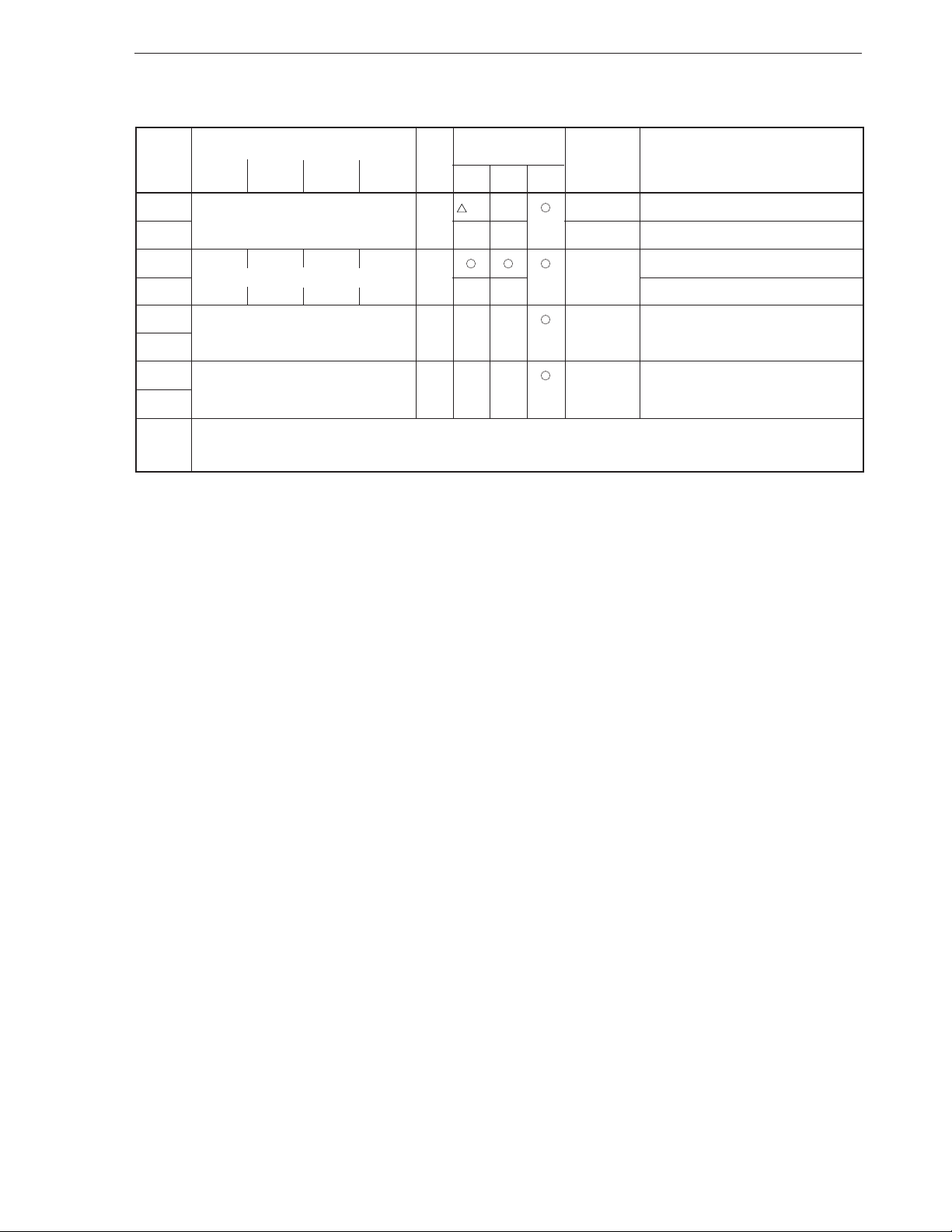

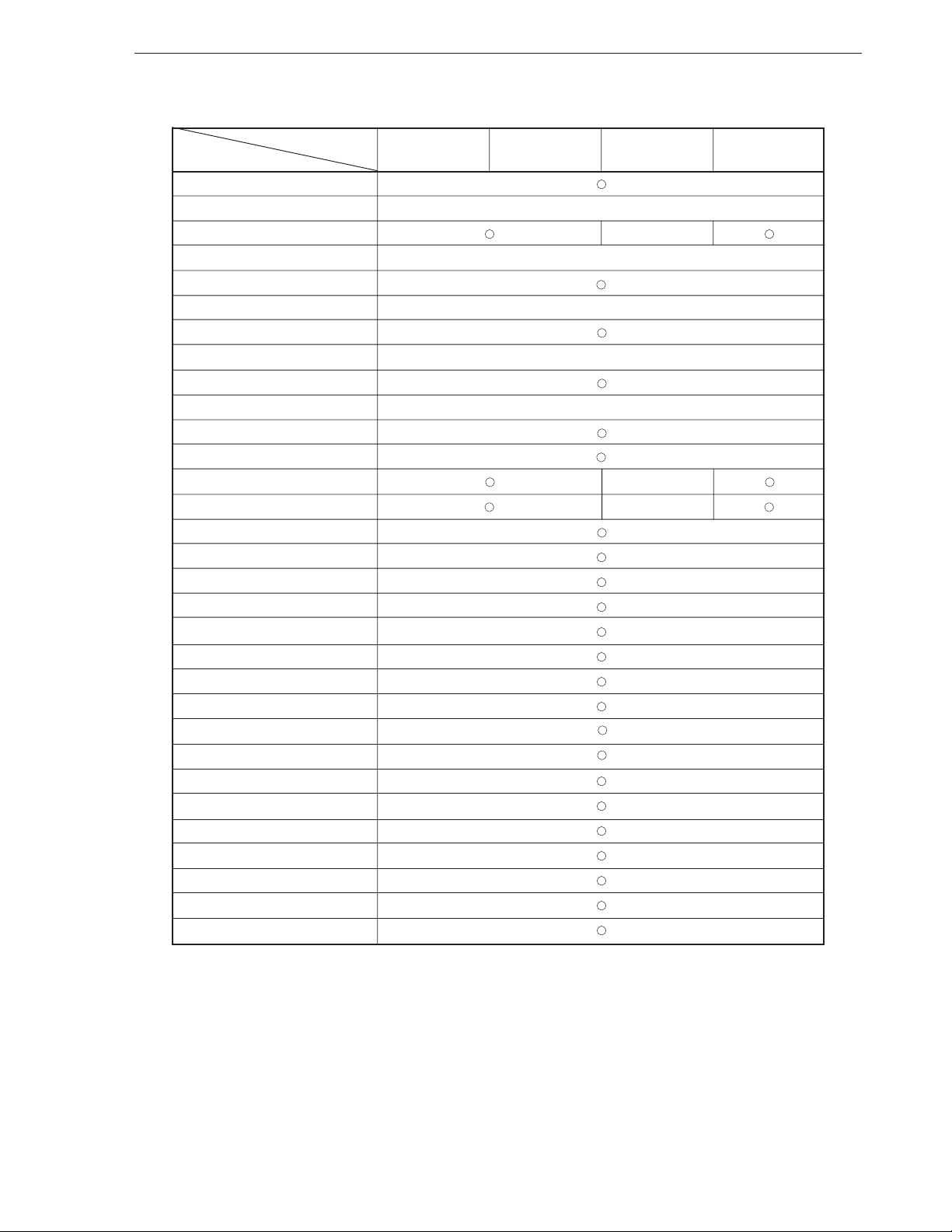

2.1 Pin Functions of µPD754244

Table 2-1. Pin Functions of Digital I/O Ports

CHAPTER 2 PIN FUNCTIONS

Pin Name I/O

P30 I/O PTO0 × Input E-B

P31 PTO1

P32 PTO2

P33 –

P60 I/O AVREF × Input F -A

P61 INT0

P62 PTH00

P63 PTH01

P70 Input KR4 × Input B -A

P71 KR5

P72 KR6

P73 KR7

P80 I/O – × Input F -A

Alternate

Function I/O Type

Programmable 4-bit I/O port (Port 3).

Input/output can be specified in 1-bit units.

On-chip pull-up resistor can be specified by

software in 4-bit units.

Programmable 4-bit I/O port (Port 6).

Input/output can be specified in 1-bit units.

An on-chip pull-up resistor can be specified

by software in 4-bit units

A noise eliminator is selectable for P61/

INT0.

4-bit input port (Port 7).

A pull-up resistor can be incorporated (mask

option).

1-bit I/O port (PORT8).

An on-chip pull-up resistor can be specified

by software.

Function

Note 2

.

8-Bit

After Reset

I/O Circuit

Note 1

Notes 1. Circled characters indicate Schmitt-triggered input.

2. Do not specify connection of an on-chip pull-up resistor when using a programmable threshold port.

24 User’s Manual U10676EJ3V0UM

Page 25

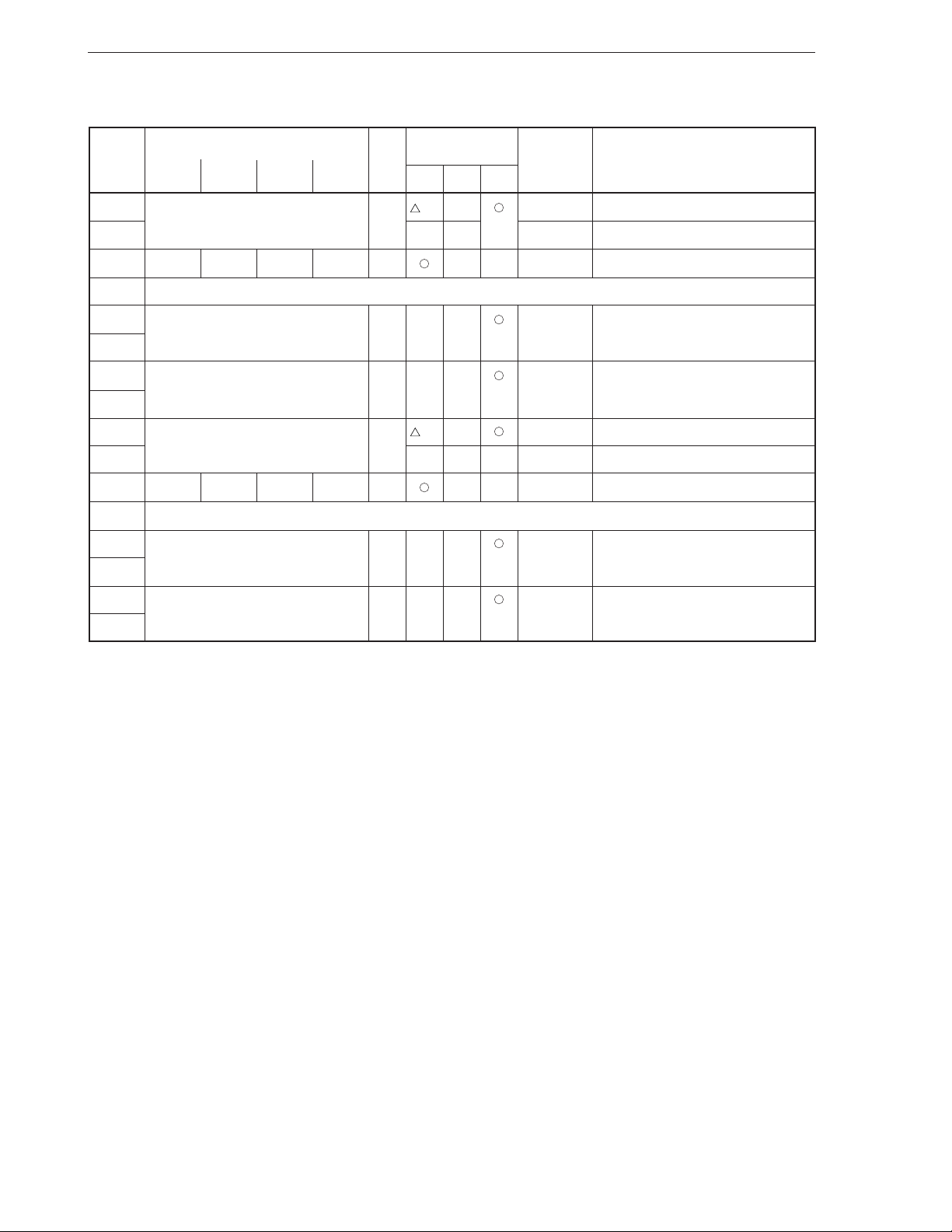

CHAPTER 2 PIN FUNCTIONS

Table 2-2. Functions of Non-Port Pins

Pin Name I/O

Alternate

Function Type

Function

After Reset

I/O Circuit

Note

PTO0 Output P30 Timer counter output pins. Input E-B

PTO1 P31

PTO2 P32

INT0 Input P61 Edge-detected vectored interrupt input Input F -A

(edge to be detected is selectable).

Noise eliminator is selectable.

Noise

eliminator/

asynchronous

selectable

KR4 to KR7 Input P70 to P73 Falling edge-detected testable input. Input B -A

PTH00 Input P62 Variable threshold voltage 2-bit analog input. Input F -A

PTH01 P63

KRREN Input – Key return reset enable pin. Input B

Reset signal is generated at falling edge of KRn

when KRREN = high in STOP mode.

AVREF Input P60 Reference voltage input pin. Input F -A

CL1 Input – Provided in µPD754144 only. – –

These pins connect R and C for system clock

CL2 Output oscillation. No external clock can be input to

these pins.

X1 Input – Provided in µPD754244 only. – –

These pins connect crystal/ceramic oscillator for

X2 – system clock oscillation. When external clock is

used, input it to X1 and inverse phase to X2.

RESET Input – System reset input pin (active-low) – B -A

IC – – Internally connected. Connect directly to VDD.– –

VDD – – Positive power supply pin. – –

VSS – – Ground potential. – –

Note Circled characters indicate Schmitt triggered input.

User’s Manual U10676EJ3V0UM

25

Page 26

CHAPTER 2 PIN FUNCTIONS

2.2 Description of Pin Functions

2.2.1 P30 to P33 (Port 3) ... I/O pins shared with PTO0 to PTO2

P60 to P63 (Port 6) ... I/O pins shared with AV

P80 (Port 8) ... I/O pin

These are 4-bit I/O ports with output latches (ports 3 and 6) and a 1-bit I/O port with an output latch (port 8).

Ports 3 and 6 also have the following functions, in addition to the I/O port function.

• Port 3: Timer counter output (PTO0 to PTO2)

• Port 6: Programmable threshold port reference voltage input (AV

Vectored interrupt input (INT0)

Threshold variable voltage input (PTH00, PTH01)

The input or output mode of ports 3 and 6 is selected by port mode register group A (PMGA), and the input

or output mode of port 8 is selected by port mode register group C (PMGC). Ports 3 and 6 can be set to the input

or output mode in 1-bit units.

Ports 3, 6, and 8 can also be connected to an internal pull-up resistor by software. This is done by manipulating

the pull-up resistor specification registers (POGA and POGB). Specify connection of the pull-up resistor to ports

3 and 6 in 4-bit units. Connection of the pull-up resistor to port 8 can be specified in 1-bit units.

I/O for ports 3 and 6 is possible in 4-bit or 1-bit units. Manipulation in 8-bit units is not possible.

Generation of the RESET signal sets the input mode.

REF, INT0, PTH00, PTH01

REF)

2.2.2 P70 to P73 (Port 7) ... input pins shared with KR4 to KR7

Port 7 is a 4-bit input port.

This port also has a key interrupt input (KR4 to KR7) function, in addition the input port function.

Each pin is always set to input irrespective of the operation of alternate function pins. These pins have Schmitt-

triggered input to prevent malfunction due to noise.

Internal pull-up resistors are specifiable by a mask option in 1-bit units.

2.2.3 PTO0 to PTO2 ... output pins shared with port 3

These are the output pins of timer counters 0 to 2, and output square-wave pulses. To output the signal of a timer

counter, clear the output latch of the corresponding pin of port 3 to “0”. Then, set the bit corresponding to port 3 of

port mode register group A (PMGA) to “1” to set the output mode.

The output of the TOUT F/F pin is cleared to “0” by the timer start instruction.

For details, refer to 6.4.2 (3) Timer counter operation (8-bit).

26 User’s Manual U10676EJ3V0UM

Page 27

CHAPTER 2 PIN FUNCTIONS

2.2.4 INT0 ... input pin shared with port 6

This pin inputs the vectored interrupt signal detected by the edge. A noise eliminator is selectable for INT0. The

edge to be detected can be specified by using the edge detection mode register (IM0).

(1) INT0 (bits 0 and 1 of IM0)

(a) Active at rising edge

(b) Active at falling edge

(c) Active at both rising and falling edges

(d) External interrupt signal input disabled

INT0 is an asynchronous input pin, and a signal having a specific high-level width input to this pin can be

acknowledged as an interrupt, regardless of the operating clock of the CPU. In addition, an internal noise

eliminator can be connected to this pin by software, and the sampling clock that is used for noise elimination

can be changed in two steps. In this case, the width of the signal that can be acknowledged differs depending

on the CPU operating clock.

When the RESET signal is asserted, IM0 is cleared to “0”, and the rising edge is selected as the active edge.

INT0 can be used to release the STOP and HALT modes. However, when the noise eliminator is selected,

INT0 cannot be used to release the STOP and HALT modes.

INT0 is a Schmitt-triggered input pin.

2.2.5 KR4 to KR7 ... input pins shared with port 7

These are key interrupt input pins. KR4 to KR7 are parallel falling edge-detected interrupt input pins.

The interrupt source can be specified for “KR4 to KR7” by using the edge detection mode register (IM2).

When the RESET signal is asserted, these pins serve as port 7 pins and are set to the input mode.

2.2.6 KRREN

This is a key return reset function selection pin. It is always set to input.

When the KRREN pin is high and it is in STOP mode, a falling input on pins KR4/P70 to KR7/P73 generates a

system reset. At this time, STOP mode is released.

When the KRREN pin is low, pins KR4/P70 to KR7/P73 function as normal input pins or release standby.

2.2.7 TH00 and TH01 ... input pins shared with port 6

These are the input pins of the programmable threshold port (threshold voltage variable analog input port).

Setting the programmable threshold port mode register (PTHM) can change the threshold voltage in 16 stages.

User’s Manual U10676EJ3V0UM

27

Page 28

CHAPTER 2 PIN FUNCTIONS

2.2.8 AVREF ... input pin shared with port 6

This is a reference voltage input pin. An analog reference voltage for the programmable threshold port is input.

µ

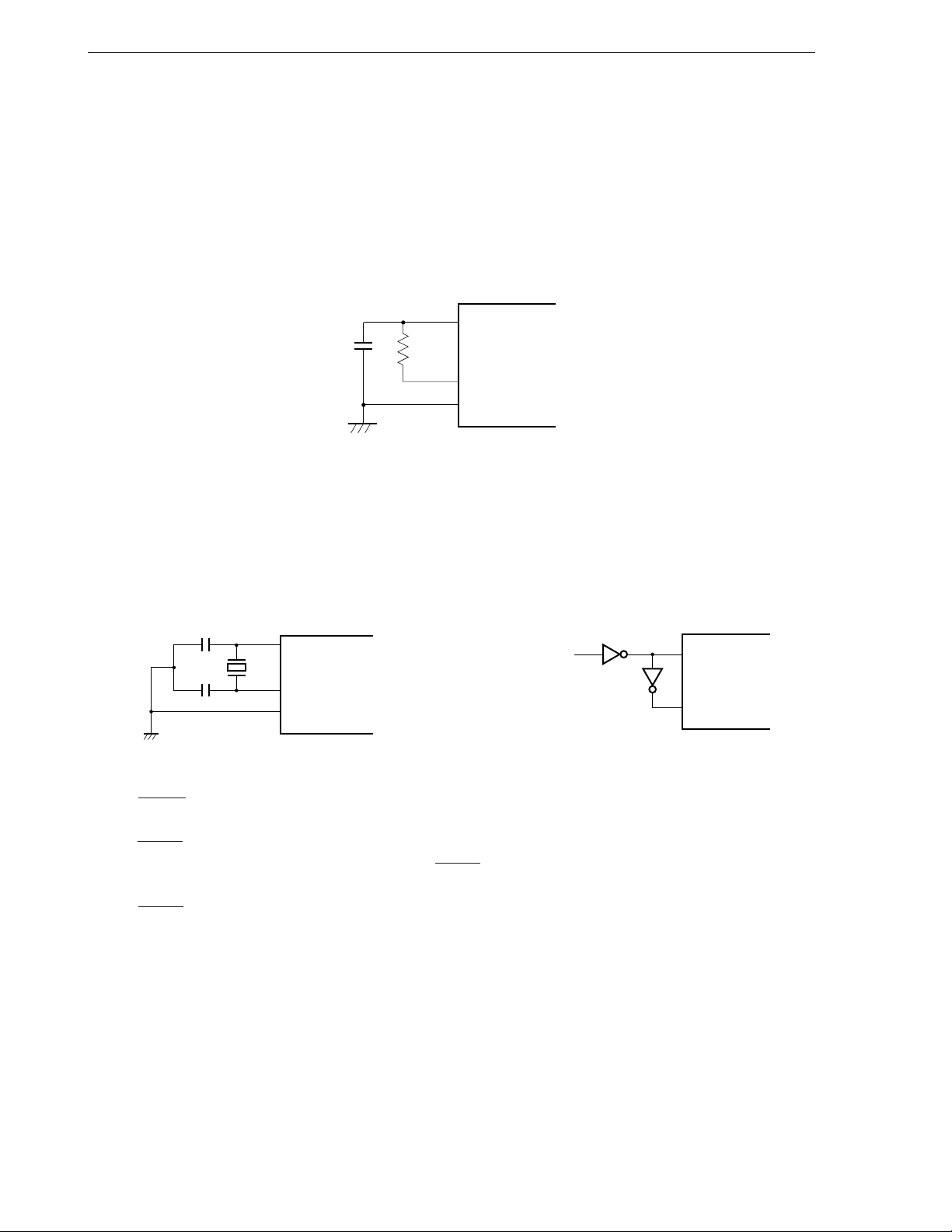

2.2.9 CL1 and CL2 (

PD754144 only)

These pins are used to connect the RC oscillator resistor (R) and capacitor (C) of the system clock oscillator.

No external clock can be input.

RC oscillation

µ

PD754144

CL1

C

R

CL2

VSS

2.2.10 X1 and X2 (µPD754244 only)

These pins connect a crystal/ceramic oscillator for system clock oscillation.

An external clock can also be input to these pins.

(a) Ceramic/crystal oscillation (b) External clock

PD754244

µ

X1

X2

Crystal resonator

or

ceramic resonator

µ

PD754244

X1

X2

SS

V

(4.194304 MHz TYP.)

ExternaI

clock

2.2.11 RESET

This pin inputs an active-low reset signal.

The RESET signal is an asynchronous input signal and is asserted when a signal with a specific low-level width

is input to this pin regardless of the operating clock. The RESET signal takes precedence over all the other operations.

This pin can not only be used to initialize and start the CPU, but also to release the STOP and HALT modes.

The RESET pin is a Schmitt-triggered input pin.

This pin can be connected to an internal pull-up resistor by a mask option.

28 User’s Manual U10676EJ3V0UM

Page 29

CHAPTER 2 PIN FUNCTIONS

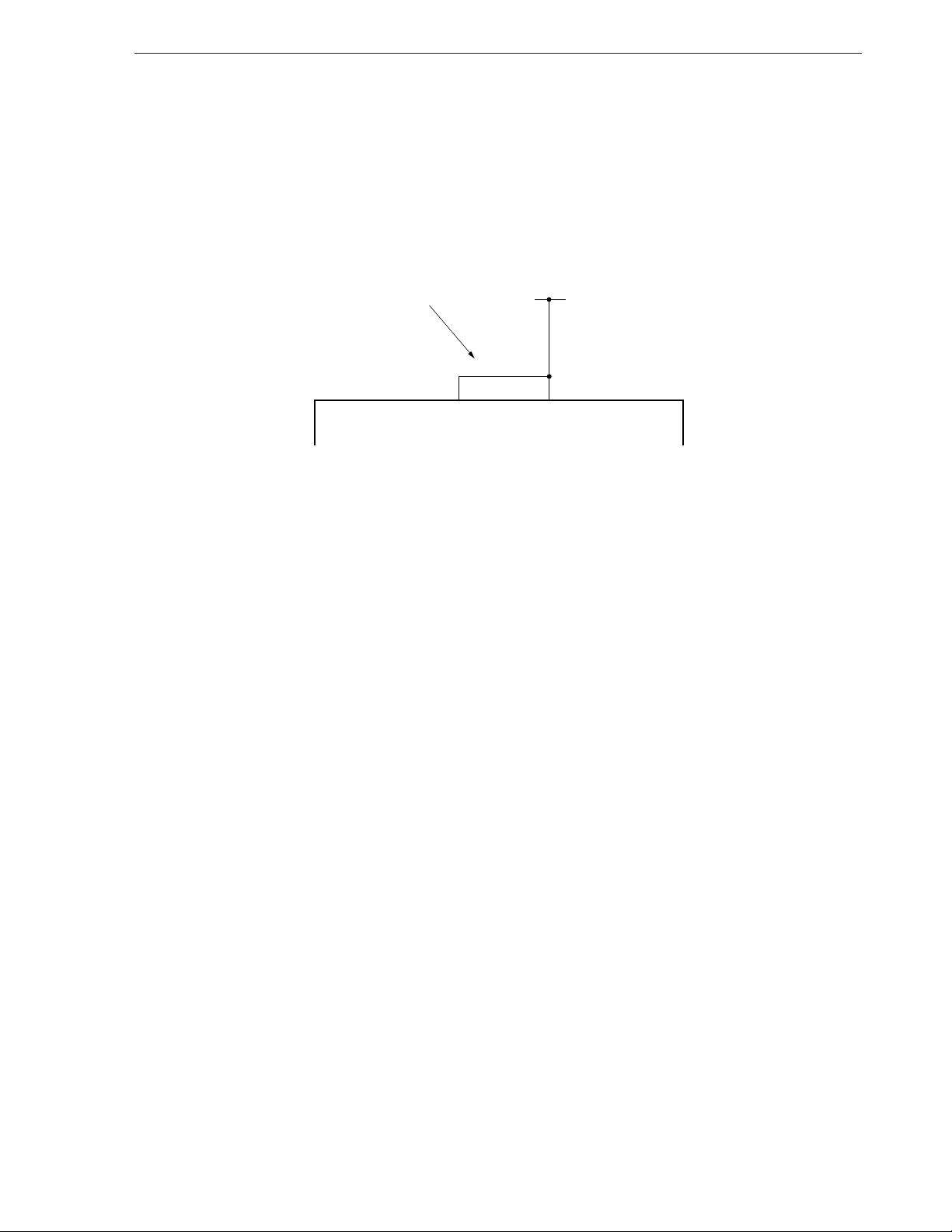

2.2.12 IC

The IC (Internally Connected) pin sets the test mode in which the µPD754244 is tested before shipment. Usually,

you should directly connect the IC pin to the V

If a voltage difference is generated between the IC and V

DD pin with as short a wiring length as possible.

DD pins because the wiring length is too long, or because

external noise is superimposed on the IC pin, your program may not be correctly executed.

2.2.13 VDD

Positive power supply pin.

2.2.14 V

SS

GND.

• Directly connect the IC pin to the V

Keep as short

as possible.

IC

V

DD

V

DD

DD pin.

User’s Manual U10676EJ3V0UM

29

Page 30

CHAPTER 2 PIN FUNCTIONS

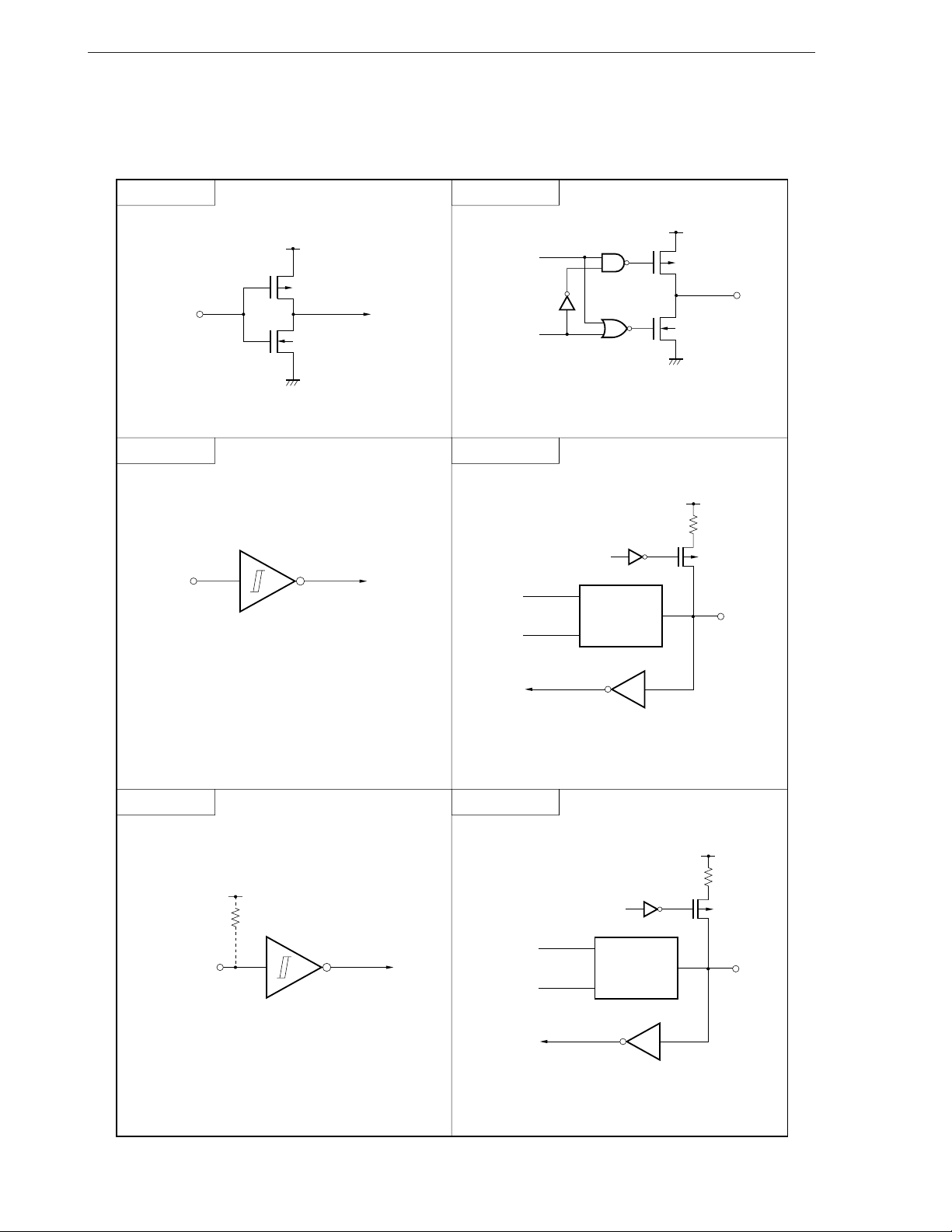

2.3 Pin I/O Circuits

The following diagrams show the I/O circuits of the pins of the µPD754244. Note that in these diagrams the I/

O circuits have been slightly simplified.

Type A

IN

CMOS specification input buffer.

Type B

IN

Type D

V

V

DD

Data

P-ch

N-ch

Output

disable

DD

P-ch

OUT

N-ch

Push-pull output that can be placed in output

high-impedance (both P-ch, N-ch off).

Type E-B

DD

V

P.U.R.

Data

Output

P.U.R.

enable

Type D

P-ch

IN/OUT

disable

Schmitt-triggered input with hysteresis characteristics.

Type B-A

DD

V

P.U.R (Mask Option)

IN

P.U.R. : Pull-Up Resistor

Type F-A

Output

disable

Data

Type A

P.U.R. : Pull-Up Resistor

P.U.R.

enable

Type D

Type B

P.U.R. : Pull-Up Resistor

V

DD

P.U.R.

P-ch

IN/OUT

30 User’s Manual U10676EJ3V0UM

Page 31

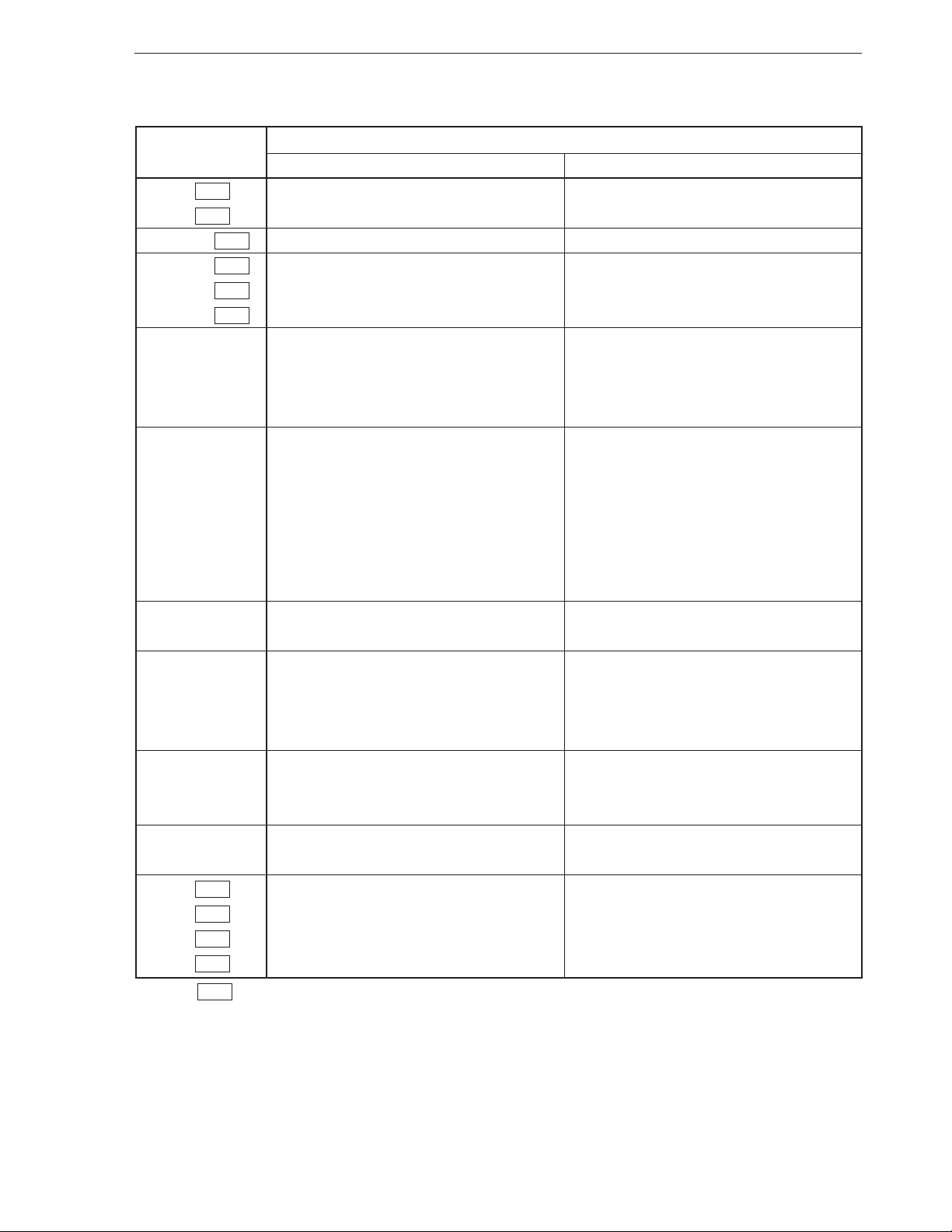

2.4 Processing of Unused Pins

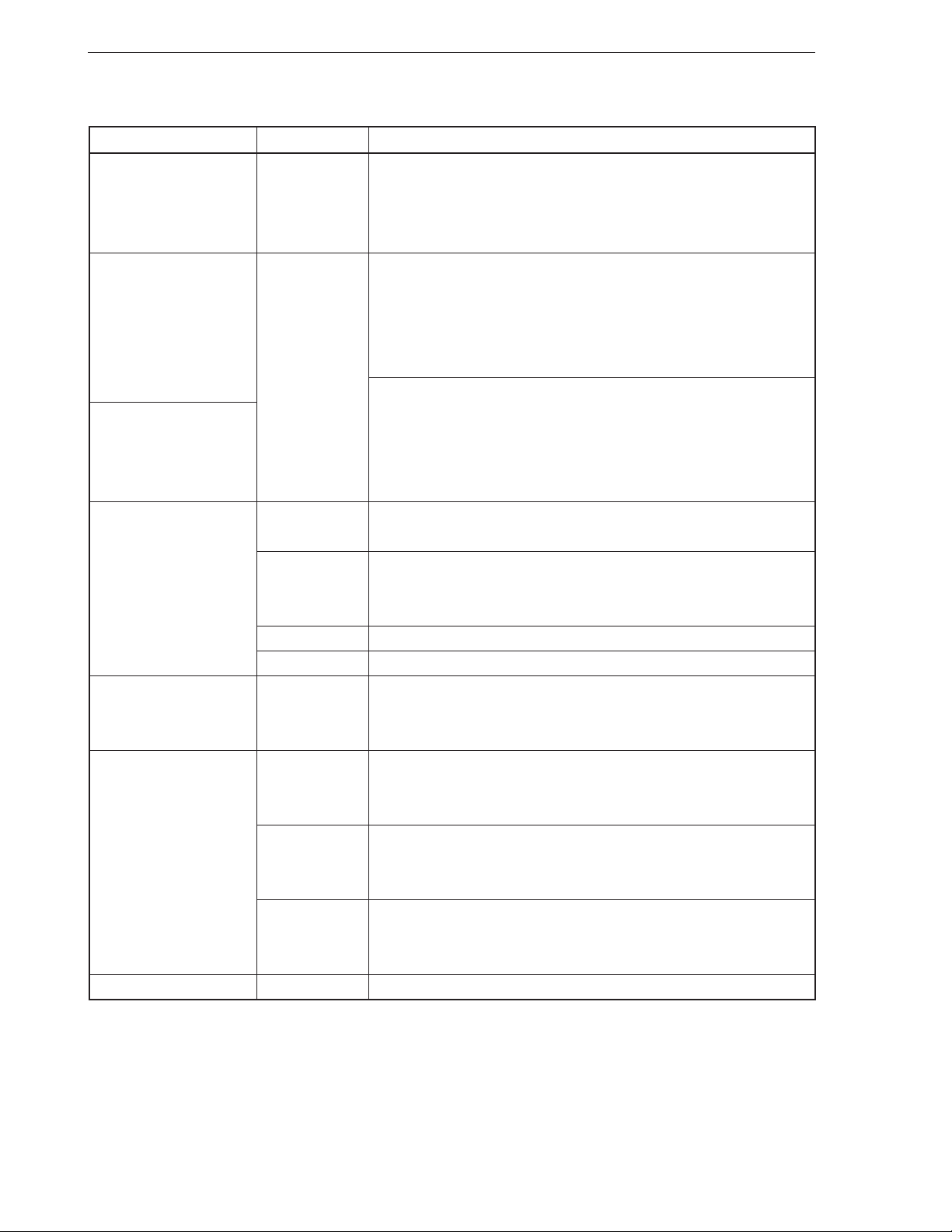

Table 2-3. Recommended Connection of Unused Pins

Pin Recommended Connection

P30/PTO0 Input: Independently connect to VSS or VDD via a resistor.

P31/PTO1

P32/PTO2

P33

P60/AVREF

P61/INT0

P62/PTH00

P63/PTH01

P70/KR4 Connect to VDD.

P71/KR5

P72/KR6

CHAPTER 2 PIN FUNCTIONS

Output: Leave open.

P73/KR7

P80 Input: Independently connect to VSS or VDD via a resistor.

Output: Leave open.

KRREN When this pin is connected to VDD, the internal reset signal is

generated at the falling edge of the KRn pin in the STOP mode.

When this pin is connected to VSS, the internal reset signal is not

generated even if the falling edge of the KRn pin is detected in the

STOP mode.

IC Connect directly to VDD.

User’s Manual U10676EJ3V0UM

31

Page 32

CHAPTER 3 FEATURES OF ARCHITECTURE AND MEMORY MAP

The 75XL architecture employed for the µPD754244 has the following features.

• Internal RAM: 4K words × 4 bits MAX. (12-bit address)

• Expandability peripheral hardware

To realize these superb features, the following techniques have been employed.

(1) Bank configuration of data memory

(2) Bank configuration of general-purpose registers

(3) Memory mapped I/O

This chapter describes these features.

3.1 Bank Configuration of Data Memory and Addressing Modes

3.1.1 Bank configuration of data memory

The µPD754244 is provided with a static RAM at the addresses 000H to 07FH of memory bank 0 of the data memory

space. EEPROM (16 × 8 bits) is allocated to addresses 400H to 41FH of memory bank 4, and peripheral hardware

units (such as I/O ports and timers) are allocated to addresses F80H to FFFH of memory bank 15.

µ

PD754244 employs a memory bank configuration that directly or indirectly specifies the lower 8 bits of an

The

address by an instruction and the higher 4 bits of the address by a memory bank, to address the data memory space

of 12-bit address (4K words × 4 bits).

To specify a memory bank (MB), the following hardware units are provided.

• Memory bank enable flag (MBE)

• Memory bank select register (MBS)

MBS is a register that selects a memory bank. Memory banks 0, 4, and 15 can be set. MBE is a flag that enables

or disables the memory bank selected by MBS. When MBE is 0, the specified memory bank (MB) is fixed, regardless

of MBS, as shown in Figure 3-1. When MBE is 1, however, a memory bank is selected according to the setting of

MBS, so that the data memory space can be expanded.

To address the data memory space, MBE is usually set to 1 and the data memory of the memory bank specified

by MBS is manipulated. By selecting the mode of MBE = 0 or the mode of MBE = 1 for each processing of the program,

programming can be efficiently carried out.

Adapted Program Processing Effect

MBE = 0 mode • Interrupt servicing Saving/restoring MBS unnecessary

• Processing repeating internal hardware Changing MBS unnecessary

manipulation and stack RAM manipulation

• Subroutine processing Saving/restoring MBS unnecessary

MBE = 1 mode • Normal program processing

32 User’s Manual U10676EJ3V0UM

Page 33

CHAPTER 3 FEATURES OF ARCHITECTURE AND MEMORY MAP

Figure 3-1. Selecting MBE = 0 Mode and MBE = 1 Mode

<Main program>

SET 1 MBE

<Subroutine>

CLR1 MBE

RET

MBE = 0

(Interrupt servicing)

; MBE = 0 by vector table

MBE = 0

RETI

Internal hardware

and static RAM

manipulation

repeated.

MBE

= 1

CLR 1 MBE

MBE

= 0

SET 1 MBE

MBE

= 1

Remark Solid line: MBE = 1, dotted line: MBE = 0

Because MBE is automatically saved or restored during subroutine processing, it can be changed even while

subroutine processing is being executed. MBE can also be saved or restored automatically during interrupt servicing,

so that MBE during interrupt servicing can be specified as soon as the interrupt servicing is started, by setting the

interrupt vector table. This feature is useful for high-speed interrupt servicing.

To change MBS by using subroutine processing or interrupt servicing, save or restore it to the stack by using the

PUSH or POP instruction.

MBE is set by using the SET1 or CLR1 instruction. Use the SEL instruction to set MBS.

Examples 1. To clear MBE and fix memory bank

CLR1 MBE ; MBE ← 0

2. To select memory bank 4

SET1 MBE ; MBE ← 1

SEL MB4 ; MBE ← 4

User’s Manual U10676EJ3V0UM

33

Page 34

CHAPTER 3 FEATURES OF ARCHITECTURE AND MEMORY MAP

3.1.2 Addressing mode of data memory

The 75XL architecture employed for the µPD754244 provides the seven types of addressing modes shown in Table

3-1. This means that the data memory space can be efficiently addressed by the bit length of the data to be processed

and that programming can be carried out efficiently.

(1) 1-bit direct addressing (mem.bit)

This mode is used to directly address each bit of the entire data memory space by using the operand of an

instruction.

The memory bank (MB) to be specified is fixed to 0 in the mode of MBE = 0 if the address specified by the

operand ranges from 00H to 7FH, and to 15 if the address specified by the operand is 80H to FFH. In the

mode of MBE = 0, therefore, both the data area of addresses 000H to 07FH and the peripheral hardware area

of F80H to FFFH can be addressed.

In the mode of MBE = 1, MB = MBS; therefore, the entire data memory space can be addressed.

This addressing mode can be used with four instructions: the bit set and reset instructions (SET1 and CLR1),

and the two bit test (SKT and SKF).

Example To set FLAG1, reset FLAG2, and test whether FLAG3 is 0

FLAG1 EQU 03FH.1 ; Bit 1 of address 3FH

FLAG2 EQU 057H.2 ; Bit 2 of address 57H

FLAG3 EQU 077H.0 ; Bit 0 of address 77H

SET1 MBE ; MBE ← 1

SEL MB0 ; MBS ← 0

SET1 FLAG1 ; FLAG1 ← 1

CLR1 FLAG2 ; FLAG2 ← 0

SKF FLAG3 ; FLAG3 = 0?

34 User’s Manual U10676EJ3V0UM

Page 35

CHAPTER 3 FEATURES OF ARCHITECTURE AND MEMORY MAP

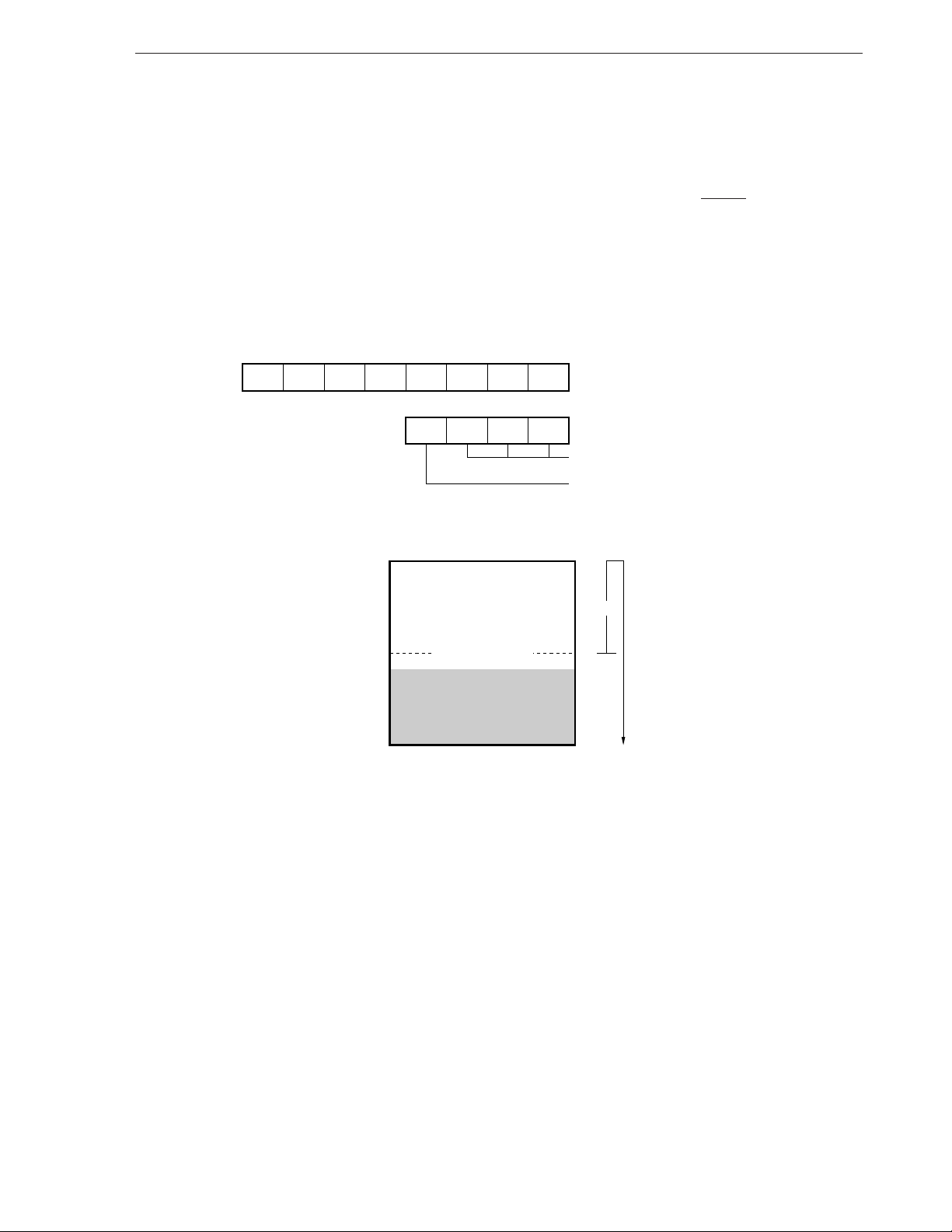

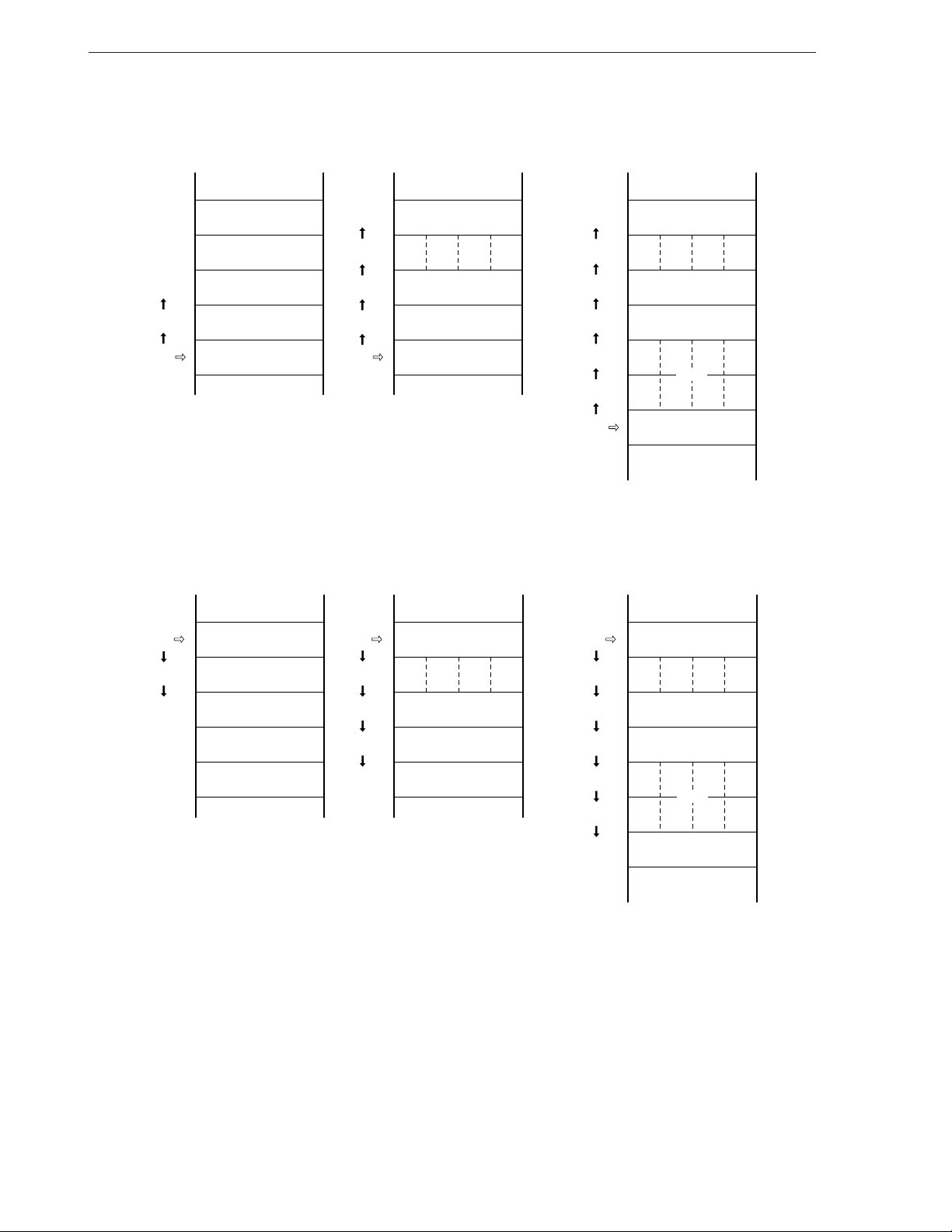

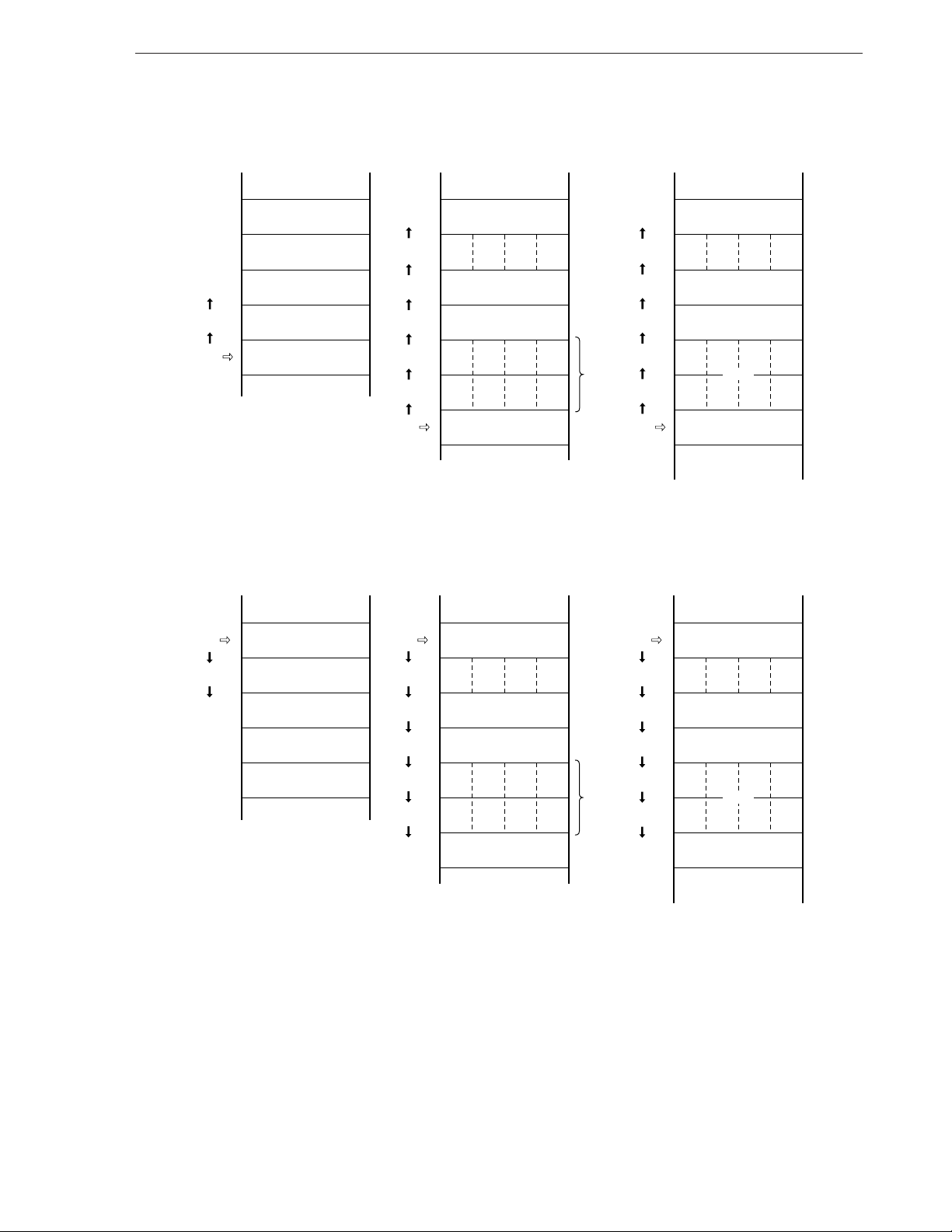

Figure 3-2. Data Memory Configuration and Addressing Range for Each Addressing Mode

Addressing mode

mem

mem. bit

@HL

@H+mem. bit

@DE

@DL

Stack

addressing

fmem. bit