Page 1

µ

PD17134A SUBSERIES

4-BIT SINGLE-CHIP MICROCONTROLLER

µ

PD17134A

µ

PD17135A

µ

PD17136A

µ

PD17137A

µ

PD17P136A

µ

PD17P137A

Document No. U11607EJ3V0UM00 (3rd edition)

Date Published December 1996 N

©

1993

Printed in Japan

Page 2

NOTES FOR CMOS DEVICES

1 PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and

ultimately degrade the device operation. Steps must be taken to stop generation of static electricity

as much as possible, and quickly dissipate it once, when it has occurred. Environmental control

must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using

insulators that easily build static electricity. Semiconductor devices must be stored and transported

in an anti-static container, static shielding bag or conductive material. All test and measurement

tools including work bench and floor should be grounded. The operator should be grounded using

wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions

need to be taken for PW boards with semiconductor devices on it.

2 HANDLING OF UNUSED INPUT PINS FOR CMOS

Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided

to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence

causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input

levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each

unused pin should be connected to V

possibility of being an output pin. All handling related to the unused pins must be judged device

by device and related specifications governing the devices.

DD or GND with a resistor, if it is considered to have a

3 STATUS BEFORE INITIALIZATION OF MOS DEVICES

Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS

does not define the initial operation status of the device. Immediately after the power source is

turned ON, the devices with reset function have not yet been initialized. Hence, power-on does

not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until

the reset signal is received. Reset operation must be executed immediately after power-on for

devices having reset function.

Page 3

Regional Information

Some information contained in this document may vary from country to country. Before using any NEC

product in your application, please contact the NEC office in your country to obtain a list of authorized

representatives and distributors. They will verify:

• Device availability

• Ordering information

• Product release schedule

• Availability of related technical literature

• Development environment specifications (for example, specifications for third-party tools and

components, host computers, power plugs, AC supply voltages, and so forth)

• Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary

from country to country.

NEC Electronics Inc. (U.S.)

Santa Clara, California

Tel: 800-366-9782

Fax: 800-729-9288

NEC Electronics (Germany) GmbH

Duesseldorf, Germany

Tel: 0211-65 03 02

Fax: 0211-65 03 490

NEC Electronics (UK) Ltd.

Milton Keynes, UK

Tel: 01908-691-133

Fax: 01908-670-290

NEC Electronics Italiana s.r.1.

Milano, Italy

Tel: 02-66 75 41

Fax: 02-66 75 42 99

NEC Electronics (Germany) GmbH

Benelux Office

Eindhoven, The Netherlands

Tel:040-2445845

Fax: 040-2444580

NEC Electronics (France) S.A.

Velizy-Villacoublay, France

Tel:01-30-67 58 00

Fax: 01-30-67 58 99

NEC Electronics (France) S.A.

Spain Office

Madrid, Spain

Tel: 01-504-2787

Fax: 01-504-2860

NEC Electronics (Germany) GmbH

Scandinavia Office

Taeby, Sweden

Tel: 08-63 80 820

Fax: 08-63 80 388

NEC Electronics Hong Kong Ltd.

Hong Kong

Tel:2886-9318

Fax: 2886-9022/9044

NEC Electronics Hong Kong Ltd.

Seoul Branch

Seoul, Korea

Tel: 02-528-0303

Fax: 02-528-4411

NEC Electronics Singapore Pte. Ltd.

United Square, Singapore 1130

Tel:253-8311

Fax: 250-3583

NEC Electronics Taiwan Ltd.

Taipei, Taiwan

Tel: 02-719-2377

Fax: 02-719-5951

NEC do Brasil S.A.

Sao Paulo-SP, Brasil

Tel: 011-889-1680

Fax: 011-889-1689

J96. 8

Page 4

SIMPLEHOST

is a trademark of NEC Corp.

MS-DOS and Windows are trademarks of Microsoft Corp.

PC/AT and PC DOS are trademarks of IBM Corp.

The export of this product from Japan is prohibited without governmental license. To export or re-export this product from

a country other than Japan may also be prohibited without a license from that country. Please call an NEC sales

representative.

The information in this document is subject to change without notice.

No part of this document may be copied or reproduced in any form or by any means without the prior written

consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in

this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property

rights of third parties by or arising from use of a device described herein or any other liability arising from use

of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other

intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices,

the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or

property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety

measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a

customer designated “quality assurance program“ for a specific application. The recommended applications of

a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device

before using it in a particular application.

Standard: Computers, office equipment, communications equipment, test and measurement equipment,

audio and visual equipment, home electronic appliances, machine tools, personal electronic

equipment and industrial robots

Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster

systems, anti-crime systems, safety equipment and medical equipment (not specifically designed

for life support)

Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life

support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books.

If customers intend to use NEC devices for applications other than those specified for Standard quality grade,

they should contact an NEC sales representative in advance.

Anti-radioactive design is not implemented in this product.

M7 96.5

Page 5

Major Revisions in This Edition

Page Description

Throughout Change of name µPD1713XA to µPD17134A subseries

p. 5 Correction of (2) Program memory write/verify mode in 1.4 PIN CONFIGURATION

p. 18 Change of Figure 3-2 Value of Program Counter after Instruction

Partial correction of 3.2.2 On Execution of Branch Instruction (BR)

p. 19 Partial correction of 3.2.3 On During Execution of Subroutine Call

p. 23 Change of CHAPTER 4 PROGRAM MEMORY (ROM)

p. 31 Partial correction of Figure 5-1 Data Memory Configuration

p. 35 Change of CHAPTER 6 STACK

p. 43 Partial correction of 7.2.2 Address Register Functions

p. 47 Change of 7.5 INDEX REGISTER (IX) AND DATA MEMORY ROW ADDRESS

POINTER (MEMORY POINTER: MP)

p. 58 Partial change of 7.6.2 Functions of General Register Pointer

p. 59 Partial change of 7.7.1 Program Status Word Configuration

p. 61 Change of 7.7.4 Zero Flag (Z) and Compare Flag (CMP)

p. 61 Partial correction of 7.7.5 Carry Flag (CY)

p. 71 Partial correction of 9.2.3 Register File Manipulation Instructions

p. 111 Change of CHAPTER 13 PERIPHERAL HARDWARE

p. 149 Change of CHAPTER 14 INTERRUPT FUNCTIONS

p. 169 Change of CHAPTER 16 STANDBY FUNCTION

p. 179 Change of CHAPTER 17 RESET

p. 190 Partial change of Table 18-2 Differences between Mask ROM Version and One-

Time PROM Version

p. 194 Partial change of 19.3 LIST OF THE INSTRUCTION SET

p. 198 Partial change of 19.5 INSTRUCTIONS

p. 255 Change of CHAPTER 20 ASSEMBLER RESERVED WORDS

p. 257 Partial change of 20.2 RESERVED SYMBOLS

p. 261 Addition of APPENDIX A DEVELOPMENT OF µPD171×× SUBSERIES

p. 263 Addition of APPENDIX B COMPARISON OF FUNCTIONS BETWEEN µPD17135A,

17137A, AND µPD17145 SUBSERIES

p. 267 Addition of APPENDIX D NOTES ON CONFIGURATION OF SYSTEM CLOCK

OSCILLATION CIRCUIT

The mark shows major revisions made in this edition.

Page 6

PREFACE

Target : This manual is intended for user engineers who understand the functions of each product in

the µPD17134A subseries and try to design application systems using the µPD17134A

subseries.

Purpose : The purpose of this manual is for the user to understand the hardware functions of the

µ

PD17134A subseries.

Use : The manual assumes that the reader has a general knowledge of electricity, logic circuits,

microcomputers.

µ

• To understand the functions of the

→ Read the manual from CONTENTS.

• To look up instruction functions in detail when you know the mnemonic of an

instruction;

→ Use APPENDIX E INSTRUCTION LIST.

• To look up an instruction when you do not know its mnemonic but know outlines of

the function;

→ Refer to 19.3 LIST OF THE INSTRUCTION SET for search for the mnemonic of the

instruction, then see 19.5 INSTRUCTIONS for the functions.

PD17134A subseries in a general way;

µ

• To learn the electrical specifications of the

PD17134A subseries

→ Refer to the Data Sheet available separately.

µ

• To learn the application examples of the functions of the

PD17134A subseries

→ Refer to the Application Note available separately.

Legend : Data representation weight : High-order and low-order digits are indicated from left to right.

Active low representation : ××× (pin or signal name is overlined)

Memory map address : Top: low-order, bottom: high-order

Note

Note : Explanation of

in the text

Caution : Caution to which you should pay attention

Remark : Supplementary explanation to the text

Number representation : Binary number ...×××× or ××××B

Decimal number ...××××

Hexadecimal number ...××××H

Page 7

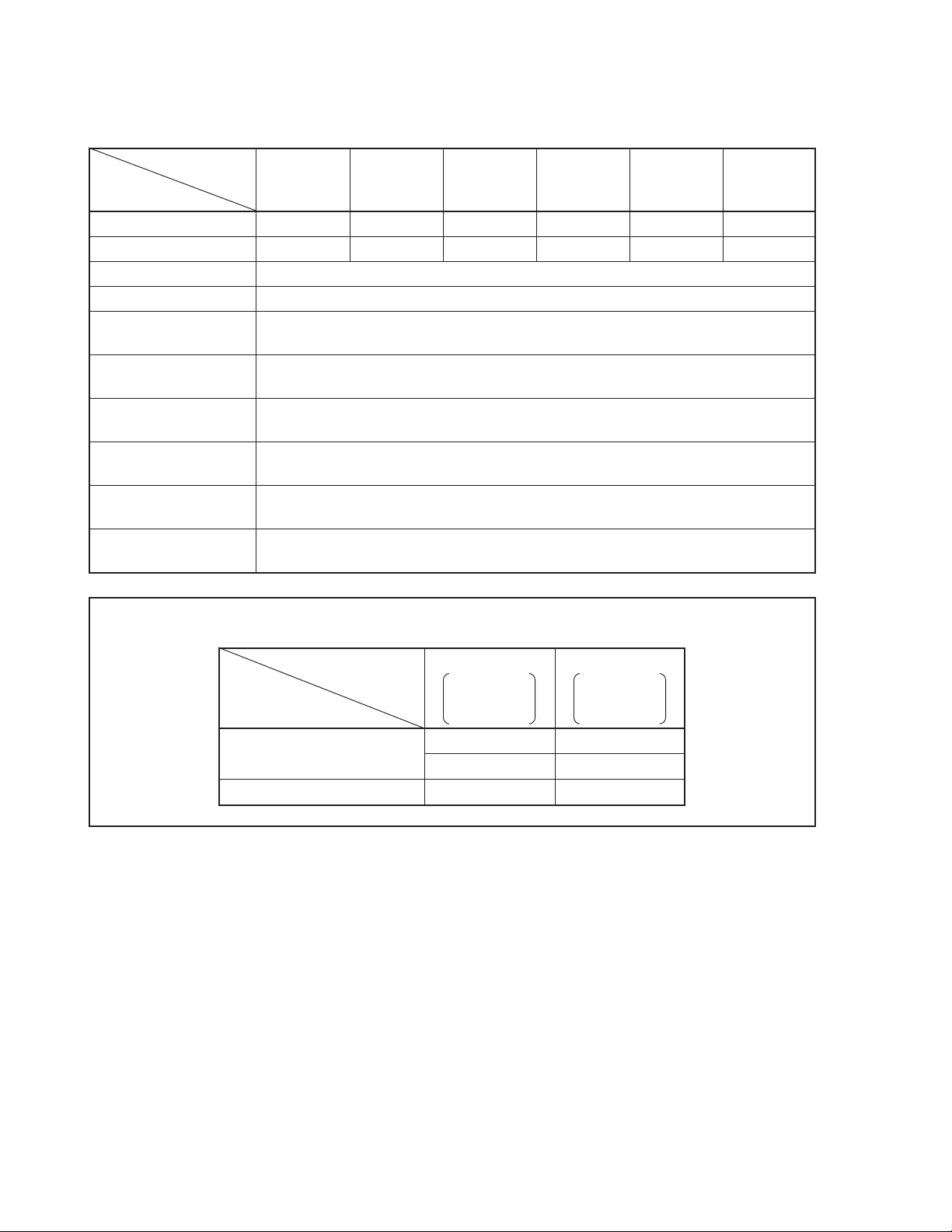

Related Documents : The following documents are provided for the µPD17134A subseries.

The numbers listed in the table are the document numbers.

Product name

µ

PD17134AµPD17135AµPD17136AµPD17137AµPD17P136AµPD17P137A

Document name

Brochure IF-1166 IF-1169 IF-1166 IF-1169 IF-1168 IF-1165

Data sheet U10591E U10592E U10591E U10592E IC-2871 IC-2872

User’s manual IEU-1369

Application note IEA-1297 (Introduction), IEA-1293 (Rice cooker, thermos bottle)

IE-17K (Ver. 1.6) EEU-1467

user’s manual

IE-17K-ET (Ver. 1.6) EEU-1466

user’s manual

SE board EEU-1379

user’s manual

SIMPLEHOST

user’s manual

AS17K assembler EEU-1287

user’s manual

Device file U10777E

user’s manual

TM

EEU-1336 (Introduction), EEU-1337 (Reference)

Pin name and symbol name should be read according to the system clock type.

System clock RC oscillation Ceramic oscillation

µ

PD17134A

µ

PD17136A

Pin name, symbol name

Pin for system clock oscillation OSC1 XIN

System clock fCC fX

µ

PD17P136A

OSC0 XOUT

µ

PD17135A

µ

PD17137A

µ

PD17P137A

Page 8

TABLE OF CONTENTS

CHAPTER 1 GENERAL DESCRIPTION ................................................................................................. 1

1.1 FUNCTION LIST ........................................................................................................................................ 2

1.2 ORDERING INFORMATION ..................................................................................................................... 3

1.3 BLOCK DIAGRAM .................................................................................................................................... 4

1.4 PIN CONFIGURATION (TOP VIEW) ........................................................................................................ 5

CHAPTER 2 PIN FUNCTIONS ............................................................................................................... 9

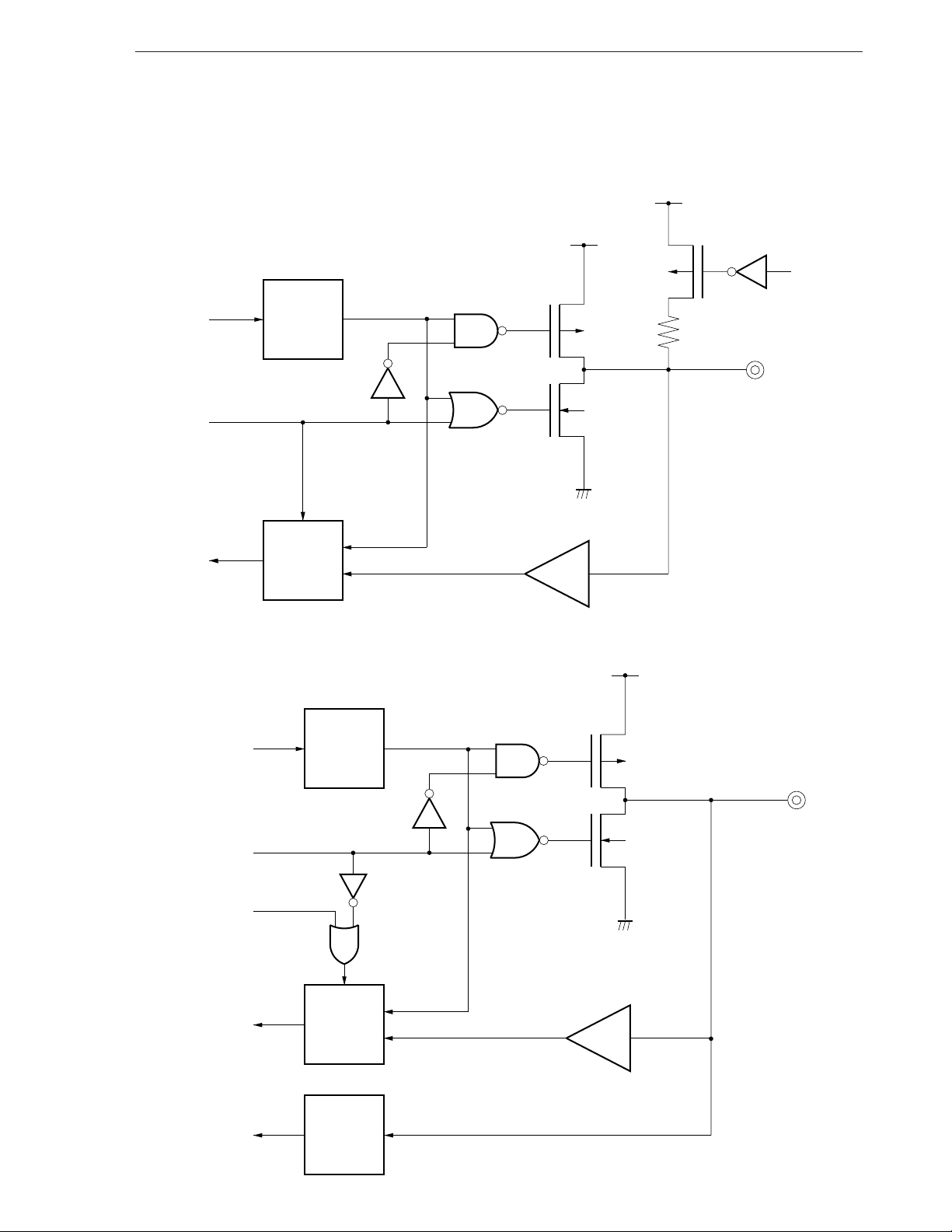

2.1 PIN FUNCTIONS ....................................................................................................................................... 9

2.2 PIN INPUT/OUTPUT CIRCUIT ............................................................................................................... 11

2.3 PROCESSING OF UNUSED PINS ......................................................................................................... 14

2.4 NOTES ON USING RESET PIN AND P1B

0 PIN ................................................................................... 15

CHAPTER 3 PROGRAM COUNTER (PC) ........................................................................................... 17

3.1 PROGRAM COUNTER CONFIGURATION............................................................................................ 17

3.2 PROGRAM COUNTER OPERATION ..................................................................................................... 17

3.2.1 At Reset ..................................................................................................................................... 18

3.2.2 During Execution of the Branch Instruction (BR)..................................................................... 18

3.2.3 During Execution of Subroutine Calls (CALL).......................................................................... 1 9

3.2.4 During Execution of Return Instructions (RET, RETSK, RETI)............................................... 20

3.2.5 During Table Reference (MOVT) .............................................................................................. 20

3.2.6 During Execution of Skip Instructions (SKE, SKGE, SKLT, SKNE, SKT, SKF)...................... 21

3.2.7 When an Interrupt Is Received ................................................................................................. 2 1

CHAPTER 4 PROGRAM MEMORY (ROM) .......................................................................................... 23

4.1 PROGRAM MEMORY CONFIGURATION ............................................................................................. 23

4.2 PROGRAM MEMORY USAGE ............................................................................................................... 24

4.2.1 Flow of the Program.................................................................................................................. 24

4.2.2 Table Reference......................................................................................................................... 27

CHAPTER 5 DATA MEMORY (RAM) .................................................................................................... 31

5.1 DATA MEMORY CONFIGURATION....................................................................................................... 31

5.1.1 System Register (SYSREG) ..................................................................................................... 32

5.1.2 Data Buffer (DBF)...................................................................................................................... 32

5.1.3 General Register (GR) .............................................................................................................. 33

5.1.4 Port Registers............................................................................................................................ 33

5.1.5 General Data Memory ............................................................................................................... 34

5.1.6 Unmounted Data Memory ......................................................................................................... 3 4

- i -

Page 9

CHAPTER 6 STACK .............................................................................................................................. 3 5

6.1 STACK CONFIGURATION ...................................................................................................................... 35

6.2 FUNCTIONS OF THE STACK ................................................................................................................ 35

6.3 ADDRESS STACK REGISTERS (ASRs)............................................................................................... 3 6

6.4 INTERRUPT STACK REGISTERS (INTSKs) ........................................................................................ 36

6.5 STACK POINTER (SP) AND INTERRUPT STACK REGISTERS ........................................................ 37

6.6 STACK OPERATION ............................................................................................................................... 38

6.6.1 On Execution of Instructions CALL, RET, RETSK................................................................... 38

6.6.2 Table Reference (MOVT DBF, @AR Instruction) ..................................................................... 3 8

6.6.3 Operation on Execution of Interrupt Receipt and RETI Instruction ......................................... 39

6.7 STACK NESTING LEVELS AND THE PUSH AND POP INSTRUCTIONS ......................................... 39

CHAPTER 7 SYSTEM REGISTER (SYSREG) .................................................................................... 41

7.1 SYSTEM REGISTER CONFIGURATION............................................................................................... 41

7.2 ADDRESS REGISTER (AR) ................................................................................................................... 43

7.2.1 Address Register Configuration................................................................................................ 43

7.2.2 Address Register Functions...................................................................................................... 43

7.3 WINDOW REGISTER (WR) .................................................................................................................... 45

7.3.1 Window Register Configuration ................................................................................................ 45

7.3.2 Window Register Functions ...................................................................................................... 45

7.4 BANK REGISTER (BANK) ..................................................................................................................... 46

7.4.1 Bank Register Configuration ..................................................................................................... 46

7.4.2 Functions of Bank Register....................................................................................................... 46

7.5 INDEX REGISTER (IX) AND DATA MEMORY ROW ADDRESS POINTER

(MEMORY POINTER: MP)...................................................................................................................... 47

7.5.1 Index Register (IX) .................................................................................................................... 47

7.5.2 Data Memory Row Address Pointer (Memory Pointer: MP).................................................... 47

7.5.3 IXE = 0 and MPE = 0 (No Data Memory Modification) ........................................................... 49

7.5.4 IXE = 0 and MPE = 1 (Diagonal Indirect Data Transfer)......................................................... 51

7.5.5 IXE = 1 and MPE = 0 (Index Modification) ............................................................................... 53

7.6 GENERAL REGISTER POINTER (RP) .................................................................................................. 57

7.6.1 General Register Pointer Configuration ................................................................................... 57

7.6.2 Functions of the General Register Pointer............................................................................... 58

7.7 PROGRAM STATUS WORD (PSWORD) ............................................................................................... 59

7.7.1 Program Status Word Configuration......................................................................................... 5 9

7.7.2 Functions of the Program Status Word .................................................................................... 60

7.7.3 Index Enable Flag (IXE)............................................................................................................ 61

7.7.4 Zero Flag (Z) and Compare Flag (CMP) .................................................................................. 61

7.7.5 Carry Flag (CY) ......................................................................................................................... 61

7.7.6 Binary-Coded Decimal Flag (BCD)........................................................................................... 6 2

7.7.7 Notes Concerning Use of Arithmetic Operations ..................................................................... 62

7.8 NOTES CONCERNING USE OF THE SYSTEM REGISTER ............................................................... 6 3

7.8.1 Reserved Words for the System Register................................................................................ 63

7.8.2 Handling of System Register Addresses Fixed at 0 ................................................................ 6 5

- ii -

Page 10

CHAPTER 8 GENERAL REGISTER (GR) ........................................................................................... 67

8.1 GENERAL REGISTER CONFIGURATION ............................................................................................ 67

8.2 FUNCTIONS OF THE GENERAL REGISTER....................................................................................... 67

CHAPTER 9 REGISTER FILE (RF)...................................................................................................... 69

9.1 REGISTER FILE CONFIGURATION ...................................................................................................... 69

9.1.1 Configuration of the Register File............................................................................................. 69

9.1.2 Relationship between the Register File and Data Memory..................................................... 69

9.2 FUNCTIONS OF THE REGISTER FILE................................................................................................. 70

9.2.1 Functions of the Register File................................................................................................... 70

9.2.2 Functions of Control Register ................................................................................................... 70

9.2.3 Register File Manipulation Instructions .................................................................................... 71

9.3 CONTROL REGISTER ............................................................................................................................ 72

9.4 NOTES CONCERNING USE OF THE REGISTER FILE....................................................................... 73

9.4.1 Notes Concerning Operation of the Control Register (Read-Only and Unused Registers) ... 73

9.4.2 Register File Symbol Definitions and Reserved Words........................................................... 7 3

CHAPTER 10 DATA BUFFER (DBF) ................................................................................................... 77

10.1 DATA BUFFER CONFIGURATION ........................................................................................................ 7 7

10.2 FUNCTIONS OF THE DATA BUFFER ................................................................................................... 78

10.2.1 Data Buffer and Peripheral Hardware ...................................................................................... 7 9

10.2.2 Data Transfer with Peripheral Hardware.................................................................................. 80

10.2.3 Table Reference......................................................................................................................... 81

CHAPTER 11 ARITHMETIC AND LOGIC UNIT (ALU) ....................................................................... 83

11.1 ALU BLOCK CONFIGURATION ............................................................................................................ 83

11.2 FUNCTIONS OF THE ALU BLOCK ....................................................................................................... 83

11.2.1 Functions of the ALU................................................................................................................. 83

11.2.2 Functions of Temporary Registers A and B.............................................................................. 88

11.2.3 Functions of the Status Flip-flop............................................................................................... 88

11.2.4 Operations in 4-Bit Binary ......................................................................................................... 89

11.2.5 Operations in BCD ..................................................................................................................... 89

11.2.6 Operations in the ALU Block..................................................................................................... 9 0

11.3 ARITHMETIC OPERATIONS (ADDITION AND SUBTRACTION IN 4-BIT BINARY AND BCD) ....... 91

11.3.1 Addition and Subtraction When CMP = 0 and BCD = 0.......................................................... 9 1

11.3.2 Addition and Subtraction When CMP = 1 and BCD = 0.......................................................... 9 1

11.3.3 Addition and Subtraction When CMP = 0 and BCD = 1.......................................................... 9 2

11.3.4 Addition and Subtraction When CMP = 1 and BCD = 1.......................................................... 9 2

11.3.5 Notes Concerning Use of Arithmetic Operations ..................................................................... 92

11.4 LOGICAL OPERATIONS ........................................................................................................................ 93

11.5 BIT JUDGEMENTS ................................................................................................................................. 94

11.5.1 TRUE (1) Bit Judgement ........................................................................................................... 94

11.5.2 FALSE (0) Bit Judgement ......................................................................................................... 95

- iii -

Page 11

11.6 COMPARISON JUDGEMENTS .............................................................................................................. 96

11.6.1 “Equal to” Judgement ................................................................................................................ 96

11.6.2 “Not Equal to” Judgement ......................................................................................................... 97

11.6.3 “Greater Than or Equal to” Judgement .................................................................................... 97

11.6.4 “Less Than” Judgement ............................................................................................................ 98

11.7 R OTATIONS ............................................................................................................................................. 99

11.7.1 Rotation to the Right ................................................................................................................. 99

11.7.2 Rotation to the Left.................................................................................................................. 100

CHAPTER 12 PORTS ......................................................................................................................... 1 01

12.1 PORT 0A (P0A0, P0A1, P0A2, P0A3).................................................................................................... 10 1

12.2 PORT 0B (P0B0, P0B1, P0B2, P0B3).................................................................................................... 10 2

12.3 PORT 0C (P0C0/ADC0, P0C1/ADC1, P0C2/ADC2, P0C3/ADC3) .......................................................... 103

12.4 PORT 0D (P0D

12.5 PORT 1A (P1A0, P1A1, P1A2, P1A3).................................................................................................... 10 5

12.6 PORT 1B (P1B0).................................................................................................................................... 105

12.7 PORT CONTROL REGISTER ............................................................................................................... 106

12.7.1 Input/Output Switching by Group I/O...................................................................................... 106

12.7.2 Input/Output Switching by Bit I/O ........................................................................................... 107

12.7.3 Specifying Pull-Up Resistor Incorporation Using Software ................................................... 109

0/SCK, P0D1/SO, P0D2/SI, P0D3/TM0OUT)................................................................ 104

CHAPTER 13 PERIPHERAL HARDWARE ......................................................................................... 111

13.1 8-BIT TIMERS/COUNTERS (TM0 and TM1)........................................................................................111

13.1.1 8-Bit Timers/Counters Configuration .......................................................................................111

13.1.2 Operation of 8-Bit Timers/Counters........................................................................................ 115

13.1.3 Selecting Count Pulse ............................................................................................................. 115

13.1.4 Setting Count Value to Modulo Register................................................................................ 116

13.1.5 Reading Value of Count Register ........................................................................................... 117

13.1.6 Setting of Interval Time ........................................................................................................... 118

13.1.7 Error of Interval Time............................................................................................................... 119

13.1.8 Timer 0 Output......................................................................................................................... 121

13.2 BASIC INTERVAL TIMER (BTM) ......................................................................................................... 122

13.2.1 Basic Interval Timer Configuration .......................................................................................... 122

13.2.2 Registers Controlling Basic Interval Timer ............................................................................. 123

13.2.3 Operation of Basic Interval Timer ........................................................................................... 124

13.2.4 Watchdog Timer Function ....................................................................................................... 125

13.3 A/D CONVERTER ................................................................................................................................. 128

13.3.1 A/D Converter Configuration ................................................................................................... 128

13.3.2 Functions of A/D Converter..................................................................................................... 129

13.3.3 Setting Values in the 8-bit Data Register (ADCR) ................................................................. 132

13.3.4 Reading Values from the 8-bit Data Register (ADCR) .......................................................... 133

13.3.5 A/D Converter Operation......................................................................................................... 134

13.4 SERIAL INTERFACE (SIO) .................................................................................................................. 141

13.4.1 Functions of the Serial Interface............................................................................................. 141

13.4.2 3-wire Serial Interface Operation Modes................................................................................ 14 3

13.4.3 Setting Values in the Shift Register........................................................................................ 147

13.4.4 Reading Values from the Shift Register ................................................................................. 148

- iv -

Page 12

CHAPTER 14 INTERRUPT FUNCTIONS............................................................................................ 14 9

14.1 INTERRUPT SOURCE TYPES AND VECTOR ADDRESSES............................................................ 15 0

14.2 HARDWARE COMPONENTS OF THE INTERRUPT CONTROL CIRCUIT ....................................... 151

14.3 INTERRUPT SEQUENCE ..................................................................................................................... 158

14.3.1 Receiving an Interrupt ............................................................................................................. 158

14.3.2 Return from the Interrupt Routine........................................................................................... 159

14.3.3 Interrupt Accepting Timing ...................................................................................................... 160

14.4 MULTI-INTERRUPT............................................................................................................................... 163

14.5 PROGRAM EXAMPLE OF INTERRUPT ............................................................................................. 164

CHAPTER 15 AC ZERO CROSS DETECTION .................................................................................. 167

CHAPTER 16 STANDBY FUNCTION.................................................................................................. 16 9

16.1 OVERVIEW OF THE STANDBY FUNCTION ....................................................................................... 16 9

16.2 HALT MODE .......................................................................................................................................... 170

16.2.1 Setting HALT Mode ................................................................................................................. 1 70

16.2.2 Star t Address after HALT Mode Is Released ......................................................................... 170

16.2.3 HALT Mode Setting Conditions ............................................................................................... 172

16.3 STOP MODE.......................................................................................................................................... 174

16.3.1 Setting of STOP Mode ............................................................................................................ 174

16.3.2 Star t Address after STOP Mode Is Released ........................................................................ 174

16.3.3 STOP Mode Setting Conditions.............................................................................................. 176

CHAPTER 17 RESET ........................................................................................................................... 17 9

17.1 RESET FUNCTION ................................................................................................................................ 180

17.2 RESETTING ........................................................................................................................................... 181

17.3 POWER-ON/POWER-DOWN RESET FUNCTION .............................................................................. 18 2

17.3.1 Conditions Required to Enable the Power-On Reset Function............................................. 182

17.3.2 Power-On Reset Function and Operation .............................................................................. 183

17.3.3 Condition Required for Use of the Power-Down Reset Function.......................................... 18 5

17.3.4 Power-Down Reset Function and Operation.......................................................................... 18 5

CHAPTER 18 ONE-TIME PROM WRITING/VERIFYING .................................................................... 189

18.1 DIFFERENCES BETWEEN MASK ROM VERSION AND ONE-TIME PROM MODEL..................... 1 89

18.2 OPERATION MODE WHEN PROGRAM MEMORY IS WRITTEN/VERIFIED ................................... 190

18.3 WRITING PROCEDURE OF PROGRAM MEMORY ........................................................................... 191

18.4 READING PROCEDURE OF PROGRAM MEMORY .......................................................................... 192

CHAPTER 19 INSTRUCTION SET ...................................................................................................... 193

19.1 OVERVIEW OF THE INSTRUCTION SET........................................................................................... 193

19.2 LEGEND ................................................................................................................................................. 194

19.3 LIST OF THE INSTRUCTION SET....................................................................................................... 195

19.4 ASSEMBLER (AS17K) EMBEDDED MACRO INSTRUCTIONS ........................................................ 197

- v -

Page 13

19.5 INSTRUCTIONS .................................................................................................................................... 198

19.5.1 Addition Instructions ................................................................................................................ 1 98

19.5.2 Subtraction Instructions........................................................................................................... 209

19.5.3 Logical Operation Instructions ................................................................................................ 216

19.5.4 Judgment Instructions ............................................................................................................. 221

19.5.5 Comparison Instructions.......................................................................................................... 223

19.5.6 Rotation Instructions................................................................................................................ 226

19.5.7 Transfer Instructions ................................................................................................................ 227

19.5.8 Branch Instructions.................................................................................................................. 243

19.5.9 Subroutine Instructions............................................................................................................ 246

19.5.10 Interrupt Instructions................................................................................................................ 251

19.5.11 Other Instructions .................................................................................................................... 253

CHAPTER 20 ASSEMBLER RESERVED WORDS ............................................................................255

20.1 MASK OPTION DIRECTIVE ................................................................................................................. 25 5

20.1.1 Specifying Mask Option .......................................................................................................... 255

20.2 RESERVED SYMBOLS......................................................................................................................... 257

APPENDIX A DEVELOPMENT OF µPD171×× SUBSERIES .............................................................26 1

APPENDIX B COMPARISON OF FUNCTIONS BETWEEN µPD17135A, 17137A, AND

µPD17145 SUBSERIES................................................................................................ 263

APPENDIX C DEVELOPMENT TOOLS .............................................................................................. 2 65

APPENDIX D NOTES ON CONFIGURATION OF SYSTEM CLOCK OSCILLATION CIRCUIT...... 267

APPENDIX E INSTRUCTION LIST...................................................................................................... 269

E.1 INSTRUCTION LIST (by function) ...................................................................................................... 2 69

E.2 IINSTRUCTION LIST (alphabetical order) ......................................................................................... 270

APPENDIX F ORDERING MASK ROM............................................................................................... 27 1

- vi -

Page 14

LIST OF FIGURES (1/3)

Figure No. Title Page

3-1 Program Counter...................................................................................................................................... 17

3-2 Value of the Program Counter after Instruction Execution .................................................................... 1 8

3-3 Value in the Program Counter after Reset ............................................................................................. 18

3-4 Value in the Program Counter during Execution of a BR addr Instruction ........................................... 18

3-5 Value in the Program Counter during Execution of an Indirect Branch Instruction.............................. 19

3-6 Value in the Program Counter during Execution of a CALL addr.......................................................... 1 9

3-7 Value in the Program Counter during Execution of an Indirect Subroutine Call .................................. 20

3-8 Value in the Program Counter during Execution of a Return Instruction.............................................. 20

µ

4-1 Program Memory Map for the

4-2 CALL addr Instruction .............................................................................................................................. 26

4-3 Table Reference (MOVT DBF, @AR)...................................................................................................... 27

5-1 Data Memory Configuration..................................................................................................................... 31

5-2 System Register Configuration................................................................................................................ 32

5-3 Data Buffer Configuration ........................................................................................................................ 32

5-4 General Register (GR) Configuration...................................................................................................... 33

5-5 Port Register Configuration ..................................................................................................................... 33

PD17134A Subseries ........................................................................... 2 3

6-1 Stack Configuration.................................................................................................................................. 35

7-1 Allocation of System Register in Data Memory...................................................................................... 41

7-2 System Register Configuration................................................................................................................ 42

7-3 Address Register Configuration .............................................................................................................. 43

7-4 Address Register Used as a Peripheral Circuit...................................................................................... 44

7-5 Window Register Configuration............................................................................................................... 45

7-6 Example of Window Register Operation ................................................................................................. 45

7-7 Bank Register Configuration ................................................................................................................... 46

7-8 Index Register Configuration ................................................................................................................... 47

7-9 Modification of Data Memor y Address by Index Register and Memory Pointer ................................... 48

7-10 Operation Example When IXE = 0 and MPE = 0................................................................................... 50

7-11 Operation Example When IXE = 0 and MPE = 1................................................................................... 52

7-12 Operation Example When IXE = 1 and MPE = 0................................................................................... 54

7-13 Operation Example When IXE = 1 and MPE = 0................................................................................... 55

7-14 Operation Example When IXE = 1 and MPE = 0 (Array Processing) ................................................... 56

7-15 General Register Pointer Configuration.................................................................................................. 57

7-16 General Register Configuration............................................................................................................... 58

7-17 Program Status Word Configuration ....................................................................................................... 59

7-18 Outline of Functions of the Program Status Word ................................................................................. 60

8-1 General Register Configuration............................................................................................................... 68

- vii -

Page 15

LIST OF FIGURES (2/3)

Figure No. Title Page

9-1 Register File Configuration ...................................................................................................................... 69

9-2 Relationship Between the Register File and Data Memory ................................................................... 7 0

9-3 Accessing the Register File Using the PEEK and POKE Instructions .................................................. 72

9-4 Control Register Configuration ................................................................................................................ 75

10-1 Allocation of the Data Buffer ................................................................................................................... 77

10-2 Data Buffer Configuration........................................................................................................................ 77

10-3 Relationship Between the Data Buffer and Peripheral Hardware ......................................................... 78

11-1 ALU Configuration.................................................................................................................................... 84

12-1 Input/Output Switching by Group I/O .................................................................................................... 106

12-2 Port Control Register of Bit I/O ............................................................................................................. 107

12-3 Specifying Pull-Up Resistor Incorporation Using Software.................................................................. 109

13-1 Configuration of the 8-Bit Timer Counters............................................................................................ 112

13-2 Timer 0 Mode Register .......................................................................................................................... 113

13-3 Timer 1 Mode Register .......................................................................................................................... 114

13-4 Setting Count Value to Modulo Register............................................................................................... 116

13-5 Reading Count Value of Count Register............................................................................................... 117

13-6 Error When Count Register Is Cleared to 0 During Counting ............................................................. 119

13-7 Error When Counting Is Started from Count Stop Status.................................................................... 120

13-8 Timer 0 Output Setting Register ............................................................................................................ 121

13-9 Basic Interval Timer Configuration........................................................................................................ 12 2

13-10 BTM Mode Register ............................................................................................................................... 123

13-11 Watchdog Timer Mode Register............................................................................................................ 124

13-12 Timing Char t of Watchdog Timer (with WDTRES Flag Used) ............................................................. 1 26

13-13 Block Diagram of the A/D Converter..................................................................................................... 128

13-14 A/D Converter Control Register ............................................................................................................ 130

13-15 Setting a Value in the 8-Bit Data Register (ADCR) .............................................................................. 13 2

13-16 Reading Values from the 8-bit Data Register (ADCR) ......................................................................... 1 33

13-17 Relationship between the Analog Input Voltage and Digital Conversion Result ................................ 134

13-18 Using the Successive Mode for the A/D Converter.............................................................................. 13 6

13-19 A/D Conversion Timing in the Continuous Mode ................................................................................. 137

13-20 Using the Single Mode for the A/D Converter ...................................................................................... 139

13-21 Single Mode Operation (Comparison) Timing ...................................................................................... 140

13-22 Block Diagram of the Serial Interface ................................................................................................... 142

13-23 Timing of 8-Bit Transmission and Reception Mode (Simultaneous Transmission and Reception) .. 143

13-24 Timing of the Clock Synchronization 8-Bit Reception Mode (SO Pin Output High Impedance)........ 144

13-25 Serial Interface Control Register ........................................................................................................... 145

13-26 Setting a Value in the Shift Register..................................................................................................... 147

13-27 Reading a Value from the Shift Register .............................................................................................. 14 8

- viii -

Page 16

LIST OF FIGURES (3/3)

Figure No. Title Page

14-1 Interrupt Control Register ...................................................................................................................... 152

14-2 Interrupt Processing Procedure ............................................................................................................ 158

14-3 Return from Interrupt Processing.......................................................................................................... 159

14-4 Interrupt Accepting Timing (When INTE = 1, IP××× = 1) ..................................................................... 160

14-5 Example of Multi-interrupt ..................................................................................................................... 163

15-1 Block Diagram for the AC Zero Cross Detector ................................................................................... 167

15-2 Zero Cross Detection Signal ................................................................................................................. 168

16-1 Releasing HALT Mode ........................................................................................................................... 17 1

16-2 Releasing STOP Mode.......................................................................................................................... 175

17-1 Reset Block Configuration..................................................................................................................... 181

17-2 Reset Operation..................................................................................................................................... 181

17-3 Example of the Power-On Reset Operation ......................................................................................... 18 4

17-4 Example of the Power-Down Reset Operation ..................................................................................... 18 6

17-5 Example of Reset Operation during the Period from Power-Down Reset to Power Recovery ......... 187

18-1 Procedure of Program Memory Writing ................................................................................................ 191

18-2 Procedure of Program Memory Reading .............................................................................................. 192

D-1 External Circuit of System Clock Oscillation Circuit............................................................................. 267

D-2 Example of Incorrect Oscillation Circuits .............................................................................................. 268

- ix -

Page 17

LIST OF TABLES (1/2)

Table No. Title Page

2-1 Processing of Unused Pins ..................................................................................................................... 14

4-1 Program Memory Configuration .............................................................................................................. 23

4-2 Vector Address for the µPD17134A Subseries ...................................................................................... 2 4

6-1 Operation of Stack Pointer ...................................................................................................................... 37

6-2 Operation of the Instructions CALL, RET, and RETSK .......................................................................... 38

6-3 Stack Operation during Table Reference................................................................................................ 38

6-4 Operation during Interrupt Receipt and RETI Instruction ...................................................................... 39

6-5 Stack Operation during the PUSH and POP Instructions ...................................................................... 39

7-1 Specifying the Bank in Data Memory...................................................................................................... 46

7-2 Instructions Subject to Address Modification .......................................................................................... 48

7-3 Zero Flag (Z) and Compare Flag (CMP) ................................................................................................ 61

10-1 Peripheral Hardware................................................................................................................................79

11-1 List of ALU Instructions............................................................................................................................ 86

11-2 Results of Arithmetic Operations Performed in 4-Bit Binary and BCD.................................................. 8 9

11-3 Types of Arithmetic Operations ............................................................................................................... 91

11-4 Logical Operations ................................................................................................................................... 93

11-5 Table of Tru e Values for Logical Operations .......................................................................................... 93

11-6 Bit Judgement Instructions ...................................................................................................................... 94

11-7 Comparison Judgement Instructions ....................................................................................................... 96

12-1 Writing into and Reading from the Port Register (0.70H).................................................................... 101

12-2 Writing into and Reading from the Port Register (0.71H).................................................................... 102

12-3 Switching the Port and A/D Converter .................................................................................................. 103

12-4 Register File Contents and Pin Functions ............................................................................................ 104

12-5 Contents Read from the Port Register (0.73H).................................................................................... 105

12-6 Writing into and Reading from the Port Register (1.70H).................................................................... 105

13-1 Data Conversion Time for the A/D Converter....................................................................................... 138

13-2 Serial Clock List ..................................................................................................................................... 14 1

13-3 Operating Mode of the Serial Interface ................................................................................................. 143

14-1 Interrupt Source Types .......................................................................................................................... 150

14-2 Interrupt Request Flag and Interrupt Enable Flag ................................................................................ 151

16-1 Status in Standby Mode ........................................................................................................................ 169

16-2 HALT Mode Release Condition ............................................................................................................. 170

16-3 Start Address after HALT Mode Is Released........................................................................................ 170

16-4 STOP Mode Release Condition ............................................................................................................ 174

16-5 Start Address after STOP Mode Is Released....................................................................................... 174

- x -

Page 18

LIST OF TABLES (2/2)

Table No. Title Page

17-1 Hardware Status at Reset ..................................................................................................................... 180

18-1 Pins Used for Writing/Verifying Program Memory ................................................................................ 18 9

18-2 Differences Between Mask ROM Version and One-Time PROM Version .......................................... 190

18-3 Setting Operation Modes....................................................................................................................... 190

20-1 Mask Option Definition Directive........................................................................................................... 256

- xi -

Page 19

[MEMO]

- xii -

Page 20

CHAPTER 1 GENERAL DESCRIPTION

The µPD17134A subseries is a 4-bit single-chip microcontroller employing the 17K architecture and containing an

8-bit A/D converter (4 channels), a timer (3 channels), an AC zero cross detector, a power-on reset circuit, and a serial

interface.

µ

PD17P136A and 17P137A are the one-time PROM version of the µPD17136A and 17137A, respectively,

The

and are suitable for program evaluation at system development and for small-scale production.

µ

The following are features of the

17K architecture: general-purpose register mode, instruction length: fixed to 16 bits

•

Instruction execution time: 2 µs (fX = 8 MHz, ceramic oscillation)

•

Program memory:µPD17134A : 2K bytes (1024 × 16 bits)

•

µ

PD17135A : 2K bytes (1024 × 16 bits)

µ

PD17136A : 4K bytes (2048 × 16 bits)

µ

PD17137A : 4K bytes (2048 × 16 bits)

µ

PD17P136A : 4K bytes (2048 × 16 bits, one-time PROM)

µ

PD17P137A : 4K bytes (2048 × 16 bits, one-time PROM)

Data memory (RAM): 112 × 4 bits

•

A/D converter: 4 channels (8-bit resolution, successive approximation type)

•

Timer: 3 channels (8-bit timer/counter × 2 channels, basic interval timer

•

Serial interface: 1 channel (clocked 3-wire mode)

•

Supply voltage: VDD = 4.5 to 5.5 V (fX = 400 kHz to 8 MHz)

•

VDD = 2.7 to 5.5 V (fX = 400 kHz to 4 MHz)

DD = 2.7 to 5.5 V (fCC = 400 kHz to 2 MHz) for

V

PD17134A subseries.

8 µs (fCC = 2 MHz, RC oscillation)

Note

)

µ

PD17134A and 17136A

1

Note An internal reset signal can be generated by using the basic interval timer (watchdog timer function).

µ

These features of the

application fields;

Electronic thermos bottle

•

Rice cooker

•

Audio equipment

•

Battery charger

•

Printer

•

Plain Paper Copier

•

PD17134A subseries are suitable for use as a controller or a slave device in the following

1

Page 21

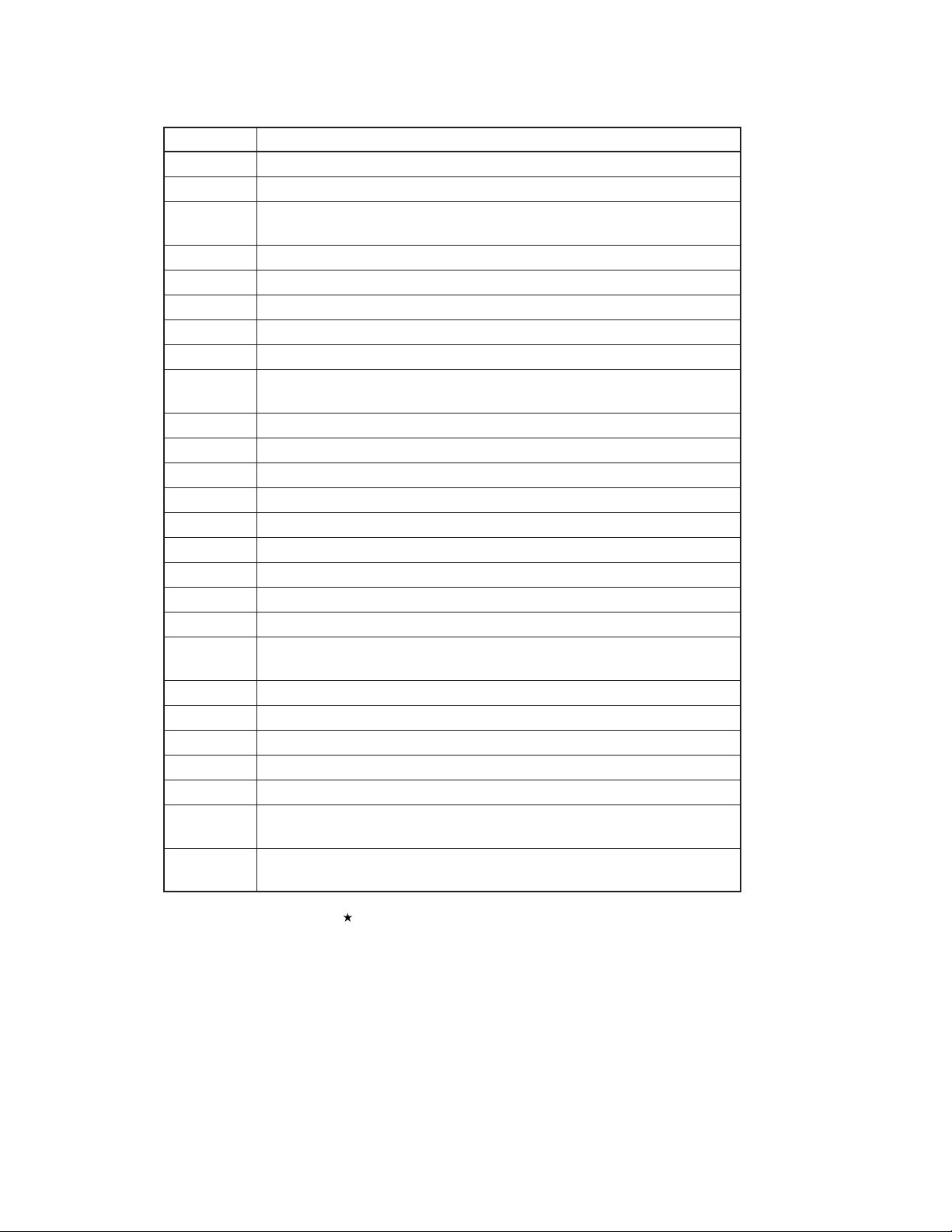

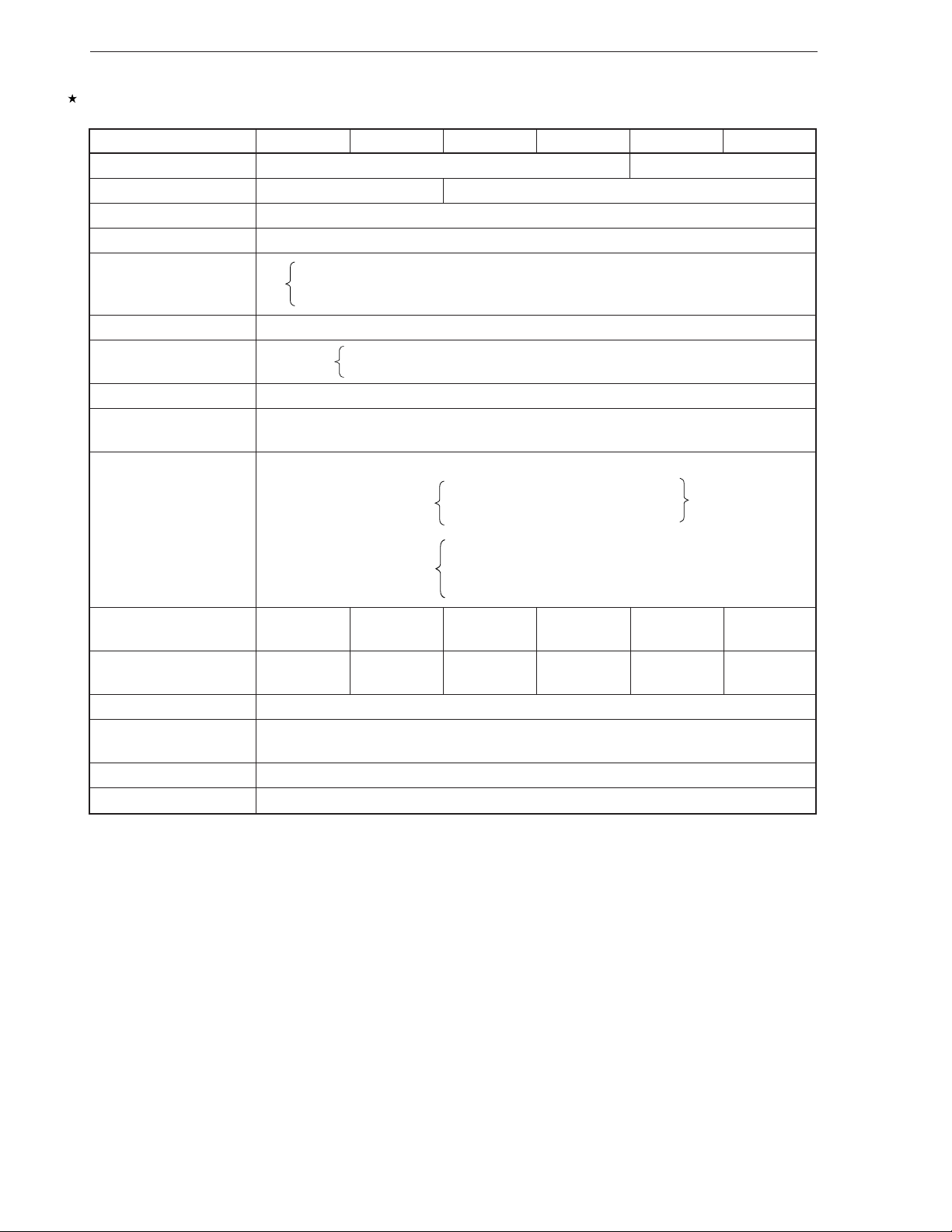

1.1 FUNCTION LIST

CHAPTER 1 GENERAL DESCRIPTION

Item

ROM configuration Mask ROM One-time PROM

ROM capacity 2KB (1024 ✕ 16 bits) 4KB (2048 ✕ 16 bits)

RAM capacity 112 ✕ 4 bits

Stack Address stack × 5, interrupt stack × 3

Number of I/O port • I/O : 20

A/D converter 8-bit resolution × 4 channels (shared with port pin), absolute precision ± 1.5 LSB or less

Timer

Serial interface 1 channel (3 wires)

AC zero cross detection Provided (can be used in application circuit at VDD = 5 V ± 10%)

function

Interrupt • Nesting by hardware (up to 3 levels)

System clock RC Ceramic RC Ceramic RC Ceramic

Instruction 8 µs2

execution time at fX = 2 MHz at fX = 8 MHz at fX = 2 MHz at fX = 8 MHz at fX = 2 MHz at fX = 8 MHz

Standby HALT, STOP

Power-on/ Available (effective only for application circuit with VDD = 5 V ± 10 %, 400 kHz to 4 MHz)

power-down reset

Supply voltage VDD = 2.7 to 5.5 V (5 V ± 10 % when using A/D converter)

Package 28-pin plastic shrink DIP, 28-pin plastic SOP

µ

PD17134A

22 • Input only : 1

• Sensor input

3 channels

• External interrupts (INT) : 1 Falling edge detection Selectable

• Internal interrupts : 1

oscillation oscillation oscillation oscillation oscillation oscillation

µ

PD17135A

Note

: 1

• 8-bit timer counter : 2 channels (16-bit timer 1 channel applicable)

• 7-bit basic interval timer : 1 channel (watchdog timer applicable)

µ

s8

µ

PD17136A

Rising edge detection

Both rising and falling edges detection

• Timer 0 (TM0)

• Timer 1 (TM1)

• Basic interval timer (BTM)

• Serial interface (SIO)

µ

s2

µ

PD17137AµPD17P136AµPD17P137A

µ

s8

µ

s2

µ

s

Note The INT pin can be used as an input pin (sense input) when the external interrupt function is not used. The

sense input function is to read the status of the pin by using the INT flag of a control register, instead of a port

register.

Caution The PROM model is highly compatible with the mask ROM model in terms of functions but its internal

ROM circuit and electrical characteristics are partially different from those of the mask ROM model.

To replace the PROM model with the mask ROM model, thoroughly evaluate the application by using

a sample of the mask ROM model.

2

Page 22

CHAPTER 1 GENERAL DESCRIPTION

1.2 ORDERING INFORMATION

Part number Package Internal ROM

µ

PD17134ACT-××× 28-pin plastic shrink DIP (400 mil) Mask ROM

µ

PD17135ACT-××× 28-pin plastic shrink DIP (400 mil) Mask ROM

µ

PD17136ACT-××× 28-pin plastic shrink DIP (400 mil) Mask ROM

µ

PD17137ACT-××× 28-pin plastic shrink DIP (400 mil) Mask ROM

µ

PD17P136ACT 28-pin plastic shrink DIP (400 mil) One-time PROM

µ

PD17P137ACT 28-pin plastic shrink DIP (400 mil) One-time PROM

µ

PD17134AGT-××× 28-pin plastic SOP (375 mil) Mask ROM

µ

PD17135AGT-××× 28-pin plastic SOP (375 mil) Mask ROM

µ

PD17136AGT-××× 28-pin plastic SOP (375 mil) Mask ROM

µ

PD17137AGT-××× 28-pin plastic SOP (375 mil) Mask ROM

µ

PD17P136AGT 28-pin plastic SOP (375 mil) One-time PROM

µ

PD17P137AGT 28-pin plastic SOP (375 mil) One-time PROM

Remark ×××: ROM code number

3

Page 23

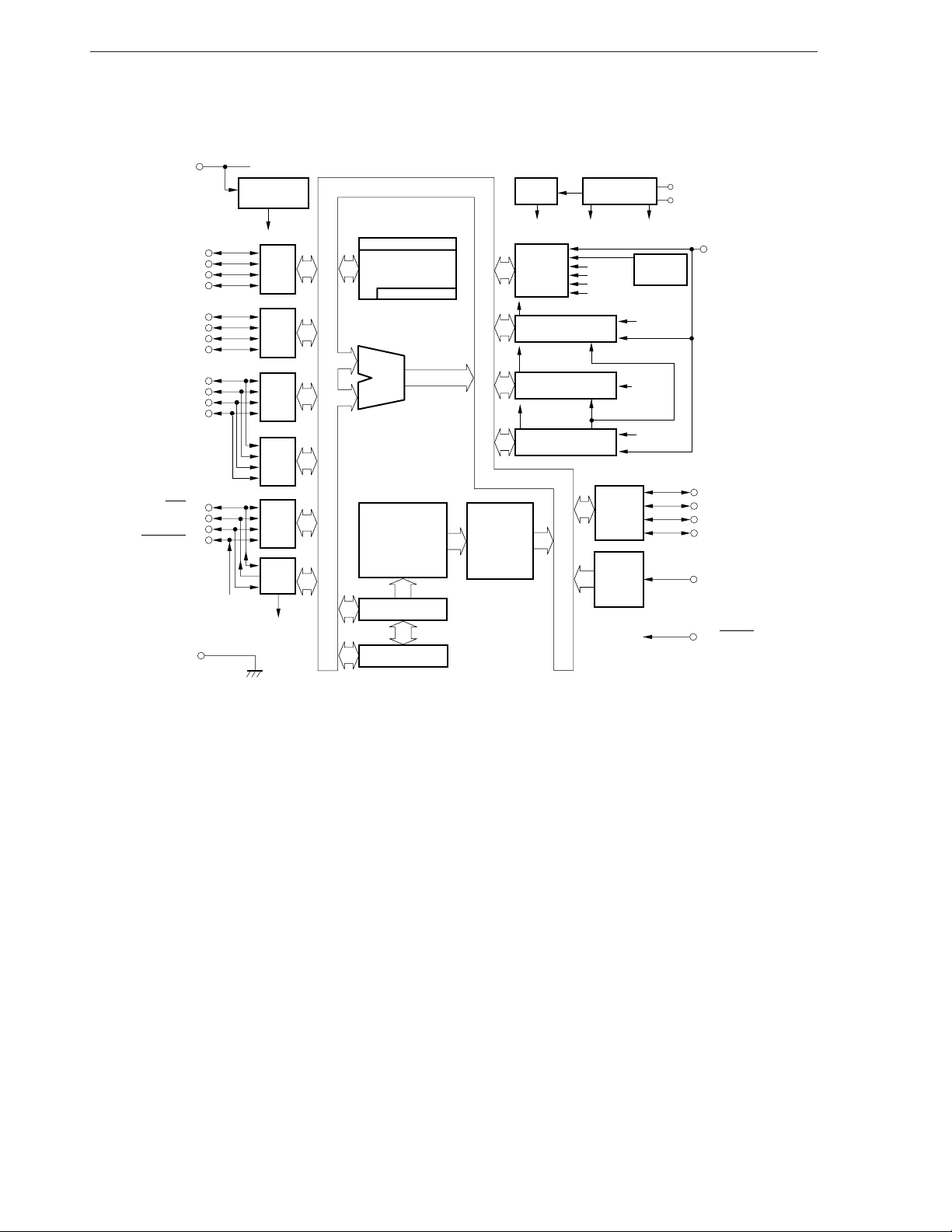

1.3 BLOCK DIAGRAM

V

DD

P0A

0

P0A

1

P0A

2

P0A

3

P0B

0

P0B

1

P0B

2

P0B

3

P0C0/ADC

P0C1/ADC

P0C2/ADC

P0C3/ADC

P0D

P0D0/SCK

3

1

/SO

P0D

P0D

2

/TM0OUT

GND

/SI

0

1

2

3

TM0

POWER-ON/

POWER-DOWN

RESET

P0A

(CMOS)

P0B

(CMOS)

P0C

(CMOS)

A/D

Con-

verter

P0D

(N-ch)

Serial

Interface

IRQSIO

CHAPTER 1 GENERAL DESCRIPTION

Clock

divider

N

f

X

/2

RF

RAM

112 × 4 bits

SYSTEM REG.

ALU

Note1

ROM/

One-Time

PROM

Program counter

Note2

Stack

Instruction

decoder

Interrupt

controller

IRQBTM

Basic interval timer

IRQTM1

Timer 1

IRQTM0

Timer 0

System clock

generator

CPU CLOCK CLK STOP

AC

IRQTM0

ZEROCROSS

IRQTM1

detector

IRQBTM

IRQSIO

N

fX/2

N

fX/2

N

f

X

/2

P1A

(N-ch)

P1B

X

IN

Note2

(CLK)

X

OUT

INT

P1A

0

P1A

1

P1A

2

P1A

3

P1B

0

(VPP)

RESET

Remarks 1. The terms CMOS and N-ch in square brackets indicate the output form of the port.

CMOS : CMOS push-pull output

N-ch : N-channel open-drain output (Each pin can contain pull-up resistor bit-wise as specified

using a mask option.)

2. The devices in parentheses are effective only in the case of program memory write/verify mode of

µ

PD17P136A and µPD17P137A.

the

Notes 1. The ROM (or PROM) capacity of each product is as follows:

µ

1024 × 16 bits :

PD17134A, 17135A

2048 × 16 bits :µPD17136A, 17137A, 17P136A, 17P137A

2. The stack capacity of each product is as follows:

µ

5 × 10 bits :

PD17134A, 17135A

5 × 11 bits :µPD17136A, 17137A

4

Page 24

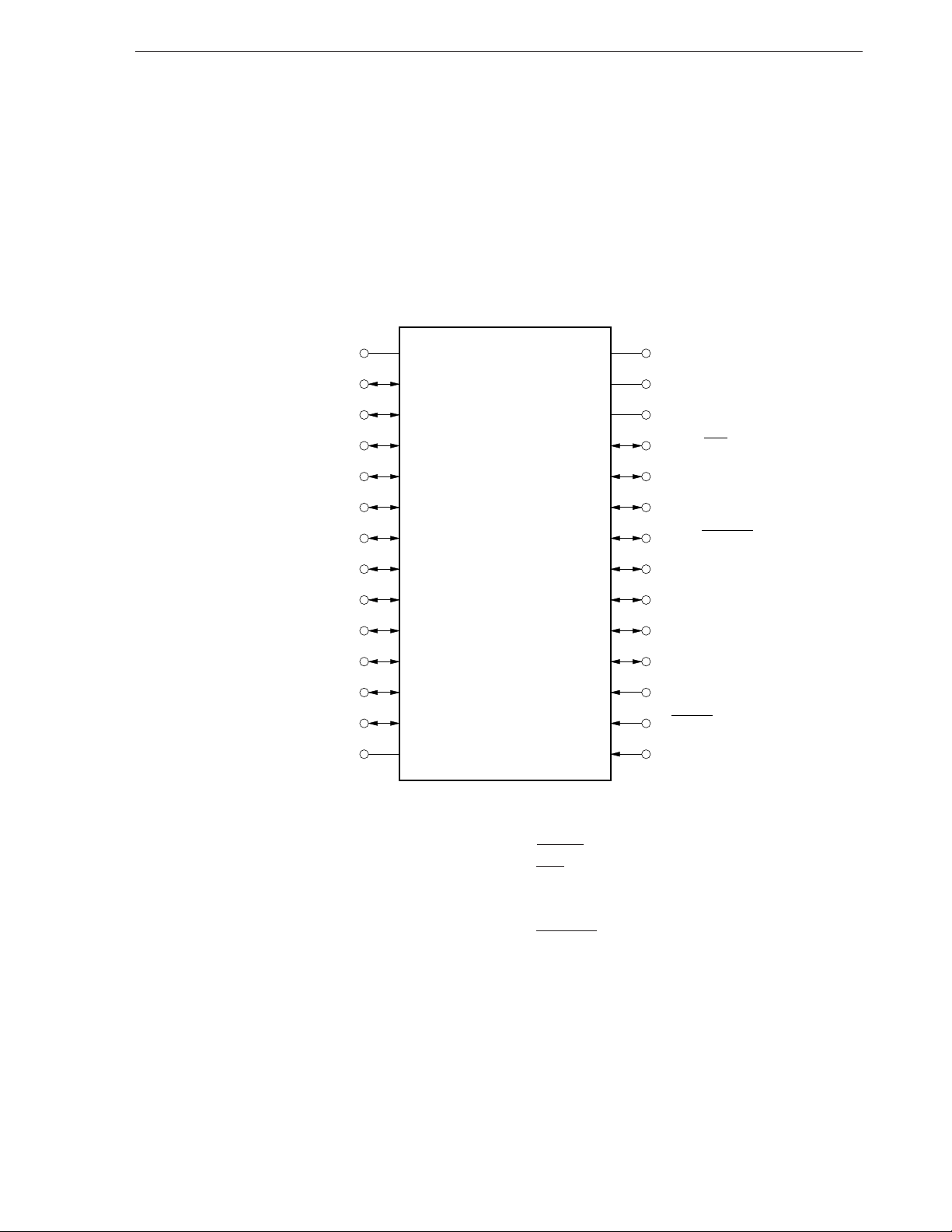

CHAPTER 1 GENERAL DESCRIPTION

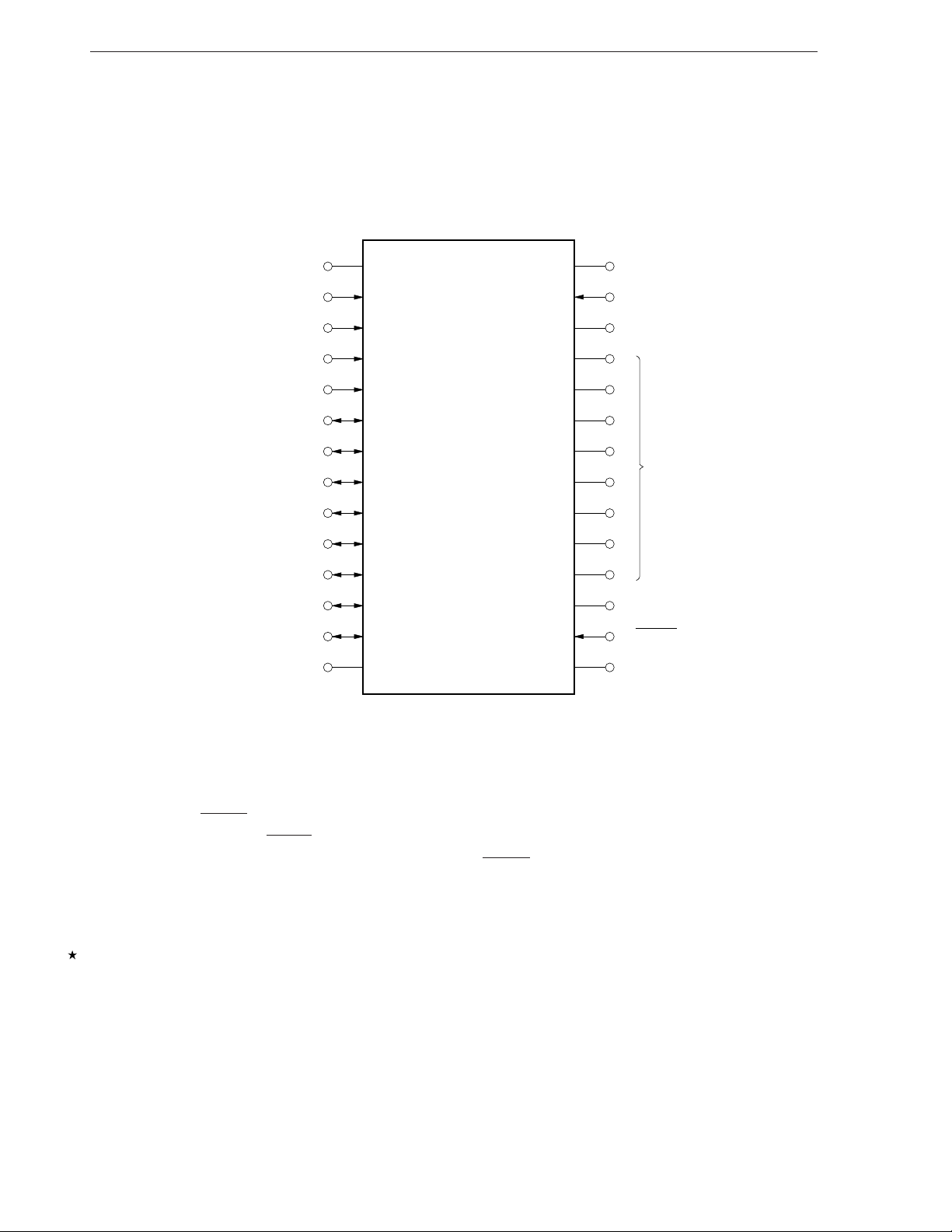

1.4 PIN CONFIGURATION (TOP VIEW)

(1) Normal operating mode

28-pin plastic shrink DIP (400 mil)

µ

PD17134ACT-×××, µPD17135ACT-×××, µPD17136ACT-×××, µPD17137ACT-×××

µ

PD17P136ACT-×××, µPD17P137ACT-×××

28-pin plastic SOP (375 mil)

µ

PD17134AGT-×××, µPD17135AGT-×××, µPD17136AGT-×××, µPD17137AGT-×××

µ

PD17P136AGT-×××, µPD17P137AGT-×××

V

ADC

V

1

28

DD

P0C3/ADC

P0C2/ADC

P0C1/ADC

P0C0/ADC

P0B

P0B

P0B

P0B

P0A

P0A

P0A

P0A

3

2

1

0

3

2

1

0

3

2

1

0

GND

0 to ADC3 : Analog input for the A/D

ADC

2

3

4

5

6

7

8

9

10

11

12

13

14 15

converter

GND : Ground

INT : External interrupt input

0, OSC1 : System clock oscillation

OSC

0 to P0A3 : Port 0A

P0A

P0B0 to P0B3 : Port 0B

P0C0 to P0C3 : Port 0C

0 to P0D3 : Port 0D

P0D

P1A0 to P1A3 : Port 1A

27

26

25

24

23

22

21

20

19

18

17

16

XIN (OSC1)

OUT

(OSC0)

X

0

/SCK

P0D

1

/SO

P0D

P0D

2

/SI

P0D

3

/TM0OUT

P1A

0

P1A

1

P1A

2

P1A

3

P1B

0

RESET

INT

P1B0 : Port 1B

RESET : Reset input

SCK : Serial clock input/output

SI : Serial data input

SO : Serial data output

TM0OUT : Timer 0 carry output

ADC : Analog power supply

V

VDD : Power supply

IN, XOUT : System clock oscillation

X

5

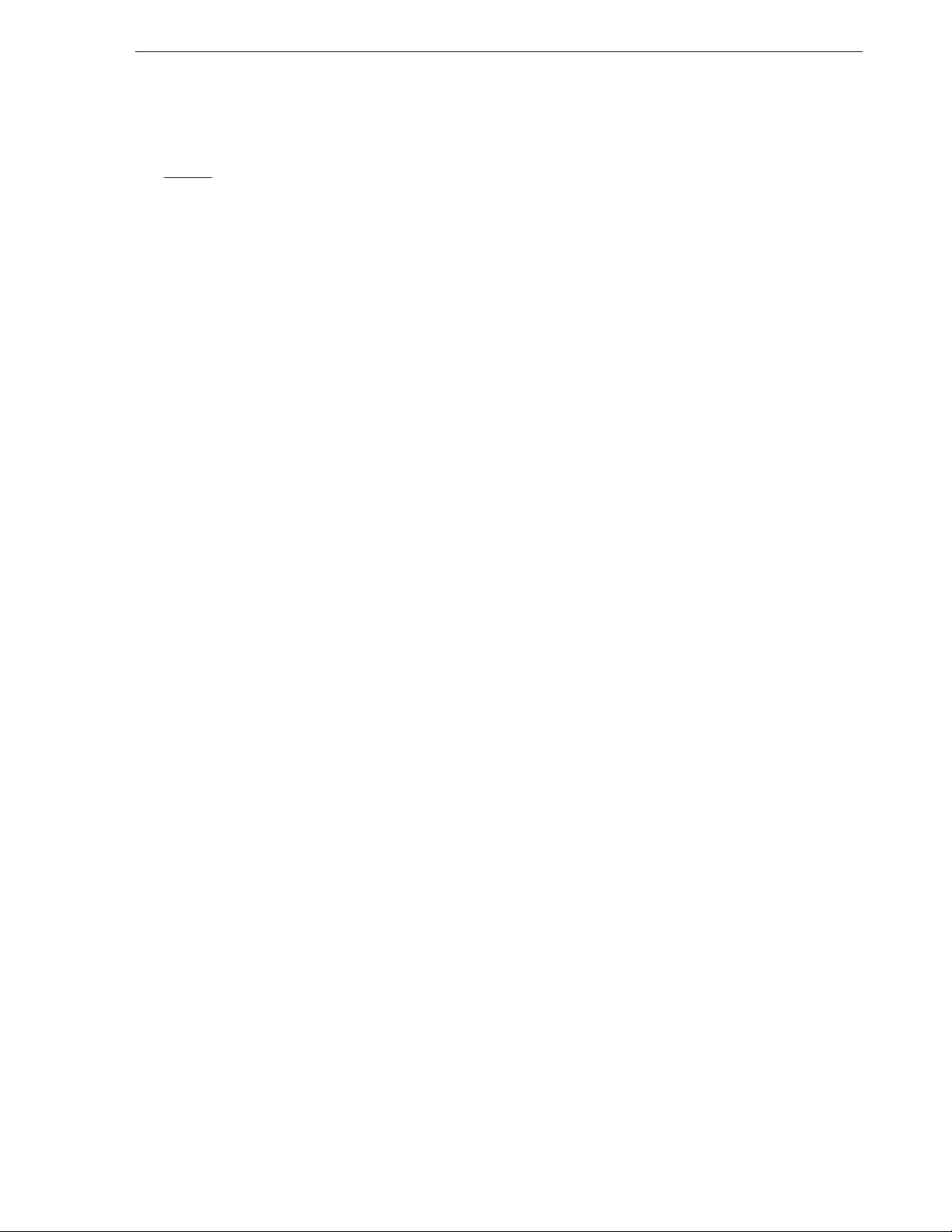

Page 25

CHAPTER 1 GENERAL DESCRIPTION

(2) Program memory write/verify mode

28-pin plastic shrink DIP (400 mil)

µ

PD17P136ACT, 17P137ACT

28-pin plastic SOP (375 mil)

µ

PD17P136AGT, 17P137AGT

(VDD)

MD

MD

MD

MD

GND

V

1

3

2

1

0

D

7

D

6

2

3

4

5

6

7

28

27

26

25

24

23

22

DD

CLK

(Open)

(L)

D

5

D

4

D

3

D

2

D

1

D

0

8

9

10

11

12

13

21

20

19

18

17

16

14 15

V

PP

RESET

(L)

Caution ( ) represents processing of the pins which are not used in program memory write/verify

mode.

L : Connect to GND via pull-down resistor one by one.

RESET : Set the same electric potential as V

DD in program memory write/verify mode.

RESET pin is also used for system reset input before setting program memory

write/verify mode. Therefore, RESET pin should be set to the same electric

DD 10

µ

potential as V

s or later than that of VDD pin (For details, refer to CHAPTER

18 ONE-TIME PROM WRITING/VERIFYING).

Open : Do not connect anything.

DD : Connect to VDD directly.

V

6

Page 26

CHAPTER 1 GENERAL DESCRIPTION

CLK : Clock input for address updating

D0-D7 : Data input/output

GND : Ground

0-MD3 : Operation mode select

MD

RESET : Reset input

DD : Power supply

V

VPP : Program voltage application

7

Page 27

[MEMO]

8

Page 28

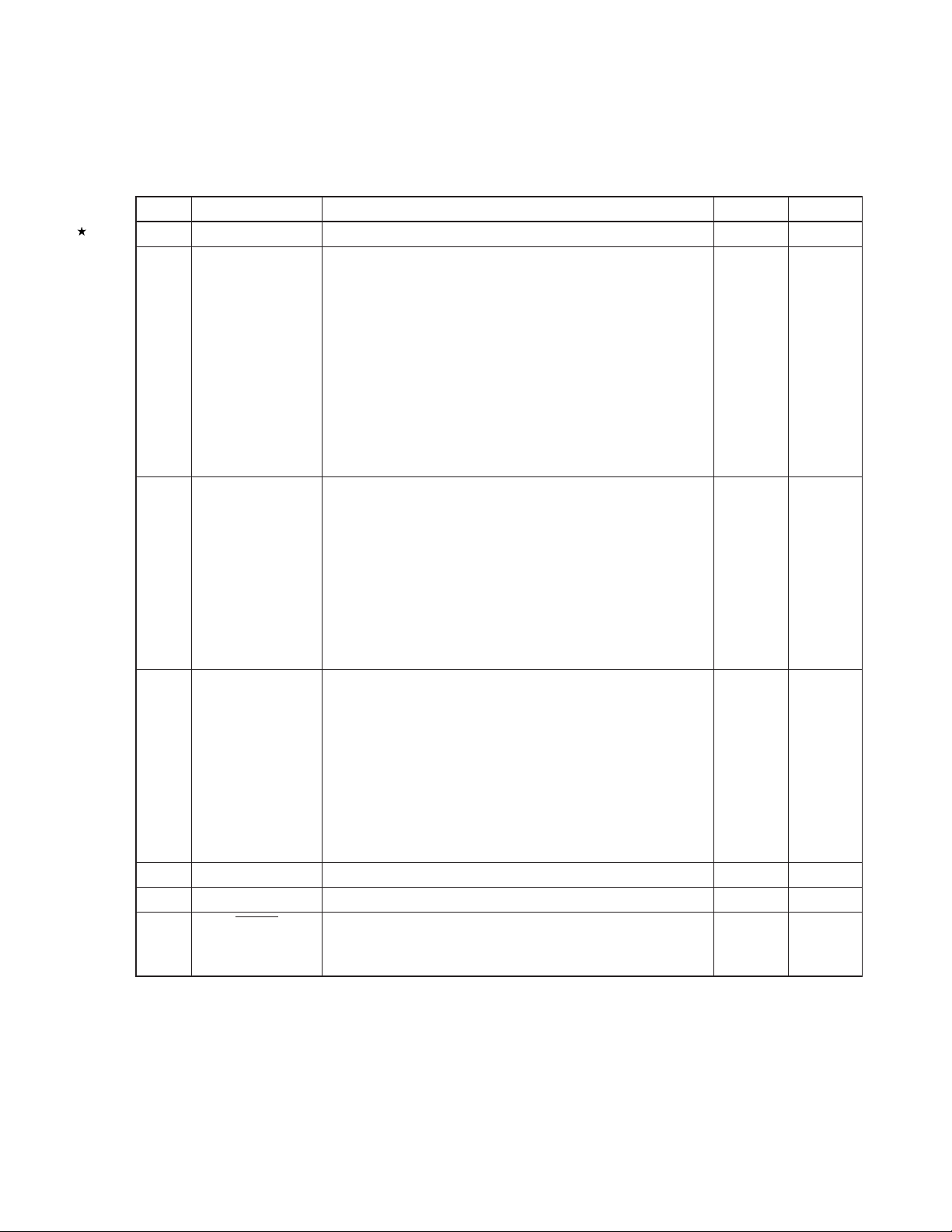

CHAPTER 2 PIN FUNCTIONS

2.1 PIN FUNCTIONS

Pin No. Pin name Function Output At reset

1VADC Supplies power and reference voltage for the A/D converter — —

Note1

Note1

Note1

Note1

Note1

Constitute port 0C, serve as analog input pins of A/D CMOS Input

Note1

is written or verified.

P0C3 to P0C0

•

• 4-bit input/output port

• Input/output setting in 1-bit unit

ADC3 to ADC0

•

• Analog input for the A/D converter

MD3 to MD0

•

• Available for the µPD17P136A and µPD17P137A only

• Selects operating mode at program memory writing/

verification

Used as port 0B, or data input/output pins in program CMOS Input

P0B3 to P0B0

•

• 4-bit input/output port

• Input/output setting in 4-bit unit

• Software-selectable pull-up resistor

D7 to D4

•

• Available for the µPD17P136A and µPD17P137A only

• 8-bit data input/output at program memory writing/

verification

Used as port 0A, or data input/output pin in program memory CMOS Input

P0A3 to P0A0

•

• 4-bit input/output port

• Input/output setting in 4-bit unit

• Software-selectable pull-up resistor

D3 to D0

•

• Available for the µPD17P136A and µPD17P137A only

• 8-bit data input/output at program memory writing/

verification

A pull-up resistor can be internally connected by mask

Note2

option

2 P0C3/ADC3/MD3

| | converter, or select operating mode when program memory push-pull (P0C)

5 P0C0/ADC0/MD0

6 P0B3/D7

| | memory write/verify mode. push-pull (P0B)

9 P0B0/D4

10 P0A3/D3

| | write/verify mode. push-pull (P0A)

13 P0A0/D0

14 GND Ground — —

15 INT External interrupt request input or sensor signal input — Input

16 RESET System reset input pin — Input

Notes 1. The MD0-MD3 and D0-D7 pins are valid with the µPD17P136A and 17P137A only.

2. The µPD17P136A and 17P137A do not have a pull-up resistor connected by mask option.

9

Page 29

CHAPTER 2 PIN FUNCTIONS

Pin No. Pin name Function Output At reset

17 P1B0/VPP

18 P1A3 Port 1A N-ch open Input

| | • 4-bit input/output port drain

21 P1A0 • Input/output setting in 4-bit unit

22 P0D3/TM0OUT Used as port 0D, or timer 0 carry output, serial data input, N-ch open Input

23 P0D 2/SI

24 P0D1/SO

25 P0D0/SCK

26 XOUT In the case of the µPD17135A/17137A/17P137A — —

27 XIN/CLK

26 OSC0 In the case of the µPD17134A/17136A/17P136A

27 OSC1/CLK

28 VDD Power supply — —

Note1

Note3

Note3

Used as port 1B, or programming voltage supply pin in Input Input

program memory write/verify mode.

P1B0

•

• 1-bit input port

• A pull-up resistor can be internally connected by mask

VPP

•

• Available for the µPD17P136A and µPD17P137A only

• Applies programming voltage (+12.5 V) at program

• A pull-up resistor can be internally connected by mask

serial data output, and serial clock input/output pins drain