Page 1

DATA SHEET

MOS INTEGRATED CIRCUIT

µ

PD17072,17073

4-BIT SINGLE-CHIP MICROCONTROLLER

WITH HARDWARE FOR DIGITAL TUNING SYSTEM

DESCRIPTION

µ

PD17072 and 17073 are low-voltage 4-bit single-chip CMOS microcontrollers containing hardware ideal for

organizing a digital tuning system.

The CPU employs 17K architecture and can manipulate the data memory directly, perform arithmetic operations,

and control peripheral hardware with a single instruction. All the instructions are 16-bit one-word instructions.

As peripheral hardware, a prescaler that can operate at up to 230 MHz for a digital tuning system, a PLL frequency

synthesizer, and an intermediate frequency (IF) counter are integrated in addition to I/O ports, an LCD controller/driver,

A/D converter, and BEEP.

Therefore, a high-performance, multi-function digital tuning system can be configured with a single chip of

µ

PD17072 or 17073.

Because the µPD17072 and 17073 can operate at low voltage (VDD = 1.8 to 3.6 V), they are ideal for controlling

battery-cell driven portable devices such as portable radio equipment, headphone stereos, or radio cassette

recorders.

FEATURES

• 17K architecture: general-purpose register system

• Program memory (ROM)

µ

6 KB (3072 × 16 bits):

8 KB (4096 × 16 bits): µPD17073

• General-purpose data memory (RAM)

176 × 4 bits

• Instruction execution time

µ

s (with 75-kHz crystal resonator: normal operation)

53.3

µ

106.6

• Decimal operation

• Table reference

• Hardware for PLL frequency synthesizer

Dual modulus prescaler (230 MHz max.), programmable divider, phase comparator, charge pump

• Various peripheral hardware

General-purpose I/O ports, LCD controller/driver, serial interface, A/D converter, BEEP, intermediate frequency

(IF) counter

• Many interrupts

External: 1 channel

Internal: 2 channels

• Power-ON reset, CE reset, and power failure detector

• CMOS low power consumption

• Supply voltage: V

s (with 75-kHz crystal resonator: low-speed mode)

DD = 1.8 to 3.6 V

PD17072

Unless otherwise stated, the

The information in this document is subject to change without notice.

Document No. U11450EJ1V0DS00 (1st edition)

Date Published September 1996 P

Printed in Japan

µ

PD17073 is taken as a representative product in this document.

©

1996

Page 2

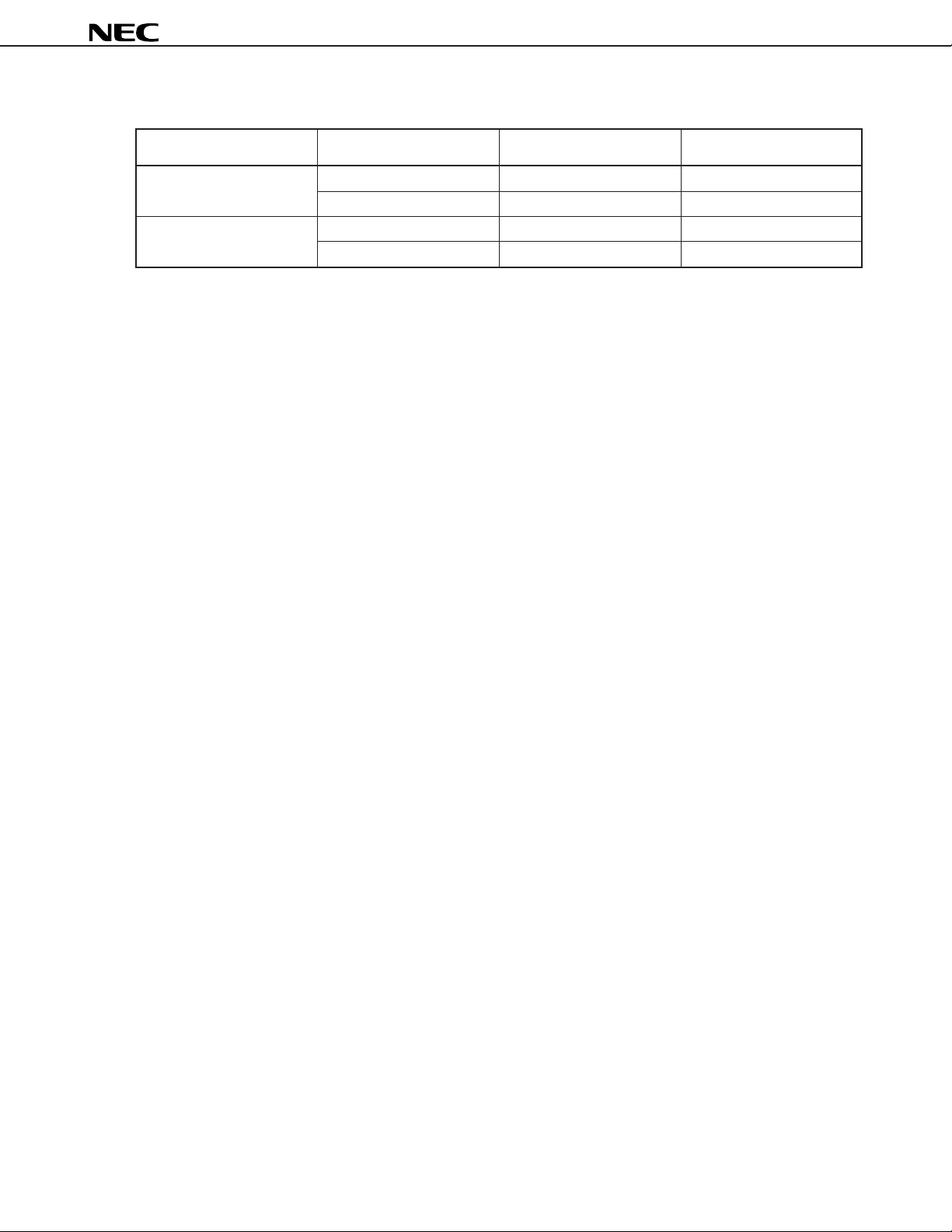

ORDERING INFORMATION

Part Number Package

µ

PD17072GB-×××-1A7 56-pin plastic QFP (10 × 10 mm, 0.65-mm pitch)

µ

PD17072GB-×××-9EU 64-pin plastic TQFP (fine pitch) (10 × 10 mm, 0.5-mm pitch)

µ

PD17073GB-×××-1A7 56-pin plastic QFP (10 × 10 mm, 0.65-mm pitch)

µ

PD17073GB-×××-9EU 64-pin plastic TQFP (fine pitch) (10 × 10 mm, 0.5-mm pitch)

Remark ××× is a ROM code number.

µ

PD17072,17073

2

Page 3

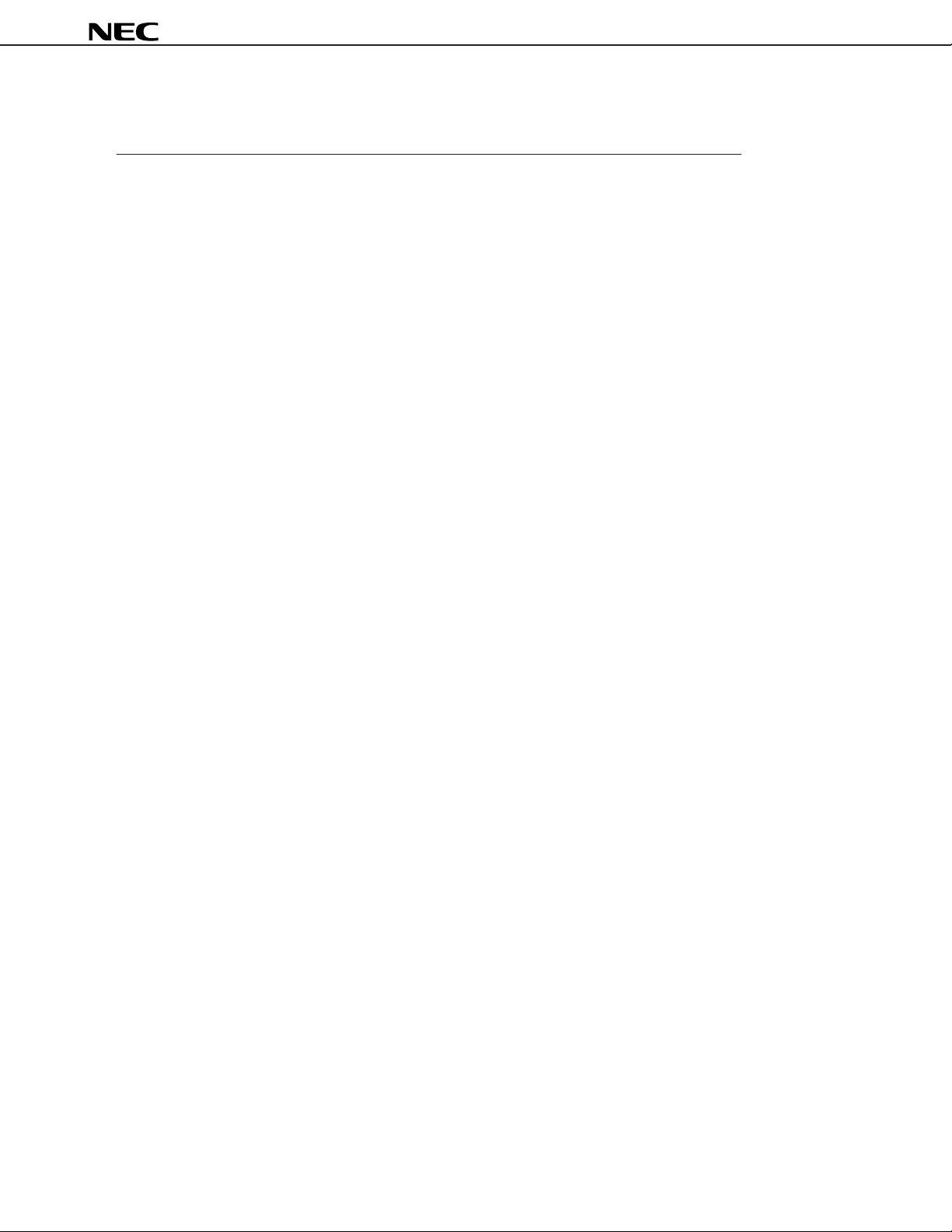

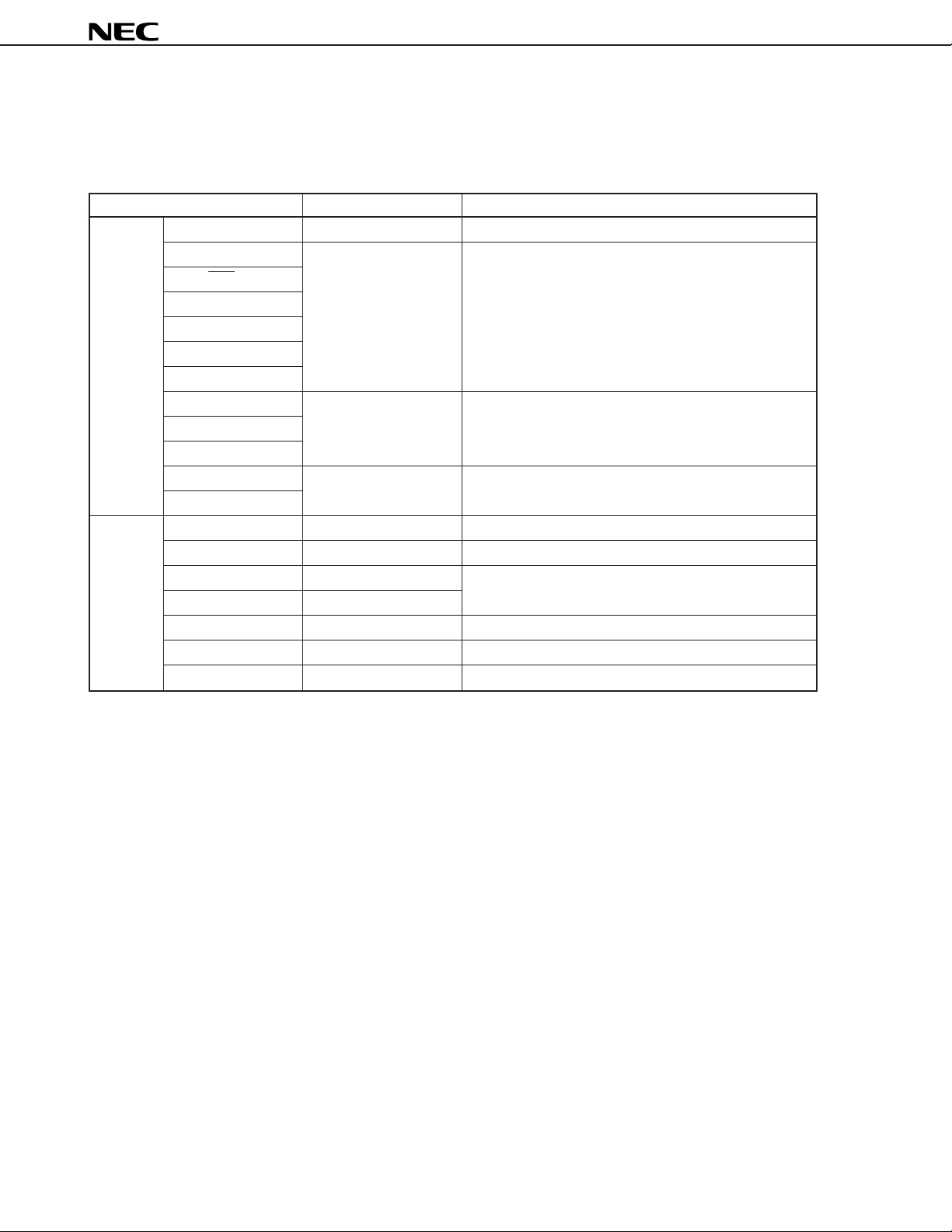

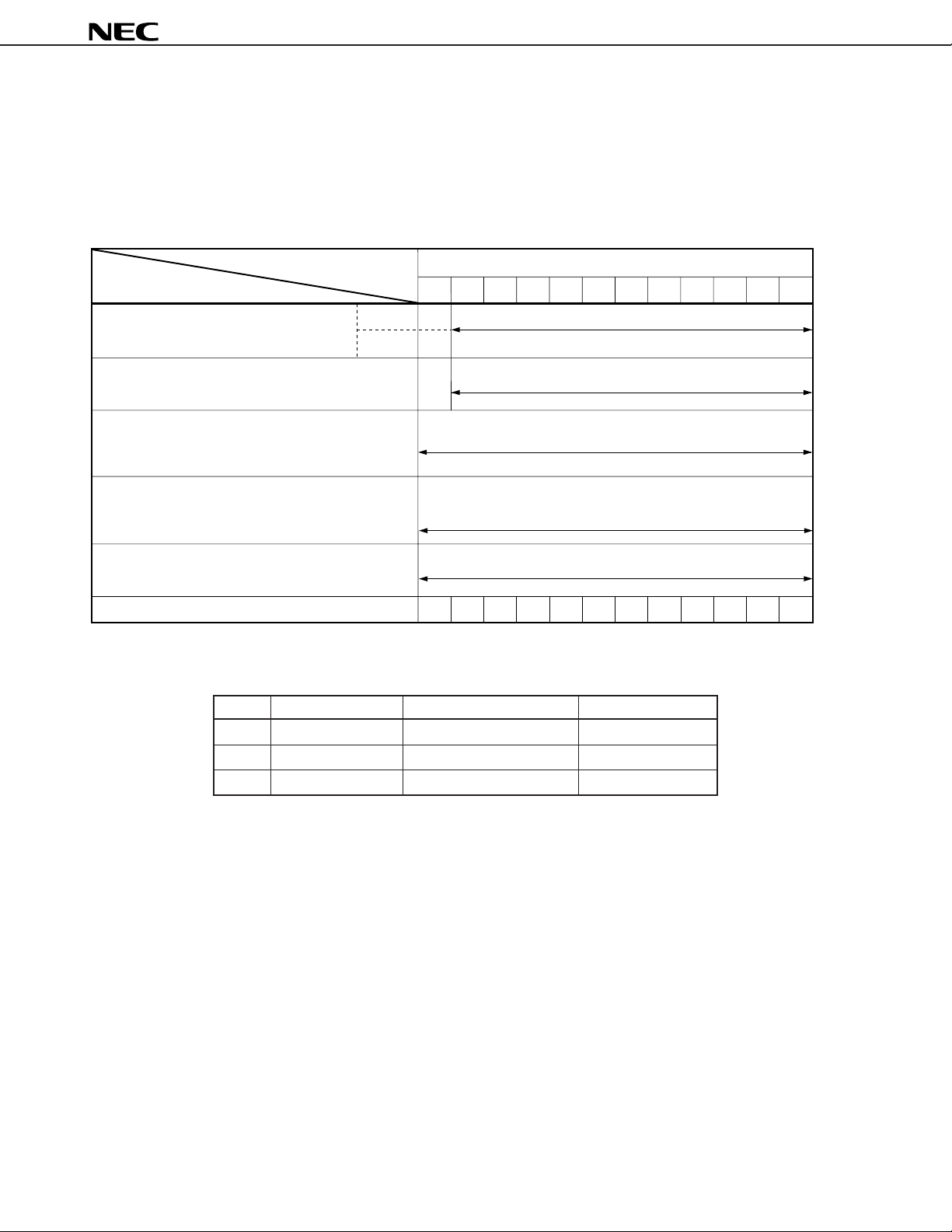

FUNCTION OUTLINE

Item Function

Program memory (ROM) • 6K bytes (3072 × 16 bits): µPD17072

• 8K bytes (4096 × 16 bits): µPD17073

• Table reference area: 4096 × 16 bits

General-purpose data memory • 176 × 4 bits

(RAM) General-purpose register: 16 × 4 bits

(fixed at 00H through 0FH of BANK0, shared with data buffers.)

LCD segment register 15 × 4 bits

Peripheral control register 32 × 4 bits

Instruction execution time • 53.3 µs (with 75-kHz crystal resonator: normal operation)

• 106.6 µs (with 75-kHz crystal resonator: low-speed mode)

Selectable by software

Stack level • Address stack: 2 levels (stack can be manipulated)

• Interrupt stack: 1 level (stack cannot be manipulated)

General-purpose port • I/O port: 8

• Input port: 4

• Output port: 9

BEEP • 1 type

• Selectable frequency (1.5 kHz, 3 kHz)

LCD controller/driver • 15 segments, 4 commons

1/4 duty, 1/2 bias, frame frequency of 62.5 Hz, drive voltage VLCD1 = 3.1 V (TYP.)

Serial interface • 1 channel (Serial I/O mode)

3-wire/2-wire mode selectable

A/D converter 4 bits × 2 channels (successive approximation via software)

Interrupt • 3 channels (maskable interrupt)

External interrupt: 1 (INT pin)

Internal interrupt: 2 (basic timer 1, serial interface)

Timer • 2 channels

Basic timer 0: 125 ms

Basic timer 1: 8 ms, 32 ms

Reset • Power-ON reset (on power application)

• Reset by CE pin (CE pin: low level → high level)

• Power failure detection function

PLL Division method • Direct division method (VCOL pin: 8 MHz MAX.)

frequency • Pulse swallow method (VCOL pin: 55 MHz MAX.)

synthesizer (VCOH pin: 230 MHz MAX.)

Reference • 6 types selectable by program

frequency 1, 3, 5, 6.25, 12.5, 25 kHz

Charge pump Error out output: 1 line (EO pin)

Phase comparator Unlock detectable by program

Frequency counter • Frequency measurement

P0D3/FMIFC/AMIFC pin: FMIF mode, 10 to 11 MHz

P0D3/FMIFC/AMIFC pin: AMIF mode

P0D2/AMIFC pin

Supply voltage VDD = 1.8 to 3.6 V

Package • 56-pin plastic QFP (10 × 10 mm, 0.65-mm pitch)

• 64-pin plastic TQFP (10 × 10 mm, 0.5-mm pitch)

400 to 500 kHz

µ

PD17072,17073

3

Page 4

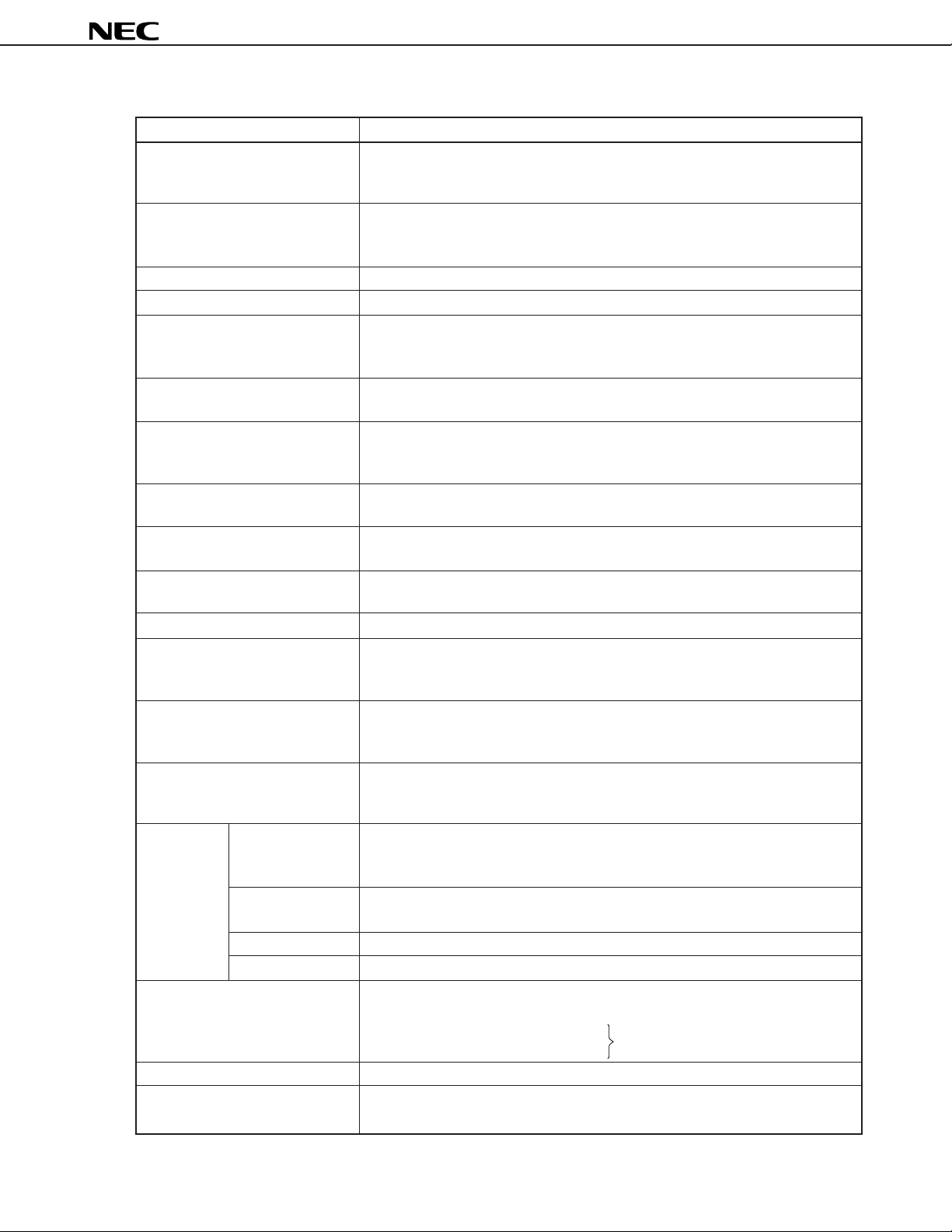

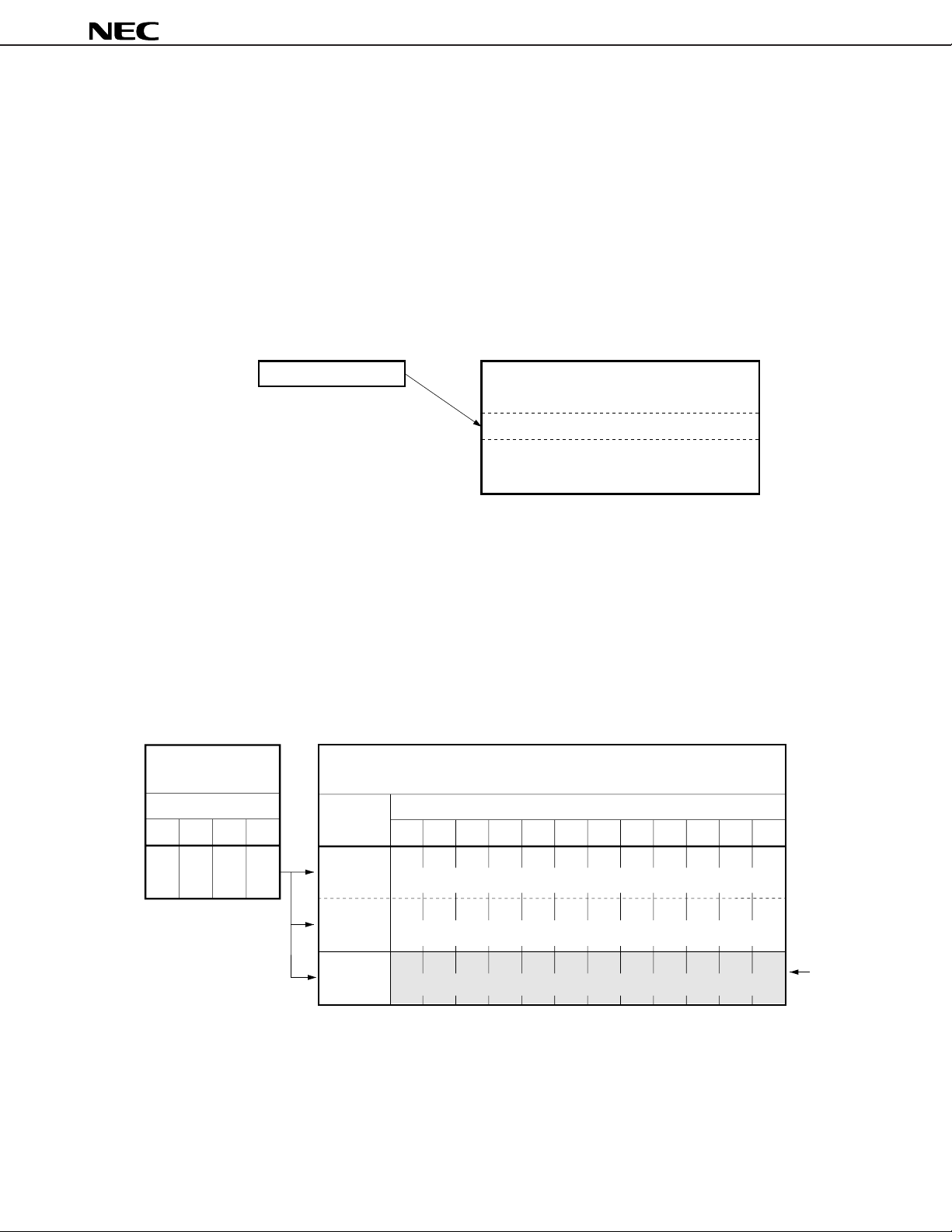

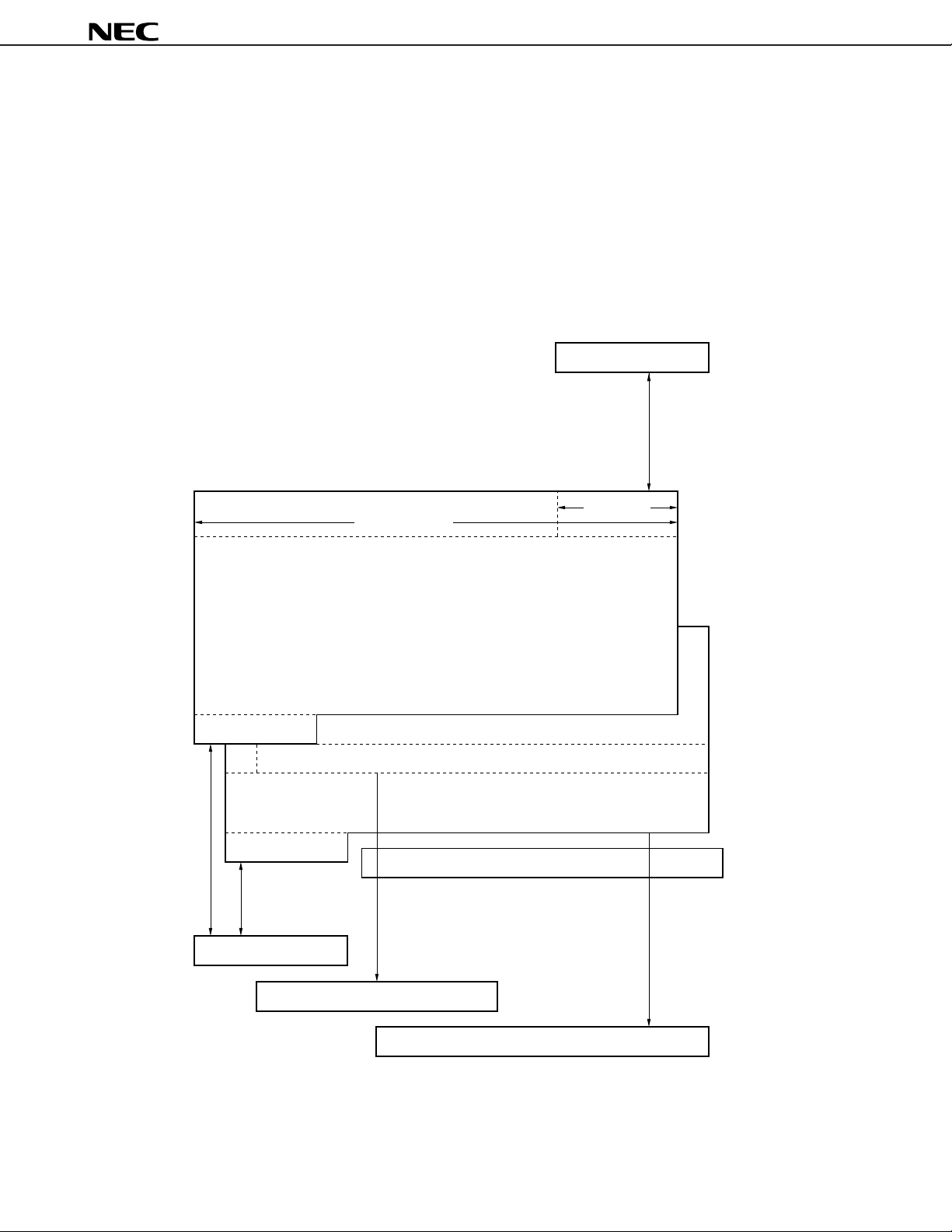

BLOCK DIAGRAM

µ

PD17072,17073

P0A0-P0A3

P0B0-P0B3

P0C0, P0C1

P0D2, P0D3

P1A0-P1A3

P1B0-P1B3

P1C0

LCD

REG

LCD

REG

CAP

LCD

LCD

CAP

SCK/P0B2

Serial

Interface

RAM

SI/SO1/P0B3

SO0/P1C0

176×4 bits

BEEP

BEEP

SYSTEM REG.

Port

Interrupt

Controller

INT

ALU

Basic Timer0

Instruction

Decoder

0

1

0

Voltage

Doubler

3072×16 bits ( PD17072)

4096×16 bits ( PD17073)

ROM

µ

µ

1

Basic Timer1

A/D

Converter

Frequency

Counter

AD0/P1A2

AD1/P1A3

FMIFC/AMIFC/P0D3

AMIFC/P0D2

COM0

COM3

LCD0

LCD14

X

X

OUT

REG1

LCD

Controller

/Driver

Program Counter

12 bits

PLL

Stack

EO

VCOH

VCOL

2×12 bits

PLL

Voltage

REG0

Regulator

IN

OSC

XTAL

Voltage

CPU

Peripheral

Reset

DD

V

CE

GND

Regulator

4

Page 5

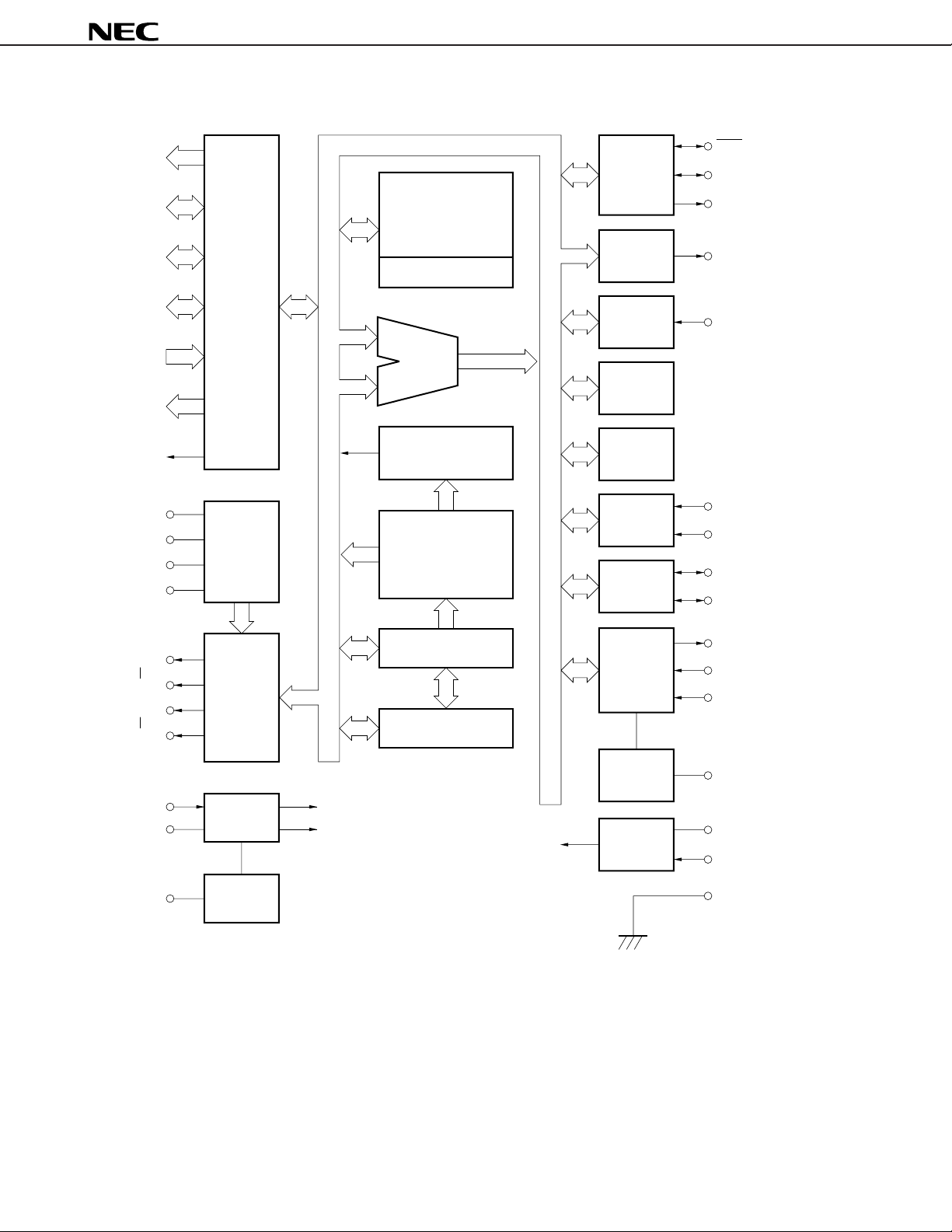

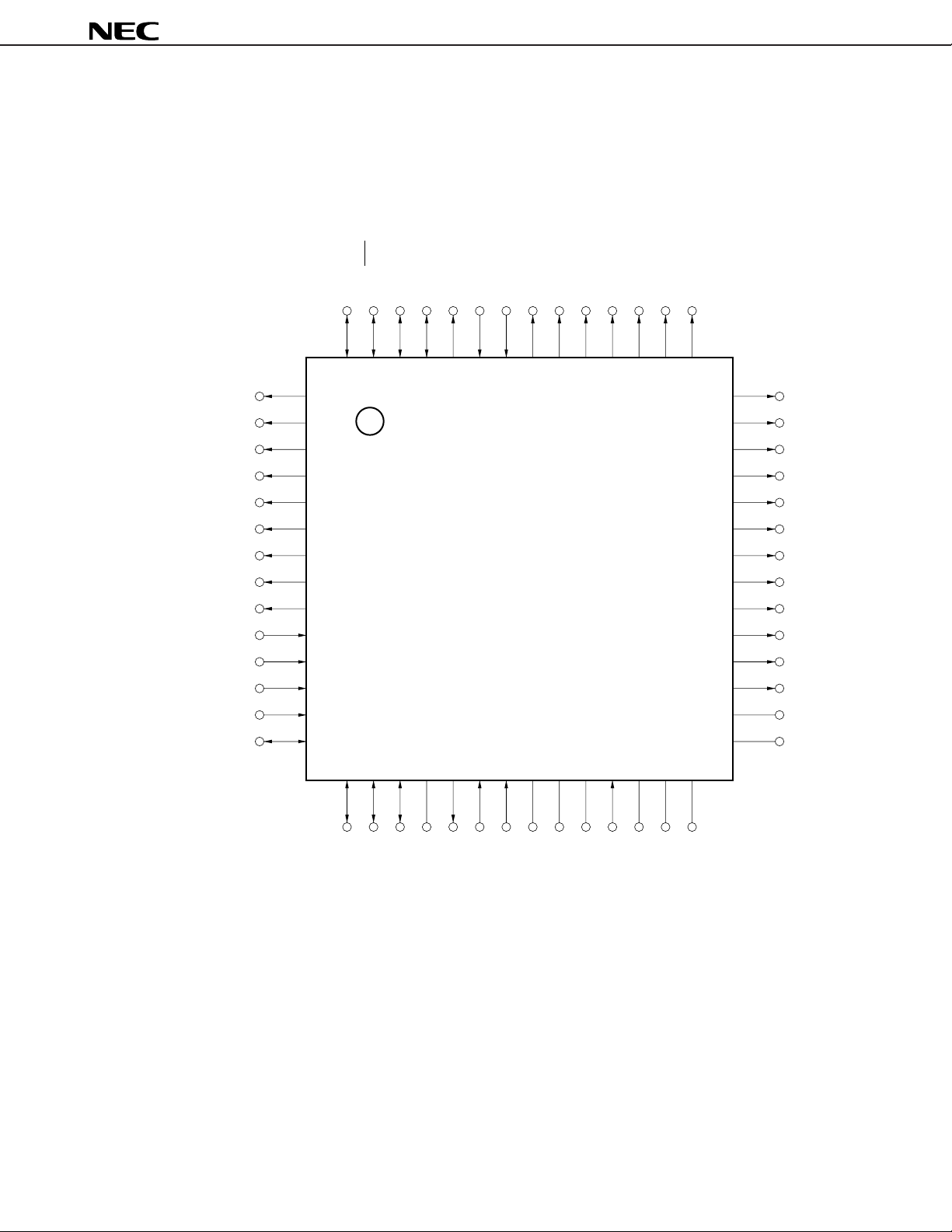

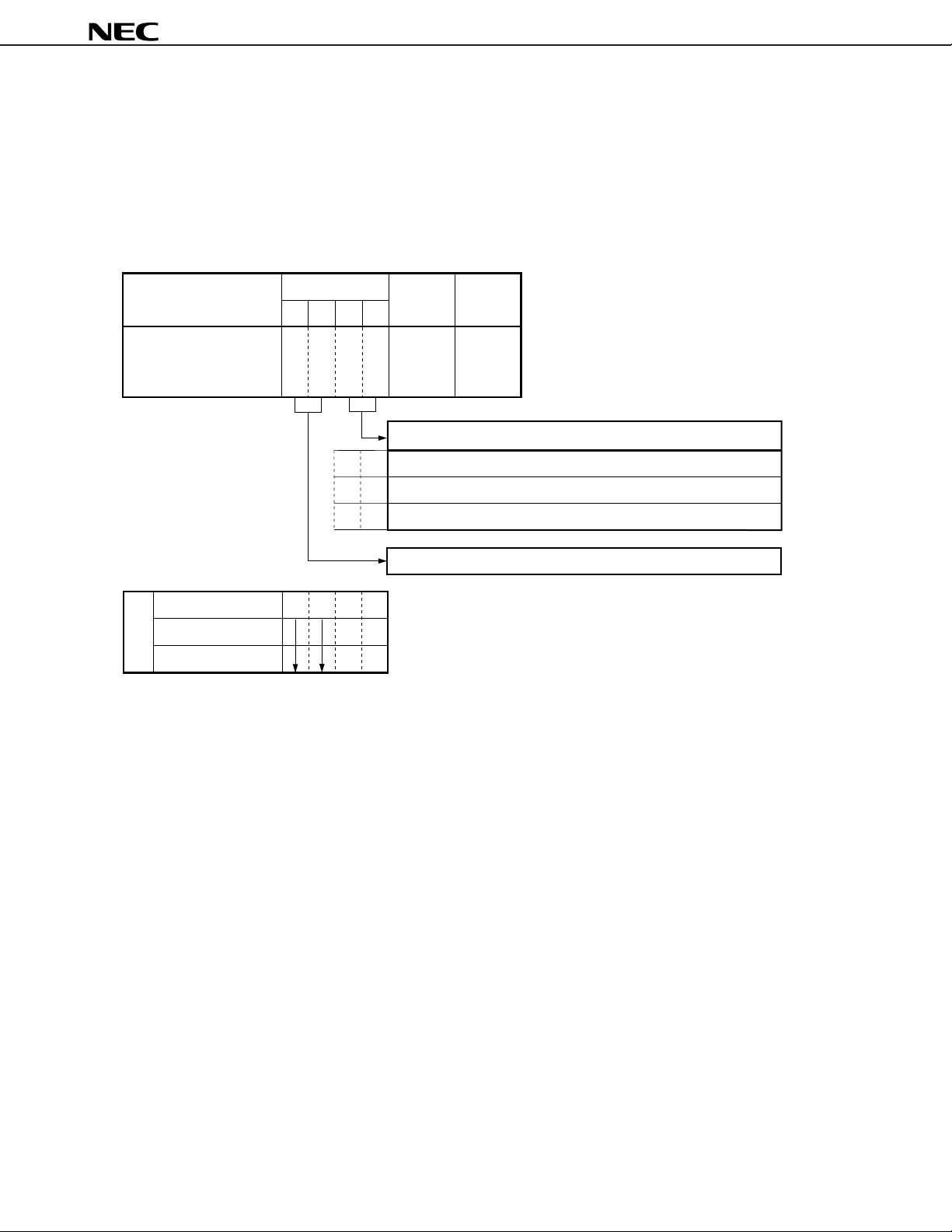

PIN CONFIGURATION (Top View)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

42

41

40

39

38

37

36

35

34

33

32

31

30

29

15 16 17 18 19 20 21 22 23 24 25 26 27 28

56 55 54 53 52 51 50 49 48 47 46 45 44 43

P1C0/SO0

P0A0

P0A1

P0A2

P0A3

P1B0

P1B1

P1B2

P1B3

P1A0

P1A1

P1A2/AD0

P1A3/AD1

P0C0

LCD7

LCD6

LCD5

LCD4

LCD3

LCD2

LCD1

LCD0

COM3

COM2

COM1

COM0

REG

LCD1

CAP

LCD1

P0B3/SI/SO1

P0B2/SCK

P0B1

P0B0

BEEP

INT

CE

LCD14

LCD13

LCD12

LCD11

LCD10

LCD9

LCD8

P0C1

P0D2/AMIFC

P0D3/FMIFC/AMIFC

GND

EO

VCOL

VCOH

REG0

V

DD

XOUT

XIN

REG1

REG

LCD0

CAP

LCD0

56-pin plastic QFP (10 × 10 mm)

µ

PD17072GB-×××-1A7

µ

PD17073GB-×××-1A7

µ

PD17072,17073

5

Page 6

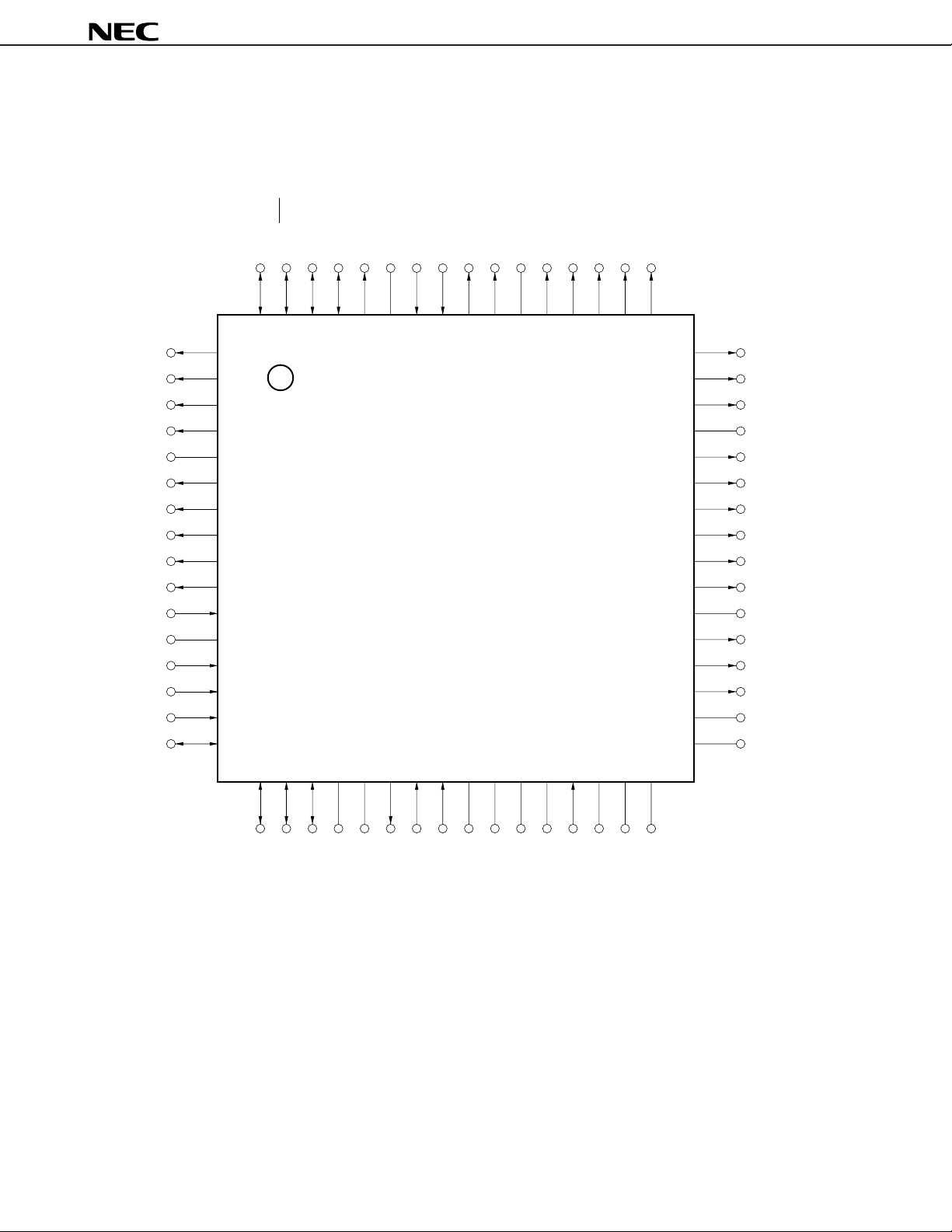

64-pin plastic TQFP (fine pitch) (10 × 10 mm)

µ

PD17072GB-×××-9EU

µ

PD17073GB-×××-9EU

P0B3/SI/SO1

P0B2/SCK

P0B1

P0B0

BEEPNCINT

64 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49

P1C0/SO0

P0A0

P0A1

P0A2

NC

P0A3

P1B0

P1B1

P1B2

P1B3

P1A0

NC

P1A1

P1A2/AD0

P1A3/AD1

P0C0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

CE

LCD14

LCD13NCLCD12

LCD11

LCD10

LCD9

µ

PD17072,17073

LCD8

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

LCD7

LCD6

LCD5

NC

LCD4

LCD3

LCD2

LCD1

LCD0

COM3

NC

COM2

COM1

COM0

REG

CAP

LCD

LCD

1

1

17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32

0

P0C1

GND

GND

EO

VCOL

VCOH

REG0

DDVDD

V

OUT

X

IN

X

REG1

LCD

REG

0

LCD

CAP

P0D2/AMIFC

P0D3/FMIFC/AMIFC

6

Page 7

PIN IDENTIFICATION

AD0, AD1 : A/D converter input

AMIFC : Intermediate frequency (IF) counter input

BEEP : BEEP output

CLD0, CAPLCD1 : Capacitor connection for LCD drive voltage

CAP

CE : Chip enable

COM0-COM2 : LCD common signal output

EO : Error out

FMIFC : Intermediate frequency (IF) counter input

GND : Ground

INT : External interrupt request signal input

LCD0-LCD14 : LCD segment signal output

NC : No connection

P0A0-P0A3 : Port 0A

P0B0-P0B3 : Port 0B

P0C0, P0C1 : Port 0C

P0D2, P0D3 : Port 0D

P1A0-P1A3 : Port 1A

P1B0-P1B3 : Port 1B

P1C0 : Port 1C

LCD0, REGLCD1 : LCD drive voltage

REG

REG0 : PLL voltage regulator

REG1 : Oscillation circuit voltage regulator

SCK : Serial clock I/O

SI : Serial data input

SO0, SO1 : Serial data output

VCOL : Local oscillator input

VCOH : Local oscillator input

DD : Positive power supply

V

XIN, XOUT : Crystal resonator connection pins

µ

PD17072,17073

7

Page 8

µ

PD17072,17073

CONTENTS

1. PIN FUNCTION.................................................................................................................................. 12

1.1 Pin Function List ...................................................................................................................................... 12

1.2 Equivalent Circuits of Pins....................................................................................................................... 15

1.3 Processing of Unused Pins ..................................................................................................................... 18

1.4 Notes on Using CE Pin............................................................................................................................ 19

2. PROGRAM MEMORY (ROM) ........................................................................................................... 20

2.1 General ..................................................................................................................................................... 2 0

2.2 Program Memory ..................................................................................................................................... 21

2.3 Program Counter......................................................................................................................................21

2.4 Execution Flow of Program Memory ....................................................................................................... 2 2

2.5 Notes on Using Program Memory........................................................................................................... 22

3. ADDRESS STACK (ASK) ................................................................................................................. 23

3.1 General ..................................................................................................................................................... 2 3

3.2 Address Stack Register (ASR) ................................................................................................................ 23

3.3 Stack Pointer (SP) ................................................................................................................................... 24

3.4 Operations of Address Stack................................................................................................................... 25

3.5 Notes on Using Address Stack................................................................................................................ 2 5

4. DATA MEMORY (RAM) ..................................................................................................................... 26

4.1 General ..................................................................................................................................................... 2 6

4.2 Configuration and Function of Data Memory.......................................................................................... 27

4.3 Addressing Data Memory ........................................................................................................................ 30

4.4 Notes on Using Data Memory ................................................................................................................. 31

5. SYSTEM REGISTER (SYSREG) ...................................................................................................... 32

5.1 General ..................................................................................................................................................... 3 2

5.2 Address Register (AR)............................................................................................................................. 33

5.3 Bank Register (BANK) ............................................................................................................................. 35

5.4 Program Status Word (PSWORD).......................................................................................................... 36

5.5 Notes on Using System Register ............................................................................................................ 37

6. GENERAL REGISTERS (GR)........................................................................................................... 38

6.1 Outline of General Registers ................................................................................................................... 38

6.2 Address Creation of General Register with Each Instruction ................................................................ 3 9

6.3 Notes on Using General Register ........................................................................................................... 39

7. ALU (ARITHMETIC LOGIC UNIT) BLOCK....................................................................................... 40

7.1 General ..................................................................................................................................................... 4 0

7.2 Configuration and Function of Each Block ............................................................................................. 41

7.3 ALU Processing Instructions ................................................................................................................... 41

7.4 Notes on Using ALU ................................................................................................................................44

8

Page 9

µ

PD17072,17073

8. PERIPHERAL CONTROL REGISTERS ........................................................................................... 45

8.1 Outline of Peripheral Control Registers .................................................................................................. 45

8.2 Configuration and Function of Peripheral Control Registers ................................................................. 46

9. DATA BUFFER (DBF) ....................................................................................................................... 54

9.1 General ..................................................................................................................................................... 5 4

9.2 Data Buffer ............................................................................................................................................... 55

9.3 List of Peripheral Hardware and Data Buffer Functions ........................................................................ 56

9.4 Notes on Using Data Buffer ..................................................................................................................... 56

10. GENERAL-PURPOSE PORT ............................................................................................................ 57

10.1 General..................................................................................................................................................... 57

10.2 General-Purpose I/O Ports (P0B, P0C, P0D) ......................................................................................... 58

10.3 General-Purpose Input Ports (P1A) ........................................................................................................ 62

10.4 General-Purpose Output Ports (P0A, P1B, P1C)................................................................................... 6 5

11. INTERRUPT....................................................................................................................................... 6 6

11.1 General..................................................................................................................................................... 66

11.2 Interrupt Control Block............................................................................................................................. 67

11.3 Interrupt Stack Register........................................................................................................................... 70

11.4 Stack Pointer, Address Stack Register, and Program Counter ............................................................. 72

11.5 Interrupt Enable Flip-Flop (INTE)............................................................................................................ 72

11.6 Accepting Interrupt................................................................................................................................... 73

11.7 Operations after Accepting Interrupt ....................................................................................................... 77

11.8 Exiting from Interrupt Service Routine.................................................................................................... 78

11.9 External (INT Pin) Interrupts ................................................................................................................... 79

11.10 Internal Interrupt....................................................................................................................................... 81

12. TIMER ................................................................................................................................................ 82

12.1 General..................................................................................................................................................... 82

12.2 Basic Timer 0 ........................................................................................................................................... 82

12.3 Basic Timer 1 ........................................................................................................................................... 91

13. A/D CONVERTER ............................................................................................................................. 98

13.1 General..................................................................................................................................................... 98

13.2 Setting A/D Converter Power Supply ...................................................................................................... 99

13.3 Input Selector Block............................................................................................................................... 100

13.4 Compare Voltage Generator Block and Compare Block ..................................................................... 102

13.5 Comparison Timing Chart...................................................................................................................... 107

13.6 Perfor mance of A/D Converter .............................................................................................................. 107

13.7 Using A/D Converter .............................................................................................................................. 108

13.8 Status at Reset .......................................................................................................................................111

14. SERIAL INTERFACE ....................................................................................................................... 112

14.1 General................................................................................................................................................... 112

14.2 Clock Input/Output Control Block and Data Input/Output Control Block............................................. 113

14.3 Clock Control Block ............................................................................................................................... 116

14.4 Clock Counter ........................................................................................................................................ 116

9

Page 10

µ

PD17072,17073

14.5 Presettable Shift Register...................................................................................................................... 117

14.6 Wait Control Block ................................................................................................................................ . 117

14.7 Serial Interface Operation ..................................................................................................................... 118

14.8 Notes on Setting and Reading Data ..................................................................................................... 122

14.9 Operational Outline of Serial Interface ................................................................................................. 123

14.10 Status on Reset ..................................................................................................................................... 125

15. PLL FREQUENCY SYNTHESIZER ................................................................................................ 126

15.1 General................................................................................................................................................... 126

15.2 Input Selector Block and Programmable Divider ................................................................................. 127

15.3 Reference Frequency Generator ........................................................................................................... 133

φ

15.4 Phase Comparator (

15.5 PLL Disable Status ................................................................................................................................ 139

15.6 Use of PLL Frequency Synthesizer ...................................................................................................... 1 40

15.7 Status on Reset ..................................................................................................................................... 143

-DET), Charge Pump, and Unlock FF ............................................................... 135

16. INTERMEDIATE FREQUENCY (IF) COUNTER ............................................................................. 14 4

16.1 Outline of Intermediate Frequency (IF) Counter .................................................................................. 1 44

16.2 IF Counter Input Selector Block and Gate Time Control Block ........................................................... 145

16.3 Start Control Block and IF Counter....................................................................................................... 147

16.4 Using IF Counter.................................................................................................................................... 152

16.5 Status at Reset ...................................................................................................................................... 154

17. BEEP................................................................................................................................................ 1 55

17.1 Configuration and Function of BEEP .................................................................................................... 155

17.2 Output Wave Form of BEEP ................................................................................................................. 156

17.3 Status at Reset ...................................................................................................................................... 157

18. LCD CONTROLLER/DRIVER ......................................................................................................... 15 8

18.1 Outline of LCD Controller/Driver ........................................................................................................... 158

18.2 LCD Drive Voltage Generation Block .................................................................................................... 159

18.3 LCD Segment Register.......................................................................................................................... 160

18.4 Common Signal Output and Segment Signal Output Timing Control Blocks ..................................... 162

18.5 Common Signal and Segment Signal Output Waves .......................................................................... 163

18.6 Using LCD Controller/Driver.................................................................................................................. 165

18.7 Status at Reset ...................................................................................................................................... 167

19. STANDBY ........................................................................................................................................ 168

19.1 General................................................................................................................................................... 168

19.2 Halt Function .......................................................................................................................................... 1 70

19.3 Clock Stop Function............................................................................................................................... 178

19.4 Device Operations in Halt and Clock Stop Statuses ............................................................................ 181

19.5 Note on Processing of Each Pin in Halt and Clock Stop Statuses ..................................................... 1 82

19.6 Device Control Function by CE Pin ...................................................................................................... 185

19.7 Low-Speed Mode Function .................................................................................................................... 187

10

Page 11

µ

PD17072,17073

20. RESET .............................................................................................................................................. 188

20.1 Configuration of Reset Block................................................................................................................. 1 88

20.2 Reset Function ....................................................................................................................................... 18 9

20.3 CE Reset ................................................................................................................................................ 190

20.4 Power-ON Reset .................................................................................................................................... 19 4

20.5 Relations between CE Reset and Power-ON Reset............................................................................ 197

20.6 Power Failure Detection ........................................................................................................................ 199

21.µPD17012 INSTRUCTIONS ............................................................................................................ 20 4

21.1 Instruction Set Outline ........................................................................................................................... 204

21.2 Legend.................................................................................................................................................... 20 5

21.3 Instruction List........................................................................................................................................ 206

21.4 Assembler (AS17K) Embedded Macroinstructions .............................................................................. 207

22.µPD17073 RESERVED WORDS .................................................................................................... 208

22.1 Data Buffer (DBF) .................................................................................................................................. 208

22.2 System Register (SYSREG).................................................................................................................. 208

22.3 LCD Segment Register.......................................................................................................................... 209

22.4 Port Register .......................................................................................................................................... 210

22.5 Peripheral Control Register ................................................................................................................... 211

22.6 Peripheral Hardware Register .....................................................................................................................

22.7 Others..................................................................................................................................................... 213

23. ELECTRICAL CHARACTERISTICS ............................................................................................... 214

24. PACKAGE DRAWINGS ................................................................................................................... 217

25. RECOMMENDED SOLDERING CONDITIONS .............................................................................. 219

APPENDIX A. NOTES ON CONNECTING CRYSTAL RESONATOR................................................220

APPENDIX B. DEVELOPMENT TOOLS ..............................................................................................221

11

Page 12

µ

PD17072,17073

1. PIN FUNCTION

1.1 Pin Function List

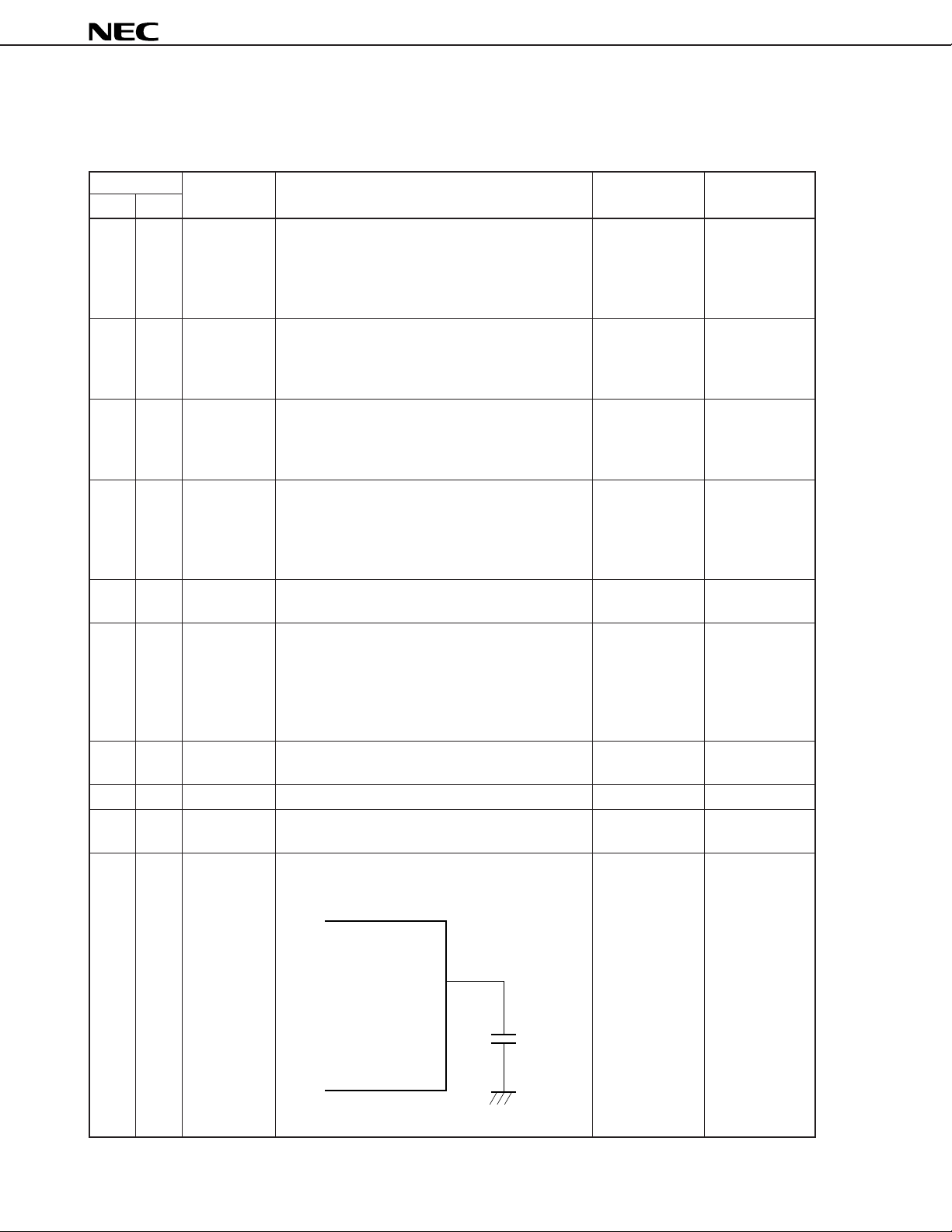

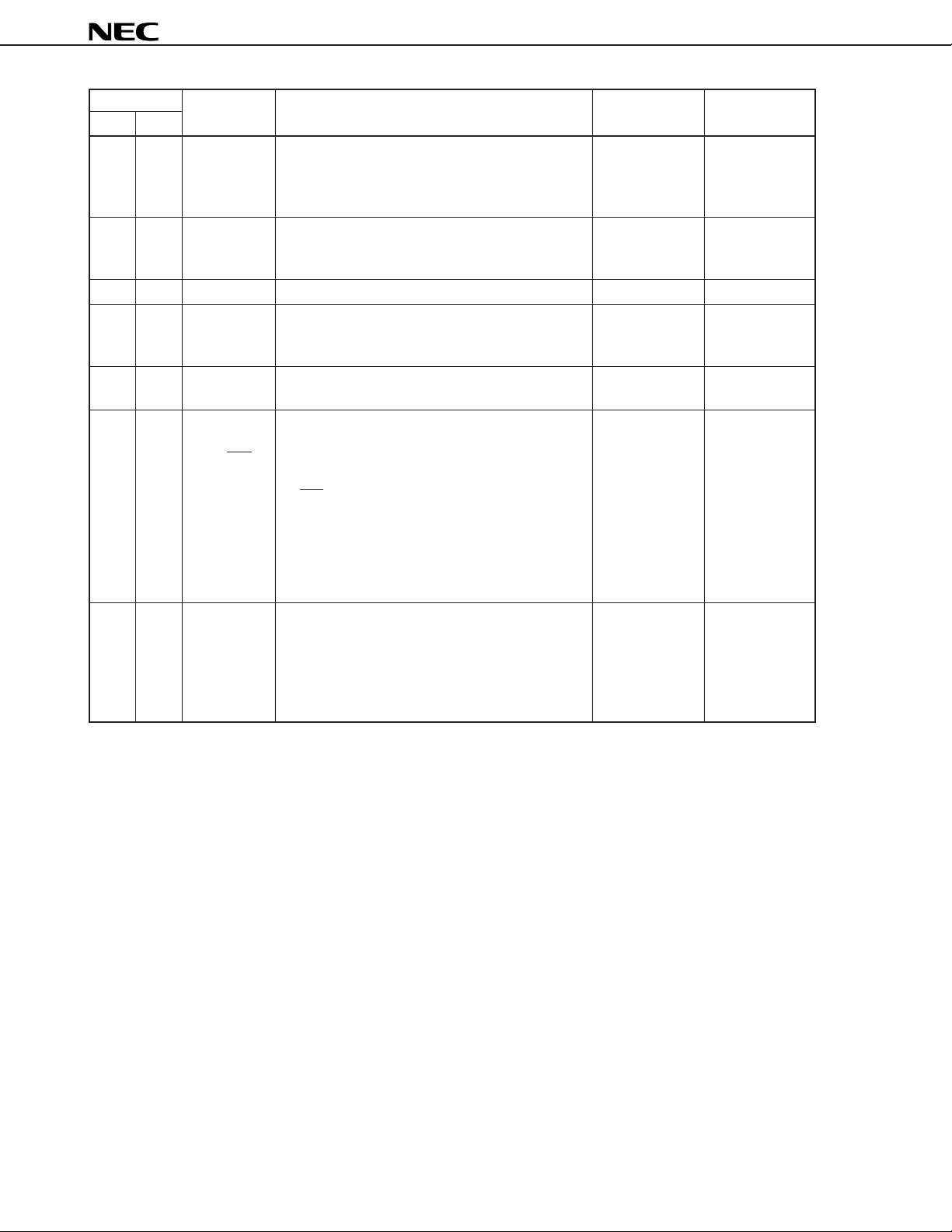

Pin No. Symbol Function Output format At power-ON

QFP TQFP reset

1 1 P1C0/SO0 Port 1C and output of serial interface. CMOS push-pull Low-level output

P1C0

•

• 1-bit output port

SO0

•

• Serial data output

2 2 P0A0 4-bit output port (port 0A). CMOS push-pull Low-level output

3 3 P0A1

4 4 P0A2

5 6 P0A3

6 7 P1B0 4-bit output port (port 1B). CMOS push-pull Low-level output

7 8 P1B1

8 9 P1B2

9 10 P1B3

10 11 P1A0 Port 1A and analog inputs to A/D converter. — Inputs with pull11 13 P1A1

12 14 P1A2/AD0 • 4-bit input port

13 15 P1A3/AD1

14 16 P0C0 2-bit I/O port (port 0C). CMOS push-pull Input

15 17 P0C1 Input/output mode can be set in 1-bit units.

16 18 P0D2/AMIFC Port 0D and IF counter inputs. CMOS push-pull Input

17 19 P0D3/FMIFC/•P0D3, P0D2

AMIFC • 2-bit I/O port

18 20 GND Ground — —

21

19 22 EO Output from charge pump of PLL frequency synthesizer CMOS 3-state Floating

20 23 VCOL Input local oscillation frequency of PLL. — Floating

21 24 VCOH

22 25 REG0 Output of PLL voltage regulator. — Low-level output

P1A3-P1A0 down resistor

•

AD1, AD0

•

• Analog inputs to A/D converter

• Can be set in input/output mode in 1-bit units.

FMIFC, AMIFC

•

• IF counter inputs

Connect this pin to GND via 0.1-µF capacitor.

12

REG0

0.1 F

µ

Page 13

µ

PD17072,17073

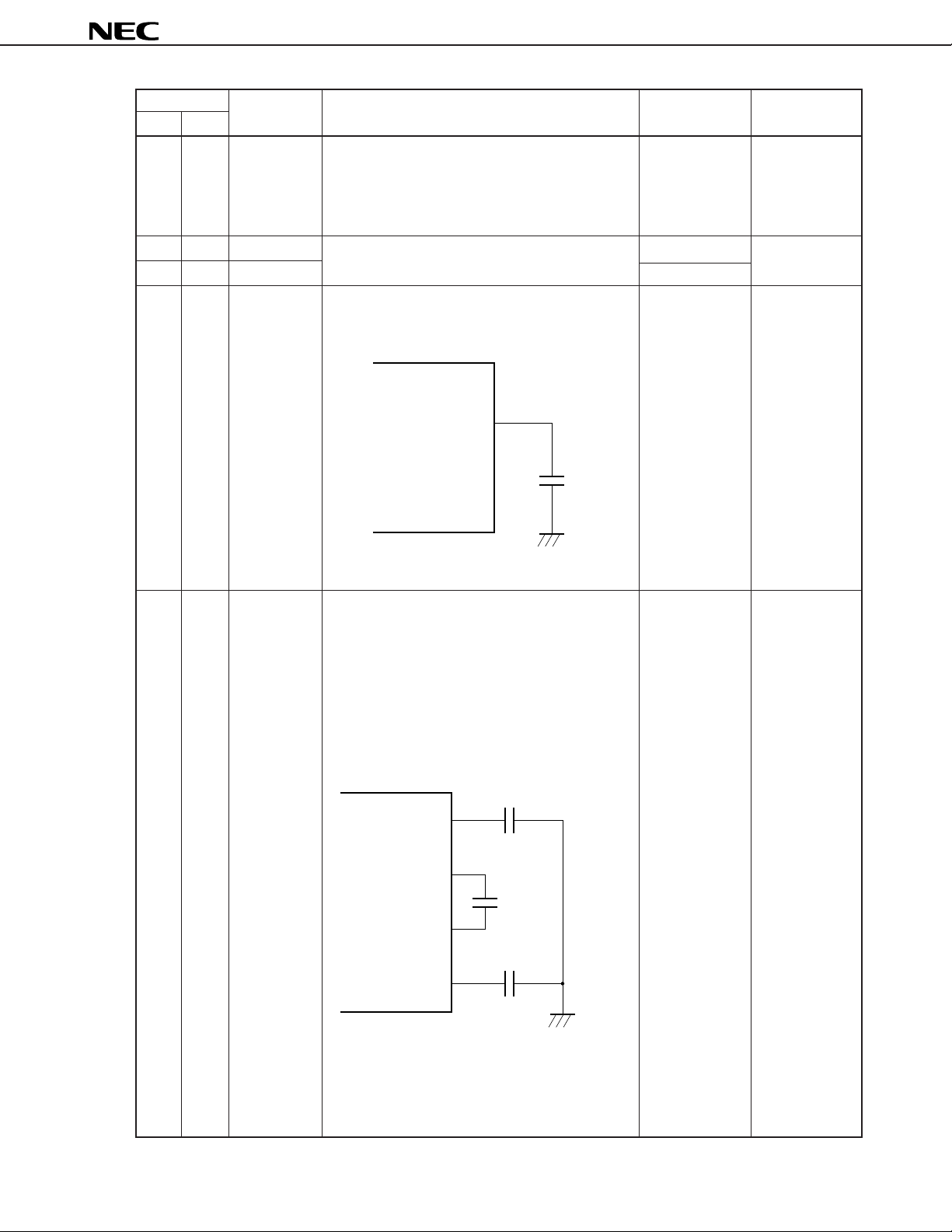

Pin No. Symbol Function Output format At power-ON

QFP TQFP reset

23 26 VDD Positive power supply. — —

27 Supply 1.8 to 3.6 V (TA = –20 to +70 °C) to operate

all functions.

Do not apply voltage higher than that of VDD pin to

any pin other than VDD.

24 28 XOUT Pins for connecting crystal resonator for system CMOS push-pull —

25 29 XIN

26 30 REG1 Output of voltage regulator for oscillation circuit. — —

clock oscillation.

Connect this pin to GND via 0.1-µF capacitor.

REG1

0.1 F

—

µ

27 31 REGLCD0

28 32 CAPLCD0 LCD drive power pins.

29 33 CAPLCD1

30 34 REGLCD1 Connect capacitors for doubler circuit to generate

REGLCD1, REGLCD0——

•

CAPLCD1, CAPLCD0

•

LCD drive voltage, across these pins.

To configure doubler circuit, connect capacitors

as shown below.

REG

CAP

CAP

REG

LCD

LCD

LCD

LCD

C1 = C2 = 0.1 F

C3 = 0.01 F

C1

1

1

C3

0

0

C2

µ

µ

Caution The value of the LCD drive voltage differs

if the values of C1, C2, and C3 are changed

because of the configuration of the doubler

circuit.

13

Page 14

µ

PD17072,17073

Pin No. Symbol Function Output format At power-ON

QFP TQFP reset

31 35 COM0 Common signal outputs of LCD controller/driver. CMOS ternary Low-level output

32 36 COM1 output

33 37 COM2

34 39 COM3

35 40 LCD0 Segment signal outputs of LCD controller/driver. CMOS push-pull Low-level output

| | |

49 56 LCD14

50 57 CE Device operation select and reset signal input. — Input

51 58 INT External interrupt request signal input. — Input

Interrupt request is issued at rising or falling edge

of signal input to this pin.

52 60 BEEP BEEP signal output pin. CMOS push-pull Low-level output

BEEP output of 1.5 kHz or 3 kHz can be selected.

53 61 P0B0 Port 0B and serial interface I/O. CMOS push-pull Input

54 62 P0B1

55 63 P0B2/SCK • 4-bit I/O port

56 64 P0B3/SI/SO1 • Can be set in input or output mode in 1-bit units.

— 5 NC No connection — —

12

38

45

54

59

P0B3-P0B0

•

SCK

•

• Serial clock I/O

SO1

•

• Serial data output

SI

•

• Serial data input

14

Page 15

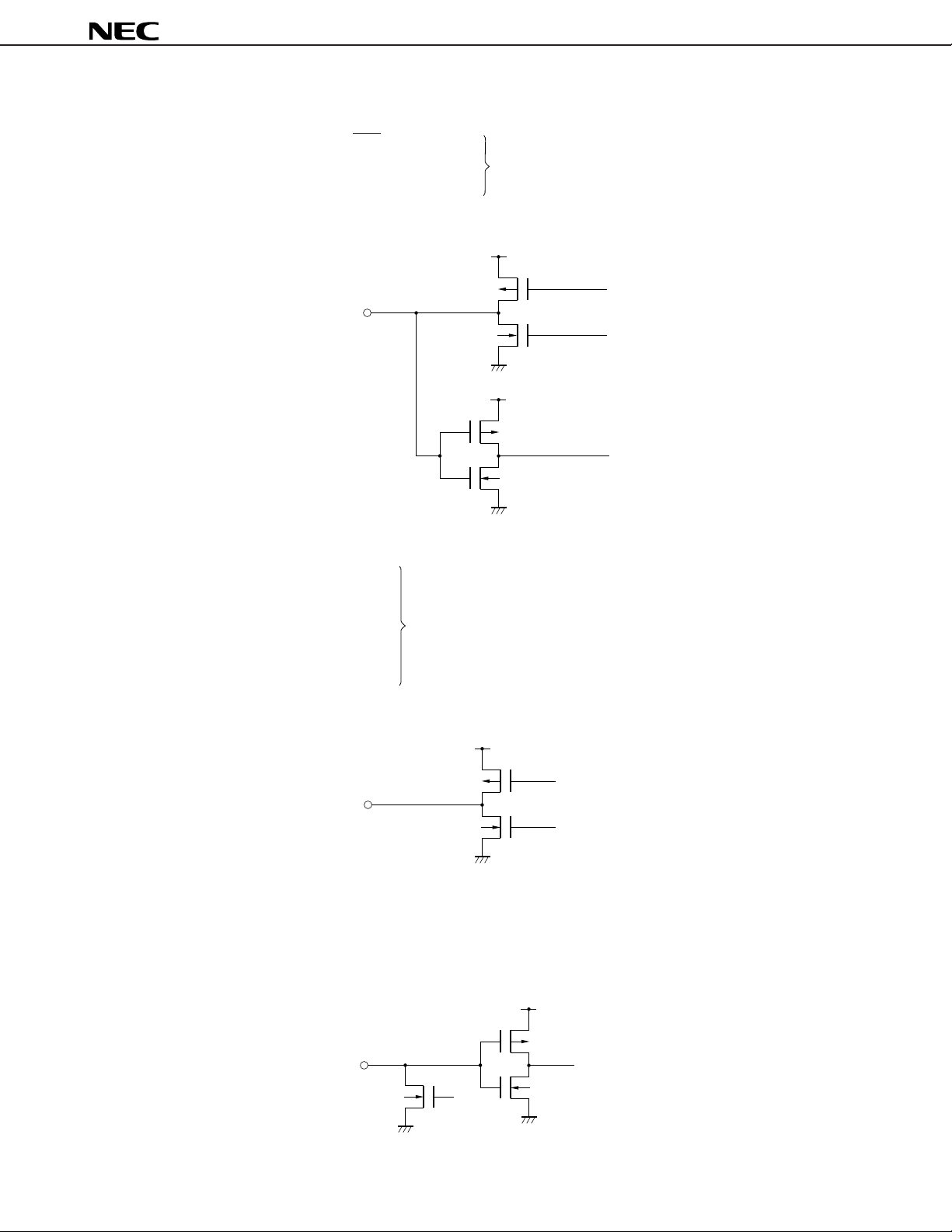

1.2 Equivalent Circuits of Pins

(1) P0B (P0B3/SI/SO1, P0B2/SCK, P0B1, P0B0)

P0C (P0C1, P0C0) (I/O)

P0D (P0D3/FMIFC/AMIFC, P0D2/AMIFC)

µ

PD17072,17073

V

DD

V

DD

(2) P0A (P0A3, P0A2, P0A1, P0A0)

P1B (P1B3, P1B2, P1B1, P1B0)

P1C (P1C0/SO0)

LCD14-LCD0

(Output)

BEEP

EO

V

DD

(3) P1A (P1A3/AD1, P1A2/AD0, P1A1, P1A0) (Input)

V

DD

High ON

resistance

15

Page 16

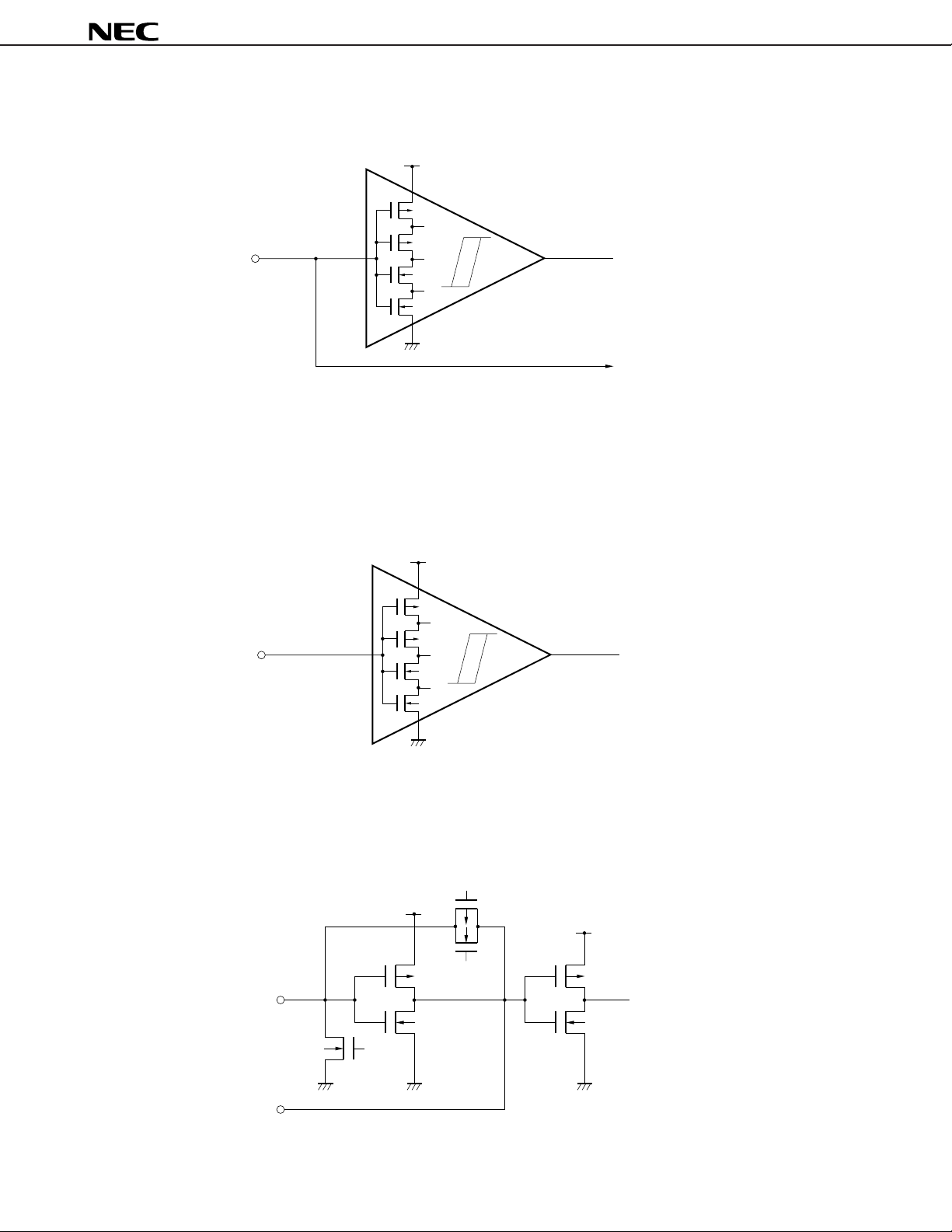

(4) CE (Schmitt trigger input)

(5) INT (Schmitt trigger input)

µ

PD17072,17073

V

DD

CE flag

(6) XOUT (output), XIN (input)

X

IN

V

DD

V

DD

High ON

resistance

V

DD

16

High ON

resistance

OUT

X

Page 17

(7) COM3 through COM0 (output)

(8) VCOH (input)

µ

PD17072,17073

V

V

LCD0

LCD1

High ON resistance

(9) VCOL (input)

VDD

PLL disable signal

VDD

High ON resistance

VDD

PLL disable signal

High ON resistance

VDD

17

Page 18

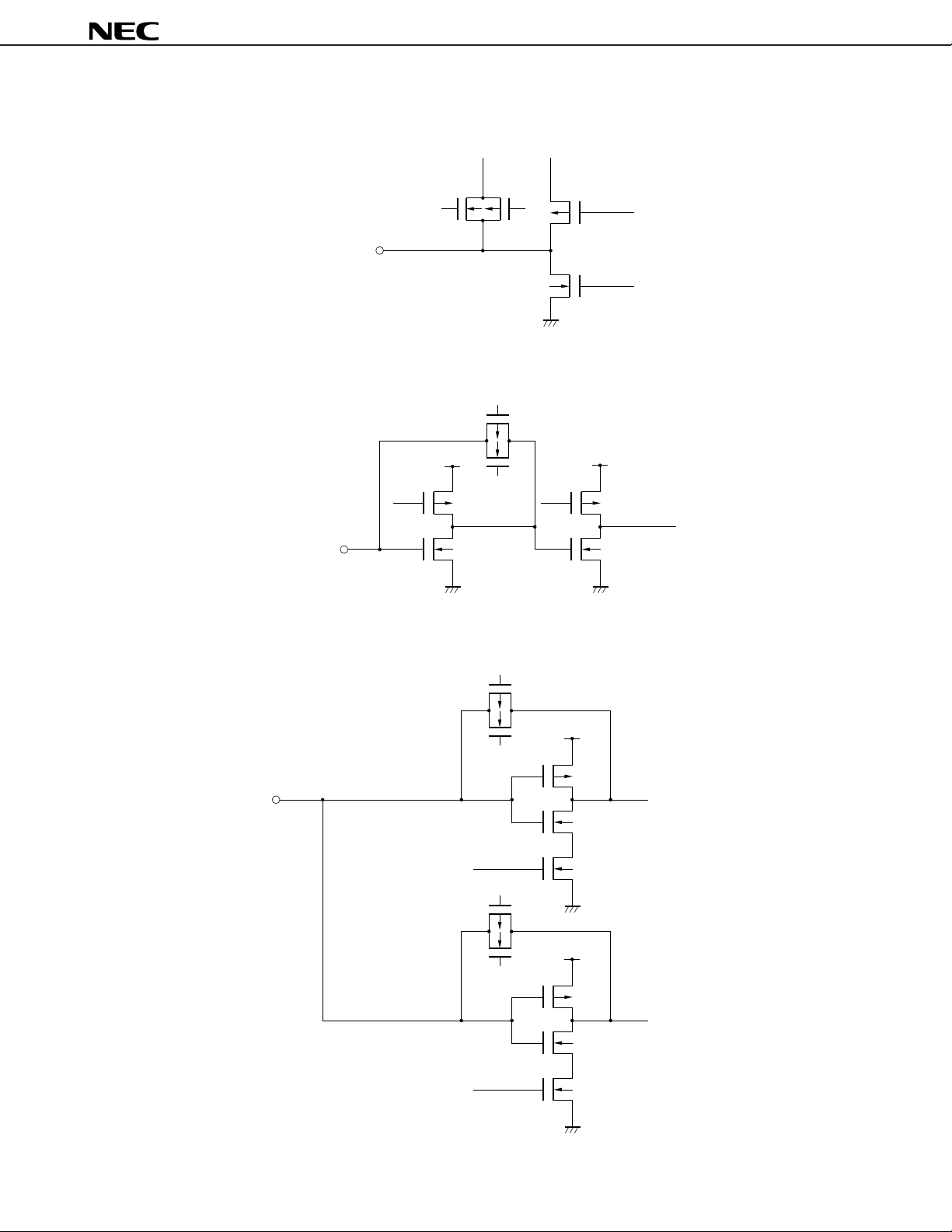

1.3 Processing of Unused Pins

It is recommended that the unused pins be connected as follows:

Table 1-1. Processing of Unused Pins

Pin name I/O mode Recommended processing of unused pins

Port pin P0A0-P0A3 CMOS push-pull output Open

P0B0, P0B1 I/O

P0B2/SCK

P0B3/SI/SO1

P0C0, P0C1

P0D2/AMIFC

P0D3/FMIFC/AMIFC

P1A0, P1A1 Input Connect each of these pins to VDD or GND via resistor

P1A2/AD0

P1A3/AD1

P1B0-P1B3 CMOS push-pull output Open

P1C0/SO0

Pins other BEEP CMOS push-pull output Open

than port

pins

CE Input Connect to VDD via resistor

COM0-COM3 Output Open

EO Output

INT Input Connect to GND via resistor

LCD0-LCD14 CMOS push-pull output Open

VCOH, VCOL Input Connect each of these pins to GND via resistor

Note 1

Set by software to output low level and open

Note 2

Note 2

µ

PD17072,17073

Note 2

.

.

.

Note 2

.

Notes 1. The I/O ports are set in the input mode on power application, on clock stop, and on CE reset.

2. When pulling up (connecting to VDD via resistor) or pulling down (connecting to GND via resistor) a pin

externally with high resistance, the pin almost goes into a high-impedance state, and consequently, the

current consumption (through current) of the port increases. Generally, the pull-up or pull-down

resistance is several 10 kΩ, though it varies depending on the application circuit.

18

Page 19

µ

PD17072,17073

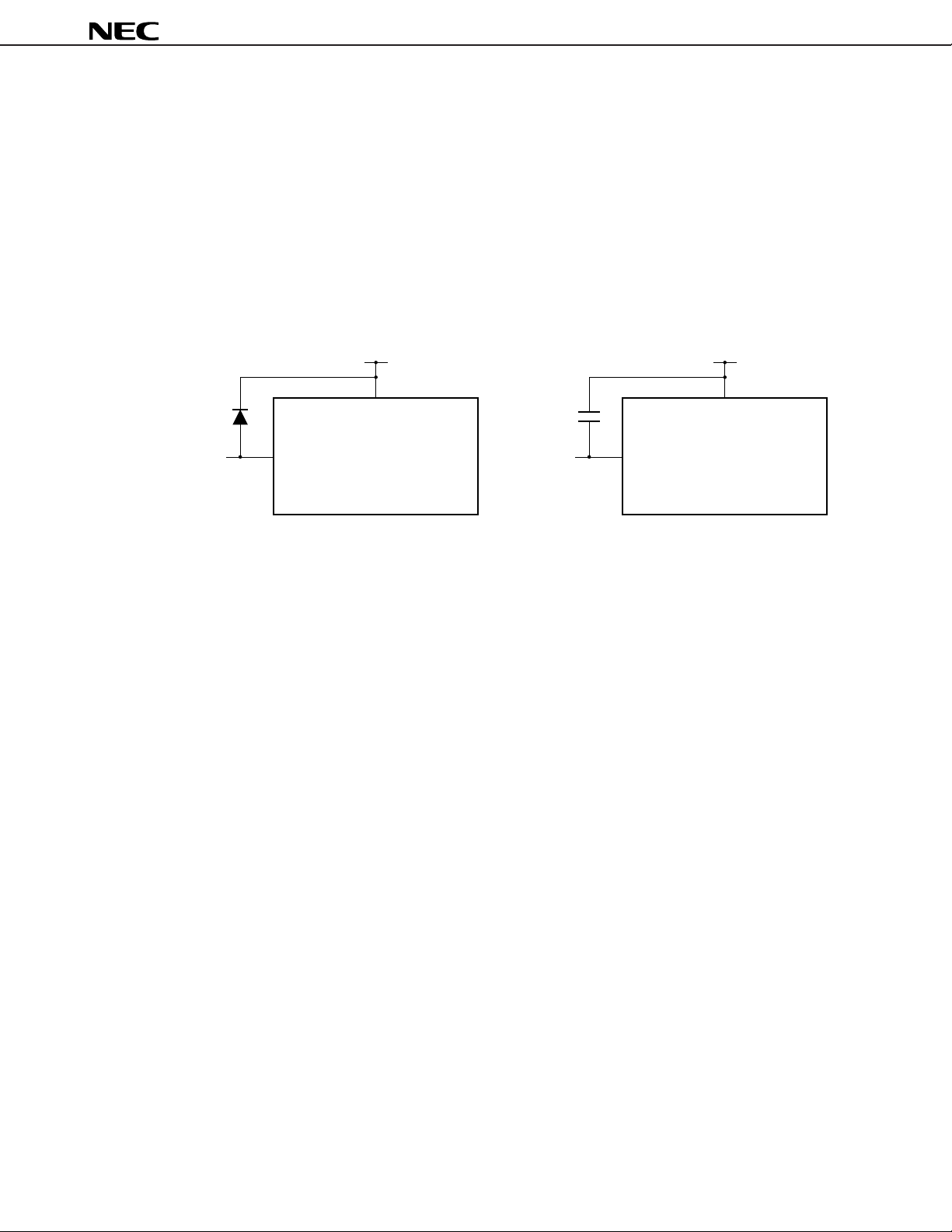

1.4 Notes on Using CE Pin

The CE pin has a function to set a test mode in which the internal operations of the µPD17073 are tested (dedicated

to IC test), in addition to the functions listed in 1.1 Pin Function List.

When a voltage higher than V

VDD is applied to the CE pin even during normal operation, the test mode is set, affecting the normal operation.

If the wiring of the CE pin is too long, the above problem occurs because wiring noise is superimposed on the CE

pin.

Therefore, wire the CE pin with as short a wiring length as possible to suppress noise. If noise cannot be avoided,

use external components as shown below to suppress noise.

DD is applied to the CE pin, the test mode is set. This means that if noise exceeding

• Connect a diode with low V

Diode with

F

low V

CE

F between CE and VDD • Connect a capacitor between CE and VDD

V

DD

V

DD

CE

V

DD

V

DD

19

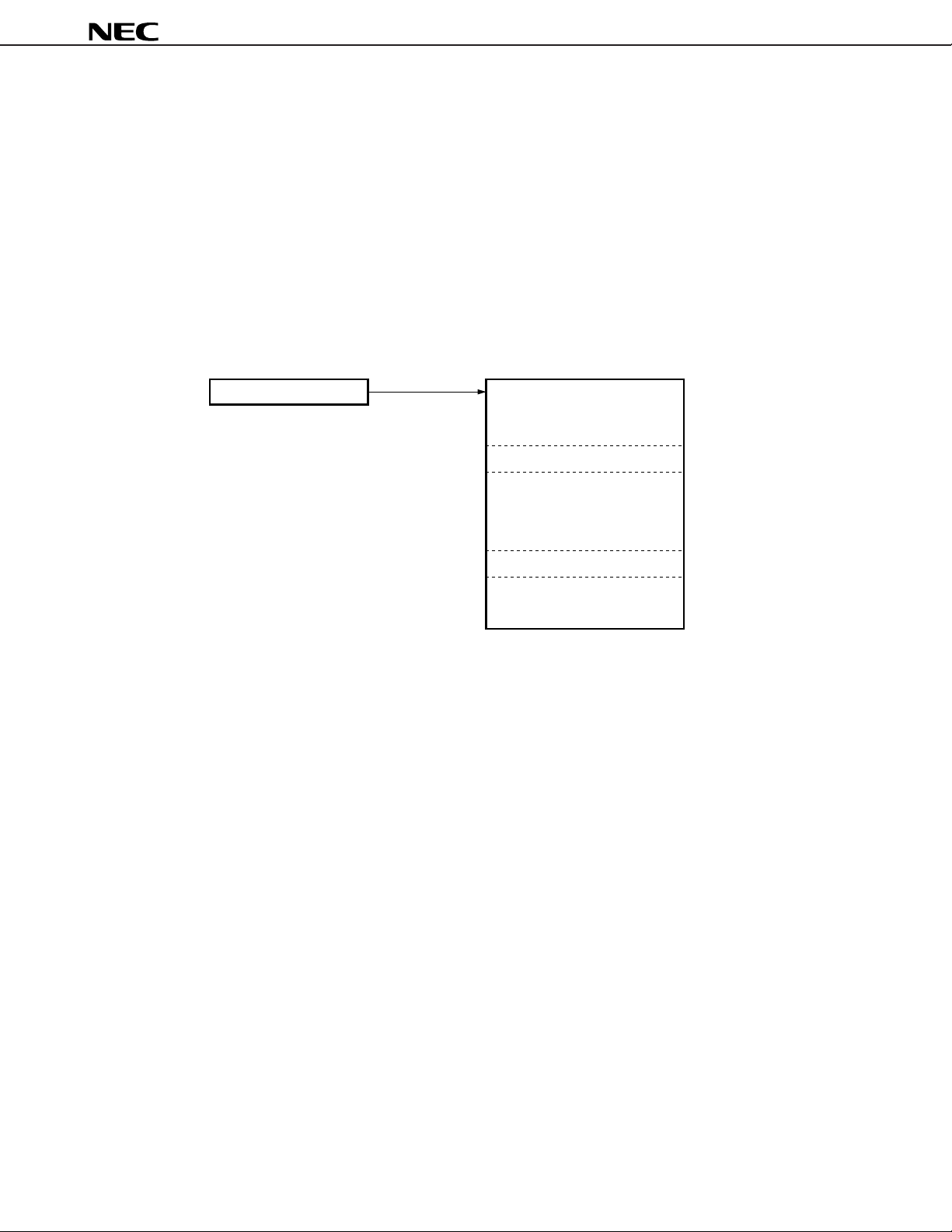

Page 20

µ

2. PROGRAM MEMORY (ROM)

2.1 General

Figure 2-1 shows the configuration of the program memory.

As shown in this figure, the program memory consists of a program memory and a program counter.

The addresses of the program memory are specified by the program counter.

The program memory has the following two major functions:

(1) Stores program

(2) Stores constant data

Figure 2-1. Outline of Program Memory

PD17072,17073

Program counter

Specifies address

Program memory

•

•

•

Instruction

•

•

•

•

•

•

Constant data

•

•

•

20

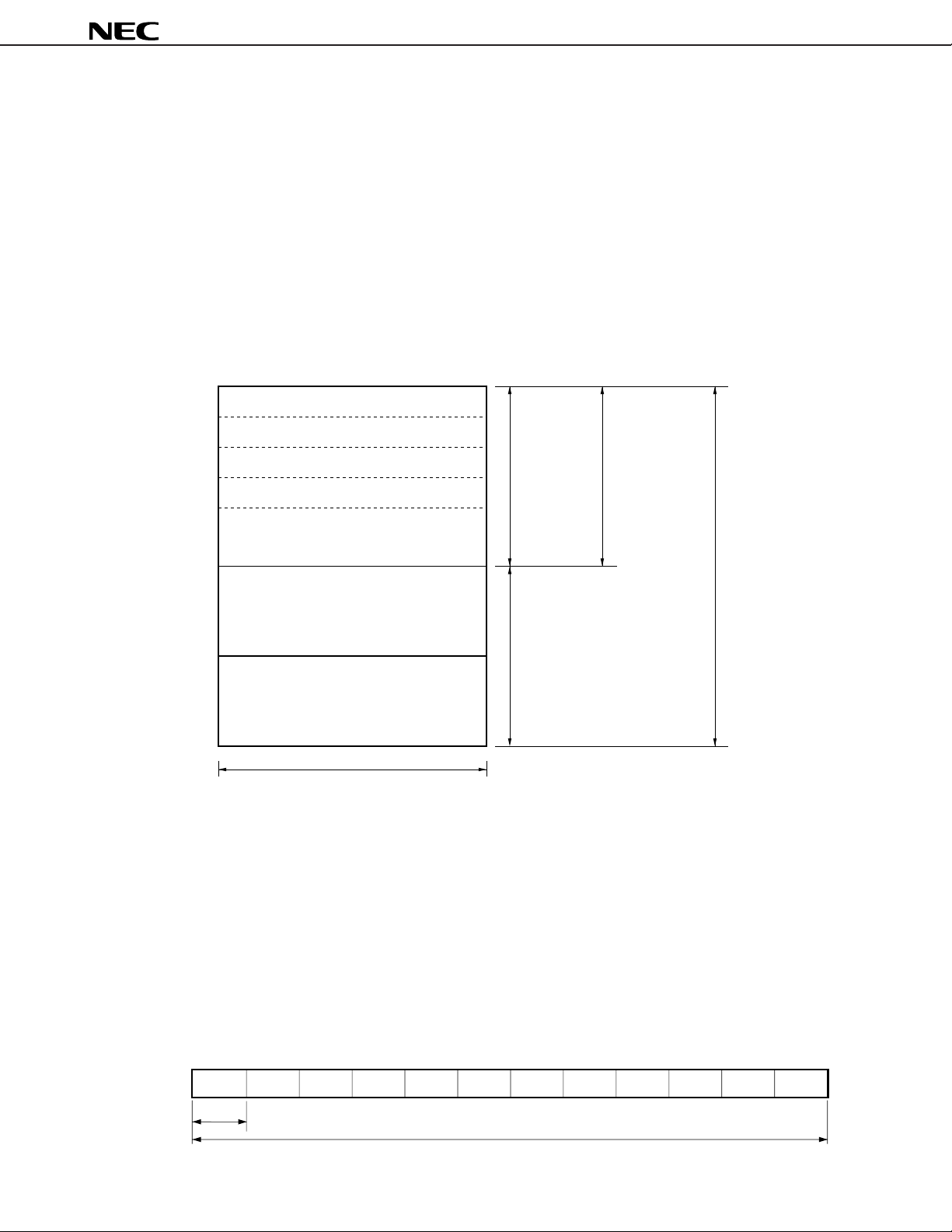

Page 21

µ

PD17072,17073

2.2 Program Memory

Figure 2-2 shows the configuration of the program memory.

As shown in this figure, the program memory is configured as follows:

µ

PD17072: 3072 × 16 bits (0000H-0BFFH)

µ

PD17073: 4096 × 16 bits (0000H-0FFFH)

Therefore, the addresses of the program memory range from 0000H to 0FFFH.

All the “instructions” are “one-word instructions” each of which is 16 bits long. Consequently, one instruction can

be stored in one address of the program memory.

As constant data, the contents of the program memory are read to the data buffer by using a table reference

instruction.

Figure 2-2. Configuration of Program Memory

0

0

0

0

H

0

0

0

1

H

0

0

0

2

H

0

0

0

3

H

Reset start address

Serial interface interrupt vector

Basic timer 1 interrupt vector

INT pin interrupt vector

Page 0

CALL addr

instruction

subroutine

entry address

BR addr

instruction

branch address

BR @AR

instruction

branch address

CALL @AR

0

7

F

F

H

0

B

F

F

H

0

F

F

F

H

Caution With the

µ

(with PD17072)

(with PD17073)

µ

16 bits

µ

PD17072, the range of addresses that can be called by each instruction is 0000H to

Page 1

instruction

subroutine entry

address

MOVT DBF @AR

instruction table

reference address

0BFFH. The area from addresses 0C00H through 0FFFH is an undefined area.

2.3 Program Counter

Figure 2-3 shows the configuration of the program counter.

The program counter specifies an address of the program memory.

As shown in this figure, the program counter is a 12-bit binary counter. The most significant bit b

page.

11 indicates a

PC

11

Page

PC

Figure 2-3. Configuration of Program Counter

10

PC

9

PC

8

PC

7

PC

PC

PC

6

5

PC

4

PC

3

PC

2

PC

1

PC

0

21

Page 22

µ

PD17072,17073

2.4 Execution Flow of Program Memory

Execution of the program is controlled by the program counter which specifies an address of the program memory.

Figure 2-4 shows the values to be set to the program counter when each instruction is executed.

Table 2-1 shows the vector addresses that are to be set to the program counter when each interrupt occurs.

Figure 2-4. Specification by Program Counter On Execution of Each Instruction

Instruction

BR addr

CALL addr

BR @AR

CALL @AR

MOVT DBF, @AR

RET

RETSK

RETI

When interrupt is accepted

Power-ON reset, CE reset

Priority Internal/external Interrupt source Vector address

Program counter

Page 0

Page 1

11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

b

0

1

0

000000000000

Contents of program counter (PC)

Instruction operand (addr)

Instruction operand (addr)

Contents of address register

Contents of address stack register (ASR)

specified by stack pointer (SP)

(Return address)

Vector address of each interrupt

Table 2-1. Interrupt Vector Address

1 External INT pin 0003H

2 External Basic timer 1 0002H

3 External Serial interface 0001H

2.5 Notes on Using Program Memory

(1)µPD17072

The program memory addresses of the µPD17072 are 0000H through 0BFFH. However, because the

addresses that can be specified by the program counter (PC) are 0000H through 0FFFH, keep the following

points in mind when specifying a program memory address:

• Be sure to write a branch instruction to address 0BFFH, when writing an instruction to this address.

• Do not write an instruction to addresses 0C00H through 0FFFH.

• Do not branch to addresses 0C00H through 0FFFH.

µ

(2) With

PD17073

The program memory addresses of the µPD17073 are 0000H through 0FFFH. Keep the following point in mind:

• Be sure to write a branch instruction to address 0FFFH, when writing an instruction to this address.

22

Page 23

µ

PD17072,17073

3. ADDRESS STACK (ASK)

3.1 General

Figure 3-1 outlines the address stack.

The address stack consists of a stack pointer and an address stack register.

The address of the address stack register is specified by the stack pointer.

The address stack saves return addresses when a subroutine call instruction has been executed and when an

interrupt has been accepted.

The address stack is also used when a table reference instruction is executed.

Figure 3-1. Outline of Address Stack

Stack pointer Address stack register

Specifies address

Return address

3.2 Address Stack Register (ASR)

Figure 3-2 shows the configuration of the address stack register.

The address stack register consists of three 12-bit registers ASR0-ASR2. Actually, however, no register is

assigned to ASR2, and the address stack register therefore consists of two 12-bit registers (ASR0 and ASR1).

The address stack saves return addresses when a subroutine call instruction has been executed, when an interrupt

has been accepted, and when a table reference instruction is executed.

Figure 3-2. Configuration of Address Stack Register

Stack pointer

(SP)

Bit

3b2b1b0

b

0 0 SP1 SP0

Address

0H

1H

2H

b

11b10b9b8b7b6b5b4b3b2b1b0

Address stack register (ASR)

Bit

ASR0

ASR1

ASR2 (Undefined)

Cannot

be used

23

Page 24

µ

PD17072,17073

3.3 Stack Pointer (SP)

Figure 3-3 shows the configuration and functions of the stack pointer.

The stack pointer is a 4-bit binary counter.

The stack pointer specifies the addresses of the address stack registers.

The value of the stack pointer can be directly read or written by using a register manipulation instruction.

Figure 3-3. Configuration and Functions of Stack Pointer

At

reset

Name

Stack pointer

SP

Power-ON

Clock stop

CE

Flag symbol

3b2b1b0

b

S

0

0

0010

S

P

P

1

0

00

01

10

10

10

Address

01H R/W

Address 0 (ASR0)

Address 1 (ASR1)

Address 2 (ASR2)

Fixed to "0"

Read/

Write

Specifies address of address stack register (ASR)

24

Page 25

µ

PD17072,17073

3.4 Operations of Address Stack

3.4.1 Subroutine call (“CALL addr” or “CALL @AR”) and return (“RET” or “RETSK”) instructions

When a subroutine call instruction is executed, the value of the stack pointer is decremented by one and the return

address is stored to the address stack register specified by the stack pointer.

When a return instruction is executed, the contents of the address stack specified by the stack pointer (return

address) is restored to the program counter, and the value of the stack pointer is incremented by one.

3.4.2 Table reference instruction (“MOVT DBF, @AR”)

When the table reference instruction is executed, the value of the stack pointer is decremented by one and the

return address is stored to the address stack register specified by the stack pointer.

Next, the contents of the program memory addressed by the address register are read to the data buffer, and the

contents of the address stack register specified by the stack pointer (return address) are restored to the program

counter. The value of the stack pointer is then incremented by one.

3.4.3 On acceptance of interrupt and execution of return instruction (“RETI” instruction)

When an interrupt is accepted, the value of the stack pointer is decremented by one, and the return address is

stored to the address stack register specified by the stack address.

When the return instruction is executed, the contents of the address stack register specified by the stack pointer

(return address) are restored to the program counter and the value of the stack pointer is incremented by one.

3.4.4 Address stack manipulation instructions (“PUSH AR” and “POP AR”)

When the “PUSH” instruction is executed, the value of the stack pointer is decremented by one, and the contents

of the address register are transferred to the address stack register specified by the stack pointer.

When the “POP” instruction is executed, the contents of the address stack register specified by the stack pointer

are transferred to the address register, and the value of the stack pointer is incremented by one.

3.5 Notes on Using Address Stack

The nesting level of the address stack is two, and the value of the address stack register ASR2 is “undefined” when

the value of the stack pointer is 2H.

Consequently, if a subroutine is called or an interrupt is used exceeding 2 levels without manipulating the stack,

program execution returns to an “undefined” address.

25

Page 26

µ

PD17072,17073

4. DATA MEMORY (RAM)

4.1 General

Figure 4-1 outlines the data memory.

As shown in this figure, the data memory consists of a general-purpose data memory, system register, data buffer,

general register, LCD segment register, port register, and peripheral control register.

The data memory stores data, transfers data with peripheral hardware, sets conditions for the peripheral hardware,

display data, transfers data with ports, and controls the CPU.

Figure 4-1. Outline of Data Memory

Peripheral hardware

Data transfer

Column address

0123456789ABCDEF

0

1

2

3

4

Row address

5

6

Port register BANK1

7

Port register

Data transfer

Port

Data buffer

General register

Data memory

BANK0

LCD segment register

Peripheral control register

System register

Data transfer

26

LCD

Condition

setting

Peripheral hardware

Page 27

µ

PD17072,17073

4.2 Configuration and Function of Data Memory

Figure 4-2 shows the configuration of the data memory.

As shown in this figure, the data memory is divided into three banks, and each bank consists of 128 nibbles with

7H row addresses and 0FH column addresses.

In terms of function, the data memory can be divided into six blocks each of which is described in the following

paragraphs 4.2.1 through 4.2.8.

The contents of the data memory can be operated, compared, judged, and transferred in 4-bit units by data memory

manipulation instructions.

Table 4-1 lists the data memory manipulation instructions.

4.2.1 System registers (SYSREG)

The system registers are allocated to addresses 74H through 7FH.

These registers are allocated independently of the bank and directly control the CPU. The same system registers

exist at addresses 74H through 7FH of each bank.

µ

With the

and PSWORD (program status word: addresses 7EH and 7FH) can be manipulated.

For details, refer to 5. SYSTEM REGISTER (SYSREG).

PD17073, only AR (address register: addresses 75H through 77H), BANK (bank register: address 79H),

4.2.2 Data buffer (DBF)

The data buffer is allocated to addresses 0CH through 0FH of BANK0.

The data buffer reads the constant data in the program memory (table reference), and transfers data with peripheral

hardware.

For details, refer to 9. DATA BUFFER (DBF).

4.2.3 General registers

µ

With the

and cannot be moved.

Operations and data transfer between the general registers and data memory can be executed with a single

instruction.

The general registers can be controlled by data memory manipulation instructions, like the other data memory

areas.

For details, refer to 6. GENERAL REGISTER (GR).

4.2.4 LCD segment registers

The LCD segment registers are allocated to addresses 41H through 4FH of BANK1 of the data memory, and are

used to set the display data of the LCD controller/driver.

For details, refer to 18. LCD CONTROLLER/DRIVER.

4.2.5 Port registers

The port registers are allocated to addresses 70H through 73H of BANK0 and addresses 70H through 73H of

BANK1, and are used to set the output data of each general-purpose port and read the data of the input ports.

For details, refer to 10. GENERAL-PURPOSE PORT.

PD17073, the general registers are fixed at row address 0 of BANK0, i.e., addresses 00H through 0FH,

4.2.6 Peripheral control registers

The peripheral control registers are allocated to addresses 50H through 6FH of BANK1 and are used to set the

conditions of the peripheral hardware (such as PLL, serial interface, A/D converter, IF counter, and timer).

For details, refer to 8. PERIPHERAL CONTROL REGISTER.

27

Page 28

µ

PD17072,17073

4.2.7 General-purpose data memory

The general-purpose data memory is allocated to the area of the data memory excluding the system register, LCD

segment register, port register, and peripheral control register.

µ

With the

be used as the general-purpose data memory.

4.2.8 Data memory areas not provided

For these data memory areas, refer to 4.4.2 Notes on data memory areas not provided, 8.2 Configuration and

Function of Peripheral Control Registers, and Table 10-1 Relation between Each Port (Pin) and Port Register.

PD17073, a total of 176 nibbles (176 × 4 bits), 112 nibbles of BANK0 and 64 nibbles of BANK1, can

28

Page 29

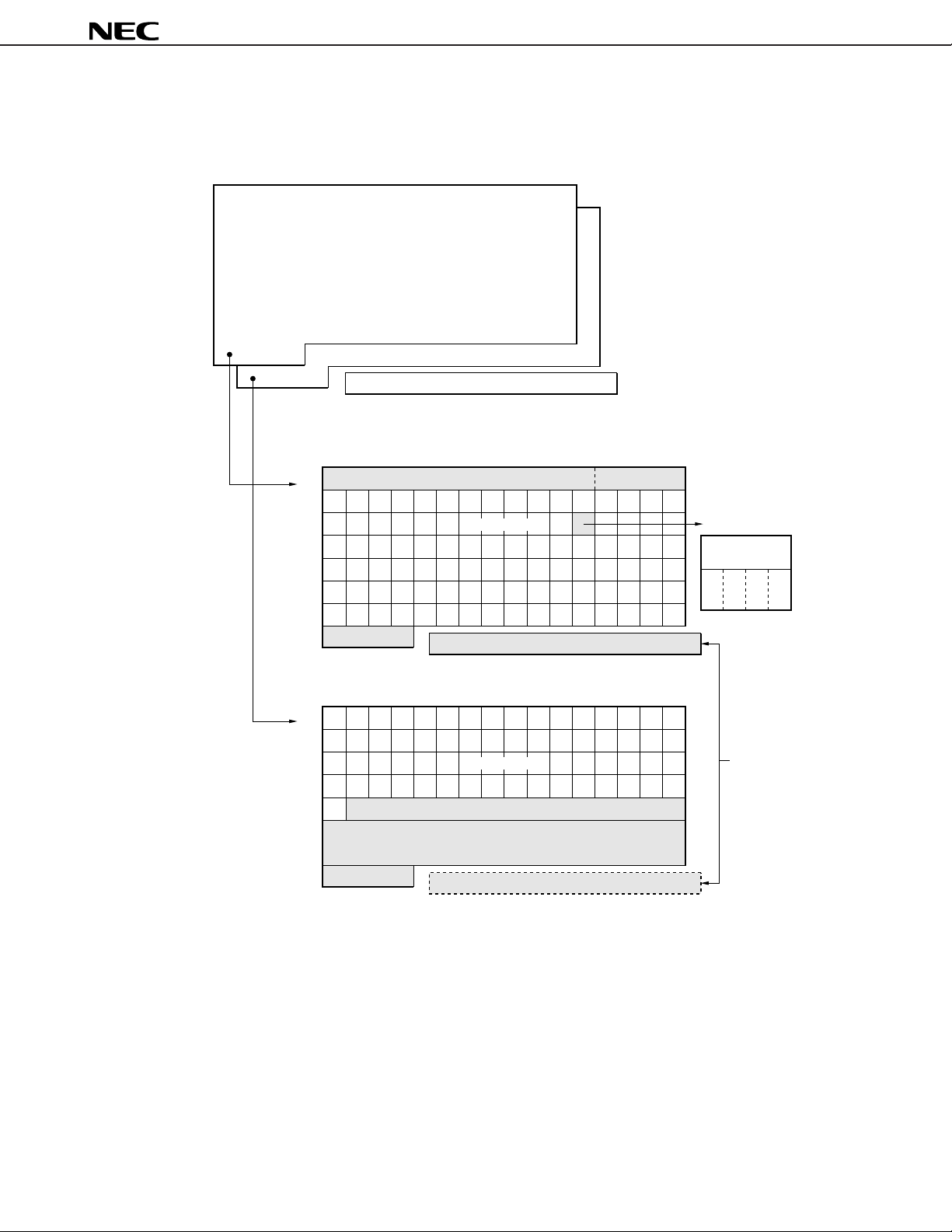

Figure 4-2. Configuration of Data Memory

Column address

0123456789ABCDEF

0

1

2

3

4

Row address

5

6

7

0

1

2

3

4

5

Row addressRow address

6

7

Data memory

BANK0

BANK1

System register

Column address

0123456789ABCDEF

General register

BANK0

Port register

System register (SYSREG)

Data buffer

µ

PD17072,17073

Example

Address 2BH

of BANK0

b

3b2b1b0

0123456789ABCDEF

0

1

2

3

4

5

6

Port register

7

BANK1

LCD segment register

Peripheral control register

System register (SYSREG)

Same system

register exists.

Caution Address 40H of BANK1, bit 3 of address 50H, and address 73H are test mode areas. Do not write

“1” to these areas.

29

Page 30

Table 4-1. Data Memory Manipulation Instructions

Function Instruction

µ

PD17072,17073

Add

Operation Subtract

Logical OR

Compare

Transfer LD

Judge

ADD

ADDC

SUB

SUBC

AND

XOR

SKE

SKGE

SKLT

SKNE

MOV

ST

SKT

SKF

4.3 Addressing Data Memory

Figure 4-3 shows how to address the data memory.

An address of the data memory is specified by using a bank, row address, and column address.

The row address and column address are directly specified by a data memory manipulation instruction, but the

bank is specified by the contents of the bank register.

For details of the bank register, refer to 5. SYSTEM REGISTER (SYSREG).

Figure 4-3. Addressing Data Memory

Data memory address M

Bank Row address Column address

b

b3b2b1b

Bank register Instruction operand

0

b2b

0

1

b3b2b1b

0

30

Page 31

µ

PD17072,17073

4.4 Notes on Using Data Memory

4.4.1 On power-ON reset

On power-ON reset, the contents of the general-purpose data memory are “undefined”.

Initialize the memory if necessary.

4.4.2 Notes on data memory not provided

If a data memory manipulation instruction is executed to manipulate an address where no data memory is assigned,

the following operations are performed:

(1) Device operation

When a read instruction is executed, “0” is read.

Nothing is changed even when a write instruction is executed.

Address 40H of BANK1, bit 3 of address 50H, and address 73H are test mode areas. Do not write “1” to these

areas.

(2) Assembler operation

The program is assembled normally. No “error” occurs.

(3) In-circuit emulator operation

“0” is read when a read instruction is executed.

Nothing is changed when a write instruction is executed.

No “error” occurs.

31

Page 32

µ

PD17072,17073

5. SYSTEM REGISTER (SYSREG)

5.1 General

Figure 5-1 shows the location of the system register on the data memory and outline.

As shown, the system register is assigned to addresses 74H-7FH of the data memory, regardless of bank. In other

words, the same system register is assigned to addresses 74H-7FH of any bank.

Since the system register is located on the data memory, it can be manipulated by all the data memory manipulation

instructions.

µ

With the

status word (PSWORD: 7EH, 7FH) of addresses 74H through 7FH can be manipulated.

PD17073, only the address register (AR: 74H through 77H), bank register (BANK: 79H), and program

Figure 5-1. Location of System Register on Data Memory and Outline

Column address

00123456789ABCDEF

1

2

3

4

5

Row address

6

7

Data memory

BANK0

BANK1

System register

Address 74H 75H 76H 77H 78H 79H

Name

Outline

Address 7AH 7BH 7CH 7DH 7EH 7FH

Name

Address register

(AR)

Controls program memory address

Fixed to 0

Fixed to 0 Bank register

(BANK)

Specifies data

memory bank

Program status word

(PSWORD)

32

Outline

Controls operation

Page 33

µ

PD17072,17073

5.2 Address Register (AR)

5.2.1 Configuration of address register

Figure 5-2 shows the configuration of the address register.

As shown in this figure, the address register consists of 16 bits of the system register: 74H through 77H (AR3

through AR0). However, the higher 4 bits are always fixed to 0, and therefore, the address register actually functions

as a 12-bit register.

Figure 5-2. Address Register Configuration

Address 74H 75H 76H 77H

Name

Symbol

Bit

AR3

3

2b1b0b3b2b1b0b3b2b1b0b3b2b1b0

b

b

Address register (AR)

AR2 AR1 AR0

M

Power-ON

Clock stop

At reset

CE

Data

000

0

0

0

0

Remark Power-ON : On power-ON reset

Clock stop : On execution of clock stop instruction

CE : On CE reset

L

S

B

0

0

0

0

0

0

S

B

0

0

0

33

Page 34

µ

PD17072,17073

5.2.2 Functions of address register

The address register specifies a program memory address when the table reference instruction (“MOVT DBF,

@AR”), stack manipulation instruction (“PUSH AR” or “POP AR”), indirect branch instruction (“BR @AR”), and indirect

subroutine call instruction (“CALL @AR”) has been executed.

A dedicated instruction (“INC AR”) that can increment the value of the address register by one is available.

The following paragraphs (1) through (5) describe the operations of the address register when each of these

instructions has been executed.

(1) Table reference instruction (“MOVT DBF, @AR”)

When the “MOVT DBF, @AR” instruction is executed, the constant data (16 bits) of the program memory

address specified by the contents of the address register are read to the data buffer.

The addresses of the constant data which can be specified by the address register are 0000H-0FFFH.

(2) Stack manipulation instruction (“PUSH AR”, “POP AR”)

By executing the “PUSH AR” instruction, the stack pointer is decremented by one and the contents of the

address register (AR) are stored to the address stack register specified by the stack pointer.

When the “POP AR” instruction is executed, the contents of the address stack register specified by the stack

pointer are transferred to the address register, and the stack pointer is incremented by one.

(3) Indirect branch instruction (“BR @AR”)

When the “BR @AR” instruction is executed, the program execution branches to a program memory address

specified by the contents of the address register.

The branch addresses that can be specified by the address register are 0000H-0FFFH.

(4) Indirect subroutine call instruction (“CALL @AR”)

When the “CALL @AR” instruction is executed, the subroutine at the program memory address specified by

the contents of the address register can be called.

The first addresses of the subroutine that can be specified by the address register are 0000H-0FFFH.

(5) Address register increment instruction (“INC AR”)

This instruction increments the contents of the address register by one each time it is executed.

Since the address register is configured of 12 bits, its contents become “0000H” when the “INC AR” instruction

is executed with the contents of the address register being “0FFFH”.

5.2.3 Address register and data buffer

The address register can transfer data through the data buffer as a part of the peripheral hardware.

For details, refer to 9. DATA BUFFER (DBF).

34

Page 35

µ

PD17072,17073

5.3 Bank Register (BANK)

5.3.1 Configuration of bank register

Figure 5-3 shows the configuration of the bank register.

As shown in this figure, the bank register consists of 4 bits of address 79H (BANK) of the system register. Note,

however, that the higher 3 bits are always fixed to “0”; therefore, this register actually serves as a 1-bit register.

Figure 5-3. Bank Register Configuration

Address 79H

Bank register

3

b

(BANK)

BANK

b

2

00

0

0

0

b1b

0

0

Power-ON

Clock stop

At reset

CE

Name

Symbol

Bit

Data

5.3.2 Function of bank register

The bank register selects a bank of the data memory.

Table 5-1 shows the value of the bank register and how a bank of the data memory is specified.

Since the bank register exists on the system register, its contents can be rewritten regardless of the currently

specified bank.

In other words, the current bank status has nothing to do with manipulation of the bank register.

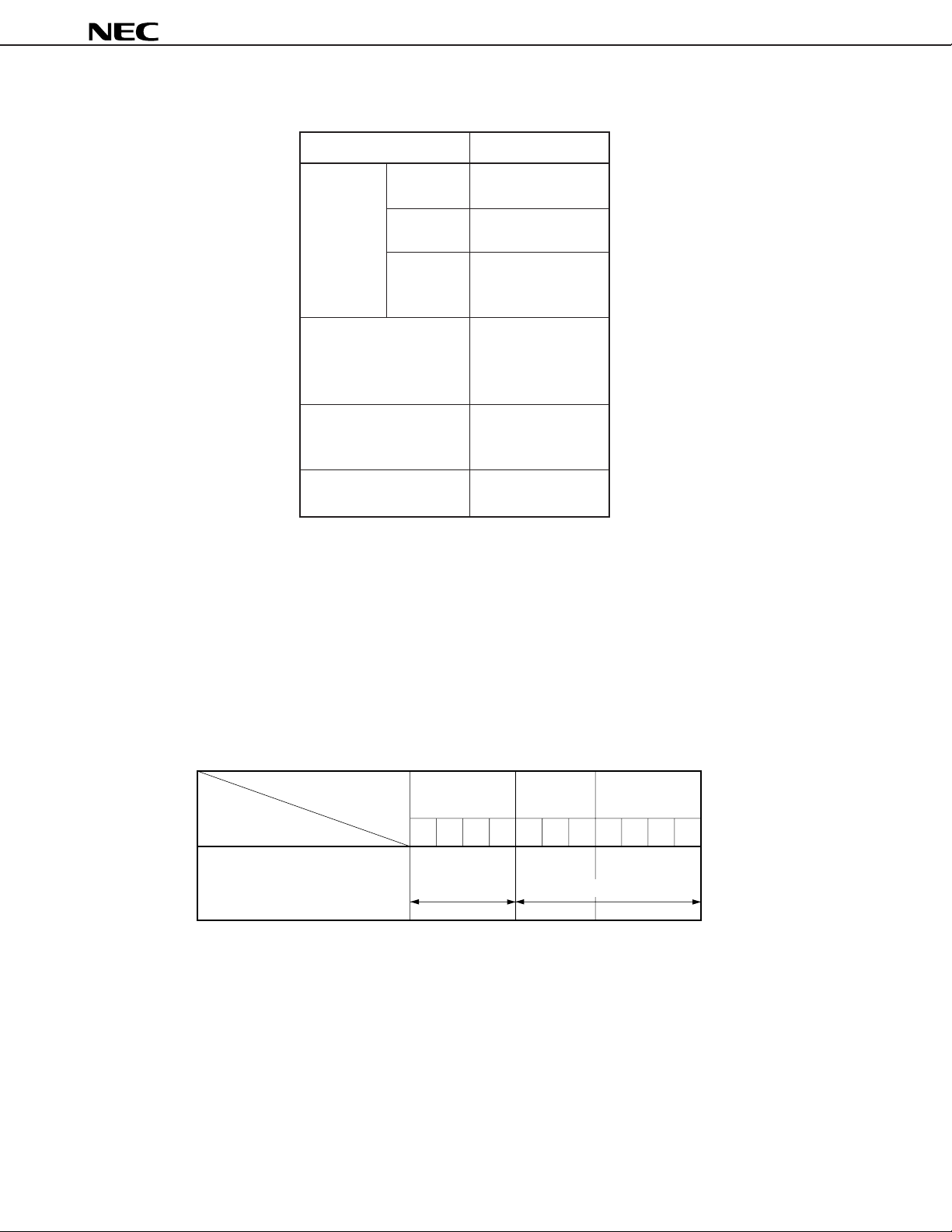

Table 5-1. Specifying Bank of Data Memory

Bank register

(BANK)

b3 b2 b1 b0

––––––

0000

0001

––––––

––––––

Bank of data

memory

BANK0

BANK1

35

Page 36

µ

PD17072,17073

5.4 Program Status Word (PSWORD)

5.4.1 Configuration of program status word

Figure 5-4 shows the configuration of the program status word.

As shown in this figure, the program status word consists of a total of 5 bits: the least significant bit of address

7EH (RPL) and 4 bits of 7FH (PSW) of the system register. However, bit 0 of 7FH is always fixed to 0.

Each of the 5 bits in the program status word has its own function as a BCD flag (BCD), compare flag (CMP), carry

flag (CY), zero flag (Z), respectively.

Figure 5-4. Program Status Word Configuration

Power-ON

Clock stop

At reset

CE

Address

Name

Symbol

Bit

Data

7EH 7FH

Program status

0

0

0

word (PSWORD)

C

B

C

D

C

M

Y

P

0

0

0

Z

(RP)

RPL PSW

0 b2 b2 b0 b0 b2 b2 b0

b

0

36

Page 37

µ

PD17072,17073

5.4.2 Functions of program status word

The program status word sets conditions, under which the ALU (Arithmetic Logic Unit) performs arithmetic or

transfer operations, and indicates the results of the operations.

Table 5-2 outlines the function of each flag of the program status word.

For details, refer to 7. ALU (Arithmetic Logic Unit) BLOCK.

Table 5-2. Functional Outline of Each Flag of Program Status Word

(RP)

RPL PSW

3b2b1b0b3b2b1b0

b

Program status

word (PSWORD)

B

C

CYZ0

C

M

D

P

Flag name Function

Zero flag (Z)

Carry flag (CY)

Compare flag (CMP)

Indicates that the result of arithmetic operation is 0. Condition under which this flag is set differs depending on

contents of compare flag.

Indicates occurrence of carry or borrow as a result of

executing addition or subtraction instruction.

Reset (0) when carry or borrow does not occur. Set (1) when

carry or borrow occurs. Also used as shift bit of "RORC r"

instruction.

Stores or does not store result of arithmetic operation in

data memory or general register.

0: Stores result

1: Does not store result

BCD flag (BCD)

Executes arithmetic operation in decimal.

0: Executes binary operation

1: Executes decimal operation

5.4.3 Notes on using program status word

When an arithmetic operation (addition or subtraction) instruction is executed to the program status word, the result

of the arithmetic operation is stored in the program status word.

Even if an operation that generates a carry has been executed, for example, if the result of the operation is 0000B,

0000B is stored in PSW.

5.5 Notes on Using System Register

The data in the system register which are fixed to “0” are not influenced even when a write instruction is executed.

When these data are read, “0” is always read.

37

Page 38

µ

PD17072,17073

6. GENERAL REGISTERS (GR)

6.1 Outline of General Registers

With the µPD17073, the general registers are fixed at row address 0 of BANK0 on the data memory, and consist

of 16 nibbles (16 × 4 bits) of 00H through 0FH.

The 16 nibbles of the row address 0 specified as the general registers can perform operations and data transfer

with the data memory with a single instruction.

In other words, operations and data transfer between data memory areas can be executed with a single instruction.

The general registers can be controlled by data memory manipulation instructions, like the other data memory

areas.

Figure 6-1. Outline of General Registers

Column address

0123456789ABCDEF

0

1

2

3

4

Row address

5

6

7

General registers

Transfer, operation

Data memory

BANK0

BANK1

System registers

38

Page 39

µ

PD17072,17073

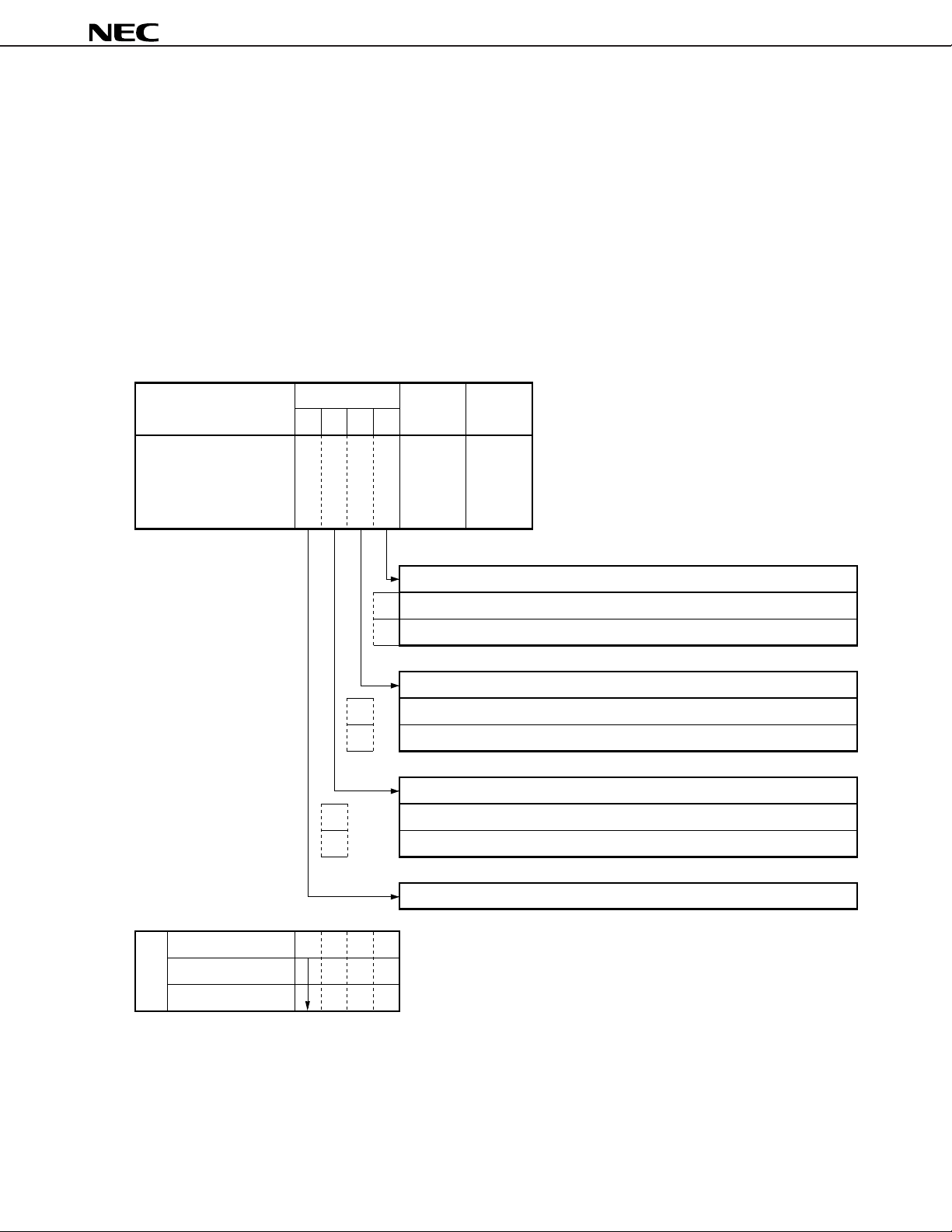

6.2 Address Creation of General Register with Each Instruction

The following paragraphs 6.2.1 and 6.2.2 describe how the address of the general register is created when each

instruction is executed.

For details of the operation of each instruction, refer to 7. ALU (Arithmetic Logic Unit) BLOCK.

6.2.1 Addition (“ADD r, m”, “ADDC r, m”),

subtraction (“SUB r, m”, “SUBC r, m”),

logical operation (“AND r, m”, “OR r, m”, “XOR r, m”),

direct transfer (“LD r, m”, “ST m, r”),

rotate processing (“RORC r”) instructions

Table 6-1 shows the address of general register “R” specified by an instruction operand “r”. The operand “r”

specifies only the column address.

Table 6-1. Address Creation of General Register

Bank Row address Column address

3 b2 b1 b0 b2 b1 b0 b3 b2 b1 b0

b

General register address R

Fixed to 0

Fixed to 1

r

6.2.2 Indirect transfer (“MOV @r, m”, “MOV m, @r”) instructions

Table 6-2 shows the address of the general register “R” specified by instruction operand “r”, and the indirect transfer

address specified by “@R”.

Table 6-2. Address Creation of General Register

Bank Row address Column address

b

3b2b1b0b2b1b0b3b2b1b0

General register address R

Indirect transfer address @R

Fixed to 0

Fixed to 0

Fixed to 0

Fixed to 0

r

Contents of R

6.3 Notes on Using General Register

There is no instruction available that performs an operation between the general register and immediate data.

To perform an operation between the data memory specified as the general register and immediate data, the data

memory must be treated as data memory instead of as the general register.

39

Page 40

µ

PD17072,17073

7. ALU (ARITHMETIC LOGIC UNIT) BLOCK

7.1 General

Figure 7-1 shows the configuration of the ALU block.

As shown in the figure, the ALU block consists of an ALU, temporary registers A and B, program status word,

decimal adjuster circuit, and data memory address control circuit.

The ALU performs arithmetic operation, judgment, comparison, rotation, and transfer of 4-bit data on the data

memory.

Figure 7-1. Outline of ALU Block

Data bus

Address

control

Data memory

Temporary

register A

Temporary

register B

Program

status word

Carry/borrow/zero

detection/decimal/storage

ALU

• Arithmetic operation

• Logical operation

• Bit judgment

• Comparison

• Rotation

• Transfer

Decimal

adjuster circuit

40

Page 41

µ

PD17072,17073

7.2 Configuration and Function of Each Block

7.2.1 Functions of ALU

The ALU performs arithmetic operation, logical operation, bit judgment, comparison, rotation, and transfer of 4-

bit data as the instruction specified by the program.

7.2.2 Temporary registers A and B

Temporary registers A and B temporarily stores 4-bit data.

These registers are automatically used when an instruction is executed and cannot be controlled by program.

7.2.3 Program status word

The program status word controls the operations of the ALU and stores the status of the ALU. For details, refer

to 5.4 Program Status Word (PSWORD).

7.2.4 Decimal adjuster circuit

When the BCD flag of the program status word is set to 1 during an arithmetic operation, the result of the operation

is converted into decimal numbers by the decimal adjuster circuit.

7.2.5 Address control circuit

The address control circuit specifies an address of the data memory.

7.3 ALU Processing Instructions

Table 7-1 shows the operations of the ALU when each instruction is executed.

Table 7-2 shows the decimal adjusted data when a decimal operation is performed.

41

Page 42

ALU function

Addition

Instruction

ADD

ADDC

r, m

m, #n4

r, m

m, #n4

Table 7-1. ALU Processing Instruction List

Difference of operation due to program status word (PSWORD)

Value of

BCD flag

0

0

Value of

CMP flag

– –––––––––– –––––––––– –––––––––– –––––––––– –––––––––– –––––––––– –––––––––– –––––––––– –––––––––– –––––––––

0

1

Operation

Stores result of

binary addition

Does not store

result of binary

operation

Set if carry or

borrow occurs;

otherwise, reset

Operation of CY

flag

µ

PD17072,17073

Operation of Z flag

Set if result of operation

is 0000B; otherwise, reset

Retains status if result of

operation is 0000B;

otherwise, reset

Subtraction

Logical

operation

Judgment

Comparison

SUB

SUBC

OR

AND

XOR

SKT

SKF

SKE

SKNE

SKGE

SKLT

r, m

m, #n4

r, m

m, #n4

r, m

m, #n4

r, m

m, #n4

r, m

m, #n4

m, #n

m, #n

m, #n4

m, #n4

m, #n4

m, #n4

1

1

Any

(retained)

Any

(retained)

Any

(retained)

0

1

Any

(retained)

Any

(reset)

Any

(retained)

Stores result of

decimal operation

Does not store

result of decimal

operation

No change

No change

No change

Retains previous

status

Retains previous

status

Retains previous

status

Set if result of operation is

0000B; otherwise, reset

Retains status if result of

operation is 0000B;

otherwise, reset

Retains previous status

Retains previous status

Retains previous status

Transfer

Rotation

42

LD

ST

MOV

RORC

r, m

m, r

m, #n4

@r, m

m, @r

r

Any

(retained)

Any

(retained)

Any

(retained)

Any

(retained)

No change

No change

Retains previous

status

Value of b0 of

general register

Retains previous status

Retains previous status

Page 43

Table 7-2. Decimal Adjusted Data

µ

PD17072,17073

Result of

operation

10 0 1010B 1 0000B

11 0 1011B 1 0001B

12 0 1100B 1 0010B

13 0 1101B 1 0011B

14 0 1110B 1 0100B

15 0 1111B 1 0101B

16 1 0000B 1 0110B

17 1 0001B 1 0111B

18 1 0010B 1 1000B

19 1 0011B 1 1001B

20 1 0100B 1 1110B

21 1 0101B 1 1111B

22 1 0110B 1 1100B

23 1 0111B 1 1101B

24 1 1000B 1 1110B

25 1 1001B 1 1111B

26 1 1010B 1 1100B

27 1 1011B 1 1101B

28 1 1100B 1 1010B

29 1 1101B 1 1011B

30 1 1110B 1 1100B

31 1 1111B 1 1101B

Hexadecimal addition Decimal addition

CY

0 0 0000B 0 0000B

1 0 0001B 0 0001B

2 0 0010B 0 0010B

3 0 0011B 0 0011B

4 0 0100B 0 0100B

5 0 0101B 0 0101B

6 0 0110B 0 0110B

7 0 0111B 0 0111B

8 0 1000B 0 1000B

9 0 1001B 0 1001B

Result of

operation

CY

Result of

operation

Result of

operation

10 0 1010B 1 1100B

11 0 1011B 1 1101B

12 0 1100B 1 1110B

13 0 1101B 1 1111B

14 0 1110B 1 1100B

15 0 1111B 1 1101B

–16 1 0000B 1 1110B

–15 1 0001B 1 1111B

–14 1 0010B 1 1100B

–13 1 0011B 1 1101B

–12 1 0100B 1 1110B

–11 1 0101B 1 1111B

–10 1 0110B 1 0000B

– 9 1 0111B 1 0001B

– 8 1 1000B 1 0010B

– 7 1 1001B 1 0011B

– 6 1 1010B 1 0100B

– 5 1 1011B 1 0101B

– 4 1 1100B 1 0110B

– 3 1 1101B 1 0111B

– 2 1 1110B 1 1000B

– 1 1 1111B 1 1001B

Hexadecimal subtraction

CY

0 0 0000B 0 0000B

1 0 0001B 0 0001B

2 0 0010B 0 0010B

3 0 0011B 0 0011B

4 0 0100B 0 0100B

5 0 0101B 0 0101B

6 0 0110B 0 0110B

7 0 0111B 0 0111B

8 0 1000B 0 1000B

9 0 1001B 0 1001B

Result of

operation

Decimal subtraction

CY

Result of

operation

Remark The shaded part indicates that decimal adjustment is not made correctly.

43

Page 44

µ

PD17072,17073

7.4 Notes on Using ALU

7.4.1 Notes on executing operation to program status word

When an arithmetic operation is performed to the program status word, the result of the operation is stored in the

program status word.

The CY and Z flags of the program status word are usually set or reset according to the result of an arithmetic

operation executed. However, if the program status word itself is used for an operation, the result of the operation

is stored in the program status word, making it impossible to judge whether a carry or borrow occurs, or the result

of the operation is zero.

However, if the CMP flag is set, the result of the operation is not stored in the program status word; consequently,