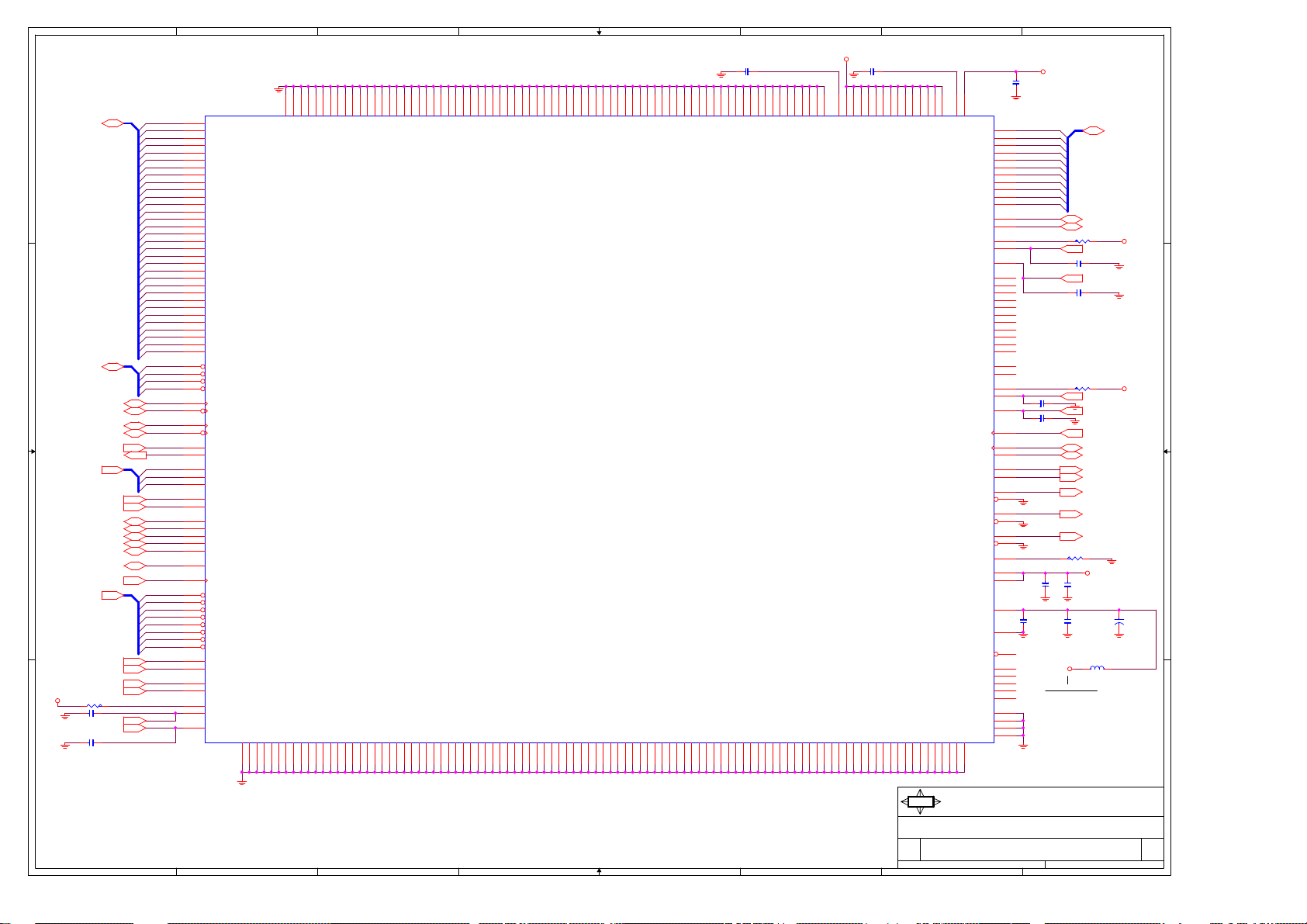

MSI MS-6726 Schematics

1

Cover Sheet

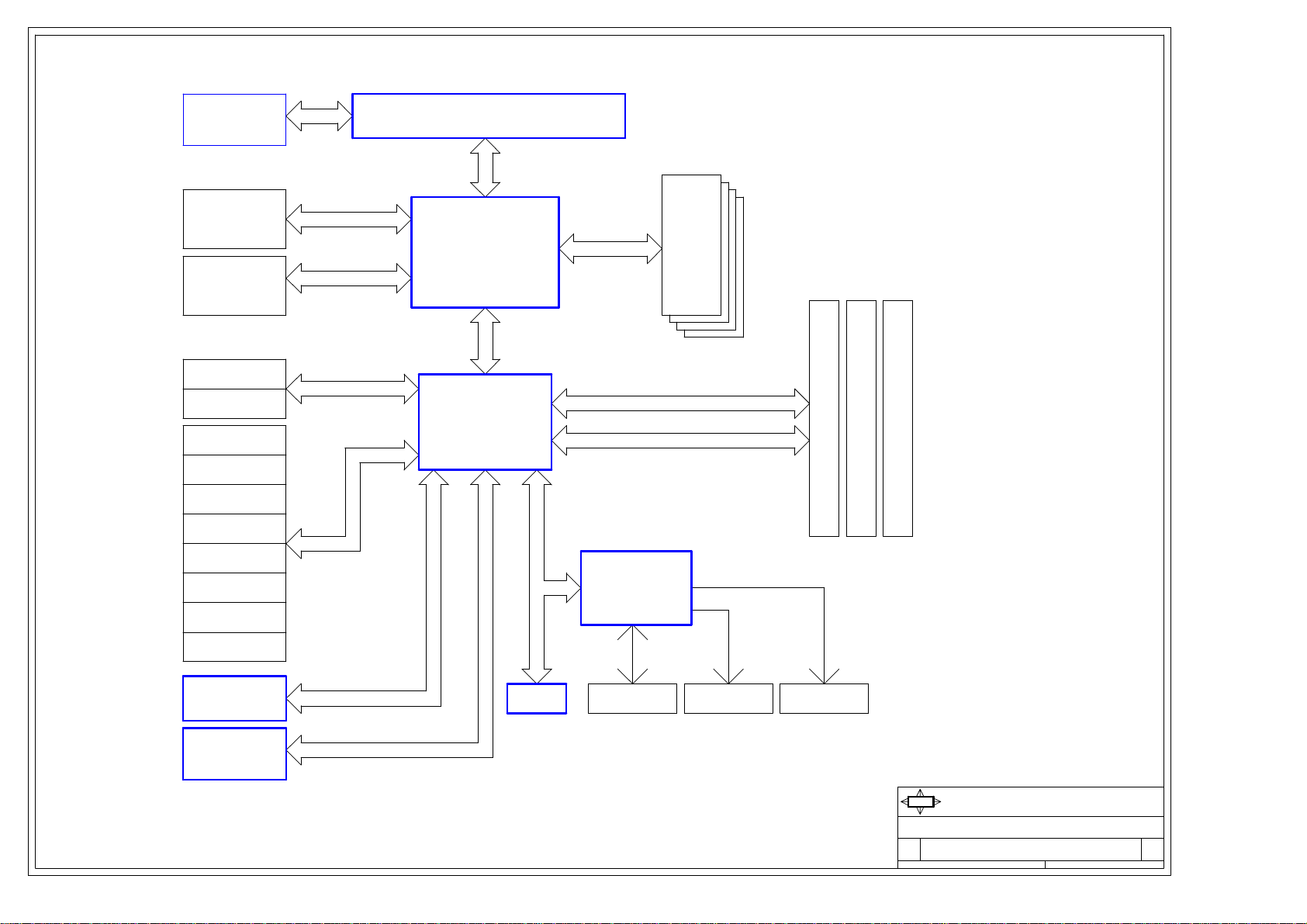

Block Diagram

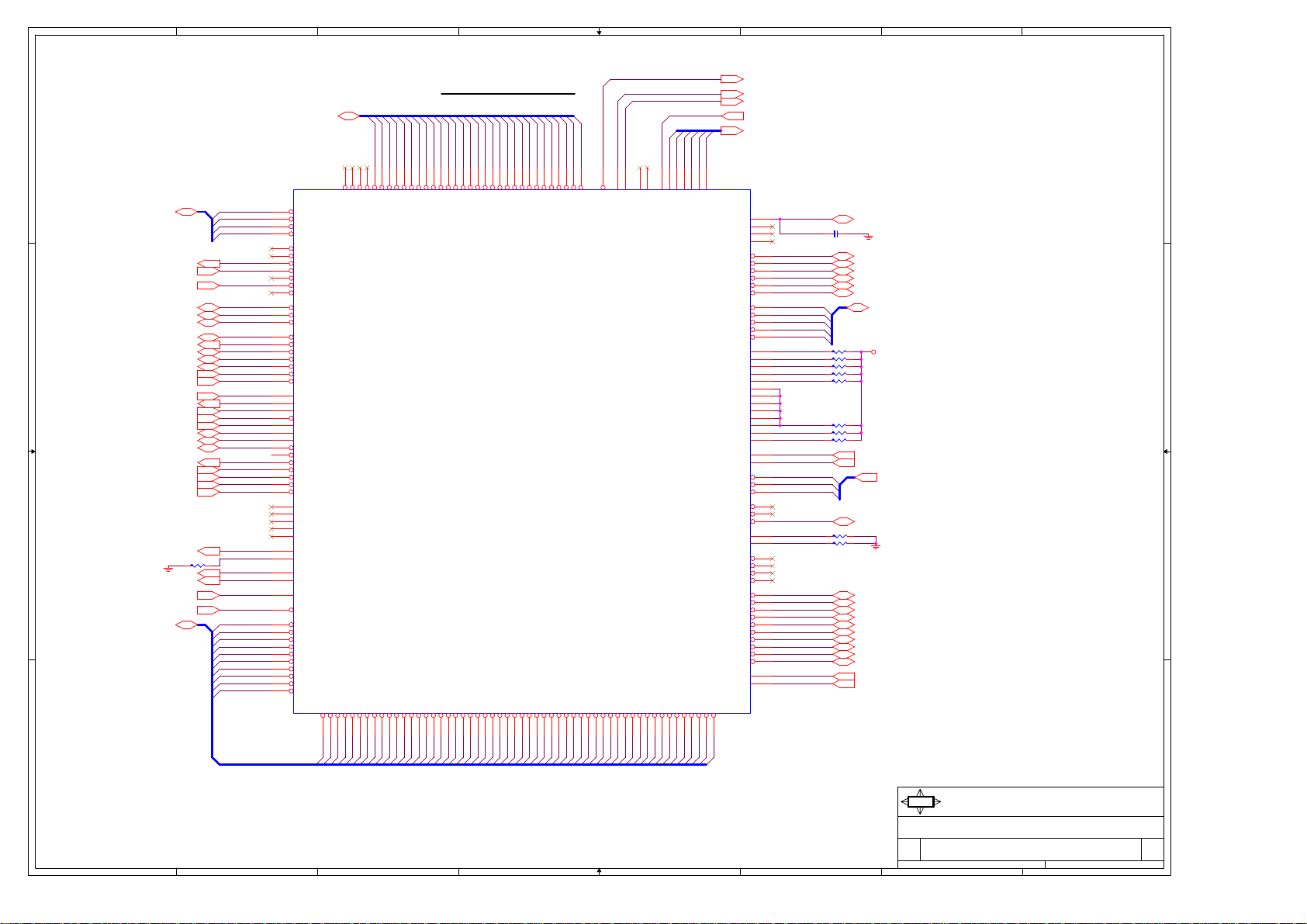

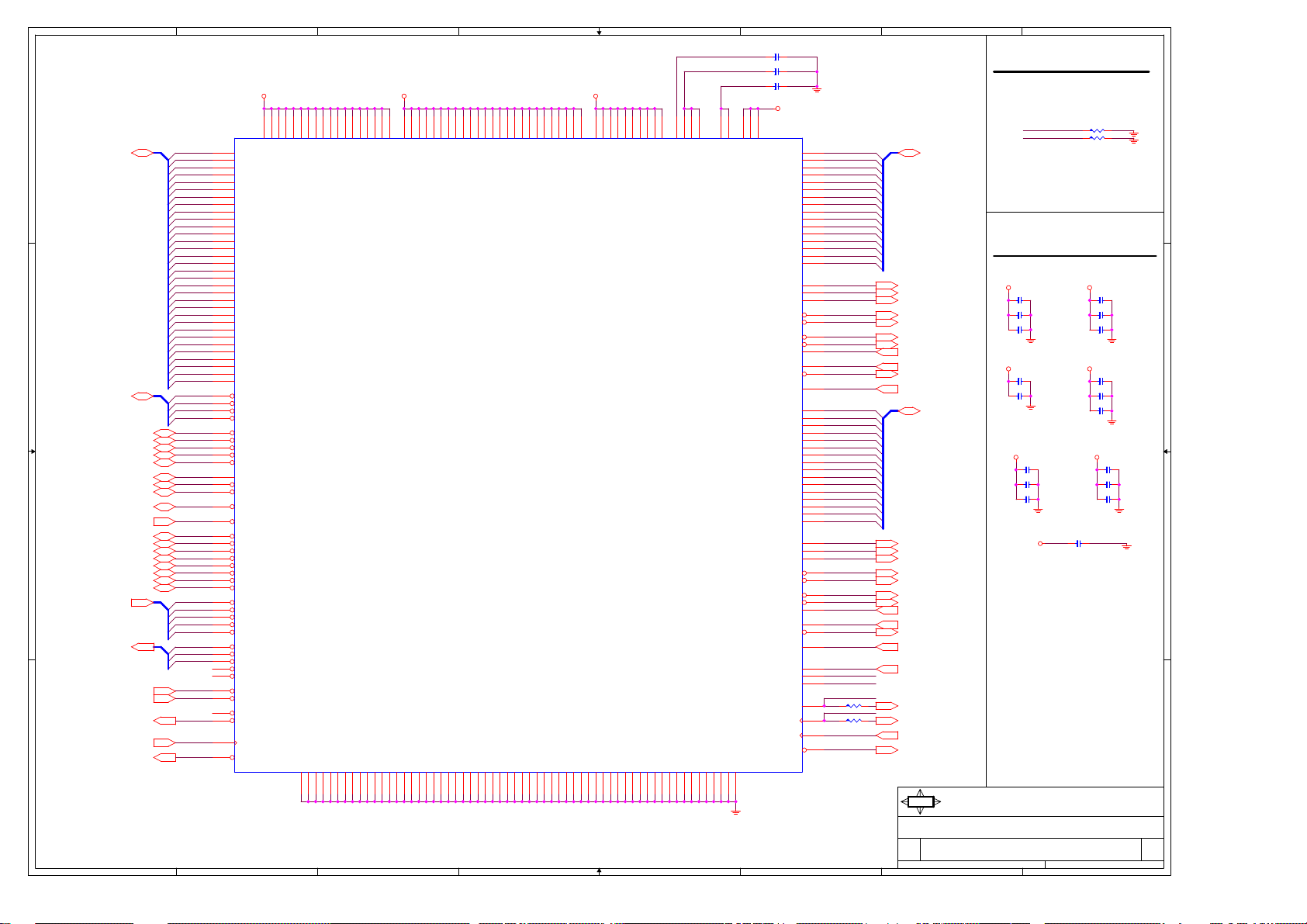

Intel mPGA478B CPU - Signals

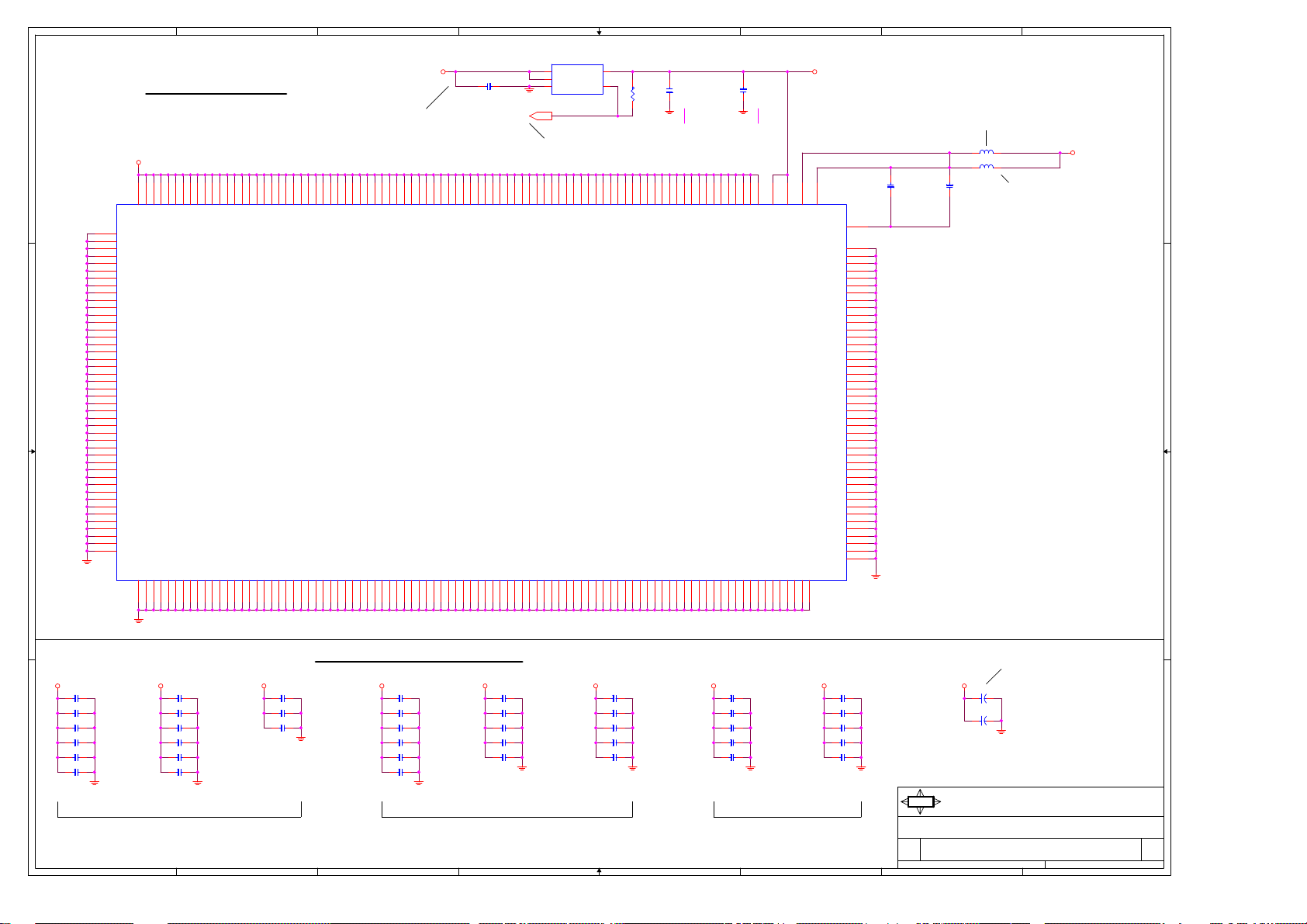

Intel mPGA478B CPU - Power

1

2

3

4

MS-6726D2

Intel (R) Springdale (GMCH) + ICH5 Chipset

Version 0A

11/26/2002 Finished

Intel Northwood & Prescott mPGA478B Processor

Intel Springdale - Host Signals

Intel Springdale - Memory Signals

Intel Springdale - AGP & LDT Signals 7

Intel ICH5 - PCI & IDE & AC97 Signals

Intel ICH5 - Other Signals

Clock - Cypress CY28405 & FWH

LPC I/O - LPC47M292

AC97 Audio - AD1980

Broadcom BCM 4401/5705

A A

DDR System Memory 1 & 2

DDR System Memory 3 & 4

AGP 4X/8X Slot

5

6

8

9

10

11

12

13

14

15

16

CPU:

Intel Northwood/Prescott - 3.0G & Above

System Chipset:

Intel Springdale - GMCH (North Bridge)

Intel ICH5 (South Bridge)

On Board Chipset:

BIOS -- FWH EEPROM

AC'97 Codec -- AD1980

LPC Super I/O -- LPC47M292

LAN -- BCM 4401/5705

CLOCK -- Cypress CY28405

Main Memory:

PCI Slots 1 & 2 & 3

ATA33/66/100 IDE & Video Connectors

USB & LAN Connectors

ATX & Front Panel

AGP & MEMORY & USB Regulator Controller

VCC_DAC & VTT Regulator & VR Thermal

VRM 10 - Intersil HIP 6556B + HIP 6602B

PULL UP/ DOWN RESISTORS

GPIO

MANUAL

Revision History 1 - 3

17

18

19

20

21

22

23

24

25

26

27 - 29

DDR2700 * 4 (Max 4GB)

Expansion Slots:

PCI2.3 SLOT * 3

AGP4X/8X SLOT * 1

Intersil PWM:

Controller: HIP6556B

Driver: HIP6602B * 2 + HIP6601B * 1

Regulators

System : FAN5236

1

MSI

Title

Size Document Number Rev

Date: Sheet of

MICRO-STAR INt'L CO., LTD.

H/W Project Leader : Andy Chen

H/W Project Engineer : Prudence Wang

COVER SHEET

MS-6726D2

1 29Tuesday, November 26, 2002

0A

1

VRM 10

Intersil 6556

Intel mPAG478B Processor

Block Diagram

4-Phase PWM

FSB

64/128 bits DDR

133/166MHz@2.1/2.7GB/s

4 DDR

DIMM

Modules

AGP 1.5V

Connector

Analog

133/166MHz@4.2/4.5GB/s

4X/8X w/Fast Write

66MHz@2.1GB/s

Springdale - G

Video

Out

HCT

ICH5

Link

PCI CNTRL

PCI ADDR/DATA

33MHz@133MB/s

PCI Slot 1

PCI Slot 2

PCI Slot 3

66MHz@266MB/s

UltraDMA

IDE Primary

IDE Secondary

A A

USB Port 0

33/66/100/133

44.44MHz(W)/50MHz(R)@88.9/100MB/s

USB Port 1

USB Port 2

USB Port 3

USB Port 4

USB

240MHz@60MB/s

LPC Bus

33MHz@16.5MB/s

LPC SIO

USB Port 5

SMSC

LPC47M292

USB Port 6

USB Port 7

AD1980

AC'97 Codec

GIGA LAN

BCM4401/5705

AC'97 Link

12.288MHz@1.536MB/s

PCI

33MHz@133MB/s

Flash

Floppy Parallel Serial

1

MSI

Title

Size Document Number Rev

Date: Sheet of

MICRO-STAR INt'L CO., LTD.

H/W Project Leader : Andy Chen

H/W Project Engineer : Prudence Wang

BLOCK DIAGRAM

MS-6726D2

2 29Tuesday, November 26, 2002

0A

8

7

6

5

4

3

2

1

VID0

AE5

VID1#

VID0#

LINT0/INTR

D2#

D1#

B22

B21

GTLREF0

GTLREF1

GTLREF2

GTLREF3

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

BCLK1#

BCLK0#

RS2#

RS1#

RS0#

AP1#

AP0#

BR0#

COMP1

COMP0

DP3#

DP2#

DP1#

DP0#

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

LINT1/NMI

D0#

NORTH/PRES

CRITICAL

ITP_DBR# (24)

VCC_SENSE (23)

VSS_SENSE (23)

VID_GD (4)

VID[0..5] (11,23)

GTLREF

AA21

AA6

F20

F6

BPM#5

AB4

BPM#4

AA5

BPM#3

Y6

BPM#2

AC4

BPM#1

AB5

BPM#0

AC6

HREQ#4

H3

HREQ#3

J3

HREQ#2

J4

HREQ#1

K5

HREQ#0

J1

TESTHI12

AD25

TESTHI11

A6

TESTHI10

Y3

TESTHI9

W4

TESTHI8

U6

AB22

AA20

AC23

AC24

AC20

TESTHI2

AC21

TESTHI1

AA2

TESTHI0

AD24

AF23

AF22

HRS#2

F4

HRS#1

G5

HRS#0

F1

V5

AC1

H6

COMP1

P1

COMP0

L24

L25

K26

K25

J26

R5

L5

W23

P23

J23

F21

W22

R22

K22

E22

E5

D1

GTLREF (5,24)

C1 220p_X7R

16V

BPM#5 (24)

BPM#4 (24)

BPM#3 (24)

BPM#2 (24)

BPM#1 (24)

BPM#0 (24)

R3 62

R4 62

R5 62

R6 62

R7 62

R9 62

R624 62

R10 62

CPU_CLK# (10)

CPU_CLK (10)

HBR#0 (5,24)

R13 61.9RST

R15 61.9RST

HADSTB#1 (5)

HADSTB#0 (5)

HDSTBP#3 (5)

HDSTBP#2 (5)

HDSTBP#1 (5)

HDSTBP#0 (5)

HDSTBN#3 (5)

HDSTBN#2 (5)

HDSTBN#1 (5)

HDSTBN#0 (5)

NMI (9)

INTR (9)

HREQ#[0..4] (5)

VCCP

HRS#[0..2] (5)

CPU SIGNAL BLOCK

HA#[3..31](5)

D D

HA#31

HA#25

HA#26

HA#28

HA#30

HA#27

HA#29

CPU1A

HDBI#[0..3](5)

FERR#(9)

STPCLK#(9)

HDBI#0

HDBI#1

HDBI#2

HDBI#3

HINIT#(9)

HDBSY#(5)

HDRDY#(5)

HTRDY#(5)

HADS#(5)

HDEFER#(5)

ITP_TRST#(24)

THERMDP#(11)

THERMDN#(11)

TRMTRIP#(9,16,24)

PROCHOT#(5)

HLOCK#(5)

HBNR#(5)

HIT#(5)

HITM#(5)

HBPRI#(5)

ITP_TDI(24)

ITP_TDO(24)

ITP_TMS(24)

ITP_TCK(24)

IGNNE#(9)

SMI#(9)

A20M#(9)

SLP#(9)

BOOT(23)

R627 X_0

BSEL0(5,10)

BSEL1(5,10)

OPTIMIZ

C C

B B

CPU_GD(9,24)

CPURST#(5,24)

HD#[0..63](5)

HD#63

HD#62

HD#61

HD#60

HD#59

HD#58

HD#57

HD#56

HD#55

HD#54

E21

DBI0#

G25

DBI1#

P26

DBI2#

V21

DBI3#

AC3

IERR#

V6

MCERR#

B6

FERR#

Y4

STPCLK#

AA3

BINIT#

W5

INIT#

AB2

RSP#

H5

DBSY#

H2

DRDY#

J6

TRDY#

G1

ADS#

G4

LOCK#

G2

BNR#

F3

HIT#

E3

HITM#

D2

BPRI#

E2

DEFER#

C1

TDI

D5

TDO

F7

TMS

E6

TRST#

D4

TCK

B3

THERMDA

C4

THERMDC

A2

THERMTRIP#

AF26

GND/SKTOCC#

C3

PROCHOT#

B2

IGNNE#

B5

SMI#

C6

A20M#

AB26

SLP#

A22

RESERVED0

A7

RESERVED1

AE21

RESERVED2

AF24

RESERVED3

AF25

RESERVED4

AD1

BOOTSELECT

AE26

OPTIMIZED/COMPAT#

AD6

BSEL0

AD5

BSEL1

AB23

PWRGOOD

AB25

RESET#

AA24

D63#

AA22

D62#

AA25

D61#

Y21

D60#

Y24

D59#

Y23

D58#

W25

D57#

Y26

D56#

W26

D55#

V24

D54#

AB1Y1W2V3U4T5W1R6V2T4U3P6U1T2R3P4P3R2T1N5N4N2M1N1M4M3L2M6L3K1L6K4K2

A35#

A34#

A33#

A32#

A31#

A30#

A29#

A28#

A27#

A26#

A25#

D53#

D52#

D51#

D50#

D49#

D48#

D47#

D46#

D45#

D44#

D43#

D42#

D41#

D40#

V22

U21

V25

U23

U24

U26

T23

T22

T25

T26

R24

R25

P24

R21

HA#24

A24#

D39#

N25

HA#22

HA#23

A23#

D38#

N26

M26

HA#21

A22#

D37#

N23

HA#20

A21#

D36#

M24

HA#19

A20#

D35#

P21

HA#18

A19#

D34#

N22

HA#17

A18#

D33#

M23

HA#16

A17#

D32#

H25

HA#15

A16#

D31#

K23

HA#14

A15#

D30#

J24

HA#13

A14#

D29#

L22

HA#12

A13#

D28#

M21

HA#11

A12#

D27#

H24

HA#10

A11#

D26#

G26

HA#9

A10#

D25#

L21

HA#8

A9#

D24#

D26

HA#7

A8#

D23#

F26

HA#6

A7#

D22#

E25

A6#

D21#

HA#5

A5#

D20#

F24

HA#4

F23

HA#3

A4#

D19#

G23

A3#

D18#

E24

D17#

H22

AE25A5A4

DBR#

D16#

D15#

D25

J21

VSS_SENSE

VCC_SENSE

D14#

D13#

D12#

D23

C26

H21

AD26

AC26

ITP_CLK1

D11#

D10#

G22

B25

VID5

AD2

AD3

ITP_CLK0

VIDPWRGD

D9#

D8#

D7#

C24

C23

B24

VID4

AE1

VID5#

D6#

D22

VID3

AE2

VID4#

D5#

C21

VID2

AE3

VID3#

D4#

A25

VID1

AE4

VID2#

D3#

A23

HD#47

HD#48

HD#45

HD#46

HD#44

HD#43

6

HD#42

HD#41

HD#40

HD#39

HD#38

HD#37

HD#52

HD#53

HD#50

HD#49

A A

8

7

HD#51

HD#35

HD#36

HD#34

HD#33

HD#31

HD#32

HD#30

HD#29

HD#27

HD#28

HD#26

HD#25

5

HD#23

HD#24

HD#21

HD#22

HD#20

HD#19

HD#18

HD#17

HD#16

HD#15

HD#14

HD#13

HD#12

HD#10

HD#11

HD#9

HD#8

HD#7

HD#6

4

HD#5

HD#4

HD#3

HD#2

HD#1

HD#0

MSI

Title

Size Document Number Rev

3

Date: Sheet of

MICRO-STAR INt'L CO., LTD.

H/W Project Leader : Andy Chen

H/W Project Engineer : Prudence Wang

Intel mPGA478B - Signals

MS-6726D2

2

3 29Tuesday, November 26, 2002

0A

1

8

7

6

5

4

3

2

1

AF4

VSS

H26H4J2

AF3

VCC-VID

VCC-VIDPRG

VSS

VSS

VSS

J22

AD20

VCC-IOPLL

VSS

VSS

J25J5K21

1.2V 150mA

VCC_VID

CPU_IOPLL

AE23

VCCA

VSSA

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

NORTH/PRES

CRITICAL

AD22

Y5

Y25

Y22

Y2

W6

W3

W24

W21

V4

V26

V23

V1

U5

U25

U22

U2

T6

T3

T24

T21

R4

R26

R23

R1

P5

P25

P22

P2

N6

N3

N24

N21

M5

M25

M22

M2

L4

L26

L23

L1

K6

K3

K24

EC3

22u-1206_X5R

6.3V

VSSA

It must close bulk caps.

It support DC current if 100mA.

L1 10uH-0805-100mA

L2 10uH-0805-100mA

EC4

10u-1206_Y5V

10V

DC voltage drop should

be less than 70mV.

VCCP

U1

VID_GD(3,10,23)

AF7

AF9

VCC

VCC

VSS

VSS

D14

D16

VIDGD rising time is 150ns.VID to VIDGD deassertion time is 1ms for max.

B11

B13

B15

B17

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

D18

D20

D21D3D24D6D8E1E11

1

VIN

3

2

GNDENPOK

SN105125-150mA

CRITICAL

B19B7B9

VCC

VCC

VSS

VSS

VCC3

AE20

VCC

VSS

C13

AE6

VCC

VSS

C15

AE8

VCC

VSS

C17C2C19

AF11

AF13

VCC

VSS

CB336 0.1u_X7R

AF15

AF17

AF19

AF2

AF21

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

C22

C25C5C7C9D12

VCC

VSS

AF5

VCC

VSS

CPU VOLTAGE BLOCK

VID Voltage is from 1.14V to 1.32V.

It is derived from 3.3V.

D D

VCCP

A10

A12

A14

A16

A18

A20A8AA10

AA12

AA14

AA16

AA18

AA8

AB11

AB13

AB15

AB17

AB19

AB7

AB9

AC10

VCC

VSS

AE24

AE7

VCC

VSS

AE9

VCC

VSS

AC12

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

AF1

AF10

AF12

AF14

CPU1B

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

AE11

VSS

AE13

VSS

AE15

VSS

AE17

VSS

AE19

VCC

VSS

AE22

D10

VSS

A11

VSS

A13

VSS

A15

VSS

A17

VSS

A19

VSS

A21

VSS

A24

VSS

A26

VSS

A3

VSS

A9

VSS

AA1

VSS

AA11

VSS

AA13

VSS

AA15

VSS

AA17

VSS

C C

B B

AA19

AA23

AA26

AA4

AA7

AA9

AB10

AB12

AB14

AB16

AB18

AB20

AB21

AB24

AB3

AB6

AB8

AC11

AC13

AC15

AC17

AC19

AC2

AC22

AC25

AC5

AC7

AC9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AD10

VSS

AD12

VSS

AD14

VSS

AD16

VSS

AD18

VSS

AD21

VSS

AD23

AD4

VSS

AD8

It should be able to source 150mA.

It drives the power logic of BSEL[1:0] and VID[5:0]. It must rout to the enable pin of PWM and CK-409.

VID to VIDGD delay time is from 1ms to 10ms. VIDGD to Vccp delay time is from 1ms to 10ms.

AC14

AC16

AC18

AC8

AD11

AD13

AD15

AD17

AD19

AD7

AD9

AE10

AE12

AE14

AE16

AE18

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AF16

AF18

AF20

AF6

AF8

B10

B12

B14

B16

B18

B23

B20

B26B4B8

C11

VCC

VSS

5

VOUT

4

C10

C12

C14

C16

C18

C20C8D11

D13

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

E13

E15

E17

E19

E23

E4

E26

VCC_VID

R36

2.43KSTC41u-0805_X7R

D15

D17

D19D7D9

E10

E12

E14

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

E7E9F10

F12

F14

F16

F18F2F22

E16

E18

VCC

VSS

F25F5F8

E20E8F11

VCC

VCC

VSS

VSS

VCC

VSS

F13

VCC

VSS

G21G6G24

Near processorNear regulator

F15

F17

VCC

VCC

VCC

VSS

VSS

VSS

G3H1H23

C5

0.1u_X7R

F19

F9

VCC

VCC

VSS

VSS

CPU DECOUPLING CAPACITORS

VCCP VCCP VCCP VCCP VCCP VCCPVCCP VCCP

EC36

22u-1206_X5R

EC29

22u-1206_X5R

EC28

22u-1206_X5R

EC43

22u-1206_X5R

EC38

A A

22u-1206_X5R

EC17

22u-1206_X5R

EC35

22u-1206_X5R

EC21

22u-1206_X5R

EC8

22u-1206_X5R

EC42

22u-1206_X5R

EC39

22u-1206_X5R

EC16

22u-1206_X5R

EC31

X_22u-1206_X5R

EC7

X_22u-1206_X5R

EC9

X_22u-1206_X5R

EC44

22u-1206_X5R

EC24

22u-1206_X5R

EC22

22u-1206_X5R

EC14

22u-1206_X5R

EC6

22u-1206_X5R

EC13

22u-1206_X5R

EC15

X_22u-1206_X5R

EC30

X_22u-1206_X5R

EC32

X_22u-1206_X5R

EC23

X_22u-1206_X5R

EC5

X_22u-1206_X5R

Place these caps within north side of processorPlace these caps within socket cavity Place these caps within south side of processor

8

7

6

5

EC49

X_22u-1206_X5R

EC45

X_22u-1206_X5R

EC25

X_22u-1206_X5R

EC37

X_22u-1206_X5R

EC46

X_22u-1206_X5R

4

EC10

X_22u-1206_X5R

EC18

X_22u-1206_X5R

EC26

X_22u-1206_X5R

EC33

X_22u-1206_X5R

EC40

X_22u-1206_X5R

EC11

X_22u-1206_X5R

EC19

X_22u-1206_X5R

EC27

X_22u-1206_X5R

EC34

X_22u-1206_X5R

EC41

X_22u-1206_X5R

Title

Size Document Number Rev

3

Date: Sheet of

820u/2.5V properly in further

VCCP

Solder side

MSI

MICRO-STAR INt'L CO., LTD.

2

+

EC12

150u-2.5V

CRITICAL

+

EC20

150u-2.5V

CRITICAL

H/W Project Leader : Andy Chen

H/W Project Engineer : Prudence Wang

Intel mPGA478B - Power

MS-6726D2

4 29Tuesday, November 26, 2002

1

0A

8

VCCA_FSB(24)

VCCA_DPLL(24)

HA#[3..31](3)

D D

C C

HADSTB#0(3)

HADSTB#1(3)

HBR#0(3,24)

HBPRI#(3)

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HBNR#(3)

HLOCK#(3)

HADS#(3)

HREQ#[0..4](3)

HIT#(3)

HITM#(3)

HDEFER#(3)

HTRDY#(3)

HDBSY#(3)

HDRDY#(3)

HRS#[0..2](3)

B B

MCH_CLK(10)

MCH_CLK#(10)

PWRGDA(20)

CPURST#(3,24)

PCIRST_ICH5#(8)

PROCHOT#(3,22,24)

R37 2.49KST

BSEL0(3)

BSEL1(3)

R38 2KST

R39 2KST

R40 2.49KST

R41 20RST

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HRS#0

HRS#1

HRS#2

ICH_SYNC#

SEL0

SEL1

HRCOMP

AE14

HSWING(24)

GTLREF(3,24)

220p_X7R

C6

VCCA_FSB

C224 0.1u_X7R

VCCA_DPLL

U2A

D26

HA3#

D30

HA4#

L23

HA5#

E29

HA6#

B32

HA7#

K23

HA8#

C30

HA9#

C31

HA10#

J25

HA11#

B31

HA12#

E30

HA13#

B33

HA14#

J24

HA15#

F25

HA16#

D34

HA17#

C32

HA18#

F28

HA19#

C34

HA20#

J27

HA21#

G27

HA22#

F29

HA23#

E28

HA24#

H27

HA25#

K24

HA26#

E32

HA27#

F31

HA28#

G30

HA29#

J26

HA30#

G26

HA31#

B30

HAD_STB0#

D28

HAD_STB1#

B24

BREQ0#

B26

BPRI#

B28

BNR#

E25

HLOCK#

F27

ADS#

B29

HREQ0#

J23

HREQ1#

L22

HREQ2#

C29

HREQ3#

J21

HREQ4#

K21

HIT#

E23

HITM#

L21

DEFER#

D24

HTRDY#

E27

DBSY#

G24

DRDY#

G22

RS0#

C27

RS1#

B27

RS2#

B7

HCLKP

C7

HCLKN

PWROK

E8

CPURST#

AK4

RSTIN#

AJ8

ICH_SYNC#

L20

PROCHOT#

L13

BSEL0

L12

BSEL1

E24

HDRCOMP

C25

HDSWING

F23

HDVREF

7

B3

VCCA_DPLL

A31

B4

J6J7J8J9K6K7K8K9L6L7L9

VCC

VCCA_FSB

VCCA_FSB

VSS

VSS

VSS

VSS

VSS

C12

C14

C16

C18

C10

C8

VCC

VSS

6

VCC_AGP VTT

N11N9P10

P11

R11

T16

T17

N10

M10

M11M8M9

L10

L11

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

C20

C22

C24

C26

C28D1D11

D13

D15

D17

D9

VCC

VSS

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

D19

D21

D23

D25

D27

D29

T18

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

D31

D33

D35

F3F5F8

E3

F1

E1

5

T19

U16

U17

U20

V16

V18

V20

W16

W19

W20

Y16

Y17

Y18

Y19

Y20

A3

A33

VCC

VCC

VSS

VSS

F24

F26

G28

NCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

G31

G35

H12

H5

H8

H9

VCC

VSS

T20

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VCC

VSS

VSS

VSS

VSS

VSS

VSS

F18

F20

F22

F14

F16

F12

VCC

VSS

F10

A35B2B25

VSS

VSS

H14

H16H2H20

VSS

H18

B34C1C23

VSS

VSS

H22

4

C35

E26

M31

AF13

AF23

AJ12

AN1

AP2

AR3

AR33

R25

AR35

NC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

H24

H26

H30

H33

J10

J12

J14

J16

J18

J20

J22

J28

J32

J35

A7A9A11

VSS

VSS

VSS

VSS

K11

K12

3

D5D6D7E6E7

A13

A16

A20

A23

A25

A27

A29

A32

C4

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

K14

K16

K18

K33

K20

K22

K25

K27

K29

L24

F7

VTT

VTT

VTT

VTT

VTT

VTT

VSS

VSS

VSS

VSS

VSS

VSS

VSS

M3M6M26

L25

L26

L35

L31

A4A5A6B5B6C5C6

VTT

VTT

VTT

VTT

VTT

VTT

VSS

VSS

VSS

VSS

VSS

VSS

M27

M28

M30

M33N1N4

2

VTT_FSB1

VTT_FSB2

A15

A21

HD0#

VTT

HD1#

HD2#

HD3#

VTT_FSB

VTT_FSB

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

DINV_0#

DINV_1#

DINV_2#

DINV_3#

HD_STBP0#

HD_STBN0#

HD_STBP1#

HD_STBN1#

HD_STBP2#

HD_STBN2#

HD_STBP3#

HD_STBN3#

Intel Springdale

CRITICAL

B23

E22

B21

D20

B22

D22

B20

C21

E18

E20

B16

D16

B18

B17

E16

D18

G20

F17

E19

F19

J17

L18

G16

G18

F21

F15

E15

E21

J19

G14

E17

K17

J15

L16

J13

F13

F11

E13

K15

G12

G10

L15

E11

K13

J11

H10

G8

E9

B13

E14

B14

B12

B15

D14

C13

B11

D10

C11

E10

B10

C9

B9

D8

B8

C17

L17

L14

C15

B19

C19

L19

K19

G9

F9

D12

E12

C225 0.47u_Y5V

C226 0.47u_Y5V

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

HDBI#0

HDBI#1

HDBI#2

HDBI#3

1

16V

HD#[0..63] (3)

HDBI#[0..3] (3)

HDSTBP#0 (3)

HDSTBN#0 (3)

HDSTBP#1 (3)

HDSTBN#1 (3)

HDSTBP#2 (3)

HDSTBN#2 (3)

HDSTBP#3 (3)

HDSTBN#3 (3)

A A

PWRGDA(20)

8

PWRGDA

ICH_SYNC#

VCC3

53

1

2

7

ICH_GD PWRGDA ICH_GD

4

U28

NC7SZ08

ICH_GD (9)

6

R526 X_0

5

4

3

MSI

Title

Size Document Number Rev

Date: Sheet of

MICRO-STAR INt'L CO., LTD.

H/W Project Leader : Andy Chen

H/W Project Engineer : Prudence Wang

Intel Springdale - CPU Signals

MS-6726D2

2

5 29Tuesday, November 26, 2002

0A

1

8

MCS_A#0(14)

MCS_A#1(14)

D D

MCS_A#2(14)

MCS_A#3(14)

MRAS_A#(14)

MCAS_A#(14)

MWE_A#(14)

MA_A[0..12](14)

MAB_A[1..5](14)

C C

MBA_A0(14)

MBA_A1(14)

MDQM_A[0..7](14)

MDQS_A[0..7](14)

MCLK_A0(14)

MCLK_A#0(14)

MCLK_A1(14)

B B

MCLK_A#1(14)

MCLK_A2(14)

MCLK_A#2(14)

MCLK_A3(14)

MCLK_A#3(14)

MCLK_A4(14)

MCLK_A#4(14)

MCLK_A5(14)

MCLK_A#5(14)

0.01u_X7RC12

0.01u_X7RC15

0.01u_X7RC16

0.01u_X7RC18

C256 2.2u_Y5V

6.3V

C227 0.47u_Y5V

C228 0.22u_Y5V

C229 0.1u_X7R

8

C230 0.22u_Y5V

C231 0.1u_X7R

A A

MDQ_A[0..63](14) MCKE_A[0..3] (14)

AA34

AC33

AB34

MA_A0

AJ34

MA_A1

AL33

MA_A2

AK29

MA_A3

AN31

MA_A4

AL30

MA_A5

AL26

MA_A6

AL28

MA_A7

AN25

MA_A8

AP26

MA_A9

AP24

MA_A10

AJ33

MA_A11

AN23

MA_A12

AN21

MAB_A1

AL34

MAB_A2

AM34

MAB_A3

AP32

MAB_A4

AP31

MAB_A5

AM26

AE33

AH34

MDQM_A0

AP12

MDQM_A1

AP16

MDQM_A2

AM24

MDQM_A3

AP30

MDQM_A4

AF31

MDQM_A5

W33

MDQM_A6

MDQM_A7

MDQS_A0

AN11

MDQS_A1

AP15

MDQS_A2

AP23

MDQS_A3

AM30

MDQS_A4

AF34

MDQS_A5

MDQS_A6

MDQS_A7

AK32

AK31

AP17

AN17

AK33

AK34

AM16

AL16

XRCOMP

XCOMPH

XCOMPL

SMVREF

XRCOMP(24)

XCOMPH(24)

XCOMPL(24)

VREF(24)

VCC_DDR_C2(24)

VCC_DDR_C3(24)

U2B

SCS_A0#

Y31

SCS_A1#

Y32

SCS_A2#

W34

SCS_A3#

SRAS_A#

Y34

SCAS_A#

SWE_A#

SMAA_A0

SMAA_A1

SMAA_A2

SMAA_A3

SMAA_A4

SMAA_A5

SMAA_A6

SMAA_A7

SMAA_A8

SMAA_A9

SMAA_A10

SMAA_A11

SMAA_A12

SMAB_A1

SMAB_A2

SMAB_A3

SMAB_A4

SMAB_A5

SBA_A0

SBA_A1

SDM_A0

SDM_A1

SDM_A2

SDM_A3

SDM_A4

SDM_A5

M34

SDM_A6

H32

SDM_A7

SDQS_A0

SDQS_A1

SDQS_A2

SDQS_A3

SDQS_A4

V34

SDQS_A5

M32

SDQS_A6

H31

SDQS_A7

SMDCLK_A0

SMDCLK_A0#

SMDCLK_A1

SMDCLK_A1#

N33

SMDCLK_A2

N34

SMDCLK_A2#

SMDCLK_A3

SMDCLK_A3#

SMDCLK_A4

SMDCLK_A4#

P31

SMDCLK_A5

P32

SMDCLK_A5#

AK9

SMXRCOMP

AN9

SMXCOMPVOH

AL9

SMXCOMPVOL

E34

SMVREF_A

VCC_DDR_C1

VCC_DDR_C2

VCC_DDR_C3

VCC_DDR_C4

VCC_DDR_C5

7

MDQ_A3

MDQ_A2

MDQ_A1

AP11

AM12

AN13

SDQ_A1

SDQ_A2

VCC_DDR

VCC_DDR

E35

AA35

R35

MDQ_A4

MDQ_A5

MDQ_A6

AM10

AL10

AL12

SDQ_A3

SDQ_A4

SDQ_A5

VCC_DDR

VCC_DDR

VCC_DDR

AR15

AR21

AL6

MDQ_A7

MDQ_A9

MDQ_A8

AP13

AP14

AM14

SDQ_A6

SDQ_A7

SDQ_A8

VCC_DDR

VCC_DDR

VCC_DDR

AM1

AM2

AL7

SDQ_A9

VCC_DDR

MDQ_A0

AP10

SDQ_A0

7

MDQ_A12

MDQ_A10

MDQ_A11

AL18

AP19

AL14

SDQ_A10

SDQ_A11

VCC_DDR

VCC_DDR

AN8

AP3

AP4

VCC_DDR

MDQ_B[0..63](15)

MDQ_A13

MDQ_A14

MDQ_A15

AN15

AP18

AM18

SDQ_A12

SDQ_A13

SDQ_A14

VCC_DDR

VCC_DDR

VCC_DDR

AP5

AP6

AP7

6

MDQ_A16

MDQ_A17

MDQ_A18

AP22

AM22

AL24

SDQ_A15

SDQ_A16

SDQ_A17

VCC_DDR

VCC_DDR

VCC_DDR

AR4

AR5

AR7

6

MDQ_A19

MDQ_A21

MDQ_A20

AN27

AP21

AL22

SDQ_A18

SDQ_A19

SDQ_A20

VCC_DDR

VCC_DDR

AR31

AJ10

MDQ_B0

MDQ_A23

MDQ_A22

AP25

AP27

SDQ_A21

SDQ_A22

SDQ_A23

SDQ_B0

SDQ_B1

SDQ_B2

AE15

AL11

MDQ_B2

MDQ_B1

MDQ_A25

MDQ_A24

MDQ_A26

AP28

AP29

AP33

SDQ_A24

SDQ_A25

SDQ_B3

SDQ_B4

AE16

AL8

AF12

MDQ_B3

MDQ_B5

MDQ_B4

MDQ_A28

MDQ_A27

AM33

AM28

SDQ_A26

SDQ_A27

SDQ_A28

SDQ_B5

SDQ_B6

SDQ_B7

AK11

AG12

MDQ_B6

MDQ_B7

MDQ_A30

MDQ_A31

MDQ_A29

AN29

AM31

AN34

SDQ_A29

SDQ_A30

SDQ_B8

SDQ_B9

AE17

AL13

AK17

MDQ_B8

MDQ_B9

MDQ_B10

MDQ_A32

MDQ_A33

AH32

AG34

SDQ_A31

SDQ_A32

SDQ_A33

SDQ_B10

SDQ_B11

SDQ_B12

AL17

AK13

MDQ_B12

MDQ_B11

5

MDQ_A35

MDQ_A36

MDQ_A34

AF32

AD32

AH31

SDQ_A34

SDQ_A35

SDQ_B13

SDQ_B14

AJ14

AJ16

AJ18

MDQ_B15

MDQ_B14

MDQ_B13

5

MDQ_A38

MDQ_A37

AG33

AE34

SDQ_A36

SDQ_A37

SDQ_A38

SDQ_B15

SDQ_B16

SDQ_B17

AE19

AE20

MDQ_B17

MDQ_B16

MDQ_A41

MDQ_A40

MDQ_A39

AD34

AC34

AB31

SDQ_A39

SDQ_A40

SDQ_B18

SDQ_B19

AG23

AK23

AL19

MDQ_B18

MDQ_B20

MDQ_B19

MDQ_A42

MDQ_A43

V32

V31

SDQ_A41

SDQ_A42

SDQ_A43

SDQ_B20

SDQ_B21

SDQ_B22

AK21

AJ24

MDQ_B22

MDQ_B21

MDQ_A45

MDQ_A46

MDQ_A44

AD31

AB32

U34

SDQ_A44

SDQ_A45

SDQ_B23

SDQ_B24

AE22

AK25

AH26

MDQ_B24

MDQ_B23

MDQ_B25

MDQ_A47

MDQ_A48

U33

T34

SDQ_A46

SDQ_A47

SDQ_A48

SDQ_B25

SDQ_B26

SDQ_B27

AG27

AF27

MDQ_B27

MDQ_B26

MDQ_A50

MDQ_A51

MDQ_A49

T32

K34

K32

SDQ_A49

SDQ_A50

SDQ_B28

SDQ_B29

AJ26

AJ27

AD25

MDQ_B30

MDQ_B28

MDQ_B29

MDQ_A53

MDQ_A52

T31

P34

SDQ_A51

SDQ_A52

SDQ_A53

SDQ_B30

SDQ_B31

SDQ_B32

AF28

AE30

MDQ_B32

MDQ_B31

4

MDQ_A55

MDQ_A56

MDQ_A54

L34

L33

J33

SDQ_A54

SDQ_A55

SDQ_B33

SDQ_B34

AC27

AC30

Y29

MDQ_B35

MDQ_B33

MDQ_B34

4

MDQ_A57

MDQ_A58

H34

E33

SDQ_A56

SDQ_A57

SDQ_A58

SDQ_B35

SDQ_B36

SDQ_B37

AE31

AB29

MDQ_B37

MDQ_B36

MDQ_A61

MDQ_A59

MDQ_A60

F33

K31

J34

SDQ_A59

SDQ_A60

SDQ_B38

SDQ_B39

AA26

AA27

AA30

MDQ_B40

MDQ_B39

MDQ_B38

MDQ_A63

MDQ_A62

G34

F34

SDQ_A61

SDQ_A62

SDQ_A63

SDQ_B40

SDQ_B41

SDQ_B42

W30

U27

MDQ_B41

MDQ_B42

MCKE_A1

MCKE_A0

AL20

AN19

SCKE_A0

SCKE_A1

SDQ_B43

SDQ_B44

SDQ_B45

T25

AA31

V29

MDQ_B43

MDQ_B44

MDQ_B45

MCKE_A2

MCKE_A3

AM20

AP20

SCKE_A2

SCKE_A3

SDQ_B46

SDQ_B47

SDQ_B48

U25

R27

P29

MDQ_B48

MDQ_B47

MDQ_B46

AC26

AB25

AC25

VCCA_DDR

VCCA_DDR

VCCA_DDR

SDQ_B49

SDQ_B50

SDQ_B51

R30

K28

L30

MDQ_B49

MDQ_B51

MDQ_B50

3

VCCA_DDR

C20 0.1u_X7R

VCCADDR

AN4

AM3

AN5

AM5

AL35

VCC_DDR

VCC_DDR

VCC_DDR

VCCA_DDR

SDQ_B52

SDQ_B53

SDQ_B54

SDQ_B55

SDQ_B56

R31

R26

P25

L32

K30

H29

MDQ_B53

MDQ_B56

MDQ_B57

MDQ_B55

MDQ_B52

MDQ_B54

3

AM6

AM7

AM8

VCC_DDR

VCC_DDR

VCC_DDR

SDQ_B57

SDQ_B58

SDQ_B59

F32

G33

N25

MDQ_B58

MDQ_B60

MDQ_B59

2

VCCA_DDR (24)

VCC_DDR

Its current is 4.1A.

AN2

AN6

AN7

P3P6P8

N35

VCC_DDR

VCC_DDR

VCC_DDR

SDQ_B60

SDQ_B61

SDQ_B62

M25

J29

G32

MDQ_B62

MDQ_B61

MDQ_B63

N32

VSS

VCC_DDR

SDQ_B63

SCKE_B0

AK19

AF19

MCKE_B0

MCKE_B1

VSS

VSS

VSS

SCMDCLK_B0

SCMDCLK_B0#

SCMDCLK_B1

SCMDCLK_B1#

SCMDCLK_B2

SCMDCLK_B2#

SCMDCLK_B3

SCMDCLK_B3#

SCMDCLK_B4

SCMDCLK_B4#

SCMDCLK_B5

SCMDCLK_B5#

SMYRCOMP

SMYCOMPVOH

SMYCOMPVOL

SCKE_B1

SCKE_B2

SCKE_B3

Intel Springdale

AG19

AE18

CRITICAL

MCKE_B2

MCKE_B3

SCS_B0#

VSS

SCS_B1#

SCS_B2#

SCS_B3#

SRAS_B#

SCAS_B#

SWE_B#

SMAA_B0

SMAA_B1

SMAA_B2

SMAA_B3

SMAA_B4

SMAA_B5

SMAA_B6

SMAA_B7

SMAA_B8

SMAA_B9

SMAA_B10

SMAA_B11

SMAA_B12

SMAB_B1

SMAB_B2

SMAB_B3

SMAB_B4

SMAB_B5

SBA_B0

SBA_B1

SDM_B0

SDM_B1

SDM_B2

SDM_B3

SDM_B4

SDM_B5

SDM_B6

SDM_B7

SDQS_B0

SDQS_B1

SDQS_B2

SDQS_B3

SDQS_B4

SDQS_B5

SDQS_B6

SDQS_B7

SMVREF_B

U26

T29

V25

W25

W26

W31

W27

AG31

AJ31

AD27

AE24

AK27

AG25

AL25

AF21

AL23

AJ22

AF29

AL21

AJ20

AE27

AD26

AL29

AL27

AE23

Y25

AA25

AG11

AG15

AE21

AJ28

AC31

U31

M29

J31

AF15

AG13

AG21

AH27

AD29

U30

L27

J30

AG29

AG30

AF17

AG17

N27

N26

AJ30

AH29

AK15

AL15

N31

N30

AA33

R34

R33

AP9

MA_B0

MA_B1

MA_B2

MA_B3

MA_B4

MA_B5

MA_B6

MA_B7

MA_B8

MA_B9

MA_B10

MA_B11

MA_B12

MAB_B1

MAB_B2

MAB_B3

MAB_B4

MAB_B5

MDQM_B0

MDQM_B1

MDQM_B2

MDQM_B3

MDQM_B4

MDQM_B5

MDQM_B6

MDQM_B7

MDQS_B0

MDQS_B1

MDQS_B2

MDQS_B3

MDQS_B4

MDQS_B5

MDQS_B6

MDQS_B7

YRCOMP

YCOMPH

YCOMPL

VREF

MCS_B#0 (15)

MCS_B#1 (15)

MCS_B#2 (15)

MCS_B#3 (15)

MRAS_B# (15)

MCAS_B# (15)

MWE_B# (15)

MBA_B0 (15)

MBA_B1 (15)

MCLK_B0 (15)

MCLK_B#0 (15)

MCLK_B1 (15)

MCLK_B#1 (15)

MCLK_B2 (15)

MCLK_B#2 (15)

MCLK_B3 (15)

MCLK_B#3 (15)

MCLK_B4 (15)

MCLK_B#4 (15)

MCLK_B5 (15)

MCLK_B#5 (15)

0.01u_X7RC11

0.01u_X7RC13

0.01u_X7RC14

0.01u_X7RC17

MCKE_B[0..3] (15)

MSI

Title

Size Document Number Rev

Date: Sheet of

MICRO-STAR INt'L CO., LTD.

H/W Project Leader : Andy Chen

H/W Project Engineer : Prudence Wang

Intel Springdale - Memory Signals

MS-6726D2

2

6 29Tuesday, November 26, 2002

1

MA_B[0..12] (15)

MAB_B[1..5] (15)

MDQM_B[0..7] (15)

MDQS_B[0..7] (15)

YRCOMP (24)

YCOMPH (24)

YCOMPL (24)

1

0A

8

7

6

5

4

3

2

1

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VSS

VSS

VSS

AR9

AR11

AR13

VCCA_AGP

AG1

Y11

VCC_AGP

VCCA_AGP

VCCA_AGP

HI_STRF

HI_STRS

HI_RCOMP

HI_SWING

HI_VREF

CISTRF

CISTRS

CI_RCOMP

CI_SWING

CI_VREF

DREFCLK

DDCA_CLK

DDCA_DATA

VSYNC

HSYNC

BLUE#

GREEN

GREEN#

REFSET

VCC_DAC

VCC_DAC

VCCA_DAC

VSSA_DAC

EXTTS#

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

VSS

VSS

VSS

VSS

AR23

AR16

AR20

AF5

HI0

AG3

HI1

AK2

HI2

AG5

HI3

AK5

HI4

AL3

HI5

AL2

HI6

AL4

HI7

AJ2

HI8

AH2

HI9

AJ3

HI10

AH5

AH4

AD4

AE3

AE2

AK7

CI0

AH7

CI1

AD11

CI2

AF7

CI3

AD7

CI4

AC10

CI5

AF8

CI6

AG7

CI7

AE9

CI8

AH9

CI9

AG6

CI10

AJ6

AJ5

AG2

AF2

AF4

G4

F2

H3

E2

G3

H7

BLUE

G6

H6

G5

F4

RED

E4

RED#

D2

G1

G2

0.1u_X7R 0.01u_X7R

C2

D3

AP8

AG9

AG10

AN35

AP34

AR1

AR25

VSS

AR27

VSS

AR29

VSS

AR32

VSS

Intel Springdale

CRITICAL

VCC_AGP

C24

0.1u_X7R

HL0

HL1

HL2

HL3

HL4

HL5

HL6

HL7GAD8

HL8

HL9

HL10

HL_COMP

R62 52.3RST

CI_RCOMP

R63 52.3RST

C232 0.1u_X7R

C233 0.1u_X7R

GSET

R64 137RST

CB24

VCCA_DAC

C27

0.1u_X7R

VCC_DAC

1.7V@250mA

HL[0..10] (9)

HL_STRF (9)

HL_STRS (9)

HL_SWING (24)

0.01u_X7RC25

HL_VREF (24)

0.01u_X7RC26

CI_SWING (24)

CI_VREF (24)

DOT_48 (10)

3VDDCCL (18)

3VDDCDA (18)

CRT_VSYNC (18)

CRT_HSYNC (18)

CRT_B (18)

CRT_G (18)

CRT_R (18)

VCC3

CB25

+

CB26

0.01u_X7R

L6 100nH-300mA

VCC_AGP

VCC_AGP

CT27

470u-16V

VCC_AGP_C

P26

P27

P28

P30

P33R1R4

R32T1T3

AE32

VSS

VSS

AE35

VSS

VSS

T6T8T9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AF3

AF11

AF14

AF6

AF9

VSS

AD30

VSS

AD33

VSS

AD28

AE1

VSS

AE4

VSS

VSS

AE10

P9

VSS

VSS

AE11

AE12

VSS

VSS

VSS

VSS

AE13

VSS

VSS

AE25

VSS

VSS

AE26

GAD[0..31](16)

D D

C C

GC_BE#[0..3](16)

AD_STB0(16)

AD_STB#0(16)

AD_STB1(16)

AD_STB#1(16)

GREQ#(16)

GGNT#(16)

ST[0..2](16)

RBF#(16)

WBF#(16)

GFRAME#(16)

GIRDY#(16)

GTRDY#(16)

GDEVSEL#(16)

B B

GSTOP#(16)

GPAR(16)

MCH_66(10)

SBA[0..7](16)

SB_STB(16)

SB_STB#(16)

PIPE#(16)

VCC_AGP

A A

DBI_LO(16)

R66 43.2RST

0.01u_X7RC28

GSWING(16)

AGP_REF(16)

0.01u_X7RC29

GAD0

GAD1

GAD2

GAD3

GAD4

GAD5

GAD6

GAD7

GAD9

GAD10

GAD11

GAD12

GAD13

GAD14

GAD15

GAD16

GAD17

GAD18

GAD19

GAD20

GAD21

GAD22

GAD23

GAD24

GAD25

GAD26

GAD27

GAD28

GAD29

GAD30

GAD31

GC_BE#0

GC_BE#1

GC_BE#2

GC_BE#3

ST0

ST1

ST2

RBF#

WBF#

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

GRCOMP

GSWING

U2C

AE6

GAD0/DVOB_HSYNC

AC11

GAD1/DVOB_VSYNC

AD5

GAD2/DVOB_D1

AE5

GAD3/DVOB_D0

AA10

GAD4/DVOB_D3

AC9

GAD5/DVOB_D2

AB11

GAD6/DVOB_D5

AB7

GAD7/DVOB_D4

AA9

GAD8/DVOB_D6

AA6

GAD9/DVOB_D9

AA5

GAD10/DVOB_D8

W10

GAD11/DVOB_D11

AA11

GAD12/DVOB_D10

W6

GAD13/DVOBC_CLKINT

W9

GAD14/DVOB_FLDSTL

V7

GAD15/MDDC_DATA

AA2

GAD16/DVOC_VSYNC

Y4

GAD17/DVOC_HSYNC

Y2

GAD18/DVOC_BLANK#

W2

GAD19/DVOC_D0

Y5

GAD20/DVOC_D1

V2

GAD21/DVOC_D2

W3

GAD22/DVOC_D3

U3

GAD23/DVOC_D4

T2

GAD24/DVOC_D7

T4

GAD25/DVOC_D6

T5

GAD26/DVOC_D9

R2

GAD27/DVOC_D8

P2

GAD28/DVOC_D11

P5

GAD29/DVOC_D10

P4

GAD30/DVOBC_INTR#

M2

GAD31/DVOC_FLDSTL

Y7

GCBE0/DVOB_D7

W5

GCBE1/DVOB_BLANK#

AA3

GCBE2

U2

GCBE3/DVOC_D5

AC6

GADSTBF0/DVOB_CLK

AC5

GADSTBS0/DVOB_CLK#

V4

GADSTBF1/DVOC_CLK

V5

GADSTBS1/DVOC_CLK#

N6

GREQ

M7

GGNT

N3

GST0

N5

GST1

N2

GST2

R10

GRBF

R9

GWBF

U6

GFRAME/MDVI_DATA

V11

GIRDY/MI2CCLK

AB5

GTRDY/MDVI_CLK

AB4

GDEVSEL/MI2CDATA

W11

GSTOP/MDDC_CLK

AB2

GPAR/ADD_DETECT

H4

GCLKIN

R6

GSBA0#/ADD_ID0

P7

GSBA1#/ADD_ID1

R3

GSBA2#/ADD_ID2

R5

GSBA3#/ADD_ID3

U9

GSBA4#/ADD_ID4

U10

GSBA5#/ADD_ID5

U5

GSBA6#/ADD_ID6

T7

GSBA7#/ADD_ID7

U11

GSBSTBF

T11

GSBSTBS

M4

DBI_HI

M5

DBI_LO

AC2

GRCOMP/DVOBC_RCOMP

AC3

GVSWING

AD2

GVREF

AF16

VSS

VSS

AF18

VSS

VSS

T10

VSS

VSS

AF20

T26

AF22

VSS

VSS

T27

AF24

VSS

VSS

T28

AF25

VSS

VSS

T30

VSS

VSS

AF30

T33

VSS

VSS

AF33

T35

AG4

U4

VSS

VSS

AG8

U18

U19

U32V3V8V9V10

VSS

VSS

VSS

VSS

VSS

VSS

AG14

AG16

AG18

VSS

VSS

VSS

VSS

AG20

V6

VSS

VSS

AG22

VSS

VSS

AG24

VSS

VSS

AG26

VSS

VSS

AG28

V17

VSS

VSS

AG32

V19

VSS

VSS

AG35

V26

AH3

V27

VSS

VSS

AH6

V28

V30W4W17

VSS

VSS

VSS

VSS

AH12

AH10

VSS

VSS

V33

AH14

VSS

VSS

AH16

Y3

W18

W32Y6Y8Y9Y26

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AH18

AH20

AH22

AH24

VSS

VSS

AH30

VSS

VSS

VSS

VSS

AH33

Y28

Y30

Y33

Y35

Y27

AA1

AA4

AA32

AB10

AB26

AC1

AC4

AC32

AB28

VSS

VSS

AL32

AB30

VSS

VSS

AM9

AB33

VSS

VSS

AM11

VSS

VSS

AM13

VSS

VSS

AM15

VSS

VSS

AM17

AC35

VSS

VSS

AM19

AD3

VSS

VSS

AM21

AD6

VSS

VSS

AM23

AB27

AB3

AB6

AB8

AK12

VSS

VSS

AK14

VSS

VSS

AK16

VSS

VSS

AK18

VSS

VSS

AK20

VSS

VSS

AK22

VSS

VSS

AB9

AK24

VSS

VSS

AK26

VSS

VSS

VSS

VSS

AK28

VSS

VSS

AL1

Y10

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AK3

AJ9

AJ32

AJ35

AK8

AK10

VSS

VSS

AJ1

AJ4

C23 0.1u_X7RC215 0.1u_X7R

L1L5Y1J1J2J3K2K3K4K5J4J5L4L2L3

AD8

AD9

AD10

VSS

VSS

VSS

VCC_AGP

VCC_AGP

VCC_AGP

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AM25

AM27

AM29

AM35

AN10

AN12

AN14

AN16

VCC_AGP

VSS

VCC_AGP

VCC_AGP

VSS

VSS

AN18

AN20

VCC_AGP

VCC_AGP

VSS

VSS

AN22

AN24

AN26

VCCA_AGP_C

VCC_AGP

VCC_AGP

VCC_AGP

VSS

VSS

VSS

AN28

AN30

AN32

MSI

Title

Size Document Number Rev

8

7

6

5

4

3

Date: Sheet of

MICRO-STAR INt'L CO., LTD.

H/W Project Leader : Andy Chen

H/W Project Engineer : Prudence Wang

Intel Springdale - AGP & HLink & LAN Signals

MS-6726D2

2

7 29Tuesday, November 26, 2002

1

0A

8

7

6

VCC3 VCC_AGP

5

3VSB

4

SUS_A

C238 0.1u_X7R

SUS_B

C239 0.1u_X7R

SUS_C

C240 0.1u_X7R

Solder

3

2

1

ICH5 Pull Down Resistors

3VSB

AC_SDIN1

B5F6G1H6K6L6M10

D D

C C

AD[0..31](13,17)

C_BE#[0..3](13,17)

FRAME#(13,17)

IRDY#(13,17)

TRDY#(13,17)

DEVSEL#(13,17)

STOP#(13,17)

PERR#(13,17)

SERR#(13,17)

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

C_BE#0

C_BE#1

C_BE#2

C_BE#3

PAR(13,17)

LOCK#(17)

PCI_PME#(13,16,17)

PIRQ#A(16,17)

PIRQ#B(16,17)

B B

PIRQ#C(17)

PIRQ#D(17)

PIRQ#E(13,17)

PIRQ#F(17)

PIRQ#G(17)

PIRQ#H(17)

PREQ#[0..4](13,17)

PGNT#[0..2](13,17)

REQA#(24)

PREQ#5(17)

PGNT#5(17)

PREQ#0

PREQ#1

PREQ#2

PREQ#3

PREQ#4

PGNT#0

PGNT#1

PGNT#2

PREQ#5

PGNT#5

ICH_PCLK(10)

A A

PCIRST_ICH5#(5,10,11,18)

8

U3A

J4

AD0

J5

AD1

G3

AD2

K4

AD3

H5

AD4

H2

AD5

J3

AD6

J2

AD7

K5

AD8

F2

AD9

M4

AD10

H4

AD11

L5

AD12

G2

AD13

K1

AD14

G5

AD15

G4

AD16

L1

AD17

B2

AD18

P5

AD19

H3

AD20

N5

AD21

C4

AD22

N4

AD23

E6

AD24

P3

AD25

D3

AD26

N2

AD27

F5

AD28

P4

AD29

F4

AD30

P2

AD31

E3

C/BE0#

J1

C/BE1#

N3

C/BE2#

M2

C/BE3#

D2

FRAME#

M3

IRDY#

E4

TRDY#

L3

DEVSEL#

E5

STOP#

F1

PAR

K2

PERR#

L4

SERR#

L2

PLOCK#

V2

PME#

B3

PIRQA#

E1

PIRQB#

A2

PIRQC#

C2

PIRQD#

D7

PIRQE#/GPI2

A6

PIRQF#/GPI3

E2

PIRQG#/GPI4

B1

PIRQH#/GPI5

D5

REQ0#

C1

REQ1#

C5

REQ2#

B6

REQ3#

C6

REQ4#/GPI40

D4

GNT0#

A3

GNT1#

B7

GNT2#

C7

GNT3#

A4

GNT4#/GPO48

A5

REQA#/GPI0

E7

REQB#REQ5#/GPI1

E8

GNTA#/GPO16

B4

GNTB#/GNT5#/GPO17

N1

PCICLK

V4

PCIRST#

Intel ICH5

CRITICAL

7

VCC3_3

VCC3_3

VCC3_3

G19

G21

VCC3_3

VCC3_3

VCC3_3

GND

A1A7A10

VCC3_3

VCC3_3

GND

GND

A15

N10P6R13

VCC3_3

VCC3_3

GND

GND

A17

A19

V19

VCC3_3

VCC3_3

GND

GND

A21

A23

W15

W17

VCC3_3

VCC3_3

GND

GND

AA5

AA7

W24

AD13

VCC3_3

VCC3_3

GND

GND

AA9

AA11

AD20

VCC3_3

VCC3_3

GND

GND

AA13

AA21

6

K10

GND

AA24

K12

K13

VCC1_5

VCC1_5

GND

GND

AB5

AB7

L19

P19

VCC1_5

VCC1_5

GND

GND

AB9

AB11

R10R6H24

VCC1_5

VCC1_5

GND

GND

AB15

AB18

J19

VCC1_5

VCC1_5

GND

GND

AC2

AC4

K19

M15

VCC1_5

VCC1_5

GND

GND

AC6

AC8

N15

N23

VCC1_5

VCC1_5

GND

GND

AC10

AC13

VCC1_5

GND

E15

F15

F14

R12W6W7

VCC1_5

VCC1_5S

VCC1_5S

VCC1_5S

VCC1_5S

GND

GND

GND

GND

GND

AC23

AD4

AD6

AD8

AD17

5

W8

VCC1_5S

VCC1_5S

GND

GND

AD21

AD12

W9

W10

VCC1_5S

VCC1_5S

GND

GND

B13

B17

W19

E22

W11

VCC1_5S

VCC1_5S

GND

GND

B19

B21

B23C3C8

B15

VCC1_5S

VCCSUS3_3

GND

GND

GND

E13

E14

E18

F16

VCCSUS3_3

VCCSUS3_3

VCCSUS3_3

GND

GND

GND

C16

C18

C20

C22D1D6

F17

F18

K15U6V6

VCCSUS3_3

VCCSUS3_3

VCCSUS3_3

VCCSUS3_3

GND

GND

GND

GND

D11

D16

F19Y5AA4

VCCSUS3_3

VCCSUS3_3

VCCSUS1_5A

GND

GND

GND

GND

D18

D20

D22

D24

4

AB4F7F8

VCCSUS1_5B

VCCSUS1_5B

VCCSUS1_5B

GND

GND

GND

GND

GND

E17

E19

E20

E21

E11

F10

F11

PDD0

PDD1

PDD2

PDD3

PDD4

PDD5

PDD6

PDD7

PDD8

VCCLAN3_3/VCCSUS3_3

VCCLAN3_3/VCCSUS3_3

VCCLAN3_3/VCCSUS3_3

VCCLAN1_5/VCCSUS1_5C

VCCLAN1_5/VCCSUS1_5C

PDD9

PDD10

PDD11

PDD12

PDD13

PDD14

PDD15

PDA0

PDA1

PDA2

PDCS1#

PDCS3#

PDIOR#

PDIOW#

PIORDY

PDDREQ

PDDACK#

IRQ14

SDD0

SDD1

SDD2

SDD3

SDD4

SDD5

SDD6

SDD7

SDD8

SDD9

SDD10

SDD11

SDD12

SDD13

SDD14

SDD15

SDA0

SDA1

SDA2

SDCS1#

SDCS3#

SDIOR#

SDIOW#

SIORDY

SDDREQ

SDDACK#

IRQ15

AC_SDIN0

AC_SDIN1

AC_SDIN2

AC_SDOUT

AC_SYNC

AC_BIT_CLK

AC_RST#

GND

GND

GND

E23F3F9

AB16

Y13

Y14

AC14

AA14

AC15

AD14

AB14

AD15

Y15

AD16

AA15

AC16

Y16

AA16

AB17

AA19

AD19

AC19

AB19

Y18

AD18

AA17

AA18

AC17

AC18

Y17

AA22

AB23

AD23

AD24

AB21

AC21

AB20

AC20

Y19

AD22

AC22

AA20

AB22

AC24

AB24

AA23

W22

W23

W21

V22

V20

Y23

Y22

Y21

Y20

W20

Y24

E12

D12

A13

A9

B8

D8

C12

3

PDD0

PDD1

PDD2

PDD3

PDD4

PDD5

PDD6

PDD7

PDD8

PDD9

PDD10

PDD11

PDD12

PDD13

PDD14

PDD15

SDD0

SDD1

SDD2

SDD3

SDD4

SDD5

SDD6

SDD7

SDD8

SDD9

SDD10

SDD11

SDD12

SDD13

SDD14

SDD15

AC_SDIN1

AC_SDIN2

SDOUT

R77 33

SYNC

R78 33

PDD[0..15] (18)

ICH5 Decoupling Capacitors

All caps be placed less than 100mils.

PD_A0 (18)

PD_A1 (18)

PD_A2 (18)

PD_CS#1 (18)

PD_CS#3 (18)

PD_IOR# (18)

PD_IOW# (18)

PD_IORDY (18)

PD_DREQ (18)

PD_DACK# (18)

IRQ14 (18)

SDD[0..15] (18)

SD_A0 (18)

SD_A1 (18)

SD_A2 (18)

SD_CS#1 (18)

SD_CS#3 (18)

SD_IOR# (18)

SD_IOW# (18)

SD_IORDY (18)

SD_DREQ (18)

SD_DACK# (18)

IRQ15 (18)

AC_SDIN0 (12)

AC_SDOUT (12)

AC_SYNC (12)

AC_BITCLK (12)

AC_RST# (12)

MSI

Title

Size Document Number Rev

Date: Sheet of

2

VCC3 VCC3

3VSB 3VSB

VCC_AGP

MICRO-STAR INt'L CO., LTD.

Intel ICH5 - PCI & IDE & AC97 Signals

MS-6726D2

R75 X_10K

AC_SDIN2

R76 X_10K

CB41

0.1u_X7R

CB43

0.1u_X7R

CB45

0.1u_X7R

CB47

0.1u_X7R

CB48

10u-0805_Y5V

CB42

0.1u_X7R

CB44

0.1u_X7R

CB46

0.1u_X7R

CB49

0.1u_X7R

CB50

0.01u_X7R

CB52

0.22u_Y5V

16V

VCC_AGPVCC_AGP

CB53

0.1u_X7R

CB55

0.1u_X7R

CB57

0.1u_X7R

CB59 0.01u_X7R

H/W Project Leader : Andy Chen

H/W Project Engineer : Prudence Wang

8 29Tuesday, November 26, 2002

1

Solder

Solder

CB54

0.1u_X7R

CB56

0.1u_X7R

CB58

0.1u_X7R

0A

Loading...

Loading...