5

4

3

2

1

D D

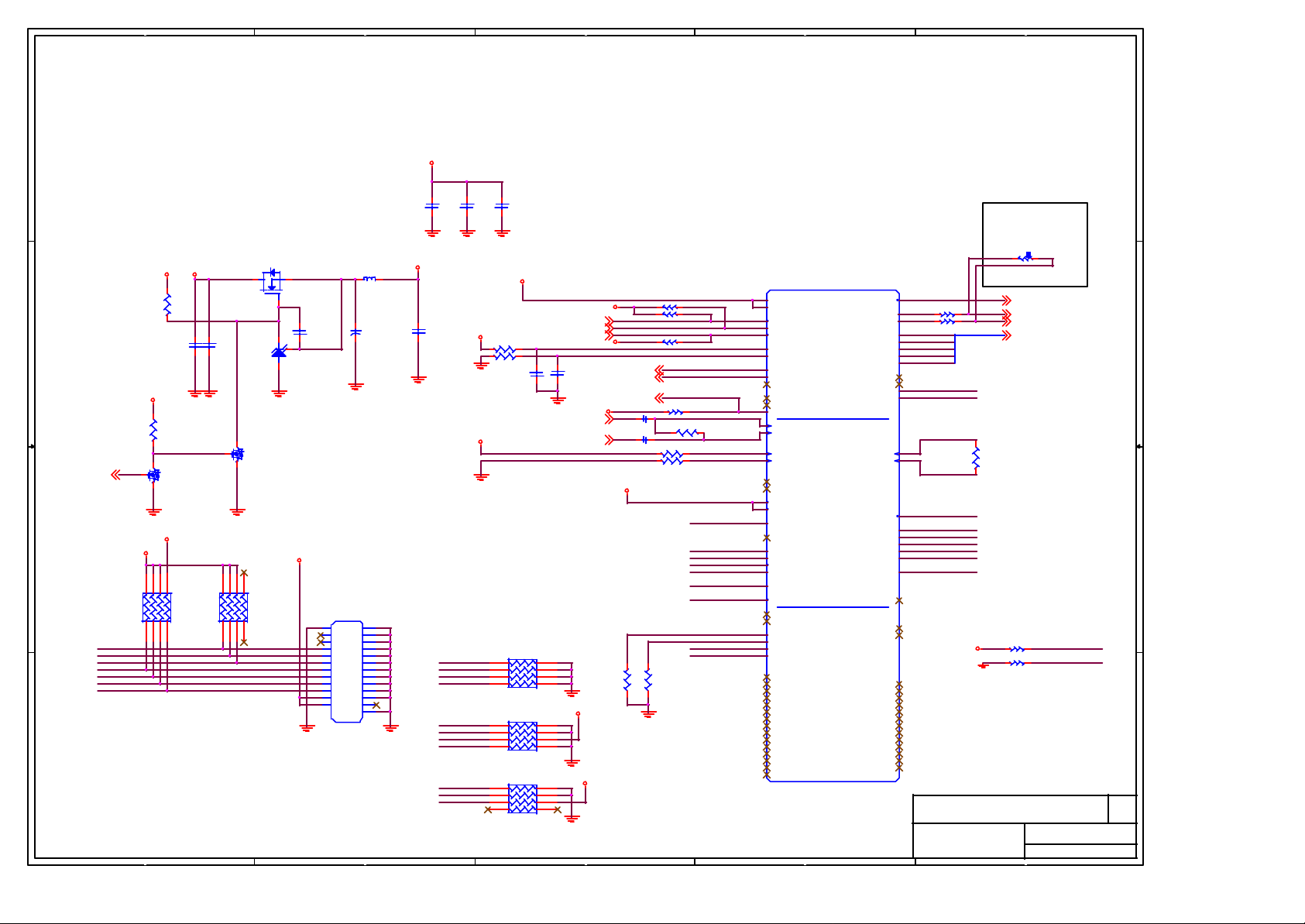

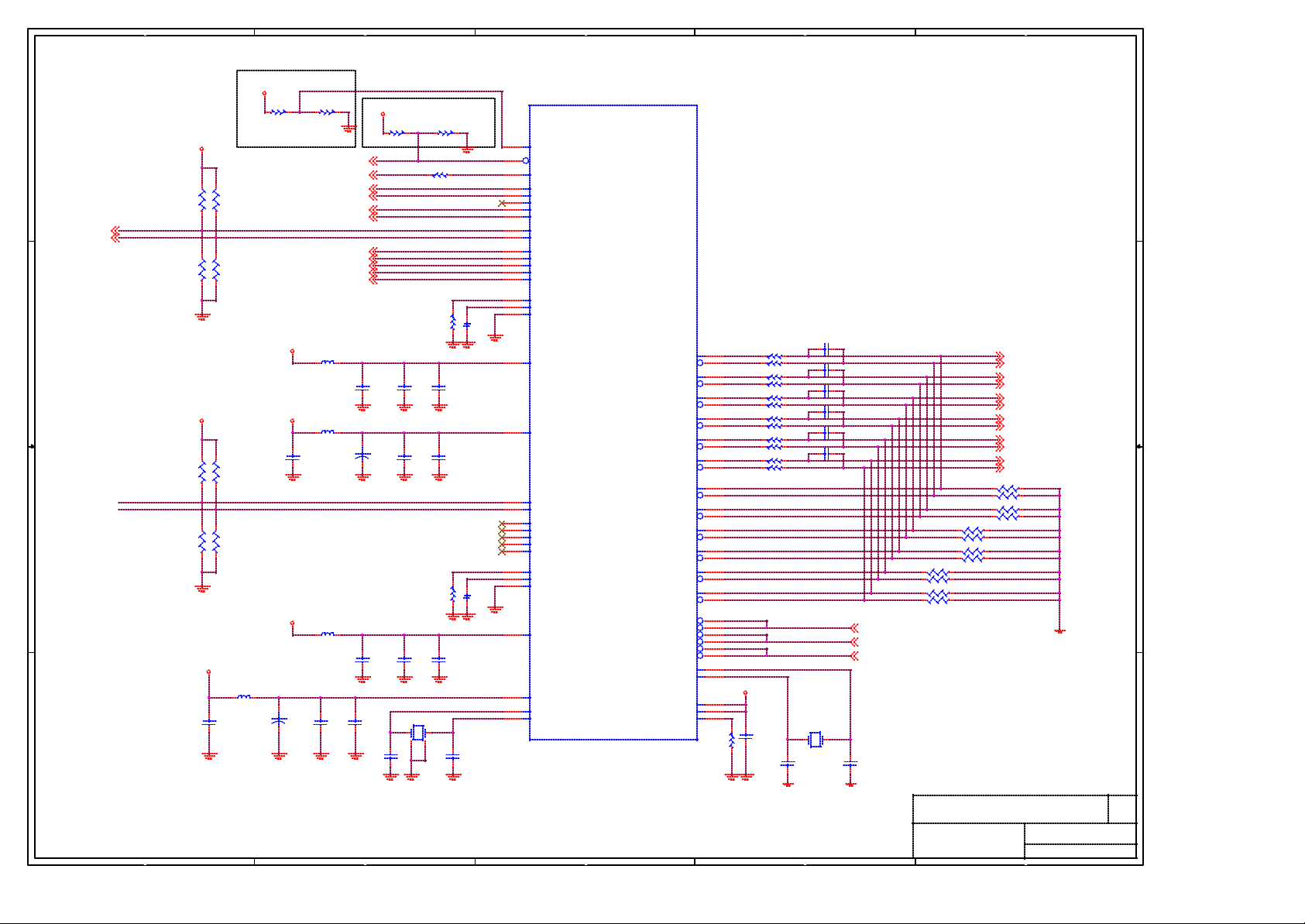

MS-6725D2 uATX

Title Page

Cover Sheet 1

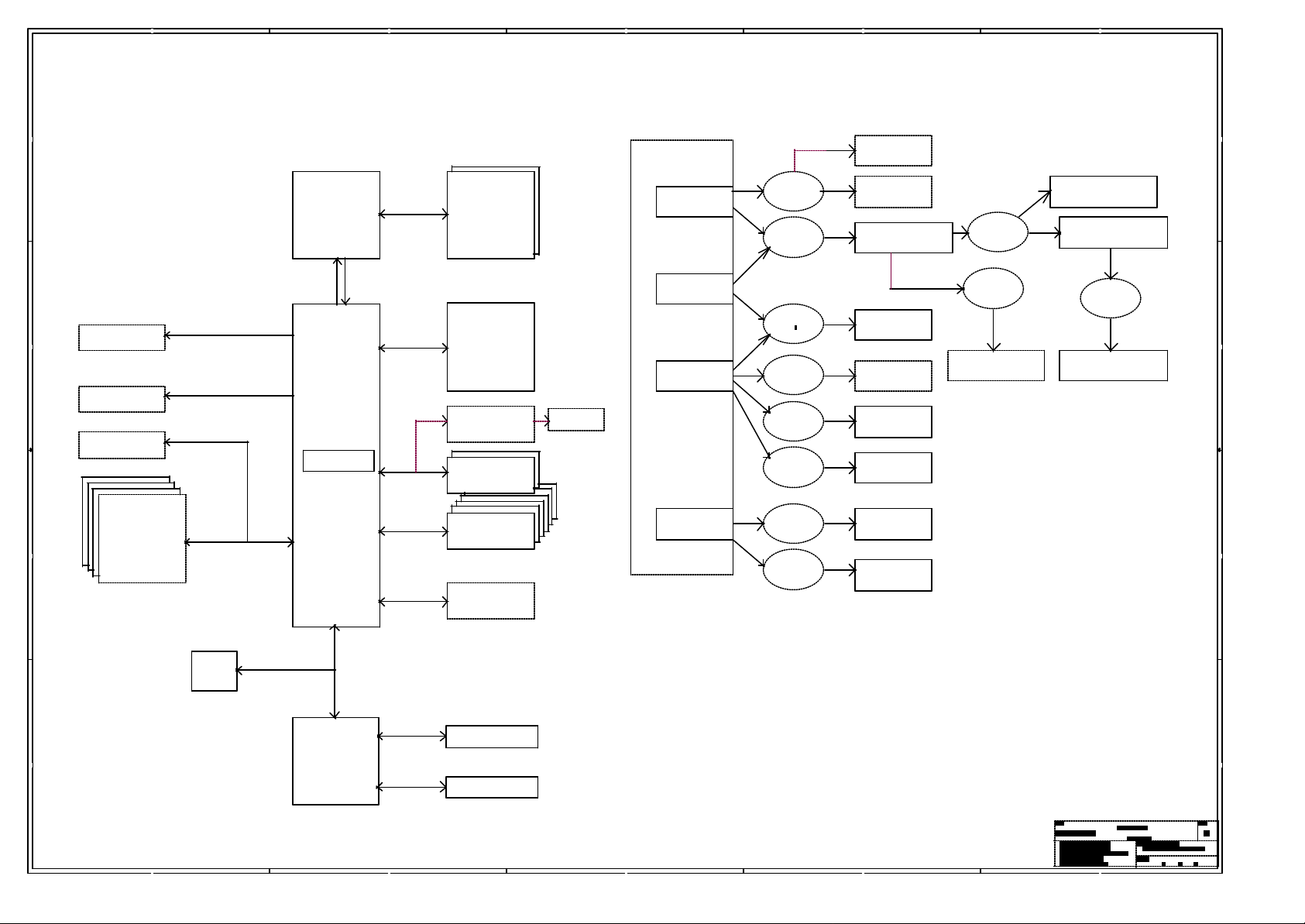

Block Diagram

AMD Clawhammer

Nvidia CK8 7,8,9,10,11

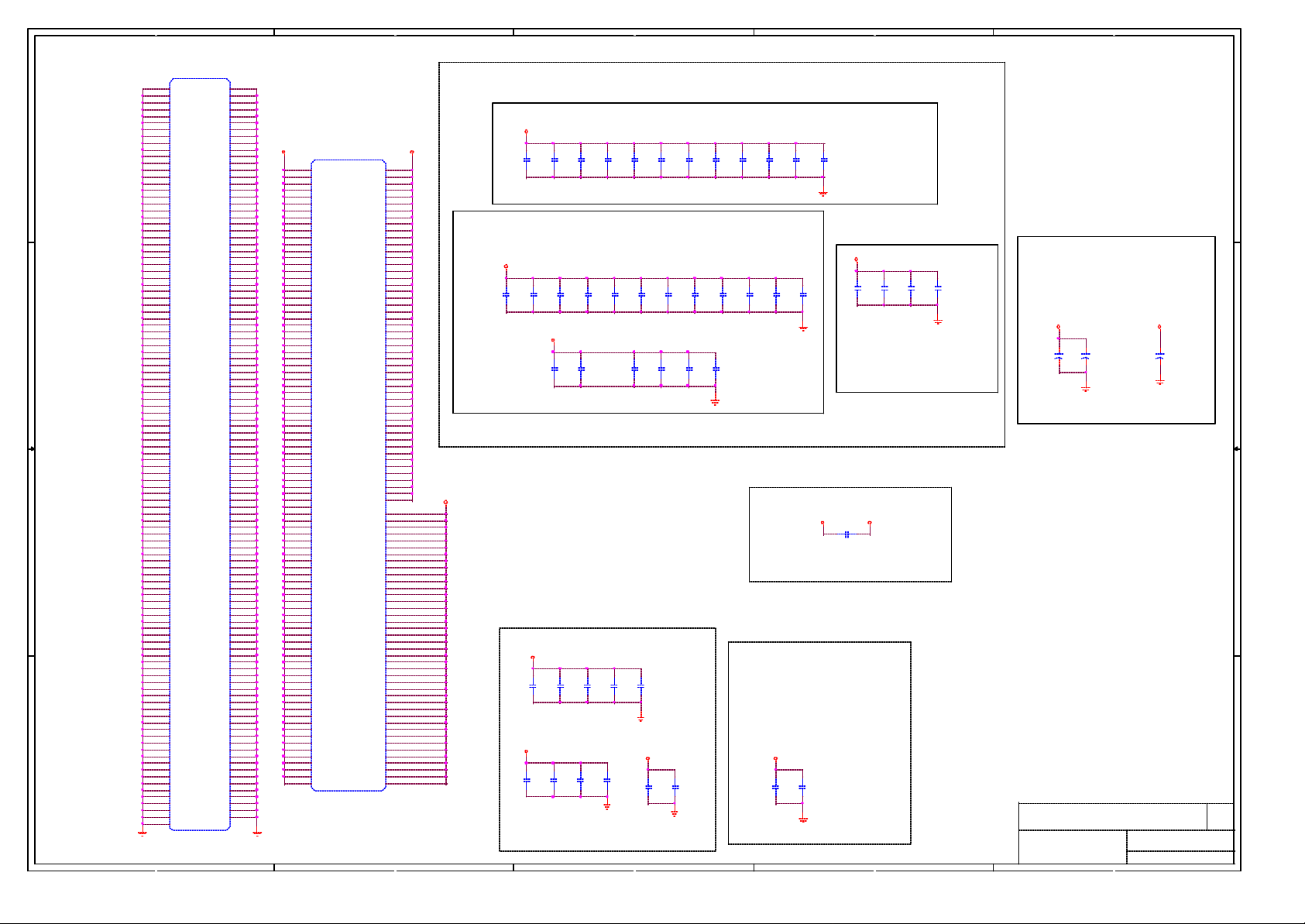

System Memory

DDR Terminations

AGP 8X SLOT 16

C C

VGA CONNECTOR

PCI Connectors

AC'97 Codec

AUDIO POR T

Gigabit LAN

USB Port

IDE Connectors

LPC I/O & H/W mornitor

System ROM & D_LED

B B

Dual Power & AGP Power

PWROK & USB PWR & ATX CONN.

Front Panel and FAN

S-ATA PHY

BULK / Decopuling / PULL-UP

K8 Core Power

ICS LAN PHY(10-100T BASE)

Menu Parts

2

3History

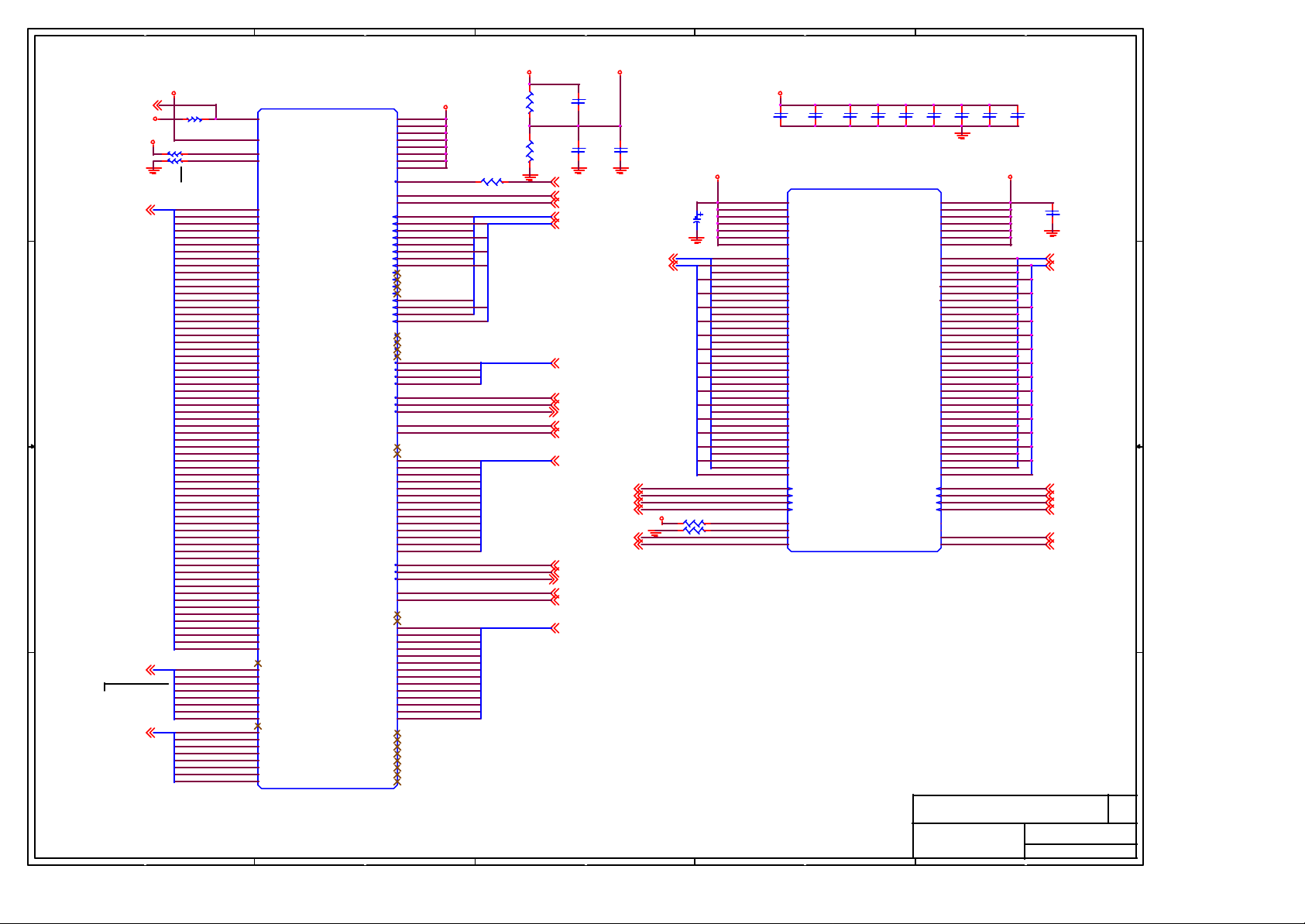

4,5,6

12,13

14,15

17

18,19

20

21

22

23

24

25

26

27I/O Connectors

28DDR Power & HT Power

29

30

31

32

33

34

35

36

A A

Micro Star Restricted Secret

5

4

3

2

1

5

D D

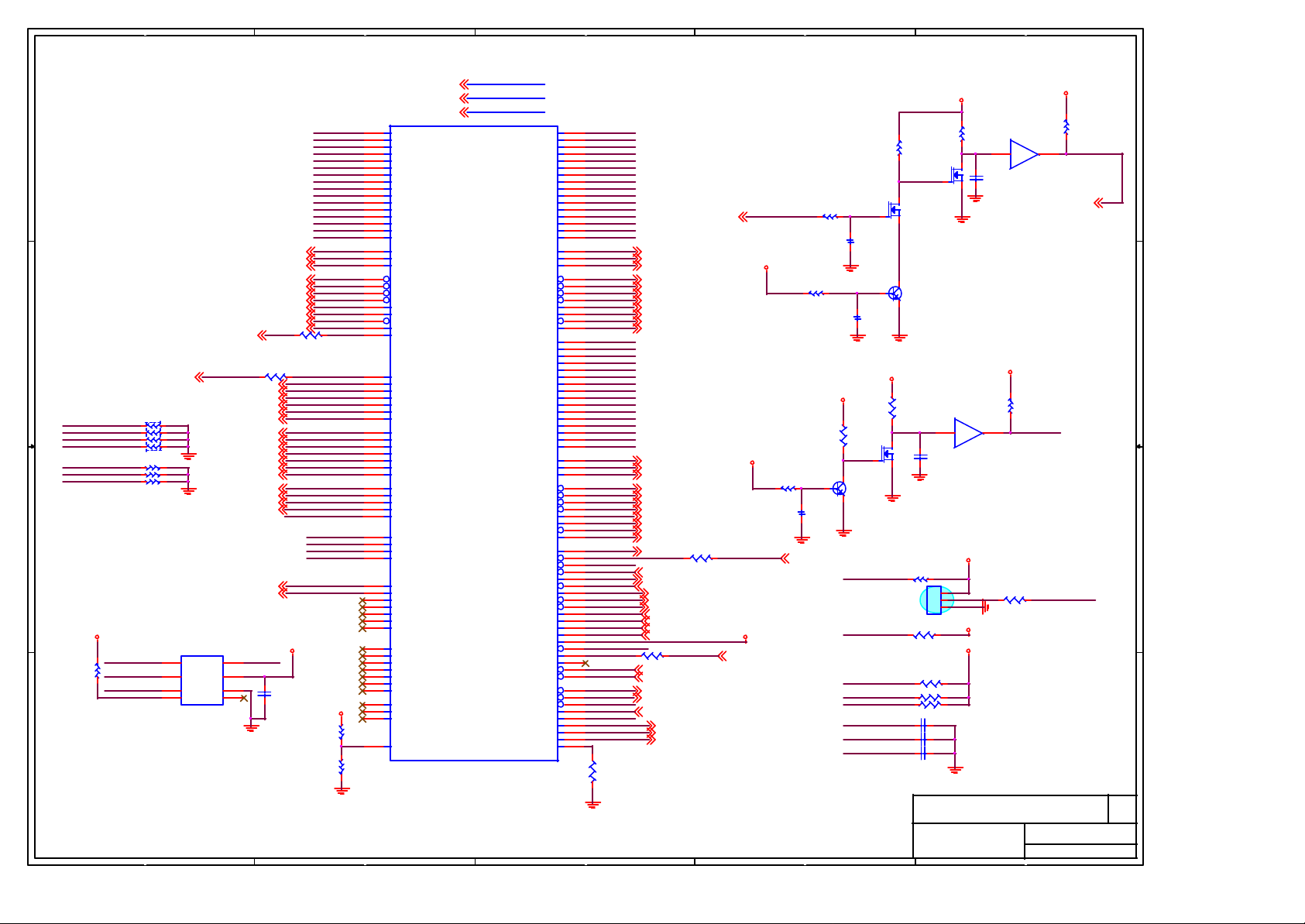

32

25

VCC

VDD

1

U24_1

VPP

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

RFU

CE

GND

GND1

21

20

19

18

17

15

14

13

22

28

16

26

27

3

4

5

6

7

8

9

2

VCCA

CLK

MODE

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

RESET_L

WE_L

OE_L

C C

31

29

30

10

11

12

23

24

B B

4

PCB

_

JBAT1(1-2)

1

2

JC-D2-GN-SB

3

COM1

COMPORT

JROM(1-2)

1

2

JC-D2-GN-SB

HS1

_

JBOOT(2-3)

1

2

JC-D2-GN-SB

2

HS2

_

VBAT1-1

1

HS3

_

A A

Title

Size Document Number Rev

5

4

3

Date: Sheet of

<Title>

<Doc> <RevCode>

A

2

1 1Tuesday, December 17, 2002

1

S-ATA X2

5

4

3

2

1

Block

Diagram

D D

ATX P.S.U

1.2V_HT

Clawhammer

Unbuffered

DDR333 SDRAM

VCC

ISL6525

MOSFET

LINK 0

16x16

IN

OUT

VCC5_SB

YLT1084

C C

B B

VGA CONNECTOR

ICS LAN

PHY(10-100T)

BCM5702(GIGABIT)

PCI Slots x4

MII_25MHZ

32b/33MHz

Nvidia

CK8(G)

Clock Generator

8X AGP Port

S-ATA PHY

EIDE (ATA/133) x2

USB 2.0 x6

USB Ports: 2 to backplane,

4 to header

AC'97 Audio

VCC3

S-ATA X2

+12V

MOSFET

EZ1117A

LM358MX

(OP + MOS)

TL431L

ISL6559

78L05

1.2V

VCC5_DUAL

VCC3_SB

VCC_18

VDD_15

VDDA_PLL

VDD_CORE

+5VR

ISL6525

LM358MX

(OP + MOS)

1.2V_DUAL

VTT_DDR_SUS

VDD_25_SUS

SWITCH

(45N02)

VDD_25

Power up:

1. VDDA_PLL after POK vaild.

LPC ROM

A A

5

LPC

LPC Super I/O

Floppy Disk Drive

Parallel & Serial Port

4

3

2. VDDA_PLL before VDD_CORE.

3. VDD_25_SUS before VDD_CORE.

4. VTT_DDR_SUS before VDD_CORE.

5. VTT_DDR_SUS before or with VDD_25_SUS.

6. VDD_CORE before 1.2V.

Power down:

1. 1.2V before VDD_CORE.

2. VDD_CORE before VDD_25_SUS.

3. VDD_25_SUS before or with VTT_DDR_SUS.

4. VDD_CORE before or with VDDA_PLL.

2

Micro Star Restricted Secret

1

5

D D

C C

4

3

2

1

B B

A A

M icro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

5

4

3

2

http://www.msi.com.tw

GPIO Spec.

MS-6725D2

Last Revision Date:

Tuesday, December 17, 2002

Sheet

1

3 35

Rev

0A

of

5

4

3

2

1

VREF_DDR_CLAWVDD_25_SUS

VREF_DDR_CLAW

VTT_SENSE28

VTT_DDR_SUS

D D

VDD_25_SUS

R556 51

R3 11.3RST

R4 11.3RST

MEMZN

MEMZP

AE13

AG12

D14

C14

VTT_SENSE

MEMVREF1

MEMZN

MEMZP

10Sep02-Jerry-For A2 CPU.

MD63

MD[63..0]15

C C

B B

MDQM[7..0]15

10Sep02-Jerry-For B0 CPU.

-MDQS[7..0]15

A A

5

MD62

MD61

MD60

MD59

MD58

MD57

MD56

MD55

MD54

MD53

MD52

MD51

MD50

MD49

MD48

MD47

MD46

MD45

MD44

MD43

MD42

MD41

MD40

MD39

MD38

MD37

MD36

MD35

MD34

MD33

MD32

MD31

MD30

MD29

MD28

MD27

MD26

MD25

MD24

MD23

MD22

MD21

MD20

MD19

MD18

MD17

MD16

MD15

MD14

MD13

MD12

MD11

MD10

MD9

MD8

MD7

MD6

MD5

MD4

MD3

MD2

MD1

MD0

MDQM7

MDQM6

MDQM5

MDQM4

MDQM3

MDQM2

MDQM1

MDQM0

-MDQS7

-MDQS6

-MDQS5

-MDQS4

-MDQS3

-MDQS2

-MDQS1

-MDQS0

C13

C11

AC1

AC3

AC2

AD1

AG3

AH3

AH9

AG5

AH5

AJ10

AH11

AJ11

AH15

AJ15

AG11

AJ12

AJ14

AJ16

AG1

AH7

AH13

AJ13

A16

B15

A12

B11

A17

A15

A11

A10

B9

C7

A6

A9

A5

B5

C5

A4

E2

E1

A3

B3

E3

F1

G2

G1

L3

L1

G3

J2

L2

M1

W1

W3

W2

Y1

AE1

AE3

AJ4

AE2

AF1

AJ3

AJ5

AJ6

AJ7

AJ9

R1

A13

A7

C2

H1

AA1

T1

A14

A8

D1

J1

AB1

AJ2

AJ8

MEMDATA63

MEMDATA62

MEMDATA61

MEMDATA60

MEMDATA59

MEMDATA58

MEMDATA57

MEMDATA56

MEMDATA55

MEMDATA54

MEMDATA53

MEMDATA52

MEMDATA51

MEMDATA50

MEMDATA49

MEMDATA48

MEMDATA47

MEMDATA46

MEMDATA45

MEMDATA44

MEMDATA43

MEMDATA42

MEMDATA41

MEMDATA40

MEMDATA39

MEMDATA38

MEMDATA37

MEMDATA36

MEMDATA35

MEMDATA34

MEMDATA33

MEMDATA32

MEMDATA31

MEMDATA30

MEMDATA29

MEMDATA28

MEMDATA27

MEMDATA26

MEMDATA25

MEMDATA24

MEMDATA23

MEMDATA22

MEMDATA21

MEMDATA20

MEMDATA19

MEMDATA18

MEMDATA17

MEMDATA16

MEMDATA15

MEMDATA14

MEMDATA13

MEMDATA12

MEMDATA11

MEMDATA10

MEMDATA9

MEMDATA8

MEMDATA7

MEMDATA6

MEMDATA5

MEMDATA4

MEMDATA3

MEMDATA2

MEMDATA1

MEMDATA0

MEMDQS17

MEMDQS16

MEMDQS15

MEMDQS14

MEMDQS13

MEMDQS12

MEMDQS11

MEMDQS10

MEMDQS9

MEMDQS8

MEMDQS7

MEMDQS6

MEMDQS5

MEMDQS4

MEMDQS3

MEMDQS2

MEMDQS1

MEMDQS0

U1B

RSVD_MEMADDA15

RSVD_MEMADDA14

RSVD_MEMADDB15

RSVD_MEMADDB14

MEMORY INTERFACE

VTT_A4

VTT_A1

VTT_A2

VTT_A3

VTT_B1

VTT_B2

VTT_B3

VTT_B4

MEMRESET_L

MEMCKEA

MEMCKEB

MEMCLK_H7

MEMCLK_L7

MEMCLK_H6

MEMCLK_L6

MEMCLK_H5

MEMCLK_L5

MEMCLK_H4

MEMCLK_L4

MEMCLK_H3

MEMCLK_L3

MEMCLK_H2

MEMCLK_L2

MEMCLK_H1

MEMCLK_L1

MEMCLK_H0

MEMCLK_L0

MEMCS_L7

MEMCS_L6

MEMCS_L5

MEMCS_L4

MEMCS_L3

MEMCS_L2

MEMCS_L1

MEMCS_L0

MEMRASA_L

MEMCASA_L

MEMWEA_L

MEMBANKA1

MEMBANKA0

MEMADDA13

MEMADDA12

MEMADDA11

MEMADDA10

MEMADDA9

MEMADDA8

MEMADDA7

MEMADDA6

MEMADDA5

MEMADDA4

MEMADDA3

MEMADDA2

MEMADDA1

MEMADDA0

MEMRASB_L

MEMCASB_L

MEMWEB_L

MEMBANKB1

MEMBANKB0

MEMADDB13

MEMADDB12

MEMADDB11

MEMADDB10

MEMADDB9

MEMADDB8

MEMADDB7

MEMADDB6

MEMADDB5

MEMADDB4

MEMADDB3

MEMADDB2

MEMADDB1

MEMADDB0

MEMCHECK7

MEMCHECK6

MEMCHECK5

MEMCHECK4

MEMCHECK3

MEMCHECK2

MEMCHECK1

MEMCHECK0

4

D17

A18

B17

C17

AF16

AG16

AH16

AJ17

AG10

AE8

AE7

D10

C10

E12

E11

AF8

AG8

AF10

AE10

V3

V4

K5

K4

R5

P5

P3

P4

D8

C8

E8

E7

D6

E6

C4

E5

H5

D4

G5

K3

H3

E13

C12

E10

AE6

AF3

M5

AE5

AB5

AD3

Y5

AB4

Y3

V5

T5

T3

N5

H4

F5

F4

L5

J5

E14

D12

E9

AF6

AF4

M4

AD5

AC5

AD4

AA5

AB3

Y4

W5

U5

T4

M3

N3

N1

U3

V1

N2

P1

U1

U2

VTT_DDR_SUS

MEMRESET

MEMCLK_H7

MEMCLK_L7

MEMCLK_H6

MEMCLK_L6

MEMCLK_H5

MEMCLK_L5

MEMCLK_H4

MEMCLK_L4

MEMCLK_H1

MEMCLK_L1

MEMCLK_H0

MEMCLK_L0

-MCS3

-MCS2

-MCS1

-MCS0

MAA13

MAA12

MAA11

MAA10

MAA9

MAA8

MAA7

MAA6

MAA5

MAA4

MAA3

MAA2

MAA1

MAA0

MAB13

MAB12

MAB11

MAB10

MAB9

MAB8

MAB7

MAB6

MAB5

MAB4

MAB3

MAB2

MAB1

MAB0

MCKE0

MCKE1

-MSRASA

-MSCASA

NON-POP

R5 X_0

-MCS[3..0]

R1

100RST

R2

100RST

MEMRESET_L 12,13

MCKE0 12,13,14

MCKE1 12,13,14

MEMCLK_H[7..0] 12,13,14

MEMCLK_L[7..0] 12,13,14

-MCS[3..0] 12,13,14

-MSRASA 12,14

-MSCASA 12,14

-MSWEA 12,14

MEMBANKA1 12,14

MEMBANKA0 12,14

MAA[13..0] 12,14

-MSRASB 13,14

-MSCASB 13,14

-MSWEB 13,14

MEMBAKB1 13,14

MEMBAKB0 13,14

MAB[13..0] 13,14

C1

104P

C2

C746

104P

1000P

1.2V_HT

C1372

X_100u/10V

R6 49.9RST

R7 49.9RST

L0_CADIN_H15

L0_CADIN_L15

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_L2

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H0

L0_CADIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

L0_CADIN_H[0..15]7

L0_CADIN_L[0..15]7 L0_CADOUT_L[0..15] 7

L0_CLKIN_H17

L0_CLKIN_L17

L0_CLKIN_H07

L0_CLKIN_L07

L0_CTLIN_H07

L0_CTLIN_L07

3

VLDT0

1.2V_HT

D29

D27

D25

C28

C26

B29

B27

T25

R25

U27

U26

V25

U25

W27

W26

AA27

AA26

AB25

AA25

AC27

AC26

AD25

AC25

T27

T28

V29

U29

V27

V28

Y29

W29

AB29

AA29

AB27

AB28

AD29

AC29

AD27

AD28

Y25

W25

Y27

Y28

R27

R26

T29

R29

C811

C810

0.22u

0.22u

VLDT0_A6

VLDT0_A5

VLDT0_A4

VLDT0_A3

VLDT0_A2

VLDT0_A1

VLDT0_A0

L0_CADIN_H15

L0_CADIN_L15

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H0

L0_CADIN_L0

L0_CLKIN_H1

L0_CLKIN_L1

L0_CLKIN_H0

L0_CLKIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

HYPER TRANSPORT - LINK0

2

U1A

C812

0.22u

C814

C813

0.22u

0.22u

VLDT0_B6

VLDT0_B5

VLDT0_B4

VLDT0_B3

VLDT0_B2

VLDT0_B1

VLDT0_B0

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

Title

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

C815

0.22u

C816

0.22u

C817

0.22u

C818

0.22u

VLDT0

AH29

AH27

AG28

AG26

AF29

AE28

AF25

L0_CADOUT_H15

N26

L0_CADOUT_L15

N27

L0_CADOUT_H14

L25

L0_CADOUT_L14

M25

L0_CADOUT_H13

L26

L0_CADOUT_L13

L27

L0_CADOUT_H12

J25

L0_CADOUT_L12

K25

L0_CADOUT_H11

G25

L0_CADOUT_L11

H25

L0_CADOUT_H10

G26

L0_CADOUT_L10

G27

L0_CADOUT_H9

E25

L0_CADOUT_L9

F25

L0_CADOUT_H8

E26

L0_CADOUT_L8

E27

L0_CADOUT_H7

N29

L0_CADOUT_L7

P29

L0_CADOUT_H6

M28

L0_CADOUT_L6

M27

L0_CADOUT_H5

L29

L0_CADOUT_L5

M29

L0_CADOUT_H4

K28

L0_CADOUT_L4

K27

L0_CADOUT_H3

H28

L0_CADOUT_L3

H27

L0_CADOUT_H2L0_CADIN_H2

G29

L0_CADOUT_L2

H29

L0_CADOUT_H1

F28

L0_CADOUT_L1

F27

L0_CADOUT_H0

E29

L0_CADOUT_L0

F29

J26

J27

J29

K29

N25

P25

L0_CTLOUT_H0

P28

L0_CTLOUT_L0

P27

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

C747

4.7u/1206

L0_CADOUT_H[0..15] 7

L0_CLKOUT_H1 7

L0_CLKOUT_L1 7

L0_CLKOUT_H0 7

L0_CLKOUT_L0 7

L0_CTLOUT_H0 7

L0_CTLOUT_L0 7

M icro Star Restricted Secret

K8 DDR & HT

MS-6725D2

Last Revision Date:

Tuesday, December 17, 2002

Sheet

4 35

1

Rev

0A

of

5

4

3

2

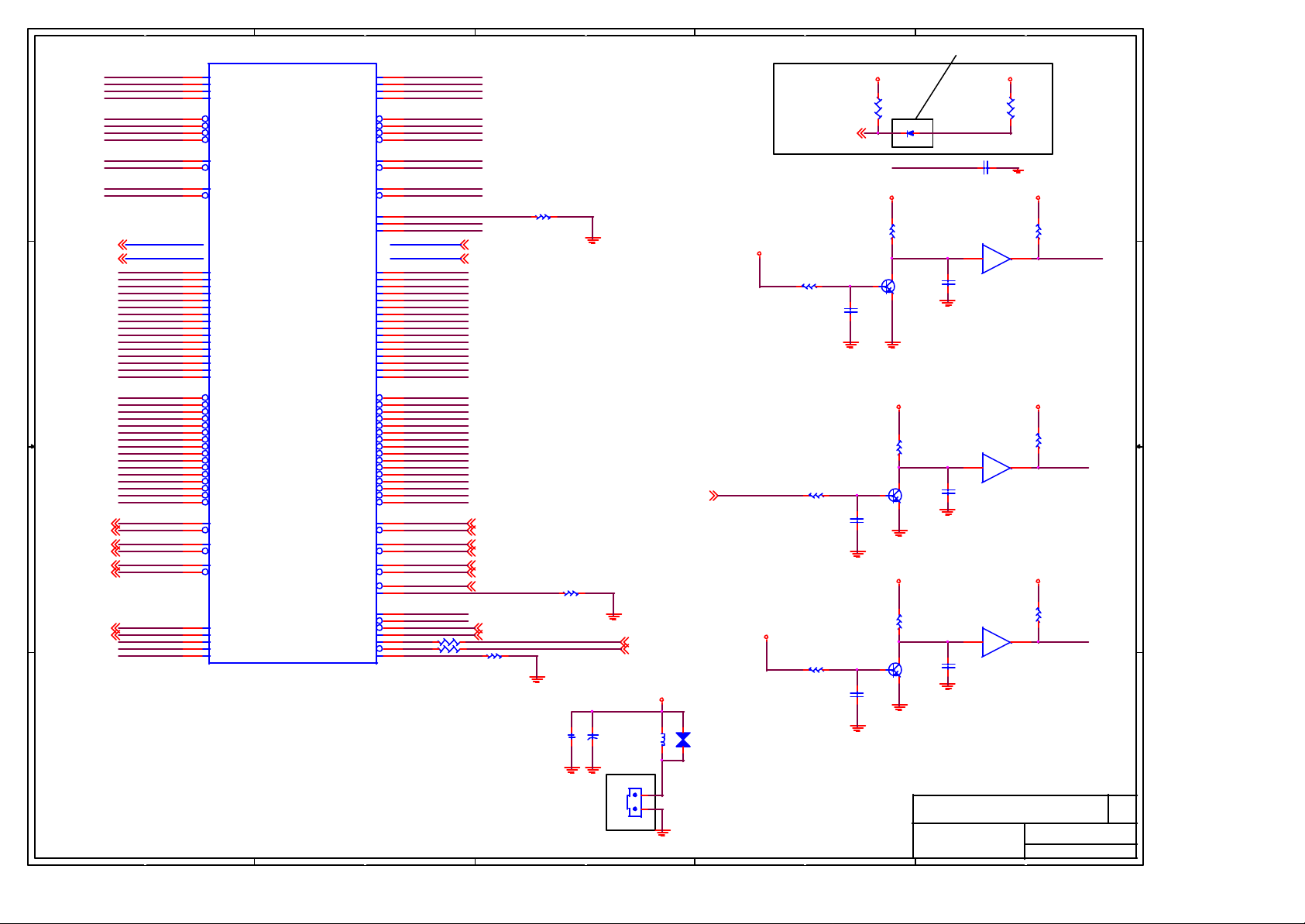

VCCA_PLL trace length from the VR1 to the

PGA must be 0.75".

1

Place al filters close to the PGA.

Keep all power and signal trce away from

D D

VCCA_PLL

C5

C4

39P

3300p

C6

0.22u

the VR1.

Inside CPU socket

Q1

VCCA_CTRL

C10

39P

123456

78

NDS351AN-S-SOT23

D

S

G

2

YREG431LS

3 1

VDD_25

RN121

8P4R-1K

VCCA_PL

VR1

C7

1000P

1

3

5

7

9

11

13

15

17

19

21

23

X_ASP-68200-07

FB33

+

VCCA_REF

JHDT

KEY

+12V

VCC3

R9

1K

C C

VDD_PWGD_230,34

YFET-NDS7002AS

B B

DBREQ_L

DBRDY

TCK

TMS

TDI

TRST_L

TDO

A A

VCC5_SB

Q91

VDD_25_SUS

VDD_25

123456

5

C9

4.7u/0805

R747

1K

PLL_CTRL

Q90

YFET-NDS7002AS

HDT Connectors

78

RN120

8P4R-1K

180nH/1210

C748

100u-16V

4

VCCA_PLL

C8

4.7u/0805

VDD_25_SUS

2

4

6

8

10

12

14

16

18

20

22

24

26

NC_AJ18

NC_AG17

NC_AF21

NC_AF22

NC_C19

NC_D20

NC_C18

NC_D18

NC_C21

NC_B19

NC_A19

VLDT0

R11 44.2RST

R12 44.2RST

VCCA_PLL

C11

1000P

RN122

X_8P4R-1K

RN123

8P4R-680

RN124

8P4R-680

LAYOUT: Route VDDA trace approx.

50 mils wide (use 2x25 mil traces to

exit ball field) and 500 mils long.

R1401 330

R1402 330

R1403 330

COREFB34

COREFB_L34

VDDIO_SENSE28

C13 3900P

C14 3900P

VTT_DDR_SUS

R26

X_1K

R557 51

R13 169RST

R14 680

R16 680

R27

X_1K

CPU_POWERGOOD7

12

34

56

78

12

34

56

78

12

34

56

78

RESET_CPU_L7

HTSTOP_L7

C12

1000P

VDD_25_SUS

CPUCLK0_H7

CPUCLK0_L7

VDD_25

VDD_25

3

VDD_25

VDD_25

L0_REF1

L0_REF0

COREFB

COREFB_L

VDDIO_SENSE

CLKIN_H

CLKIN_L

NC_AJ23

NC_AH23

DBRDY

TMS

TCK

TRST_L

TDI

NC_C18

NC_A19

NC_AE23

NC_AF23

NC_AF22

NC_AF21

AH25

AJ25

AF20

AE18

AJ27

AF27

AE26

AE12

AF12

AE11

AJ21

AH21

AJ23

AH23

AE24

AF24

C16

AG15

AH17

C15

C18

AJ28

AE23

AF23

AF22

AF21

AG2

AH1

AE21

C20

AG4

AG6

AG9

A23

A24

B23

E20

E17

B21

A21

A19

A28

C1

J3

R3

AA2

D3

B18

C6

AE9

VDDA1

VDDA2

RESET_L

PWROK

LDTSTOP_L

L0_REF1

L0_REF0

COREFB_H

COREFB_L

CORE_SENSE

VDDIOFB_H

VDDIOFB_L

VDDIO_SENSE

CLKIN_H

CLKIN_L

NC_AJ23

NC_AH23

NC_AE24

NC_AF24

VTT_A5

VTT_B5

DBRDY

NC_C15

TMS

TCK

TRST_L

TDI

NC_C18

NC_A19

KEY1

KEY0

NC_AE23

NC_AF23

NC_AF22

NC_AF21

FREE29

FREE31

FREE33

FREE35

FREE1

FREE37

FREE4

FREE38

FREE41

FREE7

FREE11

FREE12

FREE13

FREE14

FREE40

U1C

THERMTRIP_L

G_FBCLKOUT_H

G_FBCLKOUT_L

2

THERMDA

THERMDC

VID4

VID3

VID2

VID1

VID0

NC_AG18

NC_AH18

NC_AG17

NC_AJ18

DBREQ_L

NC_D20

NC_C21

NC_D18

NC_C19

NC_B19

TDO

NC_AF18

RSVD_SCL

RSVD_SDA

FREE26

FREE28

FREE30

FREE32

FREE34

FREE36

FREE10

FREE18

FREE19

FREE42

FREE24

FREE25

FREE27

A20

R1429 0

A26

R1430 0

A27

VID4

AG13

VID3

AF14

VID2

AG14

VID1

AF15

VID0

AE15

AG18

AH18

NC_AG17

AG17

NC_AJ18

AJ18

FBCLKOUT_H

AH19

AJ19

FBCLKOUT_L

DBREQ_L

AE19

NC_D20

D20

NC_C21

C21

NC_D18

D18

NC_C19

C19

NC_B19

B19

TDO

A22

AF18

D22

C22

VDD_CORE

B13

B7

C3

K1

R2

AA3

F3

C23

AG7

AE22

C24

A25

C9

M icro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

RT1 X_10K_3%

THERMTRIP_CPU_L 7

THERMDA_CPU 25

THERMDC_CPU 25

VID[4..0] 25,34

LAYOUT: Route FBC LKOUT_H/L

differentially with 20/8/5/8/20

spacing and trace width.

R15

80.6RST

R533 51

R534 51

K8 HDT & MISC

COREFB

COREFB_L

MS-6725D2

Last Revision Date:

Tuesday, December 17, 2002

Sheet

5 35

1

Rev

of

0A

5

U1E

B2

VSS1

AH20

VSS3

AB21

VSS4

W22

VSS5

M23

VSS6

L24

VSS7

AG25

VSS8

AG27

VSS9

AA10

AE16

G20

R20

U20

W20

AA20

AC20

AE20

AG20

AJ20

D21

H21

M21

AD21

AG21

G22

N22

R22

U22

AG29

AA22

AC22

AG22

AH22

AJ22

D23

H23

AB23

AD23

AG23

G24

N24

R24

U24

W24

AA24

AC24

AG24

AJ24

C25

D26

H26

M26

AD26

AF26

AH26

C27

D28

G28

H15

AB17

AD17

G18

AA18

AC18

D19

H19

AB19

AD19

AF19

N20

D2

VSS10

AF2

VSS11

W6

VSS12

Y7

VSS13

AA8

VSS14

AB9

VSS15

VSS16

J12

VSS17

B14

VSS18

Y15

VSS19

VSS20

J18

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

F21

VSS32

VSS33

K21

VSS34

VSS35

P21

VSS36

T21

VSS37

V21

VSS38

Y21

VSS39

VSS40

VSS41

B22

VSS42

E22

VSS43

VSS44

J22

VSS45

L22

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

F23

VSS57

VSS58

K23

VSS59

P23

VSS60

T23

VSS61

V23

VSS62

Y23

VSS63

VSS64

VSS65

VSS66

E24

VSS67

VSS68

J24

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

B25

VSS78

VSS79

B26

VSS80

VSS81

VSS82

VSS83

T26

VSS84

Y26

VSS85

VSS86

VSS87

VSS88

VSS89

B28

VSS90

VSS91

VSS92

F15

VSS187

VSS188

VSS206

VSS207

B16

VSS208

VSS209

VSS210

VSS211

VSS212

F19

VSS213

VSS214

K19

VSS215

Y19

VSS216

VSS217

VSS218

VSS219

J20

VSS220

L20

VSS221

VSS222

GROUND

5

D D

C C

B B

A A

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS189

VSS190

VSS191

VSS192

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS223

VSS201

VSS202

VSS203

VSS204

VSS205

L28

R28

W28

AC28

AF28

AH28

C29

F2

H2

K2

M2

P2

T2

V2

Y2

AB2

AD2

AH2

B4

AH4

B6

G6

J6

L6

N6

R6

U6

AA6

AC6

AH6

F7

H7

K7

M7

P7

T7

V7

AB7

AD7

B8

G8

J8

L8

N8

R8

U8

W8

AC8

AH8

F9

H9

K9

M9

P9

T9

V9

Y9

AD9

B10

G10

J10

L10

N10

R10

U10

W10

AC10

AH10

F11

H11

K11

Y11

AB11

AD11

B12

G12

AA12

AC12

AH12

F13

H13

K13

Y13

AB13

AD13

AF17

G14

J14

AA14

AC14

AE14

D16

E15

K15

AB15

AD15

AH14

E16

G16

J16

AA16

AC16

AE29

AJ26

E18

F17

H17

K17

Y17

GNDGND

VDD_CORE

AC15

AB14

AA15

AB16

AA17

AC17

AE17

AB18

AD18

AG19

AC19

AA19

AB20

AD20

AA21

AC21

AB22

AD22

AA23

AC23

AB24

AD24

AH24

AE25

H18

H22

H24

G13

G15

H16

G17

G19

H20

M20

G21

N21

R21

U21

W21

M22

G23

N23

R23

U23

W23

D24

M24

U1D

L7

VDD1

VDD2

VDD3

B20

VDD4

E21

VDD5

VDD6

J23

VDD7

VDD8

F26

VDD9

N7

VDD10

L9

VDD11

V10

VDD12

VDD13

K14

VDD14

Y14

VDD15

VDD16

VDD17

J15

VDD18

VDD19

VDD20

K16

VDD21

Y16

VDD22

VDD23

VDD24

J17

VDD25

VDD26

VDD27

VDD28

F18

VDD29

K18

VDD30

Y18

VDD31

VDD32

VDD33

VDD34

E19

VDD35

VDD36

VDD39

VDD38

J19

VDD37

F20

VDD40

VDD41

K20

VDD42

VDD43

P20

VDD44

T20

VDD45

V20

VDD46

Y20

VDD47

VDD48

VDD49

VDD50

J21

VDD51

L21

VDD52

VDD53

VDD54

VDD55

VDD56

VDD57

VDD58

F22

VDD59

K22

VDD60

VDD61

P22

VDD62

T22

VDD63

V22

VDD64

Y22

VDD65

VDD66

VDD67

E23

VDD68

VDD69

L23

VDD70

VDD71

VDD72

VDD73

VDD74

VDD75

VDD76

B24

VDD77

VDD78

F24

VDD79

K24

VDD80

VDD81

P24

VDD82

T24

VDD83

V24

VDD84

Y24

VDD85

VDD86

VDD87

VDD88

VDD89

K26

VDD90

P26

VDD91

V26

VDD92

POWER

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VDDIO22

VDDIO23

VDDIO24

VDDIO25

VDDIO26

VDDIO27

VDDIO28

VDDIO29

VDDIO30

VDDIO31

VDDIO32

VDDIO33

VDDIO34

VDDIO35

VDDIO36

VDDIO37

VDDIO38

VDDIO39

VDDIO40

VDDIO41

VDDIO42

VDDIO43

VDDIO44

VDDIO45

VDDIO46

VDDIO47

VDDIO48

VDDIO49

VDDIO50

VDDIO6

VDD96

VDD97

VDD98

VDD99

VDD100

VDD101

VDD102

VDD103

VDD104

VDD105

VDD106

VDD107

VDD108

VDD109

VDD110

VDD111

VDD112

VDD113

VDD114

VDD115

VDD116

VDD117

VDD118

VDD119

VDD120

VDD121

VDD122

VDD123

VDD124

VDD125

VDD126

VDD127

VDD128

VDD129

VDD130

VDD131

VDD132

VDD133

VDD93

VDD94

VDD95

4

VDD_25_SUS

E4

G4

J4

L4

N4

U4

W4

AA4

AC4

AE4

D5

AF5

F6

H6

K6

M6

P6

T6

V6

Y6

AB6

AD6

D7

G7

J7

AA7

AC7

AF7

F8

H8

AB8

AD8

D9

G9

AC9

AF9

F10

AD10

D11

AF11

F12

AD12

D13

AF13

F14

AD14

F16

AD16

D15

R4

N28

U28

AA28

AE27

R7

U7

W7

K8

M8

P8

T8

V8

Y8

J9

N9

R9

U9

W9

AA9

H10

K10

M10

P10

T10

Y10

AB10

G11

J11

AA11

AC11

H12

K12

Y12

AB12

J13

AA13

AC13

H14

AB26

E28

J28

4

LAYOUT: Plac e 6 EMI capsalong bottom right side of Clawhammer, 2 in middle

of HT link, and 12 along

X_6.8pF/BOT

VDD_CORE

VDD_CORE

C24

C23

C22

6.8pF

6.8pF

bottom left side of Claw-

VDD_CORE

C44

VDD_25_SUS

C47

C46

X_6.8pF/BOT

X_6.8pF/BOT

VDD_CORE

C68

C67

<nopop>

X_6.8pF

LAYOUT: Place beside processor.

VDD_25_SUS

C39

C38

0.22u

0.22u

C62

C61

4.7u/0805

C63

4.7u/0805

6.8pF

C48

X_6.8pF/BOT

<nopop>

X_6.8pF/BOT

C40

0.22u

4.7u/0805

C25

C64

GND

6.8pF

C49

C41

4.7u/0805

3

C26

6.8pF

C50

X_6.8pF/BOT

X_6.8pF/BOT

C70

<nopop>

X_6.8pF/BOT

C43

0.22u

0.22u

GND

VDD_25_SUS

C96

3

C27

C51

C71

0.22uF

C28

6.8pF

hammer.

C52

X_6.8pF/BOT

C72

<nopop>

X_6.8pF/BOT

C97

0.22uF

GND

EMI

LAYOUT: Place 1 capacitor every 1-1.5"

along VDD_CORE perimiter.

C29

6.8pF

C53

X_6.8pF/BOT

C73

<nopop>

X_6.8pF/BOT

GND

C33

C30

6.8pF

C54

6.8pF

C55

X_6.8pF/BOT

X_6.8pF/BOT

6.8pF

X_6.8pF/BOT

<nopop>

X_6.8pF/BOT

LAYOUT: Place on backside of processor.

LAYOUT: Place beside DDR slots.

VDD_25_SUS

C65

4.7u/0805

C34

C37

6.8pF

6.8pF

GND

VDD_CORE

C56

GND

C74

X_6.8pF/BOT

LAYOUT: Place 1000pF capacitors

between VR M & CPU.

VDD_25_SUS VTT_DDR_SUS

C132

X_0.22uF

<nopop>

C66

4.7u/0805

GND

2

1000P

2

1

NOTE: Populat e 270uF

caps or 100uF caps

C77

C76

C75

1000P

1000P

1000P

GND

in these footprints.

VDD_25_SUS

+

+

EC26

100u-16V

Title

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

EC27

100u-16V

GND

Micro Star Restricted Secret

K8 POWER & GND

VDD_25_SUS

+

EC28

100u-16V

GND

MS-6725D2

Last Revision Date:

Tuesday, December 17, 2002

Sheet

1

6 35

Rev

0A

of

5

TP_HT2_DWN0

TP_HT2_DWN1

TP_HT2_DWN2

TP_HT2_DWN3

TP_HT2_DWN*0

TP_HT2_DWN*1

TP_HT2_DWN*2

L0_CLKIN_H04

L0_CLKIN_L04

L0_CLKIN_H14

L0_CLKIN_L14

L0_CTLIN_H04

L0_CTLIN_L04

TP_HT2_DWN*3

TP_HT2_DWNCLK

-TP_HT2_DWNCLK

TP_HT2_DWNCNTL

-TP_HT2_DWNCNTL

L0_CADIN_H[0..15]

L0_CADIN_L[0..15]

L0_CADIN_H0

L0_CADIN_H1

L0_CADIN_H2

L0_CADIN_H3

L0_CADIN_H4

L0_CADIN_H5

L0_CADIN_H6

L0_CADIN_H7

L0_CADIN_H8

L0_CADIN_H9

L0_CADIN_H10

L0_CADIN_H11

L0_CADIN_H12

L0_CADIN_H13

L0_CADIN_H14

L0_CADIN_H15

L0_CADIN_L0

L0_CADIN_L1

L0_CADIN_L2

L0_CADIN_L3

L0_CADIN_L4

L0_CADIN_L5

L0_CADIN_L6

L0_CADIN_L7

L0_CADIN_L8

L0_CADIN_L9

L0_CADIN_L10

L0_CADIN_L11

L0_CADIN_L12

L0_CADIN_L13

L0_CADIN_L14

L0_CADIN_L15

L0_CLKIN_H0

L0_CLKIN_L0

L0_CLKIN_H1

L0_CLKIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

VDD_CORE_EN

HT1VDD_EN

-HT1_VLD

-MEM_VLD

-CPU_VLD

5

D D

L0_CADIN_H[0..15]4

L0_CADIN_L[0..15]4

C C

B B

VDD_CORE_EN34

HT1VDD_EN28

A A

AN29

AM28

AN27

AN26

AP29

AN28

AP27

AP26

AM25

AN25

AP30

AN30

AP18

AP17

AN16

AP15

AN13

AP12

AP11

AN10

AL18

AJ16

AJ15

AL15

AJ13

AL12

AJ12

AJ10

AN18

AN17

AM16

AN15

AM13

AN12

AN11

AM10

AM18

AK16

AK15

AM15

AK13

AM12

AK12

AJ11

AP14

AN14

AJ14

AK14

AN9

AP9

A2

C2

B1

B4

B2

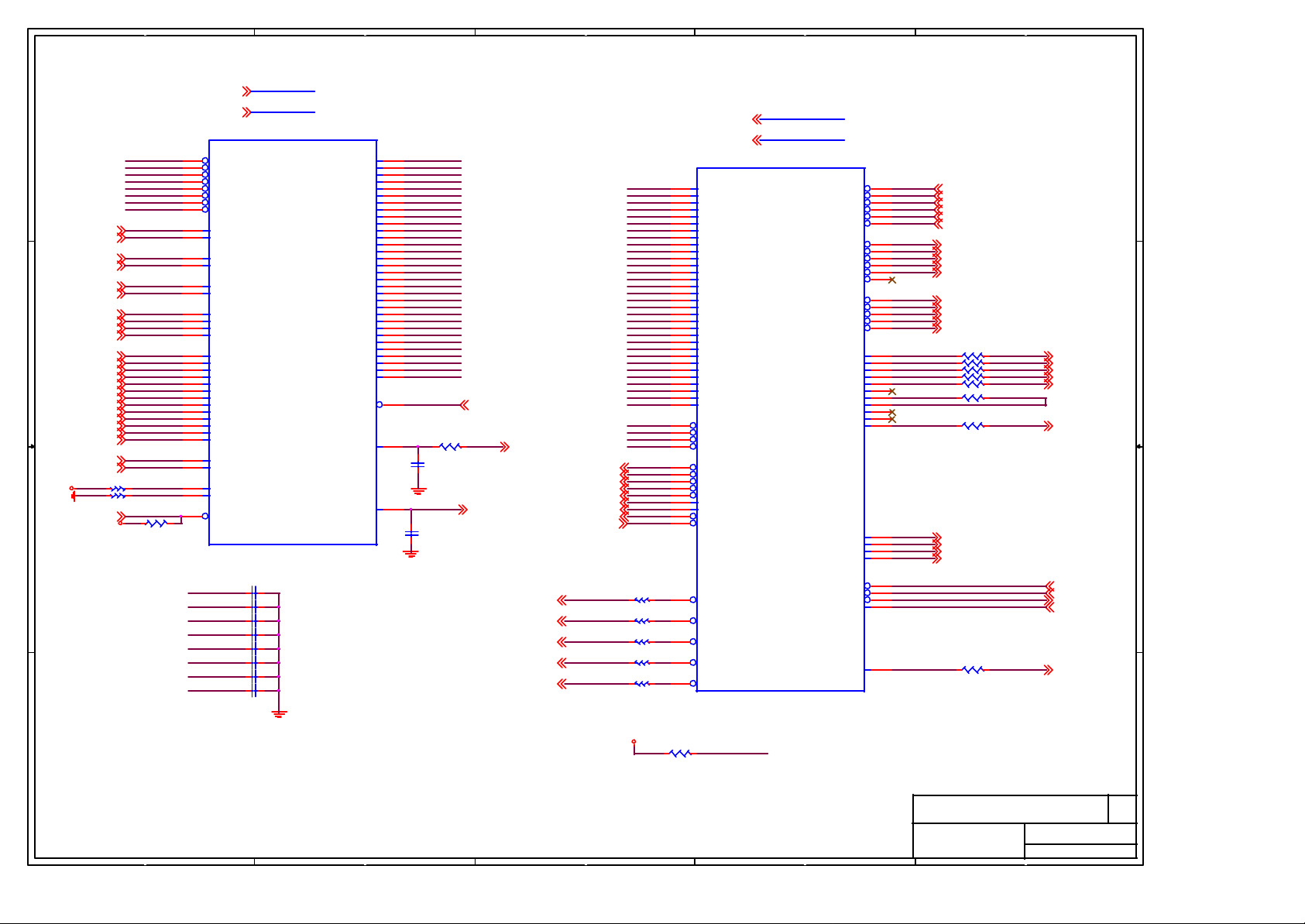

U84A

HT2_TXD0

HT2_TXD1

HT2_TXD2

HT2_TXD3

HT2_TXD0*

HT2_TXD1*

HT2_TXD2*

HT2_TXD3*

HT2_TXCLK0

HT2_TXCLK0*

HT2_TXCTL

HT2_TXCTL*

HT1_TXD0

HT1_TXD1

HT1_TXD2

HT1_TXD3

HT1_TXD4

HT1_TXD5

HT1_TXD6

HT1_TXD7

HT1_TXD8

HT1_TXD9

HT1_TXD10

HT1_TXD11

HT1_TXD12

HT1_TXD13

HT1_TXD14

HT1_TXD15

HT1_TXD0*

HT1_TXD1*

HT1_TXD2*

HT1_TXD3*

HT1_TXD4*

HT1_TXD5*

HT1_TXD6*

HT1_TXD7*

HT1_TXD8*

HT1_TXD9*

HT1_TXD10*

HT1_TXD11*

HT1_TXD12*

HT1_TXD13*

HT1_TXD14*

HT1_TXD15*

HT1_TXCLK0

HT1_TXCLK0*

HT1_TXCLK1

HT1_TXCLK1*

HT1_TXCTL

HT1_TXCTL*

CPUVDD_EN

HT1VDD_EN

HT1_VLD*

MEM_VLD*

CPU_VLD*

CK8G

1 OF 7

HT2_RXD0

HT2_RXD1

HT2_RXD2

HT2_RXD3

HT2_RXD0*

HT2_RXD1*

HT2_RXD2*

HT2_RXD3*

HT2_RXCLK0

HT2_RXCLK0*

HT2_RXCTL

HT2_RXCTL*

HT2_RSET

HT2_STOP*

HT2_REQ*

HT1_RXD0

HT1_RXD1

HT1_RXD2

HT1_RXD3

HT1_RXD4

HT1_RXD5

HT1_RXD6

HT1_RXD7

HT1_RXD8

HT1_RXD9

HT1_RXD10

HT1_RXD11

HT1_RXD12

HT1_RXD13

HT1_RXD14

HT1_RXD15

HT1_RXD0*

HT1_RXD1*

HT1_RXD2*

HT1_RXD3*

HT1_RXD4*

HT1_RXD5*

HT1_RXD6*

HT1_RXD7*

HT1_RXD8*

HT1_RXD9*

HT1_RXD10*

HT1_RXD11*

HT1_RXD12*

HT1_RXD13*

HT1_RXD14*

HT1_RXD15*

HT1_RXCLK0

HT1_RXCLK0*

HT1_RXCLK1

HT1_RXCLK1*

HT1_RXCTL

HT1_RXCTL*

HT1_STOP*

HT1_RSET

CPU_SLP*/GPIO

THERMTRIP*/GPIO

CPU_RST*

CPU_PWROK

CPU_CLK

CPU_CLK*

CPU_COMP

4

AK28

AK27

AL30

AK26

AJ28

AJ27

AL29

AJ26

AL26

AL27

AK29

AJ29

AM29

AK25

AJ25

L0_CADOUT_H[0..15]

L0_CADOUT_L[0..15]

AL1

AM1

AN1

AN2

AN4

AN5

AN6

AM7

AM4

AL5

AJ5

AL6

AJ7

AJ8

AK10

AM9

AL2

AM2

AP1

AP2

AP4

AP5

AP6

AN7

AM3

AL4

AK5

AK6

AK7

AK8

AK9

AL9

AN3

AP3

AM6

AM5

AN8

AP8

AK17

AL3

C3

AJ19

AL20

AK19

AN19

AM19

AP20

4

TP_HT2_UP0

TP_HT2_UP1

TP_HT2_UP2

TP_HT2_UP3

TP_HT2_UP*0

TP_HT2_UP*1

TP_HT2_UP*2

TP_HT2_UP*3

TP_HT2_UPCLK

-TP_HT2_UPCLK

TP_HT2_UPCNTL

-TP_HT2_UPCNTL

HT2_RSET

-TP_HT2_STOP

-TP_HT2_REQ

L0_CADOUT_H0

L0_CADOUT_H1

L0_CADOUT_H2

L0_CADOUT_H3

L0_CADOUT_H4

L0_CADOUT_H5

L0_CADOUT_H6

L0_CADOUT_H7

L0_CADOUT_H8

L0_CADOUT_H9

L0_CADOUT_H10

L0_CADOUT_H11

L0_CADOUT_H12

L0_CADOUT_H13

L0_CADOUT_H14

L0_CADOUT_H15

L0_CADOUT_L0

L0_CADOUT_L1

L0_CADOUT_L2

L0_CADOUT_L3

L0_CADOUT_L4

L0_CADOUT_L5

L0_CADOUT_L6

L0_CADOUT_L7

L0_CADOUT_L8

L0_CADOUT_L9

L0_CADOUT_L10

L0_CADOUT_L11

L0_CADOUT_L12

L0_CADOUT_L13

L0_CADOUT_L14

L0_CADOUT_L15

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

HTSTOP_L

HT_RSET

-TP_CPU_SLP

THERMTRIP_IO_L

RESET_CPU_L

CPU_POWERGOOD

R1405 0

R1406 0

CPU_COMP

R1268 X_51.1RST

L0_CADOUT_H[0..15] 4

L0_CADOUT_L[0..15] 4

L0_CLKOUT_H0 4

L0_CLKOUT_L0 4

L0_CLKOUT_H1 4

L0_CLKOUT_L1 4

L0_CTLOUT_H0 4

L0_CTLOUT_L0 4

HTSTOP_L 5

RESET_CPU_L 5

CPU_POWERGOOD 5

R1278 549RST

3

R1275 51.1RST

CPUCLK0_H

CPUCLK0_L

CB38

X_104P

+

3

C1251

10u/16V

VDD_CORE_PG28,34

CPUCLK0_H 5

CPUCLK0_L 5

+12V

FB65

X_80_0805

PFAN1

1

2

D1x2-W

VDD_CORE_PG

CP17

X_COPPER

CLOSE CK8

VDD_25_SUS

1.2V_HT

2

THERMTRIP_CPU_L5

R1274 6.2K

R1279 6.2K

2

NOTE: Diode is for possible Clawhammer

THERMTRIP_L leakage during S3

VDD_25

R1269

C1246

104P

10K

B

C1248

105p

C1250

105p

10K

10K

1K

R1266

VCC3_SB

CE

VCC3_SB

R1273

B

VCC3_SB

R1277

B

D25

1N4148S

THERMTRIP_IO_L

2N3904S

CE

2N3904S

CE

2N3904S

THERMTRIP_IO_L

AC

C1245

Q132

C1247

Q133

C1249

Q134

M icro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

C1244 X_104P

1 2

U85A

DM7407-SOIC14

104PR1271 10K

3 4

U85B

DM7407-SOIC14

104P

5 6

U85C

DM7407-SOIC14

104P

CK8 HT

VCC3

4.7K

4.7K

4.7K

MS-6725D2

1

1K

R1267

VCC3_SB

R1270

-MEM_VLD

VCC3_SB

R1272

-CPU_VLD

VCC3_SB

R1276

-HT1_VLD

Last Revision Date:

Tuesday, December 17, 2002

Sheet

7 35

1

Rev

0A

of

5

4

3

2

1

A_SBA[7..0]16

A_AD[31..0]16

M33

N33

U32

U33

R33

R34

AD32

AC33

AB30

AC30

AG33

AG29

AC29

M32

N32

M34

AH29

AG31

AK34

R29

AJ33

AJ32

AH33

U30

U29

R32

R30

P32

P33

T33

T32

V33

L33

L34

T30

P34

U84B

AGP_SBA0*

AGP_SBA1*

AGP_SBA2*

AGP_SBA3*

AGP_SBA4*

AGP_SBA5*

AGP_SBA6*

AGP_SBA7*

AGP_SBSTBF

AGP_SBSTBS

AGP_ADSTBF0

AGP_ADSTBS0

AGP_ADSTBF1

AGP_ADSTBS1

AGP_CBE0

AGP_CBE1

AGP_CBE2

AGP_CBE3

AGP_ST0

AGP_ST1

AGP_ST2

AGP_RBF

AGP_WBF

AGP_FRAME

AGP_IRDY

AGP_TRDY

AGP_REQ

AGP_GNT

AGP_STOP

AGP_DEVSEL

AGP_PAR

AGP_DBI1

AGP_DBI0

AGP_CAL_VDDQ

AGP_CAL_GND

AGP_8XDE*

CK8G

D D

A_SBA0

A_SBA1

A_SBA2

A_SBA3

A_SBA4

A_SBA5

A_SBA6

A_SBA7

A_SBSTB_P16

A_SBSTB_N16

A_ADSTB0_P16

A_ADSTB0_N16

A_ADSTB1_P16

A_ADSTB1_N16

A_CBE0_L16

A_CBE1_L16

A_CBE2_L16

A_CBE3_L16

C C

A_RBF_L16

A_WBF_L16 LAN_PCLK 22

A_FRAME_L16

A_IRDY_L16

A_TRDY_L16

A_REQ_L16

A_GNT_L16

A_STOP_L16

A_DEVSEL_L16

A_PAR16

VDD_15

R1288 51.1RST

R1289 51.1RST

A_GC8XDET_L16

B B

A_SBSTB_P

A_SBSTB_N

A_ADSTB0_P

A_ADSTB0_N

A_ADSTB1_P

A_ADSTB1_N

A_CBE0_L

A_CBE1_L

A_CBE2_L

A_CBE3_L

A_ST016

A_ST1

A_ST116

A_ST2

A_ST216

A_RBF_L

A_WBF_L

A_FRAME_L

A_IRDY_L

A_TRDY_L

A_REQ_L

A_GNT_L

A_STOP_L

A_DEVSEL_L

A_PAR

A_DBIH

A_DBIH16

A_DBIL

A_DBIL16

CAL_PD

CAL_PU

VCC3

R685 10K

PCICLK_0

PCICLK_1

PCICLK_2

PCICLK_3

PCICLK_4

PCICLK_5

PCICLK_6

PCICLK_7

A_SBA[7..0]

A_AD[31..0]

CM3 X_10p

CM4 X_10p

CM5 X_10p

CM6 X_10p

CM7 X_10p

CM8 X_10p

CM9 X_10p

CM10 X_10p

2 OF 7

AGP_AD0

AGP_AD1

AGP_AD2

AGP_AD3

AGP_AD4

AGP_AD5

AGP_AD6

AGP_AD7

AGP_AD8

AGP_AD9

AGP_AD10

AGP_AD11

AGP_AD12

AGP_AD13

AGP_AD14

AGP_AD15

AGP_AD16

AGP_AD17

AGP_AD18

AGP_AD19

AGP_AD20

AGP_AD21

AGP_AD22

AGP_AD23

AGP_AD24

AGP_AD25

AGP_AD26

AGP_AD27

AGP_AD28

AGP_AD29

AGP_AD30

AGP_AD31

AGP_PME*

AGP_CLK

APG_VREF

AA33

AA32

AB32

Y33

AB33

Y32

AC32

W33

V32

AE32

AD33

AF33

AE33

AG32

AF32

AH32

AJ30

AF31

AF29

AE30

AF30

AD30

AD29

AC31

AA29

AA30

Y29

Y31

Y30

W30

V30

U31

E26

W32

V29

A_AD0

A_AD1

A_AD2

A_AD3

A_AD4

A_AD5

A_AD6

A_AD7

A_AD8

A_AD9

A_AD10

A_AD11

A_AD12

A_AD13

A_AD14

A_AD15

A_AD16

A_AD17

A_AD18

A_AD19

A_AD20

A_AD21

A_AD22

A_AD23

A_AD24

A_AD25

A_AD26

A_AD27

A_AD28

A_AD29

A_AD30

A_AD31

-AGP_PME

CM1

X_10p

A_REFGC

CM2

104P

RM8

22

-AGP_PME 16

AGPCLK

A_REFGC 16

AGPCLK 16

A_RESET_L16

-PCIRST122

-PCIRST218,19

RESET_IDEP_L24,32

-PCIRST_LPC25,26

-FRAME18,19,22,33

-IRDY18,19,22,33

-TRDY18,19,22,33

-STOP18,19,22,33

-DEVSEL18,19,22,33

PAR18,19,22,33

-SERR18,19,22,33

-PERR18,19,22,33

-PCI_PME18,19,22,33

A_RESET_L

-PCIRST1

-PCIRST2

RESET_IDEP_L

-PCIRST_LPC

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

C_-BE0

C_-BE1

C_-BE2

C_-BE3

-FRAME

-IRDY

-TRDY

-STOP

-DEVSEL

PAR

-SERR

-PERR

-PCI_PME

R1290 33

R1295 33

R1292 33

R1293 33

R1291 33

C33

D30

C31

D34

D33

C34

D32

G32

G33

H32

H34

H33

H30

G29

G30

C32

C25

E33

F28

B33

E32

B31

A32

E31

B34

E34

F33

J30

J34

K33

J29

J33

K30

K29

K32

L32

B32

F34

J32

J31

F29

F31

F30

F32

A33

F26

P29

L30

K5

H6

U84C

PCI_AD0

PCI_AD1

PCI_AD2

PCI_AD3

PCI_AD4

PCI_AD5

PCI_AD6

PCI_AD7

PCI_AD8

PCI_AD9

PCI_AD10

PCI_AD11

PCI_AD12

PCI_AD13

PCI_AD14

PCI_AD15

PCI_AD16

PCI_AD17

PCI_AD18

PCI_AD19

PCI_AD20

PCI_AD21

PCI_AD22

PCI_AD23

PCI_AD24

PCI_AD25

PCI_AD26

PCI_AD27

PCI_AD28

PCI_AD29

PCI_AD30

PCI_AD31

PCI_CBE0*

PCI_CBE1*

PCI_CBE2*

PCI_CBE3*

PCI_FRAME*

PCI_IRDY*

PCI_TRDY*

PCI_STOP*

PCI_DEVSEL*

PCI_PAR

PCI_SERR

PCI_PERR*

PCI_PME*

PCI_RST0*

PCI_RST1*

PCI_RST2*

PCI_RST3*

PCI_RST4*

3 OF 7

AD[31..0]

C_-BE[3..0]

PCI_CLK8/GPIO_8

PCI_CLK9/GPIO_9

PCI_CLK10/GPIO_17

PCI_REQ0*

PCI_REQ1*

PCI_REQ2*

PCI_REQ3*

PCI_REQ4*

PCI_REQ5*

PCI_GNT0*

PCI_GNT1*

PCI_GNT2*

PCI_GNT3*

PCI_GNT4*

PCI_GNT5*

PCI_INTW*

PCI_INTX*

PCI_INTY*

PCI_INTZ*

PCI_INTE*

PCI_CLK0

PCI_CLK1

PCI_CLK2

PCI_CLK3

PCI_CLK4

PCI_CLK5

PCI_CLK6

PCI_CLKFB

LPC_AD0

LPC_AD1

LPC_AD2

LPC_AD3

LPC_FRAME*

LPC_DRQ0*

LPC_DRQ1*

SERIRQ

PCI_CLK7

-PREQ0

C29

E29

D27

D26

A30

A31

E27

D29

E28

C26

B29

B30

M30

N29

M29

N30

P30

A29

C28

B28

B27

A27

B26

A26

B25

B15

B14

D2

H1

H2

H3

G2

F2

J3

F1

G3

E2

-PREQ0 18,33

-PREQ1

-PREQ1 18,33

-PREQ2

-PREQ2 19,33

-PREQ3

-PREQ3 19,33

-PREQ4

-PREQ4 22,33

-PREQ5

-PREQ5 33

-PGNT0

-PGNT0 18

-PGNT1

-PGNT1 18

-PGNT2

-PGNT2 19

-PGNT3

-PGNT3 19

-PGNT4

-PGNT4 22

-PIRQA

-PIRQA 18,19,33

-PIRQB

-PIRQB 16,18,19,33

-PIRQC

-PIRQC 18,19,22,33

-PIRQD

-PIRQD 18,19,33

-PIRQE

-PIRQE 16,33

PCICLK_0A_ST0

RM1

PCICLK_1

RM2

PCICLK_2

RM3

PCICLK_3

RM4

PCICLK_4

RM5

PCICLK_6

RM7

PCI_CLKFB

PCICLK_5 LPC_PCLK

RM6

LPC_AD0

LPC_AD0 25,26

LPC_AD1

LPC_AD1 25,26

LPC_AD2

LPC_AD2 25,26

LPC_AD3

LPC_AD3 25,26

-LPC_FRAME

-LPC_REQ

LDRQ1_L

SERIRQ

PCICLK_7

RM9

22

22

22

22

22

22

22

22

PCICLK1

PCICLK2

PCICLK3

PCICLK4

LAN_PCLK

FWH_PCLK

PCICLK1 18

PCICLK2 18

PCICLK3 19

PCICLK4 19

SIO_PCLK 25

-LPC_FRAME 25,26

-LPC_REQ 33

LDRQ1_L 25,26

SERIRQ 25,33

FWH_PCLK 26

AD[31..0]18,19,22

C_-BE[3..0]18,19,22

CK8G

VCC3

A A

5

4

3

R1297 X_8.2K

LDRQ1_L

for SST FLASH

M icro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

2

http://www.msi.com.tw

CK8 AGP 8X /PCI

MS-6725D2

Last Revision Date:

Tuesday, December 17, 2002

Sheet

1

8 35

Rev

0A

of

5

4

3

2

1

BUFFERED SIO

VCC3

R1298 X_10K

1 = 24 Mhz

CB46

104P

R1304

X_1.2K

R1306

X_1.2K

R1436

X_1.2K

R1438

X_1.2K

FB69

30_0805

0 = 14.318 Mhz

D D

CK8_VSYNC_A17

CK8_HSYNC_A17

C C

B B

A A

CK8_VSYNC_A

CK8_HSYNC_A

CK8_VSYNC_B

CK8_HSYNC_B

5

R1303

X_1.2K

R1305

X_1.2K

R1435

X_1.2K

R1437

X_1.2K

VCC3

VCC3

VCC3_SB

1 2

12

+

VCC3

VCC3

1 2

VCC3

CT37

10u/16V

R1299 10K

CB42

104P

VDO_DDCSDA_A17

VDO_DDCSCL_A17

CK8_GREEN_A17

FB66

30_0805

FB67

30_0805

FB68

30_0805

1 2

CK8_RED_A17

CK8_BLUE_A17

CB47

104P

-AC_RST20

CODEC_1420

AC_SDOUT20

AC_SDIN020

AC_SYNC20

AC_BITCLK20

1 2

12

1 2

4

VCC3_SB

R1300 X_10K

-AC_RST

AC97CLK

AC_SDOUT

AC_SDIN0

AC_SYNC

AC_BITCLK

VDO_DDCSDA_A

VDO_DDCSCL_A

CK8_RED_A

CK8_BLUE_A

CK8_GREEN_A

CB40

104P

+

CT36

10u/16V

CB44

104P

C1271

103P

C1272

18p

32K-12.5pf-CSA-309-D

SPDIF_CK8

Crystal Select

1 = 27 Mhz ( CK8G )

0 = 14.318 Mhz

R1301 10K

RM10 27

R1307

X_124RST

C1264

CB41

104P

1 2

CB43

C1269

104P

1 2

R1407

X_124RST

CB45

C1270

104P

1 2

DUAL_VDD_PLL

12

3

4

Y5

AC97CLK_R

CB39

X_103P

DACA_VDD

103P

+3.3V_PLL

103P

C1369

X_103P

DACB_VDD

103P

RTC_XTALIN

RTC_XTALOUT

C1273

18p

C15

C16

AJ20

AK20

AM23

AL21

AJ21

AK22

AJ22

AM22

AM21

AN23

AP23

AK24

AJ24

AJ23

AK23

AM24

AN24

AP24

AP21

AN21

AL23

AN22

B16

E16

F17

F16

E15

E17

E1

C1

A11

B11

U84D

SPDIF

AC_RESET*

AC97_CLK

AC_SDATA_OUT

AC_SDATA_IN0

AC_SDATA_IN1

AC_SYNC

AC_BITCLK

DACA_VSYNC

DACA_HSYNC

DDC_DATA0

DDC_CLK0

DACA_RED

DACA_BLUE

DACA_GREEN

DACA_RSET

DACA_VREF

DACA_GND

DACA_VDD

+3.3V_PLL

DACB_VSYNC

DACB_HSYNC

DDC_DATA1

DDC_CLK1

DACB_RED

DACB_BLUE

DACB_GREEN

DACB_RSET

DACB_VREF

DACB_GND

DACB_VDD

+3.3V_PLL_DUAL

XTALIN_RTC

XTALOUT_RTC

CK8G

4 OF 7

A20

B20

E21

F21

A21

B21

B22

C22

A23

B23

B24

C24

D20

C20

E22

F22

D21

C21

E23

F23

E24

F24

E25

F25

D18

E18

B18

C17

A18

D17

B19

C19

D24

E19

A17

R1332

909RST

R1308 27

R1309 27

R1310 27

R1311 27

R1312 27

R1313 27

R1314 27

R1315 27

R1316 27

R1317 27

R1318 27

R1319 27

XTAL_IN

XTAL_OUT

VCC3_SB

CB48

104P

1 2

C1274

22P

USB_0

USB_0*

USB_1

USB_1*

USB_2

USB_2*

USB_3

USB_3*

USB_4

USB_4*

USB_5

USB_5*

USB2_0

USB2_0*

USB2_1

USB2_1*

USB2_2

USB2_2*

USB2_3

USB2_3*

USB2_4

USB2_4*

USB2_5

USB2_5*

USB_OC0*

USB_OC1*

USB_OC2*

USB_OC3*

USB_OC4*

USB_OC5*

XTALIN

XTALOUT

+3.3V_USB_DUAL

+3.3V_USB_DUAL

USB_RBIAS

3

C1262 X_5.6p_0402

C1263 X_5.6p_0402

C1265 X_5.6p_0402

C1266 X_5.6p_0402

C1267 X_5.6p_0402

C1268 X_5.6p_0402

-OC1

-OC3

-OC5

Y6

12

14M-32pf-HC49S-D

2

-OC1 30

-OC3 30

-OC5 31

12

C1275

22P

R1324 15K

R1325 15K

R1326 15K

R1327 15K

R1328 15K

R1329 15K

R1330 15K

R1331 15K

M icro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

DATA0+_FRONT 23

DATA0-_FRONT 23

DATA1+_REAR 23

DATA1-_REAR 23

DATA2+_FRONT 23

DATA2-_FRONT 23

DATA3+_REAR 23

DATA3-_REAR 23

DATA4+_REAR 23

DATA4-_REAR 23

DATA5+_REAR 23

DATA5-_REAR 23

R1320 15K

R1321 15K

R1322 15K

R1323 15K

CK8 AC97_USB_VGA

MS-6725D2

Last Revision Date:

Sheet

1

Tuesday, December 17, 2002

9 35

of

Rev

0A

5

4

3

2

1

5 OF 7

DDATA_P[15..0]

DDATA_S[15..0]

DDATA_M[15..0]

IDE_DATA_P0

IDE_DATA_P1

IDE_DATA_P2

IDE_DATA_P3

IDE_DATA_P4

IDE_DATA_P5

IDE_DATA_P6

IDE_DATA_P7

IDE_DATA_P8

IDE_DATA_P9

IDE_DATA_P10

IDE_DATA_P11

IDE_DATA_P12

IDE_DATA_P13

IDE_DATA_P14

IDE_DATA_P15

IDE_ADDR_P0

IDE_ADDR_P1

IDE_ADDR_P2

IDE_CS1_P*

IDE_CS3_P*

IDE_DACK_P*

IDE_IOW_P*

IDE_INTR_P

IDE_DREQ_P

IDE_IOR_P*

IDE_RDY_P

IDE_DATA_S0

IDE_DATA_S1

IDE_DATA_S2

IDE_DATA_S3

IDE_DATA_S4

IDE_DATA_S5

IDE_DATA_S6

IDE_DATA_S7

IDE_DATA_S8

IDE_DATA_S9

IDE_DATA_S10

IDE_DATA_S11

IDE_DATA_S12

IDE_DATA_S13

IDE_DATA_S14

IDE_DATA_S15

IDE_ADDR_S0

IDE_ADDR_S1

IDE_ADDR_S2

IDE_CS1_S*

IDE_CS3_S*

IDE_DACK_S*

IDE_IOW_S*

IDE_INTR_S

IDE_DREQ_S

IDE_IOR_S*

IDE_RDY_S

A20GATE/GPIO

INTRUDER*

EXT_SMI*

RI*/GPIO

SIO_PME*/GPIO

KBRDRSTIN*/GPIO

SMB_CLK0

SMB_DATA0

SMB_CLK1

SMB_DATA1

+1.2V_VBAT

SMB_ALERT*

BUF_SIO_CLK

BUF_14MHZ/GPIO

PWRGD_SB

FANRPM/GPIO

FANCTL0/GPIO

FANCTL1/GPIO

SPKR

PWRBTN*

SUSCLK

THERM*

RSTBTN*

SLP_S5*

SLP_S3*

SLP_S1*

PWRGD

TEST

V1

V5

U6

U1

U3

T3

T5

R6

R5

T6

T2

U2

V3

U5

V6

V2

Y1

Y5

AA3

AA1

AA2

W6

W2

W5

W3

Y3

Y2

AD1

AC1

AC3

AD5

AC6

AB5

AA6

AB3

AB2

AA5

AB6

AC5

AD6

AC2

AD3

AD2

AF3

AE3

AF2

AF1

AG3

AG5

AE5

AG6

AE6

AF5

AF6

F9

D11

A5

B5

E10

C6

D1

C11

A3

H5

G5

B10

B9

F11

C10

A4

B6

F7

A8

D9

C7

C8

D6

B3

E6

D5

C5

B8

DDATA_P0

DDATA_P1

DDATA_P2

DDATA_P3

DDATA_P4

DDATA_P5

DDATA_P7

DDATA_P8

DDATA_P9

DDATA_P10

DDATA_P11

DDATA_P12

DDATA_P13

DDATA_P14

DDATA_P15

DADDR_P0

DADDR_P1

DADDR_P2

DCS1P_L

DCS3P_L

DDACKP_L

DIOWP_L

IRQ14

DDRQP

DIORP_L

DRDYP

DDATA_S0

DDATA_S1

DDATA_S2

DDATA_S3

DDATA_S4

DDATA_S5

DDATA_S6

DDATA_S7

DDATA_S8

DDATA_S9

DDATA_S10

DDATA_S11

DDATA_S12

DDATA_S13

DDATA_S14

DDATA_S15

DADDR_S0

DADDR_S1

DADDR_S2

DCS1S_L

DCS3S_L

DDACKS_L

DIOWS_L

IRQ15

DDRQS

DIORS_L

DRDYS

KA20G

-INTRUDER

-EXTSMI

RI_L

SPKR

PWRBTOUT

-SIO_PME

KBRC_L

SMBCLK1

SMBDATA1

SMBCLK2

SMBDATA2

-SBM_ALLERT

SIO_24MR

THERM_L

-FP_RST

-SLP_S5

-SLP_S3

TP-SLP_S1

PWRGD_SB

CK8_PWRGD

CPU_FAN

FANCON0_IOH

FANCON1_IOH

R1361

1K

3

DADDR_P0 24

DADDR_P1 24

DADDR_P2 24

DCS1P_L 24

DCS3P_L 24

DDACKP_L 24

DIOWP_L 24

IRQ14 24,33

DDRQP 24

DIORP_L 24

DRDYP 24

DADDR_S0 24

DADDR_S1 24

DADDR_S2 24

DCS1S_L 24

DCS3S_L 24

DDACKS_L 24

DIOWS_L 24

IRQ15 24,33

DDRQS 24

DIORS_L 24

DRDYS 24

KA20G 25

R1346 X_0

RI_L 27

SPKR 31

PWRBTOUT 25

C32KHZ 25

-SIO_PME 25

KBRC_L 25

SMBCLK1 12,13,33

SMBDATA1 12,13,33

SMBCLK2 18,19,22,25,33

SMBDATA2 18,19,22,25,33

RM14

SIO_14M

22

THERM_L 25

-FP_RST 31

-SLP_S5 28,31

-SLP_S3 25,31

PWRGD_SB 35

CPU_FAN 25,31

FANCON0_IOH 31

FANCON1_IOH 31

ATX_PWR_OK25,29,30,31

PWRGD_PS

1.2V

1.2V_DUAL

R1344 6.8K

INTRUDER_L

VBAT

SIO_14M 25

R1337 1K

R1338 1K

VCC5_SB

R1343

8.2K

B

C1280

0.47u

INTRUDER_L 25,31

2

VCC3_SB

R1334

R1335

10K

YFET-NDS7002AS

C1277

X_0.33u

B

C1278

104P

VCC3_SB

CE

Q139

2N3904S

0 = User Mode Boot Init table

1 = Safe Mode Boot Init table

THERM_L

-INTRUDER

-EXTSMI

-SIO_PME

-SBM_ALLERT

BUF_25MR

SIO_24MR

SATACLK

10K

Q135

YFET-NDS7002AS

Q136

CE

Q137

2N3904S

R1341

15K

11 10

C1279

0.1u

Q138

YFET-NDS7002AS

R1348 X_4.7K

JBOOT

1

2

3

D1x3-BK

R1353 1M

R1356 4.7K

R1357 10K

R1358 1.2K

CM11 X_10p

CM12 X_10p

CM50 X_10p

Title

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

DM7407-SOIC14

VCC3

VBAT

VCC3_SB

M icro Star Restricted Secret

C1276

4.7K

U85E

9 8

U85D

DM7407-SOIC14

X_0.1u

VCC3_SB

R1342

PWRGD_SB

R1349

4.7K

CK8_IDE_MII_MISC

MS-6725D2

Last Revision Date:

Sheet

1

VCC3_SB

R1333

4.7K

CK8_PWRGD

CK8_PWRGD31

SPKR

Tuesday, December 17, 2002

10 35

of

Rev

0A

DDATA_P[15..0]24

DDATA_S[15..0]24

DDATA_M[15..0]32

R1411

60.4RST

R1360

60.4RST

AP31

AP32

AL32

AL31

AM31

AP33

AN32

AN34

AM33

AM34

AL33

AP34

AM32

AN33

AK31

AK33

AN31

AL34

AK32

C13

D14

AG1

4

B12

A12

B13

AE2

E14

F12

B17

E11

E13

F13

U84E

M2

M3

M5

L6

L2

K2

J2

K6

J1

K3

L3

L1

L5

M6

M1

N6

P1

P2

R3

R1

R2

N2

P5

P3

N5

P6

N3

J5

Y6

E9

E8

B7

F8

D3

C4

E3

E4

CK8G

IDE_DATA_M0

IDE_DATA_M1

IDE_DATA_M2

IDE_DATA_M3

IDE_DATA_M4

IDE_DATA_M5

IDE_DATA_M6

IDE_DATA_M7

IDE_DATA_M8

IDE_DATA_M9

IDE_DATA_M10

IDE_DATA_M11

IDE_DATA_M12

IDE_DATA_M13

IDE_DATA_M14

IDE_DATA_M15

IDE_ADDR_M0

IDE_ADDR_M1

IDE_ADDR_M2

IDE_CS1_M*

IDE_CS3_M*

IDE_DACK_M*

IDE_IOW_M*

IDE_INTR_M

IDE_DREQ_M

IDE_IOR_M*

IDE_RDY_M

SATA_CLK

BUF_25MHZ

MII_TXD0

MII_TXD1

MII_TXD2

MII_TXD3

MII_TXCLK

MII_TXEN

MII_RXD0

MII_RXD1

MII_RXD2

MII_RXD3

MII_RXCLK

MII_RXDV

MII_RXER

MII_COL

MII_MDIO

MII_CRS

MII_MDC

MII_PWRDWN

EE_SEL

EE_CLK

EE_DATAO

EE_DATAI

GPIO_1

GPIO_2

GPIO_3

GPIO_4

GPIO_5

GPIO_6

GPIO_7

GPIO_10

GPIO_11

GPIO_12

GPIO_13

GPIO_14

GPIO_15

GPIO_16

GPIO_18

GPIO_19

GPIO_20

IDE_COMP

DDATA_M0

D D

DADDR_M032

DADDR_M132

DADDR_M232

DDACKM_L32

U86

DI

SK

VCC

CS

GND

NC NC

X_AT93C86

SATA_CLK32

BUF_25M

DO

RM12 22

MIITXD035

MIITXD135

MIITXD235

MIITXD335

MIITXCLK35

MIITXEN35

MIIRXD035

MIIRXD135

MIIRXD235

MIIRXD335

MIIRXCLK35

MIIRXDV35

MIIRXER35

MIIMDIO35

MIIMDC35

DCABLEIDP_L24

DCABLEIDS_L24

MII_EEDI

4

8

5

MIICOL35

MIICRS35

C C

BUF_25M35

MIIRXD2

MIIRXD0

MIIRXD3

MIIRXD1

MIIRXCLK

MIITXCLK

MIIMDIO

B B

VCC3_SB

RN133 8P4R_10K

1

2

3

4

5

6

7

8

R1412 10K

R1413 10K

R1414 10K

EEPROM

MII_EEDO

R1355

MII_EECK

X_0

-MII_EECS

A A

5

3

2

1

6 7

DDATA_M1

DDATA_M2

DDATA_M3

DDATA_M4

DDATA_M5

DDATA_M6 DDATA_P6

DDATA_M7

DDATA_M8

DDATA_M9

DDATA_M10

DDATA_M11

DDATA_M12

DDATA_M13

DDATA_M14

DDATA_M15

DADDR_M0

DADDR_M1

DADDR_M2

DDRQM32

DRDYM32

RM11 22

BUF_25MR

MIITXD0

MIITXD1

MIITXD2

MIITXD3

MIITXCLK

MIITXEN

MIIRXD0

MIIRXD1

MIIRXD2

MIIRXD3

MIIRXCLK

MIIRXDV

MIIRXER

MIICOL

MIIMDIO

MIICRS

MIIMDC

TP_MII_PWRDWN

DCABLEIDP_L

DCABLEIDS_L

DCS1M_L

DCS3M_L

DDACKM_L

DIOWM_L

INTR_M

DDRQM

DIORM_L

DRDYM

SATACLK

-MII_EECS

MII_EECK

MII_EEDO

MII_EEDI

VCC3

DCS1M_L32

DCS3M_L32

DIOWM_L32

INTR_M32

DIORM_L32

VCC3_SB

C1282

X_104P

Loading...

Loading...