8

7

6

5

4

3

2

1

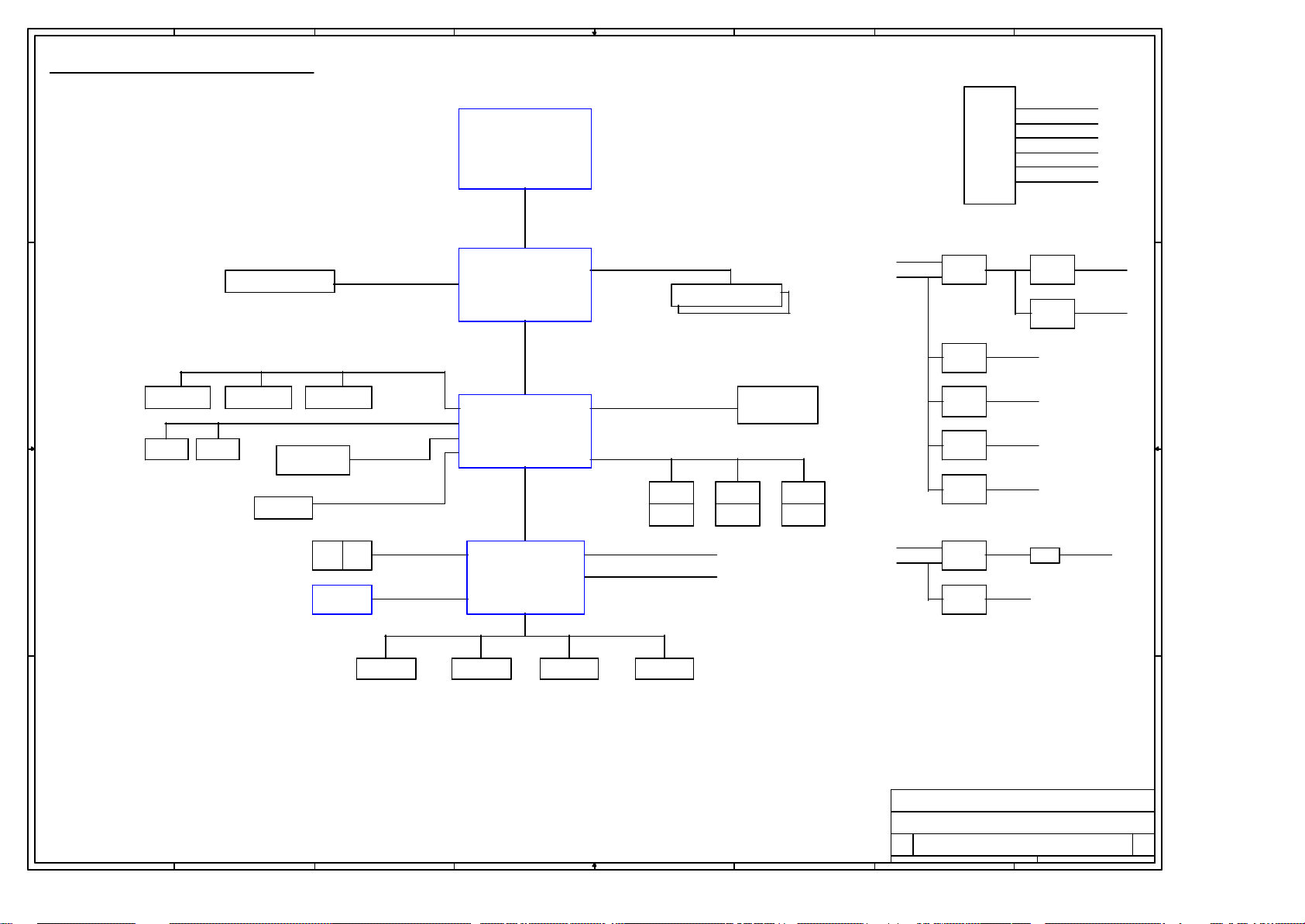

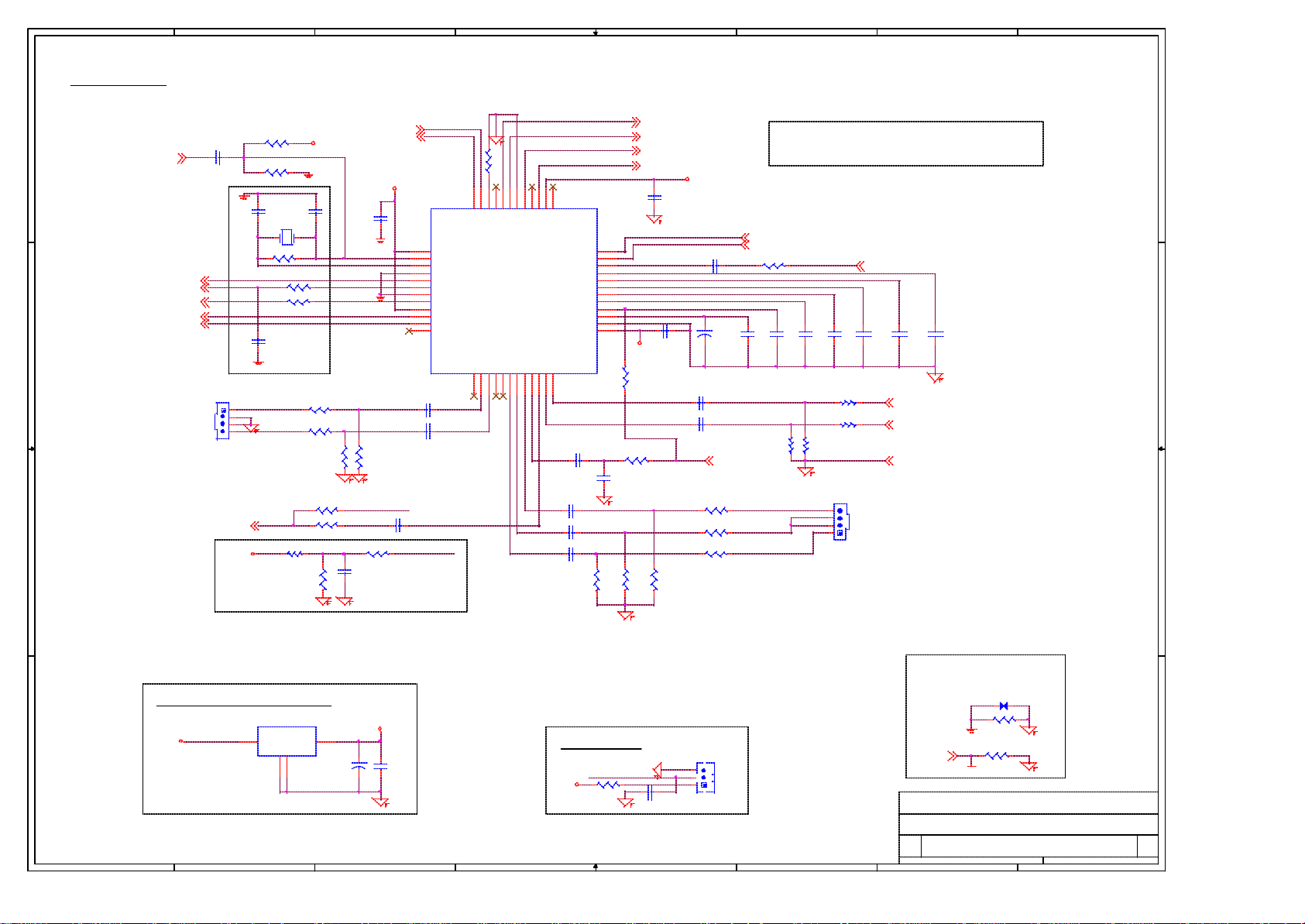

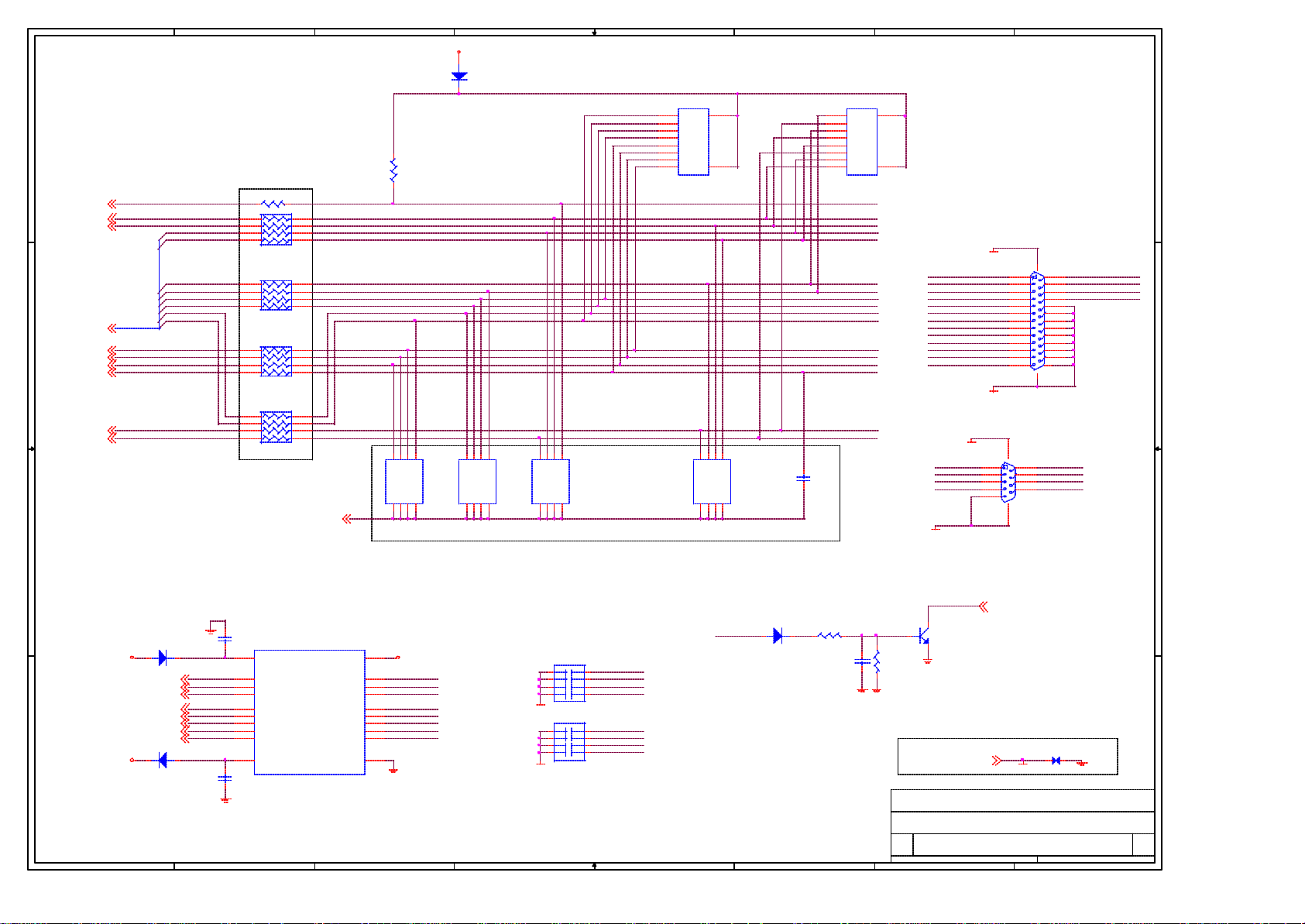

Cover Sheet

Block Diagram

CLOCK GEN

D D

AMD CPU Sockets 462

Via VT8375 KM266 North Bridge

DDR SLOT

DDR TERMINATOR

AGP SLOT

1

2

3

4 - 5

6 - 8

9

10

11

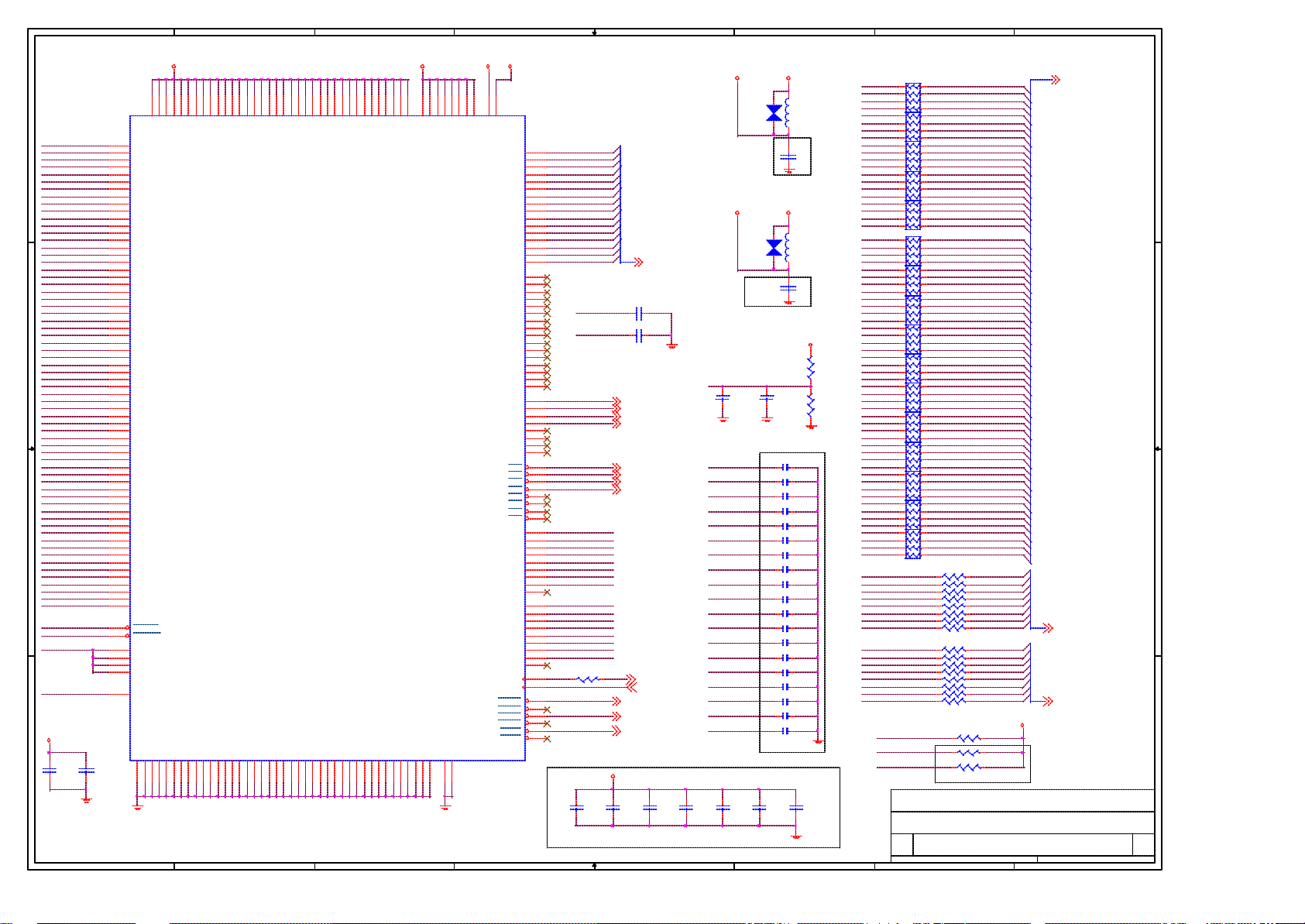

MS-6596 Ver : 3.0

VIA KT400 + VT8235 Chipset

CPU:

AMD Athlon XP / Athlon / Duron Socket 462

Via VT8235 South Bridge 12 - 14

PCI SLOTS 1,2&3 15

C C

LAN

IDE CONNECTOR

USB & KB/MS CONNECTOR

AC'97 CODEC

AUDIO CONNECTOR

16

17

18

19

20

FLASH ROM & FAN CONNECTOR 21

System Chipset:

VIA VT8377 (KT400 ) + VT8235

On Board Chipset:

LPC Super I/O -- W83697HF

Lan : Via PHY VT6103

Expansion Slots:

LPC I/O(W83697HF)

B B

PARALLEL & SERIAL CONN.

22

23

AGP 3.0 Slot * 1

DDR Slot * 2

PCI 2.2 Slot * 3

MS-5 ACPI CONTROLLER, REGULATORS

ATX POWER CON, FRONT PANEL & Thermal Trip

VRM 9.0

DECOUPLING CAPACITORS

HISTORY

A A

8

7

6

24

25

26

27

28

29

30

MICRO-STAR INT'L CO.,LTD.

31

32

5

4

3

Title

Size Document Number Rev

Custom

Date: Sheet of

COVER PAGE

MS-6596

2

1 28Wednesday, October 30, 2002

1

3.0

8

7

6

5

4

3

2

1

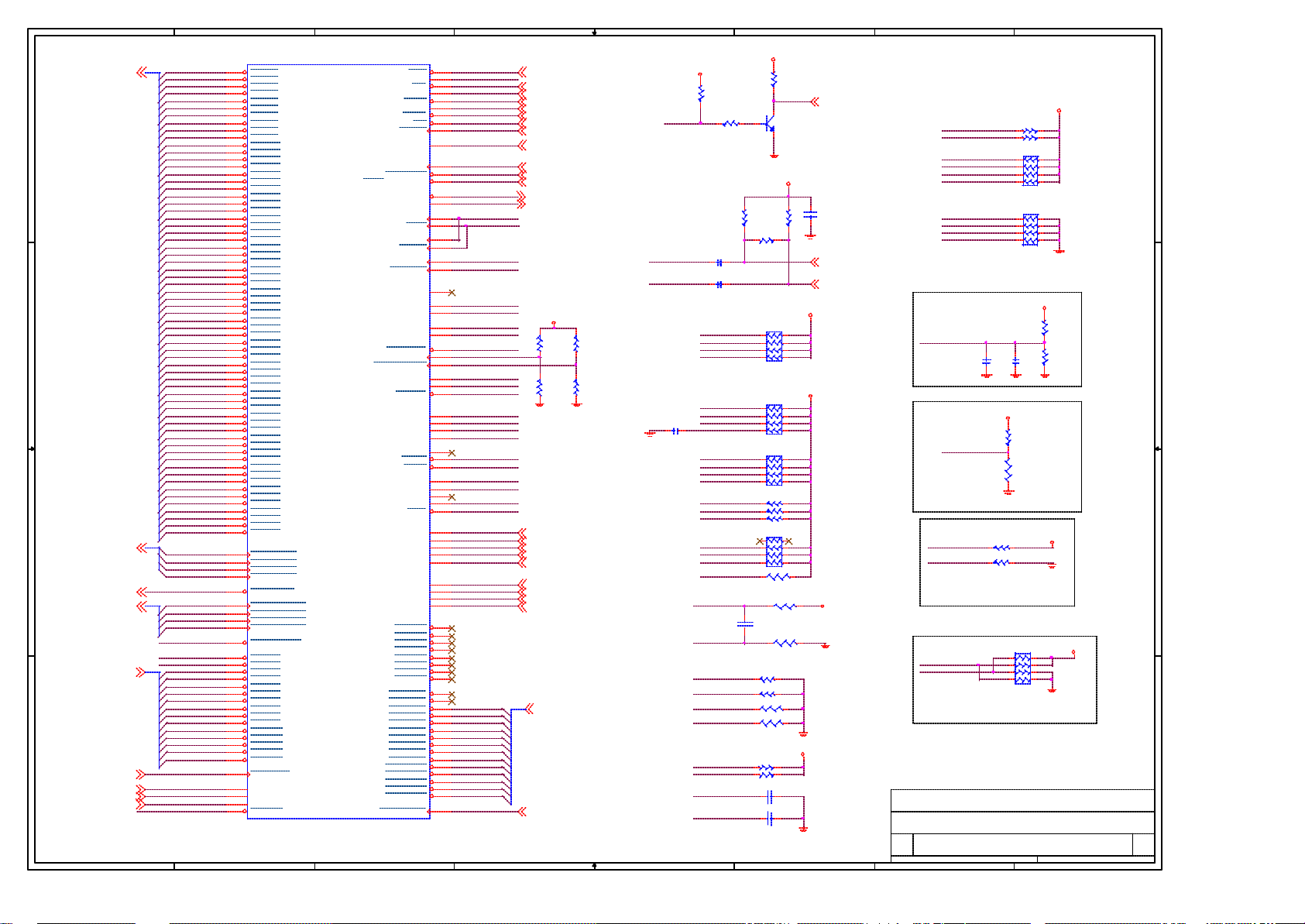

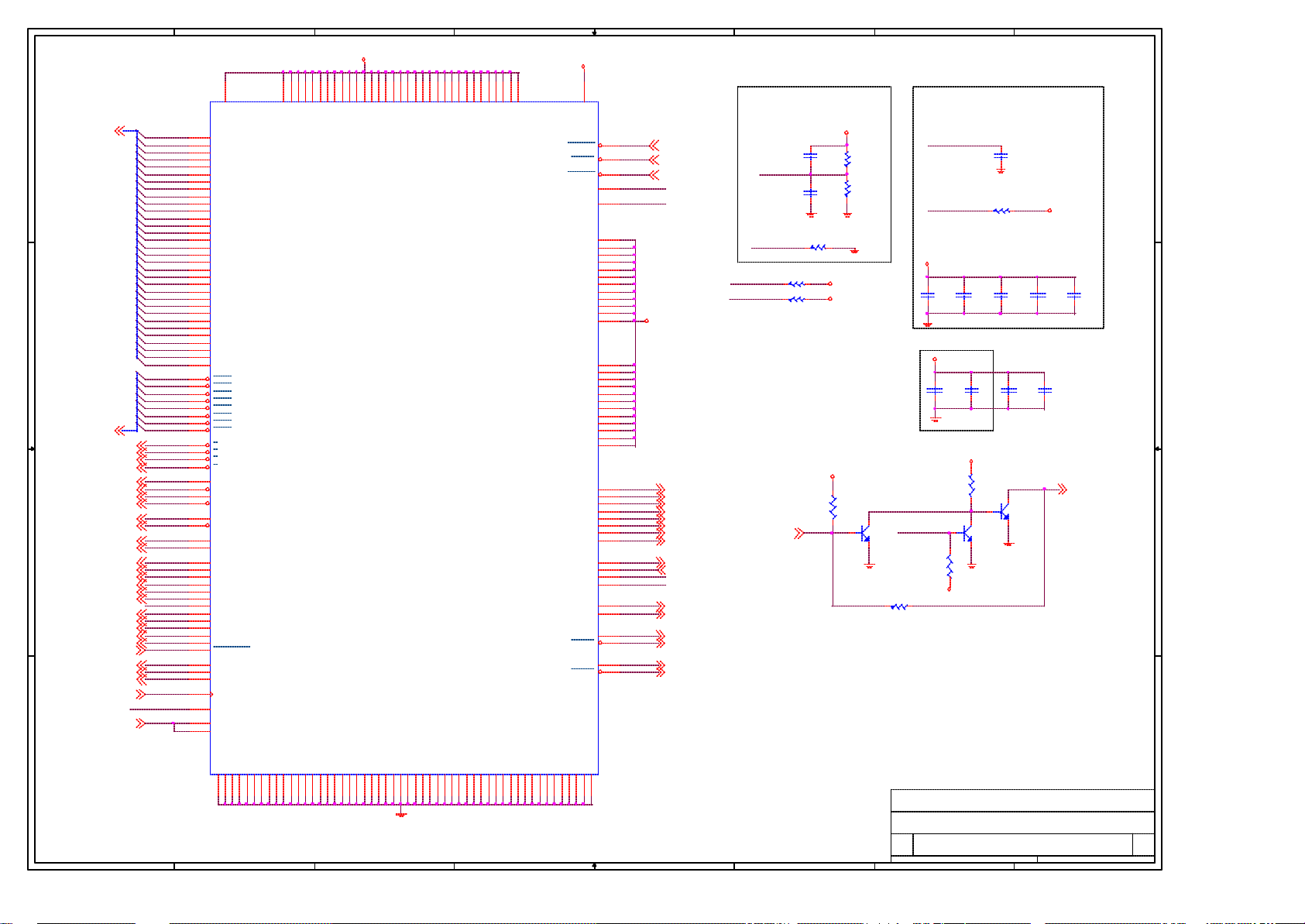

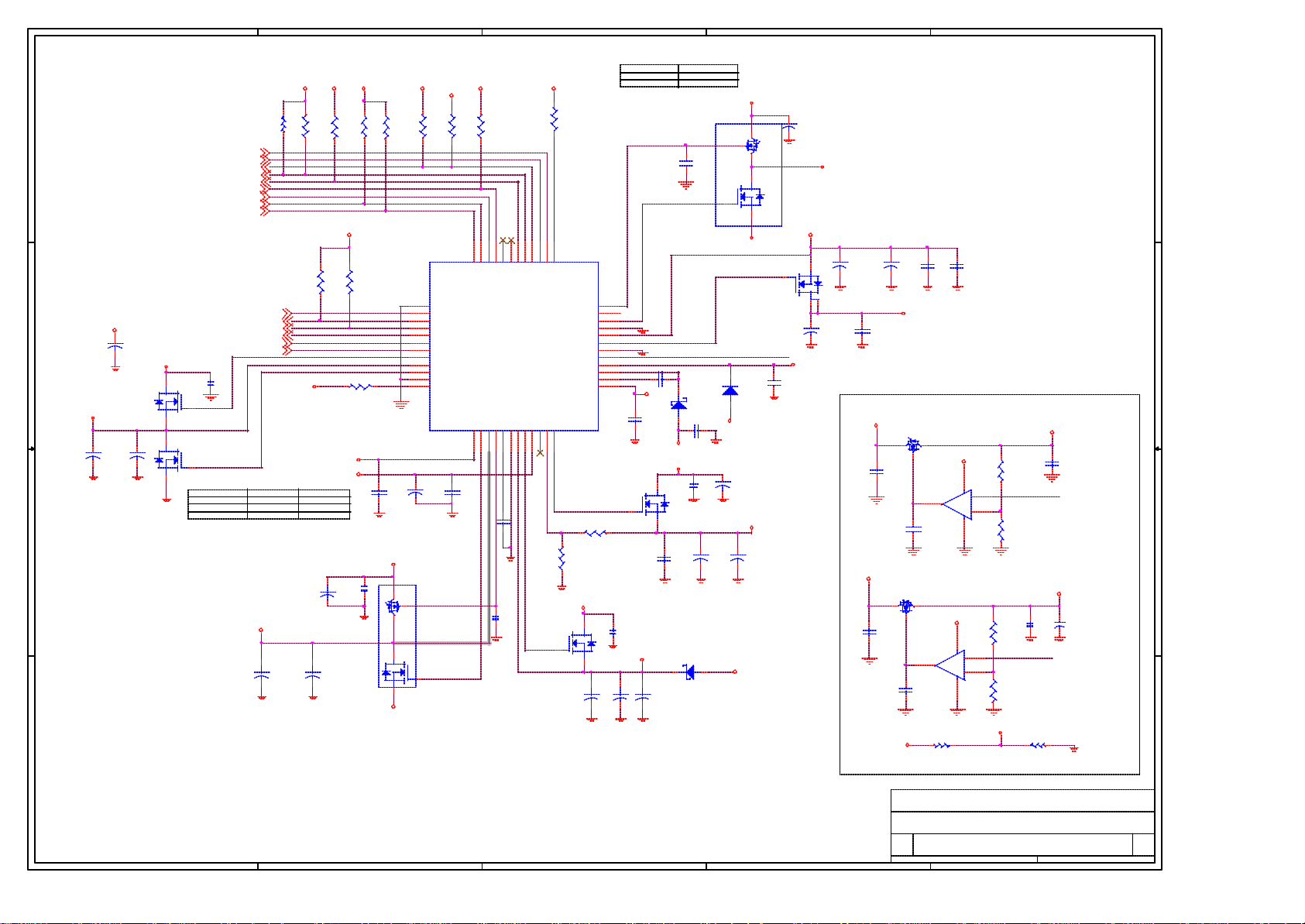

System Block Diagram

+ 12V

- 12V

D D

SOCKET-462

Host Bus

(100/133MHz)

ATX CONN

+ 5V

- 5V

3.3V

VCC5SBY

(100/133MHz)

CPU

FAN

SYS

FAN

8X/4X/2X (66MHz)

PS/2IDE 1

MII

FAN CONTROL

Via VT8377

V-Link

8x/4x/2x

(66MHz)

Via VT8235

LPC

Bus

2 DDR DIMM MODUAL

AC'97 Link (14.318MHz)

USB2.0

USB 0

USB 1

VOLTAGE MONITOR

TEMPERATURE MONITOR

USB 2

USB 3

AC'97

AUDIO CODEC

ALC650

USB 4

USB 5

AGP Connector

C C

PCI SLOT 3

PCI SLOT 2 PCI SLOT 1

IDE 2

B B

PCI (33MHz)

ULTRA DMA 33/66/100/133

KEYBOARD

/MOUSE

LAN PHY

VCC5SBY

VCC3

VCC5SBY

VCC5

VCC3SBY VCCM

VCC25SBY

DDR_VTT

VCC2_5

VDDQ

VCCA_PLL

5VDUAL

KBUVCC

LPC Super I/O

FLASH

ROM

GPIO

SERIAL PARALLEL FLOPPY

VCORE

A A

MICRO-STAR INT'L CO.,LTD.

Title

Size Document Number Rev

Custom

8

7

6

5

4

3

Date: Sheet of

System Block Diagram

MS-6596

2

2 28Tuesday, October 29, 2002

1

3.0

8

7

6

5

4

3

2

1

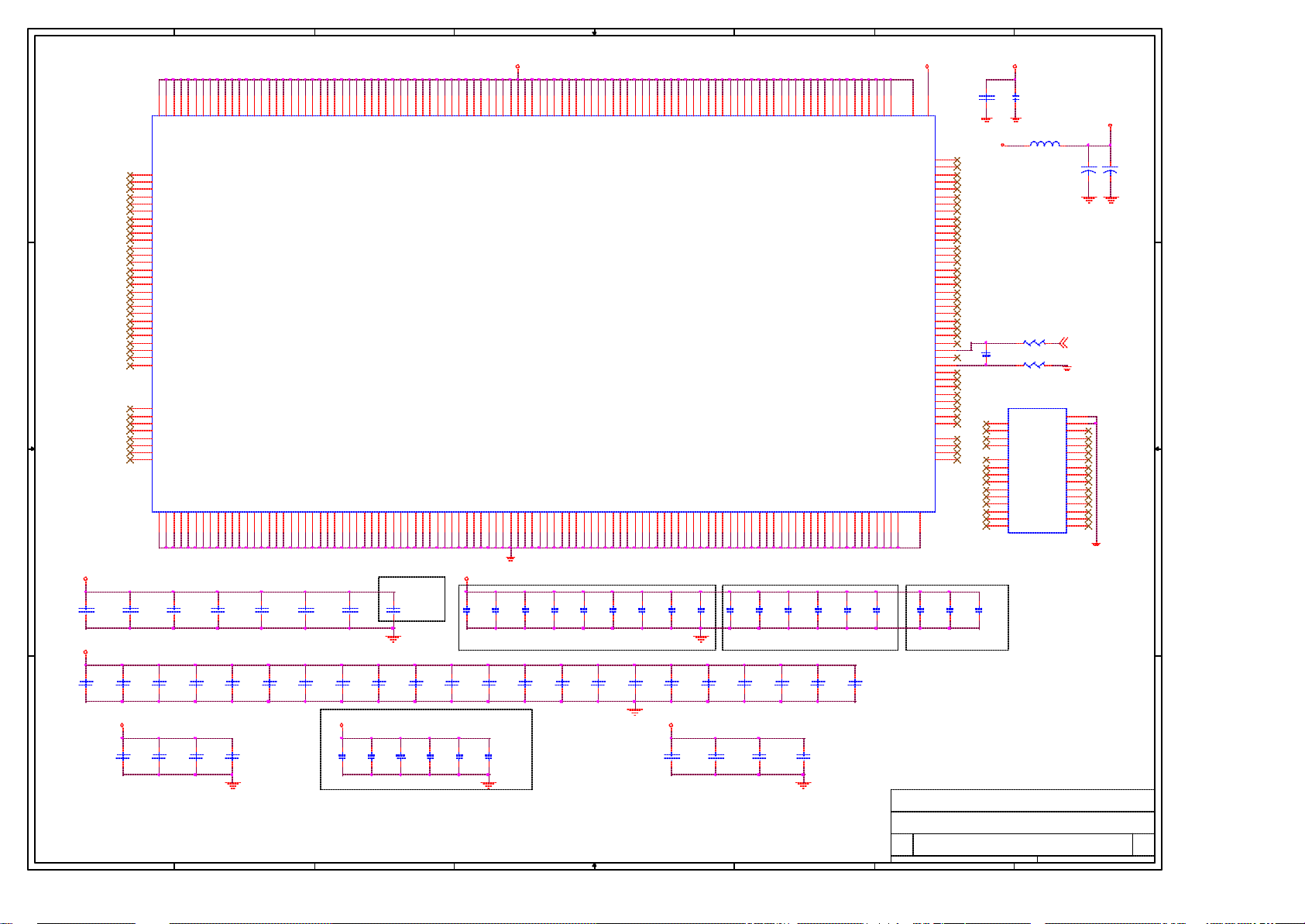

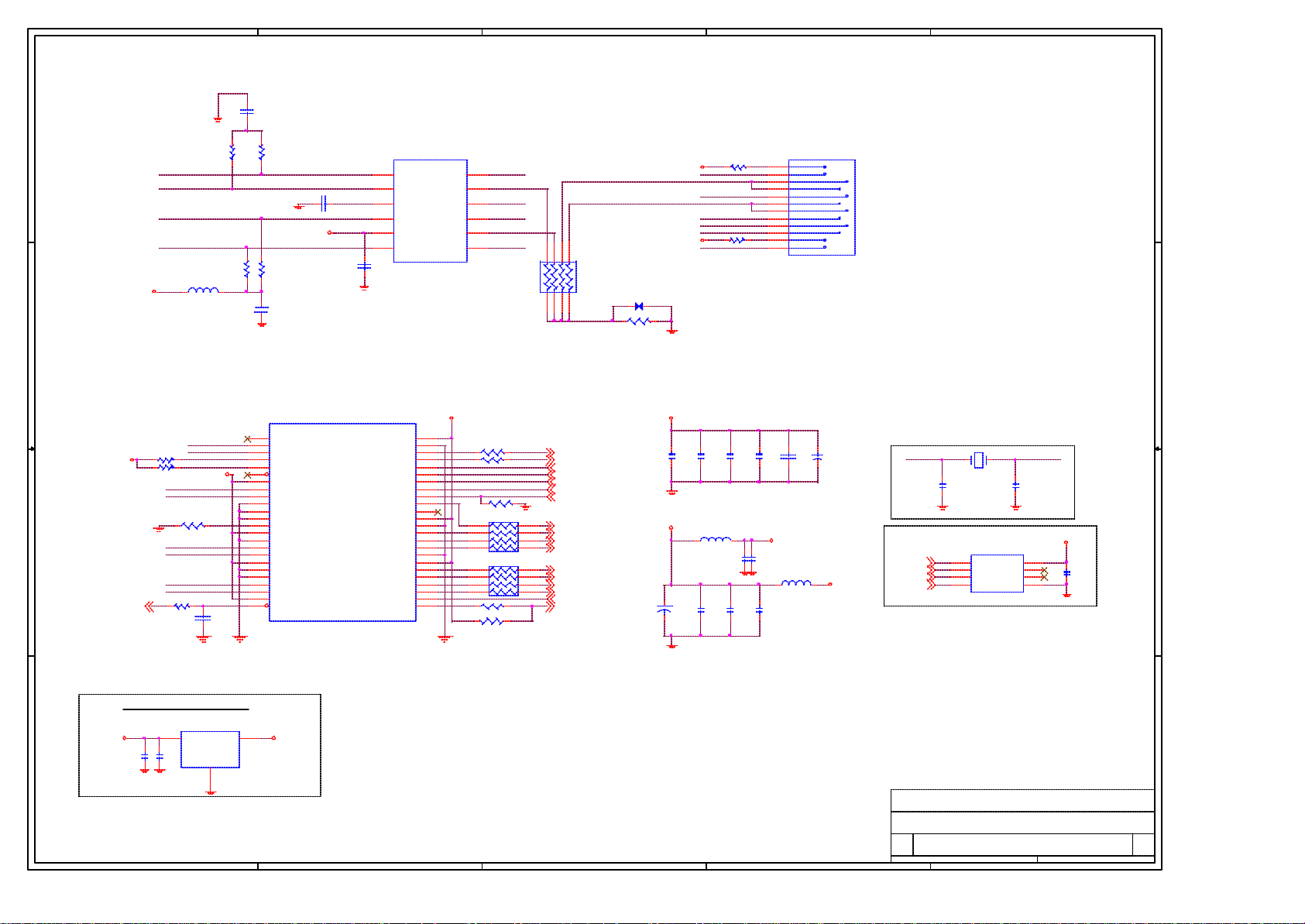

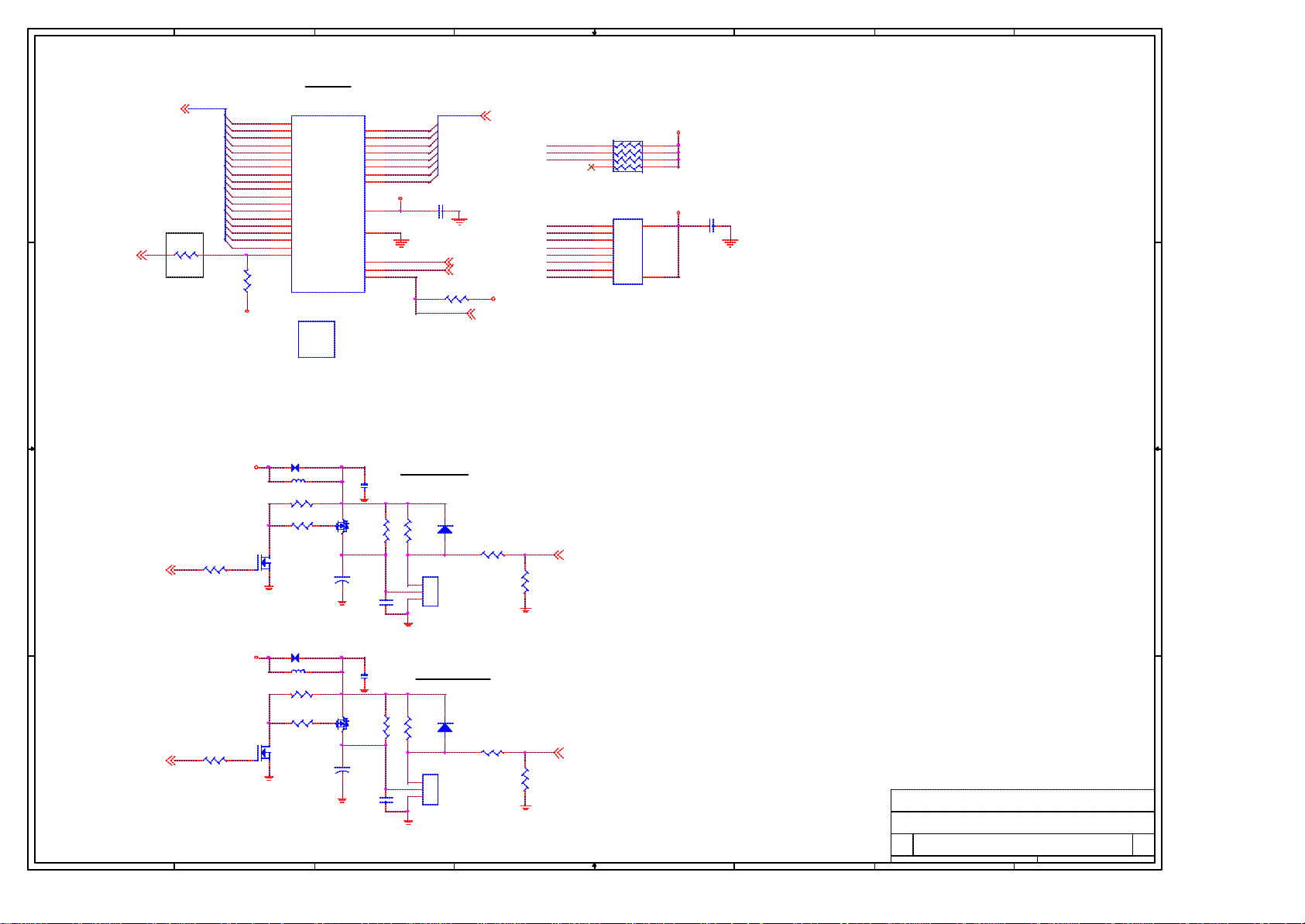

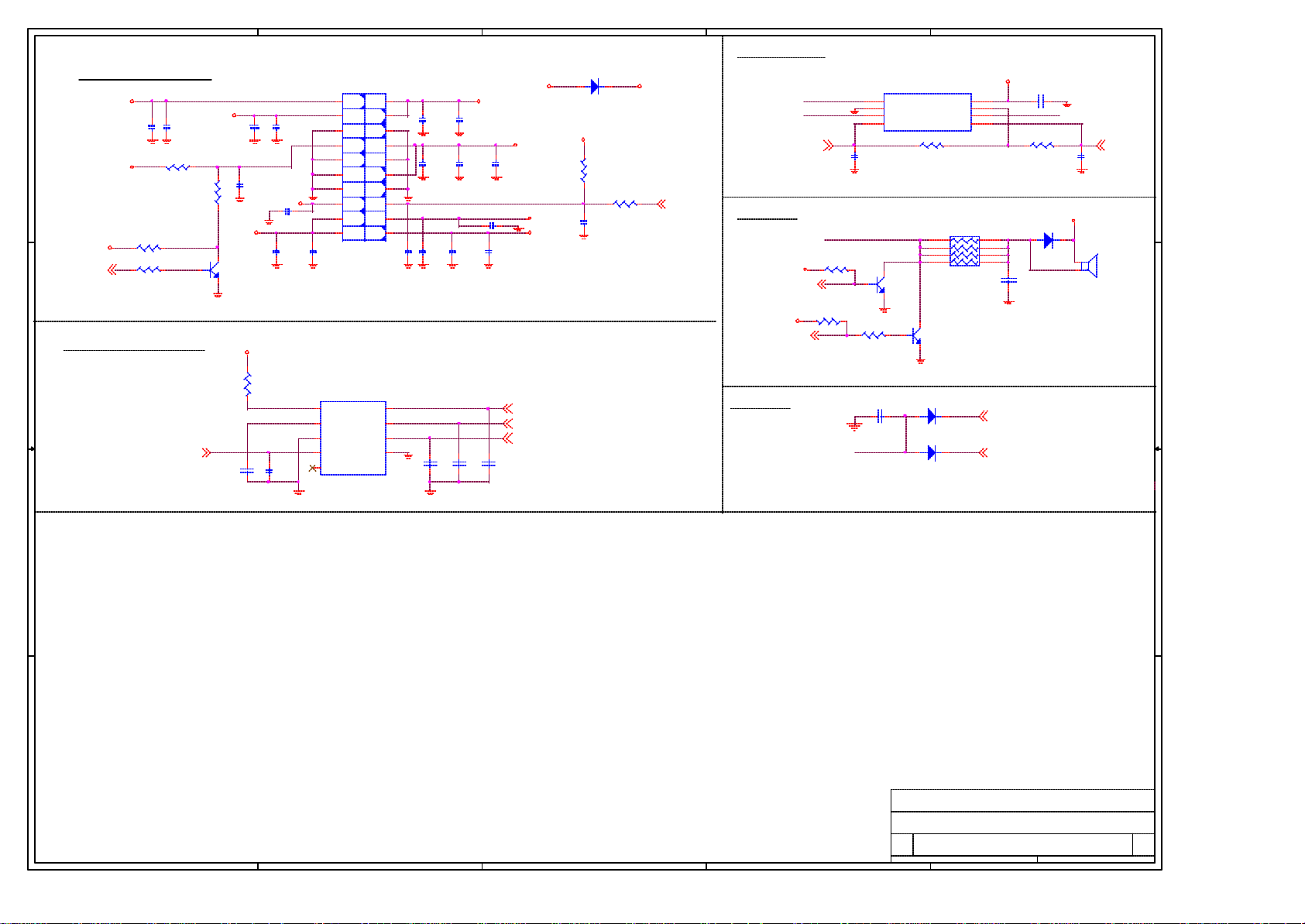

Main Clock Generator

D D

VCC3

CP12

X_COPPER

CB104

L36

X_80-0805

10u/16V ECSMD

VCC3

CB94

C C

X_0.1u

CB891uCB103

EC53

L38 X_80-0805

CP13

X_COPPER

VCC2_5

L35

X_80-0805

SMBCLK{9,13,24}

SMBDAT{9,13,24}

CP11

X_COPPER

CB93

0.1u

FP_RST#{24,25}

CB102

1u

CB96

0.1u

CB91

1u

0.1u

CB95

1u

1u

VCC2_5

VADDR25

CB92

CB90

1u

1u

R223 X_0

R216 475RST

B B

VCC3

REF1

53

1

2

X_NC7SZ08P5X-SOT23_5

APICSB

4

U11

U13

5

VDDAGP

16

VDDPCI

22

VDD48M

51

VDDCPU

55

VDDREF

2

GND2

9

GND9

13

GND13

19

GND48M

33

GND33

39

GND39

47

GNDI

54

GND54

23

AVDD

24

AGND

50

VDDI

34

VDD3.3/2.5-34

40

VDD3.3/2.5-40

27

SCLK

28

SDATA

25 1

IREF REF0/FS0

CPUCLK_PPT

CPUCLK_PPC

CPUCLKST

CPUCLKSC

DDRT0

DDRC0

DDRT1

DDRC1

DDRT2

DDRC2

DDRT3

DDRC3

DDRT4

DDRC4

DDRT5

DDRC5

BUFFER_IN

FBOUT

AGP0/MODE

AGP1/SEL_CPU

AGP2/PCI_STOP#

PCICLK_F/FS1

PCICLK0/SEL_SD_DDR#

PCICLK1/MULTSEL0

PCICLK2

PCICLK3

PCICLK4

PCICLK5/CPU_STP#

48M/FS3RESET/PD#

24_48M/FS2

VTT_PWRGD#/REF1

XIN

3

14M-32pf-HC49S-D

C209

22p

XOUT

CY28341-2 A

4

Y1

C193

22p

RN72

10-8P4R

RN69

22-8P4R

RN70

22-8P4R

RN71

22-8P4R

MULTSEL0

SELCPU

SELDDR#

R244 4.7K

R272 10K

R283 10K

7 8

5 6

3 4

1 2

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

R187 22

R246 22

R270 22

R248 22

RN78 22-8P4R

1 2

3 4

5 6

7 8

R241 22

R252 22

R271 22

R243 22

R254 33

R266 33

R196 X_62

R197 X_261RST

48

49

53

52

44

43

42

41

38

37

36

35

32

31

30

29

45

46

6

SELCPU

7

8

FS1

10

SELDDR#

11

MULTSEL0

12

14

15

17

18

FS3

2026

FS2

21

FS0

REF1

56

VCC3

FS1_S{13}

FS3_S{13}

CPUCLK1

CPUCLK-1

CPUCLK-0

CPUCLK0

DDRCLK0

DDRCLK-0

DDRCLK1

DDRCLK-1

DDRCLK2

DDRCLK-2

DDRCLK3

DDRCLK-3

DDRCLK4

DDRCLK-4

DDRCLK5

DDRCLK-5

DCLKO

AGPCLK0MODE

VLCLK

AGPCLK1

PCICLK3

SIOPCLK

PCICLK2

PCICLK1

PCLKSB

USBCLK

SIO48M

APICSB

SBCLK14

APICCPU

R231 X_4.7K

R247 4.7K

R249 4.7K

FS0

FS1

FS3

FS2

CPUCLK1 {6}

CPUCLK-1 {6}

CPUCLK-0 {4}

CPUCLK0 {4}

DDRCLK0 {9}

DDRCLK-0 {9}

DDRCLK1 {9}

DDRCLK-1 {9}

DDRCLK2 {9}

DDRCLK-2 {9}

DDRCLK3 {9}

DDRCLK-3 {9}

DDRCLK4 {9}

DDRCLK-4 {9}

DDRCLK5 {9}

DDRCLK-5 {9}

DCLKO {7}

DCLKI {7}

AGPCLK0 {8}

VLCLK {12}

AGPCLK1 {11}

PCICLK3 {15}

SIOPCLK {22}

PCICLK2 {15}

PCICLK1 {15}

PCLKSB {12}

USBCLK {14}

SIO48M {22}

APICSB {12}

SBCLK14 {13}

AC97CLK {19}

APICCPU {4}

R250 X_2.7K

R251 X_4.7K

R253 4.7K

By-Pass Capacitors Place

near to the Clock Outputs

AGPCLK0

VLCLK

AGPCLK1

PCICLK3

SIOPCLK

PCICLK2

PCICLK1

PCLKSB

APICCPU

APICSB

SBCLK14

USBCLK

SIO48M

DCLKO

By-Pass Capacitors Place

near to the Clock Outputs

DDRCLK0

DDRCLK-0

DDRCLK1

DDRCLK-1

DDRCLK2

DDRCLK-2

DDRCLK3

DDRCLK-3

DDRCLK4

DDRCLK-4

DDRCLK5

DDRCLK-5

CPUCLK0

CPUCLK-0

CPUCLK-1

CPUCLK1

10pC217

10pC229

10pC218

CN14 X_10p-8P4C

1 2

3 4

5 6

7 8

X_10pC215

X_10pC185

X_10pC216

X_10pC214

X_10pC220

X_10pC219

R157 X_4.7K

R173 X_4.7K

CN11 10p-8P4C

1 2

3 4

5 6

7 8

CN12 10p-8P4C

1 2

3 4

5 6

7 8

CN10 10p-8P4C

1 2

3 4

5 6

7 8

CN13 10p-8P4C

1 2

3 4

5 6

7 8

VCC2_5

R207 X_22

VCC2_5

REF1

A A

53

1

2

NC7SZ08P5X-SOT23_5

R198 22

4

APICCPU

U10

MICRO-STAR INT'L CO.,LTD.

Title

Size Document Number Rev

Custom

8

7

6

5

4

3

Date: Sheet of

2

CLOCK GEN

MS-6596

3 28Friday, November 22, 2002

3.0

1

8

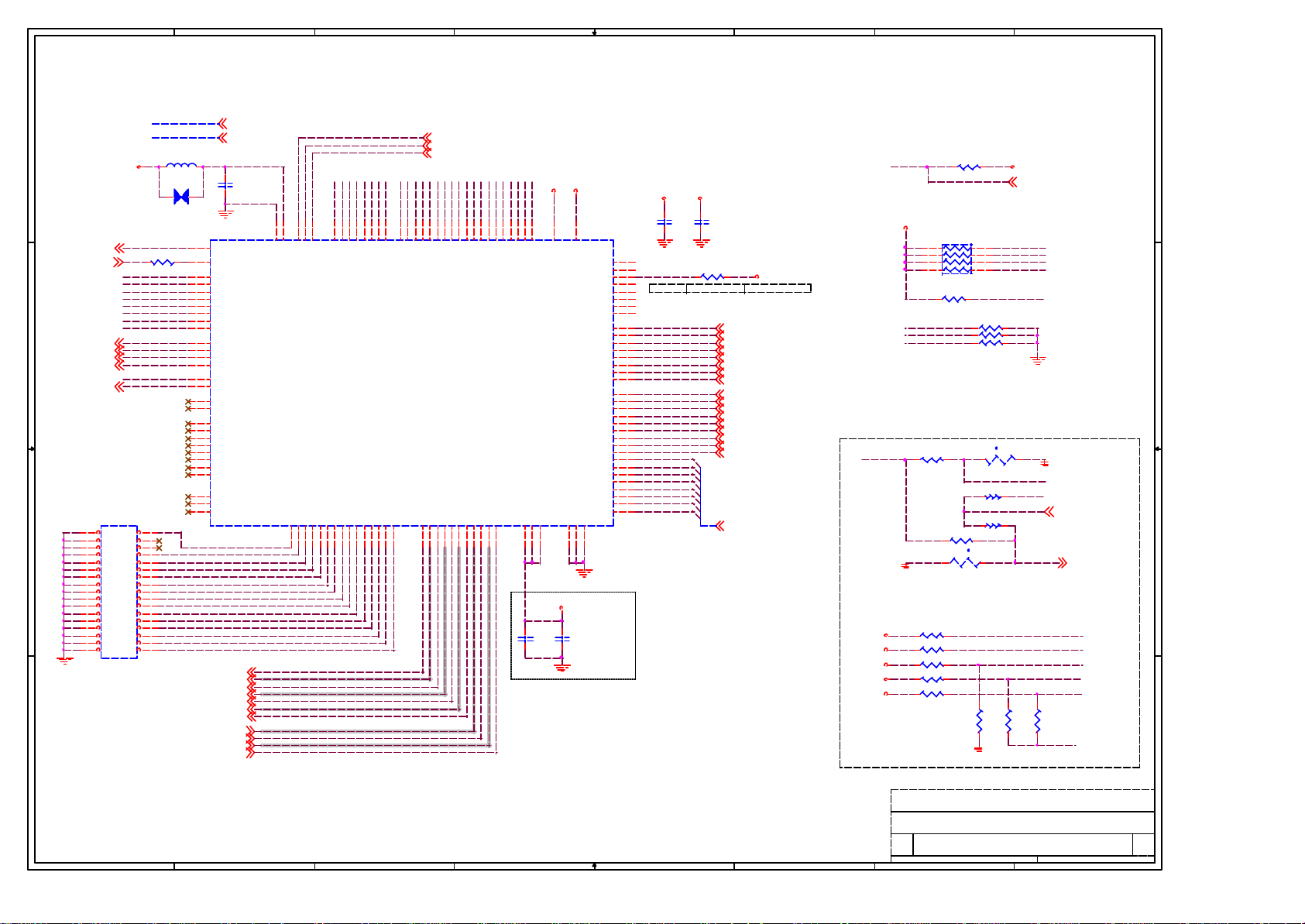

SDATA#[0:63]{6}

D D

C C

B B

DICLK#[0:3]{6}

DIVAL#{6}

DOCLK#[0:3]{6}

SDATA#0

SDATA#1

SDATA#2

SDATA#3

SDATA#4

SDATA#5

SDATA#6

SDATA#7

SDATA#8

SDATA#9

SDATA#10

SDATA#11

SDATA#12

SDATA#13

SDATA#14

SDATA#15

SDATA#16

SDATA#17

SDATA#18

SDATA#19

SDATA#20

SDATA#21

SDATA#22

SDATA#23

SDATA#24

SDATA#25

SDATA#26

SDATA#27

SDATA#28

SDATA#29

SDATA#30

SDATA#31

SDATA#32

SDATA#33

SDATA#34

SDATA#35

SDATA#36

SDATA#37

SDATA#38

SDATA#39

SDATA#40

SDATA#41

SDATA#42

SDATA#43

SDATA#44

SDATA#45

SDATA#46

SDATA#47

SDATA#48

SDATA#49

SDATA#50

SDATA#51

SDATA#52

SDATA#53

SDATA#54

SDATA#55

SDATA#56

SDATA#57

SDATA#58

SDATA#59

SDATA#60

SDATA#61

SDATA#62

SDATA#63

DICLK#0

DICLK#2

DICLK#3

DIVAL#

DOCLK#0

DOCLK#1

DOCLK#2

DOCLK#3

DOVAL#

AIN#0

AIN#1

AIN#[2:14]{6}

A A

AICLK#{6}

CFWDRST{6}

CONNECT{6}

PROCRDY{6}

8

AIN#2

AIN#3

AIN#4

AIN#5

AIN#6

AIN#7

AIN#8

AIN#9

AIN#10

AIN#11

AIN#12

AIN#13

AIN#14

AICLK#

CFWDRST

CONNECT

PROCRDY

FILVAL#

AA35

AA33

AE37

AC33

AC37

AA37

AC35

AN33

AE35

AL31

AJ29

AL29

AG33

AJ37

AL35

AE33

AJ35

AG37

AL33

AN37

AL37

AG35

AN29

AN35

AN31

AJ33

AJ21

AL23

AN23

AJ31

W37

W35

Y35

U35

U33

S37

S33

Y37

S35

Q37

Q35

N37

J33

G33

G37

E37

G35

Q33

N33

L33

N35

L37

J37

A37

E35

E31

E29

A27

A25

E21

C23

C27

A23

A35

C35

C33

C31

A29

C29

E23

C25

E17

E13

E11

C15

E9

A13

C9

A9

C21

A21

E19

C19

C17

A11

A17

A15

W33

J35

E27

E15

C37

A33

C11

7

SDATA0

SDATA1

SDATA2

SDATA3

SDATA4

SDATA5

SDATA6

SDATA7

SDATA8

SDATA9

SDATA10

SDATA11

SDATA12

SDATA13

SDATA14

SDATA15

SDATA16

SDATA17

SDATA18

SDATA19

SDATA20

SDATA21

SDATA22

SDATA23

SDATA24

SDATA25

SDATA26

SDATA27

SDATA28

SDATA29

SDATA30

SDATA31

SDATA32

SDATA33

SDATA34

SDATA35

SDATA36

SDATA37

SDATA38

SDATA39

SDATA40

SDATA41

SDATA42

SDATA43

SDATA44

SDATA45

SDATA46

SDATA47

SDATA48

SDATA49

SDATA50

SDATA51

SDATA52

SDATA53

SDATA54

SDATA55

SDATA56

SDATA57

SDATA58

SDATA59

SDATA60

SDATA61

SDATA62

SDATA63

SDATAINCLK0

SDATAINCLK1

SDATAINCLK2

SDATAINCLK3

SDATAINVAL

SDATAOUTCLK0

SDATAOUTCLK1

SDATAOUTCLK2

SDATAOUTCLK3

SDTATOUTVAL

SADDIN0

SADDIN1

SADDIN2

SADDIN3

SADDIN4

SADDIN5

SADDIN6

SADDIN7

SADDIN8

SADDIN9

SADDIN10

SADDIN11

SADDIN12

SADDIN13

SADDIN14

SADDINCLK

CLKFWDRST

CONNECT

PROCRDY

SFILLVAL

7

Socket 462

6

IGNNE

RESET

STPCLK

PWROK

PICCLK

PICD0/BYPASSCLK

PICD1/BYPASSCLK

COREFB-

COREFB+

CLKIN

CLKIN

RSTCLK

RSTCLK

K7CLKOUT

K7CLKOUT

ANALOG

SYSVREFMODE

VREF_SYS

PLLBYPASS

PLLBYPASSCLK

PLLBYPASSCLK

PLLMON1

PLLMON2

PLLTEST

SCANCLK1

SCANCLK2

SCANINTEVAL

SCANSHIFTEN

DBRDY

DBREQ

FLUSH

SCHECK0

SCHECK1

SCHECK2

SCHECK3

SCHECK4

SCHECK5

SCHECK6

SCHECK7

SADDOUT0

SADDOUT1

SADDOUT2

SADDOUT3

SADDOUT4

SADDOUT5

SADDOUT6

SADDOUT7

SADDOUT8

SADDOUT9

SADDOUT10

SADDOUT11

SADDOUT12

SADDOUT13

SADDOUT14

SADDOUTCLK

6

CPU1A

A20M

FERR

INIT

INTR

NMI

SMI

TCK

TDI

TDO

TMS

TRST

VID0

VID1

VID2

VID3

VID4

FID0

FID1

FID2

FID3

5

4

3

2

1

VCC3

FERR

Place Near

socket-A

CPUCLK_R

CPUCLK#_R

39PC13

4

VCORE

R21

X_680

R15 1K

60.4RST

680PC45

680PC49

FID3

FID2

FID1

FID0

CPUINIT#

IGNNE#

CPURST#

A20M#

SMI#

NMI

INTR

STPCLK#

FLUSH#

PLLMON1

PLLMON2

AIN#0

AIN#1

PLLBP#

CPURST#

COREFB+

COREFB-

AIN#0

AIN#1

DOVAL#

FILVAL#

APICD0

APICD1

CPURST#

PWRGD_CPU

B

NPN-3904LT1-SOT23

R67

60.4RST

R68

301RST

1 2

3 4

5 6

7 8

330-8P4R

RN8 680-8P4R

1 2

3 4

5 6

7 8

RN7 680-8P4R

1 2

3 4

5 6

7 8

R39 680

R51 56

R47 56

RN27 680-8P4R

1 2

3 4

5 6

7 8

R32 X_270

RESERVE

R48 X_10K

C24

4.7u-1206

R54 X_0

R82 X_680

R81 X_680

R83 270

R85 270

R52 330

R58 330

C11 180p

C20 X_180p

RN6

R8

510

C

E

VCORE

R71

Q1

VCC2_5

VCORE

VCC2_5

3

FERR# {12}

C50

0.01u

CPUCLK0 {3}

CPUCLK-0 {3}

VCORE

VCORE

TRST#

PLLTEST#

DBREQ#

TCK

TMS

TDI

R22 510

R30 510

RN14

1 2

3 4

5 6

7 8

510-8P4R

SSHIFTEN

SINTVAL

SCANCLK2

SCANCLK1

RN10

1 2

3 4

5 6

7 8

270-8P4R

VCORE

0.5 * VCORE

VREF_SYS

CB3

39p

R18

100RST

R13

100RST

CB4

0.1u

VCORE

R26

VREFMODE

VREFMODE=Low=No voltage scaling

ZN

ZPDICLK#1

match the transmission line

Push-pull compensation circuit

CLKOUT

CLKOUT#

* Trace lengths of CLKOUT

and -CLKOUT are between

2" and 3"

X_1K

R24

270

R33 40.2RST

R37 56.2RST

RN21 100-8P4R

for

internal

VREFSYS

VCORE

78

56

34

12

VCORE

MICRO-STAR INT'L CO.,LTD.

Title

Size Document Number Rev

Custom

Date: Sheet of

2

Socket 462 - 1

MS-6596

4 28Friday, November 22, 2002

1

3.0

AE1

AG1

AJ3

AL1

AJ1

AN3

AG3

AN5

AC1

AE3

N1

N3

N5

AG13

AG11

AN17

AL17

AN19

AL19

AL21

AN21

FERR

STPCLK#

COREFBCOREFB+

CPUCLK_R

CPUCLK#_R

CLKOUT

CLKOUT#

A20M# {12}

CPUINIT# {12}

INTR {12}

IGNNE# {12}

NMI {8}

CPURST# {24}

SMI# {12}

STPCLK# {12}

PWRGD_CPU {24}

APICCPU {3}

APICD0 {12}

APICD1 {12}

COREFB- {26}

COREFB+ {26}

AJ13

VREFMODE

AA5

VREF_SYS

W5

ZN

ZP

AE5

AJ25

AN15

AL15

AN13

AL13

AC3

S1

S5

S3

Q5

AA1

AA3

AL3

Q1

U1

U5

Q3

U3

L1

L3

L5

L7

J7

W1

W3

Y1

Y3

U37

Y33

L35

E33

E25

A31

C13

A19

J1

J3

C7

A7

E5

A5

E7

C1

C5

C3

G1

E1

A3

G5

G3

ZP

PLLBP#

PLLMON1

PLLMON2

PLLTEST#

SCANCLK1

SCANCLK2

SINTVAL

SSHIFTEN

DBREQ#

FLUSH#

TCK

TDI

TMS

TRST#

VID0

VID1

VID2

VID3

VID4

FID0

FID1

FID2

FID3

AOUT#2

AOUT#3

AOUT#4

AOUT#5

AOUT#6

AOUT#7

AOUT#8

AOUT#9

AOUT#10

AOUT#11

AOUT#12

AOUT#13

AOUT#14

ZN

AC5

E3

VCORE

R63

100RST

R59

100RST

VID0 {26}

VID1 {26}

VID2 {26}

VID3 {26}

VID4 {26}

FID0 {13}

FID1 {13}

FID2 {13}

FID3 {13}

AOUT#[2:14] {6}

AOCLK# {6}

5

R57

100RST

R61

100RST

8

H12

H16

H20

H24M8P30R8T30V8X30Z8AB30

D D

VCC_CORE1

VCC_CORE2

VCC_CORE3

VCC_CORE4

VCC_SRAM1

VCC_SRAM2

VCC_SRAM3

VCC_SRAM4

VCC_SRAM5

VCC_SRAM6

VCC_SRAM7

VCC_SRAM8

VCC_SRAM9

VCC_SRAM11

VCC_SRAM13

VCC_SRAM14

VCC_SRAM16

VCC_SRAM17

VCC_SRAM19

VCC_SRAM20

VCC_SRAM21

VCC_SRAM22

VCC_SRAM23

VCC_SRAM24

VCC_SRAM25

VCC_SRAM26

VCC_SRAM27

VCC_SRAM28

VCC_SRAM29

VCC_SRAM30

VCC_SRAM31

KEY4

KEY6

KEY8

KEY10

KEY12

KEY14

KEY16

KEY18

VSS1

VSS2

VSS3

H14

H18

H22

H26

VCC_CORE5

VSS4

VSS5

M30P8R30T8V30X8Z30

AD30

AD8

AF10

AF28

AF30

AF32

AF6

AF8

AH30

AH8

AJ9

AK8

AL9

AM8

F30

F8

H10

H28

H30

H32

H6

H8

K30

K8

AG15

AG29

AJ7

AL7

AN7

G25

G17

G9

N7

Y7

AG7

C C

B B

VCORE

C34

C36

4.7u-0805

4.7u-0805

C64

4.7u-0805

VCORE

VCC_CORE6

VCC_CORE7

VCC_CORE8

VCC_CORE9

VCC_CORE10

VSS6

VSS7

VSS8

VSS9

VSS10

C87

4.7u-0805

7

AF14

AF18

AF22

AF26

VCC_CORE11

VCC_CORE12

VCC_CORE13

VCC_CORE14

VCC_CORE15

VSS11

VSS12

VSS13

VSS14

VSS15

AB8

AF12

AF16

AF20

AF24

C52

4.7u-0805

AM34

AK36

AK34

AK30

AK26

VCC_CORE16

VCC_CORE17

VCC_CORE18

VCC_CORE19

VCC_CORE20

VCC_CORE21

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

AM36

AK32

AK28

AK24

AK20

C83

4.7u-0805

AK22

AK18

AK14

AK10

AL5

VCC_CORE22

VCC_CORE23

VCC_CORE24

VCC_CORE25

VSS22

VSS23

VSS25

VSS26

AK16

AK12

AK4

AK2

AH36

AH26

AM30

AH22

AH18

AH14

VCC_CORE26

VCC_CORE27

VCC_CORE28

VCC_CORE29

VCC_CORE30

VCC_CORE31

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

AM32

AH34

AH32

AH28

AH24

C71

4.7u-0805

6

AH10

AH4

AH2

AF36

AF34

VCC_CORE32

VCC_CORE33

VCC_CORE34

VCC_CORE35

VCC_CORE36

VSS33

VSS34

VSS35

VSS37

VSS38

AH20

AH16

AH12

AF4

AF2

Near M8/P8

C51

4.7u-0805

AD6

AM26

AD4

AD2

AB36

VCC_CORE37

VCC_CORE38

VCC_CORE39

VCC_CORE40

VSS39

VSS40

VSS41

VSS42

AD36

AD34

AD32

AB6

AB4

AB34

AB32Z6Z4Z2X36

VCC_CORE41

VCC_CORE42

VCC_CORE43

VCC_CORE44

VCC_CORE45

VSS43

VSS44

VSS45

VSS46

VSS47

AB2

Z36

Z34

Z32X6AM28X4X2

VCORE

C29

39p

5

VCORE

X34

AM22

X32V6V4V2T36

VCC_CORE46

VCC_CORE47

VCC_CORE48

VCC_CORE49

VCC_CORE50

VCC_CORE51

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

V36

V34

C80

C43

39p

39p

T34

T32R6R4R2AM18

VCC_CORE52

VCC_CORE53

VCC_CORE54

VCC_CORE55

VSS54

VSS55

VSS56

VSS57

V32T6T4T2R36

C90

39p

P36

VCC_CORE56

VCC_CORE57

VCC_CORE58

VCC_CORE59

VCC_CORE60

VCC_CORE61

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

R34

AM24

R32P6P4P2M36

C68

39p

P34

P32M4M6M2K36

VCC_CORE62

VCC_CORE63

VCC_CORE64

VCC_CORE65

VSS64

VSS65

VSS66

VSS67

M34

M32K6K4K2AM20

C84

39p

4

K34

K32H4H2

VCC_CORE66

VCC_CORE67

VCC_CORE68

VCC_CORE69

VCC_CORE70

VCC_CORE71

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

H36

H34

C86

C61

39p

39p

AM14

F36

F34

F32

F28

VCC_CORE72

VCC_CORE73

VCC_CORE74

VCC_CORE75

VSS74

VSS75

VSS76

VSS77

F26

F22

F18

F14

F10F6F4F2AM16

C33

39p

F24

F20

F16

F12

D32

VCC_CORE76

VCC_CORE77

VCC_CORE78

VCC_CORE79

VCC_CORE80

VCC_CORE81

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

D36

C21

39p

3

0~100 mA, 2.25~2.75V

VCCA_PLL

D28

AM10

D24

D20

D16

D12D8D4D2B36

B32

AM2

B28

B24

B20

B16

B12B8B4

AJ5

AC7

AJ23

CPU1B

VCC_Z

VCC_A

AA31

NC1

AC31

NC2

VCC_CORE82

VCC_CORE83

VCC_CORE84

VCC_CORE85

VCC_CORE86

VCC_CORE87

VCC_CORE88

VCC_CORE89

VCC_CORE90

VCC_CORE91

VCC_CORE92

VCC_CORE93

VCC_CORE94

VCC_CORE95

VCC_CORE96

VCC_CORE97

VCC_CORE98

VCC_CORE99

VCC_CORE100

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

D34

D30

D26

D22

D18

D14

D10D6B34

AM12

B30

B26

B22

B18

B14

B10B6B2

AM4

AK6

C94

C7

C95

39p

39p

C70

39p

C48

39p

39p

F or VCORE output cap Alone VCORE edge

VCC_CORE101

NC3

NC6

NC7

NC8

NC9

NC10

NC11

NC12

NC13

NC15

NC16

NC17

NC18

NC19

NC20

NC21

NC22

NC23

NC24

NC25

NC27

NC28

NC29

NC30

NC31

NC32

NC33

NC34

NC35

NC36

NC37

NC42

NC43

NC44

NC45

BP0_CUT

BP1_CUT

BP2_CUT

BP3_CUT

VSS103

VSS104

VSS_Z

Socket 462

AM6

AE7

C10

39p

AE31

AG23

AG25

AG31

AG5

AJ11

AJ15

AJ17

AJ19

AJ27

AL11

AN11

AN9

G11

G13

G27

G29

G31

J31

J5

L31

N31

Q31

S31

S7

U31

U7

W31

W7

Y31

Y5

AG19

G21

AG21

G19

AN27

AL27

AN25

AL25

2

VCCA25

C69

C108

39p

39p

2.5V

VCCA_PLL

C74

C72

33P

0.1u

L15 600-0805

C58

X_10u-1206

C35

X_1000p

R60 0

R74 0

CPUTD {22,25}

Place Close to H/W monitor

Socket 462

XX1

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND GND

CPU1C

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

XX2

YY24

YY23

YY22

YY21

YY20

YY19

YY18

YY17

YY16

YY15

YY14

YY13

YY12

AO1

AO2

AO3

AO4

YY1

YY2

YY3

YY4

YY5

YY6

YY7

YY8

YY9

YY10 YY11

1

VCCA_PLL

C66

10u-0805

C28

0.22u

C60

0.22u

C89

0.22u

VCORE

C44

C78

0.01u

A A

0.01u

C73

0.22u

C41

0.01u

C27

0.22u

C56

0.01u

C88

0.22u

C81

0.22u

C32

0.22u

0.22u

C85

0.22u

C59

0.22u

C63

VCORE VCORE

C314

C316

C320

X_39p(S/S)

C315

X_39p(S/S)

C317

X_39p(S/S)

C318

X_39p(S/S)

X_39p(S/S)

X_39p(S/S)

C79

0.22u

C30

0.22u

C91

0.22u

C46

0.22u

C39

0.22u

C77

10u-1206

C62

0.22u

C31

0.22u

C38

10u-1206

C67

0.22u

C76

10u-1206

C47

0.22u

C26

10u-1206

C82

0.22u

C55

0.22u

Solder Side

MICRO-STAR INT'L CO.,LTD.

Title

Size Document Number Rev

Custom

8

7

6

5

4

3

Date: Sheet of

2

Socket 462 - 2

MS-6596

5 28Friday, November 22, 2002

3.0

1

8

HOST BUS

M18

AIN#2

E26

D D

AIN#3

AIN#4

AIN#5

AIN#6

AIN#7

AIN#8

AIN#9

AIN#10

AIN#11

AIN#12

AIN#13

AIN#14

AICLK#A

AOUT#[2:14]{4}

C C

AOCLK#{4}

DOCLK#[0:3]{4}

DIVAL#{4}

CFWDRST{4}

CONNECT{4}

PROCRDY{4}

CPUCLK1{3}

CPUCLK-1{3}

AOUT#2

AOUT#3

AOUT#4

AOUT#5

AOUT#6

AOUT#7

AOUT#8

AOUT#9

AOUT#10

AOUT#11

AOUT#12

AOUT#13

AOUT#14

-DICLK_0

-DICLK_1

-DICLK_2

-DICLK_3

DOCLK#0

DOCLK#1

DOCLK#2

DOCLK#3

S2KCOMP

B B

S2KVREF

VIDNB{26}

NB1_X

Heat Sink-High/Black

DICLK#[0:3]{4}

A A

8

AIN2

A25

AIN3

E24

AIN4

A26

AIN5

C25

AIN6

D25

AIN7

C24

AIN8

C23

AIN9

D23

AIN10

D26

AIN11

E23

AIN12

A24

AIN13

B23

AIN14

B25

AINCLK

W34

AOUT2

W33

AOUT3

Y32

AOUT4

AA32

AOUT5

W32

AOUT6

AB32

AOUT7

Y34

AOUT8

AA34

AOUT9

AB34

AOUT10

AB31

AOUT11

AA31

AOUT12

W31

AOUT13

AB33

AOUT14

AA33

AOUTCLK

B28

DICLK0

F33

DICLK1

L32

DICLK2

T34

DICLK3

C28

DOCLK0

F32

DOCLK1

K32

DOCLK2

T33

DOCLK3

A23

DIVAL

A22

CFWDRST

E22

CONNECT

C22

PROCRDY

K29

HCLK+

L29

HCLK-

G30

S2KCOMP

AA30

S2KVREF0

E25

S2KVREF1

AA29

VID

At The Center Between CPU & NB

DICLK#0

DICLK#1

DICLK#2 -DICLK_2

DICLK#3 -DICLK_3

AICLK#A

VTT

L18

A33

VTT

A20

A34

B33

B34

VTT

VTT

VTT

VTT

VSS

VSS

A32

B24

B27

L22 10nH

L18 10nH

L19 10nH

L16 10nH

L25 10nH

7

VTT

VSS

7

A21

B30

6

VCORE VCC2_5AVDD1

B20

B21

C20

C21

D20

D21

E20

E21

F20

F21

L20

L21

L22

L23

M20

M21

M22

M23

M24

N23

P23

P24

R23

R24

T23

T24

U23

U24

V23

VTT

VSS

B31

VTT

VSS

B32

VTT

VSS

C31

VTT

VSS

C33

VTT

VSS

C34

VTT

VSS

D24

VTT

VSS

D27

VTT

VSS

D30

VTT

VSS

D31

VTT

VSS

E33

VTT

VSS

E31

VTT

VSS

F27

VTT

VSS

N24

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

F26

H33

H31

H29

L33

L31

J29

M30

N30

P33

P31

P30

VTT

VSS

P29

VTT

VSS

R30

VTT

VSS

R29

VTT

VSS

T30

VTT

VSS

T29

VTT

VSS

U33

V24

VTT

VSS

U31

VCORE

L24 10nH

5PC113

L23 10nH

5PC109

L20 10nH

5PC107

L17 10nH

5PC98

L21 10nH

5PC118

-DICLK_0

-DICLK_1

AICLK# {4}

CB121

CB127

0.1u(S/S)

0.1u(S/S)

VCC2_5

CB138

CB123

0.1u(S/S)

0.1u(S/S)

6

W23

W24

AD29

AD30

VTT

VTT

VTT

VTT

VTT

VSS

VSS

VSS

VSS

VSS

B22

Y33

Y31

Y30

Solder Side

CB125

0.1u(S/S)

CB128

0.1u(S/S)

AD31

VTT

VSS

W30

AD32

VTT

VSS

D22

5

AD33

VTT

VSS

AC34

5

AD34

AE29

VTT

VSS

AC33

AC32

CB132

0.1u(S/S)

CB142

0.1u(S/S)

AE30

VTT

VSS

AC31

AE31

VTT

VSS

AC30

VTT

VSS

AE32

VTT

VSS

AC29

AE33

AE34

VTT

VTT

CB130

0.1u(S/S)

CB124

0.1u(S/S)

L19

M19

VTT

VTT

L30

H30

AGND1

F30

G29

K30

VTS2K

VDS2K

AVDD1

VSS2K

VT8377

CB133

X_0.1u(S/S)

CB141

0.1u(S/S)

NB1A

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D20

D21

D22

D23

D24

D25

D26

D27

D28

D29

D30

D31

D32

D33

D34

D35

D36

D37

D38

D39

D40

D41

D42

D43

D44

D45

D46

D47

D48

D49

D50

D51

D52

D53

D54

D55

D56

D57

D58

D59

D60

D61

D62

D63

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

A27

E29

A29

B29

A30

C29

C30

A31

C27

E27

C26

E28

A28

D28

B26

D29

D32

D34

E30

H32

J34

F31

G31

H34

C32

D33

G34

E34

E32

F34

G32

G33

J30

K31

M31

M32

N31

N34

M34

N33

J32

J31

J33

K34

L34

K33

N32

M33

R31

V32

V33

T32

V34

U34

V31

V30

P34

P32

R34

R33

R32

U30

T31

U32

CB135

0.1u(S/S)

CB137

0.1u(S/S)

4

SDATA#0

SDATA#1

SDATA#2

SDATA#3

SDATA#4

SDATA#5

SDATA#6

SDATA#7

SDATA#8

SDATA#9

SDATA#10

SDATA#11

SDATA#12

SDATA#13

SDATA#14

SDATA#15

SDATA#16

SDATA#17

SDATA#18

SDATA#19

SDATA#20

SDATA#21

SDATA#22

SDATA#23

SDATA#24

SDATA#25

SDATA#26

SDATA#27

SDATA#28

SDATA#29

SDATA#30

SDATA#31

SDATA#32

SDATA#33

SDATA#34

SDATA#35

SDATA#36

SDATA#37

SDATA#38

SDATA#39

SDATA#40

SDATA#41

SDATA#42

SDATA#43

SDATA#44

SDATA#45

SDATA#46

SDATA#47

SDATA#48

SDATA#49

SDATA#50

SDATA#51

SDATA#52

SDATA#53

SDATA#54

SDATA#55

SDATA#56

SDATA#57

SDATA#58

SDATA#59

SDATA#60

SDATA#61

SDATA#62

SDATA#63

4

CB139

0.1u(S/S)

SDATA#[0:63] {4}AIN#[2:14]{4}

S2KCOMP

R98 300RST

VIDNB

POWER/GROUND FOR

INTERNAL CPU CLOCK LOGIC

AVDD1

CP20

X_COPPER

VCC2_5

CB82

0.1u

CB66

CB75

0.1u

X_0.1u

VCORE

CB21

X_0.1u

CB47

CB20

X_0.1u

X_0.1u

S2KVREF

CB118

CB120

X_0.01u(S/S)

0.01u(S/S)

Solder

3

C1140.01u

VCC2_5

CB67

0.1u

CB28

X_0.1u

100RST(S/S)

R387

100RST(S/S)

3

FB1

X_300

CB116

0.01u(S/S)

Solder

CB54

0.1u

VCORE

R388

2

NB1D

Y29

VDD

W29

VDD

V29

VDD

U29

VDD

N29

VDD

M29

VDD

F29

VDD

F28

VDD

F25

VDD

F24

VDD

F23

VDD

F22

VDD

F16

VDD

F15

VDD

E16

VDD

E15

VDD

D16

VDD

D15

VDD

C16

VDD

C15

VDD

B16

VDD

B15

VDD

A16

VDD

A15

VDD

A17

VDD

B17

VDD

C17

VDD

D17

VDD

E17

VDD

F17

AD23

AD22

AD21

AD20

AD19

AD18

AD17

AD16

AD15

AD14

AD13

AD12

AC24

AC23

AC22

AC21

AC20

AC19

AC18

AC17

AC16

AC15

AC14

AC13

AC12

AC11

AB24

AB23

AB12

AB11

AA24

AA23

AA12

AA11

VDD

L13

VCC1

L14

VCC1

M13

VCC1

M14

VCC1

L16

VCC1

L15

VCC1

M16

VCC1

M15

VCC1

T12

VCC1

T11

VCC1

R12

VCC1

R11

VCC1

P12

VCC1

P11

VCC1

N12

VCC1

N11

VCC1

M12

VCC1

M11

VCC1

L12

VCC1

Y23

VCC3

Y24

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

Y12

VCC3

Y11

VCC3

VT8377

CB55

0.1u

CB119

0.1u(S/S)

Solder

CB29

X_0.01u

VDDQ

VCCM

MICRO-STAR INT'L CO.,LTD.

Title

Size Document Number Rev

Custom

Date: Sheet of

2

KT400 - 1

MS-6596

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

1

VCC2_5VCC2_5

U11

U12

V11

V12

W11

W12

B19

VSS

B18

VSS

L17

VSS

M17

VSS

AA21

VSS

AA20

VSS

AA19

VSS

AA18

VSS

AA17

VSS

AA16

VSS

AA15

VSS

AA14

VSS

Y21

VSS

Y20

VSS

Y19

VSS

Y18

VSS

Y17

VSS

Y16

VSS

Y15

VSS

Y14

VSS

W21

VSS

W20

VSS

W19

VSS

W18

VSS

W17

VSS

W16

VSS

W15

VSS

W14

VSS

V21

VSS

V20

VSS

V19

VSS

V18

VSS

V17

VSS

V16

VSS

V15

VSS

V14

VSS

U21

VSS

U20

VSS

U19

VSS

U18

VSS

U17

VSS

U16

VSS

U15

VSS

U14

VSS

T21

VSS

T20

VSS

T19

VSS

T18

VSS

T17

VSS

T16

VSS

T15

VSS

T14

VSS

R21

VSS

R20

VSS

R19

VSS

R18

VSS

R17

VSS

R16

VSS

R15

VSS

R14

VSS

P21

VSS

P20

VSS

P19

VSS

P18

VSS

P17

VSS

P16

VSS

P15

VSS

P14

VSS

F19

VSS

F18

VSS

E19

VSS

E18

VSS

D19

VSS

D18

VSS

C19

VSS

C18

VSS

A19

VSS

A18

VSS

3.0

6 28Friday, November 22, 2002

1

8

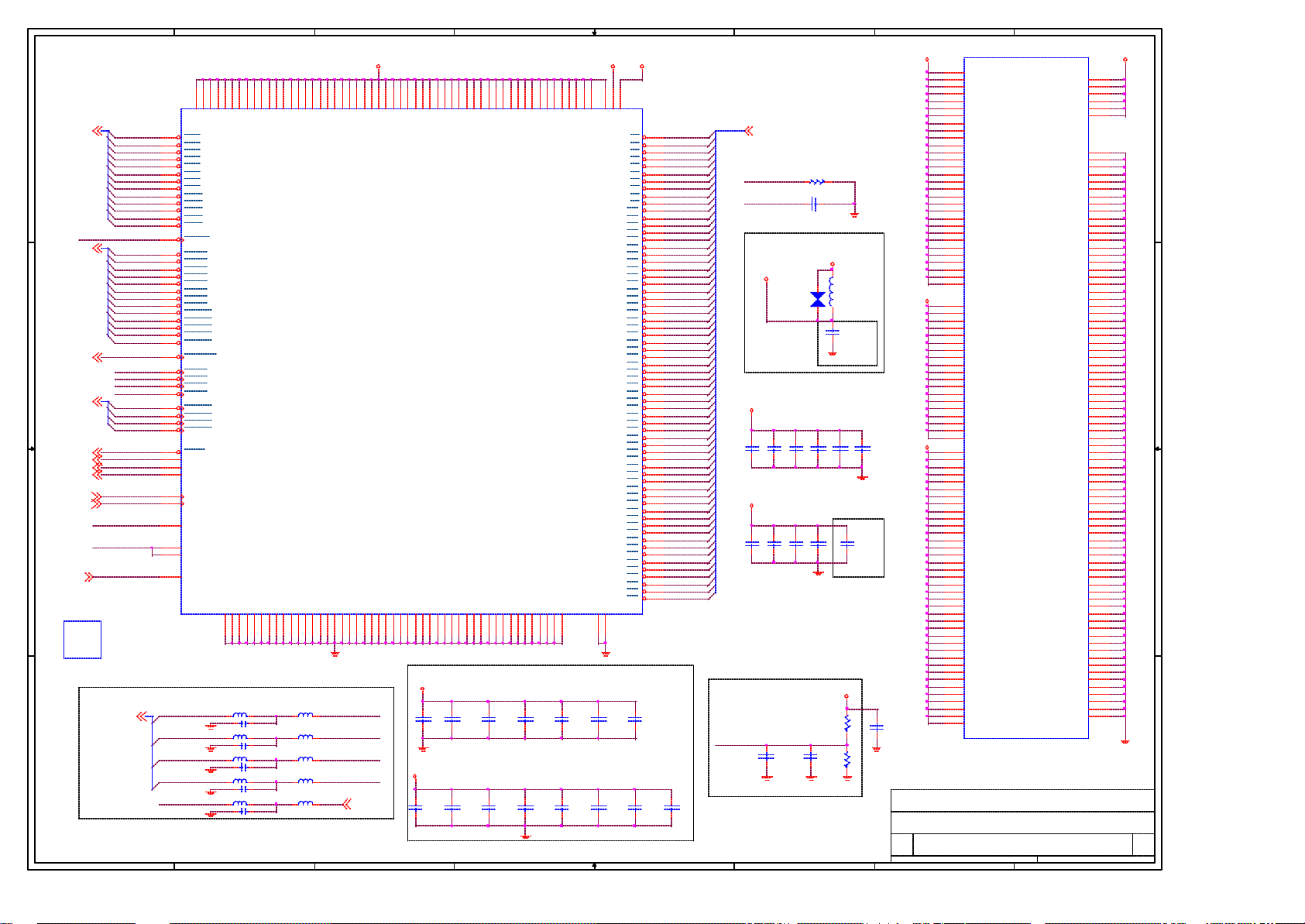

MEMORY

D D

MD_0

MD_1

MD_2

MD_3

MD_4

MD_5

MD_6

MD_7

MD_8

MD_9

MD_10

MD_11

MD_12

MD_13

MD_14

MD_15

MD_16

MD_17

MD_18

MD_19

MD_20

MD_21

MD_22

MD_23

MD_24

MD_25

MD_26

MD_27

MD_28

C C

MD_29

MD_30

MD_31

MD_32

MD_33

MD_34

MD_35

MD_36

MD_37

MD_38

MD_39

MD_40

MD_41

MD_42

MD_43

MD_44

MD_45

MD_46

MD_47

MD_48

MD_49

MD_50

MD_51

MD_52

MD_53

MD_54

MD_55

MD_56

B B

MD_57

MD_58

MD_59

MD_60

MD_61

MD_62

MD_63

-QDRRD

-QDRWR

MVREF0

GCKE

AK31

AM33

AN32

AP33

AK32

AL34

AN34

AP34

AP32

AM31

AM29

AM28

AN31

AP31

AN29

AP29

AN28

AP27

AM26

AP25

AP28

AM27

AM25

AN25

AM24

AN23

AP22

AM21

AP24

AP23

AN22

AP21

AM14

AN13

AP12

AM11

AP14

AP13

AN12

AP11

AN10

AP10

AM10

AK11

AK27

AJ28

AJ19

AJ12

AK29

AM9

AP8

AM8

AN7

AP7

AM7

AM6

AN4

AP3

AP6

AN6

AP4

AM4

AP1

AN3

AK1

AP2

AN1

AM2

AK2

VCCM VCC2_5 AVDD2 AVDD3

AG1

AG2

AG3

AG4

AG5

AG6

AH1

VCC3

VCC3

VCC3

VCC3

VCC3

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

AL1

MD58

MD59

MD60

MD61

MD62

MD63

QDRRD

QDRWR

MVREF0

MVREF1

MVREF2

AJ7

MVREF3

VCC3

GCKE

VCCM

VSS

VSS

VSS

VSS

VSS

A A

CB56

CB53

0.1u

0.1u

VSS

AJ8

AK18

8

VSS

VSS

AJ9

AJ15

AJ16

AJ20

AJ26

AJ27

AJ23

AH2

VCC3

VCC3

VSS

VSS

AJ29

AH3

AJ30

AH4

VCC3

VSS

AJ31

AH5

VCC3

VCC3

VSS

VSS

AJ32

AH6

AL2

AJ1

VCC3

VCC3

VSS

VSS

AL5

7

7

AJ2

AL8

AJ3

VCC3

VCC3

VSS

VSS

AL11

AJ4

VCC3

VSS

AL14

AJ5

VCC3

VSS

AL16

AJ6

VCC3

VSS

AL17

AF29

VCC3

VSS

AL18

AF30

VCC3

VSS

AL19

AF31

VCC3

VSS

AL21

AF32

VCC3

VSS

AL24

AF33

VCC3

VSS

AL27

AF34

VCC3

VSS

AL30

AG29

VCC3

VSS

AL33

AG30

VCC3

VSS

AK16

AG31

VCC3

VSS

AK19

AG32

VCC3

VSS

AN2

AG33

VCC3

VSS

AN5

AG34

VCC3

VSS

AN8

AH29

VCC3

VSS

AN11

AH30

VCC3

VSS

AN14

6

AH31

VCC3

VSS

AN17

6

AH32

VCC3

VSS

AN18

AH33

VCC3

VSS

AN21

AH34

VCC3

VSS

AN24

VSS

AN27

AJ10

VDD

VSS

AN30

AJ11

VDD

VSS

AN33

AJ13

AJ14

VDD

AJ33

AJ21

AJ22

VDD

VDD

AGND2

AGND3

AJ18

VDD

AJ24

AJ25

VDD

VDD

AJ34

AJ17

AVDD2

AVDD3

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

MAA13

MAA14

MAA15

MAB0

MAB1

MAB2

MAB3

MAB4

MAB5

MAB6

MAB7

MAB8

MAB9

MAB10

MAB11

MAB12

MAB13

MAB14

MAB15

MPD0/CKE0

MPD1/CKE1

MPD2/CKE2

MPD3/CKE3

MPD4/CKE4

MPD5/CKE5

MPD6/CKE6

MPD7/CKE7

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

DQM8

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

DCLKO

DCLKI

SRASA

SRASB

SCASA

SCASB

SWEA

SWEB

VT8377

CS0

CS1

CS2

CS3

CS4

CS5

CS6

CS7

NB1B

5

R96

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

-DQS_0

-DQS_1

-DQS_2

-DQS_3

-DQS_4

-DQS_5

-DQS_6

-DQS_7

RMA0

RMA1

RMA2

RMA3

RMA4

RMA5

RMA6

RMA7

RMA8

RMA9

RMA10

RMA11

RMA12

RMA13

RMA14

RMA15

DCLKO

DCLKI

22

AM15

AM16

AM18

AM20

AK20

AL23

AK22

AL25

AK24

AK26

AK15

AL12

AL13

AL28

AK30

AL31

AL15

AK17

AP17

AM19

AL20

AL22

AK21

AK25

AK23

AL26

AK14

AK12

AK13

AK28

AL29

AL32

AN19

AP19

AN15

AP15

AP20

AN20

AP16

AN16

AL7

AK5

AK6

AM5

AL4

AK4

AL3

AK3

AM32

AP30

AP26

AM22

AM12

AN9

AL6

AM3

AM17

AM34

AM30

AN26

AM23

AM13

AP9

AP5

AM1

AP18

AK33

AK34

AL9

AL10

AK7

AK9

AK10

AK8

VCCM

CB131

0.1u(S/S)

Solder Side

5

RMA[15:0] {9,10}

C11710p

C12010p

CKE0 {9,10}

CKE1 {9,10}

CKE2 {9,10}

CKE3 {9,10}

RCS-0 {9,10}

RCS-1 {9,10}

RCS-2 {9,10}

RCS-3 {9,10}

DCLKO {3}

DCLKI {3}

RSRAS# {9,10}

RSCAS# {9,10}

RSWE# {9,10}

CB134

0.1u(S/S)

4

CB126

0.1u(S/S)

4

POWER FOR DRAM CLCOK

DESKEW CIRCUIT

AVDD2 VCC2_5

CP21

X_COPPER

CB117

1u(S/S)

Solder

POWER FOR DDR DLL CIRCUIT

VCC2_5AVDD3

CP22

X_COPPER

CB122

1u(S/S)

Solder

SSTL_2 RECEIVER VREF FOR DDR

MVREF0

CB43

CB42

1000p

0.1u

RMA0

C331 X_33p(S/S)

RMA1

C330 X_33p(S/S)

RMA2

C329 X_33p(S/S)

RMA3

C328 X_33p(S/S)

RMA4

C327 X_33p(S/S)

RMA5

C325 X_33p(S/S)

RMA6

C326 X_33p(S/S)

RMA7

C323 X_33p(S/S)

RMA8

C324 X_33p(S/S)

RMA9

C322 X_33p(S/S)

RMA10

C332 X_33p(S/S)

RMA11

C334 X_33p(S/S)

RMA12

C333 X_33p(S/S)

RMA13

C321 X_33p(S/S)

RMA14

C319 X_33p(S/S)

RMA15

C341 X_33p(S/S)

RSRAS#

C336 X_33p(S/S)

RSCAS#

C338 X_33p(S/S)

RSWE#

C337 X_33p(S/S)

Solder

CB140

0.1u(S/S)

CB129

0.1u(S/S)

CB136

0.1u(S/S)

FB2

X_300

FB3

X_300

3

VCC2_5

CB143

0.1u(S/S)

3

2

Place these damping resistors close to DIMM1

MD_4

1 2

R92

1KST

R91

1KST

MD_0

MD_5

MD_1

MD_2

MD_6

MD_7

MD_3

MD_8

MD_9

MD_12

MD_13

MD_10

MD_15

MD_14

MD_11

MD_20

MD_16

MD_17

MD_21

MD_18

MD_19

MD_22

MD_23

MD_28

MD_24

MD_25

MD_29

MD_26

MD_30

MD_27

MD_31

MD_42

MD_43

MD_46

MD_47

MD_40

MD_44

MD_45

MD_41

MD_36

MD_32

MD_33

MD_37

MD_34

MD_38

MD_39

MD_35

MD_48

MD_49

MD_52

MD_53

MD_54

MD_50

MD_55

MD_51

MD_60

MD_56

MD_61

MD_57

MD_62

MD_58

MD_63

MD_59

-DQS_0

-DQS_1

-DQS_2

-DQS_3

-DQS_4

-DQS_5

-DQS_6

-DQS_7

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

-QDRRD

-QDRWR

GCKE

RN13

3 4

22-8P4R

5 6

7 8

1 2

RN18

3 4

22-8P4R

5 6

7 8

1 2

RN19

3 4

22-8P4R

5 6

7 8

1 2

RN25

3 4

22-8P4R

5 6

7 8

1 2

RN29

3 4

22-8P4R

5 6

7 8

1 2

RN33

3 4

22-8P4R

5 6

7 8

1 2

RN36

3 4

22-8P4R

5 6

7 8

1 2

RN39

3 4

22-8P4R

5 6

7 8

1 2

RN54

3 4

22-8P4R

5 6

7 8

1 2

RN50

3 4

22-8P4R

5 6

7 8

1 2

RN45

3 4

22-8P4R

5 6

7 8

1 2

RN48

3 4

22-8P4R

5 6

7 8

1 2

RN56

3 4

22-8P4R

5 6

7 8

1 2

RN60

3 4

22-8P4R

5 6

7 8

1 2

RN62

3 4

22-8P4R

5 6

7 8

1 2

RN65

3 4

22-8P4R

5 6

7 8

R49

R75

R84 22

R89 22

R116

R127

R141 22

R152

R55

R76

R86 22

R90 22

R117

R129

R140 22

R153

R130 4.7K

R389 X_4.7K(S/S)

R390 X_4.7K(S/S)

MICRO-STAR INT'L CO.,LTD.

Title

Size Document Number Rev

Custom

Date: Sheet of

2

RMD4

RMD0

RMD5

RMD1

RMD2

RMD6

RMD7

RMD3

RMD8

RMD9

RMD12

RMD13

RMD10

RMD15

RMD14

RMD11

RMD20

RMD16

RMD17

RMD21

RMD18

RMD19

RMD22

RMD23

RMD28

RMD24

RMD25

RMD29

RMD26

RMD30

RMD27

RMD31

RMD42

RMD43

RMD46

RMD47

RMD40

RMD44

RMD45

RMD41

RMD36

RMD32

RMD33

RMD37

RMD34

RMD38

RMD39

RMD35

RMD48

RMD49

RMD52

RMD53

RMD54

RMD50

RMD55

RMD51

RMD60

RMD56

RMD61

RMD57

RMD62

RMD58

RMD63

RMD59

22

22

22

22

22

22

22

22

22

22

Solder

RDQS0

RDQS1

RDQS2

RDQS3

RDQS4

RDQS5

RDQS6

RDQS7

RDQM0

RDQM1

RDQM2

RDQM3

RDQM4

RDQM5

RDQM6

RDQM7

VCCM

KT400 - 2

MS-6596

1

RMD[63:0] {9,10}

RDQS[7:0] {9,10}

RDQM[7:0] {9,10}

7 28Friday, November 22, 2002

1

3.0

8

AGP,VLINK

7

VDDQ

6

5

VCC25SBY

4

3

2

1

PWROK

RESET

SUS_ST

TESTIN

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VPAR

LVREF

LCOMPP

UPCMD

DNCMD

DNSTB

DNSTB

UPSTB

UPSTB

Y4

VSUS25

NMI

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VD0

VD1

VD2

VD3

VD4

VD5

VD6

VD7

VBE

NB1C

AB4

AA5

AB5

AB29

AB30

F11

F12

F13

F14

G6

H6

L6

M6

V6

W6

Y6

AA6

AC1

AC2

AC3

AC4

AC5

AC6

AD1

AD2

AD3

AD4

AD5

AD6

V3

V1

AA3

AA1

U1

U3

AB2

AB1

W2

U2

W4

Y5

AB3

Y3

W1

W3

Y1

Y2

-TESTIN

NMI_NB

LVREF_NB

LCOMPP

PWRGD_NB {12,13}

PCIRST1# {22,24}

SUSST# {13}

VCC2_5

VLAD0 {12}

VLAD1 {12}

VLAD2 {12}

VLAD3 {12}

VLAD4 {12}

VLAD5 {12}

VLAD6 {12}

VLAD7 {12}

-VBE {12}

VPAR {12}

UPCMD {12}

DNCMD {12}

DNSTB+ {12}

DNSTB- {12}

UPSTB+ {12}

UPSTB- {12}

VLINK

1. VLINK REFERENCE VOLTAGE - 0.9V

LVREF_NB

CB71

0.01u

CB72

X_0.1u

VCC2_5

R155

3KST

R154

1KST

2. VLINK P-CHANNEL COMPENSATION

LCOMPP

R147 360RST

-TESTIN

PIPE#

R122 4.7K

R142 X_0

NMI_SB{12}

R64

X_4.7K

VCC3

VCC2_5

VDDQ

B

Q6

X_NPN-3904LT1-SOT23

C

E

R65 0

AGP

1. AGPVREF (PROVIDED BY AGP 4X

CARD OR BY SYSTEM FOR OTHERS)

AVREFGC

CB81

1u

2. AGPNCOMP : AGP N-CHANNEL

COMPENSATION

AGPNCOMP

R149 60.4RST

3. AGP POWER : VCCAGP

VDDQ

C143

C187

X_1u-0805

C340

0.1u(S/S)

C139

0.1u

C164

0.1u

X_1u-0805

VDDQ

C339

0.1u(S/S)

Solder Side

VCC3

R73

X_4.7K

NMI_NB

X_NPN-3904LT1-SOT23

R77

X_4.7K

VCC3

B

C

B

E

C

X_NPN-3904LT1-SOT23

Q9

E

VDDQ

CB77

CB69

X_0.1u

0.1u

C136

0.1u

NMI {4}

Q8

J6

D D

C C

B B

AAD[31:0]{11}

SBA[7:0]{11}

ADSTB#0{11}

ADSTB#1{11}

DBIH_PIPE{11}

AFRAME#{11}

ADEVSEL#{11}

AGPCLK0{3}

AVREFGC{11}

AAD0

AAD1

AAD2

AAD3

AAD4

AAD5

AAD6

AAD7

AAD8

AAD9

AAD10

AAD11

AAD12

AAD13

AAD14

AAD15

AAD16

AAD17

AAD18

AAD19

AAD20

AAD21

AAD22

AAD23

AAD24

AAD25

AAD26

AAD27

AAD28

AAD29

AAD30

AAD31

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

ACBE#0{11}

ACBE#1{11}

ACBE#2{11}

ACBE#3{11}

ADSTB0{11}

ADSTB1{11}

SBSTB{11}

SBSTB#{11}

DBIL{11}

AIRDY#{11}

ATRDY#{11}

ASTOP#{11}

APAR{11}

PIPE#

RBF#{11}

WBF#{11}

AREQ#{11}

AGNT#{11}

ASERR{11}

AGP8X#{11}

ST0{11}

ST1{11}

ST2{11}

AGPNCOMP

A10

B14

A14

A13

C14

A11

C11

C10

B11

B12

A12

E10

D11

E11

E14

D14

E12

C13

D12

C12

F10

M1

L1

K2

K1

K3

J1

J2

J3

F1

G3

F2

F3

E1

D1

D2

D3

C5

D6

A4

B5

A5

E7

B6

A6

B8

A8

D8

C8

A9

C9

B9

H1

B1

A3

A7

G2

G1

C6

C7

E8

E9

E3

F4

G4

H3

L3

D9

J4

M2

K5

J5

VCCQQ

GD0

GD1

GD2

GD3

GD4

GD5

GD6

GD7

GD8

GD9

GD10

GD11

GD12

GD13

GD14

GD15

GD16

GD17

GD18

GD19

GD20

GD21

GD22

GD23

GD24

GD25

GD26

GD27

GD28

GD29

GD30

GD31

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

C/BE0

C/BE1

C/BE2

C/BE3

AD_STBF0

AD_STBS0

AD_STBF1

AD_STBS1

SB_STBF

SB_STBS

DBIH

DBIL

GFRAME

GIRDY

GTRDY

GDEVSEL

GSTOP

GPAR

PIPE

RBF

WBF

GREQ

GGNT

GSERR

AGP8XDET

ST0

ST1

ST2

GCLK

AGPCOMP

AGPVREF0

AGPVREF1

A1A2B2B3C2C3C4D4D5E5E6F5F6F7F8N4N5N6P1P2P3P4P5P6R1R2R3R4R5

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

N1N2N3

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

R6

VCC1

VCC1

A A

8

VSSQQ

K6

T1

VSS

VSS

B4B7B10

VSS

7

VSS

VSS

B13C1D7

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

D10

D13E2E4

E13F9G5H2H4H5K4L2L5M3T2T3T4T5T6U4U5U6V2V4V5W5AA2

L4

M4

M5

6

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AA4

VSS

AB6

VSS

AE1

VSS

AE2

VSS

AE3

5

VSS

AE4

VSS

AE5

VSS

AE6

VSS

AF1

VSS

AF2

VSS

AF3

VSS

AF4

VSS

AF5

VSS

AF6

VSS

VT8377

MICRO-STAR INT'L CO.,LTD.

Title

Size Document Number Rev

Custom

4

3

Date: Sheet of

2

KT400 - 3

MS-6596

8 28Friday, November 22, 2002

1

3.0

8

7

6

5

4

3

2

1

MEMORY

VDDQ

VDDQ

VSS

VSS

VDDQ

VDDQ

VSS

VSS

VDDQ

VDDQ

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VREF

VDDID

SDA

VSS

VSS

WP

SCL

SA0

SA1

SA2

15223054627796

VDDQ

VDDQ

VSS

VSS

3111826344250586674818993

DIMM1

RMD[63:0] {7,10}

RMD0

2

RMD1

4

RMD2

6

RMD3

8

RMD4

94

RMD5

95

RMD6

98

RMD7

99

RMD8

12

RMD9

13

RMD10

19

RMD11

20

RMD12

105

RMD13

106

RMD14

109

RMD15

110

RMD16

23

RMD17

24

RMD18

28

RMD19

31

RMD20

114

RMD21

117

RMD22

121

RMD23

123

RMD24

33

RMD25

35

RMD26

39

RMD27

40

RMD28

126

RMD29

127

RMD30

131

RMD31

133

RMD32

53

RMD33

55

RMD34

57

RMD35

60

RMD36

146

RMD37

147

RMD38

150

RMD39

151

RMD40

61

RMD41

64

RMD42

68

RMD43

69

RMD44

153

RMD45

155

RMD46

161

RMD47

162

RMD48

72

RMD49

73

RMD50

79

RMD51

80

RMD52

165

RMD53

166

RMD54

170

RMD55

171

RMD56

83

RMD57

84

RMD58

87

RMD59

88

RMD60

174

RMD61

175

RMD62

178

RMD63

179

DDRVREF DDRVREF

1

82

90

92

SMBDAT SMBDAT

91

181

182

183

RCS-2{7,10}

RCS-3{7,10}

CKE2{7,10}

CKE3{7,10}

DDRCLK3{3}

DDRCLK1{3}

DDRCLK5{3}

DDRCLK-3{3}

DDRCLK-1{3}

DDRCLK-5{3}

DDR DIMM

104

112

128

136

143

156

164

172

180738467085108

VDD

VDD

VDD

VDD

VDD

VDD

VSS

160

VSS

152

VSS

145

VSS

139

VSS

132

VSS

124

VDDQ

VSS

116

D D

RMA[15:0]{7,10}

RDQM[7:0]{7,10}

C C

RDQS[7:0]{7,10}

VCCM

R38

1KST

R41

1KST

PUT NEAR DIMM 30mils

B B

Trace/45mils Space

A A

CB9

X_0.01u

CB11

X_0.01u

DDRVREF

RSRAS#{7,10}

RSCAS#{7,10}

DDRCLK2{3}

DDRCLK0{3}

DDRCLK4{3}

DDRCLK-2{3}

DDRCLK-0{3}

DDRCLK-4{3}

CB7

0.01u

RSRAS# RSRAS# RMD59

RSCAS# RSCAS# RMD60

RSWE# RSWE# RMD61

RSWE#{7,10}

RCS-0{7,10}

RCS-1{7,10}

CKE0 WP CKE2

CKE0{7,10}

CKE1 SMBCLK CKE3 SMBCLK

CKE1{7,10}

120

VDD

148

VDD

168

VDD

184

VCC3 VCC3

RMA0 RMD4

RMA1 RMD5

RMA2 RMD6

RMA3 RMD7

RMA4 RMD8

RMA5 RMD9

RMA6 RMD10

RMA7 RMD11

RMA8 RMD12

RMA9 RMD13

RMA10 RMD14

RMA13 RMD15

RMA14 RMD16

RMA15

RMA11 RMA11 RMD19

RMA12

RDQM0 RMD23

RDQM1 RMD24

RDQM2 RMD25

RDQM3 RMD26

RDQM4 RMD27

RDQM5 RMD28

RDQM6 RMD29

RDQM7 RMD30

RDQS0

RDQS1

RDQS2

RDQS3

RDQS4

RDQS5

RDQS6

RDQS7

48

43

41

130

37

32

125

29

122

27

141

118

115

167

59

52

113

97

107

119

129

149

159

169

177

140

14

25

36

56

67

78

86

47

44

45

49

51

134

135

142

144

10

101

102

173

103

154

65

63

157

158

71

163

21

111

137

16

76

138

17

75

5

9

VDDSPD

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

BA0

BA1

BA2

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

NC

NC(RESET#)

NC

NC

NC

NC(FETEN)

RAS#

CAS#

WE#

S0#

S1#

NC(S2#)

NC(S3#)

CKE0

CKE1

CK0

CK1

CK2

CK0#

CK1#

CK2#

176

VDDQ

VDDQ

VSS

VSS

100

VDDQ

VDDQ

VDDQ

addr =

1010000b

VSS

VSS

VSS

VDDQ

VDDQ

VSS

VSS

VCCMVCCM

VDDQ

VDDQ

VSS

VSS

VDDQ

VDDQ

VSS

VSS

VDDQ

VDDQ

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VREF

VDDID

VSS

VSS

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

WP

SCL

SDA

SA0

SA1

SA2

15223054627796

VDDQ

VDDQ

VSS

VSS

3111826344250586674818993

DIMM2

2

4

6

8

94

95

98

99

12

13

19

20

105

106

109

110

23

24

28

31

114

117

121

123

33

35

39

40

126

127

131

133

53

55

57

60

146

147

150

151

61

64

68

69

153

155

161

162

72

73

79

80

165

166

170

171

83

84

87

88

174

175

178

179

1

82

90

92

91

181

182

183

DDR DIMM

RMD0

RMD1

RMD2

RMD3

RMD17

RMD18

RMD20

RMD21

RMD22

RMD31

RMD32

RMD33

RMD34

RMD35

RMD36

RMD37

RMD38

RMD39

RMD40

RMD41

RMD42

RMD43

RMD44

RMD45

RMD46

RMD47

RMD48

RMD49

RMD50

RMD51

RMD52

RMD53

RMD54

RMD55

RMD56

RMD57

RMD58

RMD62

104

112

128

136

143

156

164

172

180738467085108

VDD

VDD

VDD

VDD

VDD

VDD

VSS

160

VSS

152

VSS

145

VSS

139

VSS

132

VSS

124

VDDQ

VSS

116

120

VDD

148

VDD

168

VDD

184

RMA0

RMA1

RMA2

RMA3

RMA4

RMA5

RMA6

RMA7

RMA8

RMA9

RMA10

RMA13

RMA14

RMA15

RMA12

RDQM0

RDQM1

RDQM2

RDQM3

RDQM4

RDQM5

RDQM6

RDQM7

RDQS0

RDQS1

RDQS2

RDQS3

RDQS4

RDQS5

RDQS6

RDQS7

RCS-2 RMD63

RCS-3

48

43

41

130

37

32

125

29

122

27

141

118

115

167

59

52

113

97

107

119

129

149

159

169

177

140

14

25

36

56

67

78

86

47

44

45

49

51

134

135

142

144

10

101

102

173

103

154

65

63

157

158

71

163

21

111

137

16

76

138

17

75

5

9

VDDSPD

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

BA0

BA1

BA2

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

NC

NC(RESET#)

NC

NC

NC

NC(FETEN)

RAS#

CAS#

WE#

S0#

S1#

NC(S2#)

NC(S3#)

CKE0

CKE1

CK0

CK1

CK2

CK0#

CK1#

CK2#

176

VDDQ

VDDQ

VSS

VSS

100

VDDQ

VDDQ

VDDQ

addr =

1010001b

VSS

VSS

VSS

VDDQ

VDDQ

VSS

VSS

R156 4.7K

WP

VCC3

VCC3

SMBCLK {3,13,24}

SMBDAT {3,13,24}

DIMM

DECOUPLING

VCCM

CB59 0.1u

CB52 0.1u

CB65 0.1u

CB49 0.1u

CB17 0.1u

CB10 0.1u

CB44 0.1u

CB23 0.1u

CB40 0.1u

CB38 0.1u

MICRO-STAR INT'L CO.,LTD.

Title

Size Document Number Rev

Custom

8

7

6

5

4

3

Date: Sheet of

2

DDR1 & DDR2

MS-6596

9 28Friday, November 22, 2002

3.0

1

8

7

6

5

4

3

2

1

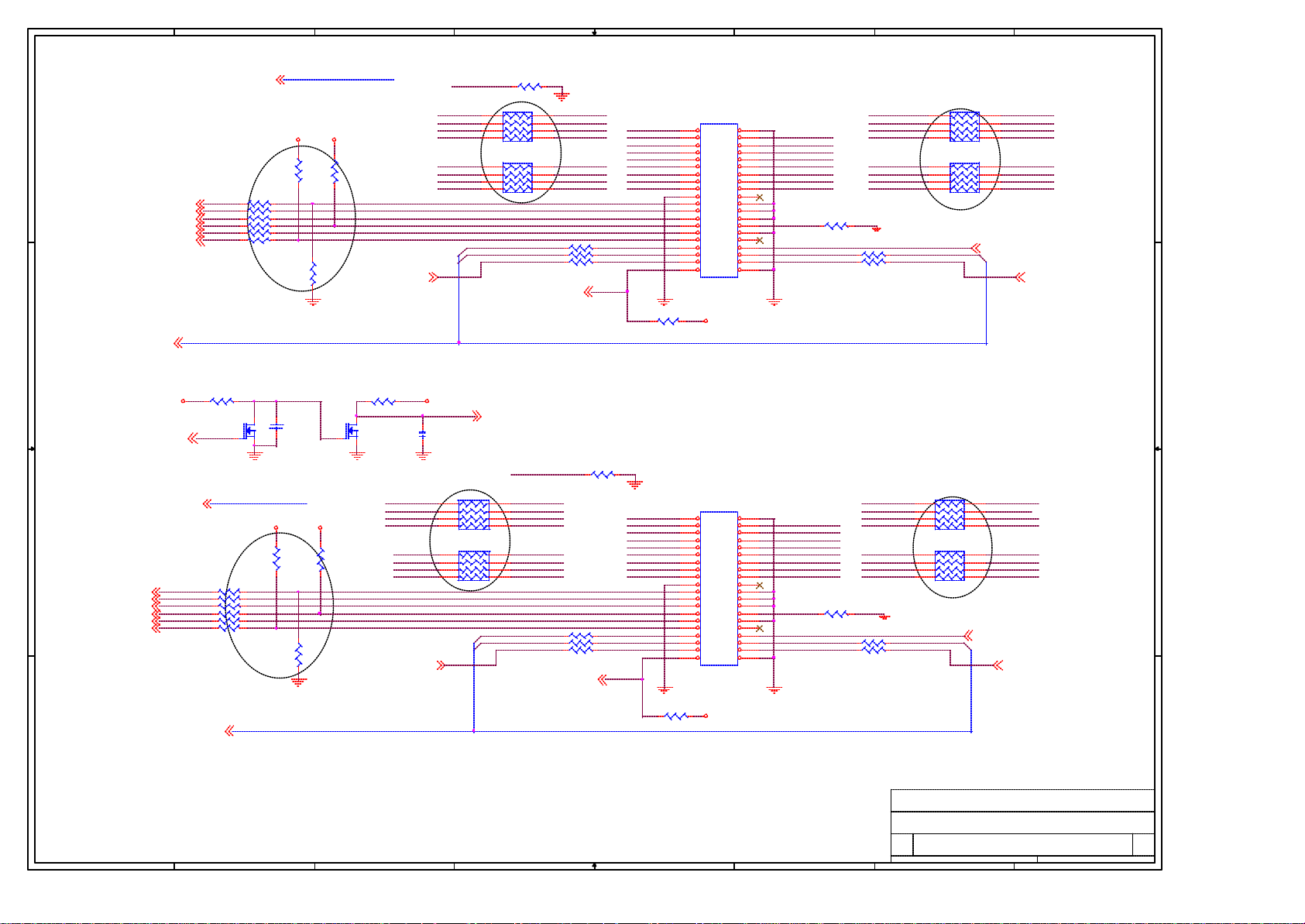

SSTL-2 Termination Resistors

RMD[63:0] {7,9}

RDQM[7:0] {7,9}

RDQS[7:0] {7,9}

D D

RMA[15:0] {7,9}

MD/DQM(/DQS)

MA/Control

CKE

SDR

LV-CMOS

LV-CMOS 10

LV-CMOS

OD 3.3V

DDR

Rs

0/10/- 10

SSTL-2

SSTL-2

0

SSTL-2

OD 2.5V

Rs

Rtt

47

47

0

47

0CS

DDR_VTT

RMD1

RMD5

RMD4

RMD0

RMD6

RMD2

RDQM0

RDQS0

RMD9 RSRAS#

RMD8

RMD3

RMD7

RDQM1

RMD13

RMD12

C C

B B

RMD11

RMD10

RMD15

RMD14

RDQM2

RMA13

RDQS2

RMD21

RMD17

RMA14

RMD16

RMD20

RMA5

RMD23

RMD19

RMA8

RMD31

RMD26

RMA3

RMD30

RMA4

RDQS3

RDQM3

RMD29

RMA7

RMD22

RMD18

RMA9

RMD25

RMD28

RMD24

RMA6

RMA0

RMA1

RMA2

RMD27

RMD39

RMA11

RMD38

RMD34

RN9 33-8P4R12

RN12 33-8P4R12

RN15 33-8P4R12

RN17 33-8P4R12

RN20 33-8P4R12

RN28 33-8P4R12

RN26 33-8P4R12

RN34 33-8P4R12

RN40 33-8P4R12

RN38 33-8P4R12

RN31 33-8P4R12

RN35 33-8P4R12

RN42 33-8P4R12

RN46 33-8P4R12

34

56

78

34

56

78

34

56

78

34

56

78

34

56

78

34

56

78

34

56

78

34

56

78

34

56

78

34

56

78

34

56

78

34

56

78

34

56

78

34

56

78

RMD36

RMD32

RMA12

RMA10

RDQM4

RDQS4

RMD37

RMD33

RSRAS#{7,9}

RMD44

RMD40

RMD35

RMD49

RMD48RDQS1

RMD47

RMD43

RCS-1{7,9}

RCS-3{7,9}

RCS-2{7,9}

RSCAS#{7,9}

RMA15

RMD53

RMD52

RMD50

RMD54

RDQS6

RDQM6

RMD59

RMD63

RMD58

RMD62

RMD56

RMD60

RMD51

RMD55

RDQS7

RDQM7

RMD57

RMD61

RMD46

RMD42

RDQS5

RDQM5

RCS-0{7,9}

RMD41

RMD45

RSWE#

RSWE#{7,9}

CKE1{7,9}

CKE3{7,9}

CKE0{7,9}

CKE2{7,9}

RN43 33-8P4R12

RN44 33-8P4R12

RN47 33-8P4R12

RN55 33-8P4R12

RN51 33-8P4R12

RN57 33-8P4R12

RN58 33-8P4R12

RN64 33-8P4R12

RN61 33-8P4R12

RN63 33-8P4R12

RN53 33-8P4R

RN49 33-8P4R12

RN22 33-8P4R

DDR_VTT

DDR_VTT

34

56

78

34

56

78

34

56

78

34

56

78

34

56

78

34

56

78

34

56

78

34

56

78

34

56

78

34

56

78

12

34

56

78

34

56

78

78

56

34

12

CB58

10u-0805

CB24

10u-0805

CB64

10u-0805

CB8

10u-0805

CB74

0.1u

CB22

0.1u

CB18

0.1u

CB12

0.1u

CB19

0.1u

CB25

0.1u

DDR_VTT DDR_VTT

CB73

0.1u

CB68

0.1u

CB62

0.1u

CB60

0.1u

CB70

0.1u

CB63

0.1u

CB61

0.1u

CB57

0.1u

CB41

0.1u

CB34

0.1u

CB45

0.1u

CB36

10u-0805

CB16

10u-0805

CB48

0.1u

CB39

0.1u

CB37

0.1u

CB35

0.1u

CB14

0.1u

CB50

0.1u

CB51

0.1u

DDR_VTT DDR_VTT

CB154

0.1u

CB156

0.1u

CB158

0.1u

CB160

0.1u

CB162

0.1u

CB166

0.1u

CB167

0.1u

CB168

0.1u

CB155

0.1u

CB157

0.1u

CB159

0.1u

CB161

0.1u

CB163

0.1u

A A

MICRO-STAR INT'L CO.,LTD.

Title

Size Document Number Rev

Custom

8

7

6

5

4

3

Date: Sheet of

DDR TERMINATOR

2

MS-6596

10 28Friday, November 22, 2002

3.0

1

8

D D

C C

B B

7

OVRCNT#

INTB#{12,15}

AGPCLK1{3}

AREQ#{8}

ST0 ST1

ST0{8}

ST2

ST2{8}

RBF#{8}

DBIL

SBA0 SBA1

VCC3

SBA2 SBA3

SBSTB{8}

SBA4 SBA5

SBA6 SBA7

DBIL

DBIL{8}

ADSTB1{8}

ACBE#2{8}

VCC3SBY

AAD31 AAD30

AAD29 AAD28

AAD27 AAD26

AAD25 AAD24

ADSTB1 ADSTB#1

AAD23 ACBE#3

AAD21

AAD19 AAD20

AAD17 AAD18

ACBE#2 AAD16

AIRDY#{8}

VDDQ

ADEVSEL#{8}

ACBE#1{8}

ADSTB0{8}

APERR#

ASERR{8}

ACBE#1

AAD14 AAD13

AAD12 AAD11

AAD10 AAD9

AAD8 ACBE#0

ADSTB0 ADSTB#0

AAD7 AAD6

AAD5 AAD4

AAD3 AAD2

AAD1 AAD0

AVREFCG

6

SBA[7:0]{8}

AAD[31:0]{8}

AGP1

B1

OVRCNT#

B2

5V

B3

5V

B4

USB+

B5

GND

B6

INTB#

B7

CLK

B8

REQ#

B9

VCC3.3

B10

ST0

B11

ST2

B12

RBF#

B13

GND

B14

RSVD(REFCLK)

B15

SBA0

B16

VCC3.3

B17

SBA2

B18

SB_STB

B19

GND

B20

SBA4

B21

SBA6

B22

RSVD(DBIL)

B23

GND

B24

3.3VAUX

B25

VCC3.3

B26

AD31

B27

AD29

B28

VCC3.3

B29

AD27

B30

AD25

B31

GND

B32

AD_STB1

B33

AD23

B34

VDDQ

B35

AD21

B36

AD19

B37

GND

B38

AD17

B39

C/BE#2

B40

VDDQ

B41

IRDY#

B42

3.3VAUX

B43

GND

B44

RSVD(CSYNC)

B45

VCC3.3

B46

DEVSEL#

B47

VDDQ

B48

PERR#

B49

GND

B50

SERR#

B51

C/BE1#

B52

VDDQ

B53

AD14

B54

AD12

B55

GND

B56

AD10

B57

AD8

B58

VDDQ

B59

AD_STB0

B60

AD7

B61

GND

B62

AD5

B63

AD3

B64

VDDQ

B65

AD1

B66

VREFCG

AIMM-D132-BN, 1.5V only

5

TYPEDET#