5

4

MS-6561 VER:1.0

3

2

1

D D

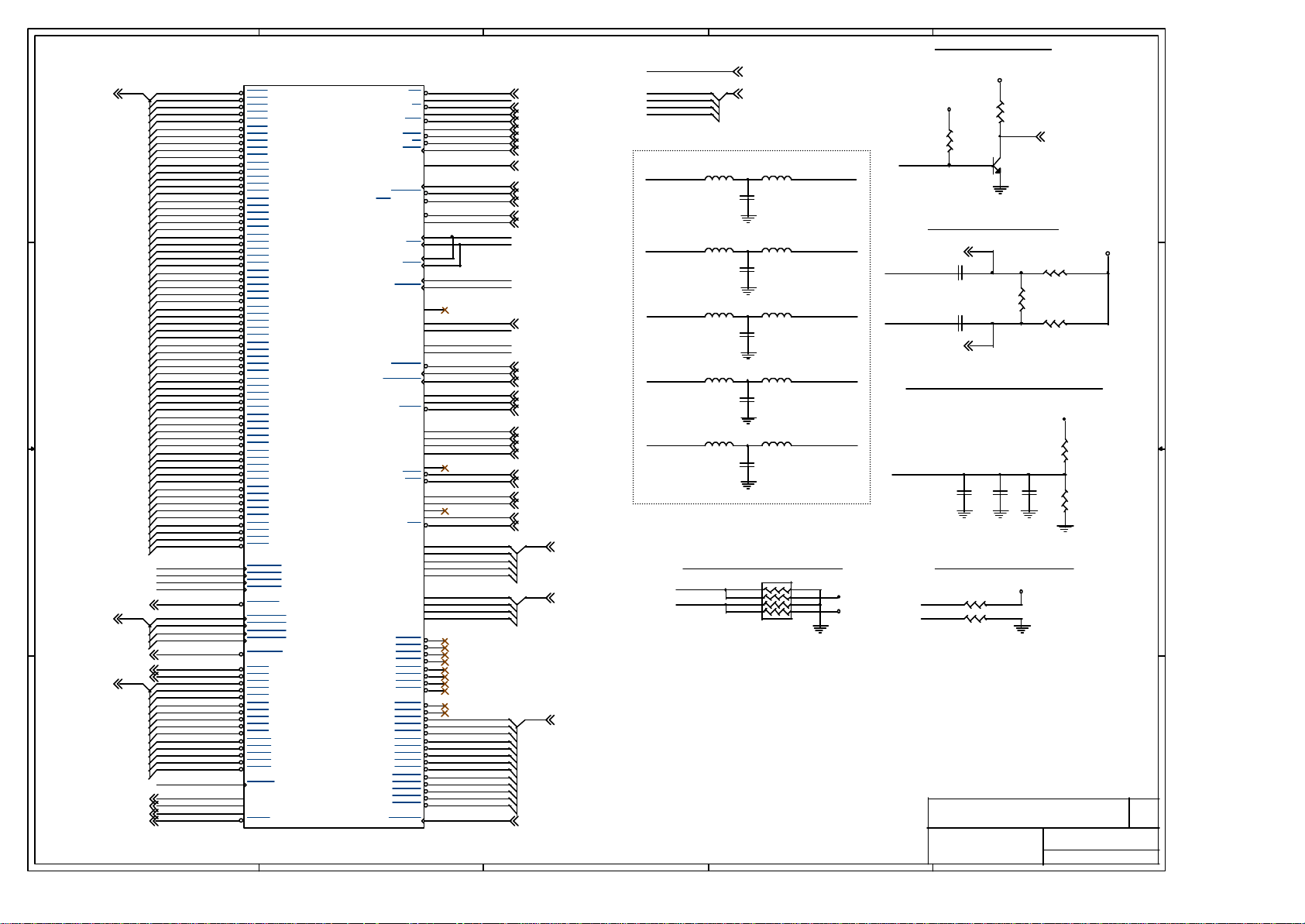

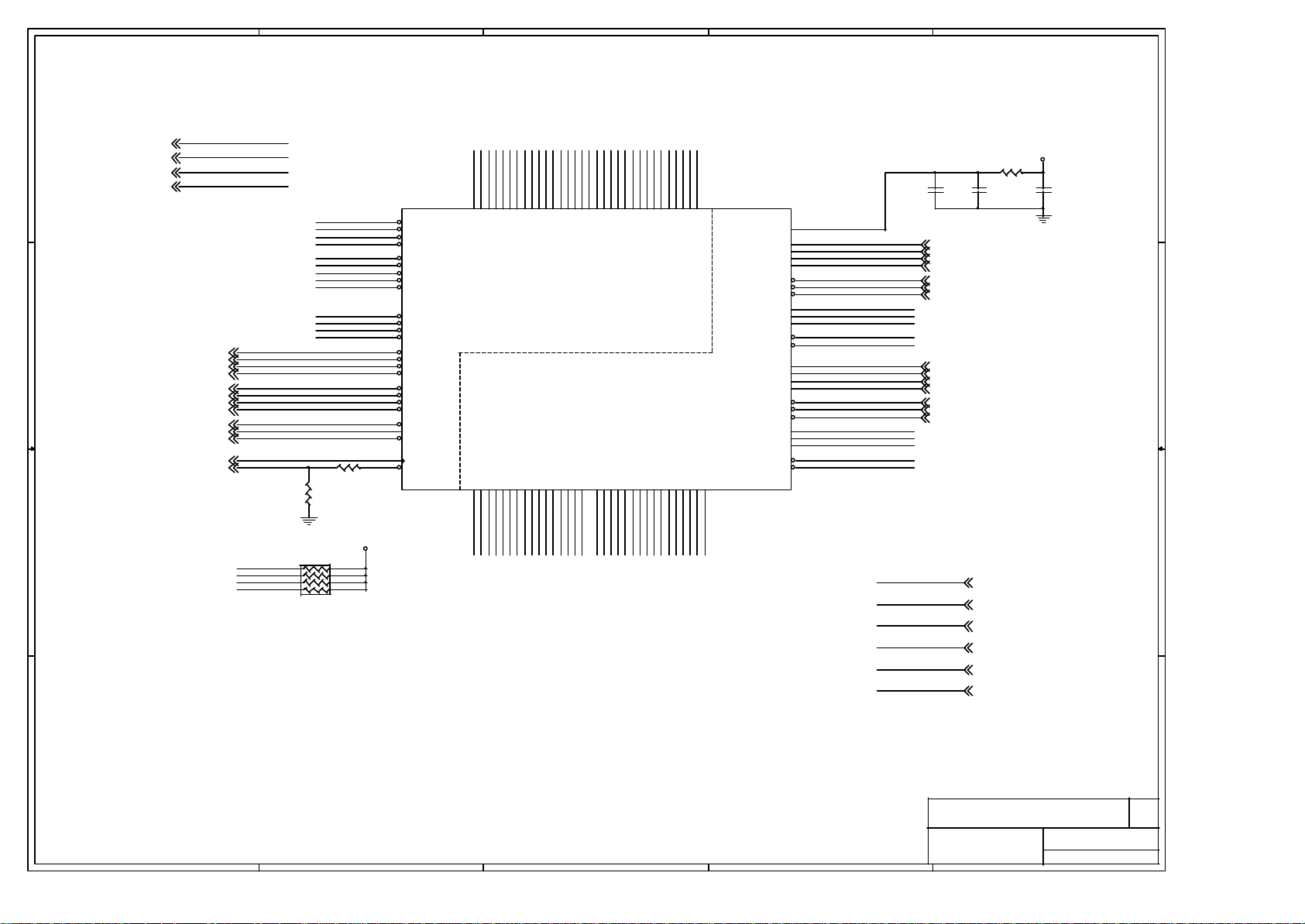

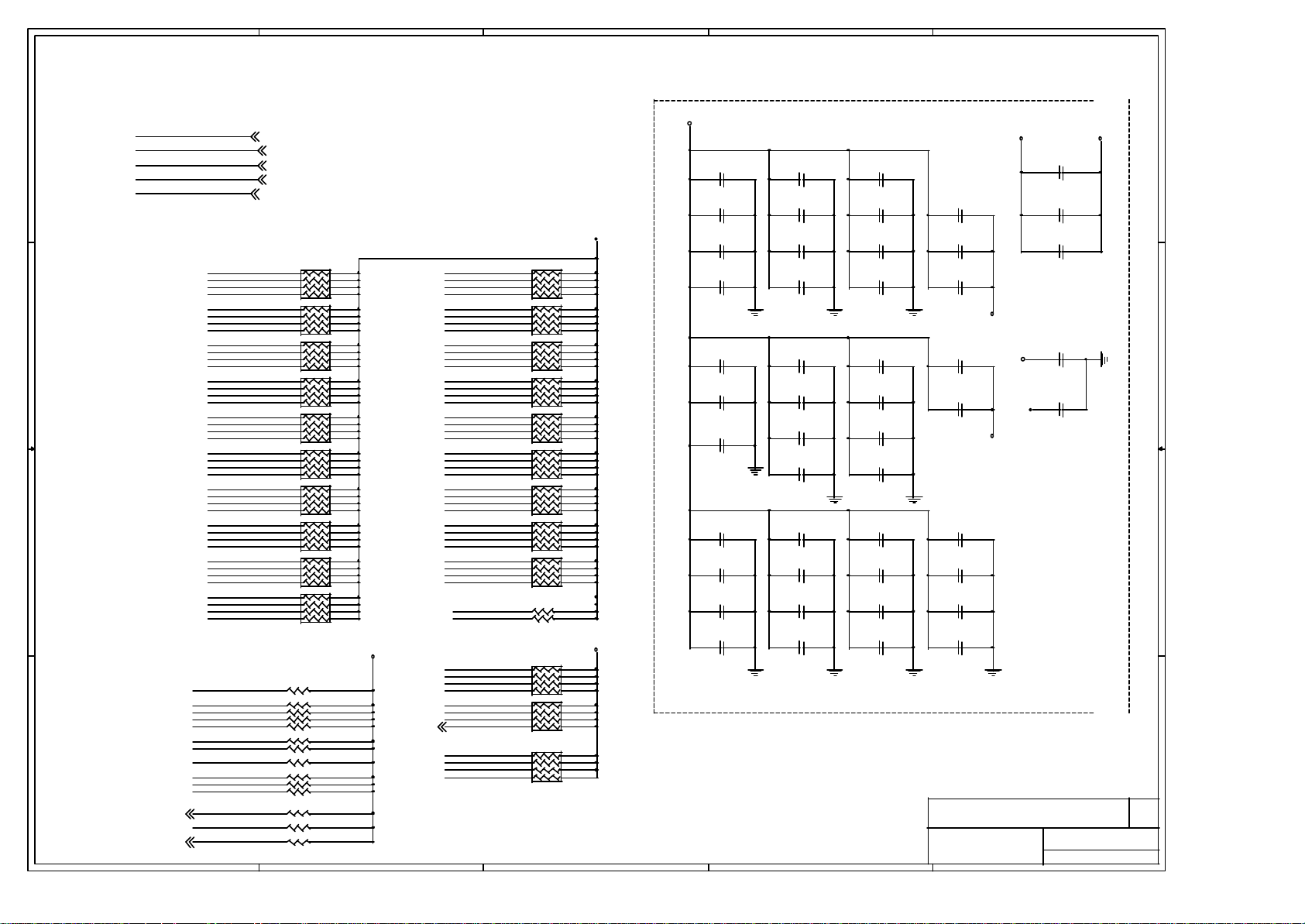

CPU: AMD Socket-462 Processor

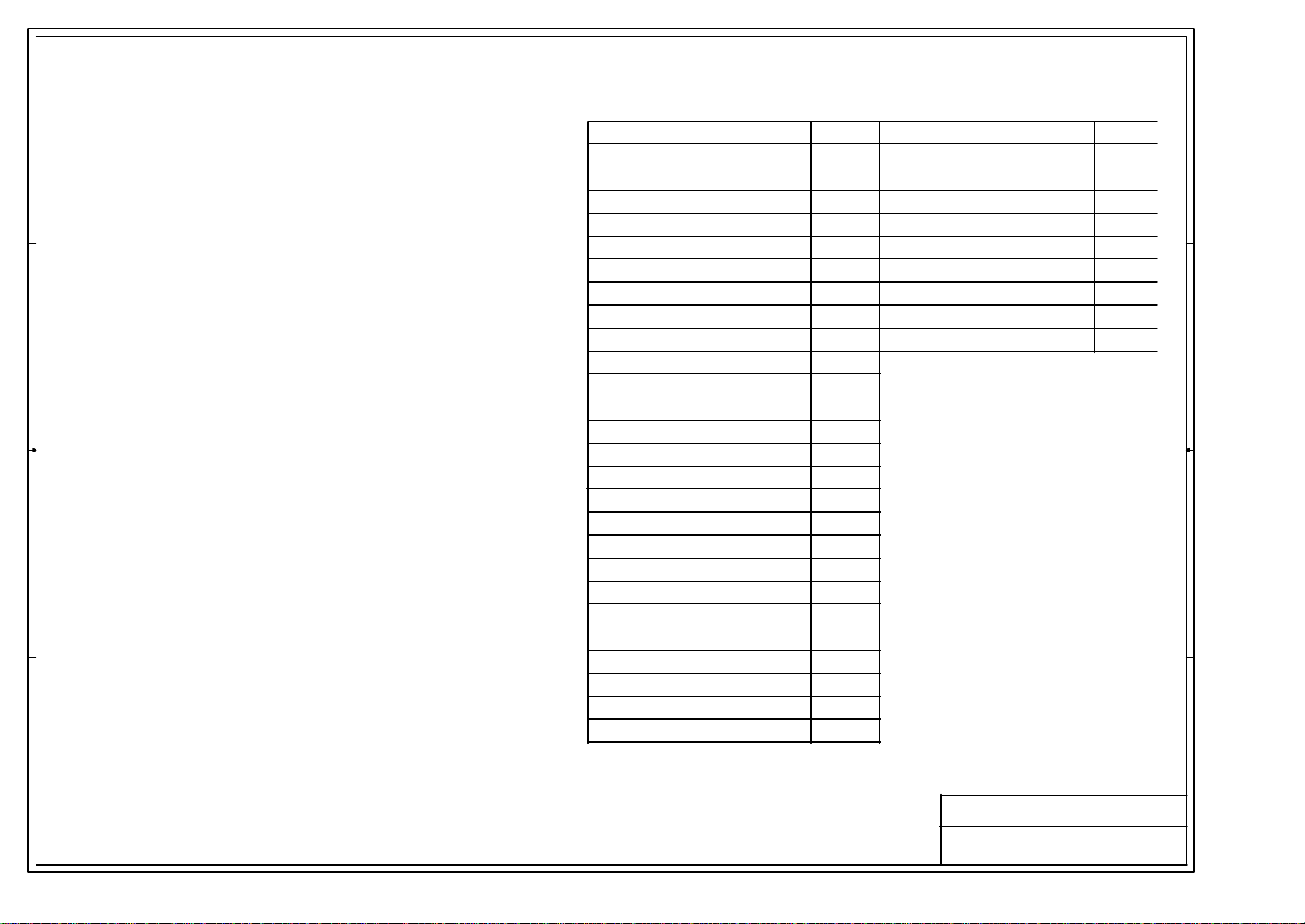

Cover Page

Chipset: SiS 745

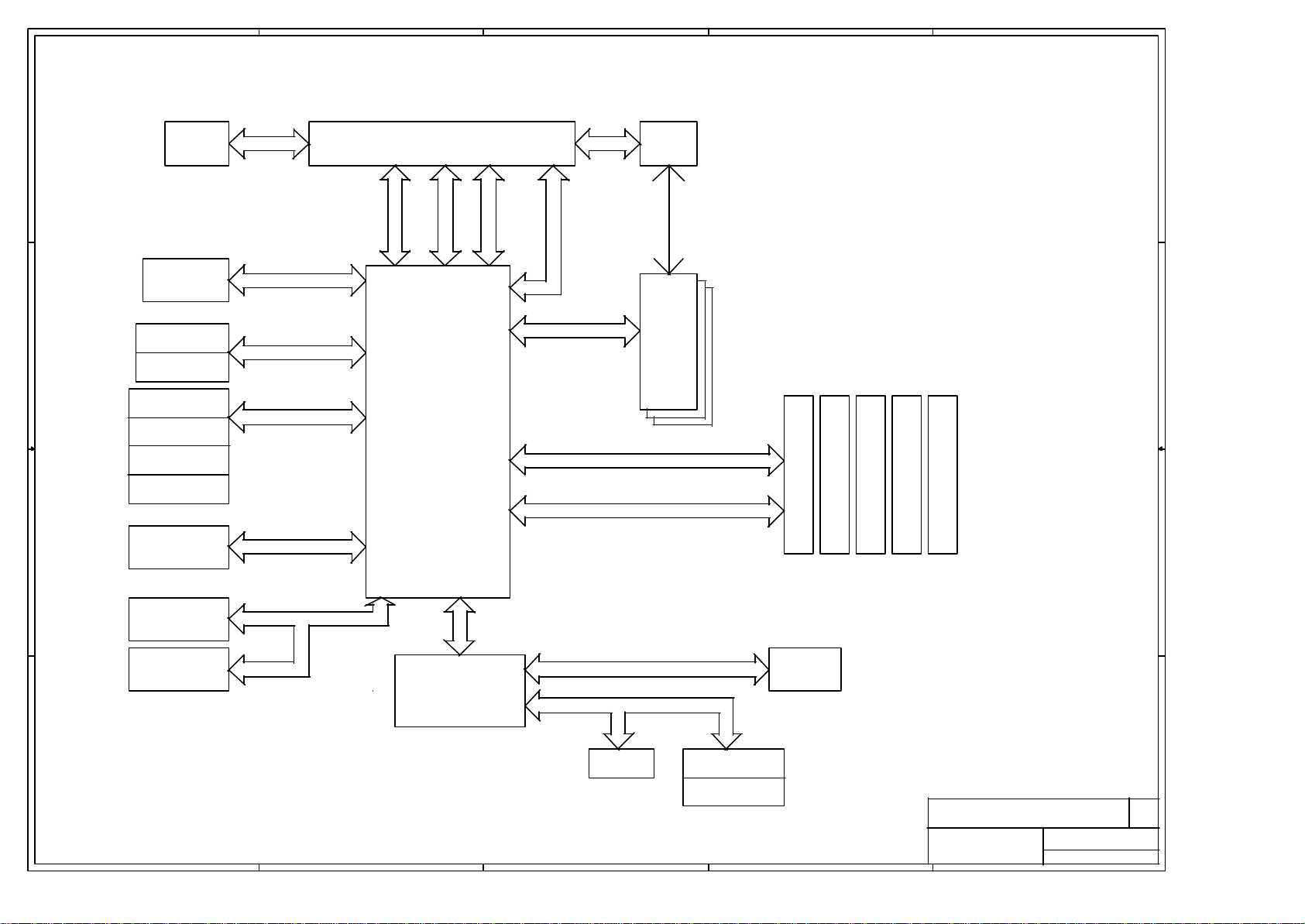

Block Diagram

Clock Generator

LPC I/O: W83697HF

Clock Buffer

AMD Socket A

AC'97 CODEC:Realtek ALC201A

IEEE1394 : TI TSB41LV02(OPTION)

SiS 745 Host / AGP

SiS 745 Memory

SiS 745 PCI / IDE

Expansion:

C C

SiS 745 Misc. Signal

SiS 745 Power

1.AGP Slot * 1

2.PCI Slot * 5

3.CNR Slot * 1

Hardware Strap

System Memory

PCI Connector

AGP Slot

IDE Connector

USB Connector

KB/MS Connector

B B

AC'97 CODEC

Audio Connector

CNR Slot

LPC I/O W83697HF

Hardware Monitor

Parallel Port

Serial Port

Flash Memory

PWM ST-L6911D

A A

PAGECONTENT

1

2

3

4

5,6,7

8

9

10

11

12

13

14,15,16

17,18,19

20

21

22

23

24

25

26

27

28

29

30

31

32

Voltage Regulator

ATX Connector

Front Pannel

Decoupling Capacitors

MS-3 & D-LED

CPU Thermal Portection

GPIO SPEC. 42

CONTENT PAGE

33,34

35

36

37

38

391394 PHY

40

41Manual Part

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

5

4

3

2

http://www.msi.com.tw

Cover Sheet

MS-6561

Last Revision Date:

Thursday, January 17, 2002

Sheet

1

1 42

Rev

1.0

of

5

4

3

2

1

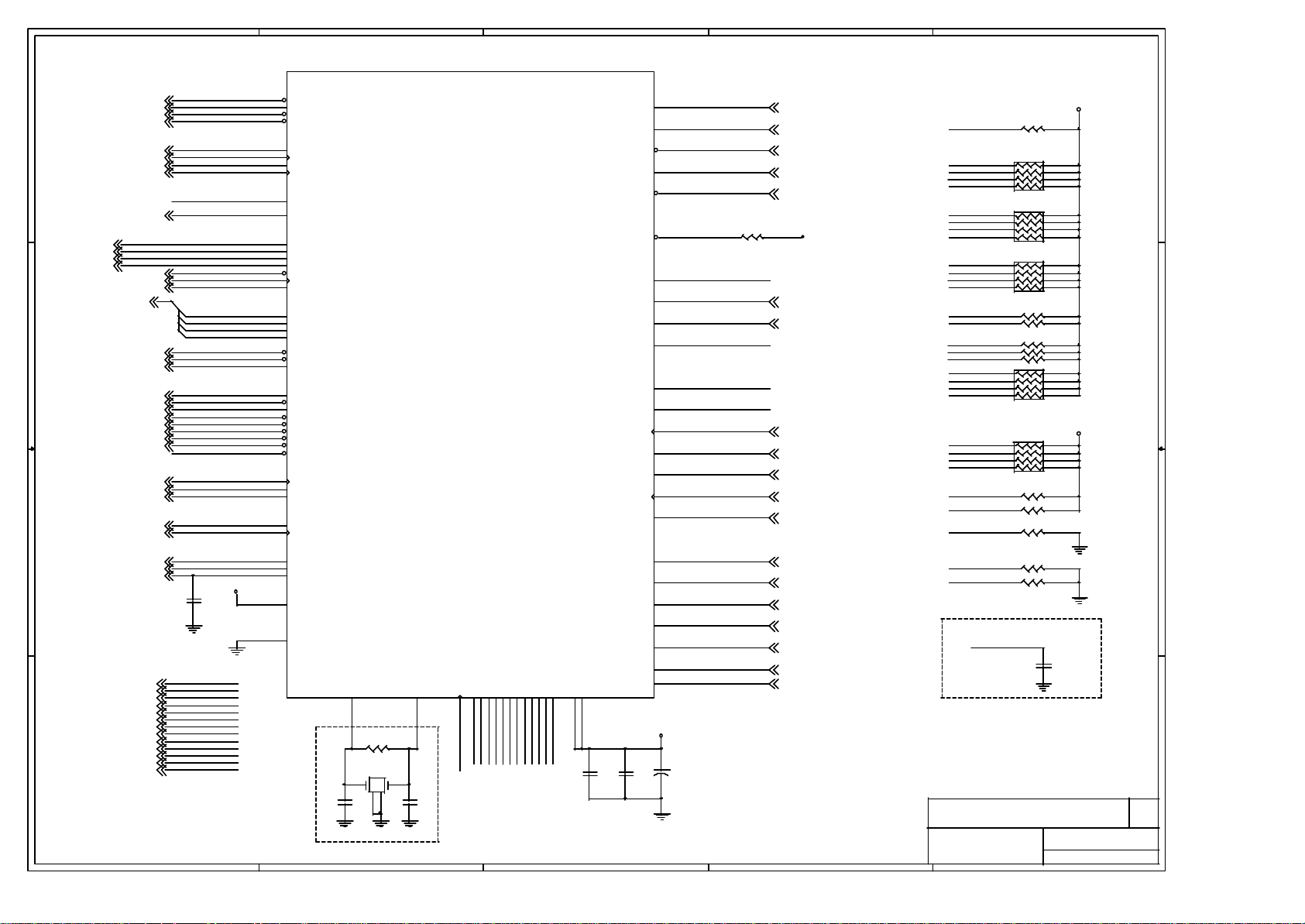

D D

VRM 9.0 Clock

K7 462-Pin Socket Processor

ADDR(In-Out)

PWR-MNG

DATA

INT & PWR-MNG

AGP 2X/4X

UltraDMA

C C

IDE Primary

33/66/100

IDE Secondary

3 DDR

Modules

PC-266

PCI 2.2

USB Port 1

USB Port 2

USB Port 3

USB Port 4

1394 PHY

B B

TI-TSB41AB3

USB

IEEE 1394

SIS745

PCI CNTRL

PCI ADDR/DATA

PCI Conn 1

PCI Conn 2

PCI Conn 3

PCI Conn 4

PCI Conn 5

Onboard

AC'97 Codec

CNR

AC'97 Link

WINBOND

LPC

ISA Bus

Flash

ROM

W83697HF

A A

5

4

Floopy Parallel

Serial

3

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jun g-He City,

Taipei Hsien, Taiwan

2

http://www.msi.com.tw

Block Diagram

MS-6561

Last Revision Date:

Sheet

1

Thursday, January 1 7, 2002

2 42

Rev

1.0

of

5

4

3

2

1

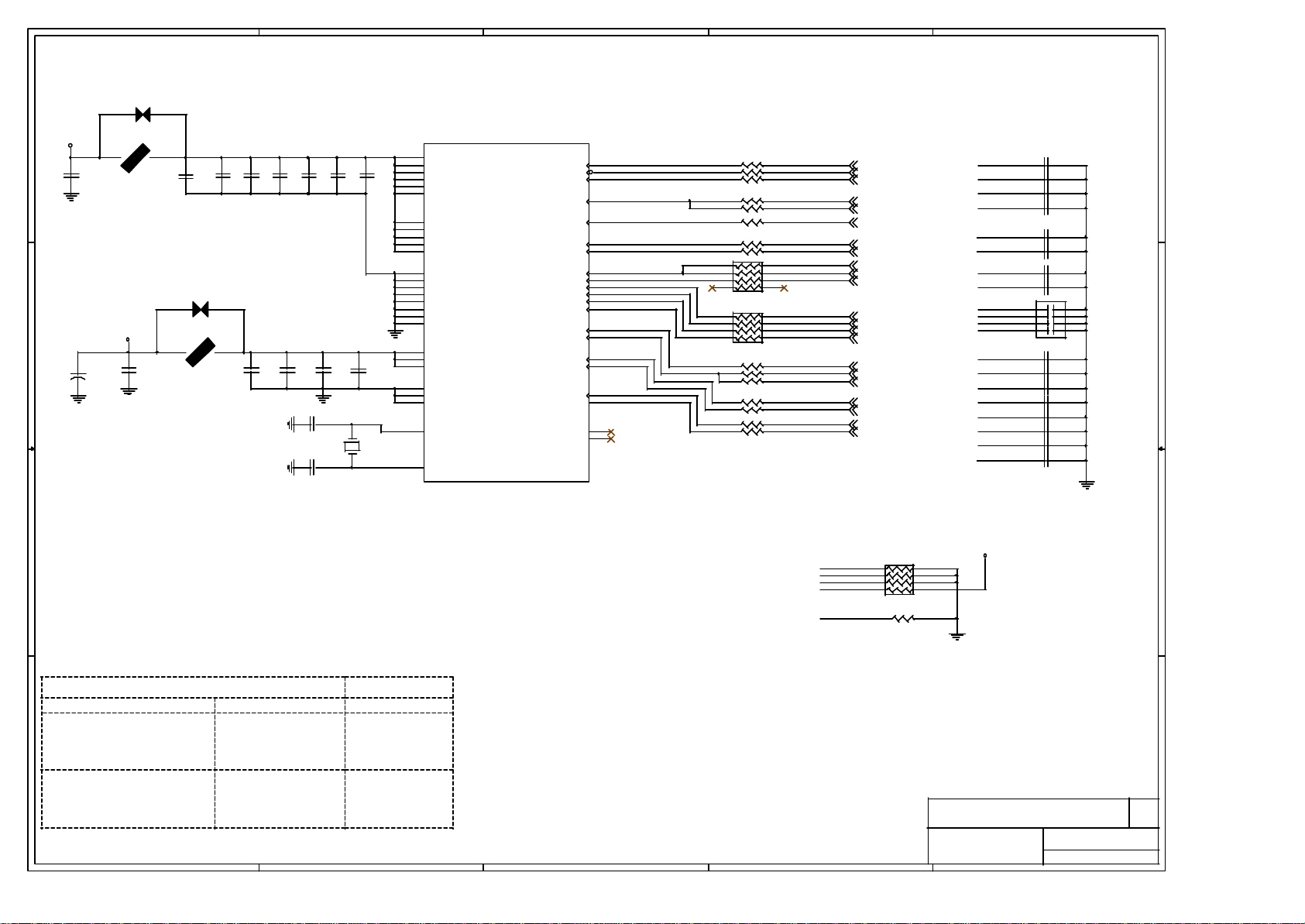

CP16

VCC3_3

D D

L18

1 2

X_COPPER

C259

104P

X_80S_0805

C392

4.7U_0805

C209

104P

C220

104P

C245

104P

C263

104P

C208

104P

C207

104P

CP2

X_COPPER

C C

VCC2_5

12

EC71

+

10U/16VS

C211

104P

L17

1 2

X_80S_0805

C204

104P

C205

104P

C206

104P

C391

4.7U_0805

C244

20p

C203

Y2

14.318MHz

20p

U7

1

VDDREF

11

VDDPCI

17

VDDAGP

21

VDD48M

36

VDDSDRAM

25

VDDCORE

32

CPUSTP#

30

SDRAMSTOP#

29

AGPSTOP#

33

PCISTP#

31

PD#

4

VSSREF

5

VSSOSC

8

VSSPCI

14

VSSPCI

20

VSSAGP

24

VSS48M

34

VSSSDRAM

26

VSSCORE

45

VDDCPU

41

VDDCPU

48

VDDAPIC

42

VSSCPU

39

VSSCPU

46

VSSAPIC

6

XIN

7

XOUT

ICS9248-199

44

CPUCLK0

43

CPUCLK#0

40

CPUCLK1

47

APICCLK

35

SDRAMCLK

18

AGPCLK0

19

AGPCLK1

9

FS2/PCICLK_F

10

FS3/PCICLK1

12

PCICLK2

13

PCICLK3

15

PCICLK4

16

PCICLK5

2

FS0/REF0

3

FS1/REF1

22

48MHZ

SCLK

SDATA

RSVD

RSVD

23

27

28

37

38

AGPSEL/24_48MHZ

R126 10

R127 10

R128 22

R120 10

R371 10

R129 10

R169 22

R170 22

FS2

FS3 PCICLK1

7 8

5 6

3 4

1 2

CPUCLK

CPUCLK#

733CCLK

APICCLK0

APICCLK1

733DCLK

733ACLK

AGPCLK1

733PCLK

SIOPCLK

RN56 8P4R-22

FS0

FS1

7 8

5 6

3 4

1 2

PCICLK2

PCICLK3

PCICLK4

PCICLK5

RN57 8P4R-22

R175 33

R176 33

R537 X_33

R171 22

R177 22

R131 100

R130 100

OSCIAGPSEL

OSCI1

AU_XIN

CPUCLK 5

CPUCLK# 5

733CCLK 8

APICCLK0 5

APICCLK1 11

733DCLK 9

733ACLK 8

AGPCLK1 20

733PCLK 10

SIOPCLK 27

PCICLK1 17

PCICLK2 18

PCICLK3 18

PCICLK4 19

PCICLK5 19

OSCI 11

OSCI1 38

AU_XIN 24

UCLK48M 11

SIO48M 27

SCLK 4,11,14,15,26,33,38

SDATA 4,11,14,15,26,33,38

733CCLK

CPUCLK

CPUCLK#

733PCLK

APICCLK0

APICCLK1

PCICLK1

SIOPCLK

PCICLK2

PCICLK3

PCICLK4

PCICLK5

OSCI

UCLK48M

SIO48M

733DCLK

AGPCLK1

733ACLK

OSCI1

AU_XIN

C195 10P

C192 10P

C193 10P

C249 10P

C394 X_10P

C385 X_10P

C384 X_10P

C383 X_10P

CN19

7 8

5 6

3 4

1 2

X_8P4C-10P

C264 10P

C252 10P

C260 10P

C197 22P

C251 10P

C250 10P

C265 10P

C477 X_10P

B B

FS3

FS2

FS1

FS0

RN59

1 2

3 4

5 6

7 8

VCC3_3

8P4R-10K

AGPSEL

SIS745 CLOCK

CPU PCI

(FS2) (FS1) (FS0)(FS3)

0 0 0

0

0 0 1

0

0 1 0

0

0 1 1

0

0

1 0 1

0

1 1

0

A A

0

1

1

1

1

1

1

1

1

1 1 1

0 0 0

0 0 1

0 1 0

0 1 1

1 0 1

1 1

1 1 1

001

0

001

0

5

SDRAM

(MHz) (MHz) (MHz)

66.6

100 100

133

66.6

100

100

133

112

124

138

150

66.6

133

150

160 120

33.3

66.6

33.3

166166

33.3

133

33.3

100

33.3

33.3

66.6

133

33.3

100

33.3

33.6

112

124

31 62

138

34.5

150

30

133

33.3

166

33.3 66.6 55.3

100

30

30

NOTE:

PCICLK<34.5MHz

AGPCLK

(MHz)

AGPSEL=0 AGPSEL=1

66.6 50

66.6

66.6

66.6

66.6

66.6

66.6

66.6

67.2

69

60

62.5

60

60

50

55.6

50

50

50

50

50

56

46.5

51.8

50

49.84

50

48

4

3

2

R172 10K

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jun g-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

Clock Generator

MS-6561

Last Revision Date:

Tuesday, March 12, 2002

Sheet

1

3 42

of

Rev

1.0

5

4

3

2

1

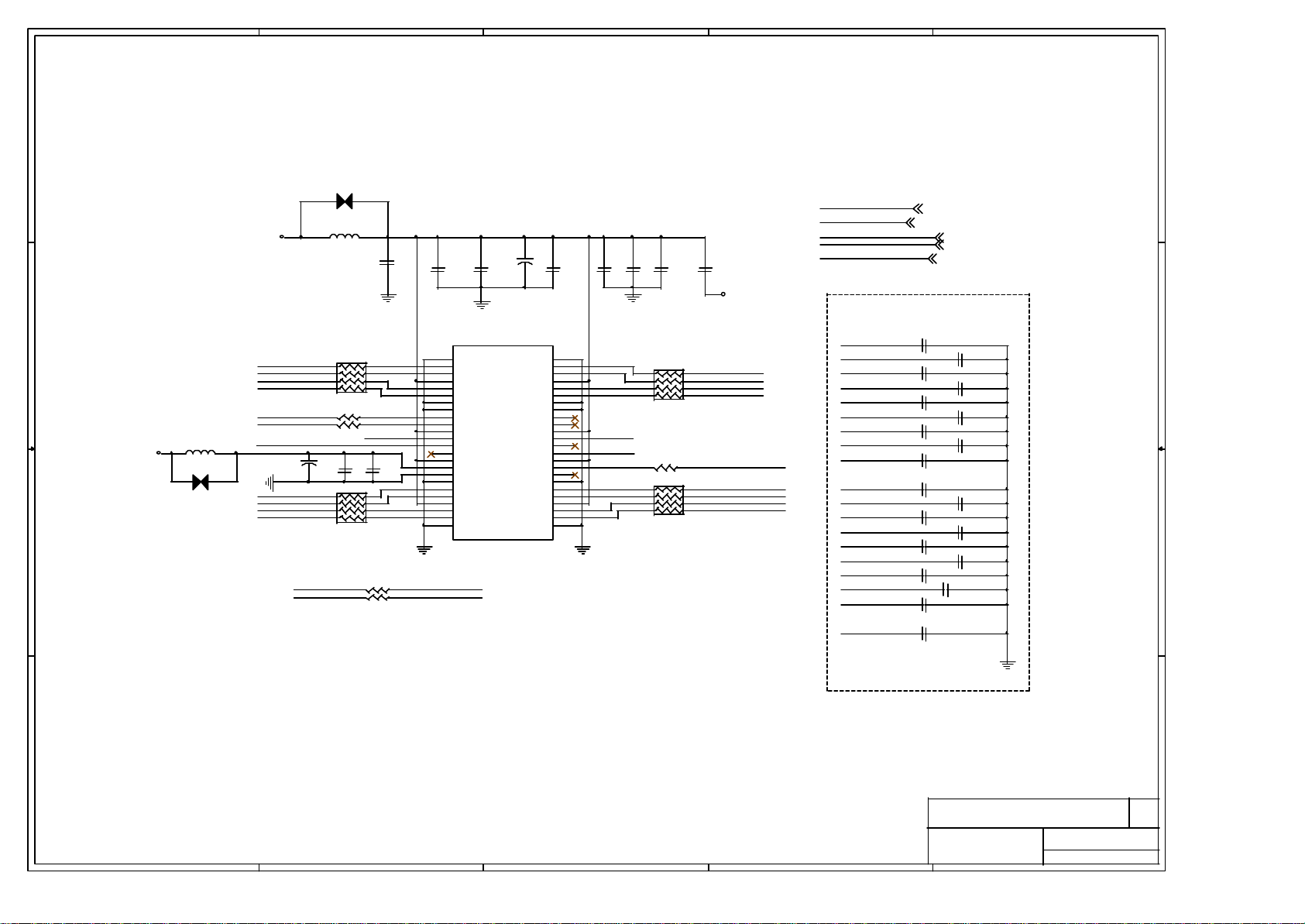

D D

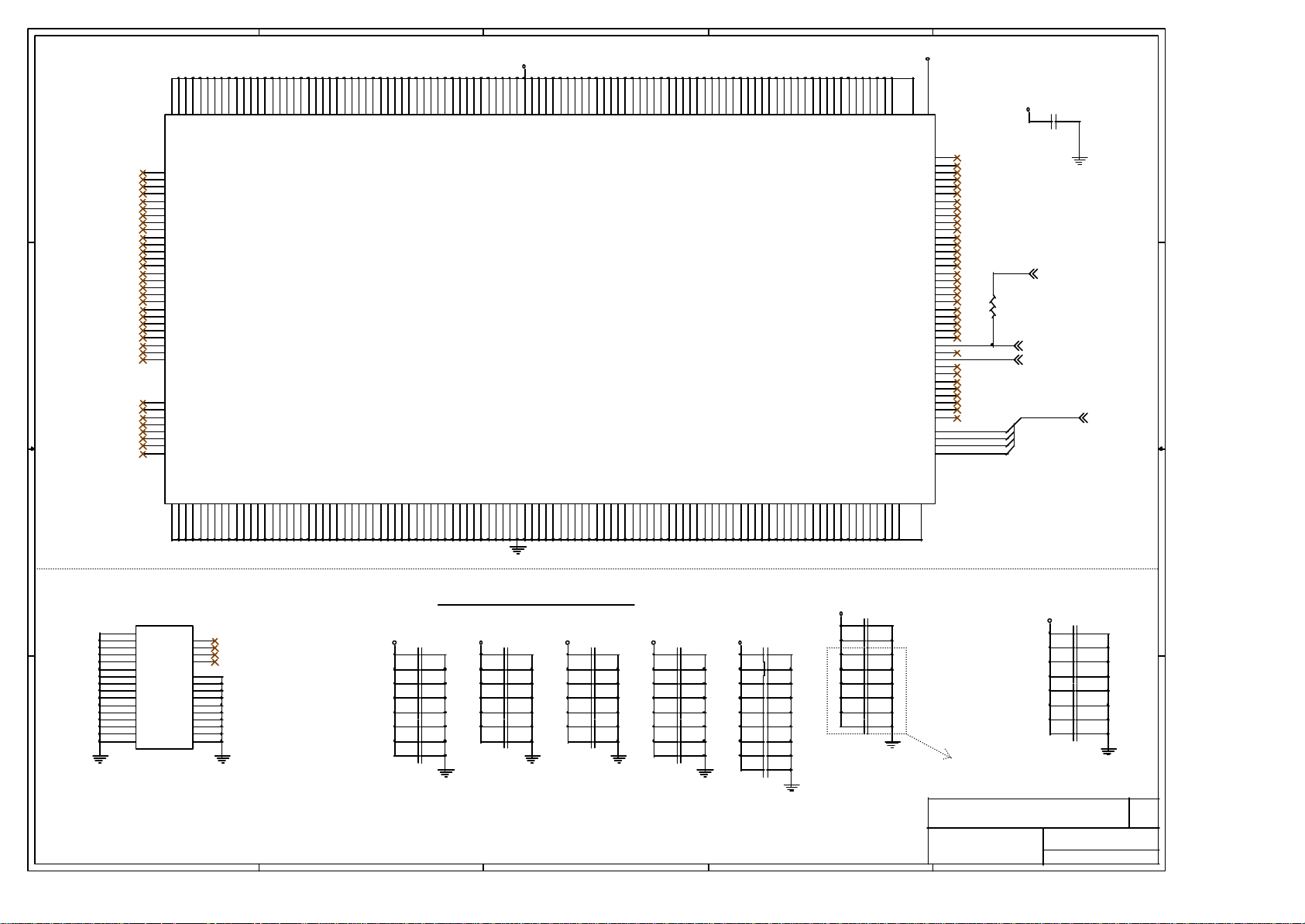

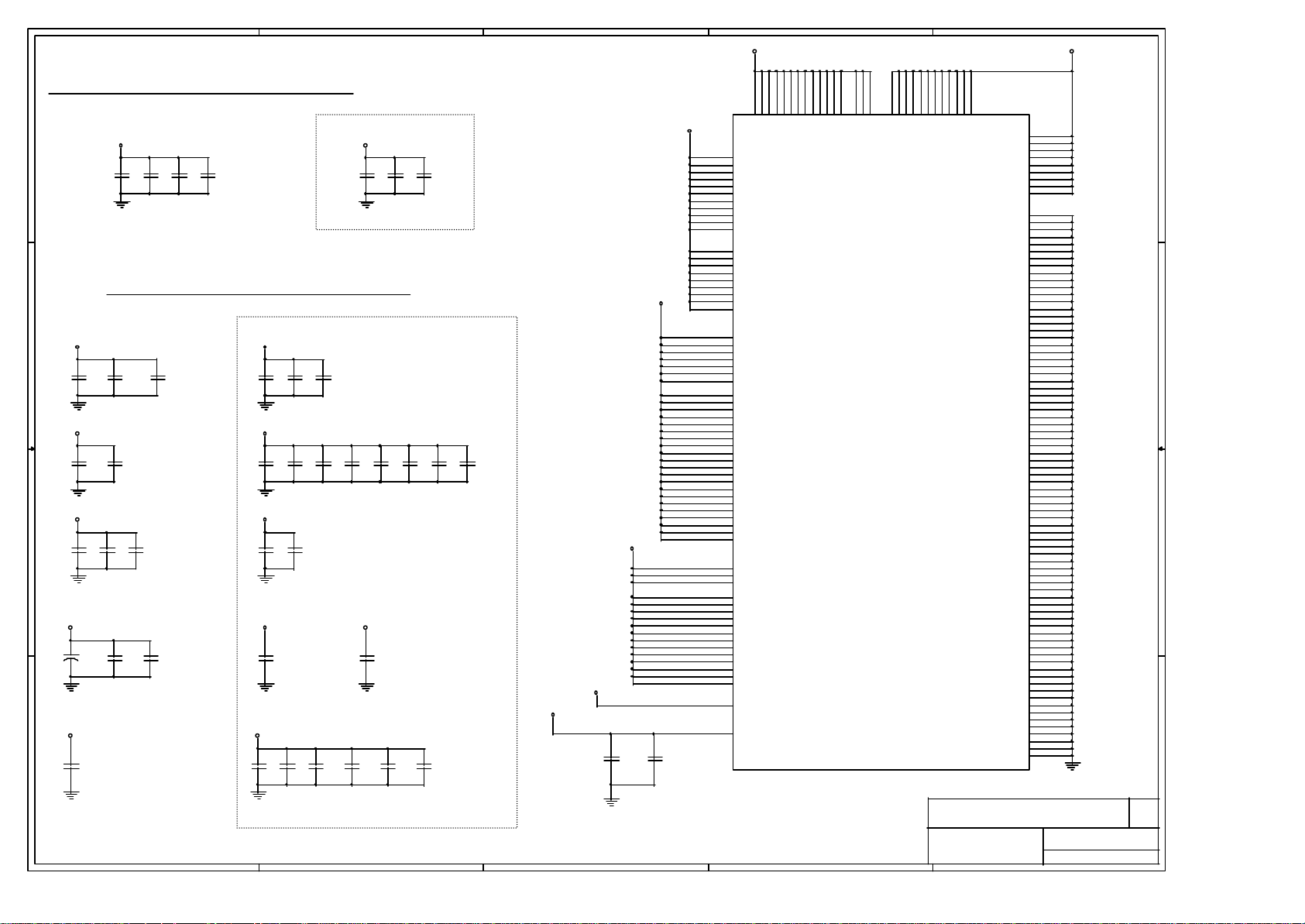

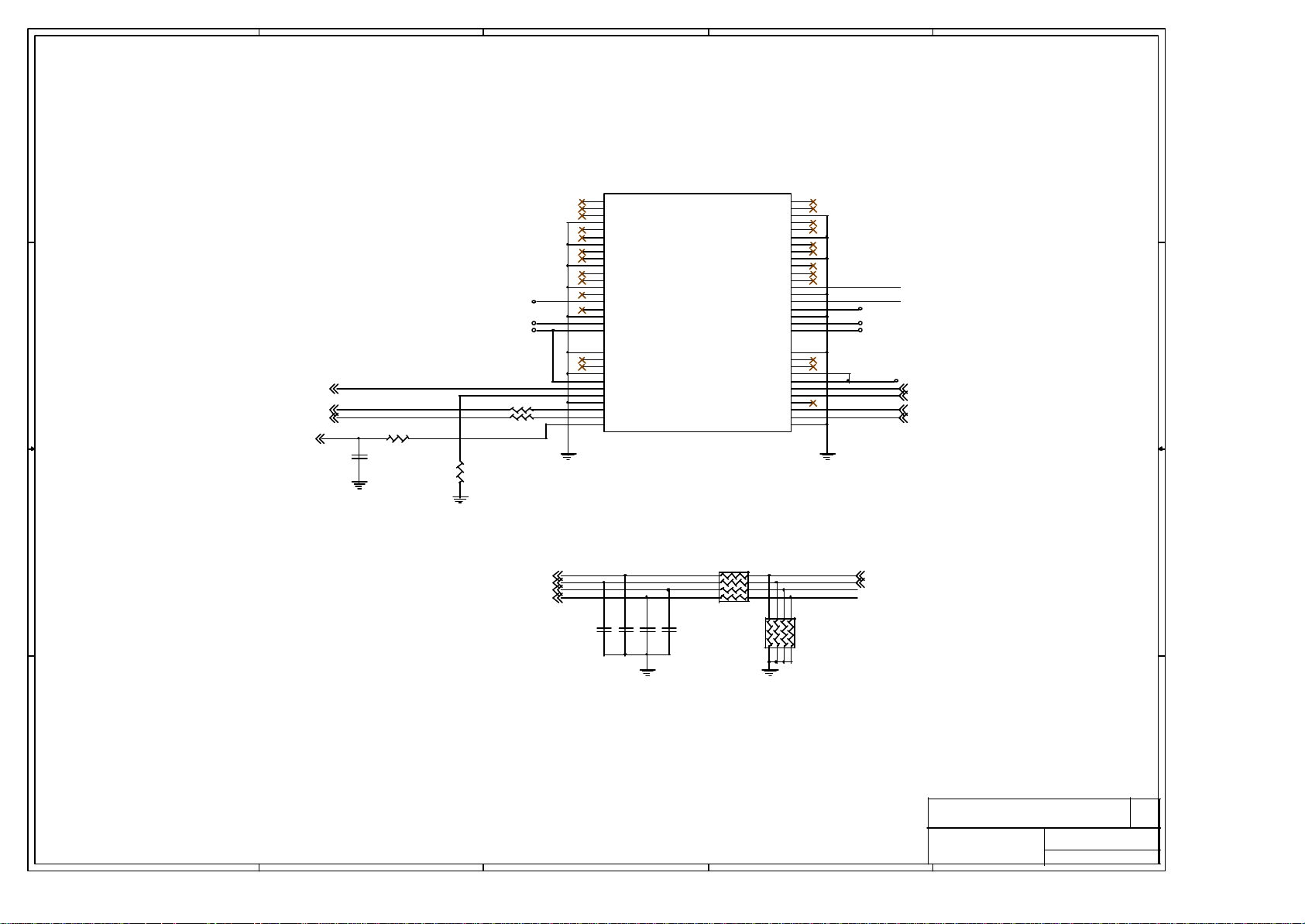

Clock Buffer (DDR)

CP3

X_COPPER

L50

VCC2_5

1 2

X_80_0805

C427

4.7U_0805

C C

DDRCLK-3

DDRCLK3

DDRCLK5

DDRCLK-5

RN112

1 2

3 4

5 6

7 8

0-0603

DDRCLK-0

R460 0_0603

1 2

R461 0_06031 2

12

BC45

0.01u

C43747U/10VS

1 2

3 4

5 6

7 8

CB1SCLK

12

BC46

0.1u

VCC2_5

L51

1 2

X_80_0805

CP15

X_COPPER

DDRCLK0

FWDCLK_DDR

DDRCLK-2

DDRCLK2

DDRCLK8

DDRCLK-8

RN115 0-0603

B B

12

BC37

0.1u

U24

1

GND

2

CLKC0

3

CLKT0

4

VDD

5

CLKT1

6

CLKC1

7

GND

8

GND

9

CLKC2

10

CLKT2

11

VDD

12

SCLK

13

CLK_INT

14

CLK_INC

15

VDD

16

AVDD

17

AGND

18

GND

19

CLKC3

20

CLKT3

21

VDD

22

CLKT4

23

CLKC4

24

GND

ICS-ICS93705CF

CBVDDR2

12

BC39

0.1u

BC40

47U/10VS

CLKC5

CLKT5

CLKT6

CLKC6

CLKC7

CLKT7

SDATA

FB_INC

FB_INT

FB_OUTT

FB_OUTC

CLKC8

CLKT8

CLKT9

CLKC9

GND

VDD

GND

GND

VDD

VDD

GND

VDD

GND

12

BC41

0.1u

12

12

12

BC42

0.1u

BC43

0.1u

BC44

0.1u

12

BC38

0.1u

V_CORE

48

47

46

45

44

43

42

41

40

39

38

CB1SDATA

37

36

FB_DDR

35

34

33

32

31

30

29

28

27

26

25

RN113

1 2

3 4

5 6

7 8

0-0603

R462 0_06031 2

RN114

1 2

3 4

5 6

7 8

0-0603

DDRCLK-1

DDRCLK1

DDRCLK4

DDRCLK-4

FB_DDR

DDRCLK-6

DDRCLK6

DDRCLK7

DDRCLK-7

DDRCLK[0..8]

DDRCLK-[0..8]

SCLK

SDATA

FWDCLK_DDR

By-Pass Capacitors

Place near to the Clock Buffer

DDRCLK3

DDRCLK-5

DDRCLK0

DDRCLK-2

DDRCLK-1

DDRCLK-8

DDRCLK4

DDRCLK7

DDRCLK6

DDRCLK-3

DDRCLK5

DDRCLK-0

DDRCLK2

DDRCLK1

DDRCLK8

DDRCLK-4

SCLK

SDATA

R465 0_06031 2

R466 0_0603

1 2

CB1SCLK

CB1SDATA

DDRCLK-7

DDRCLK-6

DDRCLK[0..8] 14,15

DDRCLK-[0..8] 14,15

FWDCLK_DDR 9

C428 10p-0603

1 2

C429 10p-06031 2

C430 10p-06031 2

C431 10p-06031 2

C432 10p-06031 2

C433 10p-0603

C434 10p-06031 2

C435 10p-06031 2

C436 10p-06031 2

C438 10p-0603

1 2

C439 10p-06031 2

C440 10p-06031 2

C441 10p-06031 2

C442 10p-06031 2

C443 10p-0603

C444 10p-06031 2

C445 10p-06031 2

C446 10p-06031 2

SCLK 3,11,14,15,26,33,38

SDATA 3,11,14,15,26,33,38

1 2

1 2

FB_DDR

C447 10p-0603

1 2

A A

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jun g-He City,

Taipei Hsien, Taiwan

5

4

3

2

http://www.msi.com.tw

Clock Buffer

MS-6561

Last Revision Date:

Tuesday, March 12, 2002

Sheet

1

4 42

Rev

1.0

of

5

4

3

2

1

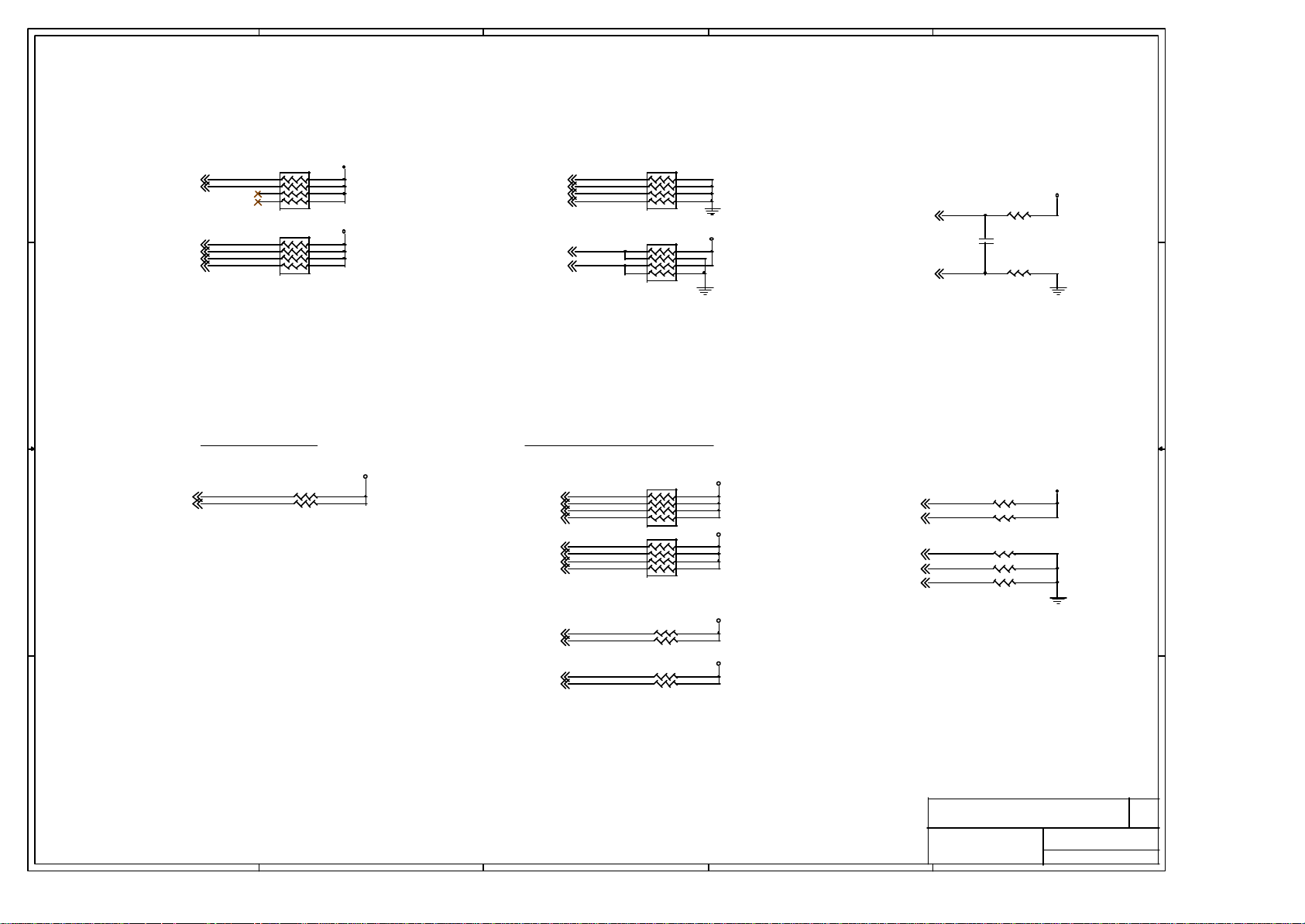

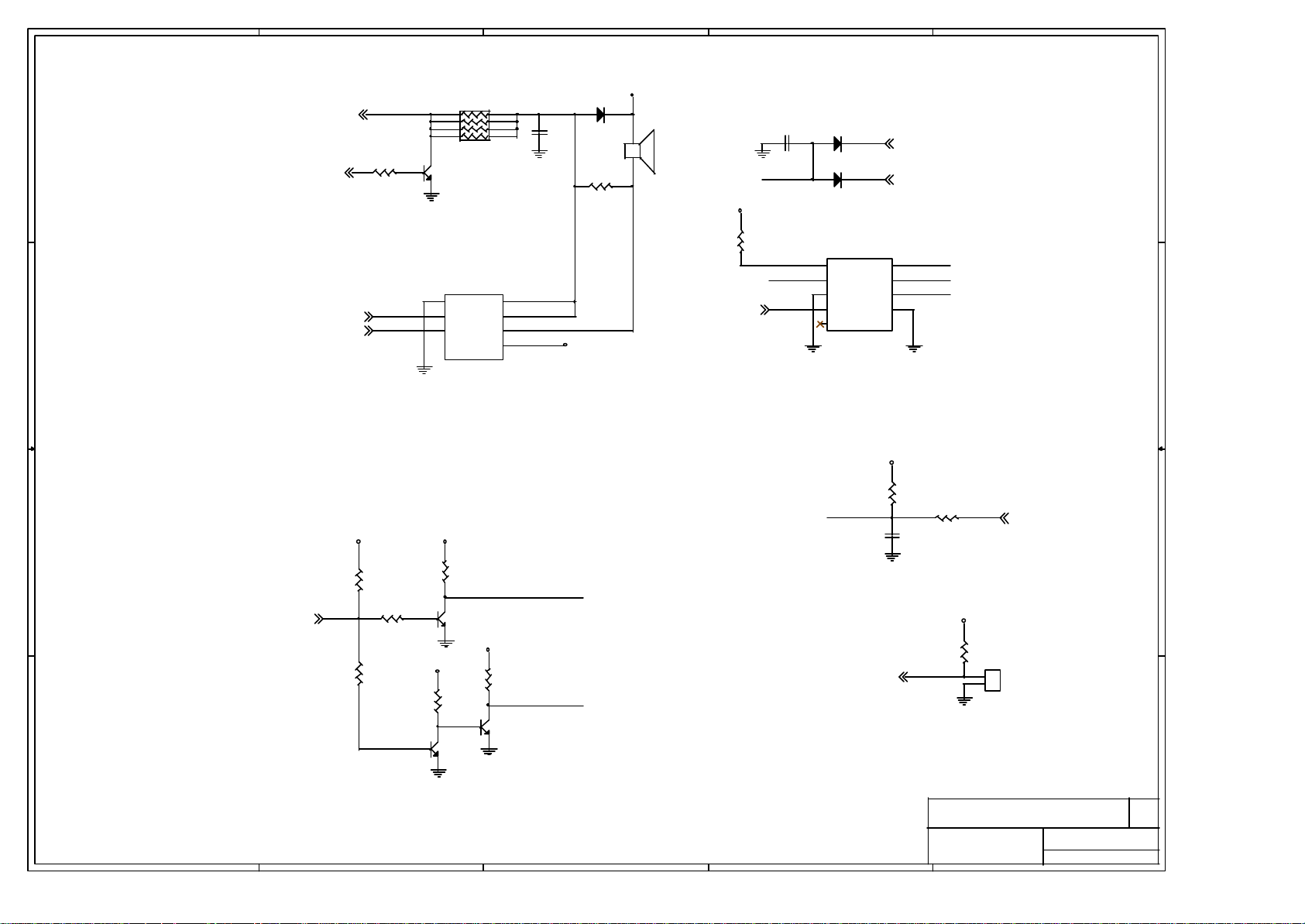

CPU FERR BLOCK

AMD 462PGA Socket - Signals

CPU1A

A20M

FERR

INIT

INTR

IGNNE

NMI

RESET

SMI

STPCLK

PWROK

PICCLK

PICD0/BYPASSCLK

PICD1/BYPASSCLK

COREFB-

COREFB+

CLKIN

CLKIN

RSTCLK

RSTCLK

K7CLKOUT

K7CLKOUT

ANALOG

SYSVREFMODE

VREF_SYS

ZN

ZP

PLLBYPASS

PLLBYPASSCLK

PLLBYPASSCLK

PLLMON1

PLLMON2

PLLTEST

SCANCLK1

SCANCLK2

SCANINTEVAL

SCANSHIFTEN

DBRDY

DBREQ

FLUSH

TCK

TDI

TDO

TMS

TRST

VID0

VID1

VID2

VID3

VID4

FID0

FID1

FID2

FID3

SCHECK0

SCHECK1

SCHECK2

SCHECK3

SCHECK4

SCHECK5

SCHECK6

SCHECK7

SADDOUT0

SADDOUT1

SADDOUT2

SADDOUT3

SADDOUT4

SADDOUT5

SADDOUT6

SADDOUT7

SADDOUT8

SADDOUT9

SADDOUT10

SADDOUT11

SADDOUT12

SADDOUT13

SADDOUT14

SADDOUTCLK

4

A20M#

AE1

FERR

AG1

INIT#_39491

AJ3

INTR

AL1

IGNNE#

AJ1

NMI

AN3

CPURST#

AG3

SMI#

AN5

STPCLK#

AC1

CPU_PWOK

AE3

APICCLK0

N1

APICD0

N3

APICD1

N5

COREFB-

AG13

COREFB+

AG11

AN17

AL17

AN19

AL19

K7CLKOUT

AL21

K7CLKOUT#

AN21

AJ13

VREFMODE

AA5

VREF_SYS

W5

ZN

AC5

ZP

AE5

PLLBP#

AJ25

PLLBYCLK

AN15

PLLBYCLK#

AL15

PLLMON1

AN13

PLLMON2

AL13

PLLTEST#

AC3

SCANCLK1

S1

SCANCLK2

S5

SINTVAL

S3

SSHIFTEN

Q5

AA1

DBREQ#

AA3

FLUSH#

AL3

TCK

Q1

TDI

U1

U5

TMS

Q3

TRST#

U3

VIDI0

L1

VIDI1

L3

VIDI2

L5

VIDI3

L7

VIDI4

J7

FIDI0

W1

FIDI1

W3

FIDI2

Y1

FIDI3

Y3

U37

Y33

L35

E33

E25

A31

C13

A19

J1

J3

SADO#2

C7

SADO#3

A7

SADO#4

E5

SADO#5

A5

SADO#6

E7

SADO#7

C1

SADO#8

C5

SADO#9

C3

SADO#10

G1

SADO#11

E1

SADO#12

A3

SADO#13

G5

SADO#14

G3

SADOCLK#

E3

N12-4620011-F02

SYSCLK

SYSCLK#

A20M# 7,11

INIT# 7,11

INTR 7,11

IGNNE# 7,11

NMI 7,11

CPURST# 7,8

SMI# 7,11

STPCLK# 7,11

CPU_PWOK 33

APICCLK0 3

APICD0 7,11

APICD1 7,11

COREFB- 7

COREFB+ 7

VREFMODE 7

PLLBP# 7

PLLBYCLK 7

PLLBYCLK# 7

PLLMON1 7

PLLMON2 7

PLLTEST# 7

SCANCLK1 7

SCANCLK2 7

SINTVAL 7

SSHIFTEN 7

DBREQ# 7

FLUSH# 7

TCK 7

TDI 7

TMS 7

TRST# 7

VIDI[0..4] 38

FIDI[0..3] 38

SADO#[2..14] 8

SADOCLK# 8

3

5

SDATA#0

SDATA#1

SDATA#2

SDATA#3

SDATA#4

SDATA#5

SDATA#6

SDATA#7

SDATA#8

SDATA#9

SDATA#10

SDATA#11

SDATA#12

SDATA#13

SDATA#14

SDATA#15

SDATA#16

SDATA#17

SDATA#18

SDATA#19

SDATA#20

SDATA#21

SDATA#22

SDATA#23

SDATA#24

SDATA#25

SDATA#26

SDATA#27

SDATA#28

SDATA#29

SDATA#30

SDATA#31

SDATA#32

SDATA#33

SDATA#34

SDATA#35

SDATA#36

SDATA#37

SDATA#38

SDATA#39

SDATA#40

SDATA#41

SDATA#42

SDATA#43

SDATA#44

SDATA#45

SDATA#46

SDATA#47

SDATA#48

SDATA#49

SDATA#50

SDATA#51

SDATA#52

SDATA#53

SDATA#54

SDATA#55

SDATA#56

SDATA#57

SDATA#58

SDATA#59

SDATA#60

SDATA#61

SDATA#62

SDATA#63

SDINCLK#0

SDINCLK#1

SDINCLK#2

SDINCLK#3

SDIVAL#

SDOCLK#0

SDOCLK#1

SDOCLK#2

SDOCLK#3

SDOVAL#

SADI#0

SADI#1

SADI#2

SADI#3

SADI#4

SADI#5

SADI#6

SADI#7

SADI#8

SADI#9

SADI#10

SADI#11

SADI#12

SADI#13

SADI#14

SDINCLK#

CFWDRST

CONNECT

PROCRDY

SFILLVAL#

SDATA#[0..63]8

D D

C C

B B

SDOCLK#[0..3]8

A A

SDIVAL#8

SDOVAL#7

SADI#07

SADI#17

SADI#[2..14]8

CFWDRST8

CONNECT8

PROCRDY8

SFILLVAL#7

AA35

SDATA0

W37

SDATA1

W35

SDATA2

Y35

SDATA3

U35

SDATA4

U33

SDATA5

S37

SDATA6

S33

SDATA7

AA33

SDATA8

AE37

SDATA9

AC33

SDATA10

AC37

SDATA11

Y37

SDATA12

AA37

SDATA13

AC35

SDATA14

S35

SDATA15

Q37

SDATA16

Q35

SDATA17

N37

SDATA18

J33

SDATA19

G33

SDATA20

G37

SDATA21

E37

SDATA22

G35

SDATA23

Q33

SDATA24

N33

SDATA25

L33

SDATA26

N35

SDATA27

L37

SDATA28

J37

SDATA29

A37

SDATA30

E35

SDATA31

E31

SDATA32

E29

SDATA33

A27

SDATA34

A25

SDATA35

E21

SDATA36

C23

SDATA37

C27

SDATA38

A23

SDATA39

A35

SDATA40

C35

SDATA41

C33

SDATA42

C31

SDATA43

A29

SDATA44

C29

SDATA45

E23

SDATA46

C25

SDATA47

E17

SDATA48

E13

SDATA49

E11

SDATA50

C15

SDATA51

E9

SDATA52

A13

SDATA53

C9

SDATA54

A9

SDATA55

C21

SDATA56

A21

SDATA57

E19

SDATA58

C19

SDATA59

C17

SDATA60

A11

SDATA61

A17

SDATA62

A15

SDATA63

W33

SDATAINCLK0

J35

SDATAINCLK1

E27

SDATAINCLK2

E15

SDATAINCLK3

AN33

SDATAINVAL

AE35

SDATAOUTCLK0

C37

SDATAOUTCLK1

A33

SDATAOUTCLK2

C11

SDATAOUTCLK3

AL31

SDTATOUTVAL

AJ29

SADDIN0

AL29

SADDIN1

AG33

SADDIN2

AJ37

SADDIN3

AL35

SADDIN4

AE33

SADDIN5

AJ35

SADDIN6

AG37

SADDIN7

AL33

SADDIN8

AN37

SADDIN9

AL37

SADDIN10

AG35

SADDIN11

AN29

SADDIN12

AN35

SADDIN13

AN31

SADDIN14

AJ33

SADDINCLK

AJ21

CLKFWDRST

AL23

CONNECT

AN23

PROCRDY

AJ31

SFILLVAL

SADDINCLK#

SDATAINCLK#0

SDATAINCLK#1

SDATAINCLK#2

SDATAINCLK#3

SDINCLK#

SDINCLK#0

SDINCLK#1

SDINCLK#2

SDINCLK#3

K7CLKOUT#

K7CLKOUT

SADDINCLK# 8

SDATAINCLK#[0..3] 8

L37

10n

L35

10n

L36

10n

L33

10n

L31

10n

Place on solder side

C347

5P

C345

5P

C346

5P

C344

5P

C343

5P

L40

SADDINCLK#

10n

L38

SDATAINCLK#0

10n

L39

SDATAINCLK#1

10n

L34

SDATAINCLK#2

10n

L32

SDATAINCLK#3

10n

CPU K7CLKOUT BLOCK

RN22

1 2

3 4

5 6

7 8

8P4R-100

* Trace lengths of CLKOUT and -CLKOUT

are between 2" and 3"

V_CORE

V_CORE

2

VCC3_3

FERR

V_CORE

R22

4.7K

R27

4.7K

FERR# 11

C

Q8

B

2N3904

E

CPU SYSCLK BLOCK

CPUCLK3

SYSCLK

SYSCLK#

C50 680P

C49 680P

CPUCLK#3

R44 60.4RST

R43

301RST

R42 60.4RST

Near socket-A

CPU SYSCLK REFERNCE BLOCK

0.5 * VCORE

VREF_SYS

C30

C42

473P

C40

104P

103P

CPU ZN / ZP BLOCK

ZN

ZP

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jun g-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

V_CORE

R33 40.2RST

R32 40.2RST

match the transmission line

Push-pull compensation circuit

Micro Star Restricted Secret

Socket A_Signal

MS-6561

Last Revision Date:

Sheet

1

V_CORE

V_CORE

R38

100

R37

100

Thursday, January 1 7, 2002

5 42

of

Rev

1.0

5

AMD 462PGA Socket - Power

H12

H16

H20

H24M8P30R8T30V8X30Z8AB30

D D

C C

AD30

AD8

AF10

AF28

AF30

AF32

AF6

AF8

AH30

AH8

AJ9

AK8

AL9

AM8

F30

H10

H28

H30

H32

K30

K8

AJ7

AL7

AN7

G25

G17

Y7

AG7

AG15

AG29

F8

H6

H8

G9

N7

VCC_CORE1

VCC_CORE2

VCC_CORE3

VCC_CORE4

VCC_SRAM1

VCC_SRAM2

VCC_SRAM3

VCC_SRAM4

VCC_SRAM5

VCC_SRAM6

VCC_SRAM7

VCC_SRAM8

VCC_SRAM9

VCC_SRAM11

VCC_SRAM13

VCC_SRAM14

VCC_SRAM16

VCC_SRAM17

VCC_SRAM19

VCC_SRAM20

VCC_SRAM21

VCC_SRAM22

VCC_SRAM23

VCC_SRAM24

VCC_SRAM25

VCC_SRAM26

VCC_SRAM27

VCC_SRAM28

VCC_SRAM29

VCC_SRAM30

VCC_SRAM31

KEY4

KEY6

KEY8

KEY10

KEY12

KEY14

KEY16

KEY18

VCC_CORE5

VCC_CORE6

VCC_CORE7

VCC_CORE8

VCC_CORE9

VCC_CORE10

AF14

AF18

AF22

AF26

VCC_CORE11

VCC_CORE12

VCC_CORE13

VCC_CORE14

VCC_CORE15

AM34

AK36

AK34

AK30

AK26

VCC_CORE16

VCC_CORE17

VCC_CORE18

VCC_CORE19

VCC_CORE20

AK22

VCC_CORE21

AK18

AK14

AK10

AL5

AH26

VCC_CORE22

VCC_CORE23

VCC_CORE24

VCC_CORE25

VCC_CORE26

4

AM30

AH22

AH18

AH14

AH10

VCC_CORE27

VCC_CORE28

VCC_CORE29

VCC_CORE30

VCC_CORE31

AH4

AH2

AF36

AF34

AD6

VCC_CORE32

VCC_CORE33

VCC_CORE34

VCC_CORE35

VCC_CORE36

AM26

AD4

AD2

AB36

AB34

VCC_CORE37

VCC_CORE38

VCC_CORE39

VCC_CORE40

VCC_CORE41

AB32Z6Z4Z2X36

VCC_CORE42

VCC_CORE43

VCC_CORE44

VCC_CORE45

VCC_CORE46

V_CORE

X34

AM22

X32V6V4V2T36

VCC_CORE47

VCC_CORE48

VCC_CORE49

VCC_CORE50

VCC_CORE51

T34

T32R6R4R2AM18

VCC_CORE52

VCC_CORE53

VCC_CORE54

VCC_CORE55

VCC_CORE56

3

P36

P34

VCC_CORE57

VCC_CORE58

VCC_CORE59

VCC_CORE60

VCC_CORE61

P32M4M6M2K36

VCC_CORE62

VCC_CORE63

VCC_CORE64

VCC_CORE65

VCC_CORE66

K34

K32H4H2

AM14

VCC_CORE67

VCC_CORE68

VCC_CORE69

VCC_CORE70

VCC_CORE71

F36

F34

F32

F28

F24

VCC_CORE72

VCC_CORE73

VCC_CORE74

VCC_CORE75

VCC_CORE76

F20

F16

F12

D32

D28

VCC_CORE77

VCC_CORE78

VCC_CORE79

VCC_CORE80

VCC_CORE81

AM10

D24

D20

D16

D12D8D4D2B36

VCC_CORE82

VCC_CORE83

VCC_CORE84

VCC_CORE85

VCC_CORE86

2

B32

VCC_CORE87

VCC_CORE88

VCC_CORE89

VCC_CORE90

VCC_CORE91

AM2

B28

B24

B20

B16

VCC_CORE92

VCC_CORE93

VCC_CORE94

VCC_CORE95

VCC_CORE96

B12B8B4

AJ5

VCC_CORE97

VCC_CORE98

VCC_CORE99

VCC_CORE100

VCC_CORE101

VCCA_PLL

AC7

AJ23

VCC_Z

VCC_A

NC1

NC2

NC3

NC6

NC7

NC8

NC9

NC10

NC11

NC12

NC13

NC15

NC16

NC17

NC18

NC19

NC20

NC21

NC22

NC23

NC24

NC25

NC27

NC28

NC29

NC30

NC31

NC32

NC33

NC34

NC35

NC36

NC37

NC42

NC43

NC44

NC45

BP0_CUT

BP1_CUT

BP2_CUT

BP3_CUT

0~100 mA

2.25~2.75V

CPU1B

N12-4620011-F02

AA31

AC31

AE31

AG23

AG25

AG31

AG5

AJ11

AJ15

AJ17

AJ19

AJ27

AL11

AN11

AN9

G11

G13

G27

G29

G31

J31

J5

L31

N31

Q31

S31

S7

U31

U7

W31

W7

Y31

Y5

AG19

G21

AG21

G19

AN27

AL27

AN25

AL25

BP0

BP1

BP2

BP3

VCCA_PLL

R418

X_0

THERMDP 40

THERMDN 40

1

C81 1U_0805

VTIN2 27,28

BP[0..4]

BP[0..4] 38

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

H14

H18

H22

H26

M30P8R30T8V30X8Z30

B B

CPU1C

XX1

GND

XX2

GND

YY24

GND

YY23

GND

YY22

GND

YY21

GND

YY20

GND

YY19

GND

YY18

GND

YY17

GND

YY16

GND

YY15

GND

YY14

GND

YY13

GND

YY12

GND

A A

N12-4620011-F02

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GNDGND

AO1

AO2

AO3

AO4

YY1

YY2

YY3

YY4

YY5

YY6

YY7

YY8

YY9

YY10YY11

AB8

AF12

AF16

AF20

AF24

AM36

AK32

AK28

AK24

AK20

AK16

AK12

AK4

AK2

AH36

AM32

AH34

AH32

AH28

AH24

AH20

AH16

AH12

AF4

AF2

AD36

AD34

AD32

AB6

AB4

AB2

Z36

Z34

Z32X6AM28X4X2

CPU DECOUPLING CAPACITORS

V_COREV_CORE V_CORE V_CORE

C24 224P

C26 224P

C37 224P

C101 224P

C91 224P

C86 224P

C61 224P

C28 224P

C84 224P

C102 224P C104 224P

C72 224P

C27 224P

C77 224P

C75 224P

V36

V34

V32T6T4T2R36

V_CORE

R34

AM24

R32P6P4P2M36

C103 224P

C105 224P

C53 224P

C66 224P

C44 224PC93 224P

C33 224P

M34

M32K6K4K2AM20

H36

H34

C100 39P

C94 39P

C83 39P

C25 39P

C95 39P

C76 39P

C62 39P

C96 39P

F26

F22

F18

F14

F10F6F4F2AM16

D36

D34

D30

C38 39P

C73 39P

C31 39P

C52 39P

C98 39P

C99 39P

C32 39P

C34 39P

C90 39P

D26

D22

D18

D14

D10D6B34

AM12

B30

B26

V_CORE

B22

B18

B14

C51 X_39P

C64 X_39P

C74 X_39P

C41 X_39P

C63 X_39P

C54 X_39P

C89 X_39P

C67 X_39P

B10B6B2

DECOUPLING CAPACITOR INSIDE SOCKET

5

4

3

2

AM4

AK6

AM6

VSS_Z

AE7

Title

Document Number

place on solder side

inside socket

Micro Star Restricted Secret

Socket A_Power

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jun g-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

MS-6561

V_CORE

C78 4.7U_0805

C39 4.7U_0805

C82 4.7U_0805

C43 4.7U_0805

C87 4.7U_0805

C88 4.7U_0805

C65 4.7U_0805

C97 4.7U_0805

Last Revision Date:

Monday, January 21, 2002

Sheet

6 42

1

Rev

1.0

of

5

4

3

2

1

AMD 462PGA Socket - Pull up / down Block

D D

PLLTEST#

PLLTEST#5

DBREQ#

DBREQ#5

TMS

TMS5

TRST#

TRST#5

TDI

TDI5

TCK

TCK5

**All CPU interface are

C C

2.5V tolerant**

RN9

1 2

3 4

5 6

7 8

8P4R-510

RN5

1 2

3 4

5 6

7 8

8P4R-510

CPU APIC BLOCK CPU PULL-UP / DOWN BLOCK

V_CORE

V_CORE

SCANCLK25

SCANCLK15

SSHIFTEN5

PLLBYCLK5

PLLBYCLK#5

SCANCLK2

SCANCLK1

SINTVAL

SINTVAL5

SSHIFTEN

PLLBYCLK

PLLBYCLK#

RN1

1 2

3 4

5 6

7 8

8P4R-270

RN19

1 2

3 4

5 6

7 8

8P4R-100

V_CORE

V_CORE

COREFB+5

COREFB+

COREFB-

COREFB-5

R28 10K

C449

2.2u

R31 10K

VCC2_5

APICD05,11

APICD15,11

B B

A A

5

APICD0

APICD1

for test only

Pull to VCCA_PLL

R373 330

R372 330

CPURST#5,8

4

IGNNE#

IGNNE#5,11

CPURST#

A20M#

A20M#5,11

STPCLK#

STPCLK#5,11

SMI#

SMI#5,11

NMI

NMI5,11

INTR

INTR5,11

INIT#_39491

INIT#5,11

FLUSH#

FLUSH#5

PLLBP#

PLLBP#5

PLLMON1

PLLMON15

PLLMON2

PLLMON25

3

RN10

1 2

3 4

5 6

7 8

8P4R-680

RN13

1 2

3 4

5 6

7 8

8P4R-680

R23 680

R50 680

R36 56

R35 56

V_CORE

V_CORE

V_CORE

V_CORE

SADI#0

SADI#05

SADI#1

SADI#15

SDOVAL#5

SFILLVAL#

SDOVAL#

VREFMODE

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jun g-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

SFILLVAL#5

VREFMODE5

2

R51 270

R52 270

R53 270

R54 270

R12 270

Micro Star Restricted Secret

V_CORE

Socket A_Pull up / Pull down

MS-6561

Last Revision Date:

Wednesday, January 2 3, 2002

Sheet

7 42

1

Rev

1.0

of

V_CORE

5

4

3

2

1

SiS 745 Host and AGP

R64

100RST

R65

D D

100RST

C C

C122

X_104P

SHOULD NOT BE CROSS POWER PLANE

B B

A A

V_CORE

V_CORE

C126

103P

C121

103P

733CCLK3

SDIVAL#5

CPURST#5,7

PROCRDY5

CONNECT5

CFWDRST5

SADDINCLK#5

SADOCLK#5

R63

60.4RST

733CCLK

R374

X_60.4RST

R74 40.2RST

R73 40.2RST

VCC3_3

VCC3_3

C119

102P

R75 0

C140

104P

C124

104P

5

C118

105P

VDDREF

VSSREF

HSTLREF

733CCLK

SDIVAL#

CPURST#

PROCRDY

CONNECT

CFWDRST

S2KCOMPND

S2KCOMPPD

SADDINCLK#

SADDOUTCLK#

C139

104P

R60 0

HSTLREF

C120

104P

SDATAINCLK#0

SDATAINCLK#1

SDATAINCLK#2

SDATAINCLK#3

SDOCLK#0

SDOCLK#1

SDOCLK#2

SDOCLK#3

SADI#2

SADI#3

SADI#4

SADI#5

SADI#6

SADI#7

SADI#8

SADI#9

SADI#10

SADI#11

SADI#12

SADI#13

SADI#14

SADO#2

SADO#3

SADO#4

SADO#5

SADO#6

SADO#7

SADO#8

SADO#9

SADO#10

SADO#11

SADO#12

SADO#13

SADO#14

S2KCOMPND

S2KCOMPPD

CPUPHYAVDD

C141

103P

C117

104P

VCC1_8

R28

R27

R29

AA27

E24

C21

F23

D24

D23

A23

A22

F24

W24

F27

K24

N28

U29

F25

L24

M24

R25

B27

A26

C25

C27

D25

D26

B26

B24

B25

A27

B23

A24

C23

W27

W26

V25

W29

W28

AA26

Y24

Y27

Y29

V26

Y26

Y25

AA24

C110

104P

C116

103P

R55 0

VDDREF

VSSREF

HSTLREF

CPUCLK

SDATAINVAL#

CPURST#

PROCRDY

CONNECT

CLKFWDRST

S2KCOMPND

S2KCOMPPD

SADDINCLK#

SADDOUTCLK#

SDATAINCLK#0

SDATAINCLK#1

SDATAINCLK#2

SDATAINCLK#3

SDATAOUTCLK#0

SDATAOUTCLK#1

SDATAOUTCLK#2

SDATAOUTCLK#3

SADDIN#2

SADDIN#3

SADDIN#4

SADDIN#5

SADDIN#6

SADDIN#7

SADDIN#8

SADDIN#9

SADDIN#10

SADDIN#11

SADDIN#12

SADDIN#13

SADDIN#14

SADDOUT#2

SADDOUT#3

SADDOUT#4

SADDOUT#5

SADDOUT#6

SADDOUT#7

SADDOUT#8

SADDOUT#9

SADDOUT#10

SADDOUT#11

SADDOUT#12

SADDOUT#13

SADDOUT#14

CPUPHYAVDD

CPUPHYAVSS

A21

B22

CPUAVDD

C109

104P

HOST

CPUAVDD

CPUAVSS

SDATA#63

SDATA#62

AA29

AA28

V24

U26

V29

SDATA#63

SDATA#62

VDDREF

C108

103P

VSSREF

SDATA#61

SDATA#60

SDATA#59

U27

U25

T29

SDATA#58

SDATA#59

SDATA#61

SDATA#60

4

SDATA#58

SDATA#57

SDATA#56

SDATA#55

T28

T27

T24

SDATA#57

SDATA#56

SDATA#55

AAD5

AAD4

AAD1

AAD0

AAD2

Y3Y2Y1Y5W4W3W6W1V4W5U5V6V3U4U6U3R4R3R2R1N6P3P6P4P5N2N3M5N4N5M6M1M2M3M4K5K6L4L1

AAD0

AAD1

AAD2

AAD3

AAD3

AAD4

AAD6

AAD5

AAD7

AAD6

AAD8

AAD7

AAD9

AAD8

745-1

SDATA#54

SDATA#53

SDATA#52

SDATA#51

SDATA#50

SDATA#49

SDATA#48

SDATA#47

SDATA#46

SDATA#45

SDATA#44

SDATA#43

SDATA#42

SDATA#41

SDATA#40

SDATA#39

T26

V27

U24

SDATA#52

SDATA#53

SDATA#54

R24

R26

V28

SDATA#50

SDATA#51

SDATA#49

P26

P27

N26

M29

N27

SDATA#46

SDATA#47

SDATA#45

SDATA#48

SDATA#[0..63]

SADI#[2..14]

SADO#[2..14]

SDATAINCLK#[0..3]

SDOCLK#[0..3]

M28

M27

L27

SDATA#44

SDATA#41

SDATA#42

SDATA#43

SDATA#38

L29

P29

N29

SDATA#38

SDATA#40

SDATA#39

P24

SDATA#37

AAD10

AAD12

AAD11

AAD9

AAD10

AAD11

AAD12

SDATA#37

SDATA#36

SDATA#35

SDATA#34

P25

N24

M26

SDATA#36

SDATA#35

SDATA#34

AAD13

AAD16

AAD15

AAD14

AAD17

AAD13

AAD14

AAD15

AAD16

SDATA#33

SDATA#32

SDATA#31

SDATA#30

M25

L26

K28

L25

K26

SDATA#33

SDATA#30

SDATA#29

SDATA#31

SDATA#32

SDATA#[0..63] 5

SADI#[2..14] 5

SADO#[2..14] 5

SDATAINCLK#[0..3] 5

SDOCLK#[0..3] 5

3

AAD20

AAD19

AAD18

AAD17

AAD18

AAD19

AAD20

SDATA#29

SDATA#28

SDATA#27

SDATA#26

J25

H26

J26

SDATA#28

SDATA#27

SDATA#26

AAD23

AAD22

AAD21

AAD21

AAD22

AAD23

SDATA#25

SDATA#24

SDATA#23

J24

H25

J29

SDATA#24

SDATA#25

SDATA#23

AAD25

AAD26

AAD24

AAD24

AAD25

AAD26

SDATA#22

SDATA#21

SDATA#20

K29

J28

K27

SDATA#20

SDATA#21

SDATA#22

AAD27

AAD27

SDATA#19

J27

SDATA#19

AAD29

AAD31

AAD28

AAD30

SBA7

AAD29

AAD30

AAD31

SBA7

AAD28

AGP

SDATA#18

SDATA#17

SDATA#16

SDATA#15

SDATA#14

SDATA#13

SDATA#12

G29

H24

D27

SDATA#16

SDATA#17

SDATA#14

SDATA#15

SDATA#11

D28

G24

C29

SDATA#13

SDATA#12

SDATA#11

H29

H27

SDATA#18

SBA4

SBA5

SBA6

SBA6

SBA5

SBA4

SDATA#10

SDATA#9

SDATA#8

E26

C28

F26

SDATA#10

SDATA#9

SDATA#8

SBA1

SBA2

SBA3

SBA3

SBA2

SDATA#7

SDATA#6

G28

G27

F29

SDATA#6

SDATA#7

SDATA#5

SBA0

K1

SBA1

SBA0

SDATA#5

SDATA#4

SDATA#3

F28

E27

E29

SDATA#4

SDATA#3

U6A

AC/BE#3

AC/BE#2

AC/BE#1

AC/BE#0

AREQ#

AGNT#

AFRAME#

AIRDY#

ATRDY#

ADEVSEL#

ASERR#

ASTOP#

APAR

RBF#

WBF#

PIPE#

ST2

ST1

ST0

SB_STB

SB_STB#

AD_STB0

AD_STB#0

AD_STB1

AD_STB#1

AGPCLK

AGPVREF

AGPCOMP

AGPAVDD0

AGPAVSS0

AGPAVDD1

AGPAVSS1

AGPVSSREF

SDATA#2

SDATA#1

SDATA#0

G26

D29

SDATA#0

SDATA#1

SDATA#2

2

L6

T1

U2

Y6

J1

J6

T2

T3

T4

R6

U1

T6

T5

J4

K4

J3

J5

K3

J2

L3

L2

V2

V1

N1

P1

H3

AA1

AA2

F1

E1

H1

H2

Y4

SIS745

AC_BE#3

AC_BE#2

AC_BE#1

AC_BE#0

AREQ#

AGNT#

AFRAME#

AIRDY#

ATRDY#

ADEVSEL#

ASERR#

ASTOP#

APAR

RBF#

WBF#

PIPE3

ST2

ST1

ST0

SB_STB

SB_STB#

AD_STB0

AD_STB#0

AD_STB1

AD_STB#1

733ACLK

AVREFGC

AGPRCOMP

AGPAVDD0

AGPAVSS0

AGPAVDD1

AGPAVSS1

AAD[0..31]

SBA[0..7]

AC_BE#[0..3]

ST[0..2]

AD_STB[0..1]

AD_STB#[0..1]

AREQ# 20

AGNT# 20

AFRAME# 20

AIRDY# 20

ATRDY# 20

ADEVSEL# 20

ASERR# 20

ASTOP# 20

APAR 20

RBF# 20

WBF# 20

PIPE# 20

SB_STB 20

SB_STB# 20

733ACLK 3

AVREFGC 20

AGPAVDD0

C172

104P

AGPAVSS0

AGPAVDD1

C184

104P

AGPAVSS1

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jun g-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

SiS 745 Host/AGP

AAD[0..31] 20

SBA[0..7] 20

AC_BE#[0..3] 20

ST[0..2] 20

AD_STB[0..1] 20

AD_STB#[0..1] 20

Place

these circuits

near to SiS745

AGPRCOMP

AVREFGC

L15

80_0805

C183

103P

L16

80_0805

C173

103P

MS-6561

Last Revision Date:

Friday, January 18, 2002

Sheet

1

VDDQ

R113

60.4RST

C170

104P

VCC3_3

EC30

10U/16VS

8 42

of

Rev

1.0

5

DMD1

DMD5

DMD0

DMD4

DMD6

DMD2

DDQS0

D D

DDQM0

DMD8

DMD3

DMD7

DMD11

DMD10

DMD15

DMD14

DDQM1

DDQS1

DMD12

DMD17

DDQS2

DMD16

DMD20

DMD22

DMD18

C C

B B

DDQM2

DMD21

DMD28

DMD24

DMD23

DMD19

DMD31

DMD27

DMD30

DMD26

DDQM3

DDQS3

DMD25

DMD29

DMD33

DMD37

DMD32

DMD36

DMD38

DDQM4

DMD34

DMD40

DMD44

DMD35

DMD39

DDQM5

DMD41

DMD45

DMD47

DMD46

DMD43

DMD42

DMD55

DMD54

DDQS6

DDQM6

A A

DMD53

DMD49

DMD52

DMD48

DMD56

DMD60

DMD51

DMD50

RN88 10-0603

1 2

3 4

5 6

7 8

RN90 10-0603

1 2

3 4

5 6

7 8

RN91 10-0603

1 2

3 4

5 6

7 8

RN93 10-0603

1 2

3 4

5 6

7 8

RN95 10-0603

1 2

3 4

5 6

7 8

RN97 10-0603

1 2

3 4

5 6

7 8

RN99 10-0603

1 2

3 4

5 6

7 8

RN94 10-0603

RN92 10-0603

RN103 10-0603

1 2

3 4

5 6

7 8

RN104 10-0603

1 2

3 4

5 6

7 8

RN105 10-0603

1 2

3 4

5 6

7 8

RN102 10-0603

RN107 10-0603

1 2

3 4

5 6

7 8

RN108 10-0603

1 2

3 4

5 6

7 8

RN109 10-0603

1 2

3 4

5 6

7 8

RN110 10-0603

1 2

3 4

5 6

7 8

RN111 10-0603

1 2

3 4

5 6

7 8

5

MD1

MD5

MD0

MD4

MD6

MD2

DQS0

DQM0

MD8

MD13DMD13

MD3

MD7

MD11

MD10

MD15

MD14

DQM1

DQS1

MD9DMD9

MD12

MD17

DQS2

MD16

MD20

MD22

MD18

DQM2

MD21

MD28

78

MD24

56

MD23

34

MD19

12

MD31

78

MD27

56

MD30

34

MD26

12

DQM3

DQS3

MD25

MD29

MD33

MD37

MD32

MD36

MD38

DQM4

DQS4DDQS4

MD34

MD40

78

MD44

56

MD35

34

MD39

12

DQM5

MD41

DQS5DDQS5

MD45

MD47

MD46

MD43

MD42

MD55

MD54

DQS6

DQM6

MD53

MD49

MD52

MD48

MD56

MD60

MD51

MD50

DDQS7

DDQM7

DMD61

DMD57

DMD59

DMD63

DMD58

DMD62

4

RN87 10-0603

1 2

3 4

5 6

7 8

RN89 10-0603

1 2

3 4

5 6

7 8

DQS7

DQM7

MD61

MD57

MD59

MD63

MD58

MD62

DMD[0..63]

DDQM[0..7]

DMA[0..14]

DDQS[0..7]

DCS-[0..5]

3

DMD[0..63] 14,15,16

DDQM[0..7] 14,15,16

SiS 745 Memory

DMA[0..14] 14,15,16

DDQS[0..7] 14,15,16

DCS-[0..5] 14,15,16

U6B

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

DQM0

DQS0

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

DQM1

DQS1

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

DQM2

DQS2

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

DQM3

DQS3

MD32 735CKE MCKE

MD33

MD34

MD35

MD36 733DCLK

MD37

MD38

MD39

DQM4

DQS4

MD40

MD41

MD42 SDAVDD

MD43

MD44 SDAVSS

MD45

MD46

MD47

DQM5

DQS5

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

DQM6

DQS6

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

DQM7

DQS7

AD28

AB26

AC26

AC24

AD29

AB25

AD26

AE29

AB24

AD27

AF29

AD25

AG29

AF26

AF28

AE27

AD24

AH28

AE26

AF27

AG26

AE24

AJ26

AJ25

AG27

AJ27

AH25

AG25

AF25

AH27

AF22

AD21

AH22

AD20

AE22

AG23

AE21

AF21

AG22

AJ23

AE18

AF18

AH18

AG17

AD17

AH19

AG18

AF17

AD16

AJ18

AE15

AG14

AJ13

AD13

AD14

AJ15

AH13

AG13

AF14

AJ14

AF13

AD12

AF12

AE12

AJ12

AE13

AD11

AJ11

AG12

AH12

AG11

AF11

AG10

AE9

AE10

AJ10

AF10

AJ9

AD10

AH10

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

DQM0

DQS0

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

DQM1

DQS1

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

DQM2

DQS2

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

DQM3

DQS3

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

DQM4

DQS4

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

DQM5

DQS5

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

DQM6

DQS6

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

DQM7

DQS7

745-2

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

MA13

MA14

RAS#

CAS#

WE#

CSA#0

CSA#1

CSA#2

CSA#3

CSA#4

CSA#5

CKE

SDCLK

SDRCLKI

FWDSDCLKO

SDAVDD

SDAVSS

DDRAVDD

DDRAVSS

DDRVREFH

DDRVREF

DDRVREFL

DDRVSSREF

AD18

AG20

AD19

AF20

AJ21

AH24

AJ24

AG24

AD22

AF23

AF19

AJ17

AG19

AD23

AF24

AG16

AD15

AF16

AE16

AH16

AJ16

AH15

AG15

AF15

C10

AB27

AJ20

AJ19

AB29

AB28

AC29

AC27

AJ22

AH21

AG21

AE19

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

MA13

MA14

RAS#

CAS#

DDWE#

DDRAVDD

DDRAVSS

DDRVREFH

DDRVREF0

DDRVREFL

R447 0

R448 0

R449 0

R450 0

R451 0

R453 0

MA0

MA1

MA2

MA3

MA4

MA6

MA5

MA8

MA10

MA12

MA11

MA14

MA13

MA9 DMA9

MA7

DRASDCAS-

DWE-

RN106 8P4R-0

R455 22

C426

10P

SIS745

4

3

RN101 8P4R-0

RN100 8P4R-0

RN96 8P4R-0

1 2

3 4

5 6

7 8

RN98 8P4R-0

1 2

3 4

5 6

7 8

78

56

34

12

DCS-4

DCS-5

733DCLK 3

FWDCLK_DDR

DDRVREFL

2

DMA0

12

DMA1

34

DMA2

56

DMA3

78

DMA4

12

DMA6

34

DMA5

56

DMA8

78

DMA10

DMA12

DMA11

DMA14

DMA13

DMA7

DRAS- 14,15,16

DCAS- 14,15,16

DWE- 14,15,16

DCS-2

DCS-0

DCS-3

DCS-1

MCKE 15,34

FWDCLK_DDR 4

12

BC34

0.1u

12

BC36

0.1u

2

VCC2_5

SDAVDD

SDAVSS

DDRAVDD

DDRAVSS

DDRVREFH

R457

274RST

R459

191RST

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jun g-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

C422

104P

C424

104P

12

BC31

0.1u

12

BC32

0.1u

DDRVREF0

1

L48

1 2

121S

C423

103P

1 2

C425

103P

VCC2_5

12

BC33

0.1u

12

BC35

0.1u

SiS 745 Memory

MS-6561

Last Revision Date:

Thursday, January 1 7, 2002

Sheet

1

L49

121S

R452

191RST

R454

274RST

VCC3_3

EC60

X_10U/16VS

VCC3_3

VCC2_5

R456

150RST

R458

143RST

9 42

of

EC61

10U/16VS

Rev

1.0

5

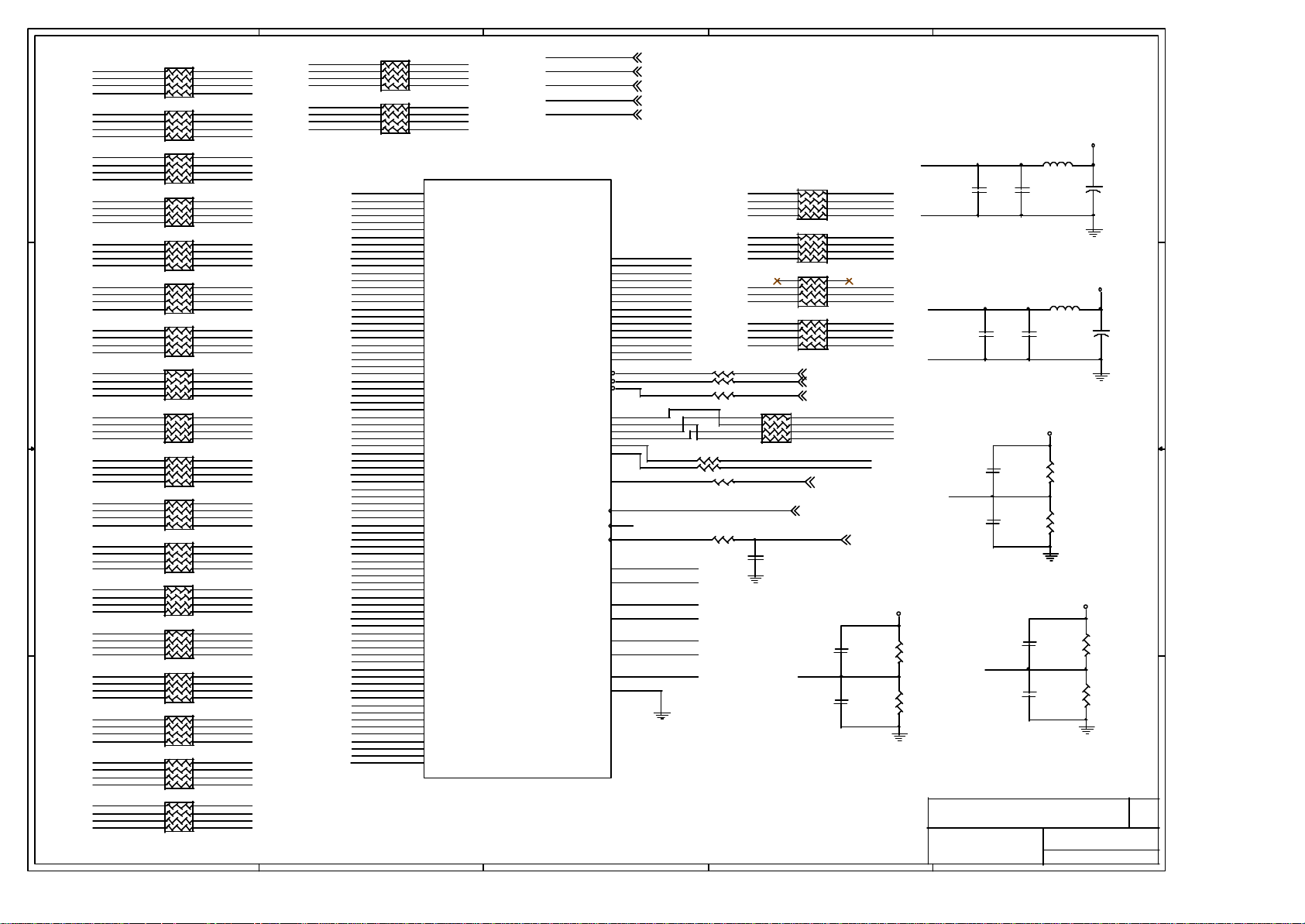

SiS 745 PCI and IDE

4

3

2

1

D D

C C

B B

AD[0..31]13,17,18,19,38

PREQ#[0..3]17,18,19

PGNT#[0..4]17,18,19

C/BE#[0..3]13,17,18,19

AD[0..31]

PREQ#[0..3]

PGNT#[0..4]

C/BE#[0..3]

INTA#17,18,19,20

INTB#17,18,19,20

INTC#17,18,19

INTD#17,18,19

FRAME#17,18,19

IRDY#17,18,19

TRDY#17,18,19

STOP#17,18,19

SERR#17,18,19

PAR13,17,18,19

DEVSEL#17,18,19

733PCLK3

PCIRST#33

INTC#

INTD#

INTB#

INTA#

INTA#

INTB#

INTC#

INTD#

FRAME#

IRDY#

TRDY#

STOP#

SERR#

PAR

DEVSEL#

733PCLK

PCIRST#

PREQ#3

PREQ#2

PREQ#1

PREQ#0

PGNT#4

PGNT#3

PGNT#2

PGNT#1

PGNT#0

C/BE#3

C/BE#2

C/BE#1

C/BE#0

R99 33

R381

4.7K

RN37

1 2

3 4

5 6

7 8

8P4R-8.2K

VCC3_3

H18

D18

A18

C18

E17

C19

AH8

A11

E9

B7

E8

B6

A6

B3

E4

H9

C7

H8

C3

F2

D4

C2

D3

C1

D1

F6

PREQ#3

PREQ#2

PREQ#1

PREQ#0

PGNT#4

PGNT#3

PGNT#2

PGNT#1

PGNT#0

C/BE#3

C/BE#2

C/BE#1

C/BE#0

INT#A

INT#B

INT#C

INT#D

FRAME#

IRDY#

TRDY#

STOP#

SERR#

PAR

DEVSEL#

PCICLK

PCIRST#

AD29

AD28

AD31

AD30

D7

F8A5B5E7C6B4D6C5F7A4E6A3C4D5B2F4E5D2E3E2F5F3G6G5G4H6G3G2H5G1H4

AD31

AD30

AD29

AD27

AD28

AD26

AD27

AD25

AD26

AD25

AD24

AD24

AD23

AD23

AD22

AD22

AD21

AD21

AD20

AD20

AD19

AD19

AD18

AD18

AD17

AD17

AD16

AD16

AD15

AD15

AD14

AD14

AD13

AD13

AD12

AD12

AD11

AD11

AD10

AD10

AD9

AD9

AD8

AD8

AD7

AD7

PCI

745-3

IDE

IDB0

IDB1

IDB2

IDB3

IDB4

IDB5

IDB6

IDB7

IDB8

IDB9

IDB10

IDB11

IDB12

IDB13

IDB14

IDB15

IDA0

IDA1

IDA2

IDA3

IDA4

IDA5

IDA6

AD7

SDD0

AF7

SDD1

AJ5

SDD2

AG5

SDD3

AE6

SDD4

AE5

SDD5

AJ4

SDD6

AD6

SDD7

AG4

SDD8

AH4

SDD9

AF5

AF6

SDD10

AH5

SDD11

SDD12

AG6

AH6

SDD13

AJ6

SDD15

SDD14

AF1

PDD0

AE2

AC5

PDD1

AD3

PDD2

AB5

PDD3

AB6

PDD4

AC3

PDD5

AA6

PDD6

IDA7

PDD7

AD6

AC2

PDD8

AD6

IDA8

AB4

AD5

AD5

IDA9

AD1

PDD9

AD4

AD3

AD4

AD3

IDA10

IDA11

AD2

PDD11

PDD10

AD2

AD2

IDA12

AE1

AC4

PDD12

AD0

AD1

AD1

AD0

IDA13

IDA14

AE3

PDD13

PDD14

IDA15

AF2

PDD15

U6C

IDEAVDD

ICHRDYA

IDREQA

IIRQA

CBLIDA/GP6

IIOR#A

IIOW#A

IDACK#A

IDSAA2

IDSAA1

IDSAA0

IDECSA#1

IDECSA#0

ICHRDYB

IDREQB

IIRQB

CBLIDB/GP7

IIOR#B

IIOW#B

IDACK#B

IDSAB2

IDSAB1

IDSAB0

IDECSB#1

IDECSB#0

SIS745

AJ8

AF3

AD4

AE4

AH3

AD5

AC6

AG1

AH2

AG2

AG3

AF4

AJ3

AJ7

AH7

AF9

AD9

AE7

AG7

AD8

AE8

AF8

AG8

AG9

AH9

PIORDY

PDREQ

IRQ14

PD_80P

PDIOR#

PDIOW#

PDACK#

PDA2

PDA1

PDA0

PDCS#1

PDCS#0

SIORDY

SDREQ

IRQ15

SD_80P

SDIOR#

SDIOW#

SDACK#

SDA2

SDA1

SDA0

SDCS#1

SDCS#0

PDA[0..2]

PDCS#[0..1]

SDA[0..2]

SDCS#[0..1]

PDD[0..15]

SDD[0..15]

C164

103P

PIORDY 21

PDREQ 21

IRQ14 21

PD_80P 21

PDIOR# 21

PDIOW# 21

PDACK# 21

SIORDY 21

SDREQ 21

IRQ15 21

SD_80P 21

SDIOR# 21

SDIOW# 21

SDACK# 21

PDA[0..2] 21

PDCS#[0..1] 21

SDA[0..2] 21

SDCS#[0..1] 21

PDD[0..15] 21

SDD[0..15] 21

R110 0

C159

104P

VCC1_8

C160

104P

A A

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jun g-He City,

Taipei Hsien, Taiwan

5

4

3

2

http://www.msi.com.tw

SiS 745 PCI / IDE

MS-6561

Last Revision Date:

Thursday, January 1 7, 2002

Sheet

1

10 42

Rev

1.0

of

5

4

3

2

1

SiS 745 Misc. Signals

PSON#34

ACPILED36

PWRBTN#36,40

PME#17,18,19,20,27

D D

AC_SDIN126

AC_SDIN024,26

AC_SDOUT24,26

AC_SYNC24,26

C C

B B

A A

KBDAT23

KBCLK23

MSDAT23

MSCLK23

OSCI3

AC_RST#24,26

AC_BITCLK24,26

SPK24,36

LAD[0..3]27

LDRQ#27

LFRAME#27

SIRQ27

NMI5,7

SMI#5,7

INTR5,7

A20M#5,7

INIT#5,7

IGNNE#5,7

FERR#5

STPCLK#5,7

APICCLK13

APICD05,7

APICD15,7

SDATA3,4,14,15,26,33,38

SCLK3,4,14,15,26,33,38

AUXOK34

BATOK34

PWROK33,38

UV0-22

UV0+22

UV1-22

UV1+22

UV2-26

UV2+26

UV3-22

UV3+22

UV4-22

UV4+22

UV5-26

UV5+26

UCLK48M3

5

PSON#

PWRBTN#

PME#

KBDAT

KBCLK

MSDAT

MSCLK

ENTEST

OSCI

AC_SDIN1

AC_SDIN0

AC_SDOUT

AC_SYNC

AC_RST#

AC_BITCLK

SPK

LAD0

LAD1

LAD2

LAD3

LDRQ#

LFRAME#

SIRQ

NMI

SMI#

INTR

A20M#

INIT#_39491

IGNNE#

FERR#

STPCLK#

GREEN#

APICCLK1

APICD0

APICD1

SDATA

SCLK

AUXOK

BATOK

PWROK

C146

100P

UV0UV0+

UV1UV1+

UV2UV2+

UV3UV3+

UV4UV4+

UV5UV5+

UCLK48M

RTCVDD

E12

B12

D12

C12

D13

E13

A12

B18

A19

D16

D20

E19

E18

A20

AB1

AA3

AA4

AA5

AB3

AB2

AC1

C22

B20

D21

E21

B21

E20

C20

E22

D22

C13

B13

E16

D17

C17

A17

A16

F13

F17

F19

F22

F20

F21

PSON#

ACPILED

PWRBTN#

PME#

KBDAT/GP24

KBCLK/GP25

PMDAT/GP26

PMCLK/GP27

ENTEST

OSCI

AC_SDIN1

AC_SDIN0

AC_SDOUT

AC_SYNC

AC_RESET#

AC_BIT_CLK

SPK

LAD0

LAD1

LAD2

LAD3

LDRQ#

LFRAME#

SIRQ

NMI

SMI#

INTR

A20M#

INIT#

IGNNE#

FERR#

STPCLK#

GREEN#

APICCK

APICD0

APICD1

GP28

GP29

AUXOK

BATOK

PWROK

RTCVDD

RTCVSS

C148

10P

Place close to 745

OSC32KHI

B17

10M

Y1

32.768KHZ

ACPI

KBC

AC97

LPC

745-4

CPU_S

APIC

RTC

OSC32KHO

B16

R94

C151

10P

4

UV5+

USBCLK48M

D10

F11

B19

UCLK48M

UV5+

UV5-

GPIO

USB

UV3+

UV4-

UV4+

UV5-

UV4+

UV3+

UV4-

UV3-

UV3-

UV2+

UV2+

UV2-

UV2-

F10D9A7C9E10B9A9

UV1+

UV1+

UV1-

UV1-

UV0+

D8F9C8

UV0+

UV0-

UV0-

104P

B8

C153

USBVDD0

USBVDD1

A8

U6D

DON'T need to place

RING

A15

GP1

PREQ#4

B15

GP2

EXTSMI#

F16

GP3

PHY_LINKON

C16

GP4

THERM#

D19

GP5

F18

GP9

GPIO11

C15

GP11

PHY_LREQ

E15

GP12

PHY_LPS

D15

GP13

PGNT#5

A14

GP14

GPIO16

F15

GP16

GPIO17

B14

GP17

DIRECT

C14

GP18

PHY_D0

D14

GP19

PHY_D4

F14

GP20

PHY_CTL0

E14

GP21

PHY_CTL1

A13

GP22

PHY_D1

B11

OC#0

PHY_D2

C11

OC#1

PHY_D3

D11

OC#2

PHY_D5

F12

OC#3

PHY_D6

B10

OC#4

PHY_D7

E11

OC#5

GND

SIS745

C156

105P

3

A10

VCC3SBY

12

EC22

+

47uF/10V

PHY_SCLK

R339

10K

RING 30

PREQ#4 17,19

EXTSMI# 36

PHY_LINKON 39

THERM# 27

RTCVDD

PHY_LREQ 39

PHY_LPS 39

DIRECT 39

PHY_D0 39

PHY_D4 39

PHY_CTL0 39

PHY_CTL1 39

PHY_D1 39

PHY_D2 39

PHY_D3 39

PHY_D5 39

PHY_D6 39

PHY_D7 39

PHY_SCLK 39

2

close to 745

PME#

GPIO11

PGNT#5

GPIO16

GPIO17

DIRECT

PHY_LPS

PHY_CTL1

PHY_CTL0

PHY_D0

PHY_D1

PHY_D2

PHY_D3

SDATA

SCLK

PHY_LINKON

PHY_LREQ

GREEN#

PHY_D4

PHY_D5

PHY_D6

PHY_D7

LAD0

LAD1

LAD2

LAD3

LDRQ#

SIRQ

ENTEST

AC_SDIN1

AC_SDIN0

Place near to 745

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jun g-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

R96 4.7K

RN36

1 2

3 4

5 6

7 8

8P4R-4.7K

RN38

7 8

5 6

3 4

1 2

8P4R-4.7K

RN39

1 2

3 4

5 6

7 8

8P4R-4.7K

R109 1.5K

R105 1.5K

R112 4.7K

R97 4.7K

R78 4.7K

RN40

1 2

3 4

5 6

7 8

8P4R-4.7K

1 2

3 4

5 6

7 8

R114 4.7K

R115 4.7K

R88 100K

R91 100K

AC_BITCLK

Micro Star Restricted Secret

SiS 745Misc. Signal

RN48

8P4R-4.7K

R81

4.7K

C142

X_10P

MS-6561

Last Revision Date:

Thursday, February 2 8, 2002

Sheet

1

VCC3SBY

VCC3_3

11 42

Rev

1.0

of

5

SiS 735 Power

4

3

VDDQ

2

1

V_CORE

SiS 735 Four Coner Decoupling Capacitor

AA25

W25

T25

N25

K25

G25

E25

E23

J18

J19

J20

K20

S2KOVDD

S2KOVDD

S2KOVDD

S2KOVDD

S2KOVDD

S2KOVDD

S2KOVDD

S2KOVDD

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jun g-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

U6E

S2KOVDD

S2KOVDD

S2KOVDD

S2KOVDD

S2KOVDD

S2KOVDD

S2KOVDD

S2KOVDD

S2KOVDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

SiS 745 Power

M21

M22

N21

P21

R20

R21

T21

U21

U22

H21

H22

J21

J22

K21

AH23

AH26

K2

P2

W2

A25

B28

C24

C26

E28

H28

L28

P28

U28

Y28

AC28

AE28

AG28

AH11

AH14

AH17

AH20

V18

V17

V16

M12

M13

M14

M15

M16

M17

M18

N12

N13

N14

N15

N16

N17

N18

P12

P13

P14

P15

P16

P17

P18

R12

R13

R14

R15

R16

R17

R18

T12

T13

T14

T15

T16

T17

T18

U12

U13

U14

U15

U16

U17

U18

V12

V13

V14

V15

MS-6561

Last Revision Date:

Friday, January 18, 2002

Sheet

1

12 42

of

Rev

1.0

VDDQ

VDDQ

2

V9

VDDQ

VDDQ

VDDQ

VDDQ

POWER

L5R5V5

VDDQ

VDDQ

VDDQ

735

S2KOVDD

S2KOVDD

S2KOVDD

S2KOVDD

M8M9M10N8N9P9R9

VCC2_5

C167

103P

VCC3_3

K13

K14

J10

J12

J16

K9

Y9

AA9

AA10

AB9

U20

V10

J15

K12

Y16

Y14

N10

Y12

T10

AE11

AE14

AE17

AE20

AE23

AE25

AC25

AB13

AB17

AB22

AB21

AB18

W21

Y18

Y20

Y21

Y22

AA12

AA13

AA14

AA15

AA16

AA17

AA18

AA20

AA21

AA22

AB12

K18

M20

P20

Y15

Y17

K10

K15

K16

K19

N20

P10

T20

U10

W20

Y10

Y13

J13

J14

J9

OVDD

OVDD

OVDD

OVDD

OVDD

OVDD

OVDD

OVDD

OVDD

OVDD

OVDD

PVDD

PVDD

PVDD

PVDD

PVDD

PVDD

PVDD

PVDD

PVDD

OVDD_DRAM

OVDD_DRAM

OVDD_DRAM

OVDD_DRAM

OVDD_DRAM

OVDD_DRAM

OVDD_DRAM

OVDD_DRAM

OVDD_DRAM

OVDD_DRAM

OVDD_DRAM

OVDD_DRAM

OVDD_DRAM

OVDD_DRAM

OVDD_DRAM

OVDD_DRAM

OVDD_DRAM

OVDD_DRAM

OVDD_DRAM

OVDD_DRAM

OVDD_DRAM

OVDD_DRAM

OVDD_DRAM

OVDD_DRAM

OVDD_DRAM

OVDD_DRAM

OVDD_DRAM

OVDD_DRAM

S2KPVDD

S2KPVDD

S2KPVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

AUX1.8

AUX3.3

SIS745

CLOSED TO VCCM PLANE OF 735

D D

VCC3_3 V_CORE

C149

104P

C150

C169

103P

104P

Component Side

C168

103P

C356

104P

Solder Side

C354

104P

C351

104P

SiS 735 Power Decoupling Capacitor

V_CORE

C C

C352

C125

C143

1U_0805

VCC1_8

C161

1U_0805

VDDQ

C176

B B

A A

C174

104P

104P

VCC3_3

EC27

10U/16VS

VCC2_5

C157

1U_0805

Component Side Solder Side

CLOSED TO VCCM PLANE OF 735

1U_0805

C194

1U_0805

C166

104P

C175

1U_0805

5

104P

C137

1U_0805

V_CORE

C353

104P

VCC1_8

C360

104P

VDDQ

C373

104P

VCC1_8SBY

C370

104P

VCC2_5

C367

104P

C362

104P

C349

104P

C355

104P

C374

104P

C348

104P

C350

104P

C365

104P

C364

104P

VCC3_3

C366

104P

4

C361

104P

C358

104P

C369

103P

C368

104P

C359

104P

C371

104P

C357

1U_0805

VCC1_8

VCC1_8SBY

VCC3SBY

C155

104P

3

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

R10T9U8U9V8

VDDQ

5

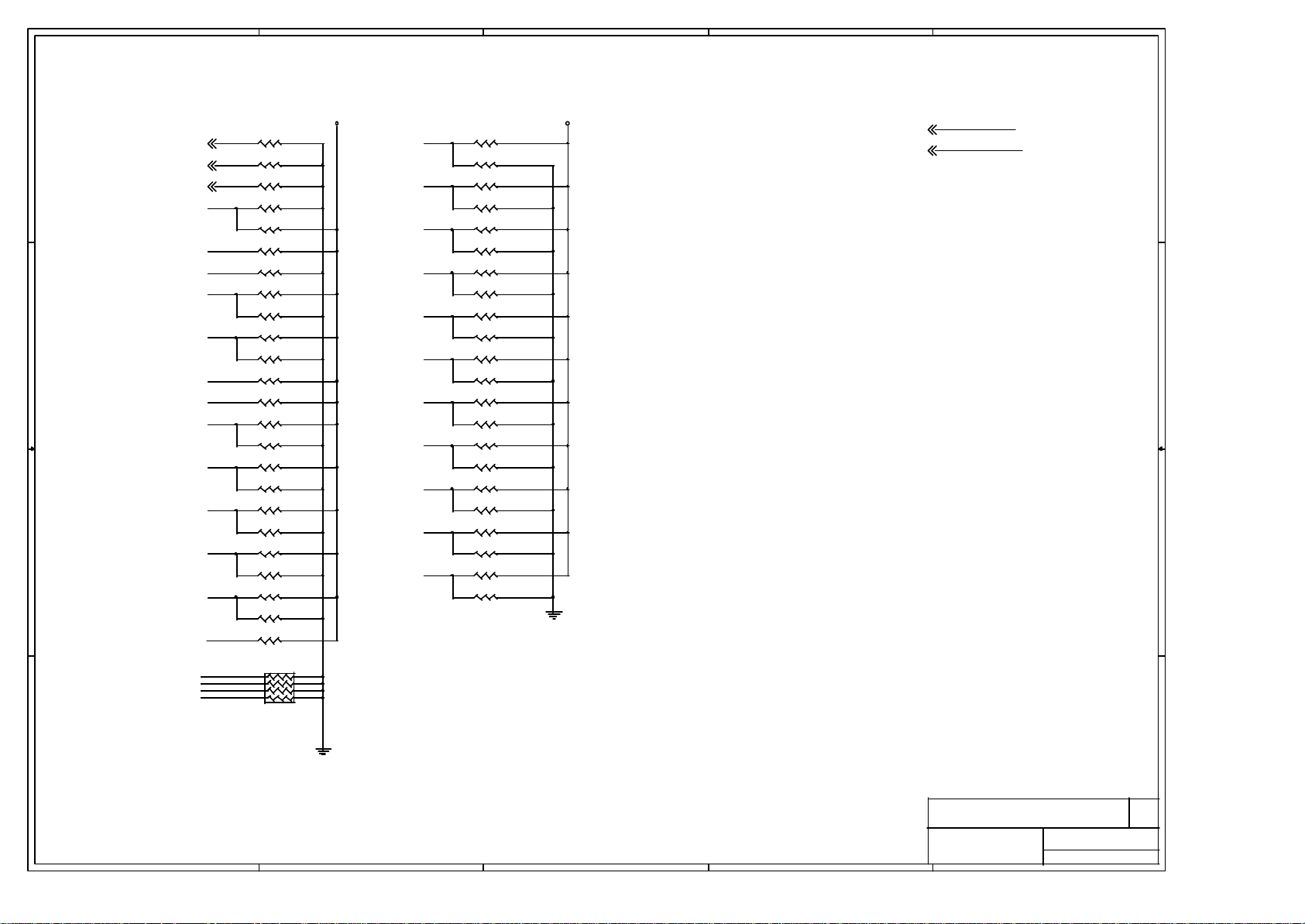

SiS 745 Hardware Trap Define

4

3

2

1

VCC3_3VCC3_3

AD10

AD9

AD8

AD7

AD6

AD5

AD4

AD3

AD2

AD1

AD0

R243 X_4.7K

R197 4.7K

R244 4.7K

R198 X_4.7K

R246 X_4.7K

R199 4.7K

R247 X_4.7K

R200 4.7K

R248 4.7K

R201 X_4.7K

R250 4.7K

R203 X_4.7K

R249 4.7K

R202 X_4.7K

R251 4.7K

R204 X_4.7K

R252 X_4.7K

R205 4.7K

R254 4.7K

R207 X_4.7K

R253 4.7K

R206 X_4.7K

AD31

AD30

AD28

AD27

AD26

AD25

AD24

AD23

AD22

AD21

AD20

AD15

AD29

R236 4.7K

R245 4.7K

R237 4.7K

R224 4.7K

R185 X_4.7K

R225 4.7K

R227 4.7K

R229 4.7K

R187 X_4.7K

R228 X_4.7K

R186 4.7K

R230 4.7K

R231 4.7K

R232 X_4.7K

R188 4.7K

R233 X_4.7K

R189 4.7K

R235 X_4.7K

R191 4.7K

R234 X_4.7K

R190 4.7K

R238 X_4.7K

R192 4.7K

R226 4.7K

RN82

1 2

3 4

5 6

7 8

8P4R-4.7K

D D

C C

B B

A A

PAR10,17,18,19

C/BE#010,17,18,19

C/BE#110,17,18,19

AD14

AD13

AD11

AD12

AD31: Allow the ROM addr ess

from FFF8_XXXX to FFFF_XXXXh

0:Disable (Reco mmend)

1:Enable

AD30: System Auto-Reset Function Enable

0:Disable

1:Enable (D efault)

AD28: Clock Forward Offs et

0:Delay 1000ps (Defa ult)

1 :No Delay

AD27: Processor Forward Clock Delay Mode

0:Disable

1:Enable (D efault)

AD26: Receiver Delay Enab le

0: Processor forward clock delay m ode

1: NB forward clock delay mode

AD23 AD22: S2K Bus Length

0 0 Short (D efault)

0 1

1 0

1 1 Long

AD21 AD20: System Clock Speed

0 0 100MHz (Def ault)

0 1 66MHz

1 0 90MHz

1 1 133MHz

AD15: Receive clock delay control mode

0: Use DLL control value

1: Use hardware tra p value

(AD[14..11]) (Default )

AD[14..11]: Receive Forward Clock Delay

0000:minimum delay

1111:maxmum d elay

AD[10..9]: Slew (Output Slew Rate )

00:minimum slew rate

11:maximum slew rate

AD8: S2K output Buffer Driving Strength Control Mode

0: Use conpensation logic control va lue

1: Use hardware trap value (AD[3..0] and

AD[7..4])

AD[7..4]: S2K output Buffer NMOS Driving Strength

0000: minimum driving strengt h

1111: maximum driving strength

AD[3..0]: S2K Output Buffer PMOS Driving Strength

0000: maximum driving strengt h

1111: minimum driving strengt h

PAR: CPU, SDRAM, PCI, AGP Clock

PLL/DLL Circuit Enabl e

0: Enable

1: Disable

C/BE#0: IDE Test Enabl e

0: Disable

1: Enable

C/BE#1: Debug Test Ena ble

0: Disable

1: Enable

AD[0..31]

AD[0..31]10,17,18,19,38

C/BE#[0..1]10,17,18,19

C/BE#[0..1]

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jun g-He City,

Taipei Hsien, Taiwan

5

4

3

2

http://www.msi.com.tw

SiS 745 Hardw are Straping

MS-6561

Last Revision Date:

Thursday, January 1 7, 2002

Sheet

1

13 42

Rev

1.0

of

5

DCS-[0..5]9,15,16

DDRCLK[0..8]4,15

DDRCLK-[0..8]4,15

DCS-[0..5]

CKE[0..5]

CKE[0..5]15

DDRCLK[0..8]

DDRCLK-[0..8]

4

DMD[0..63]9,15,16

DMA[0..14]9,15,16

DDQM[0..7]9,15,16

DDQS[0..7]9,15,16

DMD[0..63]

DMA[0..14]

DDQM[0..7]

DDQS[0..7]

3

2

1

V_DIMM

D D

C C

B B

DRAS-9,15,16

DCAS-9,15,16

DWE-9,15,16

A A

5

V_DIMM

DIM1

VDDQ

VDDQ

VSS

VSS

VDDQ

VDDQ

VSS

VSS

4

VDDQ

VDDQ

VREF

VDDID

VSS

VSS

VDDQ

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

WP

SCL

SDA

SA0

SA1

SA2

VSS

15223054627796

3111826344250586674818993

VDDQ

2

4

6

8

94

95

98

99

12

13

19

20

105

106

109

110

23

24

28

31

114

117

121

123

33

35

39

40

126

127

131

133

53

55

57

60

146

147

150

151

61

64

68

69

153

155

161

162

72

73

79

80

165

166

170

171

83

84

87

88

174

175

178

179

1

82

90

92

91

181

182

183

VSS

104

112

128

136

143

156

164

172

180738467085108

VDD

VDD

VDD

VDD

VDD

VDD

VSS

160

VSS

152

VSS

VDDQ

VSS

VSS

VSS

VSS

116

124

132

139

145

VCC3_3

120

VDD

148

VDD

168

VDD

184

DMA0

DMA1

DMA2

DMA3

DMA4

DMA5

DMA6

DMA7

DMA8

DMA9

DMA10

DMA13

DMA14

DMA11

DMA12

DDQM0

DDQM1

DDQM2

DDQM3

DDQM4

DDQM5

DDQM6

DDQM7

DDQS0

DDQS1 DMD34

DDQS2

DDQS3

DDQS4

DDQS5

DDQS6

DDQS7

DRASDCAS-

DWE-

DCS-0 DMD63

DCS-1

CKE0

CKE1

DDRCLK5

DDRCLK1

DDRCLK2

DDRCLK-5

DDRCLK-1

DDRCLK-2

48

43

41

130

37

32

125

29

122

27

141

118

115

103

59

52

113

97

107

119

129

149

159

169

177

140

5

14

25

36

56

67

78

86

47

44

45

49

51

134

135

142

144

9

10

101

102

173

167

154

65

63

157

158

71

163

21

111

137

16

76

138

17

75

VDDSPD

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

BA0

BA1

BA2

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

NC

NC(RESET#)

NC

NC

NC

NC(FETEN)

RAS#

CAS#

WE#

S0#

S1#

NC(S2#)

NC(S3#)

CKE0