8

7

6

5

4

3

2

1

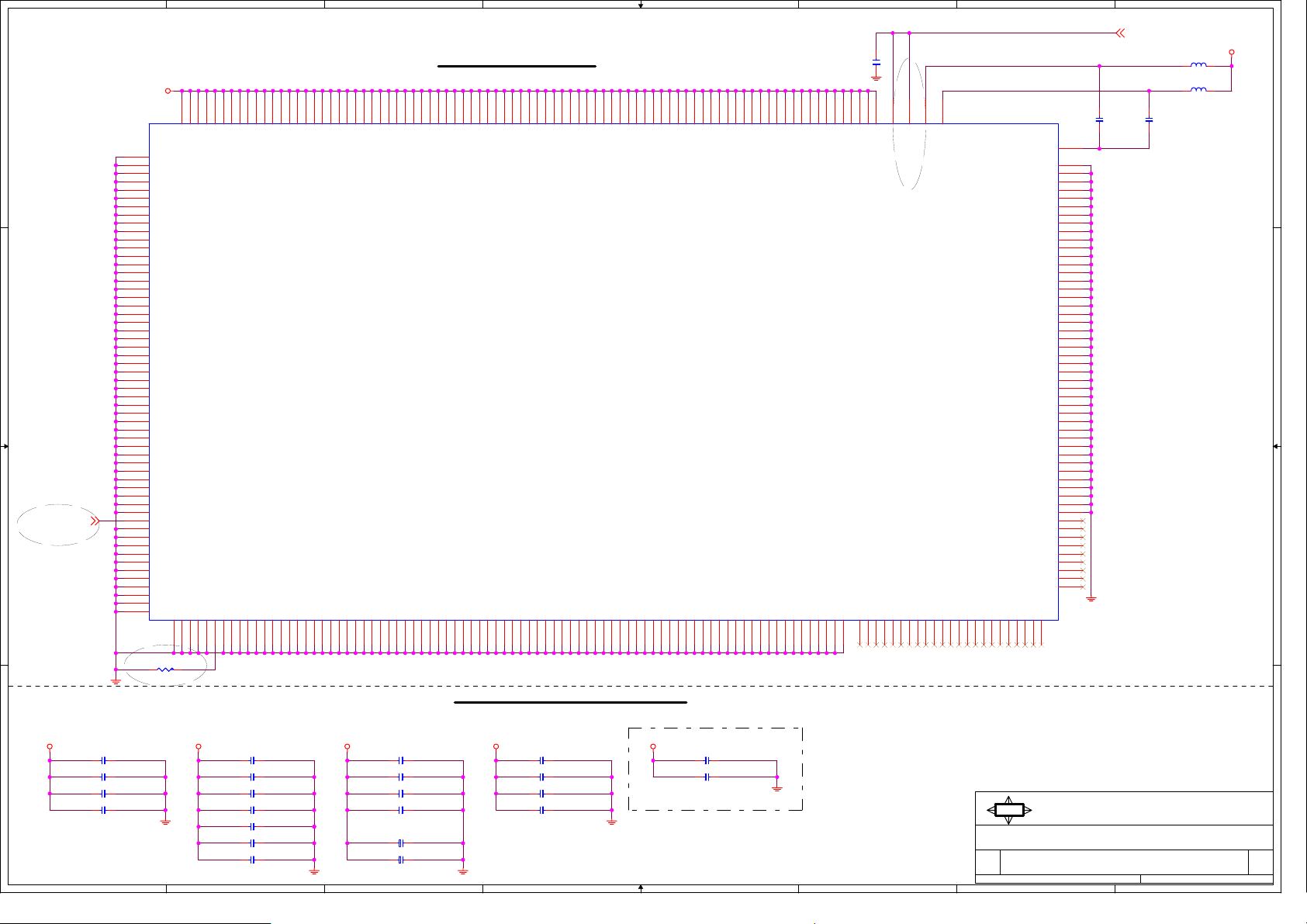

MS-6555

INTEL (R) Brookdale - GV Chipset

Version 40a FSB533

Cover Sheet

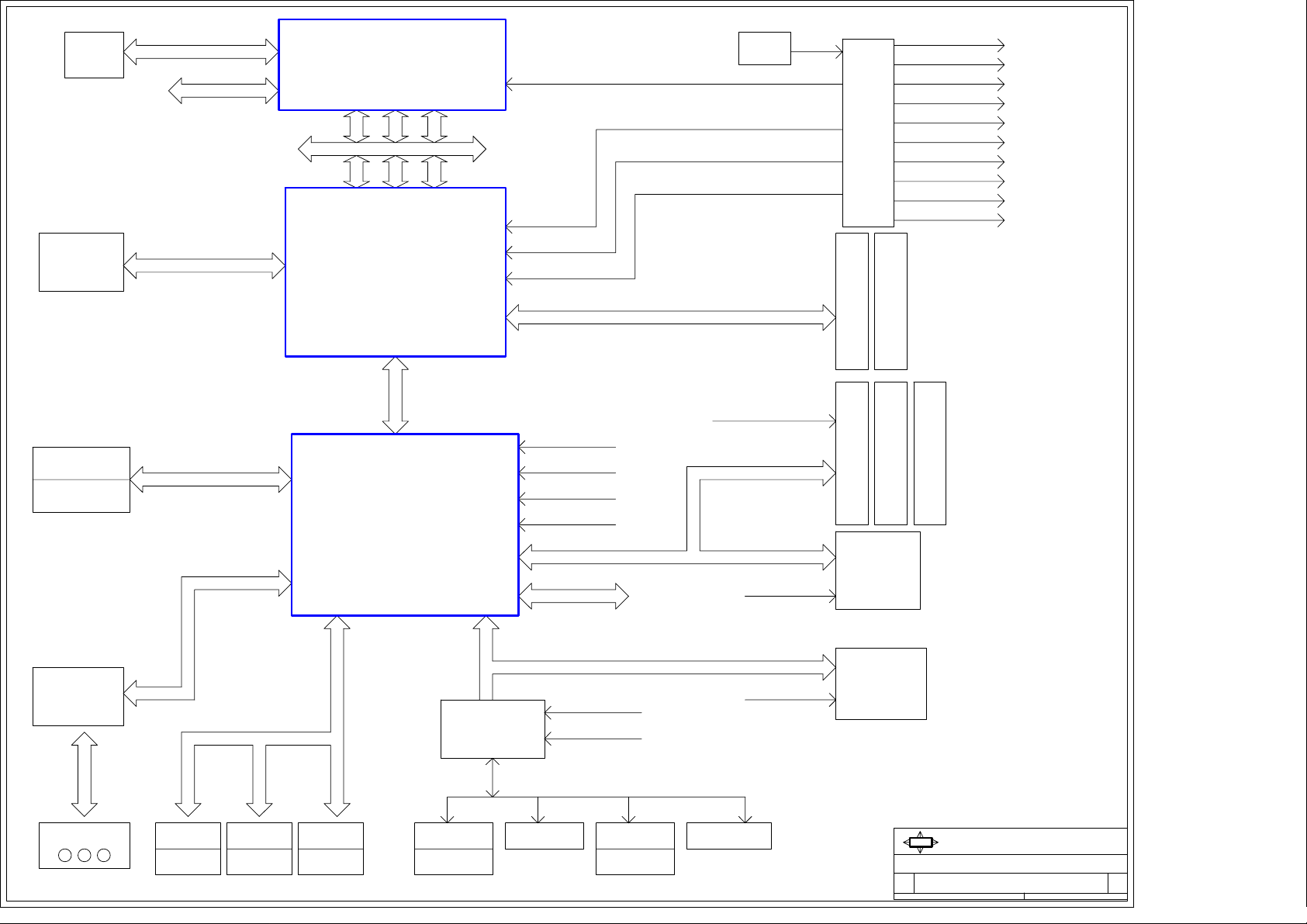

Block Diagram

1

2

Northwood / Presott 478pin mPGA-B Processor Schematics

D D

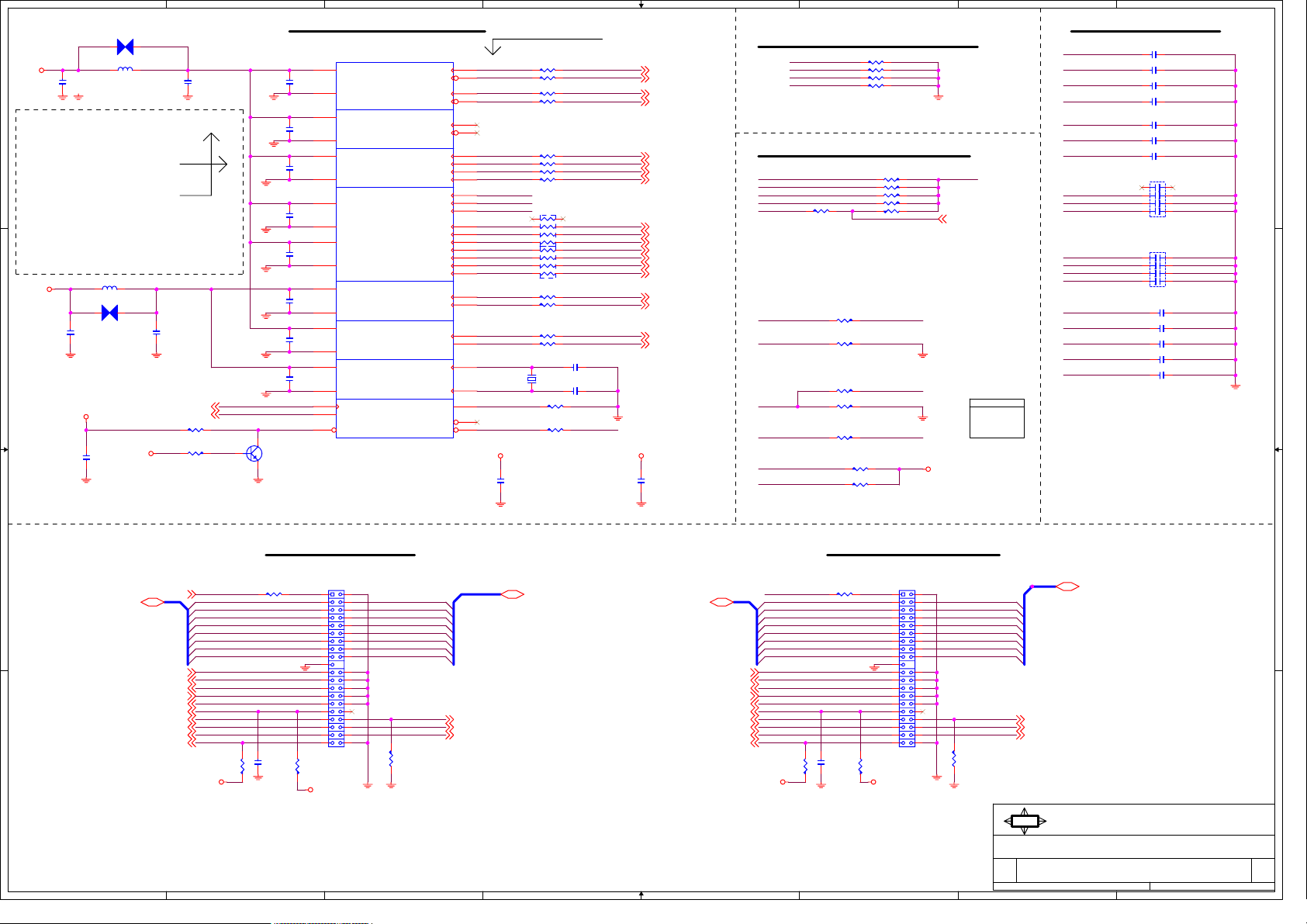

Clock CY28349 & ATA100 IDE Connector

3

CPU : Northwood / Presott mPGA-478B Processor

mPGA478-B INTEL CPU Sockets

4 - 5

System Brookdale - G / GL / GV / GE Chipset : INTEL GMCH + ICH4

INTEL Brookdale-G GMCH -- North Bridge

On Board Chipset:

INTEL ICH4 -- South Bridge

BIOS -- FWH

LPC Super I/O -- W83627THF-AW

Clock Generator -- CY28349B

C C

AC'97 Codec -- RealTek ALC655 / AD1888

Onboard Lan Chipset-- RealTek RTL8100C

Expansion Slots:

AGP2.0 Slot * 0

PCI2.2 Slot * 3

CNR Slot * 0

FWH

DDR DIMMM1,2

DDR Termination

PCI Slot 1 & 2 & 3

IO Connector

AC'97 Codec and Audio Connector

USB Connector

ACPI Controller (MS-5)

6 - 8

9 - 10

11LPC I/O - W83627THF-AW

12

13

14

15

16

17

18

19

VRM10 Intersil ISL6556B

20

Platform : Micro ATX ( 244 mm * 200 mm ; 9.61 inch * 8.03 inch)

B B

PCI LAN - Realtek RTL8100C

VGA Connector

Front Panel & Connectors & FAN

History

General SPEC

Jumper Setting & Manual Parts

A A

MS6555GV STD

(6555L2-40a-STD)

MS6555GV option: A

(6555L2-40a-A)

MS6555GL STD

8

ORCAD Config.MODEL Config. ERP NumberFunction Option

Cfg6555GV-ALC655 601-6555-19S

Cfg6555GV-AD1888

Cfg6555GL-ALC655

Cfg6555GL-AD1888 GL STD + AD1888

7

GV STD ( ALC655 )

GV STD + AD1888

GL STD ( ALC655 )

6

STD

A

GL

GLAMS6555GL option: A

601-6555-20S

5

MSI

Title

Size Document Number Rev

4

3

Date: Sheet

2

MICRO-STAR

COVER SHEET

MS-6555

21

22

23

24

25

27-28

127Wednesday, March 31, 2004

of

1

40a

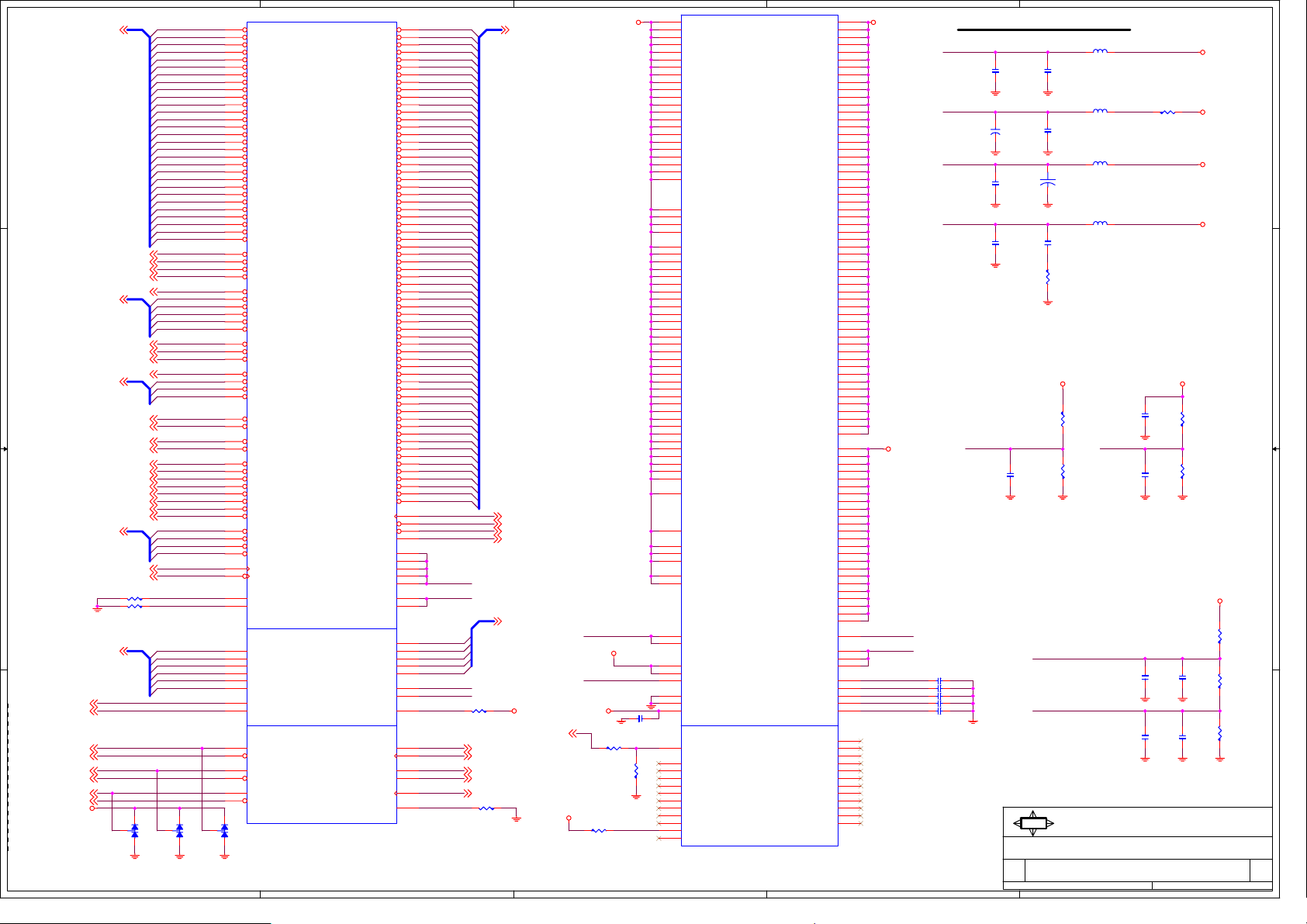

Block Diagram

VRM

INT & PWR-MNG

P4 478-Pin Processor

CTRL

ADDR

ADDR

AGTL+ BUS

CTRL

DATA

DATA

1

Clock 408

Generator

AGPCLK 66MHZ

ICH_66 66MHZ

ICH_PCLK 33MHZ

FWH_PCLK 33MHZ

SIO_PCLK 33MHZ

PCICLK0,1,2,3 33MHZ

LAN_PCLK 33MHZ

SIO_48 24MHZ

ICH_48 48MHZ

ICH_14 14.318MHZ

CPU CLK*3

3V 66M*4

PCI 33M*10

Ref CLK 14.318M*2

48M *1

24_48M *1

X'TEL

14.318MHZ

CPUCLK, CPUCLK# 100/133 MHZ

MCHCLK, MCHCLK# 100/133 MHZ

MCH_66 66MHZ

DOT_CLK 48MHZ

VGA

VGA BUS

845GV / GL

Connector

DDR1

BGA 760 Pin

HUB LINK

BUS

VCC_AGP 1.5V

MEM_STR 2.5V

ICH_66 66MHZ

ICH_PCLK 33MHZ

ICH_48 48MHZ

ICH_14 14.318MHZ

VCCP

A A

IDE Primary

UltraDMA 66/100

IDE Secondary

ICH4

FW82801DB

VCCP

VCC3 3.3V

VCC_AGP 1.5V

INT & PWR-MNG

AC'97 Link

VCC5_SB 5V

VCC3_SB 3.3V

VCC1_5SB 1.5V

DDR BUS

PCICLK0,1,2,3 33MHZ

PCI BUS

LAN_PCLK 33MHZ

LPC BUS

DDR2

PCI Slot 1

PCI Slot 2

RealTek

8100C

LAN Chip

PCI Slot 3

FirmWare

Onboard

AC'97 Codec

USB 6 PORT

LPC SIO

SIO_PCLK 33MHZ

FWH_PCLK 33MHZ

SIO_48 48MHZ

Hub

BIOS

Audio port

USB Port 5

USB Port 6

USB Port 3

USB Port 4

USB Port 1

USB Port 2

Mouse Floopy Parallel

Keyboard

Serial1,2

1

Game Port

Title

Size Document Number Rev

Date: Sheet

Block Diagram

MS-6555

of

227Wednesday, March 31, 2004

MICRO-STAR INT'L CO., LT D.

MSI

40a

8

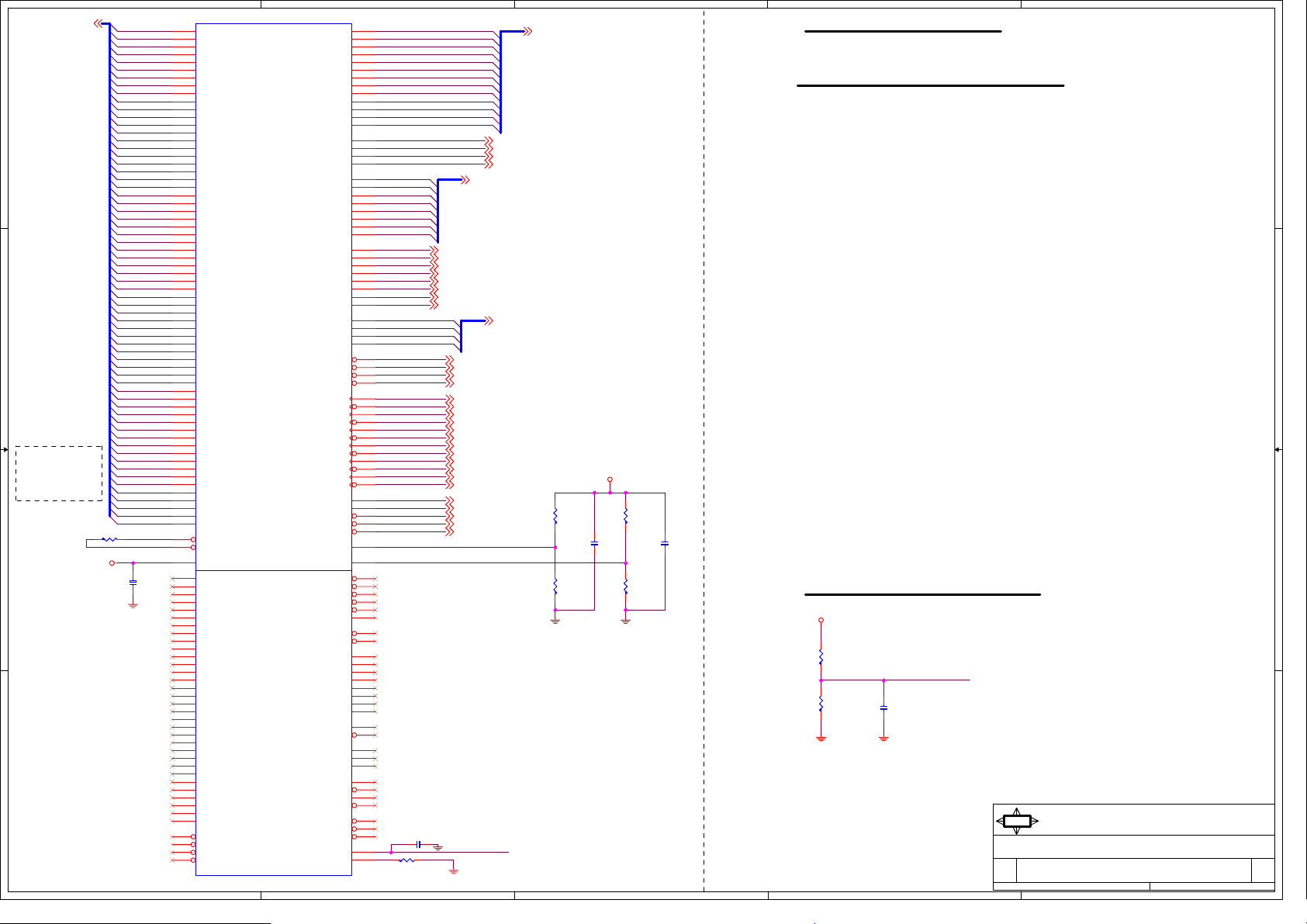

CP7 X_COPPER

VCC3

CB137

104P

D D

* Put GND copper under Clock Gen.

connect to every GND pin

* 40 mils Trace on Layer 4

with GND copper around

it

* put close to every power pin

*

Trace Width 7mils.

*

Same Group spacing 15mils

*

Different Group spacing 30mils

*

Differentical mode spacing 7mils on itself

VCC3

C C

FB18 X_80_0805

filtering from 10K~1M

FB19 X_80_0805

CP8 X_COPPER

CB154

104P

VCC3

VCCP

CB171

104P

CB145

X_10u/0805

VDDA3V

CB156

X_10u/0805

SMBCLK_ISO11,13,19

SMBDATA_ISO11,13,19

R275 10K

R281 220

7

VCC3V

SMBCLK_ISO

SMBDATA_ISO

Q29

2N3904S

6

CLOCK GENERATOR BLOCK

U16

39

CB142

104P

CB155

104P

CB143

104P

CB169

104P

CB170

104P

C163

103P

C181

103P

C175

103P

36

46

43

29

9

5

18

13

24

21

2

47

34

33

26

25

19

CPU_VDD

CPU_GND

MREF_VDD

MREF_GND

3V66_GND

PCI_VDD

PCI_GND

PCI_VDD

PCI_GND

48_VDD

48_GND

REF_VDD

REF_GND

CORE_VDD

CORE_GND

SCLK

SDATA

VTT_GD#

CY28349B

CPUCLK0

CPUCLK0#

CPUCLK1

CPUCLK1#

CPUCLK2

CPUCLK2#

3V66_03V66_VDD

3V66_1

3V66_2

3V66_48/SEL66_48#

FS2/PCI0

FS3/PCI1

SEL48_24#/PCI2

FS4/PCI3

PCI4

PCI5

PCI6

PCI7

PCI8

PCI9

FS0/48MHz

FS1/24_48MHz

MUL0/REF0

MUL1/REF1

IREF

RESET#

PWR_DN#

X1

X2

41

40

38

37

45

44

3132

30

28

27

6

7

8

10

11

12

14

15

16

17

22

23

48

1

3

4

35

20

42

CPU0

CPU0#

CPU1

CPU1#

DOT_48

FS2

FS3

SEL48_1

FS4

FS0

FS1

MUL0

MUL1

X1

X2

Iref = 2.32mA

PWR_DN#

*Trace < 0.5"

RN59

8P4R-33

RN60

8P4R-33

R267 33

R261 33

CB138

104P

5

R236 27.4RST

R237 27.4RST

R238 27.4RST

R239 27.4RST

R242 33

R243 X_33

R244 33

R245 33

7 8

5 6

3 4

1 2

7 8

5 6

3 4

1 2

R234 33

R268 33

X1 14M-32pf-HC49S-D

R240 475RST

R235 1K

MCH_66

AGPCLK

ICH_66

DOT_CLK

22PC177

22PC174

VCC3V

CPUCLK

CPUCLK#

MCHCLK

MCHCLK#

PCICLK0

PCICLK1

PCICLK2

SIO_PCLK

LAN_PCLK

FWH_PCLK

ICH_PCLK

ICH_48

SIO_24

ICH_14

CODEC_14

CPUCLK 4

CPUCLK# 4

MCHCLK 6

MCHCLK# 6

MCH_66 6

AGPCLK

ICH_66 10

DOT_CLK 6

PCICLK0 15

PCICLK1 15

PCICLK2 15

SIO_PCLK 11

LAN_PCLK 21

FWH_PCLK 12

ICH_PCLK 9

ICH_48 10

SIO_24 11

ICH_14 10

CODEC_14 17

VCC3VCC3

CB164

X_104P

Near X1Near U16 Pin 32

4

Shut Source Termination Resistors

CPUCLK

CPUCLK#

MCHCLK

MCHCLK#

Trace less 0.2"

49.9ohm for 50ohm M/B impedance

R220 49.9RST

R223 49.9RST

R221 49.9RST

R219 49.9RST

CLOCK STRAPPING RESISTORS

FS0

FS3

FS2

FS4

R258 10K

FS1

BSEL0 0 100 ; 1 133

1 1 1 1 1

SEL48_1

DOT_48

MUL0

MUL1

SMBCLK_ISO

SMBDATA_ISO

R270 X_10K

R241 10K

0 Set Pin 27 48MHz

R233 X_10K

R222 10K

R262 10K

R266 10K

R269 10K

R272 10K

R274 10K

R260 1.5K

R252 2.7K

R253 2.7K

3

FSB (MHz)FS4 FS3 FS2 FS1 FS0

100 MHz1 1 1 0 1

133 MHz

VCC3V

VCC3V

VCC3V

VCC3V

BSEL0 4,6

VCC3

MUL 1:0

0 0 4X

0 1 5X

1 0 6X

1 1 7X

2

Pull-Down Capacitors

CPUCLK

CPUCLK#

MCHCLK

MCHCLK#

AGPCLK

ICH_66

MCH_66

PCICLK0

PCICLK1

PCICLK2

SIO_PCLK

LAN_PCLK

FWH_PCLK

ICH_PCLK

ICH_14

SIO_24

ICH_48

CODEC_14

DOT_CLK

Ioh=6*Iref

Voh=0.71V

used only for EMI issue

X_10pC153

X_10pC154

X_10pC155

X_10pC156

X_10pC159

X_10pC158

X_10pC157

CN13

7

8

5

6

3

4

1

2

X_8P4C-10P

CN14

1

2

3

4

5

6

7

8

X_8P4C-10P

X_10PC152

X_10PC178

X_10PC180

X_10PC182

X_10PC160

Trace less 0.2"

1

B B

R100

4.7K

R190 33

C84

X_220P

PDD[0..7]10 SDD[0..7]10

A A

HD_RST#19

PD_DREQ10

PD_IORDY10

PD_DACK#10

PD_CS#110

HD_RST#

PDD7

PDD6

PDD5

PDD4

PDD3

PDD2

PDD1

PDD0

IRQ149

PD_A110

PD_LED23

ATA100 IDE CONNECTORS

8

7

1

3 4

5 6

7 8

91110

13 14

17 18

19

21

23

25

27

29

31

33

35

37

R129

10K

VCC3

IDE1

YJ220-CB-1

2

12

1615

22

24

26

28

30

32

34

36

38

4039

PDD8

PDD9

PDD10

PDD11

PDD12

PDD13

PDD14

PDD15

R113

15K

IDE2

R132

10K

VCC3VCC5 VCC5

3

YJ220-CW-1

1

3 4

5 6

7 8

91110

13 14

17 18

19

21

23

25

27

29

31

33

35

37

2

SDD8

SDD9

SDD10

SDD11

SDD12

12

SDD13

SDD14

1615

SDD15

22

24

26

WhiteBlue

28

30

32

34

36

38

4039

R119

15K

SD_A2 10

SD_CS#3 10

MSI

Title

Size Document Number Rev

Date: Sheet

PDD[8..15] 10

SD_DREQ10

SD_IOW#10PD_IOW#10

SD_IOR#10PD_IOR#10

SD_IORDY10

SD_DACK#10

PD_DET 12 SD_DET 12

PD_A2 10 SD_A010PD_A010

PD_CS#3 10

DIOR-:HDMARDY-(Host Strobe)

IORDY:DDMARDY-(Device Strobe)

DIOW-:STOP

PDIAG-:CBLID-

6

5

SD_A110

SD_CS#110

SD_LED23

4

HD_RST#

SDD7

SDD6

SDD5

SDD4

SDD3

SDD2

SDD1

SDD0

IRQ159

R189 33

R99

4.7K

Trace Width : 5mils

Trace Spacing : 7mils

Trace Length less than 5"

Strobe Equal

Length(longest)-Length(shortest)<0.5"

C97

X_220P

SDD[8..15] 10

CLOCK GEN & ATA100 IDE

2

MICRO-STAR

MS-6555

40a

327Wednesday, March 31, 2004

of

1

PRIMARY IDE BLOCK SECONDARY IDE BLOCK

8

7

6

5

4

3

2

1

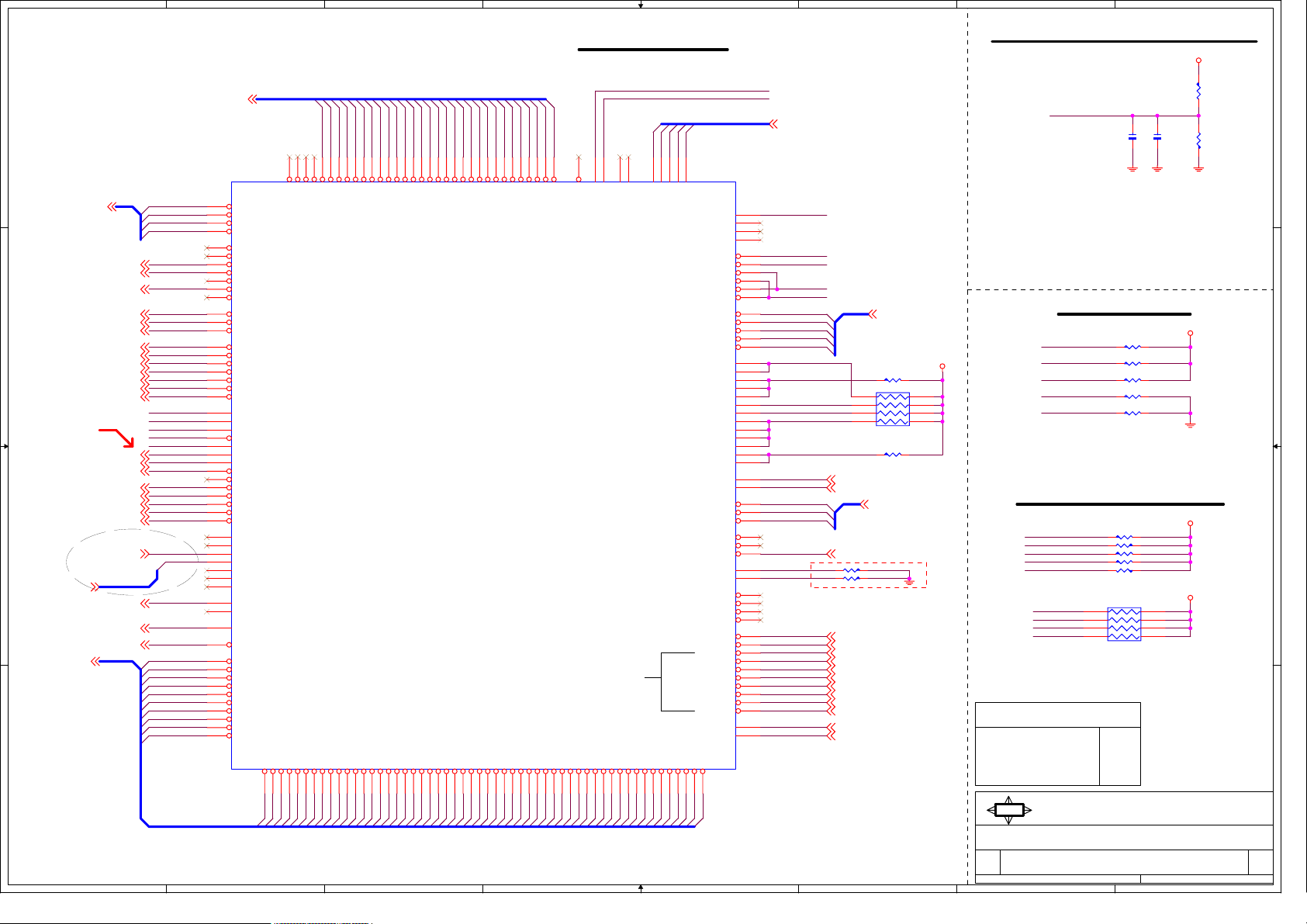

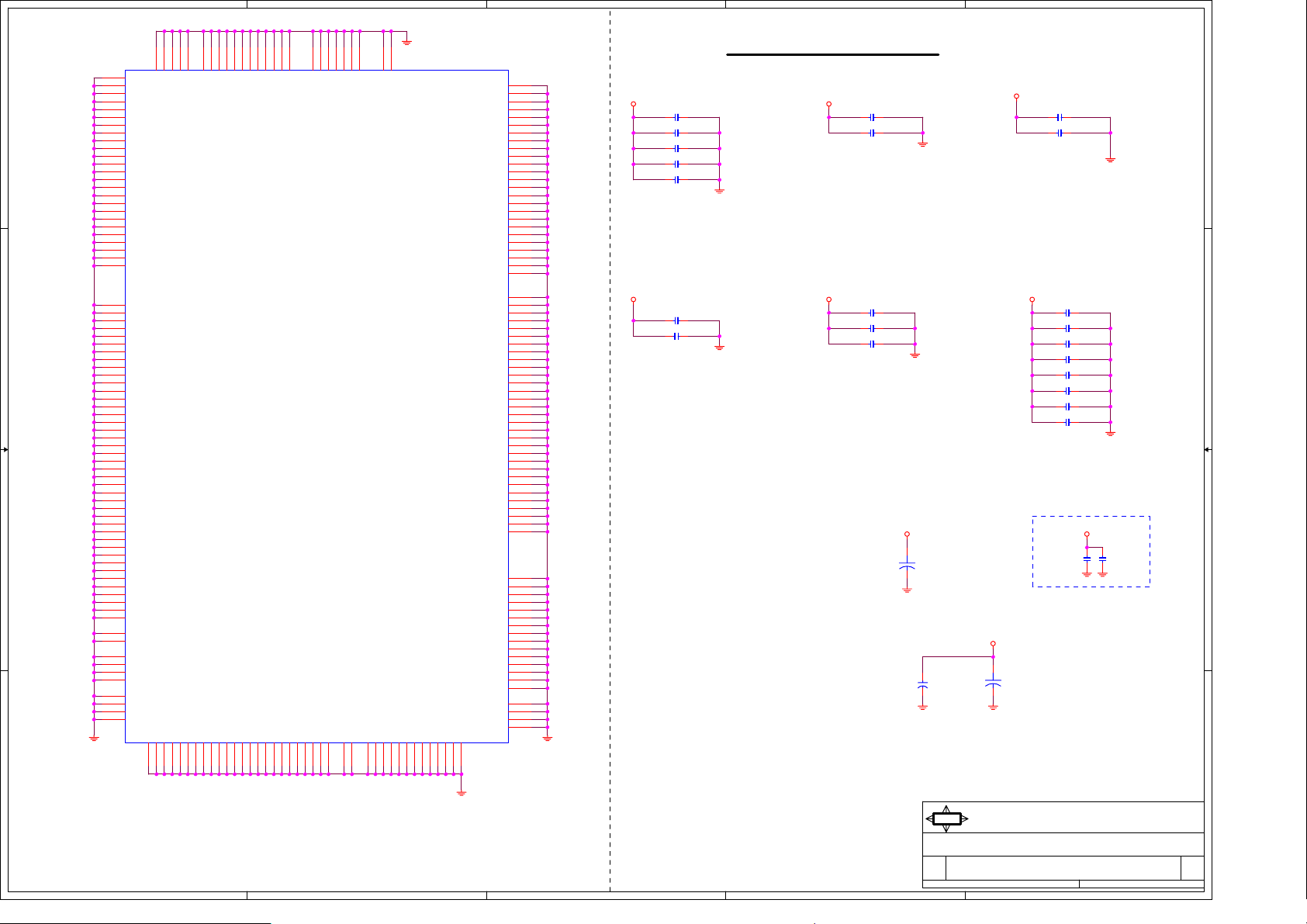

CPU SIGNAL BLOCK

VCC_SENSE

HA#[3..31]6

D D

HA#29

HA#28

A29#

D44#

R24

HA#27

A28#

D43#

R25

HA#26

A27#

D42#

P24

HA#25

A26#

D41#

R21

HA#24

A25#

D40#

N25

HA#23

A24#

D39#

N26

HA#22

A23#

D38#

M26

HA#31

HA#30

U5A

HINV#[0..3]6

STPCLK#9

HDBSY#6

HDRDY#6

C C

CPU_TMPA;VTIN_GND

Trace : 10 mil

width 10mil

space

B B

VID[0..5]20

HD#[0..63]6

A A

HTRDY#6

HLOCK#6

HBPRI#6

HDEFER#6

CPU_TMPA11

VTIN_GND11

THERMTRIP#9

PROCHOT#10

IGNNE#9

CPUVID_GD20

CPU_GD10

CPURST#6

HINV#0

HINV#1

HINV#2

HINV#3

FERR#9

HINIT#9,12

HADS#6

HBNR#6

HIT#6

HITM#6

ITP_TDI

ITP_TDO

ITP_TMS

ITP_TRST#

ITP_TCK

HSMI#9

A20M#9

SLP#9

CPUVID_GD

BSEL0

BSEL03,6

CPU_GD

CPURST#

HD#63

HD#62

HD#61

HD#60

HD#59

HD#58

HD#57

HD#56

HD#55

HD#54

VID5

E21

G25

P26

V21

AC3

AA3

AB2

AF26

AB26

A22

AD2

AD3

AE21

AF24

AF25

AD6

AD5

AB23

AB25

AA24

AA22

AA25

Y21

Y24

Y23

W25

Y26

W26

V24

V6

B6

Y4

W5

H5

H2

J6

G1

G4

G2

F3

E3

D2

E2

C1

D5

F7

E6

D4

B3

C4

A2

C3

B2

B5

C6

A7

DBI0#

DBI1#

DBI2#

DBI3#

IERR#

MCERR#

FERR#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

TDO

TMS

TRST#

TCK

THERMDA

THERMDC

THERMTRIP#

GND/SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M#

SLP#

RESERVED0

RESERVED1

RESERVED2

RESERVED3

RESERVED4

RESERVED5

RESERVED6

BSEL0

BSEL1

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

AB1Y1W2V3U4T5W1R6V2T4U3P6U1T2R3P4P3R2T1N5N4N2M1N1M4M3L2M6L3K1L6K4K2

A35#

A34#

A33#

A32#

A31#

A30#

D53#

D52#

D51#

D50#

D49#

D48#

D47#

D46#

D45#

V22

U21

V25

U23

U24

U26

T23

T22

T25

T26

HA#21

A22#

D37#

N23

HA#20

A21#

D36#

M24

HA#19

A20#

D35#

P21

HA#18

A19#

D34#

N22

HA#17

A18#

D33#

M23

HA#16

A17#

D32#

H25

HA#15

A16#

D31#

K23

HA#14

A15#

D30#

J24

HA#13

A14#

D29#

L22

HA#12

A13#

D28#

M21

HA#11

A12#

D27#

H24

HA#10

A11#

D26#

G26

HA#9

A10#

D25#

L21

A9#

D24#

HA#4

HA#5

HA#7

HA#3

HA#6

HA#8

AE25A5A4

A8#

A7#

A6#

A5#

A4#

A3#

DBR#

VCC_SENSE

VID4

AD26

AC26

AE1

ITP_CLK1

ITP_CLK0

VSS_SENSE

75ohm 5%

62ohm 5%

Differential

Host Data

Strobes

D23#

D22#

D21#

D20#

D19#

D18#

D17#

D16#

D15#

D14#

D13#

D12#

D11#

D10#

D9#

D8#

D7#

D26

F26

E25

F24

F23

G23

E24

H22

D25

J21

D23

C26

H21

G22

B25

C24

C23

B24

VSS_SENSE

VID[0..5]

VID3

VID0

VID1

VID2

AE2

AE3

AE4

AE5

VID4#

VID3#

VID2#

VID1#

VID0#

GTLREF3

GTLREF2

GTLREF1

GTLREF0

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

BCLK1#

BCLK0#

RS2#

RS1#

RS0#

AP1#

AP0#

BR0#

COMP1

COMP0

DP3#

DP2#

DP1#

DP0#

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

LINT1/NMI

LINT0/INTR

D6#

D5#

D4#

D3#

D2#

D1#

D0#

D22

C21

A25

A23

B22

B21

PGA-S478-F02

AA21

AA6

F20

F6

AB4

AA5

Y6

AC4

AB5

AC6

H3

J3

J4

K5

J1

AD25

A6

Y3

W4

U6

AB22

AA20

AC23

AC24

AC20

AC21

AA2

AD24

AF23

AF22

F4

G5

F1

V5

AC1

H6

P1

L24

L25

K26

K25

J26

R5

L5

W23

P23

J23

F21

W22

R22

K22

E22

E5

D1

VID[0..5] 20

GTLREF1

BPM#5

BPM#4

BPM#1

BPM#0

HREQ#4

HREQ#3

HREQ#2

HREQ#1

HREQ#0

TESTHI_11_12

TESTHI_8_10

TESTHI7

TESTHI6

TESTHI_2_5

TESTHI_0_1

CPUCLK#

CPUCLK

HRS#2

HRS#1

HRS#0

HBR#0

COMP1

COMP0

62ohm 1%

HREQ#[0..4] 6

VCCP

R40 62 R29 150

1 2

3 4

5 6

7 8

RN72 62R

R27 62

CPUCLK# 3

CPUCLK 3

HRS#[0..2] 6

HBR#0 6

R41 61.9RST

R78 61.9RST

* Short trace

61.9ohm 1%

HADSTB#1 6

HADSTB#0 6

HDSTBP#3 6

HDSTBP#2 6

HDSTBP#1 6

HDSTBP#0 6

HDSTBN#3 6

HDSTBN#2 6

HDSTBN#1 6

HDSTBN#0 6

NMI 9

INTR 9

CPU GTL REFERNCE VOLTAGE BLOCK

VCCP

R73

49.9RST

GTLREF1

2/3*Vccp

C55

220P

C54

105P

R74

100RST

Every pin put one 220pF cap near it.

Trace Width 10mils, Space 15mils.

Keep the voltage dividers within 1.5 inches of the

first GTLREF Pin

CPU ITP BLOCK

VCCP

ITP_TMS

ITP_TDO

ITP_TDI

ITP_TRST#

ITP_TCK

R32 39

R30 75

R45 680

R28 27

ALL COMPONENTS CLOSE TO CPU

CPU STRAPPING RESISTORS

VCCP

PROCHOT#

CPU_GD

HBR#0

CPURST#

HINIT#

BPM#0

BPM#1

BPM#5

BPM#4

Pin Definition Change

AD1 : BOOTSELECT

AD2 : VIDPWRGD

AD3 : VID5

AE26: OPTIMZED/COMPAT*

AF3 : VCCVIDLB

R13 62

R82 300

R31 150

R81 51

R216 X_330

RN73 62R

1 2

3 4

5 6

7 8

Input

Input

Output

Input

Input

VCCP

The OPTIMZED/COMPAT*(AE26)

and RSP#(AB2) pins on the CPU

socket should be left as a no

connect(NC).

MSI

HD#8

HD#52

HD#50

HD#49

HD#53

8

7

HD#46

HD#47

HD#51

HD#45

HD#48

HD#43

HD#44

HD#37

HD#41

HD#40

HD#39

HD#42

HD#33

HD#35

HD#36

HD#38

HD#34

HD#32

6

HD#26

HD#31

HD#30

HD#27

HD#29

HD#28

HD#20

HD#23

HD#25

HD#22

HD#21

HD#24

HD#15

HD#19

HD#17

HD#18

HD#16

5

HD#9

HD#12

HD#11

HD#10

HD#14

HD#13

HD#3

HD#1

HD#6

HD#7

HD#0

HD#2

HD#5

HD#4

4

3

Title

Size Document Number Rev

Date: Sheet of

2

MICRO-STAR

INTEL mPG478 CPU1

MS-6555

427Wednesday, March 31, 2004

40a

1

8

VCCP

A10

A12

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AE15

VCC

VSS

AE17

VCC

VSS

AE19

A14

AE22

D D

C C

BOOTSEL20

B B

U5B

D10

A11

A13

A15

A17

A19

A21

A24

A26

A3

A9

AA1

AA11

AA13

AA15

AA17

AA19

AA23

AA26

AA4

AA7

AA9

AB10

AB12

AB14

AB16

AB18

AB20

AB21

AB24

AB3

AB6

AB8

AC11

AC13

AC15

AC17

AC19

AC2

AC22

AC25

AC5

AC7

AC9

AD1

AD10

AD12

AD14

AD16

AD18

AD21

AD23

AD4

AD8

AE11

AE13

R168 X_60.4_1%

VCC

VSS

A16

VCC

VSS

AE24

A18

A20A8AA10

VCC

VCC

VSS

VSS

AE26

AE7

AE9

VCC

VSS

7

AA12

AA14

AA16

AA18

AA8

AB11

AB13

AB15

AB17

AB19

AB7

AB9

AC10

AC12

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AF1

AF10

AF12

AF14

AF16

AF18

AF20

AF6

AF8

B10

B12

B14

B16

B18

B20

VCC

VSS

AC14

VCC

VSS

B23

AC16

AC18

VCC

VCC

VSS

VSS

B26B4B8

6

CPU VOLTAGE BLOCK

AC8

AD11

AD13

AD15

AD17

AD19

AD7

AD9

AE10

AE12

AE14

AE16

AE18

AE20

AE6

AE8

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

C11

C13

C15

C17C2C19

C22

C25C5C7C9D12

D14

D16

D18

AF11

AF13

AF15

AF17

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

D20

D21D3D24D6D8E1E11

5

AF19

AF2

AF21

AF5

AF7

AF9

B11

B13

B15

B17

B19B7B9

C10

C12

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

E13

E15

E17

E19

E23

E7E9F10

F12

E4

E26

VCC

VSS

4

C14

C16

C18

C20C8D11

D13

D15

D17

D19D7D9

E10

E12

E14

E16

E18

E20E8F11

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

F14

F16

F18F2F22

F25F5F8

G21G6G24

G3H1H23

H26H4J2

J22

J25J5K21

VCC

VSS

3

C30

104P

VCC-VID

HVSS

XX6

HVSS

AF3

XX7

VCC-VIDPRG

HVSS

XX8

HVSS

AE23

VCC-IOPLL

HVSS

XX9

HVSS

XX10

AD20

VCCA

HVSS

XX11

HVSS

XX12

HVSS

XX13

HVSS

XX14

HVSS

XX15

HVSS

XX16

F13

F15

F17

F19

AF4

F9

VCC

VCC

VCC

VCC

VCC

VSS

HVSS

HVSS

HVSS

HVSS

XX1

XX2

XX3

XX4

XX5

HVSS

XX17

VCC_VID

VCCIOPLL

VCCA

HVSS

HVSS

XX18

XX19

HVSS

XX20

HVSS

XX21

2

VSSA

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

HVSS

HVSS

HVSS

HVSS

HVSS

HVSS

HVSS

HVSS

HVSS

HVSS

XX22

AD22

Y5

Y25

Y22

Y2

W6

W3

W24

W21

V4

V26

V23

V1

U5

U25

U22

U2

T6

T3

T24

T21

R4

R26

R23

R1

P5

P25

P22

P2

N6

N3

N24

N21

M5

M25

M22

M2

L4

L26

L23

L1

K6

K3

K24

XX32

XX31

XX30

XX29

XX28

XX27

XX26

XX25

XX24

HVSS

XX23

PGA-S478-F02

1

VCC_VID 19,20

VSSA

C58

226P/1206

C60

226P/1206

Keep the 22uF cap within 0.6" of

the CPU pin.

L8

4.7u-10%

L7

4.7u-10%

VCCP

Trace Width 12mils, Space 10mils.

CPU DECOUPLING CAPACITORS

MLCC(10uF / Y5V / 1206)

VCCP

CB14 X_10u/1206

A A

CB26 X_10u/1206

CB45 X_10u/1206

CB5 X_10u/1206

8

CB12 10u/1206

CB19 10u/1206

CB1 10u/1206

CB38 10u/1206

CB2 10u/1206

CB49 10u/1206

7

VCCPVCCP

CB21 10u/1206

CB28 10u/1206CB15 10u/1206

CB16 10u/1206

CB36 10u/1206

C3 C100U6.3SP

C2 X_C100U6.3SP

6

VCCP

CB40 X_10u-0805

CB41 X_10u-0805

CB42 X_10u-0805

CB43 X_10u-0805

5

VCCP

C4 X_C100U6.3SP

C6 X_C100U6.3SP

Place on Bottom

4

Taiyo

MLCC(10uF / Y5V / 0805)

Walsin

SP-CAP(100uF)

Ripplecur = 2000mA

Impedance = 20mΩ

Panasonic

3

MSI

Title

Size Document Number Rev

Date: Sheet of

2

MICRO-STAR

INTEL mPGA478-B CPU2

MS-6555

527Wednesday, March 31, 2004

1

40a

5

HA#[3..31]4

* Length must be matched within

+/-0.1"of the Strobe Signals

D D

HBR#04

HBNR#4

HBPRI#4

HLOCK#4

HADS#4

HREQ#[0..4]4

C C

B B

HIT#4

HITM#4

HDEFER#4

HTRDY#4

HRS#[0..2]4

HDBSY#4

HDRDY#4

HADSTB#04

HADSTB#14

HDSTBN#04

HDSTBP#04

HDSTBN#14

HDSTBP#14

HDSTBN#24

HDSTBP#24

HDSTBN#34

HDSTBP#34

HINV#[0..3]4

MCHCLK3

MCHCLK#3

R106 24.9_1%

R125 24.9_1%

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HRS#0

HRS#1

HRS#2

HINV#0

HINV#1

HINV#2

HINV#3

HY_RCOMP

HX_RCOMP

U10A

W31

HA3#

AA33

HA4#

AB30

HA5#

V34

HA6#

Y36

HA7#

AC33

HA8#

Y35

HA9#

AA36

HA10#

AC34

HA11#

AB34

HA12#

Y34

HA13#

AB36

HA14#

AC36

HA15#

AC31

HA16#

AF35

HA17#

AD36

HA18#

AD35

HA19#

AE34

HA20#

AD34

HA21#

AE36

HA22#

AF36

HA23#

AE33

HA24#

AF34

HA25#

AG34

HA26#

AG36

HA27#

AE31

HA28#

AH35

HA29#

AG33

HA30#

AG31

HA31#

U33

BREQ0#

T34

BNR#

M34

BPRI#

T35

HLOCK#

T36

ADS#

V36

HREQ0#

AA31

HREQ1#

W33

HREQ2#

AA34

HREQ3#

W35

HREQ4#

P36

HIT#

M36

HITM#

N36

DEFER#

V30

HTRDY#

R36

RS0#

U34

RS1#

P34

RS2#

U31

DBSY#

U36

DRDY#

AB35

HAD_STB0#

AF30

HAD_STB1#

N31

HD_STBN0#

L31

HD_STBP0#

G33

HD_STBN1#

J34

HD_STBP1#

C30

HD_STBN2#

E29

HD_STBP2#

D25

HD_STBN3#

E25

HD_STBP3#

N33

DINV_0#

C35

DINV_1#

B33

DINV_2#

C26 H30

DINV_3# HD_VREF0

K30

HCLKP

J31

HCLKN

V35

HY_RCOMP

B28

HX_RCOMP

HOST

Trace 10 mils & 7mils space < 0.5"

HL[0..10]9

HL_STB9

HL_STB#9

CRT_B22

CRT_B#22

CRT_G22

CRT_G#22

A A

CRT_R22

CRT_R#22

VCC_AGP

HL_STB

HL_STB#

CRT_B

CRT_B#

CRT_G

CRT_G#

CRT_R

CRT_R#

3

D11

BAV99

HL0 HL7

HL1

HL2

HL3

HL4

HL5

2

2

3

D10

BAV99

1

1

5

AA7

HI0

AB8

AC7

AC5

AD8

AF4 AD3

AD4

AC4

G15

H16

E15

F16

C15

D16

2

3

D9

BAV99

1

HUB LINK

HI1

HI2

HI3

HI4

HI5 HI_REF

HI_STBS

HI_STBF

BLUE

BLUE#

GREEN

GREEN#

RED

RED#

VGA

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

GCLKIN

RSTIN#

CPURST#

PWROK

HD_VREF1

HD_VREF2

HA_VREF

HCC_VREF

HY_SWNG

HX_SWNG

HI10

HI_SWING

HL_RCOMP

DDCA_DATA

DDCA_CLK

HSYNC

VSYNC

DREFCLK

REFSET

4

T30

R33

R34

N34

R31

L33

L36

P35

J36

K34

K36

M30

M35

L34

K35

H36

G34

G36

J33

D35

F36

F34

E36

H34

F35

D36

H35

E33

E34

B35

G31

C36

D33

D30

D29

E31

D32

C34

B34

D31

G29

C32

B31

B32

B30

B29

E27

C28

B27

D26

D28

B26

G27

H26

B25

C24

B23

B24

E23

C22

G25

B22

D24

G23

AE7

AJ31

D22

E7

H24

D27

AD30

P30

Y30

H28

AE4

HI6

AE5

HI7

AF3

HI8

AE2

HI9

AF2

AD2

AC2

C7

D7

B7

C6

D14

B16

4

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

HVREF

HSWNG

HL6

HL8

HL9

HL10

HUB_MREF

HI_SWING

HL_RCOMP

3VDDCDA

3VDDCCL

3V_HSYNC

3V_VSYNC

DOT_CLK

REFSET

Brookdale_GMCH

MCH_66 3

PCIRST#1 11,19,21

CPURST# 4

PWR_GD 10,19

HL[0..10] 9

Trace 10 mils &

7mils space <

0.5"

R159

68.1_1%

3VDDCDA 22

3VDDCCL 22

3V_HSYNC 22

3V_VSYNC 22

DOT_CLK 3

R135 137_1%

HD#[0..63] 4

VCC_AGP

BSEL03,4

VCC_AGP

VCC_AGP

VCCA_SM

VCC_AGP

VCCA_DPLL

VCC3

R390

X_8.2K

R146

8.2K

R145

8.2K

3

PSBSEL

3

CB114

0.1u

AB10

AD10

AD6

AC9

AC1

AE3

W19

AA19

W20

U21

W21

AA21

C10

D10

H10

C11

D11

G11

C12

D12

H12

G13

H14

AA17

W18

W17

U19

U17

AG2

AG1

C14

AA2

AA4

AA3

AA5

AB2

AB3

A3

A7

C1

D4

D6

G1

K6

L1

L9

P6

R1

R9

W9

V6

K10

K12

K14

K16

P10

V10

Y19

A9

B9

C9

D9

E9

B10

F10

A11

B11

E11

J11

B12

F12

J13

J15

V19

A15

B14

A13

B15

Y3

Y2

W7

Y4

Y8

A37

U10C

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_HI

VCC_HI

VCC_HI

VCC_HI

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCA_SM

VCCA_SM

VCCA_DAC

VCCA_DAC

VCCA_DPLL

VSSA_DAC

VSSA_DAC

PSBSEL

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

POWER

Other

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VTTFSB

VTTFSB

VTTFSB

VTTFSB

VTTFSB

VTTFSB

VTTFSB

VTTFSB

VTTFSB

VTTFSB

VTTFSB

VTTFSB

VTTFSB

VTTFSB

VTTFSB

VTTFSB

VTTFSB

VTTFSB

VTTFSB

VTTFSB

VTTFSB

VTTFSB

VTTFSB

VTTFSB

VCCA_FSB

VCCQ_SM

VCCQ_SM

VCCQ_SM

VTT_DECAP

VTT_DECAP

VTT_DECAP

VTT_DECAP

VTT_DECAPVCC_GPIO

AH8

AK8

AG9

AJ9

AL9

AM22

AJ23

AL37

AU9

AK10

AJ11

AL11

AU25

AM26

AU13

AM14

AJ27

AJ1

AL1

AJ15

AP15

AU29

AH2

AJ2

AK2

AL2

AM30

AH3

AJ3

AK3

AL3

AH4

AJ4

AK4

AL4

AU17

AJ5

AL5

AU5

AM18

AJ19

AK32

AU33

AH6

AK6

AP20

AG7

AJ7

AL7

AP7

AH10

AH12

AH14

AH18

AH22

AH26

B18

C18

D18

H18

B19

C19

D19

E19

G19

J19

B20

C20

D20

F20

H20

Y28

T28

M28

K26

K22

K20

F18

K18

AD28

A17

AT21

AU21

AT20

G37

L37

R37

AC37

A31B6

A2

NC

A36

NC

AH34

NC

AJ35

NC

AT1

NC

AT37

NC

AU1

NC

AU2

NC

AU36

NC

AU37

NC

B1

NC

B37

NC

Brookdale_GMCH

2

MEM_STR

Electrolytic CAP(680uF/6.3V)

Ripplecur = 230mA

PANASONIC

VCCP

VCCA_FSB

VCCQ_SM

VTT_CAP1

CB68 0.1u

VTT_CAP2

CB70 0.1u

VTT_CAP3

CB71 0.1u

VTT_CAP4

CB69 0.1u

VTT_CAP5

CB75 0.1u

GMCH REFERENCE BLOCK

VCCA_FSB

VCCA_DPLL

VCCA_SM

VCCQ_SM

HVREF

Place <0.1"

2

1

CB87

0.1u_X7R

+

C106

680uF

CB99

0.1u_X7R

CB84

0.1u_X7R

C90

0.1u

L14 0.82uH_0603

C105

22u-1206

CB92

X_0.1u_X7R

CT26

+

100u_6.3V

C102

4.7u-0805

R133

1_1%

I=30mA

L16 10uH-0805

I=35mA

L17 0R

I=500mA

L12 0.68uH-0805

I=150mA

Electrolytic CAP(100uF/6.3V)

Ripplecur = 220mA

Impedance = 370mΩ

G-Luxon

HSWNG

C79

0.1u

C95

0.01u

R122

49.9_1%

R123

100_1%

R144

1_1%

VCC_AGP

VCC_AGP

VCC_AGP

MEM_STR

VCCPVCCP

R115

301_1%

R120

150_1%

Place Cap. as Close as possible to GMCH

, Trace width 12 mils & 10mils space

Keep the voltage divider within 3" of the GMCH pin.

VCC_AGP

R167

226_1%

HI_SWING

C123

C130

0.1u

C131

0.1u

R165

100_1%

R166

100_1%

HUB_MREF

0.01u

C129

0.01u

Place 0.01uF Cap. as Close as possible to GMCH< 0.25"

Trace width 12 mils & 10mils space

MSIMSI

Title

Size Document Number Rev

Date: Sheet

MICRO-STAR

BROOKDALE-G GMCH1

MS-6555

627Wednesday, March 31, 2004

1

of

40a

5

DDRMD[0..63]13,14

D D

C C

Trace lengh

must as short

as possible

for SRCVEN

R387

X_0_Solder

B B

A A

DDR_VREF

Trace width 12 mil

with 12 mil space for

SM_VREF.

DDRMD0

DDRMD1

DDRMD2

DDRMD3

DDRMD4

DDRMD5

DDRMD6

DDRMD7

DDRMD8

DDRMD9

DDRMD10

DDRMD11

DDRMD12

DDRMD13

DDRMD14

DDRMD15

DDRMD16

DDRMD17

DDRMD18

DDRMD19

DDRMD20

DDRMD21

DDRMD22

DDRMD23

DDRMD24

DDRMD25

DDRMD26

DDRMD27

DDRMD28

DDRMD29

DDRMD30

DDRMD31

DDRMD32

DDRMD33

DDRMD34

DDRMD35

DDRMD36

DDRMD37

DDRMD38

DDRMD39

DDRMD40

DDRMD41

DDRMD42

DDRMD43

DDRMD44

DDRMD45

DDRMD46

DDRMD47

DDRMD48

DDRMD49

DDRMD50

DDRMD51

DDRMD52

DDRMD53

DDRMD54

DDRMD55

DDRMD56

DDRMD57

DDRMD58

DDRMD59

DDRMD60

DDRMD61

DDRMD62

DDRMD63

SRC_O#

SRC_I#

C125

0.1u

5

AN4

AP2

AT3

AP5

AN2

AP3

AR4

AT4

AT5

AR6

AT9

AR10

AT6

AP6

AT8

AP8

AP10

AT11

AT13

AT14

AT10

AR12

AR14

AP14

AT15

AP16

AT18

AT19

AR16

AT16

AP18

AR20

AR22

AP22

AP24

AT26

AT22

AT23

AT25

AR26

AP26

AT28

AR30

AP30

AT27

AR28

AT30

AT31

AR32

AT32

AR36

AP35

AP32

AT33

AP34

AT35

AN36

AM36

AK36

AJ36

AP36

AM35

AK35

AK34

AK24

AL23

V4

V2

W4

W5

U5

U4

U2

V3

T2

T3

T4

R2

R5

R7

T8

P3

P8

K4

K2

J2

M3

L5

L4

H4

G2

K3

J4

J5

J7

H3

K8

G4

R4

N4

M2

H2

U10B

SDQ0

SDQ1

SDQ2

SDQ3

SDQ4

SDQ5

SDQ6

SDQ7

SDQ8

SDQ9

SDQ10

SDQ11

SDQ12

SDQ13

SDQ14

SDQ15

SDQ16

SDQ17

SDQ18

SDQ19

SDQ20

SDQ21

SDQ22

SDQ23

SDQ24

SDQ25

SDQ26

SDQ27

SDQ28

SDQ29

SDQ30

SDQ31

SDQ32

SDQ33

SDQ34

SDQ35

SDQ36

SDQ37

SDQ38

SDQ39

SDQ40

SDQ41

SDQ42

SDQ43

SDQ44

SDQ45

SDQ46

SDQ47

SDQ48

SDQ49

SDQ50

SDQ51

SDQ52

SDQ53

SDQ54

SDQ55

SDQ56

SDQ57

SDQ58

SDQ59

SDQ60

SDQ61

SDQ62

SDQ63

SRCVEN_OUT#

SRCVEN_IN#

G_AD0

G_AD1

G_AD2

G_AD3

G_AD4

G_AD5

G_AD6

G_AD7

G_AD8

G_AD9

G_AD10

G_AD11

G_AD12

G_AD13

G_AD14

G_AD15

G_AD16

G_AD17

G_AD18

G_AD19

G_AD20

G_AD21

G_AD22

G_AD23

G_AD24

G_AD25

G_AD26

G_AD27

G_AD28

G_AD29

G_AD30

G_AD31

G_C/BE0#

G_C/BE1#

G_C/BE2#

G_C/BE3#

DDR

AGP

SMA0

SMA1

SMA2

SMA3

SMA4

SMA5

SMA6

SMA7

SMA8

SMA9

SMA10

SMA11

SMA12

SMAB1

SMAB2

SMAB4

SMAB5

SDQS0

SDQS1

SDQS2

SDQS3

SDQS4

SDQS5

SDQS6

SDQS7

SDM0

SDM1

SDM2

SDM3

SDM4

SDM5

SDM6

SDM7

SCKE0

SCKE1

SCKE2

SCKE3

SCS0#

SCS1#

SCS2#

SCS3#

SCMDCL_K0

SCMDCLK_0#

SCMDCLK_1

SCMDCLK_1#

SCMDCLK_2

SCMDCLK_2#

SCMDCLK_3

SCMDCLK_3#

SCMDCLK_4

SCMDCLK_4#

SCMDCLK_5

SCMDCLK_5#

SBA_0

SBA_1

SRAS#

SCAS#

SWE#

SMX_RCOMP0

SMY_RCOMPSM_VREF

G_FRAME#

G_IRDY#

G_TRDY#

G_DEVSEL#

G_STOP#

G_PAR

G_REQ#

G_GNT#

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

SB_STB

SB_STB#

ST0

ST1

ST2

AD_STB0

AD_STB0#

AD_STB1

AD_STB1#

PIPE#

RBF#

WBF#

AGP_VREF

AGP_RCOMP

Brookdale_GMCH

AL25

AN25

AP23

AK20

AL19

AL17

AP19

AP17

AN17

AK16

AK26

AL15

AN15

AP25

AN23

AN19

AK18

AR2

AT7

AT12

AT17

AR24

AT29

AT34

AL36

AP4

AR8

AP12

AR18

AT24

AP28

AR34

AL34

AP13

AN13

AK14

AL13

AL29

AP31

AK30

AN31

AL21

AK22

AN11

AP11

AM34

AL33

AP21

AN21

AP9

AN9

AP33

AN34

AN27

AP27

AK28

AN29

AP29

AF10

AJ34AM2

M4

N7

N5

N2

P2

P4

D5

B5

C3

C2

D3

D2

E4

E2

F3

F2

F4

E5

C4

B4

B3

V8

U7

M8

L7

H8

G7

G5

W2

L2

4

SDQS0

SDQS1

SDQS2

SDQS3

SDQS4

SDQS5

SDQS6

SDQS7

SDM0

SDM1

SDM2

SDM3

SDM4

SDM5

SDM6

SDM7

MSCKE0

MSCKE1

MSCKE2

MSCKE3

MSCS0#

MSCS1#

MSCS2#

MSCS3#

DCLK0

DCLK0#

DCLK1

DCLK1#

DCLK2

DCLK2#

DCLK3

DCLK3#

DCLK4

DCLK4#

DCLK5

DCLK#5

MSBS0

MSBS1

MRAS#

MCAS#

MWE#

SMX_RCOMP

SMY_RCOMP

CB105 0.1u

R164 40.2_1%

4

DDRMAA0

DDRMAA1

DDRMAA2

DDRMAA3

DDRMAA4

DDRMAA5

DDRMAA6

DDRMAA7

DDRMAA8

DDRMAA9

DDRMAA10

DDRMAA11

DDRMAA12

DDRMAB1

DDRMAB2

DDRMAB4

DDRMAB5

SDQS[0..7] 13,14

SDM0 13,14

SDM1 13,14

SDM2 13,14

SDM3 13,14

SDM4 13,14

SDM5 13,14

SDM6 13,14

SDM7 13,14

MSCS0# 13,14

MSCS1# 13,14

MSCS2# 13,14

MSCS3# 13,14

DCLK0 13

DCLK0# 13

DCLK1 13

DCLK1# 13

DCLK2 13

DCLK2# 13

DCLK3 13

DCLK3# 13

DCLK4 13

DCLK4# 13

DCLK5 13

DCLK5# 13

MSBS0 13,14

MSBS1 13,14

MRAS# 13,14

MCAS# 13,14

MWE# 13,14

AGPREF

DDRMAA[0..12] 13,14

DDRMAB1 13,14

DDRMAB2 13,14

DDRMAB4 13,14

DDRMAB5 13,14

MSCKE[0..3] 13,14

3

MEM_STR

R160

60.4_1%

R161

60.4_1%

Trace width 12 mil

with 10 mil space.

Place 0.1uF <1" to GMCH

C121

0.1u

R96

60.4_1%

R92

60.4_1%

3

C73

0.1u

2

DDR SERIAL RESISTORS

AGP SLOT DECOUPLING CAPACITORS

AGP SIGNAL REFERENCE CIRCUIT

VCC_AGP

Trace:Space=12mils:25mils

R174

1KRST

AGPREF

AGPREF: 10uA

R172

1KRST

CB117

X_104P

2

MSI

Title

Size Document Number Rev

Date: Sheet

1

MICRO-STAR

BROOKDALE-G GMCH2

MS-6555

1

727Wednesday, March 31, 2004

of

40a

5

4

3

2

1

C17

GMCH DECOUPLING CAPACITOR

D17

E17

G17

J17

V17

AH30

C31

AC3

AG3

AM3

AN3

AR3

AU3

AB4

AG4

Y17

AJ17

AR17

AR9

AM10

AR23

AU23

F24

AM24

VSS

VSS

A25

VSS

VSS

VSS

VSS

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

VSS

B17

AH16

M10

T10

Y10

AH20

AH24

AH28

4

GND

AF28

AB28

V28

P28

K24

K28

N35

VSS

R35

VSS

U35

VSS

AA35

VSS

AC35

VSS

AE35

VSS

AG35

VSS

AL35

VSS

AN35

VSS

AR35

VSS

AU35

VSS

B36

VSS

W36

VSS

AF8

VSS

AM8

VSS

G9

VSS

J9

VSS

N9

VSS

U9

VSS

AA9

VSS

AE9

VSS

A23

VSS

C23

VSS

D23

VSS

J23

VSS

AH36

VSS

AT36

VSS

C37

VSS

E37

VSS

J37

VSS

U37

VSS

AA37

VSS

AE37

VSS

AG37

VSS

AJ37

VSS

C25

VSS

AN37

VSS

AR37

VSS

AR11

VSS

AU11

VSS

J25

VSS

AJ25

VSS

AR25

VSS

F26

VSS

AK12

VSS

AM12

VSS

B13

VSS

C13

VSS

D13

VSS

E13

VSS

A27

VSS

C27

VSS

J27

VSS

AJ13

VSS

AR13

VSS

F14

VSS

AL27

VSS

AR27

VSS

AU27

VSS

F28

VSS

AM28

VSS

E1

VSS

J1

VSS

N1

VSS

U1

VSS

AA1

VSS

AE1AJ21

VSSVSS

AN1

VSS

AR1

VSS

B2

VSS

D15

VSS

AR15

VSS

AU15

VSS

N37

VSS

C16

VSS

Brookdale_GMCH

C122 0.1u

CB102 0.1u

CB103 X_0.1u

CB101 0.1u

CB104 X_0.1u

Near U10 Pin B2

Near U10 Pin E1

Near U10 Pin G1- P

Near U10 Pin J1

Near U10 Pin L1 - P

Place decoupling cap

close to GMCH AGP

Interface < 0.1"

VCC_AGP

0.01uC109

Near U10 Pin A15 - P

Near U10 Pin B14 - P

CB91 0.1u

Place decoupling cap

close to GMCH Core

Logic Interface <

0.1"

Electrolytic CAP(470uF/16V)

Ripplecur = 310mA

Panasonic

Electrolytic CAP(1000uF/6.3V)

Ripplecur = 1050mA

Impedance = 50mΩ

Panasonic

3

VCC_AGPVCC_AGP

CB100 0.1u

Near U10 Pin U1

Near U10 Pin AE1 Near U10 Pin A5

Place decoupling cap

close to GMCH Hub-Link

Interface< 0.1"

VCCP

CB81 105P

CB85 105P

CB86 X_105P

Place decoupling cap

close to GMCH CPU

Interface < 250mil

in the Vtt corridor

VCC_AGP

CT24

+

1000u_6.3V

Place Bulk cap for Core Logic,

AGP & Hub Link Interface

+

CT17

470u/16V

Place Bulk cap between

GMCH & DIMM slot

MSI

Title

Size Document Number Rev

2

Date: Sheet

Place decoupling cap

close to GMCH Memory

Interface < 0.1", with

18 mil trach width

MEM_STR

VCC_AGP

0.01uC145CB106 0.1u

C115 0.1u

Place decoupling cap

close to GMCH DAC

Interface< 0.1"

MEM_STR

CB67 0.1u

CB73 0.1u

CB76 0.1u

CB77 0.1u

CB88 0.1u

CB90 0.1u

CB93 0.1u

CB95 0.1u

VCCP

CB83

10u-1206

CT14

+

X_100u

CB78

10u-1206

MICRO-STAR

Broodale-G GMCH3

MS-6555

1

Near U10 Pin A7

Near U10 Pin AL37

Near U10 Pin AU33

Near U10 Pin AU29

Near U10 Pin AU25

Near U10 Pin AU17

Near U10 Pin AU13

Near U10 Pin AU9

Near U10 Pin AU5

827Wednesday, March 31, 2004

of

40a

U10D

U18

VSS

V18

Y18

AA18

AL31

D D

C C

B B

A A

AR31

AU31

F32

H32

K32

M32

P32

T32

V32

Y32

AB32

AD32

AF32

AH32

AM4

AG5

AN5

AR5

AR19

AM32

A33

C33

AJ33

AN33

AR33

AB6

AF6

AM6

U20

V20

Y20

AA20

AM20

A21

B21

C21

D21

E21

G21

J21

D34

W34

A35

E35

G35

J35

L35

AN7

AR7

AU7

V21

Y21

AR21

F22

H22

XX5

XX6

XX3

XX4

A5

C5

F6

H6

M6

T6

Y6

B8

C8

D8

F8

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

HVSS

HVSS

HVSS

HVSS

5

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

A29

C29

J29

L29

N29

U29

R29

W29

AA29

AC29

AE29

AG29

AJ29

AR29

F30

AT2E3G3J3L3N3R3U3W3

AM16

Loading...

Loading...