8

7

6

5

4

3

2

1

D D

MS-6546

Title Page

Cover Sheet

C C

B B

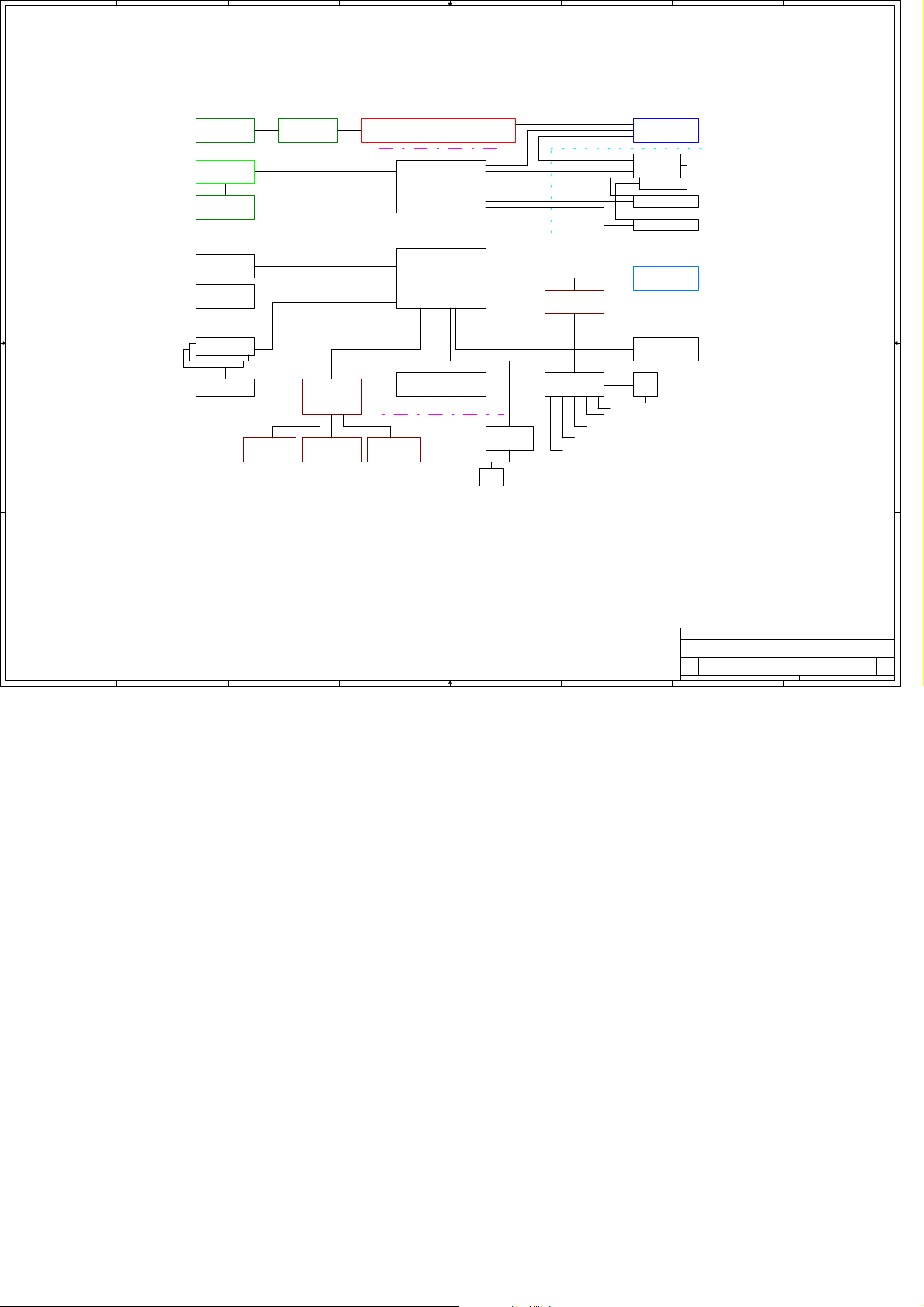

Block Diagram

Processor Sockets

Clock Synthesizer

DRCG 9

MCH

SCK/CMD

RIMM 13,14

AGP 15

ICH2

FWH

IDE Connectors

USB Connectors

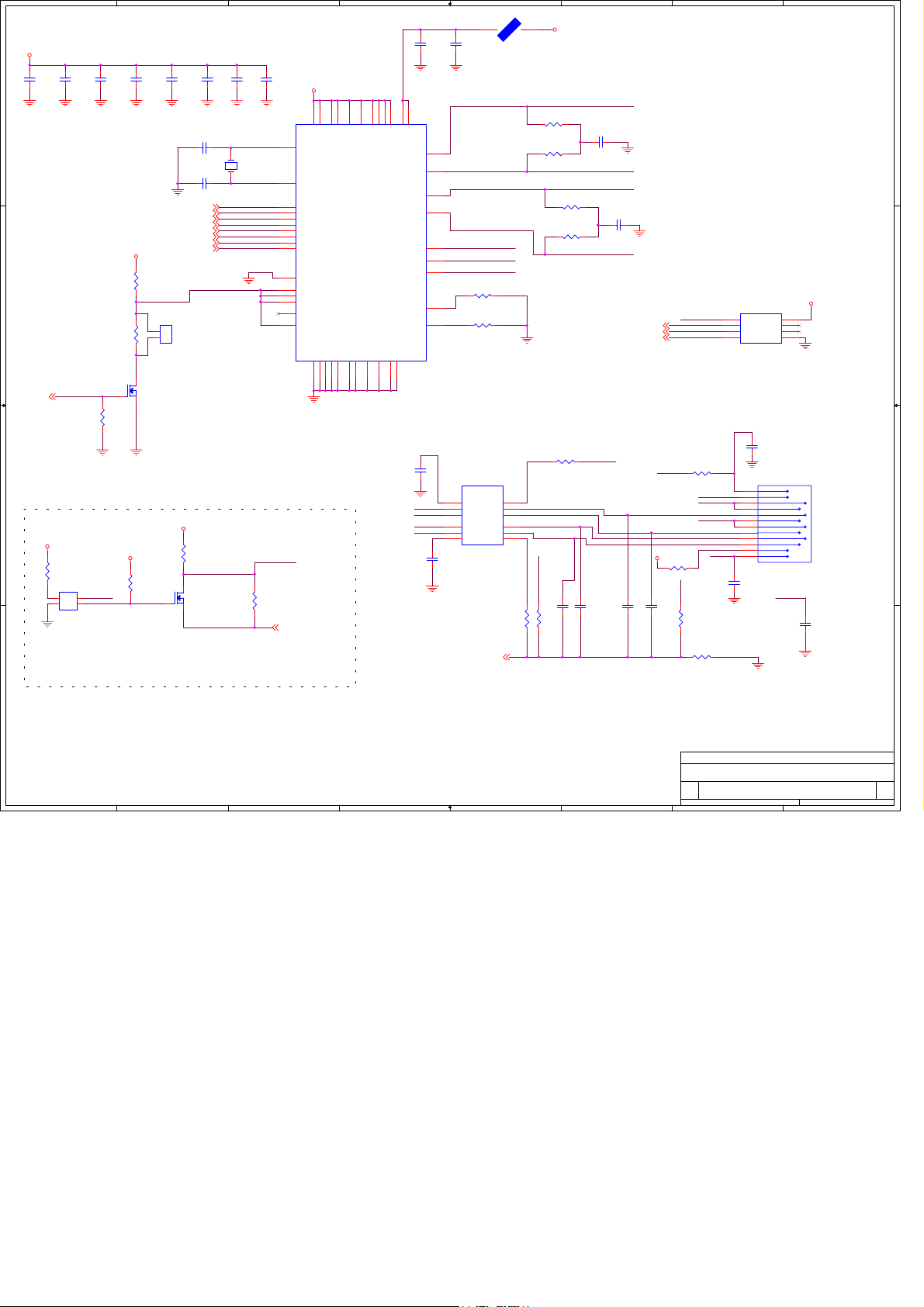

INTEL (R) 850 CHIPSET

Pentium(R) 4 PROCESSOR in 478-Pin SCHEMATICS

Title Page

1

2,3,4,5

6,7

8

10,11,12

12

16,17

18

19

20

PCI Connectors

VID 24

Audio

LPC/Flopy Connector

Hardware Monitor

Parallel Port/Serial Port

KeyBoard/Mouse Ports

PC-PC

Pull-up Resistors

Front Pannel

VRM 9.0

Voltage Regulator

Diagnostic LED

LAN

21,22,23

25,26

27CNR

28

29

30

31

32

33

34

35

36

37

41

A A

Pentium(R) 4 Mother Board

Title

Size Document Number Rev

Custom

8

7

6

5

4

3

Date: Sheet

2

COVER

MS-6546 1.0

of

139Friday, October 19, 2001

1

8

D D

7

6

5

4

3

2

1

14.318MHz

3MREF_B

3MREF

14.318MHz

33MHz

PCI_Slot_5

33MHz

PCI_Slot_4

33MHz

PCI_Slot_3

33MHz

PCI_Slot_2

33MHz

PCI_Slot_1

33MHz

33MHz

33MHz

33MHz

33MHz

48MHz Pulled_up

48MHz

66MHz

66MHz

66MHz

66MHz

50/67MHz

50/67MHz

100MHz CPU_CK

100MHz ITP_CK

100MHz MCH_CK

100MHz Pulled_up

32.7kHz

CPU

ITP Port

CK00

3.3 volt

C C

3.3 volt

3.3 volt MEM CLK

14.318MHz

B B

(Half Host CLK)

Host Clock Pairs

SUSCLK

LAN_CLK

EE_CLK

ICH

AUD_BCLK SMBCLK

POC PLD

AGP CON

HCLKOUT0

RCLKOUT0

HCLKOUT1

RCLKOUT1

MCH

24.5MHz

SMBCLK

AUDIO

CODEC

DRCG1

DRCG2

400MHz

Output

DRCG_CTM*

DRCG_CTM1

LAN

AUD_BCLK

CNR CON

AUDIO

SMBCLK

RIMM0

SCL

SMBCLK

RIMM1

SCL

SIO

KBCLK

MCLK

FWH

GLUE

HECETA

Hardware Management

RIMM2

SCL

FNT/LSB

MS/KB

RIMM4

SCL

A A

Title

Clock Distribution

Size Document Number Rev

MS-6546 1.0

Custom

8

7

6

5

4

3

Date: Sheet

2

of

239Friday, October 19, 2001

1

8

D D

7

6

5

4

3

2

1

Power

Supply

CONN

AGP 4X

AGP

CONN

VRM

AGP

CONN

C C

Heceta Hardware

Monitor

4X (266MHz) AGP

SM Bus

IDE CONN 1&2

USB Port 1:3

USB Port 4

FRNL Panel

B B

PS2 Mouse &

Keyboard

LPC Bus AC Link

SMC I/O

Parallel (1)

Serial (1)

Floppy Disk

Drive CONN

Socket 478VRM CK_SKS Clock

Scalable Bus

MCH: Memory

Controller HUB

HUB Interface

ICH2: I/O

Controller HUB

FWH: Firmware HUB

Tehama Chipset

Stuffing

Options

LAN

Scalable Bus/2

Sync Clock (2)

400MHz DIFF CLK

400MHz DIFF CLK

Direct RDRAM Channel A

Direct RDRAM Channel B

PCI (33MHz)

AC '97

Digital

Central

AC '97 Audio

Codec

Audio In

Line In

CD-ROM

Telephone In

MIC In

DRCG 1&2

RIMM SKTS 1:2

RIMM SKTS 3:4

PCI Slots 1:4

CNR Riser

(Shared slot)

AMP

Line Out

RJ45

A A

Title

Block Diagram

Size Document Number Rev

MS-6546 0A

Custom

8

7

6

5

4

3

Date: Sheet

2

of

339Thursday, October 25, 2001

1

8

7

6

5

4

3

2

1

D D

C C

B B

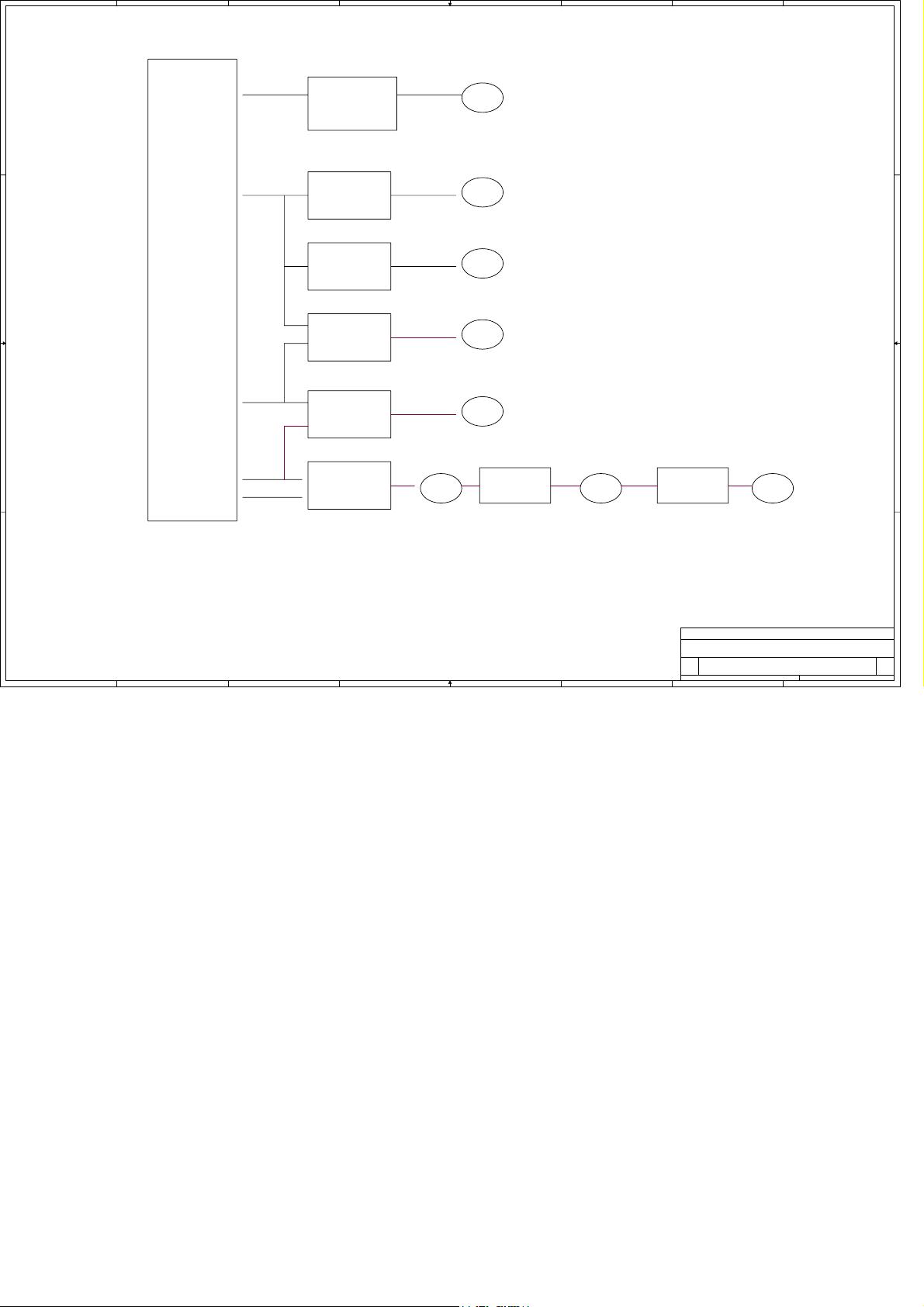

PSU

VCC12

VCC3

5VSB

VCC

VCC12

INTERSIL 3-PHASE

CONVERTER

SC1547

& MOSFET

SC1547

& MOSFET

SC1547

& MOSFET

SC1547

& MOSFET

MOSFET

5VDUAL

VCORE

VCC1.8

VDDQ

2.5VSB_STR

VCC_S4

3VSB

LT1084EZ1084

1.8VSB

A A

Title

Reset/Power on Map

Size Document Number Rev

MS-6546 1.0

Custom

8

7

6

5

4

3

Date: Sheet

2

of

439Friday, October 19, 2001

1

8

D D

7

6

5

4

3

2

1

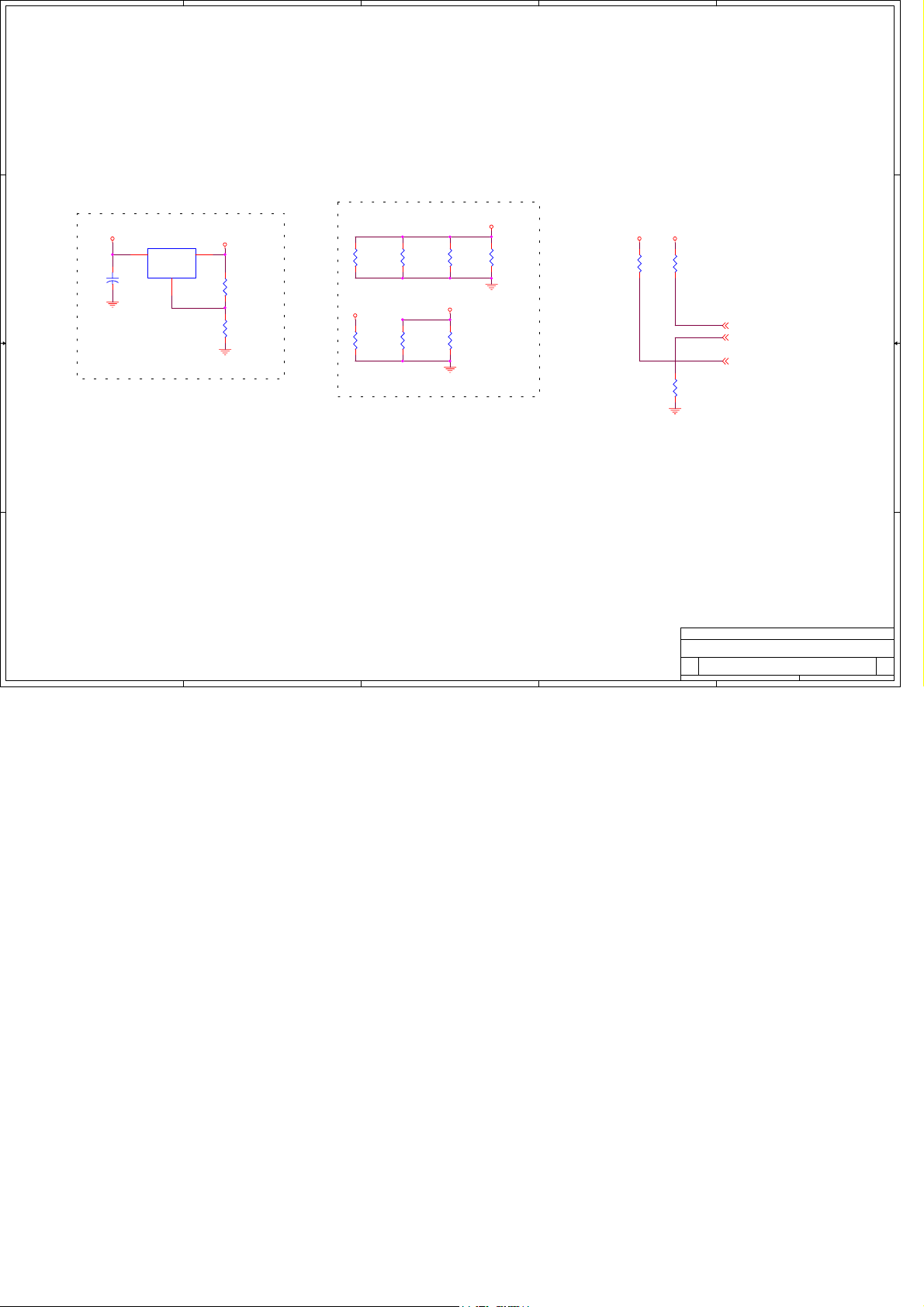

AGP

+12V

(12V)

V_AGP_Vddq

(1.5V)

C C

Vcc

(5V)

Vcc3

(3.3V)

CK-SKS

Vcc3_CLK

(3.3V)

DRCG_1

FB_DRCG1_Vcc3

(3.3V)

DRCG_2

FB_DRCG1_Vcc3

(3.3V)

FWH

Vcc3

(3.3V)

PS2 CONN

Vreg_PS2

(5V Switched)

SIO

B B

A A

Vcc3

(3.3V)

V_3P3_Stby

(3.3 Standby)

PROCESSOR

Vccp

(1.8V MAX.)

MCH

V_1P8_core

(1.8V)

V_AGP_Vddq

(1.5V)

Vccp

(16.5V MAX.)

Audio 9708

Vcc3

(3.3V)

Vcc

(5V)

V_5P0_AUD_Analog

(5V Analog)

Audio 5880

Vcc

(5V)

RAMBUS CH1

V_1P8_CMOS_CH1

(1.8V)

V_2P5_CH1

(2.5V Switched)

V_3P3_Stby

(3.3V Stanby)

RAMBUS CH2

V_1P8_CMOS_CH2

(1.8V)

V_2P5_CH2

(2.5V Switched)

V_3P3_Stby

(3.3V Stanby)

RAMBUS TERM

V_1P8_Vterm_RIMM

(1.8V)

ICH2

Vcc3

(3.3V)

V_3P3_Stby

(3.3V Standby)

V_1P8_core

(1.8V)

V_1P8_Stby

(1.8V Standby)

V_3P0_BAT_Vreg

(3.3V Standby)

(Battery Switched)

V_5P0_Stby

(5V Standby)

Vccp

(1.65V MAX.)

USB CONN

Vreg_USB

(5V Switched)

PCI Slots

Vcc3

(3.3V)

+12V

(12V)

Vcc

(5V)

V_3P3_PCIVAUX

(3.3V Switched)

CNR CONN

V_3P3_Stby

(3.3VStandby)

+12V

(12V)

Vcc

(5V)

V_5P0_Stby

(5V Standby)

Title

Power Distribution

Size Document Number Rev

MS-6546 1.0

Custom

8

7

6

5

4

3

Date: Sheet

2

of

539Friday, October 19, 2001

1

8

D D

C C

B B

A A

HD#[0..63]10

8

7

HA#[3..31]10

HDBI#[0..3]10

FERR#16,33

STPCLK#16

HINIT#16,18

HDBSY#10

HDRDY#10

HTRDY#10

HADS#10

HLOCK#10

HBNR#10

HIT#10

HITM#10

HBPRI#10

HDEFER#10

TDI_CPU33

HDBI#0

HDBI#1

HDBI#2

HDBI#3

TDO_CPU38

TMS_CPU38

TRST#_CPU33

TCK_CPU38

VTIN228,29

VAGND28,29

THERMTRIP#24,33

SKTOCC#34

PROCHOT#17,28,33

IGNNE#16

SMI#16

A20M#16

SLP#16,29

CPU_PWRGD17,33

HCPURST#10,33

HD#63

HD#62

HD#61

HD#60

HD#59

HD#58

HD#57

HD#56

HD#55

HD#54

7

AF26

AB26

AE21

AF24

AF25

AB23

AB25

AA24

AA22

AA25

E21

G25

P26

V21

AC3

AA3

W5

AB2

A22

AD2

AD3

Y21

Y24

Y23

W25

Y26

W26

V24

V6

B6

Y4

H5

H2

J6

G1

G4

G2

F3

E3

D2

E2

C1

D5

F7

E6

D4

B3

C4

A2

C3

B2

B5

C6

A7

6

HA#31

HA#30

HA#29

U6A

AB1Y1W2V3U4T5W1R6V2T4U3P6U1T2R3P4P3R2T1N5N4N2M1N1M4M3L2M6L3K1L6K4K2

A35#

A34#

A33#

A32#

A31#

A30#

DBI0#

DBI1#

DBI2#

DBI3#

IERR#

MCERR#

FERR#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

A29#

HA#28

A28#

HA#27

A27#

HA#26

A26#

HA#25

A25#

HA#24

A24#

HA#23

A23#

HA#22

A22#

5

HA#21

A21#

HA#20

A20#

HA#19

A19#

HA#18

A18#

TDO

TMS

TRST#

TCK

THERMDA

THERMDC

THERMTRIP#

SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M

SLP#

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

D53#

D52#

D51#

D50#

D49#

D48#

D47#

D46#

D45#

D44#

D43#

D42#

D41#

D40#

D39#

D38#

D37#

D36#

D35#

D34#

V22

U21

V25

U23

U24

U26

T23

T22

T25

T26

R24

R25

P24

HD#48

HD#45

HD#49

HD#46

HD#47

HD#44

HD#43

HD#42

HD#41

HD#53

HD#51

HD#52

HD#50

6

R21

HD#40

N25

HD#39

N26

HD#38

M26

HD#37

N23

HD#36

5

M24

HD#35

P21

HD#34

D33#

N22

HD#33

HA#17

A17#

D32#

M23

HD#32

HA#16

A16#

D31#

H25

HD#31

HA#15

A15#

D30#

K23

HD#30

HA#14

A14#

D29#

J24

HD#29

HA#13

A13#

D28#

L22

HD#28

HA#12

A12#

D27#

M21

HD#27

HA#11

A11#

D26#

H24

HD#26

HA#10

A10#

D25#

G26

HD#25

HA#9

A9#

D24#

L21

HD#24

HA#8

A8#

D23#

D26

HD#23

HA#7

A7#

D22#

F26

HD#22

HA#6

A6#

D21#

E25

HD#21

HA#5

A5#

D20#

F24

HD#20

HA#4

A4#

D19#

F23

HD#19

HA#3

A3#

D18#

G23

HD#18

4

VCC3

D17#

E24

HD#17

4

R43

X_150

AE25A5A4

D16#

H22

D25

HD#15

HD#16

DBR

D15#

D14#

J21

HD#14

VSS_SENSE

VCC_SENSE

D13#

D12#

D11#

D23

C26

H21

HD#11

HD#13

HD#12

AD26

AC26

ITP_CLK1

ITP_CLK0

D10#

D9#

G22

B25

HD#9

HD#10

C24

HD#8

3

VCC_SENS 35

VID[0..4] 28,35

VID3

VID2

VID4

VID1

VID0

AE1

AE2

AE3

AE4

AE5

VID4#

VID3#

VID2#

VID1#

VID0#

AA21

GTLREF3

AA6

GTLREF2

F20

GTLREF1

F6

GTLREF0

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

D8#

D7#

D6#

D5#

D4#

D3#

D2#

D1#

C23

B24

D22

C21

A25

A23

B22

HD#3

HD#4

HD#7

HD#1

HD#6

HD#2

HD#5

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

BCLK1#

BCLK0#

COMP1

COMP0

LINT1

LINT0

D0#

B21

AD6

HD#0

RS2#

RS1#

RS0#

AP1#

AP0#

BR0#

DP3#

DP2#

DP1#

DP0#

BSEL0

BSEL1

AD5

SOCKET478

3

AB4

AA5

Y6

AC4

AB5

AC6

H3

J3

J4

K5

J1

AD25

A6

Y3

W4

U6

AB22

AA20

AC23

AC24

AC20

AC21

AA2

AD24

AF23

AF22

F4

G5

F1

V5

AC1

H6

P1

L24

L25

K26

K25

J26

R5

L5

W23

P23

J23

F21

W22

R22

K22

E22

E5

D1

BPM#5

BPM#4

BPM#1

BPM#0

HREQ#4

HREQ#3

HREQ#2

HREQ#1

HREQ#0

HRS#2

HRS#1

HRS#0

R58

51RST

Title

Size Document Number Rev

Date: Sheet

VCCP

R57

49.9

R56

100

BPM#5 33

BPM#4 33

BPM#1 33

BPM#0 33

2

C35

220p

C32

C36

220p

1u

C60

C56

220p

220p

HREQ#[0..4] 10

1

VCCP

R72

49.9

C57

R71

1u

100

R78

R107

4.7K

4.7K

R59

4.7K

R49

4.7K

CPUCLK# 8

CPUCLK 8

VCCP

HRS#[0..2] 10

HBR#0 10,33

R106

51RST

HADSTB#1 10

HADSTB#0 10

HDSTBP#3 10

HDSTBP#2 10

HDSTBP#1 10

HDSTBP#0 10

HDSTBN#3 10

HDSTBN#2 10

HDSTBN#1 10

HDSTBN#0 10

LINT1 16

LINT0 16

P4-CPU1

MS-6546 0A

B

2

639Monday, October 22, 2001

1

of

8

VCCP

U6B

A10

A12

A14

A16

A18

A20A8AA10

VCC

VCC

VCC

VCC

VCC

VCC

AE13

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AE15

AE17

AE19

AE22

AE24

AE26

AE7

D10

AA11

AA13

AA15

AA17

AA19

AA23

AA26

AB10

AB12

AB14

AB16

AB18

AB20

AB21

AB24

AC11

AC13

AC15

AC17

AC19

AC22

AC25

AD10

AD12

AD14

AD16

AD18

AD21

AD23

AE11

VSS

A11

VSS

A13

VSS

A15

VSS

A17

VSS

A19

VSS

A21

VSS

A24

VSS

A26

VSS

A3

VSS

A9

VSS

AA1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AA4

VSS

AA7

VSS

AA9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AB3

VSS

AB6

VSS

AB8

VSS

VSS

VSS

VSS

VSS

VSS

AC2

VSS

VSS

VSS

AC5

VSS

AC7

VSS

AC9

VSS

AD1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AD4

VSS

AD8

VSS

VSS

P2

VSS

P22

VSS

P25

VSS

P5

VSS

R1

VSS

R23

VSS

R26

VSS

R4

VSS

T21

VSS

T24

VSS

T3

VSS

T6

VSS

U2

VSS

U22

VSS

U25

VSS

U5

VSS

V1

VSS

V23

VSS

8

D D

C C

B B

A A

7

AA12

AA14

AA16

AA18

AA8

AB11

AB13

AB15

AB17

AB19

AB7

AB9

AC10

AC12

AC14

AC16

AC18

AC8

AD11

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AE9

AF1

AF10

AF12

AF14

AF16

AF18

AF20

7

VSS

AF6

AF8

B10

B12

B14

B16

B18

B23

B20

B26B4B8

6

AD13

AD15

AD17

AD19

AD7

AD9

AE10

AE12

AE14

AE16

AE18

AE20

AE6

AE8

AF11

AF13

AF15

AF17

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

C11

C13

C15

C17C2C19

C22

C25C5C7C9D12

6

VSS

D14

D16

D18

D20

AF19

AF2

AF21

AF5

AF7

AF9

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

D21D3D24D6D8E1E11

5

VCC1.2

B11

B13

B15

B17

B19B7B9

C10

C12

AF4

AF3

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCVID

VCCVIDPRG

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

E23

V26V4W21

VSS

W24W3W6Y2Y22

E13

E15

E17

E19

5

VSS

VSS

Y25

VCC-IOPLL

VCCA

VSS

AD22

Y5

SOCKET478

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSA

4

VCCP

VCCP

C14

C16

C18

C20

C8

D11

D13

D15

D17

D19

D7

D9

E10

E12

E14

E16

E18

E20

E8

F11

F13

F15

F17

F19

F9

E26

E4

E7

E9

F10

F12

F14

F16

F18

F2

F22

F25

F5

F8

G21

G24

G3

G6

H1

H23

H26

H4

J2

J22

J25

J5

K21

K24

K3

K6

L1

L23

L26

L4

M2

M22

M25

M5

N21

N24

N3

N6

AE23

AD20

4

VCCP

VCCP

VCCP

C76

10u-1206

C37

22u-1206

C42

22u-1206

3

C33

0.1uC4X_0.1u

PLACE CAPS WITHIN CPU CAVITY

C52

10u-1206

C82

10u-1206

C44

10u-1206

FSB ADDR & CNTRL

C65

10u-1206

C106

10u-1206

C55

10u-1206

C31

10u-1206

10u-1206

C135

0.1uC50.1u

C50

PLACE CAPS WITHIN CPU CAVITY

L7

1 2

4.7u_1206

L8

1 2

4.7u_1206

3

2

VCCP

C2

C81

10u-1206

C105

10u-1206

C40

10u-1206

10u-1206

C58

0.1u

C45

C24

10u-1206

10u-1206

C28

C51

10u-1206

10u-1206

C29

C23

10u-1206

10u-1206

VCCP

VCCP

C66

10u-1206

C433

X_0.1u

C26

VCCP

C34

0.1u

0.1u

SCALABLE DATA BUS

PLACE CAPS WITHIN CPU CAVITY

C39

C61

10u-1206

10u-1206

C38

C41

10u-1206

10u-1206

C48

C75

10u-1206

10u-1206

C434

C436

0.1u

0.1u

SCALABLE DATA BUS

PLACE CAPS WITHIN CPU CAVITY

VCCP

C422

C423

X_10u-1206

X_10u-1206

Solder Side

Title

P4-CPU2

Size Document Number Rev

MS-6546 1.0

B

Date: Sheet

2

C59

0.1u

C435

X_0.1u

C424

X_10u-1206

C49

10u-1206

C46

10u-1206

C70

10u-1206

739Monday, October 22, 2001

1

C3

X_0.1u

1

C94

0.1u

of

5

4

3

2

1

VCC VCC

C409

C297

0.1u

0.1u

D D

LED017

FOR EMI

LINE_R25,26

LINE_L25,26

LNX_R26

LNX_L26

C229

C230

C202

1000p

1000p

C C

C341

X_0.1u

VCCVCC

C415

X_0.1u

1000p

C213

1000p

LED317

R412

X_2.2K

LED117

LED217

VCC3

B

R411

8.2K

C

E

X_NPN-3904LT1-S-SOT23

U32A

1 2

7407-SOIC14

U32B

3 4

7407-SOIC14

U32C

5 6

7407-SOIC14

U32D

9 8

7407-SOIC14

Q53

VCC3 VCC3

VCC3

VCC5- VCC12 5VSB VCC12-

C85

C68

0.1u

C79

0.1u

0.1u

C102

0.1u

C430

X_0.1u

C431

X_0.1u

B B

VCC

C96

0.1u

VCC VCC3 VCC3

C88

C103

0.1u

0.1u

C107

0.1u

VCC3

C242

C244

X_0.1u

X_0.1u

A A

VCC3 VCC3

C419

C387

X_0.1u

X_0.1u

for clock Generator EMI

(2001/05/02)

C370

C245

X_0.1u

X_0.1u

C310

X_0.1u

C137

X_0.1u

C289

X_0.1u

C173

X_0.1u

C78

X_0.1u

for EMI(2001/05/02)

5

SOLDER SIDE

C342

X_0.1u

4

C378

X_0.1u

JWR1

D1x6

C396

C403

X_0.1u

X_0.1u

for EMI(2001/05/02)

VCC3

VCC3

COM

COM

COM

VCC

C417

X_0.1u

6

VCC

5

4

VCC3

3

2

1

VCC

C69

C80

X_0.1u

C157

X_0.1u

X_0.1u

for EMI(2001/05/02)

C421

C377

C412

X_0.1u

X_0.1u

C388

X_0.1u

X_0.1u

3

C379

X_0.1u

C235

X_0.1u

Title

Diag. LED

Size Document Number Rev

MS-6546 1.0

B

2

Date: Sheet

of

37 39Monday, October 22, 2001

1

5

D D

4

3

2

1

VCC

U1

EZ1084B-TO263-5A

3 2

C C

VI VO

12

+

EC2

10u

VTERM

ADJ

1

R4

432

R3

200

VCC3

R431

X_330/0805

R387

X_330/0805

R398

X_330/0805

R391

X_330/0805

VCC

R385

X_330/0805

R408

X_330/0805

R386

X_330/0805

RESERVED

FOR CORSS-REGULATION

B B

A A

5

4

3

VCCP VCCPVCC3

2

R8675R89

39

TMS_CPU 6

TCK_CPU 6

TDO_CPU 6

R94

27

Title

{Title}

Size Document Number Rev

MS-6546 1.0

B

Date: Sheet

1

of

38 39Monday, October 22, 2001

3VSB

8

7

6

5

C203

104P

C204

104P

4

L21

1 2

80_0805

3VSB

3

2

1

C233

C232

104P

104P

D D

C C

ICH2 GPIO

LAN_DIS17

B B

LAN_DIS

3VSB

R453

X_8.2K

J21

LAN_DIS

12

34

X_YJ202

Add LAN Disable PIN header

2001.10.15.

C207

104P

R215

10K

G

R468

X_0

3VSB

5VDUAL

DS

2N7002S

R454

X_8.2K

C205

104P

R214

Q33

C231

104P

C216

C224

ELAN_CLK16

ELAN_RSTSYNC16

ELAN_RXD016

ELAN_RXD116

ELAN_RXD216

ELAN_TXD016

ELAN_TXD116

ELAN_TXD216

330

J22

1

2

D1x2

SHORT

3VSB

R452

X_8.2K

DS

Q61

X_2N7002S

G

C440

C442

104P

22P

22P

C441

104P

104P

3VSB

125364027914171219

VCC1

VCC2

VCCA

VCCP1

46

Y1

25MHZ

1 2

47

39

42

34

35

37

43

44

45 27

41

30

28

29

26

21

U31_CS

R455

0

CNR_EECS 16,27

VCCP2

X1

X2

LAN_CLK

LAN_RSTSYNC

LAN_RXD0

LAN_RXD1

LAN_RXD2

LAN_TXD0

LAN_TXD1

LAN_TXD2 LILED#

ADV10

ISOL_TCK

ISOL_TI

ISOL_TEX

TOUT

TESTEN

VSS1

VSS2

VSS3

VSS4

VSS5

VSSP1

VSSP2

8131824483338362022

VCCA2

VSSA

VCCT1

VCCT4

VSSA2

VCCT2

VCCT3

ACTLED#

SPDLED#

RBIAS100

VSSR1

VSSR2

X_0.01u

23

VCCR1

RBIAS10

W82562ET

C177

Place Termination R as close to 82562ET as possible

U17

VCCR2

TDP

TDN

RDP

RDN

RXIN

RXIP

TXON

TXOP

10

11

15

16

LILED

ACTLED

32

SPEEDLED

31

R202

549RST

4

R201

5

619RST

U15

7

RDC

RXC

8

RD-

RX-

6

RD+

RX+

3

TD-

TX-

1

TD+

TX+

2

TDC

CMT

TS6121C

C206

L05-0100020-B09

X_0.01u

USBGND220

R457

49.9

R458

49.9

10

RX-

9

RX+

11

14

16

15

NC_1

R466

R464

75

75

R456

75

C183

R459

57.6

R460

57.6

X_0.01u

USBGND2

C180

X_0.01u

USBGND2

TXOP

C439

X_0.01u

TXON

RXIP

RXIN

C437

X_0.01u

CNR_SHCLK16,27

CNR_EEDOUT16,27,33

CNR_EEDIN16,27

C176

X_0.01u

ACTLED

3VSB

C179

X_0.01u

R194 300

U31_CS

NC_2

R465

75

R176 300

LILED

NC_1

NC_2

R463 0/0805

U31

1

CS

VCC

2

SK

3

DI

4

DO

GND

L_93C66S

64WORD W/ 82562ET

256WORD W/ 82562EM

C167

0.01u

LANUSB1B

AMBER+

17

AMBER-

18

9

13

10

14

11

15

12

16

GREEN+

19

SPEEDLED

GREEN-

20

RJ45+USB+LEDx2-D20-BK

C189

0.01u

3VSB

8

7

NC

6

NC

5

NC

NC

RDN

NC

NC

RDP

TDN

TDP

LILED

C438

0.01u

A A

Title

LAN

Size Document Number Rev

MS-6546 1.0

Custom

8

7

6

5

4

3

Date: Sheet

2

of

39 39Monday, November 05, 2001

1

5

4

3

2

1

D D

RIMM3-X

RIMM4-X

CRIMM CRIMM

_

U13-X

MCH

C C

HEATSINK

_

U25-1

1

VPP

2

RST#

3

FGPI3

4

FGPI2

5

FGPI1

6

B B

FGPI0

7

WP#

8

TBL#

9

ID3

10

ID2

11

ID1

12

ID0

13

FWH0

14

FWH1

15

FWH2

16 17

GND FWH3

SST-256K*8-33MHz-PLCC32

FGPI4

IC(VIL)

GNDA

VCCA

FWH4

GND

INIT#

32

VCC

31

CLK

30

29

28

27

26

25

VCC

24

23

22

RFU

21

RFU

20

RFU

19

RFU

18

RFU

_

U13-X1

D1x3-1:2-BK

PCB

P01-6546100

U13-X2

D1x3-1:2-BK

AGP1-Y

X_

U25-Y

BIOS LABEL

X_G51-LA00198

AGP1-X

X_

U6-X

_

J13(1-2)

1

2

JC-D2-GN

JBAT1(1-2)

1

2

3

JC-D2-GN

J4(3)

1

2

3

JC-D2-GN

J22(1-2)

1

2

JC-D2-GN

J17(2-3)

1

2

3

JC-D2-GN

JFP2(14-15)

1

2

JC-D2-GN

J11(11-12)

1

2

JC-D2-GN

J20(1-2)

1

2

3

JC-D2-GN

J11(13-14)

1

2

JC-D2-GN

12

BAT1-X

BAT-CR2032-3V-210mAh

A A

5

U6-X1

X_

4

U6-X2

X_

3

2

Title

{Title}

Size Document Number Rev

MS-6545 0B

B

Date: Sheet

of

39 40Wednesday, October 24, 2001

1

5

4

3

2

1

J901

1

D D

VCC1

3

USB2P

4

GND1

5

GND2

D2x5-BK

E_ M_

GND3

GND4USB2N

USB3P

USB3N

VCC2

6

72

8

9

10

J902

1

VCC1

3

USB2P

4

GND1

5

GND2

_

GND3

GND4USB2N

USB3P

USB3N

VCC2

6

72

8

9

10

J900

21

43

5 6

7 8

GN_RD-D-5V-CR-A

M_

L900

C C

1 2

120-1

L901

1 2

120-1

B B

L902

1 2

120-1

L903

1 2

120-1

U13FAN

MCH

Heatsink with FAN

_

for MSI

R902

0

L_

for R335

IDE900

12

34

56

78

910

11 12

13 14

15 16

17 18

19 20

21 22

23 24

25 26

27 28

29 30

31 32

33 34

35 36

37 38

39 40

D2x20-1:21-BL-ZBT(Primary)

C916

X_33p

C917

X_33p

IDE901

12

34

56

78

910

11 12

13 14

15 16

17 18

19 20

21 22

23 24

25 26

27 28

29 30

31 32

33 34

35 36

37 38

39 40

D2x20-1:21-WH-SBT(Secondary)

CN900

1 2

3 4

5 6

7 8

X_180p

A A

Title

Size Document Number Rev

B

5

4

3

2

Date: Sheet

FOR LGE

{Title}

MS-6545 0B

of

40 40Thursday, October 25, 2001

1

Loading...

Loading...