1

Cover Sheet

Block Diagram

Clock Synthesizer

AMD 762--------North Bridge

DDR DIMM-184

AGP 4X SLOT

PCI Connectors

ATA66/100 Connectors

Parallel / Serial Port

Keyboard & Mouse

BIOS & FANs

Front Panel

A A

USB Conector

AC'97 Codec

Audio/Game Port

IDE RAID

LAN

Diagnostic LED

DDR Regulator & STR LDO

Vcore/Frequency Ajust

VRM

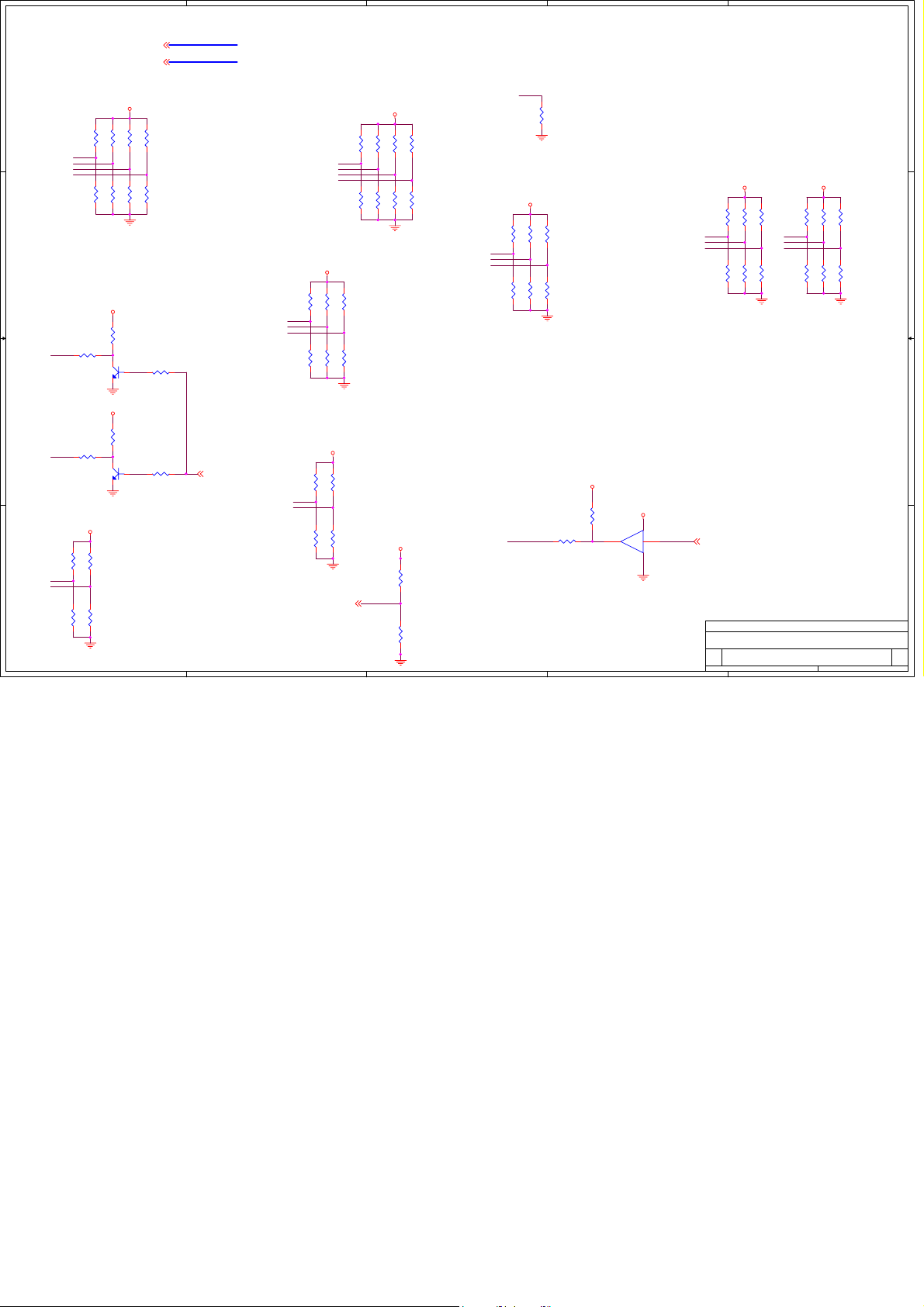

DDR Terminator

IGD4 PCI Strappings

Bypass Capacitors

ECN / History

1

2

3

4,5,6,7PGA462 Socket A CPU0/CPU1

8,9,10,11,12

13,14

15

16,17,18

19,20VIA VT686B--------South Bridge

21

22

23

24

25

26

27

28

29,30

31

32

33

34

35

36

37

38

MS-6502 ATX

Version

0A

Last Update

xx/xx/2000

CPU:

Dual AMD Socket-462 Processors

System Chipset:

AMD 762(North Bridge)

VIA 686B (South Bridge)

Expansion Slots:

AGP-Pro SLOT * 1

PCI2.2 PCI/64/33 SLOT * 5

On Board:

LAN 82550

AC97 Codec

IDE Raid

PC 2 PC

Title

Size Document Number Rev

Custom

1

Date: Sheet

MICRO-STAR

Cover Sheet

MS-6502

139Wednesday, March 21, 2001

of

0A

1

K7 462-Pin

VRM Clock

Socket

Processor

K7 462-Pin

Socket

Processor

Block Diagram

AMD SYSTEM BUS

AGP PRO

2X/4X

A A

UltraDMA

IDE Primary

33/66/100

IDE Secondary

USB Port 1

USB

AMD762

North Bridge

VIA 686B

South

Bridge

USB Port 2

USB Port 3

USB Port 4

Onboard

AC'97 Codec

PC 2 PC

AC'97

Link

AMD SYSTEM BUS

VTT 1.25V

Regulator

PCI CNTRL

PCI ADDR/DATA

4

Register

DDR

DIMM

Modules

INTEL 82550

LAN

PCI CNTRL

PCI ADDR/DATA

PCI CNTRL

Promise

20265 IDE

RAID

PCI ADDR/DATA

PCI Conn 1

PCI Conn 2

PCI Conn 3

PCI Conn 4

PCI Conn 5

PCI 2.2

10/100Mbps

ISA

Bus

Conn.

BIOS

ATA

33/66/100

ATA

33/66/100

Keyboard SerialParallel

Mouse

Game ConnFloopy

Title

Size Document Number Rev

Custom

1

Date: Sheet of

MICRO-STAR

Block Diagram

MS-6502

239Wednesday, March 21, 2001

0A

5

* 25 mils Trace on Layer 6

with GND copper around it

D D

PCISTP-<19>

CPUSTOP-<19>

FP_RST-<25>

C C

B B

A A

100/133-<34,37>

PAPICCLK<34>

OSC<20>

CPUCLK0&CPUCLK0#:

CPUCLK1&CPUCLK1#:

CPUCLK2&GCLK0 X

GCLK1 X-4.5

NBCLK&SBCLK

PCICLK GROUP X-2.5

* X MEANS THE SHORTEST LENGTH FOR MAINTAIN

PROPAGATION DELAY

* CPUCLK1'S TERMINATION CKT MUST BE PLACED

NEAR TO NB

VCC3

R335 22-REV

R340 22-REV

R318 22

R295 22

C326

10p

WIDTH/SPACE LENGTH

5/20 5 FOR DIFF. PAIR X-1 INCH

5/20 5 FOR DIFF. PAIR X-1 INCH

5/20

5/20

5/20

5/20

* Put close to every power pin

FB16

0_1206

FB15

0_1206

C371

0.01u

1 2

1 2

3 4

5 6

7 8

X

VCC3

3 4

RN68

10K

5 6

7 8

RN77

10K

C354

0.01u

4

+

EC42

10u

Y3

14M-16pf-HC49S-D

R298

1M-REV

C336

C335

22p

22p

FS2 FS1

0

000

0

0

1

0

11

0

1

0

1

11

1

C358

330p

3422189154845

VDD

VDDSD

4

VDDREF

X1

5

X2

32

PCI_STOP_L

31

CPU_STOP_L

30

PD_L

29

SPREAD_L

28

FS2

2

FS1

1

FS0

24

24MHZ/48MHZ#

35

RSVD2

44

RSVD1

GND

GND

GND

GND

212536333841

12

*Put GND copper under Clock Gen.

connect to every GND pin

CPU

FS0

SDRAM

133.3 33.3 66.7

95.0

1

100.99

0

115.0

100.7

0

103.0

1

105.0 35.0011 0 60.0

110.0

C339330p

C337330p

VDD48

VDDAGP

CPUCLKT2

VDDPCI1

VDDPCI2

CPUCLKC2

CPUCLKT1

CPUCLKC1

CPUCLKT0

CPUCLKC0

SDRAM_OUT

PCICLK_F0

GND

GND

GND

GND

GND

47

PCI AGP

31.67

33.66

38.33

33.57

34.33

36.67

C5380.01u

PCICLK6

PCICLK5

PCICLK4

PCICLK3

PCICLK2

PCICLK1

PCICLK0

AGP1

AGP0

USB0

SCLK

SDATA

W174B

63.33

67.33

76.67

67.13

66.6

66.6

C5330.01u

3

2

1

Clock Synthesizer

10u

EC44

C5290.01u

U24

+

C5370.01u

C3730.01u

C3720.01u

R302 0

42

CPUCLKC2

43

CPUCLKT1

39

CPUCLKC1

40

CPUCLKT0

36

CPUCLKC0

37

46

PCICLK6

17

PCICLK5

16

PCICLK4

14

PCICLK3

13

PCICLK2

11

PCICLK1

10

PCICLK0

8

PCICLK_FB

7

AGP1

20

AGP0

19

USB0

23

26

27

CPUCLKC2

CPUCLKC1

CPUCLKT1

CPUCLKC0

CPUCLKT0

PCICLK6

PCICLK5

PCICLK4

PCICLK3

PCICLK2

PCICLK1

PCICLK0

PCICLK_FB

AGP1

AGP0

USB0

C346 10p

NOPOP

CN15 10p

7 8

5 6

3 4

1 2

C365 10p

NOPOP

CN16 10p

7 8

5 6

3 4

1 2

7 8

5 6

3 4

1 2

CN14 10p

C369 10p

NOPOP

C367 10p

NOPOP

C374 10p

NOPOP

NOPOP

NOPOP

NOPOP

1 2

3 4

5 6

7 8

RN72 33

RN75 22

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

RN71 22

R333 22

R332 22

R336 22

PCICLK6

Close to clock generator

CPUCLK2 <8>

CPUCLK-1 <6>

CPUCLK1 <6>

CPUCLK-0 <4>

CPUCLK0 <4>

PCLK5 <18>

PCLK4 <17>

PCLK3 <17>

PCLK2 <16>

PCLK1 <16>

NBCLK <11>

SBCLK <19>

GCLK1 <15>

GCLK0 <11>

USBCLK <20>

SMBCLK <13,14,19,20,34>

SMBDATA <13,14,19,20,34>

R317 22

R327 22

VCC3

C5170.01u

C5060.01u

NOPOP

Length = X"

Length = X" - 1"

Length = X" - 2.5"

Length = X"

Length = X"

Length = X" - 4.5"

LANCLK <31>

IDECLK <29>

C5140.01u

C3760.01u

NOPOP

NOPOP

NOPOP

(5 mil trace / 20 mil clearance)

(20/5/5/5/20)

(5 mil trace / 20 mil clearance)

(5 mil trace / 20 mil clearance)

(5 mil trace / 20 mil clearance)

(5 mil trace / 20 mil clearance)

(5 mil trace / 20 mil clearance)

LAN: Length = X"(SHARE)

IDE: Length = X"(SHARE)

EMI

C900.01u

C5050.01u

NOPOP

NOPOP

Title

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet of

MICRO-STAR

Clock Synthesizer

MS-6502

1

339Wednesday, March 21, 2001

0A

A

P0_SDATA-[0..63]<8>

4 4

3 3

P0_DICLK-[0..3]<8>

2 2

P0_DOCLK-[0..3]<8>

P0_SDATA-0

P0_SDATA-1

P0_SDATA-2

P0_SDATA-3

P0_SDATA-4

P0_SDATA-5

P0_SDATA-6

P0_SDATA-7

P0_SDATA-8

P0_SDATA-9

P0_SDATA-10

P0_SDATA-11

P0_SDATA-12

P0_SDATA-13

P0_SDATA-14

P0_SDATA-15

P0_SDATA-16

P0_SDATA-17

P0_SDATA-18

P0_SDATA-19

P0_SDATA-20

P0_SDATA-21

P0_SDATA-22

P0_SDATA-23

P0_SDATA-24

P0_SDATA-25

P0_SDATA-26

P0_SDATA-27

P0_SDATA-28

P0_SDATA-29

P0_SDATA-30

P0_SDATA-31

P0_SDATA-32

P0_SDATA-33

P0_SDATA-34

P0_SDATA-35

P0_SDATA-36

P0_SDATA-37

P0_SDATA-38

P0_SDATA-39

P0_SDATA-40

P0_SDATA-41

P0_SDATA-42

P0_SDATA-43

P0_SDATA-44

P0_SDATA-45

P0_SDATA-46

P0_SDATA-47

P0_SDATA-48

P0_SDATA-49

P0_SDATA-50

P0_SDATA-51

P0_SDATA-52

P0_SDATA-53

P0_SDATA-54

P0_SDATA-55

P0_SDATA-56

P0_SDATA-57

P0_SDATA-58

P0_SDATA-59

P0_SDATA-60

P0_SDATA-61

P0_SDATA-62

P0_SDATA-63

P0_DICLK-0

P0_DICLK-1

P0_DICLK-2

P0_DICLK-3

P0_DIVAL-

P0_DIVAL-<8>

P0_DOCLK-0

P0_DOCLK-1

P0_DOCLK-2

P0_DOCLK-3

P0_AIN-[2..14]<8>

1 1

P0_AINCLK-<8>

P0_CFWDRST<8>

P0_CONNECT<8>

P0_PROCRDY<8>

P0_SFILLVAL-<8>

A

P0_DOVAL-

P0_AIN-0

P0_AIN-1

P0_AIN-2

P0_AIN-3

P0_AIN-4

P0_AIN-5

P0_AIN-6

P0_AIN-7

P0_AIN-8

P0_AIN-9

P0_AIN-10

P0_AIN-11

P0_AIN-12

P0_AIN-13

P0_AIN-14

P0_CFWDRST

P0_CONNECT

P0_PROCRDY

P0_SFILLVAL-

R266

10K

AA35

AA33

AE37

AC33

AC37

AA37

AC35

AN33

AE35

AL31

AL29

AG33

AL35

AE33

AG37

AL33

AN37

AL37

AG35

AN29

AN35

AN31

AL23

AN23

W37

W35

Y35

U35

U33

S37

S33

Y37

S35

Q37

Q35

N37

J33

G33

G37

E37

G35

Q33

N33

L33

N35

L37

J37

A37

E35

E31

E29

A27

A25

E21

C23

C27

A23

A35

C35

C33

C31

A29

C29

E23

C25

E17

E13

E11

C15

E9

A13

C9

A9

C21

A21

E19

C19

C17

A11

A17

A15

W33

J35

E27

E15

C37

A33

C11

AJ29

AJ37

AJ35

AJ33

AJ21

AJ31

SDATA0

SDATA1

SDATA2

SDATA3

SDATA4

SDATA5

SDATA6

SDATA7

SDATA8

SDATA9

SDATA10

SDATA11

SDATA12

SDATA13

SDATA14

SDATA15

SDATA16

SDATA17

SDATA18

SDATA19

SDATA20

SDATA21

SDATA22

SDATA23

SDATA24

SDATA25

SDATA26

SDATA27

SDATA28

SDATA29

SDATA30

SDATA31

SDATA32

SDATA33

SDATA34

SDATA35

SDATA36

SDATA37

SDATA38

SDATA39

SDATA40

SDATA41

SDATA42

SDATA43

SDATA44

SDATA45

SDATA46

SDATA47

SDATA48

SDATA49

SDATA50

SDATA51

SDATA52

SDATA53

SDATA54

SDATA55

SDATA56

SDATA57

SDATA58

SDATA59

SDATA60

SDATA61

SDATA62

SDATA63

SDATAINCLK0

SDATAINCLK1

SDATAINCLK2

SDATAINCLK3

SDATAINVAL

SDATAOUTCLK0

SDATAOUTCLK1

SDATAOUTCLK2

SDATAOUTCLK3

SDTATOUTVAL

SADDIN0

SADDIN1

SADDIN2

SADDIN3

SADDIN4

SADDIN5

SADDIN6

SADDIN7

SADDIN8

SADDIN9

SADDIN10

SADDIN11

SADDIN12

SADDIN13

SADDIN14

SADDINCLK

CLKFWDRST

CONNECT

PROCRDY

SFILLVAL

B

A20M

FERR

IGNNE

RESET

STPCLK

PWROK

PICCLK

PICD0/BYPASSCLK

PICD1/BYPASSCLK

COREFB-

COREFB+

CLKIN

CLKIN

RSTCLK

RSTCLK

K7CLKOUT

K7CLKOUT

ANALOG

SYSVREFMODE

VREF_SYS

PLLBYPASS

PLLBYPASSCLK

PLLBYPASSCLK

PLLMON1

PLLMON2

PLLTEST

SCANCLK1

SCANCLK2

SCANINTEVAL

SCANSHIFTEN

DBRDY

DBREQ

FLUSH

TRST

SCHECK0

SCHECK1

SCHECK2

SCHECK3

SCHECK4

SCHECK5

SCHECK6

SCHECK7

SADDOUT0

SADDOUT1

SADDOUT2

SADDOUT3

SADDOUT4

SADDOUT5

SADDOUT6

SADDOUT7

SADDOUT8

SADDOUT9

SADDOUT10

SADDOUT11

SADDOUT12

SADDOUT13

SADDOUT14

SADDOUTCLK

B

C

CPU1A

A20M-

AE1

AG1

AJ3

INIT

AL1

INTR

AJ1

AN3

NMI

AG3

AN5

SMI

AC1

AE3

R315 100

N1

N3

N5

AG13

AG11

AN17

AL17

AN19

AL19

AL21

AN21

AJ13

AA5

W5

AC5

ZN

AE5

ZP

AJ25

AN15

AL15

AN13

AL13

AC3

S1

S5

S3

Q5

P0_CPU_DBRDY

AA1

P0_DBREQ-

AA3

P0_FLUSH-

AL3

Q1

TCK

U1

TDI

U5

TDO

Q3

TMS

U3

L1

VID0

L3

VID1

L5

VID2

L7

VID3

J7

VID4

W1

FID0

W3

FID1

Y1

FID2

Y3

FID3

P0_SCHECK-0

U37

P0_SCHECK-1

Y33

P0_SCHECK-2

L35

P0_SCHECK-3

E33

P0_SCHECK-4

E25

P0_SCHECK-5

A31

P0_SCHECK-6

C13

P0_SCHECK-7

A19

J1

J3

P0_AOUT-2

C7

P0_AOUT-3

A7

P0_AOUT-4

E5

P0_AOUT-5

A5

P0_AOUT-6

E7

P0_AOUT-7

C1

P0_AOUT-8

C5

P0_AOUT-9

C3

P0_AOUT-10

G1

P0_AOUT-11

E1

P0_AOUT-12

A3

P0_AOUT-13

G5

P0_AOUT-14

G3

E3

PGA-D462

FERR

CPUINITINTR

IGNNENMI

CPURSTSMISTPCLK-

APICD0APICD1-

P0_COREFBP0_COREFB

CPUCLK0_R

CPUCLK-0_R

P0_CLKOUT

P0_CLKOUT-

P0_VREFMODE

P0_VREF_SYS

P0_ZN

P0_ZP

P0_PLLBP-

P0_PLLMON1

P0_PLLMON2

P0_PLLTEST-

P0_SCANCLK1

P0_SCANCLK2

P0_SINTVAL

P0_SSHIFTEN

P0_CPU_TCK

P0_CPU_TDI

P0_CPU_TDO

P0_CPU_TMS

P0_CPU_TRST-

P0_VID0

P0_VID1

P0_VID2

P0_VID3

P0_VID4

P0_FID0

P0_FID1

P0_FID2

P0_FID3

A20M- <6,19>

FERR <6>

CPUINIT- <6,19>

INTR <6,19>

IGNNE- <6,19>

NMI <6,19>

SMI- <6,19>

STPCLK- <6,19>

P0_DC_OK <23>

APICCLK

APICD0- <6,34>

APICD1- <6,34>

The farest VCORE and GND

P0_VID0 <34>

P0_VID1 <34>

P0_VID2 <34>

P0_VID3 <34>

P0_VID4 <34>

P0_FID0 <34>

P0_FID1 <34>

P0_FID2 <34>

P0_FID3 <34>

P0_AOUTCLK- <8>

**All CPU interface are 2.5V tolerant**

CPURST- <6,19>

C351

4700p

APICCLK <6,34>

P0_COREFB- <35>

P0_COREFB <35>

R293

R285

100

100

AMD use 100ohm

VCORE

VCORE

RN63

78

56

34

12

100

CPUCLK0<3>

RN76

7 8

5 6

3 4

1 2

680

RN66

1 2

3 4

5 6

7 8

680

R286 56

R284 56

R314 680

R267 680

R247 270

R253 270

R241 270

R236 270

680pC311

680pC307

21

21

P0_SCHECK-[0..7] <8>

P0_AOUT-[2..14] <8>

INTR

CPUINITNMI

SMI-

IGNNECPURSTA20MSTPCLK-

P0_PLLMON1

P0_PLLMON2

P0_FLUSHP0_PLLBP-

P0_AIN-0

P0_AIN-1

P0_DOVAL-

P0_SFILLVAL-

CPUCLK0_R

CPUCLK-0_R

VCORE

R274

301

P0_SSHIFTEN

P0_SINTVAL

P0_SCANCLK2

P0_DBREQCPURST-

R276 60.4

R272 60.4

CPUCLK-0<3>

C

D

VCORE

HDT2

1

1

2

3

3

4

5

5

6

7

7

8

9

9

10

11

11

12

13

13

14

15 16

15 16

D2x8-BK

NOPOP

VCORE

FERR

P0_VREFMODE

VREFMODE=Low=No voltage scaling

VCORE

Near socket-A

D

P0_DBREQ-

P0_PLLTEST-

P0_CPU_TCK

2

P0_CPU_TMS

4

P0_SCANCLK1

6

P0_CPU_TDI

8

P0_CPU_TRST-

10

P0_CPU_TDO

12

P0_CPU_DBRDY

14

P0_PLLTEST-

P0_CPU_TCK

P0_CPU_TMS

P0_CPU_TRSTP0_CPU_TDI

VCC3

R328

1K

5

2 4

3

7S14-SSOP5

U28

VCORE

for internal VREFSYS

R280

1K-REV

R282

270

P0_SCANCLK1

P0_SSHIFTEN

P0_SINTVAL

P0_SCANCLK2

1 2

3 4

5 6

7 8

Title

Size Document Number Rev

Custom

Date: Sheet

0.5 * VCORE

P0_VREF_SYS

RN79

P0_ZN

P0_ZP

10K

P0_CLKOUT

P0_CLKOUT-

* Trace lengths of CLKOUT

and -CLKOUT are between

2" and 3"

SocketA (Part 1)

C321

39p

match the transmission line

Push-Pull compensation circuit

MICRO-STAR

MS-6502

E

R313 510

R305 510

FERR-

C320

1000p

R279 40.2

R278 40.2

E

C319

0.047u

100

RN80

510

VCORE

RN59

439Thursday, March 22, 2001

VCORE

12

34

56

78

FERR- <19>

R283

100

R281

100

VCORE

VCORE

78

56

34

12

of

0A

A

B

C

D

E

* 25 mils Trace/ 12 mils Space

RN55

100

VCC P0_VCCA_PLL1P0_VCCA_PLL

7 8

5 6

3 4

1 2

C253

4 4

39p

2 1

Max 150mA,

Design for

100mA

C271

39p

2

2 1

3 1

VR6

CSK-2-SOT23-150mA

R250

0

R264

0-REV

C281

0.01u

Used when

spec.

change

2.5V

R257 10R259 0

C289

C266

C291

39p

2 1

39p

2 1

NOPOP

NOPOP

VCCA_PLL trace length from the VR1 to the PGA must be 0.75".

Place al filters close to the PGA.

Keep all power and signal trce away from the VR1.

Place a cut in the GND plane around the VCCA_PLL regulator circuit.

39p

2 1

Place

inside CPU

socket

C272

39p

2 1

Power Up Strappings :

AD[3:0] => CPU Clock Multiplier

0000 3

0001 3.5

0010 4

0011 4.5

0100 5

0101 5.5

0110 6

0111 6.5

1000 7

1001 7.5

1010 8

1011 8.5

1100 9

1101 9.5

1110 10

1111 Reserved

B20

B16

B12B8B4

VCC_CORE96

VCC_CORE97

VCC_CORE98

VCC_CORE99

VSS98

VSS99

VSS100

VSS101

B14

B10B6B2

AJ5

VCC_CORE100

VCC_CORE101

BP0_CUT

BP1_CUT

BP2_CUT

BP3_CUT

VSS102

VSS103

VSS104

AM4

AK6

AM6

D

P0_VCCA_PLL

0~100 mA,

2.25~2.75V

CPU1B

AC7

AJ23

PGA-D462

VCC_Z

VCC_A

AA31

NC1

AC31

NC2

AE31

NC3

AG23

NC6

AG25

NC7

AG31

NC8

AG5

NC9

AJ11

NC10

AJ15

NC11

AJ17

NC12

AJ19

NC13

AJ27

NC15

AL11

NC16

AN11

NC17

AN9

NC18

G11

NC19

G13

NC20

G27

NC21

G29

NC22

G31

NC23

J31

NC24

J5

NC25

L31

NC27

N31

NC28

Q31

NC29

S31

NC30

S7

NC31

U31

NC32

U7

NC33

W31

NC34

W7

NC35

Y31

NC36

Y5

NC37

AG19

NC42

G21

NC43

AG21

NC44

G19

NC45

AE7

VSS_Z

AN27

AL27

AN25

AL25

VCC

P0BP0 <34>

P0BP1 <34>

P0BP2 <34>

P0BP3 <34>

R294

The presence pin is only connected to GND

10K

through the processor

P0_PRESENCE-

Title

Size Document Number Rev

Custom

Date: Sheet

MICRO-STAR

SocketA (Part 2)

MS-6502

539Wednesday, March 21, 2001

E

0A

of

VCORE

3 3

2 2

1 1

AD30

AF10

AF28

AF30

AF32

AH30

AG15

AG29

AD8

AF6

AF8

AH8

AJ9

AK8

AL9

AM8

F30

H10

H28

H30

H32

K30

AJ7

AL7

AN7

G25

G17

G9

AG7

F8

H6

H8

K8

N7

Y7

VCC_SRAM1

VCC_SRAM2

VCC_SRAM3

VCC_SRAM4

VCC_SRAM5

VCC_SRAM6

VCC_SRAM7

VCC_SRAM8

VCC_SRAM9

VCC_SRAM11

VCC_SRAM13

VCC_SRAM14

VCC_SRAM16

VCC_SRAM17

VCC_SRAM19

VCC_SRAM20

VCC_SRAM21

VCC_SRAM22

VCC_SRAM23

VCC_SRAM24

VCC_SRAM25

VCC_SRAM26

VCC_SRAM27

VCC_SRAM28

VCC_SRAM29

VCC_SRAM30

VCC_SRAM31

KEY4

KEY6

KEY8

KEY10

KEY12

KEY14

KEY16

KEY18

H12

H16

H20

H24M8P30R8T30V8X30Z8AB30

VCC_CORE1

VCC_CORE2

VCC_CORE3

VCC_CORE4

VCC_CORE5

VSS1

VSS2

VSS3

VSS4

VSS5

H14

H18

H22

H26

M30P8R30T8V30X8Z30

A

VCC_CORE6

VCC_CORE7

VCC_CORE8

VCC_CORE9

VSS6

VSS7

VSS8

VSS9

AF14

AF18

VCC_CORE10

VCC_CORE11

VCC_CORE12

VCC_CORE13

VCC_CORE14

VSS10

VSS11

VSS12

VSS13

VSS14

AB8

AF12

AF16

AF22

AF26

AM34

AK36

VCC_CORE15

VCC_CORE16

VCC_CORE17

VCC_CORE18

VSS15

VSS16

VSS17

VSS18

AF20

AF24

AM36

AK32

AK34

AK30

AK26

AK22

VCC_CORE19

VCC_CORE20

VCC_CORE21

VCC_CORE22

VSS19

VSS20

VSS21

VSS22

AK28

AK24

AK20

AK16

AK18

AK14

AK10

AL5

VCC_CORE23

VCC_CORE24

VCC_CORE25

VCC_CORE26

VSS23

VSS25

VSS26

VSS27

AK12

AK4

AK2

AH36

AH26

AM30

AH22

AH18

VCC_CORE27

VCC_CORE28

VCC_CORE29

VSS28

VSS29

VSS30

AM32

AH34

AH32

AH28

AH14

AH10

AH4

AH2

VCC_CORE30

VCC_CORE31

VCC_CORE32

VCC_CORE33

VCC_CORE34

VSS31

VSS32

VSS33

VSS34

VSS35

AH24

AH20

AH16

AH12

AF36

AF34

AD6

AM26

VCC_CORE35

VCC_CORE36

VCC_CORE37

VCC_CORE38

VSS37

VSS38

VSS39

VSS40

AF4

AF2

AD36

AD34

B

AD4

AD2

AB36

AB34

VCC_CORE39

VCC_CORE40

VCC_CORE41

VSS41

VSS42

VSS43

AD32

AB6

AB4

AB2

AB32Z6Z4Z2X36

VCC_CORE42

VCC_CORE43

VCC_CORE44

VCC_CORE45

VCC_CORE46

VSS44

VSS45

VSS46

VSS47

VSS48

Z36

Z34

Z32X6AM28X4X2

X34

AM22

X32V6V4V2T36

VCC_CORE47

VCC_CORE48

VCC_CORE49

VCC_CORE50

VCC_CORE51

VSS49

VSS50

VSS51

VSS52

VSS53

V36

V34

T34

VCC_CORE52

VCC_CORE53

VCC_CORE54

VCC_CORE55

VSS54

VSS55

VSS56

VSS57

V32T6T4T2R36

T32R6R4R2AM18

VCC_CORE56

VCC_CORE57

VCC_CORE58

VCC_CORE59

VSS58

VSS59

VSS60

VSS61

R34

AM24

R32P6P4P2M36

P36

P34

P32M4M6M2K36

VCC_CORE60

VCC_CORE61

VCC_CORE62

VCC_CORE63

VSS62

VSS63

VSS64

VSS65

M34

K34

VCC_CORE64

VCC_CORE65

VCC_CORE66

VCC_CORE67

VCC_CORE68

VSS66

VSS67

VSS68

VSS69

VSS70

M32K6K4K2AM20

C

K32H4H2

AM14

VCC_CORE69

VCC_CORE70

VCC_CORE71

VCC_CORE72

VSS71

VSS72

VSS73

VSS74

H36

H34

F26

F36

F34

F32

F28

VCC_CORE73

VCC_CORE74

VCC_CORE75

VCC_CORE76

VSS75

VSS76

VSS77

VSS78

F22

F18

F14

F10F6F4F2AM16

F24

F20

F16

F12

VCC_CORE77

VCC_CORE78

VCC_CORE79

VCC_CORE80

VSS79

VSS80

VSS81

VSS82

D32

D28

AM10

D24

VCC_CORE81

VCC_CORE82

VCC_CORE83

VCC_CORE84

VSS83

VSS84

VSS85

VSS86

D36

D34

D30

D26

D20

D16

D12D8D4D2B36

VCC_CORE85

VCC_CORE86

VCC_CORE87

VCC_CORE88

VSS87

VSS88

VSS89

VSS90

D22

D18

D14

D10D6B34

B32

AM2

VCC_CORE89

VCC_CORE90

VCC_CORE91

VCC_CORE92

VCC_CORE93

VSS91

VSS92

VSS93

VSS94

VSS95

AM12

B30

B26

B28

B24

VCC_CORE94

VCC_CORE95

VSS96

VSS97

B22

B18

A

P1_SDATA-[0..63]<9>

4 4

3 3

P1_DICLK-[0..3]<9>

2 2

P1_DOCLK-[0..3]<9>

P1_SDATA-0

P1_SDATA-1

P1_SDATA-2

P1_SDATA-3

P1_SDATA-4

P1_SDATA-5

P1_SDATA-6

P1_SDATA-7

P1_SDATA-8

P1_SDATA-9

P1_SDATA-10

P1_SDATA-11

P1_SDATA-12

P1_SDATA-13

P1_SDATA-14

P1_SDATA-15

P1_SDATA-16

P1_SDATA-17

P1_SDATA-18

P1_SDATA-19

P1_SDATA-20

P1_SDATA-21

P1_SDATA-22

P1_SDATA-23

P1_SDATA-24

P1_SDATA-25

P1_SDATA-26

P1_SDATA-27

P1_SDATA-28

P1_SDATA-29

P1_SDATA-30

P1_SDATA-31

P1_SDATA-32

P1_SDATA-33

P1_SDATA-34

P1_SDATA-35

P1_SDATA-36

P1_SDATA-37

P1_SDATA-38

P1_SDATA-39

P1_SDATA-40

P1_SDATA-41

P1_SDATA-42

P1_SDATA-43

P1_SDATA-44

P1_SDATA-45

P1_SDATA-46

P1_SDATA-47

P1_SDATA-48

P1_SDATA-49

P1_SDATA-50

P1_SDATA-51

P1_SDATA-52

P1_SDATA-53

P1_SDATA-54

P1_SDATA-55

P1_SDATA-56

P1_SDATA-57

P1_SDATA-58

P1_SDATA-59

P1_SDATA-60

P1_SDATA-61

P1_SDATA-62

P1_SDATA-63

P1_DICLK-0

P1_DICLK-1

P1_DICLK-2

P1_DICLK-3

P1_DIVAL-

P1_DIVAL-<9>

P1_DOCLK-0

P1_DOCLK-1

P1_DOCLK-2

P1_DOCLK-3

P1_AIN-[2..14]<9>

1 1

P1_AINCLK-<9>

P1_CFWDRST<9>

P1_CONNECT<9>

P1_PROCRDY<9>

P1_SFILLVAL-<9>

A

P1_DOVAL-

P1_AIN-0

P1_AIN-1

P1_AIN-2

P1_AIN-3

P1_AIN-4

P1_AIN-5

P1_AIN-6

P1_AIN-7

P1_AIN-8

P1_AIN-9

P1_AIN-10

P1_AIN-11

P1_AIN-12

P1_AIN-13

P1_AIN-14

P1_CFWDRST

P1_CONNECT

P1_PROCRDY

P1_SFILLVAL-

R156

10K

AA35

AA33

AE37

AC33

AC37

AA37

AC35

AN33

AE35

AL31

AL29

AG33

AL35

AE33

AG37

AL33

AN37

AL37

AG35

AN29

AN35

AN31

AL23

AN23

W37

W35

Y35

U35

U33

S37

S33

Y37

S35

Q37

Q35

N37

J33

G33

G37

E37

G35

Q33

N33

L33

N35

L37

J37

A37

E35

E31

E29

A27

A25

E21

C23

C27

A23

A35

C35

C33

C31

A29

C29

E23

C25

E17

E13

E11

C15

E9

A13

C9

A9

C21

A21

E19

C19

C17

A11

A17

A15

W33

J35

E27

E15

C37

A33

C11

AJ29

AJ37

AJ35

AJ33

AJ21

AJ31

SDATA0

SDATA1

SDATA2

SDATA3

SDATA4

SDATA5

SDATA6

SDATA7

SDATA8

SDATA9

SDATA10

SDATA11

SDATA12

SDATA13

SDATA14

SDATA15

SDATA16

SDATA17

SDATA18

SDATA19

SDATA20

SDATA21

SDATA22

SDATA23

SDATA24

SDATA25

SDATA26

SDATA27

SDATA28

SDATA29

SDATA30

SDATA31

SDATA32

SDATA33

SDATA34

SDATA35

SDATA36

SDATA37

SDATA38

SDATA39

SDATA40

SDATA41

SDATA42

SDATA43

SDATA44

SDATA45

SDATA46

SDATA47

SDATA48

SDATA49

SDATA50

SDATA51

SDATA52

SDATA53

SDATA54

SDATA55

SDATA56

SDATA57

SDATA58

SDATA59

SDATA60

SDATA61

SDATA62

SDATA63

SDATAINCLK0

SDATAINCLK1

SDATAINCLK2

SDATAINCLK3

SDATAINVAL

SDATAOUTCLK0

SDATAOUTCLK1

SDATAOUTCLK2

SDATAOUTCLK3

SDTATOUTVAL

SADDIN0

SADDIN1

SADDIN2

SADDIN3

SADDIN4

SADDIN5

SADDIN6

SADDIN7

SADDIN8

SADDIN9

SADDIN10

SADDIN11

SADDIN12

SADDIN13

SADDIN14

SADDINCLK

CLKFWDRST

CONNECT

PROCRDY

SFILLVAL

B

A20M

FERR

IGNNE

RESET

STPCLK

PWROK

PICCLK

PICD0/BYPASSCLK

PICD1/BYPASSCLK

COREFB-

COREFB+

CLKIN

CLKIN

RSTCLK

RSTCLK

K7CLKOUT

K7CLKOUT

ANALOG

SYSVREFMODE

VREF_SYS

PLLBYPASS

PLLBYPASSCLK

PLLBYPASSCLK

PLLMON1

PLLMON2

PLLTEST

SCANCLK1

SCANCLK2

SCANINTEVAL

SCANSHIFTEN

DBRDY

DBREQ

FLUSH

TRST

SCHECK0

SCHECK1

SCHECK2

SCHECK3

SCHECK4

SCHECK5

SCHECK6

SCHECK7

SADDOUT0

SADDOUT1

SADDOUT2

SADDOUT3

SADDOUT4

SADDOUT5

SADDOUT6

SADDOUT7

SADDOUT8

SADDOUT9

SADDOUT10

SADDOUT11

SADDOUT12

SADDOUT13

SADDOUT14

SADDOUTCLK

B

C

CPU2A

A20M-

AE1

AG1

AJ3

INIT

AL1

INTR

AJ1

AN3

NMI

AG3

AN5

SMI

AC1

AE3

R62 100

N1

N3

N5

AG13

AG11

AN17

AL17

AN19

AL19

AL21

AN21

AJ13

AA5

W5

AC5

ZN

AE5

ZP

AJ25

AN15

AL15

AN13

AL13

AC3

S1

S5

S3

Q5

P1_CPU_DBRDY

AA1

P1_DBREQ-

AA3

P1_FLUSH-

AL3

Q1

TCK

U1

TDI

P1_CPU_TDO

U5

TDO

Q3

TMS

U3

L1

VID0

L3

VID1

L5

VID2

L7

VID3

J7

VID4

W1

FID0

W3

FID1

Y1

FID2

Y3

FID3

P1_SCHECK-0

U37

P1_SCHECK-1

Y33

P1_SCHECK-2

L35

P1_SCHECK-3

E33

P1_SCHECK-4

E25

P1_SCHECK-5

A31

P1_SCHECK-6

C13

P1_SCHECK-7

A19

J1

J3

P1_AOUT-2

C7

P1_AOUT-3

A7

P1_AOUT-4

E5

P1_AOUT-5

A5

P1_AOUT-6

E7

P1_AOUT-7

C1

P1_AOUT-8

C5

P1_AOUT-9

C3

P1_AOUT-10

G1

P1_AOUT-11

E1

P1_AOUT-12

A3

P1_AOUT-13

G5

P1_AOUT-14

G3

E3

PGA-D462

FERR

CPUINITINTR

IGNNENMI

CPURSTSMISTPCLK-

APICD0APICD1-

P1_COREFBP1_COREFB

CPUCLK1_R

CPUCLK-1_R

P1_CLKOUT

P1_CLKOUT-

P1_VREFMODE

P1_VREF_SYS

P1_ZN

P1_ZP

P1_PLLBP-

P1_PLLMON1

P1_PLLMON2

P1_PLLTEST-

P1_SCANCLK1

P1_SCANCLK2

P1_SINTVAL

P1_SSHIFTEN

P1_CPU_TCK

P1_CPU_TDI

P1_CPU_TMS

P1_CPU_TRST-

P1_VID0

P1_VID1

P1_VID2

P1_VID3

P1_VID4

P1_FID0

P1_FID1

P1_FID2

P1_FID3

A20M- <4,19>

FERR <4>

CPUINIT- <4,19>

INTR <4,19>

IGNNE- <4,19>

NMI <4,19>

SMI- <4,19>

STPCLK- <4,19>

P1_DC_OK <23>

APICCLK

APICD0- <4,34>

APICD1- <4,34>

NOPOP

The farest VCORE and GND

Already stuff on CPU0

P1_VID0 <34>

P1_VID1 <34>

P1_VID2 <34>

P1_VID3 <34>

P1_VID4 <34>

P1_FID0 <34>

P1_FID1 <34>

P1_FID2 <34>

P1_FID3 <34>

**All CPU interface are 2.5V tolerant**

APICCLK <4,34>

P1_COREFB- <35>

P1_COREFB <35>

R97

R103

100

100

NOPOP

VCORE

VCORE

RN33

78

56

34

12

100

P1_SCHECK-[0..7] <9>

P1_AOUT-[2..14] <9>

P1_AOUTCLK- <9>

CPURST- <4,19>

P1_PLLMON1

P1_PLLMON2

P1_FLUSHP1_PLLBP-

P1_AIN-0

P1_AIN-1

P1_DOVAL-

P1_SFILLVAL-

CPUCLK1_R

CPUCLK-1_R

CPUCLK1<3>

VCORE

P1_SSHIFTEN

P1_SINTVAL

P1_SCANCLK2 P1_CPU_TDI

P1_DBREQ- P1_CPU_DBRDY

CPURST-

VCORE

R101 56

R95 56

R89 680

R157 680

R172 270

R173 270

R180 270

R406 270

Reserved

R136 60.4

21

680pC154

R140

301

R143 60.4

21

680pC158

CPUCLK-1<3>

C

D

HDT1

P1_CPU_TCK

1

2

1

2

P1_CPU_TMS

3

4

3

4

P1_SCANCLK1

5

6

5

6

7

8

7

8

P1_CPU_TRST-

9

10

9

10

11

13

15 16

D2x8-BK

NOPOP

P1_CPU_TDO

12

12

14

14

P1_PLLTEST-

11

13

15 16

P1_VREFMODE

VREFMODE=Low=No voltage scaling

VCORE

Near socket-A

D

P1_DBREQ-

P1_PLLTEST-

P1_CPU_TCK

P1_CPU_TMS

P1_CPU_TRSTP1_CPU_TDI

VCORE

for internal VREFSYS

R118

1K

R113

270

P1_SCANCLK1

P1_SSHIFTEN

P1_SINTVAL

P1_SCANCLK2

7 8

5 6

3 4

1 2

Title

Size Document Number Rev

Custom

Date: Sheet

0.5 * VCORE

P1_VREF_SYS

C143

39p

RN30

10K

P1_CLKOUT

P1_CLKOUT-

* Trace lengths of CLKOUT

and -CLKOUT are between

2" and 3"

SocketA (Part 1)

C142

1000p

P1_ZN

P1_ZP

match the transmission line

Push-Pull compensation circuit

MICRO-STAR

MS-6502

E

R75 510

R81 510

RN31

510

VCORE

C141

0.047u

R119 40.2

R120 40.2

RN36

100

639Thursday, March 22, 2001

E

12

34

56

78

VCORE

VCORE

78

56

34

12

VCORE

R112

100

R117

100

of

0A

A

B

C

D

E

* 25 mils Trace/ 12 mils Space

RN32

100

VCC P1_VCCA_PLL1P1_VCCA_PLL

7 8

5 6

3 4

1 2

4 4

3 3

2 2

1 1

C122

39p

2 1

Max 150mA,

Design for

100mA

AD30

AD8

AF10

AF28

AF30

AF32

AF6

AF8

AH30

AH8

AJ9

AK8

AL9

AM8

F30

F8

H10

H28

H30

H32

H6

H8

K30

K8

AJ7

AL7

AN7

G25

G17

G9

N7

Y7

AG7

AG15

AG29

C133

39p

H12

VCC_CORE1

VCC_SRAM1

VCC_SRAM2

VCC_SRAM3

VCC_SRAM4

VCC_SRAM5

VCC_SRAM6

VCC_SRAM7

VCC_SRAM8

VCC_SRAM9

VCC_SRAM11

VCC_SRAM13

VCC_SRAM14

VCC_SRAM16

VCC_SRAM17

VCC_SRAM19

VCC_SRAM20

VCC_SRAM21

VCC_SRAM22

VCC_SRAM23

VCC_SRAM24

VCC_SRAM25

VCC_SRAM26

VCC_SRAM27

VCC_SRAM28

VCC_SRAM29

VCC_SRAM30

VCC_SRAM31

KEY4

KEY6

KEY8

KEY10

KEY12

KEY14

KEY16

KEY18

VSS1

H14

2 1

3 1

VR5

CSK-2-SOT23-150mA

H16

H20

H24M8P30R8T30V8X30Z8AB30

VCC_CORE2

VCC_CORE3

VCC_CORE4

VCC_CORE5

VCC_CORE6

VCC_CORE7

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

H18

H22

H26

M30P8R30T8V30X8Z30

A

R102

0

2

R122

0-REV

VCC_CORE8

VCC_CORE9

VCC_CORE10

VCC_CORE11

VSS8

VSS9

VSS10

VSS11

C134

0.01u

Used when

spec.

change

AF14

AF18

AF22

VCC_CORE12

VCC_CORE13

VCC_CORE14

VCC_CORE15

VSS12

VSS13

VSS14

VSS15

AB8

AF12

AF16

AF20

AF26

AM34

VCC_CORE16

VCC_CORE17

VSS16

VSS17

AF24

AM36

2.5V

R167 10R114 0

C175

39p

2 1

NOPOP

C173

39p

2 1

Place

inside CPU

socket

C144

39p

2 1

NOPOP

VCCA_PLL trace length from the VR1 to the

PGA must be 0.75".

Place al filters close to the PGA.

Keep all power and signal trce away from

the VR1.

Place a cut in the GND plane around the

VCCA_PLL regulator circuit.

AK36

AK34

AK30

AK26

AK22

AK18

AK14

AK10

AL5

AH26

AM30

AH22

AH18

AH14

AH10

AH4

AH2

AF36

AF34

AD6

AM26

VCC_CORE18

VCC_CORE19

VCC_CORE20

VCC_CORE21

VCC_CORE22

VCC_CORE23

VCC_CORE24

VCC_CORE25

VCC_CORE26

VCC_CORE27

VCC_CORE28

VCC_CORE29

VCC_CORE30

VCC_CORE31

VCC_CORE32

VCC_CORE33

VCC_CORE34

VCC_CORE35

VCC_CORE36

VCC_CORE37

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS37

VSS38

AK32

AK28

AK24

AK20

AK16

AK12

AK4

AK2

AH36

AM32

AH34

AH32

AH28

AH24

AH20

AH16

AH12

VSS39

AF4

AF2

AD36

AD34

B

C189

39p

2 1

AD4

AD2

AB36

AB34

VCC_CORE38

VCC_CORE39

VCC_CORE40

VCC_CORE41

VCC_CORE42

VSS40

VSS41

VSS42

VSS43

VSS44

AD32

AB6

AB4

AB2

AB32Z6Z4Z2X36

VCC_CORE43

VCC_CORE44

VCC_CORE45

VSS45

VSS46

VSS47

Z36

Z34

Z32X6AM28X4X2

VCORE

X34

AM22

X32V6V4V2T36

VCC_CORE46

VCC_CORE47

VCC_CORE48

VCC_CORE49

VCC_CORE50

VSS48

VSS49

VSS50

VSS51

VSS52

V36

Power Up Strappings :

AD[3:0] => CPU Clock Multiplier

0000 3

0001 3.5

0010 4

0011 4.5

0100 5

0101 5.5

0110 6

0111 6.5

T34

T32R6R4R2AM18

VCC_CORE51

VCC_CORE52

VCC_CORE53

VCC_CORE54

VCC_CORE55

VCC_CORE56

VCC_CORE57

VCC_CORE58

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

V34

V32T6T4T2R36

R34

AM24

R32P6P4P2M36

P36

P34

P32M4M6M2K36

VCC_CORE59

VCC_CORE60

VCC_CORE61

VCC_CORE62

VSS61

VSS62

VSS63

VSS64

VCC_CORE63

VCC_CORE64

VCC_CORE65

VCC_CORE66

VSS65

VSS66

VSS67

VSS68

M34

M32K6K4K2AM20

C

1000 7

1001 7.5

1010 8

1011 8.5

1100 9

1101 9.5

1110 10

1111 Reserved

K34

K32H4H2

AM14

VCC_CORE67

VCC_CORE68

VCC_CORE69

VCC_CORE70

VCC_CORE71

VSS69

VSS70

VSS71

VSS72

VSS73

H36

H34

F26

F36

F34

F32

F28

VCC_CORE72

VCC_CORE73

VCC_CORE74

VCC_CORE75

VCC_CORE76

VSS74

VSS75

VSS76

VSS77

VSS78

F22

F18

F14

F10F6F4F2AM16

F24

F20

F16

F12

VCC_CORE77

VCC_CORE78

VCC_CORE79

VCC_CORE80

VSS79

VSS80

VSS81

VSS82

D32

D28

AM10

D24

VCC_CORE81

VCC_CORE82

VCC_CORE83

VCC_CORE84

VSS83

VSS84

VSS85

VSS86

D36

D34

D30

D26

D20

D16

D12D8D4D2B36

VCC_CORE85

VCC_CORE86

VCC_CORE87

VCC_CORE88

VSS87

VSS88

VSS89

VSS90

D22

D18

D14

D10D6B34

B32

AM2

VCC_CORE89

VCC_CORE90

VCC_CORE91

VCC_CORE92

VCC_CORE93

VSS91

VSS92

VSS93

VSS94

VSS95

AM12

B30

B26

B28

B24

B20

B16

VCC_CORE94

VCC_CORE95

VCC_CORE96

VSS96

VSS97

VSS98

B22

B18

B14

B10B6B2

B12B8B4

AJ5

VCC_CORE97

VCC_CORE98

VCC_CORE99

VCC_CORE100

VCC_CORE101

VSS99

VSS100

VSS101

VSS102

VSS103

AM4

AK6

D

P1_VCCA_PLL

0~100 mA,

2.25~2.75V

CPU2B

AC7

AJ23

PGA-D462

VCC_Z

VCC_A

AA31

NC1

AC31

NC2

AE31

NC3

AG23

NC6

AG25

NC7

AG31

NC8

AG5

NC9

AJ11

NC10

AJ15

NC11

AJ17

NC12

AJ19

NC13

AJ27

NC15

AL11

NC16

AN11

NC17

AN9

NC18

G11

NC19

G13

NC20

G27

NC21

G29

NC22

G31

NC23

J31

NC24

J5

NC25

L31

NC27

N31

NC28

Q31

NC29

S31

NC30

S7

NC31

U31

NC32

U7

NC33

W31

NC34

W7

NC35

Y31

NC36

Y5

NC37

AG19

NC42

G21

NC43

AG21

NC44

G19

NC45

AN27

BP0_CUT

AL27

BP1_CUT

AN25

BP2_CUT

AL25

BP3_CUT

VSS104

VSS_Z

AM6

AE7

Title

Size Document Number Rev

Custom

Date: Sheet

P1BP0 <34>

P1BP1 <34>

P1BP2 <34>

P1BP3 <34>

MICRO-STAR

SocketA (Part 2)

MS-6502

739Wednesday, March 21, 2001

of

E

0A

5

D D

BELONG TO CLKFWD GROUP[SADDIN] MATCH

W/IN +/-50MILS OF GROUP 5/10,

CLK:5/20

BELONG TO CLKFWD GROUP[SADDOUT] MATCH

C C

W/IN +/-50MILS OF GROUP 5/10,

CLK:5/20

BELONG TO CLKFWD GROUP;MATCHED TO

INDIVIDUAL CLKFWD GROUP

RESPECTIVELY.[SDATA0], [SDATA1],

[SDATA2],[SDATA3] W/IN+/-50MILS OF

GROUP

B B

P0_AIN-[2..14]<4>

--------------------------------

P0_AOUT-[2..14]<4>

--------------------------------

P0_SCHECK-[0..7]<4>

----------------------

P0_DICLK-[0..3]<4>

P0_DOCLK-[0..3]<4>

4

AH20

AC5

AC4

AC6

AA2

AA6

AA4

AA3

AA5

AB3

AB5

AD1

AC3

AC1

AA7

AB1

Y4

Y5

Y6

G1

H2

G3

F4

H4

E1

F3

F2

F5

G5

F1

E2

D1

E3

V7

V8

P8

T1

N7

N1

J3

K3

U5

R1

M1

H3

W5

R8

N5

H1

J8

AMD-AMD762

U23A

P0_CLKFWDRST

P0_CONNECT

P0_PROCRDY

SYSCLK

P0_SADDIN2#

P0_SADDIN3#

P0_SADDIN4#

P0_SADDIN5#

P0_SADDIN6#

P0_SADDIN7#

P0_SADDIN8#

P0_SADDIN9#

P0_SADDIN10#

P0_SADDIN11#

P0_SADDIN12#

P0_SADDIN13#

P0_SADDIN14#

P0_SADDINCLK#

P0_SADDOUT2#

P0_SADDOUT3#

P0_SADDOUT4#

P0_SADDOUT5#

P0_SADDOUT6#

P0_SADDOUT7#

P0_SADDOUT8#

P0_SADDOUT9#

P0_SADDOUT10#

P0_SADDOUT11#

P0_SADDOUT12#

P0_SADDOUT13#

P0_SADDOUT14#

P0_SADDOUTCLK#

P0_SCHECK0#

P0_SCHECK1#

P0_SCHECK2#

P0_SCHECK3#

P0_SCHECK4#

P0_SCHECK5#

P0_SCHECK6#

P0_SCHECK7#

P0_SDATAINCLK0#

P0_SDATAINCLK1#

P0_SDATAINCLK2#

P0_SDATAINCLK3#

P0_SDATAINVALID#

P0_SDATAOUTCLK0#

P0_SDATAOUTCLK1#

P0_SDATAOUTCLK2#

P0_SDATAOUTCLK3#

P0_SYSFILLVALID#

P0_CFWDRST<4>

P0_CONNECT<4>

P0_PROCRDY<4>

CPUCLK2<3>

P0_AINCLK-<4>

P0_AOUTCLK-<4>

P0_SFILLVAL-<4>

P0_CFWDRST

P0_CONNECT

P0_PROCRDY

CPUCLK2

P0_AIN-2

P0_AIN-3

P0_AIN-4

P0_AIN-5

P0_AIN-6

P0_AIN-7

P0_AIN-8

P0_AIN-9

P0_AIN-10

P0_AIN-11

P0_AIN-12

P0_AIN-13

P0_AIN-14

P0_AINCLK-

P0_AOUT-2

P0_AOUT-3

P0_AOUT-4

P0_AOUT-5

P0_AOUT-6

P0_AOUT-7

P0_AOUT-8

P0_AOUT-9

P0_AOUT-10

P0_AOUT-11

P0_AOUT-12

P0_AOUT-13

P0_AOUT-14

P0_AOUTCLK-

P0_SCHECK-0

P0_SCHECK-1

P0_SCHECK-2

P0_SCHECK-3

P0_SCHECK-4

P0_SCHECK-5

P0_SCHECK-6

P0_SCHECK-7

P0_DICLK-0

P0_DICLK-1

P0_DICLK-2

P0_DICLK-3

P0_DIVAL-<4>

P0_DIVAL-

P0_DOCLK-0

P0_DOCLK-1

P0_DOCLK-2

P0_DOCLK-3

3

AMD-762

System Bus 0

P0_SDATA0#

P0_SDATA1#

P0_SDATA2#

P0_SDATA3#

P0_SDATA4#

P0_SDATA5#

P0_SDATA6#

P0_SDATA7#

P0_SDATA8#

P0_SDATA9#

P0_SDATA10#

P0_SDATA11#

P0_SDATA12#

P0_SDATA13#

P0_SDATA14#

P0_SDATA15#

P0_SDATA16#

P0_SDATA17#

P0_SDATA18#

P0_SDATA19#

P0_SDATA20#

P0_SDATA21#

P0_SDATA22#

P0_SDATA23#

P0_SDATA24#

P0_SDATA25#

P0_SDATA26#

P0_SDATA27#

P0_SDATA28#

P0_SDATA29#

P0_SDATA30#

P0_SDATA31#

P0_SDATA32#

P0_SDATA33#

P0_SDATA34#

P0_SDATA35#

P0_SDATA36#

P0_SDATA37#

P0_SDATA38#

P0_SDATA39#

P0_SDATA40#

P0_SDATA41#

P0_SDATA42#

P0_SDATA43#

P0_SDATA44#

P0_SDATA45#

P0_SDATA46#

P0_SDATA47#

P0_SDATA48#

P0_SDATA49#

P0_SDATA50#

P0_SDATA51#

P0_SDATA52#

P0_SDATA53#

P0_SDATA54#

P0_SDATA55#

P0_SDATA56#

P0_SDATA57#

P0_SDATA58#

P0_SDATA59#

P0_SDATA60#

P0_SDATA61#

P0_SDATA62#

P0_SDATA63#

P0_VREF

W3

V4

V3

V5

V6

U4

U3

U8

Y1

Y3

AA1

Y7

W1

W7

Y2

U6

U7

R7

R6

R5

R3

R4

R2

U2

T7

V1

T5

V2

T3

U1

P6

P1

P2

P4

M8

M6

L3

L7

M4

L6

P7

P5

N3

P3

M5

M7

L5

M3

K7

J6

J7

K5

J4

J2

H6

H5

M2

L4

L2

L1

K1

H7

J5

J1

AC2

P0_SDATA-0

P0_SDATA-1

P0_SDATA-2

P0_SDATA-3

P0_SDATA-4

P0_SDATA-5

P0_SDATA-6

P0_SDATA-7

P0_SDATA-8

P0_SDATA-9

P0_SDATA-10

P0_SDATA-11

P0_SDATA-12

P0_SDATA-13

P0_SDATA-14

P0_SDATA-15

P0_SDATA-16

P0_SDATA-17

P0_SDATA-18

P0_SDATA-19

P0_SDATA-20

P0_SDATA-21

P0_SDATA-22

P0_SDATA-23

P0_SDATA-24

P0_SDATA-25

P0_SDATA-26

P0_SDATA-27

P0_SDATA-28

P0_SDATA-29

P0_SDATA-30

P0_SDATA-31

P0_SDATA-32

P0_SDATA-33

P0_SDATA-34

P0_SDATA-35

P0_SDATA-36

P0_SDATA-37

P0_SDATA-38

P0_SDATA-39

P0_SDATA-40

P0_SDATA-41

P0_SDATA-42

P0_SDATA-43

P0_SDATA-44

P0_SDATA-45

P0_SDATA-46

P0_SDATA-47

P0_SDATA-48

P0_SDATA-49

P0_SDATA-50

P0_SDATA-51

P0_SDATA-52

P0_SDATA-53

P0_SDATA-54

P0_SDATA-55

P0_SDATA-56

P0_SDATA-57

P0_SDATA-58

P0_SDATA-59

P0_SDATA-60

P0_SDATA-61

P0_SDATA-62

P0_SDATA-63

P0_S2K_VREF

2

P0_SDATA-[0..63] <4>

+12V

JFAN1

2

1

D1x2-WH

1

VCC2_5

R408

100

CPUCLK2

R410

150

Put these two res. very

close to N.B.

U3_X

_

Set S2K_VREF to 50% of VCORE

P0_S2K_VREF

C265

C270

0.047u

0.039u

VCORE

R248

100

R251

100

A A

Title

{Title}

Size Document Number Rev

MS-6502 0A

B

5

4

3

2

Date: Sheet

839Wednesday, March 21, 2001

of

1

5

D D

BELONG TO CLKFWD GROUP[SADDIN] MATCH

W/IN +/-50MILS OF GROUP 5/10,

CLK:5/20

BELONG TO CLKFWD GROUP[SADDOUT] MATCH

C C

W/IN +/-50MILS OF GROUP 5/10,

CLK:5/20

BELONG TO CLKFWD GROUP;MATCHED TO

INDIVIDUAL CLKFWD GROUP

RESPECTIVELY.[SDATA0], [SDATA1],

[SDATA2],[SDATA3] W/IN+/-50MILS OF

GROUP

B B

P1_AIN-[2..14]<6>

--------------------------------

P1_AOUT-[2..14]<6>

--------------------------------

P1_SCHECK-[0..7]<6>

----------------------

P1_DICLK-[0..3]<6>

P1_DOCLK-[0..3]<6>

4

AE19

AG17

AH18

AF17

AG16

AG18

AD17

AK18

AK17

AG19

AE18

AF18

AG14

AH12

AE15

AD12

AE17

AH15

AH11

AL19

AJ19

AL18

AL17

AJ18

AK3

AE3

AG3

AF3

AD7

AF2

AD5

AD6

AF1

AH1

AG2

AG1

AL15

AJ10

AL9

AG8

AF6

AL7

AK5

AG9

AL20

AJ2

AJ3

AJ8

AJ4

AMD-AMD762

U23B

P1_CLKFWDRST

P1_CONNECT

P1_PROCRDY

P1_SADDIN2#

P1_SADDIN3#

P1_SADDIN4#

P1_SADDIN5#

P1_SADDIN6#

P1_SADDIN7#

P1_SADDIN8#

P1_SADDIN9#

P1_SADDIN10#

P1_SADDIN11#

P1_SADDIN12#

P1_SADDIN13#

P1_SADDIN14#

P1_SADDINCLK#

P1_SADDOUT2#

P1_SADDOUT3#

P1_SADDOUT4#

P1_SADDOUT5#

P1_SADDOUT6#

P1_SADDOUT7#

P1_SADDOUT8#

P1_SADDOUT9#

P1_SADDOUT10#

P1_SADDOUT11#

P1_SADDOUT12#

P1_SADDOUT13#

P1_SADDOUT14#

P1_SADDOUTCLK#

P1_SCHECK0#

P1_SCHECK1#

P1_SCHECK2#

P1_SCHECK3#

P1_SCHECK4#

P1_SCHECK5#

P1_SCHECK6#

P1_SCHECK7#

P1_SDATAINCLK0#

P1_SDATAINCLK1#

P1_SDATAINCLK2#

P1_SDATAINCLK3#

P1_SDATAINVALID#

P1_SDATAOUTCLK0#

P1_SDATAOUTCLK1#

P1_SDATAOUTCLK2#

P1_SDATAOUTCLK3#

P1_SYSFILLVALID#

P1_CFWDRST<6>

P1_CONNECT<6>

P1_PROCRDY<6>

P1_AINCLK-<6>

P1_AOUTCLK-<6>

P1_SFILLVAL-<6>

P1_CFWDRST

P1_CONNECT

P1_PROCRDY

P1_AIN-2

P1_AIN-3

P1_AIN-4

P1_AIN-5

P1_AIN-6

P1_AIN-7

P1_AIN-8

P1_AIN-9

P1_AIN-10

P1_AIN-11

P1_AIN-12

P1_AIN-13

P1_AIN-14

P1_AINCLK-

P1_AOUT-2

P1_AOUT-3

P1_AOUT-4

P1_AOUT-5

P1_AOUT-6

P1_AOUT-7

P1_AOUT-8

P1_AOUT-9

P1_AOUT-10

P1_AOUT-11

P1_AOUT-12

P1_AOUT-13

P1_AOUT-14

P1_AOUTCLK-

P1_SCHECK-0

P1_SCHECK-1

P1_SCHECK-2

P1_SCHECK-3

P1_SCHECK-4

P1_SCHECK-5

P1_SCHECK-6

P1_SCHECK-7

P1_DICLK-0

P1_DICLK-1

P1_DICLK-2

P1_DICLK-3

P1_DIVAL-<6>

P1_DIVAL-

P1_DOCLK-0

P1_DOCLK-1

P1_DOCLK-2

P1_DOCLK-3

P1_SFILLVAL-

3

AMD-762

System Bus 1

P1_SDATA0#

P1_SDATA1#

P1_SDATA2#

P1_SDATA3#

P1_SDATA4#

P1_SDATA5#

P1_SDATA6#

P1_SDATA7#

P1_SDATA8#

P1_SDATA9#

P1_SDATA10#

P1_SDATA11#

P1_SDATA12#

P1_SDATA13#

P1_SDATA14#

P1_SDATA15#

P1_SDATA16#

P1_SDATA17#

P1_SDATA18#

P1_SDATA19#

P1_SDATA20#

P1_SDATA21#

P1_SDATA22#

P1_SDATA23#

P1_SDATA24#

P1_SDATA25#

P1_SDATA26#

P1_SDATA27#

P1_SDATA28#

P1_SDATA29#

P1_SDATA30#

P1_SDATA31#

P1_SDATA32#

P1_SDATA33#

P1_SDATA34#

P1_SDATA35#

P1_SDATA36#

P1_SDATA37#

P1_SDATA38#

P1_SDATA39#

P1_SDATA40#

P1_SDATA41#

P1_SDATA42#

P1_SDATA43#

P1_SDATA44#

P1_SDATA45#

P1_SDATA46#

P1_SDATA47#

P1_SDATA48#

P1_SDATA49#

P1_SDATA50#

P1_SDATA51#

P1_SDATA52#

P1_SDATA53#

P1_SDATA54#

P1_SDATA55#

P1_SDATA56#

P1_SDATA57#

P1_SDATA58#

P1_SDATA59#

P1_SDATA60#

P1_SDATA61#

P1_SDATA62#

P1_SDATA63#

P1_VREF

AE14

AJ14

AE16

AD14

AJ15

AL14

AK15

AE13

AL16

AD15

AG15

AF15

AJ16

AH17

AJ17

AH14

AF14

AF12

AE12

AK12

AJ11

AE11

AG11

AF11

AK14

AL13

AL12

AG13

AJ13

AG12

AJ12

AL11

AG7

AF9

AK11

AL10

AK8

AL8

AH8

AK9

AE10

AE9

AD11

AG10

AJ9

AH9

AF8

AJ7

AF4

AG5

AF5

AK6

AH4

AJ5

AL4

AH3

AE8

AE7

AG6

AL6

AJ6

AE5

AH6

AL5

AB7

P1_SDATA-0

P1_SDATA-1

P1_SDATA-2

P1_SDATA-3

P1_SDATA-4

P1_SDATA-5

P1_SDATA-6

P1_SDATA-7

P1_SDATA-8

P1_SDATA-9

P1_SDATA-10

P1_SDATA-11

P1_SDATA-12

P1_SDATA-13

P1_SDATA-14

P1_SDATA-15

P1_SDATA-16

P1_SDATA-17

P1_SDATA-18

P1_SDATA-19

P1_SDATA-20

P1_SDATA-21

P1_SDATA-22

P1_SDATA-23

P1_SDATA-24

P1_SDATA-25

P1_SDATA-26

P1_SDATA-27

P1_SDATA-28

P1_SDATA-29

P1_SDATA-30

P1_SDATA-31

P1_SDATA-32

P1_SDATA-33

P1_SDATA-34

P1_SDATA-35

P1_SDATA-36

P1_SDATA-37

P1_SDATA-38

P1_SDATA-39

P1_SDATA-40

P1_SDATA-41

P1_SDATA-42

P1_SDATA-43

P1_SDATA-44

P1_SDATA-45

P1_SDATA-46

P1_SDATA-47

P1_SDATA-48

P1_SDATA-49

P1_SDATA-50

P1_SDATA-51

P1_SDATA-52

P1_SDATA-53

P1_SDATA-54

P1_SDATA-55

P1_SDATA-56

P1_SDATA-57

P1_SDATA-58

P1_SDATA-59

P1_SDATA-60

P1_SDATA-61

P1_SDATA-62

P1_SDATA-63

P1_S2K_VREF

2

P1_SDATA-[0..63] <6>

1

Set S2K_VREF to 50% of VCORE

P1_S2K_VREF

C261

0.047u

C250

0.039u

VCORE

R242

100

R244

100

A A

Title

{Title}

Size Document Number Rev

MS-6502 0A

B

5

4

3

2

Date: Sheet

939Wednesday, March 21, 2001

of

1

5

D D

C C

B B

CLKOUT[0..5]<36>

CLKOUT-[0..5]<36>

A A

DDR_REF

5

C530

0.1u

C532

0.1u

(near the chip)

DDR_VREF

VCC2_5

CLKOUT0

CLKOUT1

CLKOUT2

CLKOUT3

CLKOUT4

CLKOUT5

CLKOUT-0

CLKOUT-1

CLKOUT-2

CLKOUT-3

CLKOUT-4

CLKOUT-5

4

U23E

MAA0

F17

MAA0

MAA1

G15

MAA1

MAA2

E15

MAA2

MAA3

G14

MAA3

MAA4

F14

MAA4

MAA5

E11

MAA5

MAA6

G12

MAA6

MAA7

G9

MAA7

MAA8

G11

MAA8

MAA9

G10

MAA9

MAA10

F18

MAA10

MAA11

H11

MAA11

MAA12

F9

MAA12

MAA13

G19

MAA13

MAA14

MAA[0..14]<36>

MAB[0..14]<36>

DM[0..8]<36>

CS-[0..7]<36>

RASA-<36>

RASB-<36>

CASA-<36>

CASB-<36>

WEA-<36>

WEB-<36>

CKEA<36>

CKEB<36>

4

G18

MAA14

MAB0

H17

MAB0

MAB1

H15

MAB1

MAB2

F15

MAB2

MAB3

H14

MAB3

MAB4

E14

MAB4

MAB5

E12

MAB5

MAB6

G13

MAB6

MAB7

H12

MAB7

MAB8

F12

MAB8

MAB9

F11

MAB9

MAB10

H18

MAB10

MAB11

H9

MAB11

MAB12

E9

MAB12

MAB13

E20

MAB13

MAB14

E18

MAB14

DM0

B5

DM0

DM1

D8

DM1

DM2

A11

DM2

DM3

D14

DM3

DM4

E19

DM4

DM5

A22

DM5

DM6

D24

DM6

DM7

A28

DM7

DM8

C17

DM8

CS-0

H21

CS0#

CS-1

E23

CS1#

CS-2

F21

CS2#

CS-3

F23

CS3#

CS-4

H23

CS4#

CS-5

G23

CS5#

CS-6

G24

CS6#

CS-7

F24

CS7#

RASA-

G20

RASA#

RASB-

F20

RASB#

CASA-

G22

CASA#

CASB-

G21

CASB#

WEA- MDAT57

E21

WEA#

WEB-

H20

WEB#

CKEA

G8

CKEA

CKEB

F8

CLKOUT0

CLKOUT-0

CLKOUT1

CLKOUT-1

CLKOUT2

CLKOUT-2

CLKOUT3

CLKOUT-3

CLKOUT4

CLKOUT-4

CLKOUT5

CLKOUT-5

DDR_REF

CKEB

G16

CLKOUT0

G17

CLKOUT#0

E6

CLKOUT1

F6

CLKOUT#1

E24

CLKOUT2

E25

CLKOUT#2

E16

CLKOUT3

E17

CLKOUT#3

E7

CLKOUT4

E8

CLKOUT#4

E26

CLKOUT5

F26

CLKOUT#5

D4

DDR_REF

MECC[0..7]<36>

3

AMD-762

DDR Interface

PDL_OUTPUT_TEST

MECC0

MECC1

MECC2

MECC3

MECC4

C15

A16

A17

D17

C14

MECC0

MECC1

MECC4

MECC2

MECC3

3

MECC5

D15

B17

MECC6

MECC5

MECC6

MECC7

A18

MECC7

MDAT0

MDAT1

MDAT2

MDAT3

MDAT4

MDAT5

MDAT6

MDAT7

MDAT8

MDAT9

MDAT10

MDAT11

MDAT12

MDAT13

MDAT14

MDAT15

MDAT16

MDAT17

MDAT18

MDAT19

MDAT20

MDAT21

MDAT22

MDAT23

MDAT24

MDAT25

MDAT26

MDAT27

MDAT28

MDAT29

MDAT30

MDAT31

MDAT32

MDAT33

MDAT34

MDAT35

MDAT36

MDAT37

MDAT38

MDAT39

MDAT40

MDAT41

MDAT42

MDAT43

MDAT44

MDAT45

MDAT46

MDAT47

MDAT48

MDAT49

MDAT50

MDAT51

MDAT52

MDAT53

MDAT54

MDAT55

MDAT56

MDAT57

MDAT58

MDAT59

MDAT60

MDAT61

MDAT62

MDAT63

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

AMD-AMD762

2

VCC2_5

C542 0.1u

MDAT0

C4

MDAT1

A4

MDAT2

B6

MDAT3

D6

MDAT4

C3

MDAT5

B3

MDAT6

C5

MDAT7

A6

MDAT8

C6

MDAT9

C7

MDAT10

A9

MDAT11

D9

MDAT12

A7

MDAT13

B8

MDAT14

C8

MDAT15

B9

MDAT16

E10

MDAT17

A10

MDAT18

D11

MDAT19

B12

MDAT20

C9

MDAT21

B11

MDAT22

C11

MDAT23

D12

MDAT24

A12

MDAT25

E13

MDAT26

A14

MDAT27

B15

MDAT28

C12

MDAT29

A13

MDAT30

B14

MDAT31

A15

MDAT32

B18

MDAT33

A19

MDAT34

A20

MDAT35

D20

MDAT36

C18

MDAT37

D18

MDAT38

B20

MDAT39

C20

MDAT40

B21

MDAT41

D21

MDAT42

E22

MDAT43

B23

MDAT44

A21

MDAT45

C21

MDAT46

A23

MDAT47

C23

MDAT48

D23

MDAT49

B24

MDAT50

B26

MDAT51

C26

MDAT52

A24

MDAT53

C24

MDAT54

A25

MDAT55

A26

MDAT56

C27

B27

MDAT58

C29

MDAT59

C30

MDAT60

A27

MDAT61

D26

MDAT62

D28

MDAT63

B29

DQS0

A5

DQS1

A8

DQS2

C10

DQS3

C13

DQS4

C19

DQS5

C22

DQS6

C25

DQS7

C28

DQS8

C16

TP3

D3

Place near IGD4 for VCC2_5 decoupling

MDAT[0..63] <36>

DQS[0..8] <36>

2

C541 0.1u

C540 0.1u

C361 0.1u

C357 0.1u

C539 0.1u

C360 0.1u

VCC2_5

C528 100p

C513 100p

C519 0.1u

C524 0.1u

C511 100p

C518 1000p

C525 1000p

C527 0.1u

Place under IGD4 (NOPOP)

Title

Size Document Number Rev

Custom

Date: Sheet of

North Bridge AMD762-DDR

1

MICRO-STAR

MS-6502

1

10 39Wednesday, March 21, 2001

0F

5

4

3

2

1

AMD-762

PCI Bus

AA28

AA31

AA30

AA27

AF21

W29

W31

W27

W25

P27

R29

P30

T25

P31

U24

R26

U25

T29

R31

V24

T27

R30

T31

U26

U27

V27

V26

Y28

Y29

Y25

Y31

Y30

Y27

Y26

R27

V25

Y24

V28

V31

H28

V29

U31

U29

U30

V30

J24

J25

E30

F30

H25

H27

F29

G27

E29

D31

E31

G29

H26

F28

F27

D29

U23C

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

CBE0#

CBE1#

CBE2#

CBE3#

DEVSEL#

FRAME#

WSC#

IRDY#

PAR

SERR#

STOP#

TRDY#

SBREQ#

SBGNT#

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

REQ5#

REQ6#

GNT0#

GNT1#

GNT2#

GNT3#

GNT4#

GNT5#

GNT6#

RESET#

AMD-AMD762

AD32

AD33

AD34

AD35

AD36

AD37

AD38

AD39

AD40

AD41

AD42

AD43

AD44

AD45

AD46

AD47

AD48

AD49

AD50

AD51

AD52

AD53

AD54

AD55

AD56

AD57

AD58

AD59

AD60

AD61

AD62

AD63

CBE4

CBE5

CBE6

CBE7

PAR64

ACK64#

REQ64#

M66

VDD_PCI0

VDD_PCI1

VDD_PCI2

VDD_PCI3

VDD_PCI4

VDD_PCI5

VDD_PCI6

VDD_PCI7

VDD_PCI8

VDD_PCI9

VDD_PCI10

VDD_PCI20

VDD_PCI21

VDD_PCI22

VDD_PCI23

VDD_PCI24

PCI66_CLK0

PCI66_CLK1

PCI66_CLK2

PCICLK

4

K25

G31

L24

H30

J26

H31

J28

J30

J29

J31

L25

J27

M24

K27

K29

L26

L28

L27

L29

K31

M28

L30

M25

L31

P24

M26

M29

M27

N25

N27

R24

R25

M31

N29

N31

M30

R28

P26

U28

D30

G30

K26

K30

N26

N30

T26

T30

W26

W30

G26

L23

N23

R23

U23

W23

P25

P28

P29

AH21

C_BE-4

C_BE-5

C_BE-6

C_BE-7

PAR64

ACK64REQ64-

VCC3

AD33

AD34

AD35

AD36

AD37

AD38

AD39

AD40

AD41

AD42

AD43

AD44

AD45

AD46

AD47

AD48

AD49

AD50

AD51

AD52

AD53

AD54

AD55

AD56

AD57

AD58

AD59

AD60

AD61

AD62

AD63

M66EN-

PAR64 <16>

ACK64- <16>

REQ64- <16>WSC-<19>

R273 4.7K

R275

4.7K

NBCLK <3>

NOPOP

AD32

F31

AD[32..63] <16>

C_BE-[4..7] <16>

VCC3

AMD DOC SCH

AGP_CAL- 34.8 56.2

AGP_CAL 39.2 56.2

R252 R0603MS

AGP_CAL-

R268 38.4

AGP_CAL

AGP_VREF2X

C259

0.01u

(near the chip)

3

D D

C C

B B

A A

AD[0..31]8,19,29,31,34,37>

VCC3

R287

4.7K

C_BE-[0..3]

C_BE-[0..3]<16,17,18,19,29,31,37>

5

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

C_BE-0

C_BE-1

C_BE-2

C_BE-3

DEVSEL-<16,17,18,19,29,31>

FRAME-<16,17,18,19,29,31>

PCIRST-2<13,21,29,31,34>

WSC-

IRDY-<16,17,18,19,29,31>

PAR<16,17,18,19,29,31,37>

SERR-<16,17,18,19,31>

STOP-<16,17,18,19,29,31>

TRDY-<16,17,18,19,29,31>

SBREQ-<19,20>

SBGNT-<19,20>

REQ0-<18,31>

REQ1-<16,18>

REQ2-<16,18>

REQ3-<17,18>

REQ4-<17,18>

REQ5-<18>

REQ6-<18,29>

GNT0-<31>

GNT1-<16>

GNT2-<16>

GNT3-<17>

GNT4-<17>

GNT5-<18>

GNT6-<29>

GAD[0..31]<15>

GCLK0<3>

VDDQ

R249 150

R245

100

GAD[0..31]

VDDQ

R237

100

Reserved

C239

100p

Reserved

GAD0

GAD1

GAD2

GAD3

GAD4

GAD5

GAD6

GAD7

GAD8

GAD9

GAD10

GAD11

GAD12

GAD13

GAD14

GAD15

GAD16

GAD17

GAD18

GAD19

GAD20

GAD21

GAD22

GAD23

GAD24

GAD25

GAD26

GAD27

GAD28

GAD29

GAD30

GAD31

VDDQ

AB31

AA26

AC31

AA25

AC30

AB29

AD31

AC26

AC27

AG31

AC29

AH31

AB25

AD29

AC28

AE29

AD26

AH28

AJ30

AG29

AK29

AF27

AH29

AG27

AL28

AJ26

AD25

AF24

AG26

AG24

AF23

AE25

AJ21

AA23

AB26

AB30

AC23

AF22

AE26

AE30

AH30

AK22

AK25

AK28

AF25

Y22

AB22

AC21

AB20

2

AMD-762

AGP Bus

U23D

GAD0

GAD1

GAD2

GAD3

GAD4

GAD5

GAD6

GAD7

GAD8

GAD9

GAD10

GAD11

GAD12

GAD13

GAD14

GAD15

GAD16

GAD17

GAD18

GAD19

GAD20

GAD21

GAD22

GAD23

GAD24

GAD25

GAD26

GAD27

GAD28

GAD29

GAD30

GAD31

AGPCLK

VDD_AGP0

VDD_AGP1

VDD_AGP2

VDD_AGP3

VDD_AGP4

VDD_AGP5

VDD_AGP6

VDD_AGP7

VDD_AGP8

VDD_AGP9

VDD_AGP10

VDD_AGP11

VDD_AGP12

VDD_AGP13

VDD_AGP14

VDD_AGP15

AMD-AMD762

Title

{Title}

Size Document Number Rev

MS-6502 0A

B

Date: Sheet

GCBE0#

GCBE1#

GCBE2#

GCBE3#

GDEVSEL#

GFRAME#

GSERR#

GSTOP#

GTRDY#

GIRDY#

GPAR

WBF#

PIPE#

RBF#

GGNT#

GREQ#

ADSTB0

ADSTB0#

ADSTB1

ADSTB1#

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

SBSTB

SBSTB#

AGP_VREF4X

AGP_VREF

AGP_CAL

AGP_CAL#VDD_AGP15

AGP_VREF4X_IN

C262

0.01u

ST0

ST1

ST2

C257

1u

AB27

AD28

AJ29

AF26

AC24

AF29

AE27

AK27

AF30

AF28

AD27

AK26

AL25

AL26

AL23

AK23

AK24

AL24

AJ23

AE31

AD30

AJ27

AJ28

AG23

AE23

AJ25

AD23

AE24

AG25

AL27

AH26

AJ24

AH24

AC25

AG30

AA24

AF31AA21

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

SBSTB

SBSTB-

AGP_VREF4X_IN

AGP_VREF2X

AGP_CAL

AGP_CAL-

AGP_VREF4X_IN <15>

C254

0.1u

1

GCBE0- <15>

GCBE1- <15>

GCBE2- <15>

GCBE3- <15>

GDEVSEL- <15>

GFRAME- <15>

GSERR- <15>

GSTOP- <15>

GTRDY- <15>

GIRDY- <15>

GPAR <15>

WBF- <15>

PIPE- <15>

RBF- <15>

GGNT- <15>

GREQ- <15>

ST0 <15>

ST1 <15>

ST2 <15>

ADSTB0 <15>

ADSTB0- <15>

ADSTB1 <15>

ADSTB1- <15>

SBA[0..7]

SBSTB <15>

SBSTB- <15>

11 39Wednesday, March 21, 2001

of

SBA[0..7] <15>

5

D D

C C

B B

VCC2_5

A A

Power for clock PLL.

MUST close to

AMD-762

0_1206

FB21

100p

C492

4.7u-0805

C495

5

C491

4.7u-0805

4

AMD-762

U23F

AA11 D2

VDD_CORE P0_K7_VCORE0

AA13

VDD_CORE

AA15

VDD_CORE

AA17

VDD_CORE

AA19

VDD_CORE

B10

VDD_CORE

B13

VDD_CORE

B16

VDD_CORE

B19

VDD_CORE

B22

VDD_CORE

B25

VDD_CORE

B28

VDD_CORE

B4

VDD_CORE

B7

VDD_CORE

F10

VDD_CORE

F13

VDD_CORE

F16

VDD_CORE

F19

VDD_CORE

F22

VDD_CORE

F25

VDD_CORE

J11

VDD_CORE

J13

VDD_CORE

J15

VDD_CORE

J17

VDD_CORE

J19

VDD_CORE

J21

VDD_CORE

J23

VDD_CORE

J9

VDD_CORE

K10

VDD_CORE

K12

VDD_CORE

K14

VDD_CORE

K16

VDD_CORE

K18

VDD_CORE

K20

VDD_CORE

K22

VDD_CORE

L11

VDD_CORE

L13

VDD_CORE

L15

VDD_CORE

L17

VDD_CORE

L19

VDD_CORE

L21

VDD_CORE

M12

VDD_CORE

M14

VDD_CORE

M16

VDD_CORE

M18

VDD_CORE

M20

VDD_CORE

M22

VDD_CORE

N11

VDD_CORE

N13

VDD_CORE

N15

VDD_CORE

N17

VDD_CORE

N19

VDD_CORE

N21

VDD_CORE

P12

VDD_CORE

P14

VDD_CORE

P16

VDD_CORE

P18

VDD_CORE

P20

VDD_CORE

P22

VDD_CORE

R11

VDD_CORE

R13

VDD_CORE

R15

VDD_CORE

R17

VDD_CORE

R19

VDD_CORE

R21

VDD_CORE

T12

VDD_CORE

T14

VDD_CORE

T16

VDD_CORE

T18

VDD_CORE

T20

VDD_CORE

T22

VDD_CORE

U11

VDD_CORE

U13

VDD_CORE

U15

VDD_CORE

U17

VDD_CORE

U19

VDD_CORE

U21

VDD_CORE

V12

VDD_CORE

V14

VDD_CORE

V16

VDD_CORE

V18

VDD_CORE

V20

VDD_CORE

V22

VDD_CORE

W11

VDD_CORE

W13

VDD_CORE

W15

VDD_CORE

W17

VDD_CORE

W19

VDD_CORE

W21

VDD_CORE

Y12

VDD_CORE

Y14

VDD_CORE

Y16

VDD_CORE

Y18

VDD_CORE

Y20

VDD_CORE

F7

VDD_CORE

AG22

AVDD

TP2

AE1

SI_VDD

TP1

AD2

SI_VSS

4

POWER

P0_K7_VCORE10

P0_K7_VCORE11

P0_K7_VCORE12

P0_K7_VCORE13

P0_K7_VCORE14

P0_K7_VCORE15

P0_K7_VCORE16

P0_K7_VCORE17

P0_K7_VCORE18

P0_K7_VCORE19

P0_K7_VCORE20

P0_K7_VCORE21

P0_K7_VCORE22

P0_K7_VCORE23

P1_K7_VCORE10

P1_K7_VCORE11

P1_K7_VCORE12

P1_K7_VCORE13

P1_K7_VCORE14

P1_K7_VCORE15

P1_K7_VCORE16

P1_K7_VCORE17

P1_K7_VCORE18

P1_K7_VCORE19

P1_K7_VCORE20

P1_K7_VCORE21

P1_K7_VCORE22

P1_K7_VCORE23

P1_K7_VCORE24

P0_K7_VCORE1

P0_K7_VCORE2

P0_K7_VCORE3

P0_K7_VCORE4