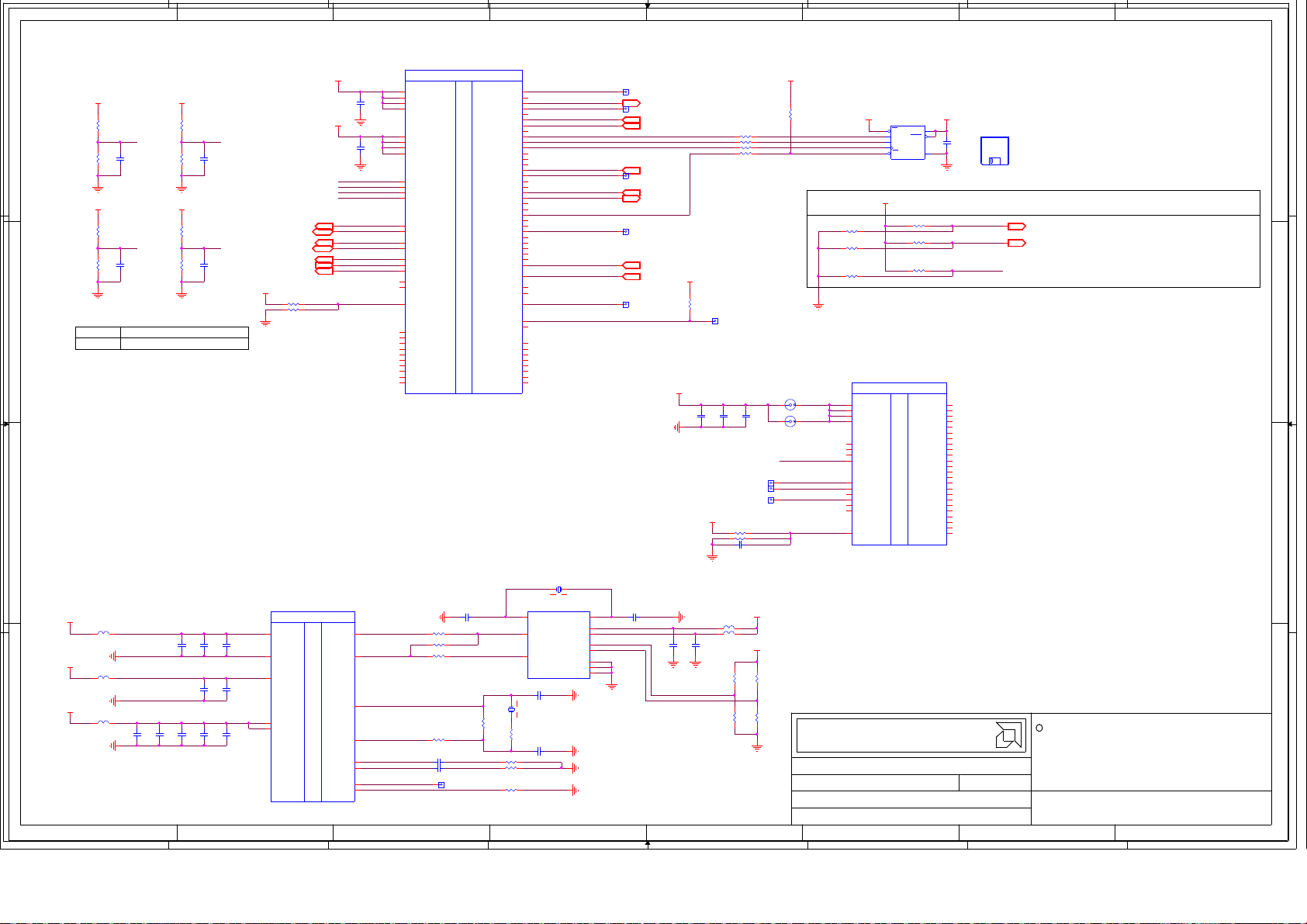

MSI MS-327 Schematics

1

8

8

8

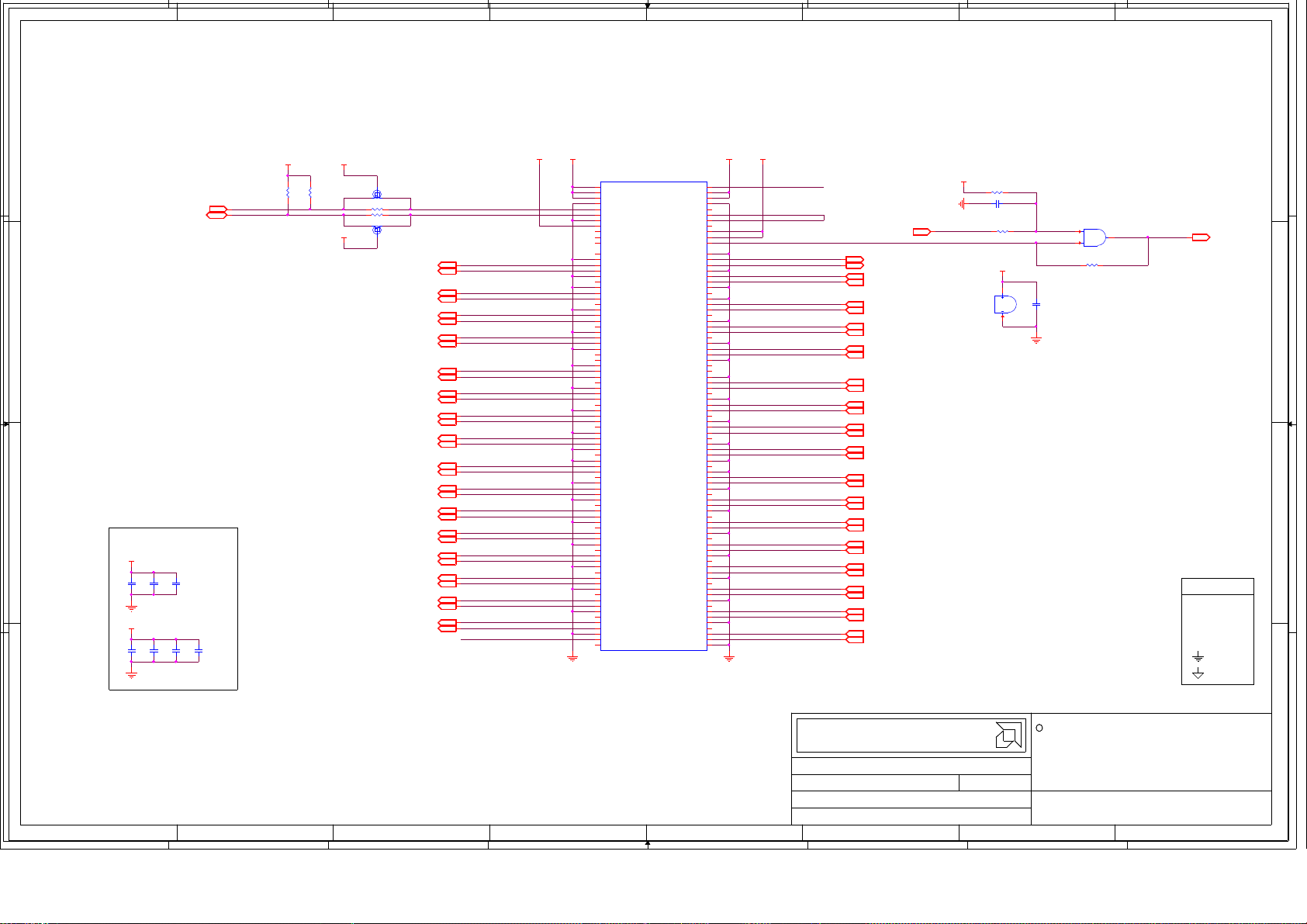

(1) PCI-EXPRESS EDGE CONNECTOR

2

7

7

7

3

6

6

6

4

5

6

345

345

345

7

2

2

2

8

1

1

1

A A

+3.3V_BUS

G_SMBCLK

5,17

IN

G_SMBDAT

5,17

BI

C

C

C

B B

C C

PLACE THESE CAPS AS CLOSE TO

PCIE CONN ECTOR AS POSSIBLE

+12V_BUS

C110

C111

10uF

0.15uF

16V

16V

+3.3V_BUS

C113

C114

10uF

0.1uF

6.3V

6.3V

C112

0.15uF

16V

C115

C116

1uF

0.01uF

6.3V

10V

R103

45.3K

1%

DNI DNI

+3.3V_BUS

2

Q100B

R104

45.3K

1%

+3.3V_BUS

2N7002DW

61

R105 0R 5%

R106 0R 5%

34

Q100A

2N7002DW

5

DNI

DNI

2

OUT

2

OUT

2

OUT

2

OUT

2

OUT

2

OUT

2

OUT

2

OUT

2

OUT

2

OUT

2

OUT

2

OUT

2

OUT

2

OUT

2

OUT

2

OUT

2

OUT

2

OUT

2

OUT

2

OUT

2

OUT

2

OUT

2

OUT

2

OUT

2

OUT

2

OUT

2

OUT

2

OUT

2

OUT

2

OUT

2

OUT

2

OUT

+3.3V_BUS +12V_BUS +12V_BUS +3.3V_BUS

MPCIE1

Mechanical Key

x16 PCIe

SMBCLK

SMBDAT

PETP0_GFXRP0

PETN0_GFXRN0

PETP1_GFXRP1

PETN1_GFXRN1

PETP2_GFXRP2

PETN2_GFXRN2

PETP3_GFXRP3

PETN3_GFXRN3

PETP4_GFXRP4

PETN4_GFXRN4

PETP5_GFXRP5

PETN5_GFXRN5

PETP6_GFXRP6

PETN6_GFXRN6

PETP7_GFXRP7

PETN7_GFXRN7

PETP8_GFXRP8

PETN8_GFXRN8

PETP9_GFXRP9

PETN9_GFXRN9

PETP10_GFXRP10

PETN10_GFXRN10

PETP11_GFXRP11

PETN11_GFXRN11

PETP12_GFXRP12

PETN12_GFXRN12

PETP13_GFXRP13

PETN13_GFXRN13

PETP14_GFXRP14

PETN14_GFXRN14

PETP15_GFXRP15

PETN15_GFXRN15

PRESENCE

B1

+12V

B2

+12V

B3

+12V

B4

GND

B5

SMCLK

B6

SMDAT

B7

GND

B8

+3.3V

B9

JTAG1

B10

3.3Vaux

B11

WAKE_

B12

RSVD_B12

B13

GND

B14

PETp0

B15

PETn0

B16

GND

B17

PRSNT2_B17

B18

GND

B19

PETp1

B20

PETn1

B21

GND

B22

GND

B23

PETp2

B24

PETn2

B25

GND

B26

GND

B27

PETp3

B28

PETn3

B29

GND

B30

RSVD_B30

B31

PRSNT2_B31

B32

GND

B33

PETp4

B34

PETn4

B35

GND

B36

GND

B37

PETp5

B38

PETn5

B39

GND

B40

GND

B41

PETp6

B42

PETn6

B43

GND

B44

GND

B45

PETp7

B46

PETn7

B47

GND

B48

PRSNT2_B48

B49

GND

B50

PETp8

B51

PETn8

B52

GND

B53

GND

B54

PETp9

B55

PETn9

B56

GND

B57

GND

B58

PETp10

B59

PETn10

B60

GND

B61

GND

B62

PETp11

B63

PETn11

B64

GND

B65

GND

B66

PETp12

B67

PETn12

B68

GND

B69

GND

B70

PETp13

B71

PETn13

B72

GND

B73

GND

B74

PETp14

B75

PETn14

B76

GND

B77

GND

B78

PETp15

B79

PETn15

B80

GND

B81

PRSNT2_B81

B82

RSVD_B82

PRSNT1_A1

PERST_

REFCLK+

REFCLK-

RSVD_A19

RSVD_A32

RSVD_A33

RSVD_A50

PERp10

PERn10

PERp11

PERn11

PERp12

PERn12

PERp13

PERn13

PERp14

PERn14

PERp15

PERn15

A1

A2

+12V

A3

+12V

A4

GND

A5

JTAG2

A6

JTAG3

A7

JTAG4

A8

JTAG5

A9

+3.3V

A10

+3.3V

A11

A12

GND

A13

A14

A15

GND

A16

PERp0

A17

PERn0

A18

GND

A19

A20

GND

A21

PERp1

A22

PERn1

A23

GND

A24

GND

A25

PERp2

A26

PERn2

A27

GND

A28

GND

A29

PERp3

A30

PERn3

A31

GND

A32

A33

A34

GND

A35

PERp4

A36

PERn4

A37

GND

A38

GND

A39

PERp5

A40

PERn5

A41

GND

A42

GND

A43

PERp6

A44

PERn6

A45

GND

A46

GND

A47

PERp7

A48

PERn7

A49

GND

A50

A51

GND

A52

PERp8

A53

PERn8

A54

GND

A55

GND

A56

PERp9

A57

PERn9

A58

GND

A59

GND

A60

A61

A62

GND

A63

GND

A64

A65

A66

GND

A67

GND

A68

A69

A70

GND

A71

GND

A72

A73

A74

GND

A75

GND

A76

A77

A78

GND

A79

GND

A80

A81

A82

GND

PRESENCE

JTDIO_LOOP

PCIE_REFCLKP

PCIE_REFCLKN

PERP0

PERN0

PERP1

PERN1

PERP2

PERN2

PERP3

PERN3

PERP4

PERN4

PERP5

PERN5

PERP6

PERN6

PERP7

PERN7

PERP8

PERN8

PERP9

PERN9

PERP10

PERN10

PERP11

PERN11

PERP12

PERN12

PERP13

PERN13

PERP14

PERN14

PERP15

PERN15

15,14

2

OUT

2

OUT

2

IN

2

IN

2

IN

2

IN

2

IN

2

IN

2

IN

2

IN

2

IN

2

IN

2

IN

2

IN

2

IN

2

IN

2

IN

2

IN

2

IN

2

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

2

2

2

2

2

2

2

2

2

2

2

2

2

2

+3.3V_BUS

R101 10K 5%

DNI

C101 0.1uF 6.3V

DNI

1.8V_EN

PERSTB

R102 0R 5%

+3.3V_BUS

IN

RST_EN

C100

0.1uF

6.3V

U100B

3 5

NC7SZ08P5X

U100A

1

2

NC7SZ08P5X

R100 1K 5%

PLACE R100 I N U100

4

PERSTB_BUF

DNI

2,11,16

OUT

SYMBOL LEGEND

DNI

DO NOT

INSTALL

b or #

ACTIVE

LOW

BUO

BRING UP

ONLY

DIGITAL

GROUND

ANALOG

GROUND

DD

DD

DD

C

C

C

BB

BB

BB

CONFIDENTIAL AND PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL AND PROPRIETARY TO ADVANCED MICRO DEVICES INC.

1.0

1.0

1.0

CONFIDENTIAL AND PROPRIETARY TO ADVANCED MICRO DEVICES INC.

2014

2014

2014

Advanced Micro Devices

Advanced Micro Devices

Advanced Micro Devices

C

C

C

This AMD Board sch ematic and de sign is the exclusi ve property of AMD, and

This AMD Board sch ematic and de sign is the exclusi ve property of AMD, and

This AMD Board sch ematic and de sign is the exclusi ve property of AMD, and

is provided only to entitie s under a non-dis closure agreemen t with AMD

is provided only to entitie s under a non-dis closure agreemen t with AMD

is provided only to entitie s under a non-dis closure agreemen t with AMD

for evaluation purposes. Further dis tribution or dis closure i s strictl y

for evaluation purposes. Further dis tribution or dis closure i s strictl y

for evaluation purposes. Further dis tribution or dis closure i s strictl y

prohibited. Use of this schema tic and des ign for any purpose other than

prohibited. Use of this schema tic and des ign for any purpose other than

prohibited. Use of this schema tic and des ign for any purpose other than

evaluation requires a Board T echnology Li cense Agreeme nt with AMD.

evaluation requires a Board T echnology Li cense Agreeme nt with AMD.

evaluation requires a Board T echnology Li cense Agreeme nt with AMD.

AMD makes no representations or warranties of a ny kind regarding this

AMD makes no representations or warranties of a ny kind regarding this

AMD makes no representations or warranties of a ny kind regarding this

schematic and design, i ncluding , not limit ed to, any implie d warranty

schematic and design, i ncluding , not limit ed to, any implie d warranty

schematic and design, i ncluding , not limit ed to, any implie d warranty

of merchantability or fitnes s for a particu lar purpose, and di sclai ms

of merchantability or fitnes s for a particu lar purpose, and di sclai ms

of merchantability or fitnes s for a particu lar purpose, and di sclai ms

responsibili ty for any consequences resulting f rom use of the

responsibili ty for any consequences resulting f rom use of the

responsibili ty for any consequences resulting f rom use of the

information incl uded herein.

information incl uded herein.

information incl uded herein.

TITLE:

TITLE:

TITLE:

2

2

2

7

TOBAGO GDDR5 x32

TOBAGO GDDR5 x32

TOBAGO GDDR5 x32

A

A

A

1

1

1

8

4

4

4

5

AMD - PLATFORM HARDWARE ENG

AMD - PLATFORM HARDWARE ENG

AMD - PLATFORM HARDWARE ENG

#48, No.1387, ZHANGDONG ROAD

#48, No.1387, ZHANGDONG ROAD

#48, No.1387, ZHANGDONG ROAD

SHANGHAI, CHINA 201203

SHANGHAI, CHINA 201203

SHANGHAI, CHINA 201203

PCI-EXPRESS EDGE CONNECTOR

PCI-EXPRESS EDGE CONNECTOR

PCI-EXPRESS EDGE CONNECTOR

SHEET:

SHEET:

SHEET:

DATE:

DATE:

DATE:

SHEET NUMBER:

SHEET NUMBER:

SHEET NUMBER:

DOCUMENT NUMBER:

DOCUMENT NUMBER:

DOCUMENT NUMBER:

Mon Nov 24 11:06:52 2014

Mon Nov 24 11:06:52 2014

Mon Nov 24 11:06:52 2014

1 19

1 19

1 19

OF

OF

OF

105-C913xx-00B

105-C913xx-00B

105-C913xx-00B

3

3

3

6

REV:

REV:

REV:

A

A

A

D D

8

8

8

1

7

7

7

2

6

6

6

3

5

5

5

4

1

8

8

8

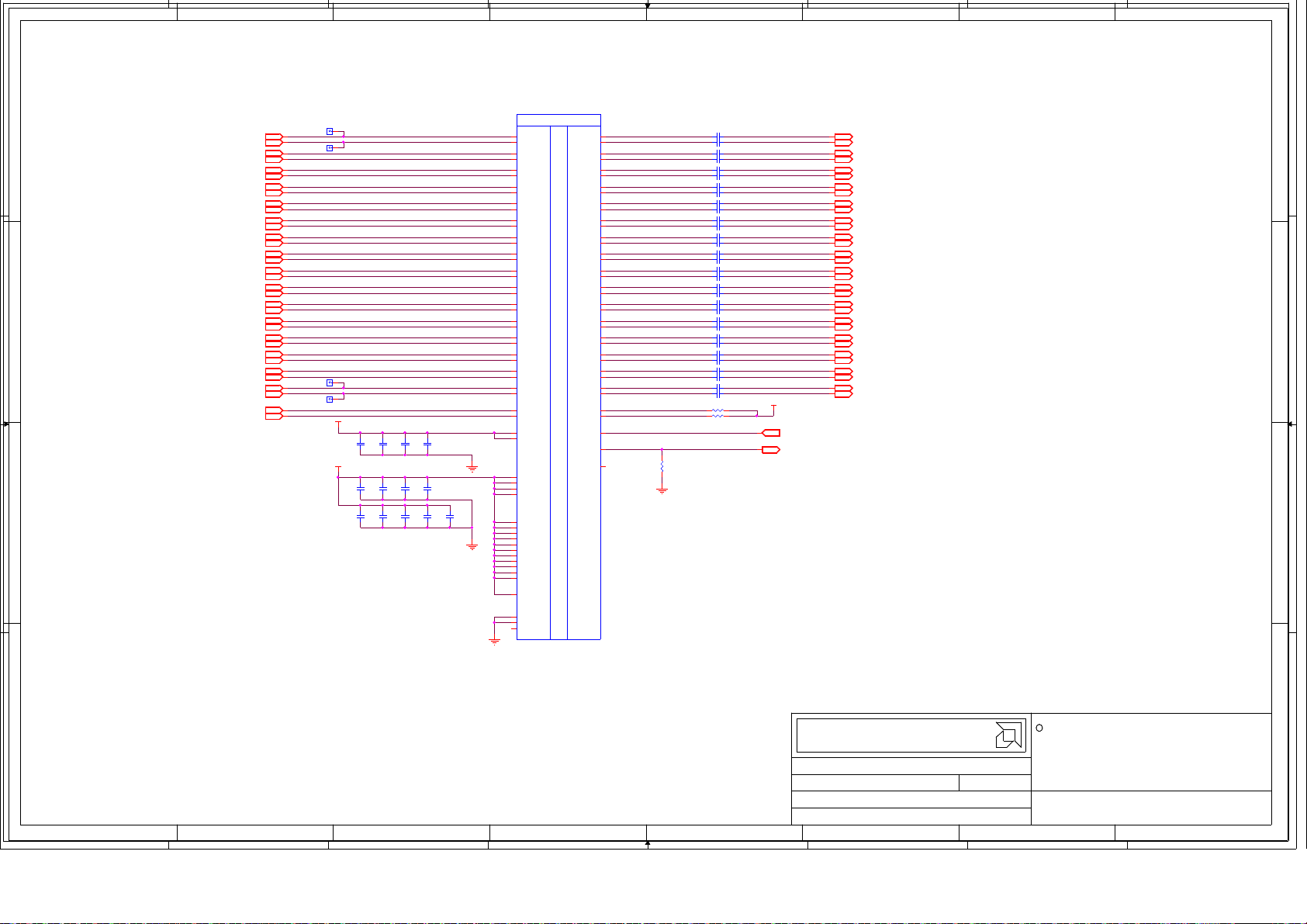

(2) TOBAGO PCIE INTERFACE

2

7

7

7

3

6

6

6

4

5

6

345

345

345

7

2

2

2

8

1

1

1

AH52

AH50

AG53

AG51

AF52

AF50

AE53

AE51

AD52

AD50

AC53

AC51

AA53

AA51

AJ51

AJ53

AU48

AR48

AA42

AA43

AC42

AC43

AG43

AE42

AE43

AE44

AG42

AA44

Y52

Y50

W53

W51

V52

V50

U53

U51

R53

R51

P52

P50

N53

N51

M52

M50

L53

L51

U43

U44

U42

W43

W42

R42

N42

N43

L43

U1B

PCIE_RX0P

PCIE_RX0N

PCIE_RX1P

PCIE_RX1N

PCIE_RX2P

PCIE_RX2N

PCIE_RX3P

PCIE_RX3N

PCIE_RX4P

PCIE_RX4N

PCIE_RX5P

PCIE_RX5N

PCIE_RX6P

PCIE_RX6N

PCIE_RX7P

PCIE_RX7N

PCIE_RX8P

PCIE_RX8N

PCIE_RX9P

PCIE_RX9N

PCIE_RX10P

PCIE_RX10N

PCIE_RX11P

PCIE_RX11N

PCIE_RX12P

PCIE_RX12N

PCIE_RX13P

PCIE_RX13N

PCIE_RX14P

PCIE_RX14N

PCIE_RX15P

PCIE_RX15N

PCIE_REFCLKP

PCIE_REFCLKN

PCIE_PVDD_1

PCIE_PVDD_2

BIF_VDDC

BIF_VDDC

BIF_VDDC

BIF_VDDC

PCIE_VDDC

PCIE_VDDC

PCIE_VDDC

PCIE_VDDC

PCIE_VDDC

PCIE_VDDC

PCIE_VDDC

PCIE_VDDC

PCIE_VDDC

PCIE_VDDC

PCIE_VDDC

PCIE_VDDC

VSS

VSS

NC_VSS

PART 2 OF 16

BONAIRE

DD

DD

PCIE_TX0P

AL48

PCIE_TX0P

PCIE_TX0N

PCIE_TX1P

PCIE_TX1N

PCIE_TX2P

PCIE_TX2N

PCIE_TX3P

PCIE_TX3N

PCIE_TX4P

PCIE_TX4N

PCIE_TX5P

PCIE_TX5N

PCIE_TX6P

PCIE_TX6N

PCIE_TX7P

PCIE_TX7N

PCIE_TX8P

PCIE_TX8N

PCIE_TX9P

PCIE_TX9N

PCIE_TX10P

PCIE_TX10N

PCIE_TX11P

PCIE_TX11N

PCIE_TX12P

PCIE_TX12N

PCIEXPRESS

PCIE_TX13P

PCIE_TX13N

PCIE_TX14P

PCIE_TX14N

PCIE_TX15P

PCIE_TX15N

PCIE_CALR_RX

PCIE_CALR_TX

PERSTB

PX_EN

NC_PX_EN_1

PCIE_TX0N

AL47

PCIE_TX1P

AL45

PCIE_TX1N

AL44

PCIE_TX2P

AJ48

PCIE_TX2N

AJ47

PCIE_TX3P

AG48

PCIE_TX3N

AG47

PCIE_TX4P

AG45

PCIE_TX4N

AG44

PCIE_TX5P

AE48

PCIE_TX5N

AE47

PCIE_TX6P

AC48

PCIE_TX6N

AC47

PCIE_TX7P

AC45

PCIE_TX7N

AC44

PCIE_TX8P

AA48

PCIE_TX8N

AA47

PCIE_TX9P

W48

PCIE_TX9N

W47

PCIE_TX10P

W45

PCIE_TX10N

W44

PCIE_TX11P

U48

PCIE_TX11N

U47

PCIE_TX12P

R48

PCIE_TX12N

R47

PCIE_TX13P

R45

PCIE_TX13N

R44

PCIE_TX14P

N48

PCIE_TX14N

N47

PCIE_TX15P

L48

PCIE_TX15N

L47

PCIE_CALR_RX

AN47

PCIE_CALR_TX

AN48

AK50

PERSTB_BUF

J48

PX_EN

J45

R152

1K

5%

DNI

C150 0.22uF 6.3V

C151 0.22uF 6.3V

C152 0.22uF 6.3V

C153 0.22uF 6.3V

C154 0.22uF 6.3V

C155 0.22uF 6.3V

C156 0.22uF 6.3V

C157 0.22uF 6.3V

C158 0.22uF 6.3V

C159 0.22uF 6.3V

C160 0.22uF 6.3V

C161 0.22uF 6.3V

C162 0.22uF 6.3V

C163 0.22uF 6.3V

C164 0.22uF 6.3V

C165 0.22uF 6.3V

C166 0.22uF 6.3V

C167 0.22uF 6.3V

C168 0.22uF 6.3V

C169 0.22uF 6.3V

C170 0.22uF 6.3V

C171 0.22uF 6.3V

C172 0.22uF 6.3V

C173 0.22uF 6.3V

C174 0.22uF 6.3V

C175 0.22uF 6.3V

C176 0.22uF 6.3V

C177 0.22uF 6.3V

C178 0.22uF 6.3V

C179 0.22uF 6.3V

C180 0.22uF 6.3V

C181 0.22uF 6.3V

R150 1K 1%

R151 1.69K 1%

PERP0

PERN0

PERP1

PERN1

PERP2

PERN2

PERP3

PERN3

PERP4

PERN4

PERP5

PERN5

PERP6

PERN6

PERP7

PERN7

PERP8

PERN8

PERP9

PERN9

PERP10

PERN10

PERP11

PERN11

PERP12

PERN12

PERP13

PERN13

PERP14

PERN14

PERP15

PERN15

+0.95V

1,11,16

IN

17,15,16

OUT

1

OUT

1

OUT

1

OUT

1

OUT

1

OUT

1

OUT

1

OUT

1

OUT

1

OUT

1

OUT

1

OUT

1

OUT

1

OUT

1

OUT

1

OUT

1

OUT

1

OUT

1

OUT

1

OUT

1

OUT

1

OUT

1

OUT

1

OUT

1

OUT

1

OUT

1

OUT

1

OUT

1

OUT

1

OUT

1

OUT

1

OUT

1

OUT

DD

C

C

C

BB

BB

BB

A A

1

IN

1

IN

1

IN

1

IN

1

IN

1

IN

1

IN

1

IN

1

IN

1

IN

1

IN

1

IN

1

IN

1

IN

1

IN

1

IN

1

IN

1

IN

1

IN

1

IN

1

IN

1

IN

1

C

C

C

B B

IN

1

IN

1

IN

1

IN

1

IN

1

IN

1

IN

1

IN

1

IN

1

IN

1

IN

1

IN

C C

TP100

TP101

TP130

TP131

+1.8V

C120

10uF

6.3V

+0.95V

C130

1uF

6.3V

C134

1uF

6.3V

PETP0_GFXRP0

PETN0_GFXRN0

PETP1_GFXRP1

PETN1_GFXRN1

PETP2_GFXRP2

PETN2_GFXRN2

PETP3_GFXRP3

PETN3_GFXRN3

PETP4_GFXRP4

PETN4_GFXRN4

PETP5_GFXRP5

PETN5_GFXRN5

PETP6_GFXRP6

PETN6_GFXRN6

PETP7_GFXRP7

PETN7_GFXRN7

PETP8_GFXRP8

PETN8_GFXRN8

PETP9_GFXRP9

PETN9_GFXRN9

PETP10_GFXRP10

PETN10_GFXRN10

PETP11_GFXRP11

PETN11_GFXRN11

PETP12_GFXRP12

PETN12_GFXRN12

PETP13_GFXRP13

PETN13_GFXRN13

PETP14_GFXRP14

PETN14_GFXRN14

PETP15_GFXRP15

PETN15_GFXRN15

PCIE_REFCLKP

PCIE_REFCLKN

C121

C122

C123

1uF

1uF

1uF

6.3V

6.3V

6.3V

C131

C132

C133

1uF

1uF

1uF

6.3V

6.3V

6.3V

C135

C136

C137

1uF

6.3V

C138

1uF

1uF

10uF

6.3V

6.3V

6.3V

CONFIDENTIAL AND PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL AND PROPRIETARY TO ADVANCED MICRO DEVICES INC.

1.0

1.0

1.0

CONFIDENTIAL AND PROPRIETARY TO ADVANCED MICRO DEVICES INC.

2014

2014

2014

Advanced Micro Devices

Advanced Micro Devices

Advanced Micro Devices

C

C

C

This AMD Board sch ematic and de sign is the exclusi ve property of AMD, and

This AMD Board sch ematic and de sign is the exclusi ve property of AMD, and

This AMD Board sch ematic and de sign is the exclusi ve property of AMD, and

is provided only to entitie s under a non-dis closure agreemen t with AMD

is provided only to entitie s under a non-dis closure agreemen t with AMD

is provided only to entitie s under a non-dis closure agreemen t with AMD

for evaluation purposes. Further dis tribution or dis closure i s strictl y

for evaluation purposes. Further dis tribution or dis closure i s strictl y

for evaluation purposes. Further dis tribution or dis closure i s strictl y

prohibited. Use of this schema tic and des ign for any purpose other than

prohibited. Use of this schema tic and des ign for any purpose other than

prohibited. Use of this schema tic and des ign for any purpose other than

evaluation requires a Board T echnology Li cense Agreeme nt with AMD.

evaluation requires a Board T echnology Li cense Agreeme nt with AMD.

evaluation requires a Board T echnology Li cense Agreeme nt with AMD.

AMD makes no representations or warranties of a ny kind regarding this

AMD makes no representations or warranties of a ny kind regarding this

AMD makes no representations or warranties of a ny kind regarding this

schematic and design, i ncluding , not limit ed to, any implie d warranty

schematic and design, i ncluding , not limit ed to, any implie d warranty

schematic and design, i ncluding , not limit ed to, any implie d warranty

of merchantability or fitnes s for a particu lar purpose, and di sclai ms

of merchantability or fitnes s for a particu lar purpose, and di sclai ms

of merchantability or fitnes s for a particu lar purpose, and di sclai ms

responsibili ty for any consequences resulting f rom use of the

responsibili ty for any consequences resulting f rom use of the

responsibili ty for any consequences resulting f rom use of the

information incl uded herein.

information incl uded herein.

information incl uded herein.

TITLE:

TITLE:

TITLE:

2

2

2

7

TOBAGO GDDR5 x32

TOBAGO GDDR5 x32

TOBAGO GDDR5 x32

A

A

A

1

1

1

8

4

4

4

5

AMD - PLATFORM HARDWARE ENG

AMD - PLATFORM HARDWARE ENG

AMD - PLATFORM HARDWARE ENG

#48, No.1387, ZHANGDONG ROAD

#48, No.1387, ZHANGDONG ROAD

#48, No.1387, ZHANGDONG ROAD

SHANGHAI, CHINA 201203

SHANGHAI, CHINA 201203

SHANGHAI, CHINA 201203

TOBAGO PCIE

TOBAGO PCIE

TOBAGO PCIE

SHEET:

SHEET:

SHEET:

DATE:

DATE:

DATE:

SHEET NUMBER:

SHEET NUMBER:

SHEET NUMBER:

DOCUMENT NUMBER:

DOCUMENT NUMBER:

DOCUMENT NUMBER:

Mon Nov 24 11:06:52 2014

Mon Nov 24 11:06:52 2014

Mon Nov 24 11:06:52 2014

2 19

2 19

2 19

OF

OF

OF

105-C913xx-00B

105-C913xx-00B

105-C913xx-00B

3

3

3

6

REV:

REV:

REV:

A

A

A

D D

8

8

8

1

7

7

7

2

6

6

6

3

5

5

5

4

1

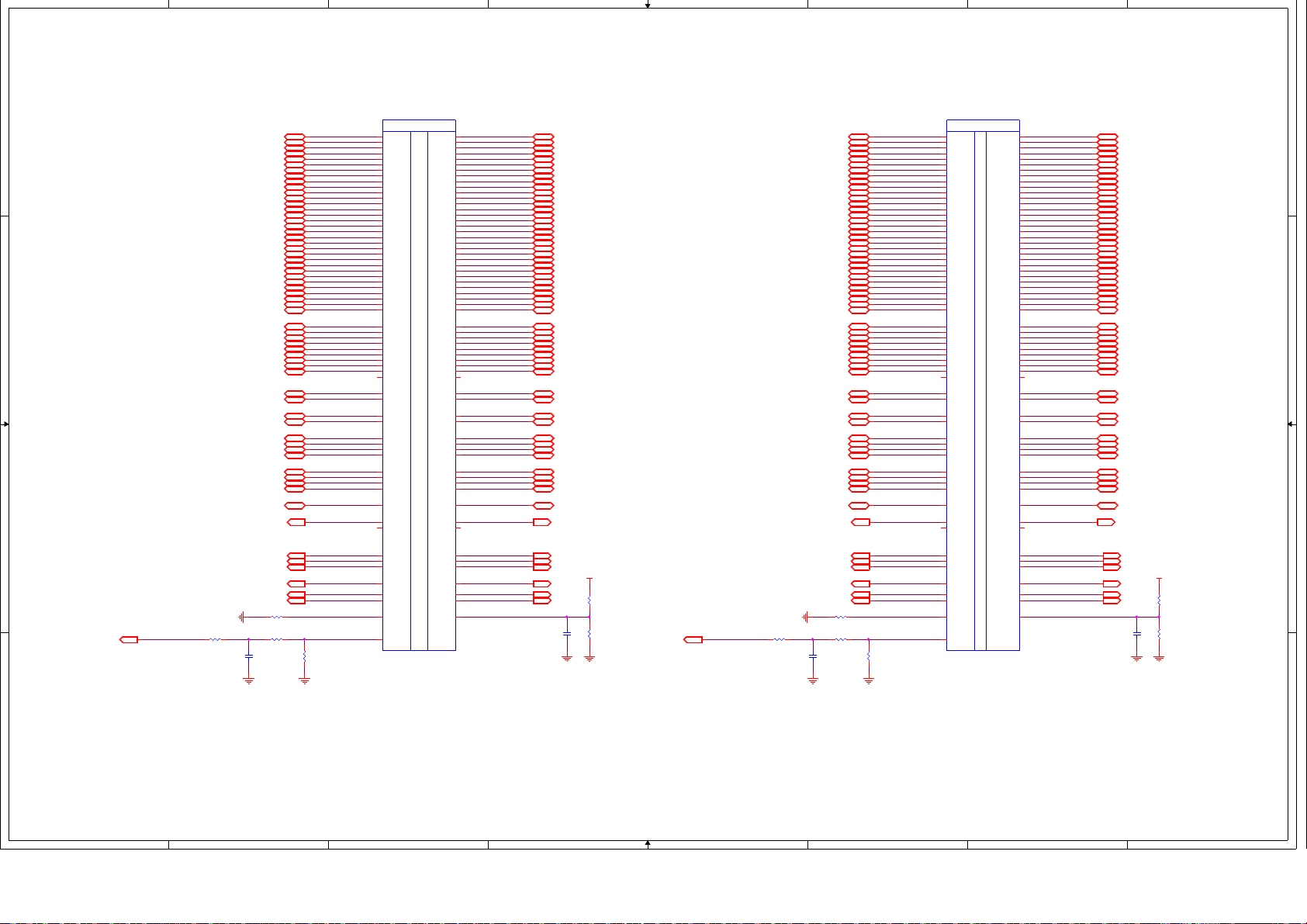

(3) TOBAGO MEMORY INTERFACE

2

3

4

5

6

7

8

A A

DQA0_<0>

4

BI

DQA0_<1>

4

BI

DQA0_<2>

4

BI

DQA0_<3>

4

BI

DQA0_<4>

4

BI

DQA0_<5>

4

BI

DQA0_<6>

4

BI

DQA0_<7>

4

BI

DQA0_<8>

4

BI

DQA0_<9>

4

BI

DQA0_<10>

4

BI

DQA0_<11>

4

BI

DQA0_<12>

4

BI

DQA0_<13>

4

BI

DQA0_<14>

4

BI

DQA0_<15>

4

BI

DQA0_<16>

4

BI

DQA0_<17>

4

BI

DQA0_<18>

4

BI

DQA0_<19>

4

BI

DQA0_<20>

4

BI

DQA0_<21>

4

BI

DQA0_<22>

4

BI

DQA0_<23>

4

BI

DQA0_<24>

4

BI

DQA0_<25>

4

BI

DQA0_<26>

4

BI

DQA0_<27>

4

BI

DQA0_<28>

4

BI

DQA0_<29>

4

BI

DQA0_<30>

4

BI

DQA0_<31>

4

R3600 1%120R

C3601

120pF

50V

BI

MAA0_<0>

4

BI

MAA0_<1>

4

BI

MAA0_<2>

4

BI

MAA0_<3>

4

BI

MAA0_<4>

4

BI

MAA0_<5>

4

BI

MAA0_<6>

4

BI

MAA0_<7>

4

BI

MAA0_<8>

4

BI

WCKA0_0

4

BI

WCKA0B_0

4

BI

WCKA0_1

4

BI

WCKA0B_1

4

BI

EDCA0_0

4

BI

EDCA0_1

4

BI

EDCA0_2

4

BI

EDCA0_3

4

BI

DDBIA0_0

4

BI

DDBIA0_1

4

BI

DDBIA0_2

4

BI

DDBIA0_3

4

BI

ADBIA0

4

BI

CSA0B_0

4

OUT

CASA0B

4

OUT

RASA0B

4

OUT

WEA0B

4

OUT

CKEA0

4

OUT

CLKA0

4

OUT

CLKA0B

4

OUT

MEM_CALRA MEM_CALRBMVREFDA MVREFDB

DNI

DRAM_RST_A_R DRAM_RST_B_R

10R 1%R3604

R3603

5.1K

1%

B B

C C

DRAM_RST_A

4

OUT

U1C

PART 3 OF 16

G51

DQA0_0

F52

DQA0_1

F50

DQA0_2

E53

DQA0_3

D50

DQA0_4

C49

DQA0_5

A49

DQA0_6

D48

DQA0_7

B48

DQA0_8

C47

DQA0_9

D46

DQA0_10

B46

DQA0_11

D44

DQA0_12

B44

DQA0_13

C43

DQA0_14

D42

DQA0_15

A41

DQA0_16

D40

DQA0_17

B40

DQA0_18

C39

DQA0_19

C37

DQA0_20

A37

DQA0_21

D36

DQA0_22

B36

DQA0_23

C35

DQA0_24

D34

DQA0_25

B34

DQA0_26

C33

DQA0_27

D32

DQA0_28

B32

DQA0_29

C31

DQA0_30

D30

DQA0_31

L33

MAA0_0

G33

MAA0_1

F37

MAA0_2

G37

MAA0_3

F39

MAA0_4

K39

MAA0_5

F29

MAA0_6

G29

MAA0_7

F33

MAA0_8

L37

MAA0_9

J53

WCKA0_0

H52

WCKA0B_0

B42

WCKA0_1

C41

WCKA0B_1

E51

EDCA0_0

C45

EDCA0_1

B38

EDCA0_2

A33

EDCA0_3

H50

DDBIA0_0

A45

DDBIA0_1

D38

DDBIA0_2

B30

DDBIA0_3

L29

ADBIA0

K35

CSA0B_0

K31

CSA0B_1

K27

CASA0B

F35

RASA0B

M41

WEA0B

G25

CKEA0

F41

CLKA0

G41

CLKA0B

F31

MEM_CALRA

L25

DRAM_RSTA

BONAIRE

DQA1_0

DQA1_1

DQA1_2

DQA1_3

DQA1_4

DQA1_5

DQA1_6

DQA1_7

DQA1_8

DQA1_9

DQA1_10

DQA1_11

DQA1_12

DQA1_13

DQA1_14

DQA1_15

DQA1_16

DQA1_17

DQA1_18

DQA1_19

DQA1_20

DQA1_21

DQA1_22

DQA1_23

DQA1_24

DQA1_25

DQA1_26

DQA1_27

DQA1_28

DQA1_29

DQA1_30

DQA1_31

MAA1_0

MAA1_1

MAA1_2

MAA1_3

MAA1_4

MAA1_5

MAA1_6

MAA1_7

MEMORY INTERFACE BANK A

MAA1_8

MAA1_9

WCKA1_0

WCKA1B_0

WCKA1_1

WCKA1B_1

EDCA1_0

EDCA1_1

EDCA1_2

EDCA1_3

DDBIA1_0

DDBIA1_1

DDBIA1_2

DDBIA1_3

ADBIA1

CSA1B_0

CSA1B_1

CASA1B

RASA1B

WEA1B

CKEA1

CLKA1

CLKA1B

MVREFDA

A29

D28

B28

C27

B26

C25

A25

D24

B24

C23

D22

B22

D20

B20

C19

D18

A17

D16

B16

C15

C13

A13

D12

B12

C11

D10

B10

C9

D8

B8

C7

B6

K19

F17

G13

F15

F13

F11

F23

L21

F19

G17

C17

B18

A5

C5

D26

C21

B14

A9

C29

A21

D14

D6

G21

K15

F21

K23

L17

G11

F25

F9

G9

F27

DQA1_<0>

DQA1_<1>

DQA1_<2>

DQA1_<3>

DQA1_<4>

DQA1_<5>

DQA1_<6>

DQA1_<7>

DQA1_<8>

DQA1_<9>

DQA1_<10>

DQA1_<11>

DQA1_<12>

DQA1_<13>

DQA1_<14>

DQA1_<15>

DQA1_<16>

DQA1_<17>

DQA1_<18>

DQA1_<19>

DQA1_<20>

DQA1_<21>

DQA1_<22>

DQA1_<23>

DQA1_<24>

DQA1_<25>

DQA1_<26>

DQA1_<27>

DQA1_<28>

DQA1_<29>

DQA1_<30>

DQA1_<31>

MAA1_<0>

MAA1_<1>

MAA1_<2>

MAA1_<3>

MAA1_<4>

MAA1_<5>

MAA1_<6>

MAA1_<7>

MAA1_<8>

WCKA1_0

WCKA1B_0

WCKA1_1

WCKA1B_1

EDCA1_0

EDCA1_1

EDCA1_2

EDCA1_3

DDBIA1_0

DDBIA1_1

DDBIA1_2

DDBIA1_3

ADBIA1

CSA1B_0

CASA1B

RASA1B

WEA1B

CKEA1

CLKA1

CLKA1B

USE INTERNAL VREF

MVREFD = 0.7 * VDDR1

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

OUT

4

OUT

4

OUT

4

OUT

OUT

OUT

OUT

+MVDD +MVDD

4

4

4

R3601

40.2R

1%

DNI

R3602

C3600

100R

1uF

1%

6.3V

DNI

DNI

DRAM_RST_B

4

OUT

1%49.9RR36151%49.9RR3605

C3611

120pF

50V

DQB0_<0>

4

BI

DQB0_<1>

4

BI

DQB0_<2>

4

BI

DQB0_<3>

4

BI

DQB0_<4>

4

BI

DQB0_<5>

4

BI

DQB0_<6>

4

BI

DQB0_<7>

4

BI

DQB0_<8>

4

BI

DQB0_<9>

4

BI

DQB0_<10>

4

BI

DQB0_<11>

4

BI

DQB0_<12>

4

BI

DQB0_<13>

4

BI

DQB0_<14>

4

BI

DQB0_<15>

4

BI

DQB0_<16>

4

BI

DQB0_<17>

4

BI

DQB0_<18>

4

BI

DQB0_<19>

4

BI

DQB0_<20>

4

BI

DQB0_<21>

4

BI

DQB0_<22>

4

BI

DQB0_<23>

4

BI

DQB0_<24>

4

BI

DQB0_<25>

4

BI

DQB0_<26>

4

BI

DQB0_<27>

4

BI

DQB0_<28>

4

BI

DQB0_<29>

4

BI

DQB0_<30>

4

BI

DQB0_<31>

4

BI

MAB0_<0>

4

BI

MAB0_<1>

4

BI

MAB0_<2>

4

BI

MAB0_<3>

4

BI

MAB0_<4>

4

BI

MAB0_<5>

4

BI

MAB0_<6>

4

BI

MAB0_<7>

4

BI

MAB0_<8>

4

BI

WCKB0_0

4

BI

WCKB0B_0

4

BI

WCKB0_1

4

BI

WCKB0B_1

4

BI

EDCB0_0

4

BI

EDCB0_1

4

BI

EDCB0_2

4

BI

EDCB0_3

4

BI

DDBIB0_0

4

BI

DDBIB0_1

4

BI

DDBIB0_2

4

BI

DDBIB0_3

4

BI

ADBIB0

4

BI

CSB0B_0

4

OUT

CASB0B

4

OUT

RASB0B

4

OUT

WEB0B

4

OUT

CKEB0

4

OUT

CLKB0

4

OUT

CLKB0B

4

OUT

1%120RR3610

DNI

1%10RR 3614

R3613

5.1K

1%

U1D

PART 4 OF 16

AJ1

DQB0_0

AH4

DQB0_1

AH2

DQB0_2

AG3

DQB0_3

AF2

DQB0_4

AE3

DQB0_5

AE1

DQB0_6

AD4

DQB0_7

AD2

DQB0_8

AC3

DQB0_9

AB4

DQB0_10

AB2

DQB0_11

Y4

DQB0_12

Y2

DQB0_13

W3

DQB0_14

V4

DQB0_15

U1

DQB0_16

T4

DQB0_17

T2

DQB0_18

R3

DQB0_19

N3

DQB0_20

N1

DQB0_21

M4

DQB0_22

M2

DQB0_23

L3

DQB0_24

K4

DQB0_25

K2

DQB0_26

J3

DQB0_27

H4

DQB0_28

H2

DQB0_29

G3

DQB0_30

F2

DQB0_31

W10

MAB0_0

U6

MAB0_1

N7

MAB0_2

R6

MAB0_3

N6

MAB0_4

L6

MAB0_5

AC6

MAB0_6

AA11

MAB0_7

W6

MAB0_8

U7

MAB0_9

U3

WCKB0_0

V2

WCKB0B_0

E1

WCKB0_1

E3

WCKB0B_1

AF4

EDCB0_0

AA3

EDCB0_1

P2

EDCB0_2

J1

EDCB0_3

AJ3

DDBIB0_0

AA1

DDBIB0_1

P4

DDBIB0_2

F4

DDBIB0_3

AA7

ADBIB0

R10

CSB0B_0

AA6

CSB0B_1

AC10

CASB0B

U11

RASB0B

L7

WEB0B

AE6

CKEB0

J6

CLKB0

J7

CLKB0B

AL6

MEM_CALRB

AE11

DRAM_RSTB

BONAIRE

DQB1_0

DQB1_1

DQB1_2

DQB1_3

DQB1_4

DQB1_5

DQB1_6

DQB1_7

DQB1_8

DQB1_9

DQB1_10

DQB1_11

DQB1_12

DQB1_13

DQB1_14

DQB1_15

DQB1_16

DQB1_17

DQB1_18

DQB1_19

DQB1_20

DQB1_21

DQB1_22

DQB1_23

DQB1_24

DQB1_25

DQB1_26

DQB1_27

DQB1_28

DQB1_29

DQB1_30

DQB1_31

MAB1_0

MAB1_1

MAB1_2

MAB1_3

MAB1_4

MAB1_5

MAB1_6

MEMORY INTERFACE BANK B

MAB1_7

MAB1_8

MAB1_9

WCKB1_0

WCKB1B_0

WCKB1_1

WCKB1B_1

EDCB1_0

EDCB1_1

EDCB1_2

EDCB1_3

DDBIB1_0

DDBIB1_1

DDBIB1_2

DDBIB1_3

ADBIB1

CSB1B_0

CSB1B_1

CASB1B

RASB1B

WEB1B

CKEB1

CLKB1

CLKB1B

MVREFDB

AK4

AL3

AM2

AM4

AN3

AP2

AP4

AR3

AT2

AT4

AU1

AU3

AW3

AY2

AY4

BA1

BB4

BC3

BD2

BD4

BF2

BF4

BG3

BH2

BH4

BJ1

BJ3

BK4

BN5

BK6

BM6

BL7

AN11

AN6

AU7

AR10

AW6

AW10

AJ6

AJ7

AN7

AU11

BB2

BA3

BN9

BM8

AN1

AV2

BE3

BL5

AK2

AV4

BE1

BK8

AJ11

AU6

AL10

AG10

AR6

BA12

AE7

BA6

BA7

AG6

DQB1_<0>

DQB1_<1>

DQB1_<2>

DQB1_<3>

DQB1_<4>

DQB1_<5>

DQB1_<6>

DQB1_<7>

DQB1_<8>

DQB1_<9>

DQB1_<10>

DQB1_<11>

DQB1_<12>

DQB1_<13>

DQB1_<14>

DQB1_<15>

DQB1_<16>

DQB1_<17>

DQB1_<18>

DQB1_<19>

DQB1_<20>

DQB1_<21>

DQB1_<22>

DQB1_<23>

DQB1_<24>

DQB1_<25>

DQB1_<26>

DQB1_<27>

DQB1_<28>

DQB1_<29>

DQB1_<30>

DQB1_<31>

MAB1_<0>

MAB1_<1>

MAB1_<2>

MAB1_<3>

MAB1_<4>

MAB1_<5>

MAB1_<6>

MAB1_<7>

MAB1_<8>

WCKB1_0

WCKB1B_0

WCKB1_1

WCKB1B_1

EDCB1_0

EDCB1_1

EDCB1_2

EDCB1_3

DDBIB1_0

DDBIB1_1

DDBIB1_2

DDBIB1_3

ADBIB1

CSB1B_0

CASB1B

RASB1B

WEB1B

CKEB1

CLKB1

CLKB1B

USE INTERNAL VREF

MVREFD = 0.7 * VDDR1

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

BI

4

OUT

4

OUT

4

OUT

4

OUT

4

OUT

4

OUT

4

OUT

R3611

40.2R

1%

DNI

C3610

R3612

1uF

100R

6.3V

1%

DNI

DNI

D D

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

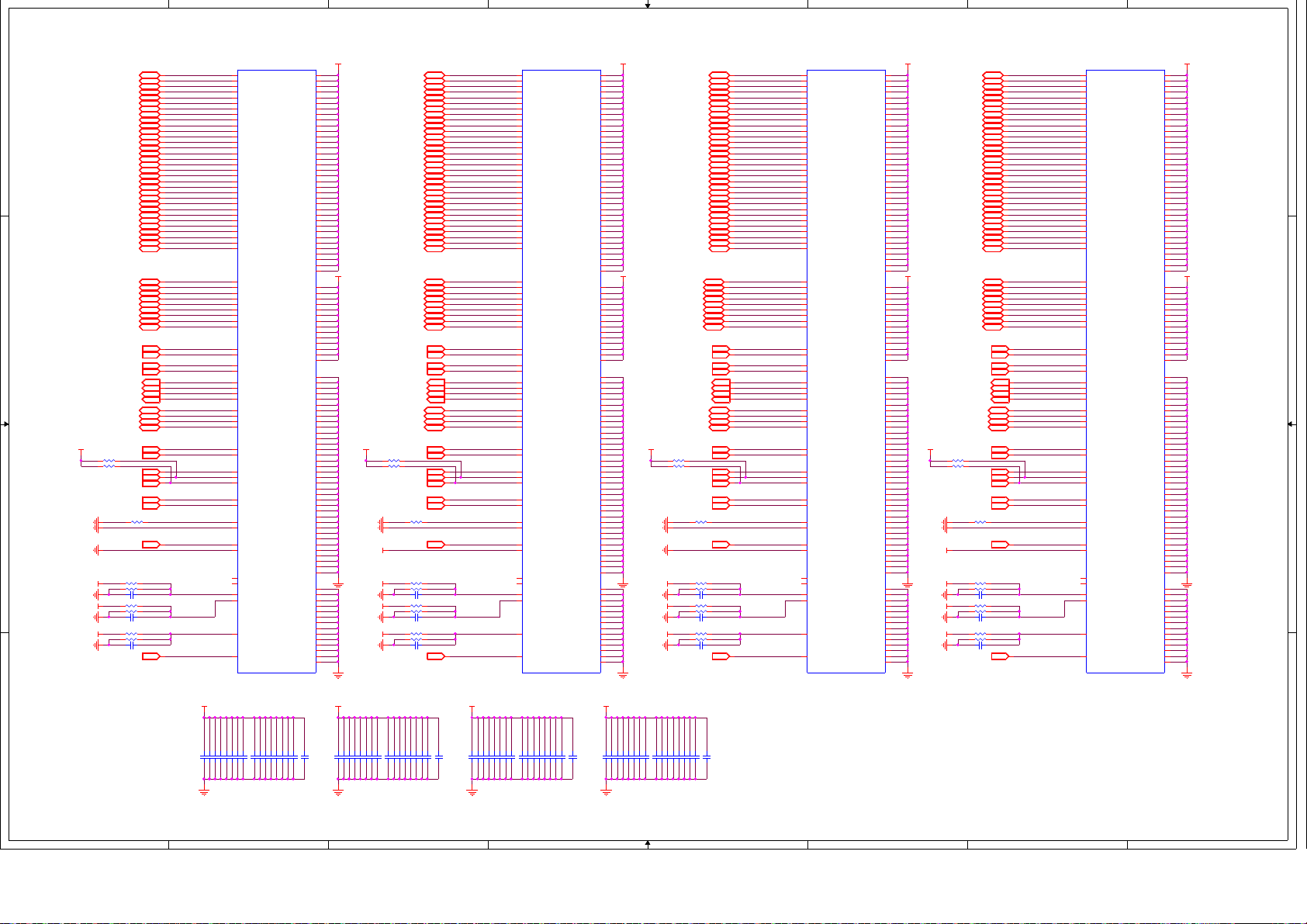

(4) GDDR5 CHAB x32

MF = 0

U2000

DQA0_<16>

3

BI

DQA0_<17>

3

BI

DQA0_<19>

3

BI

DQA0_<18>

3

BI

DQA0_<23>

3

BI

DQA0_<21>

3

BI

DQA0_<22>

3

BI

DQA0_<20>

3

60.4R 1%R2003

60.4RR2004 1%

BI

DQA0_<25>

3

BI

DQA0_<26>

3

BI

DQA0_<27>

3

BI

DQA0_<24>

3

BI

DQA0_<29>

3

BI

DQA0_<30>

3

BI

DQA0_<28>

3

BI

DQA0_<31>

3

BI

DQA0_<14>

3

BI

DQA0_<15>

3

BI

DQA0_<13>

3

BI

DQA0_<12>

3

BI

DQA0_<9>

3

BI

DQA0_<11>

3

BI

DQA0_<10>

3

BI

DQA0_<8>

3

BI

DQA0_<7>

3

BI

DQA0_<6>

3

BI

DQA0_<4>

3

BI

DQA0_<5>

3

BI

DQA0_<0>

3

BI

DQA0_<2>

3

BI

DQA0_<1>

3

BI

DQA0_<3>

3

BI

MAA0_<8>

3

BI

MAA0_<7>

3

BI

MAA0_<6>

3

BI

MAA0_<5>

3

BI

MAA0_<4>

3

BI

MAA0_<3>

3

BI

MAA0_<2>

3

BI

MAA0_<1>

3

BI

MAA0_<0>

3

BI

WCKA0_0

3

IN

WCKA0B_0

3

IN

WCKA0_1

3

IN

WCKA0B_1

3

IN

EDCA0_2

3

OUT

EDCA0_3

3

OUT

EDCA0_1

3

OUT

EDCA0_0

3

OUT

3

3

3

3

DDBIA0_2

BI

DDBIA0_3

BI

DDBIA0_1

BI

DDBIA0_0

BI

RASA0B

3

IN

CASA0B

3

IN

CKEA0

3

IN

CLKA0B

3

IN

CLKA0

3

IN

CSA0B_0

3

IN

WEA0B

3

IN

ZQ_A0 ZQ_A1 ZQ_B0 ZQ_B1

1%120RR2000

DRAM_RST_A

3,4

IN

1%2.37KR2010

1%5.49KR2011

VREFD1_A0 VREFD1_A1 VREFD1_B0 VREFD1_B1

6.3V1uFC2000

1%2.37KR2012

1%5.49KR2013

VREFD2_A0 VREFD2_A1 VREFD2_B0 VREFD2_B1

6.3V1uFC2001

VREFC_A0 VREFC_A1 VREFC_B0 VREFC _B1

1%2.37KR2014

1%5.49KR2015

6.3V1uFC2002

ADBIA0

3

IN

A A

B B

+MVDD

C C

+MVDD

+MVDD

+MVDD

M2

M4

N2

N4

T2

T4

V2

V4

M13

M11

N13

N11

T13

T11

V13

V11

F13

F11

E13

E11

B13

B11

A13

A11

F2

F4

E2

E4

B2

B4

A2

A4

J5

K4

K5

K10

K11

H10

H11

H5

H4

D4

D5

P4

P5

R2

R13

C13

C2

P2

P13

D13

D2

G3

L3

J3

J11

J12

G12

L12

J13

J10

J2

J1

A5

V5

A10

V10

J14

J4

DQ31__DQ7

DQ30__DQ6

DQ29__DQ5

DQ28__DQ4

DQ27__DQ3

DQ26__DQ2

DQ25__DQ1

DQ24__DQ0

DQ23__DQ15

DQ22__DQ14

DQ21__DQ13

DQ20__DQ12

DQ19__DQ11

DQ18__DQ10

DQ17__DQ9

DQ16__DQ8

DQ15__DQ23

DQ14__DQ22

DQ13__DQ21

DQ12__DQ20

DQ11__DQ19

DQ10__DQ18

DQ9__DQ17

DQ8__DQ16

DQ7__DQ31

DQ6__DQ30

DQ5__DQ29

DQ4__DQ28

DQ3__DQ27

DQ2__DQ26

DQ1__DQ25

DQ0__DQ24

RFU_A12_NC

A7_A8__A0_A10

A6_A11__A1_A9

A5_BA1__A3_BA3

A4_BA2__A2_BA0

A3_BA3__A5_BA1

A2_BA0__A4_BA2

A1_A9__A6_A11

A0_A10__A7_A8

WCK01__WCK23

WCK01#__WCK23#

WCK23__WCK01

WCK23#__WCK01#

EDC3__EDC0

EDC2__EDC1

EDC1__EDC2

EDC0__EDC3

DBI3#__DBI0#

DBI2#__DBI1#

DBI1#__DBI2#

DBI0#__DBI3#

RAS#__CAS#

CAS#__RAS#

CKE#

CK#

CK

CS#__WE#

WE#__CS#

ZQ

SEN

RESET#

MF

Vpp_NC

Vpp_NC1

VREFD1

VREFD2

VREFC

ABI#

VDDQ_B1

VDDQ_B3

VDDQ_B12

VDDQ_B14

VDDQ_D1

VDDQ_D3

VDDQ_D12

VDDQ_D14

VDDQ_E5

VDDQ_E10

VDDQ_F1

VDDQ_F3

VDDQ_F12

VDDQ_F14

VDDQ_G2

VDDQ_G13

VDDQ_H3

VDDQ_H12

VDDQ_K3

VDDQ_K12

VDDQ_L2

VDDQ_L13

VDDQ_M1

VDDQ_M3

VDDQ_M12

VDDQ_M14

VDDQ_N5

VDDQ_N10

VDDQ_P1

VDDQ_P3

VDDQ_P12

VDDQ_P14

VDDQ_T1

VDDQ_T3

VDDQ_T12

VDDQ_T14

VDD_C5

VDD_C10

VDD_D11

VDD_G1

VDD_G4

VDD_G11

VDD_G14

VDD_L1

VDD_L4

VDD_L11

VDD_L14

VDD_P11

VDD_R5

VDD_R10

VSSQ_A1

VSSQ_A3

VSSQ_A12

VSSQ_A14

VSSQ_C1

VSSQ_C3

VSSQ_C4

VSSQ_C11

VSSQ_C12

VSSQ_C14

VSSQ_E1

VSSQ_E3

VSSQ_E12

VSSQ_E14

VSSQ_F5

VSSQ_F10

VSSQ_H2

VSSQ_H13

VSSQ_K2

VSSQ_K13

VSSQ_M5

VSSQ_M10

VSSQ_N1

VSSQ_N3

VSSQ_N12

VSSQ_N14

VSSQ_R1

VSSQ_R3

VSSQ_R4

VSSQ_R11

VSSQ_R12

VSSQ_R14

VSSQ_V1

VSSQ_V3

VSSQ_V12

VSSQ_V14

VSS_B5

VSS_B10

VSS_D10

VSS_G5

VSS_G10

VSS_H1

VSS_H14

VSS_K1

VSS_K14

VSS_L5

VSS_L10

VSS_P10

VSS_T5

VSS_T10

+MVDD

B1

B3

B12

B14

D1

D3

D12

D14

E5

E10

F1

F3

F12

F14

G2

G13

H3

H12

K3

K12

L2

L13

M1

M3

M12

M14

N5

N10

P1

P3

P12

P14

T1

T3

T12

T14

+MVDD

C5

C10

D11

G1

G4

G11

G14

L1

L4

L11

L14

P11

R5

R10

A1

A3

A12

A14

C1

C3

C4

C11

C12

C14

E1

E3

E12

+MVDD

E14

F5

F10

H2

H13

K2

K13

M5

M10

N1

N3

N12

N14

R1

R3

R4

R11

R12

R14

+MVDD

V1

V3

V12

V14

+MVDD

B5

B10

D10

G5

+MVDD

G10

H1

H14

K1

K14

+MVDD

L5

L10

P10

T5

T10

3

BI

3

BI

3

BI

3

BI

3

BI

3

BI

3

BI

3

BI

3

BI

3

BI

3

BI

3

BI

3

BI

3

BI

3

BI

3

BI

3

BI

3

BI

3

BI

3

BI

3

BI

3

BI

3

BI

3

BI

3

BI

3

BI

3

BI

3

BI

3

BI

3

BI

3

BI

3

BI

3

BI

3

BI

3

BI

3

BI

3

BI

3

BI

3

BI

3

BI

3

BI

3

IN

3

IN

3

IN

3

IN

3

OUT

3

OUT

3

OUT

3

OUT

3

BI

3

BI

3

BI

3

BI

3

IN

3

IN

1%60.4RR2203

1%60.4RR2204

3

IN

3

IN

3

IN

3

IN

3

IN

1%120RR2200

3,4

IN

1%2.37KR2210

1%5.49KR2211

6.3V1uFC2200

1%2.37KR2212

1%5.49KR2213

6.3V1uFC2201

1%2.37KR2214

1%5.49KR2215

6.3V1uFC2202

3

IN

DQA1 _<1 6>

DQA1 _<1 7>

DQA1 _<1 9>

DQA1 _<1 8>

DQA1 _<2 3>

DQA1 _<2 1>

DQA1 _<2 2>

DQA1 _<2 0>

DQA1 _<2 4>

DQA1 _<2 5>

DQA1 _<2 6>

DQA1 _<2 7>

DQA1 _<3 0>

DQA1 _<3 1>

DQA1 _<2 8>

DQA1 _<2 9>

DQA1 _<1 3>

DQA1 _<1 4>

DQA1 _<1 5>

DQA1 _<1 2>

DQA1 _<1 0>

DQA1 _<9 >

DQA1 _<1 1>

DQA1 _<8 >

DQA1 _<7 >

DQA1 _<6 >

DQA1 _<4 >

DQA1 _<5 >

DQA1 _<0 >

DQA1 _<2 >

DQA1 _<1 >

DQA1 _<3 >

MAA1_<8>

MAA1_<0>

MAA1_<1>

MAA1_<3>

MAA1_<2>

MAA1_<5>

MAA1_<4>

MAA1_<6>

MAA1_<7>

WCKA1_0

WCKA1B_0

WCKA1_1

WCKA1B_1

EDCA1_2

EDCA1_3

EDCA1_1

EDCA1_0

DDBIA1_2

DDBIA1_3

DDBIA1_1

DDBIA1_0

CASA1B

RASA1B

CKEA1

CLKA1B

CLKA1

WEA1B

CSA1B_0

DRAM_RST_A

ADBIA1

MF = 1 MF = 0 MF = 1

U2200

M2

DQ31__DQ7

M4

DQ30__DQ6

N2

DQ29__DQ5

N4

DQ28__DQ4

T2

DQ27__DQ3

T4

DQ26__DQ2

V2

DQ25__DQ1

V4

DQ24__DQ0

M13

DQ23__DQ15

M11

DQ22__DQ14

N13

DQ21__DQ13

N11

DQ20__DQ12

T13

DQ19__DQ11

T11

DQ18__DQ10

V13

DQ17__DQ9

V11

DQ16__DQ8

F13

DQ15__DQ23

F11

DQ14__DQ22

E13

DQ13__DQ21

E11

DQ12__DQ20

B13

DQ11__DQ19

B11

DQ10__DQ18

A13

DQ9__DQ17

A11

DQ8__DQ16

F2

DQ7__DQ31

F4

DQ6__DQ30

E2

DQ5__DQ29

E4

DQ4__DQ28

B2

DQ3__DQ27

B4

DQ2__DQ26

A2

DQ1__DQ25

A4

DQ0__DQ24

J5

RFU_A12_NC

K4

A7_A8__A0_A10

K5

A6_A11__A1_A9

K10

A5_BA1__A3_BA3

K11

A4_BA2__A2_BA0

H10

A3_BA3__A5_BA1

H11

A2_BA0__A4_BA2

H5

A1_A9__A6_A11

H4

A0_A10__A7_A8

D4

WCK01__WCK23

D5

WCK01#__WCK23#

P4

WCK23__WCK01

P5

WCK23#__WCK01#

R2

EDC3__EDC0

R13

EDC2__EDC1

C13

EDC1__EDC2

C2

EDC0__EDC3

P2

DBI3#__DBI0#

P13

DBI2#__DBI1#

D13

DBI1#__DBI2#

D2

DBI0#__DBI3#

G3

RAS#__CAS#

L3

CAS#__RAS#

J3

CKE#

J11

CK#

J12

CK

G12

CS#__WE#

L12

WE#__CS#

J13

ZQ

J10

SEN

J2

RESET#

J1

MF

A5

Vpp_NC

V5

Vpp_NC1

A10

VREFD1

V10

VREFD2

J14

VREFC

J4

ABI#

VDDQ_B1

VDDQ_B3

VDDQ_B12

VDDQ_B14

VDDQ_D1

VDDQ_D3

VDDQ_D12

VDDQ_D14

VDDQ_E5

VDDQ_E10

VDDQ_F1

VDDQ_F3

VDDQ_F12

VDDQ_F14

VDDQ_G2

VDDQ_G13

VDDQ_H3

VDDQ_H12

VDDQ_K3

VDDQ_K12

VDDQ_L2

VDDQ_L13

VDDQ_M1

VDDQ_M3

VDDQ_M12

VDDQ_M14

VDDQ_N5

VDDQ_N10

VDDQ_P1

VDDQ_P3

VDDQ_P12

VDDQ_P14

VDDQ_T1

VDDQ_T3

VDDQ_T12

VDDQ_T14

VDD_C5

VDD_C10

VDD_D11

VDD_G1

VDD_G4

VDD_G11

VDD_G14

VDD_L1

VDD_L4

VDD_L11

VDD_L14

VDD_P11

VDD_R5

VDD_R10

VSSQ_A1

VSSQ_A3

VSSQ_A12

VSSQ_A14

VSSQ_C1

VSSQ_C3

VSSQ_C4

VSSQ_C11

VSSQ_C12

VSSQ_C14

VSSQ_E1

VSSQ_E3

VSSQ_E12

VSSQ_E14

VSSQ_F5

VSSQ_F10

VSSQ_H2

VSSQ_H13

VSSQ_K2

VSSQ_K13

VSSQ_M5

VSSQ_M10

VSSQ_N1

VSSQ_N3

VSSQ_N12

VSSQ_N14

VSSQ_R1

VSSQ_R3

VSSQ_R4

VSSQ_R11

VSSQ_R12

VSSQ_R14

VSSQ_V1

VSSQ_V3

VSSQ_V12

VSSQ_V14

VSS_B5

VSS_B10

VSS_D10

VSS_G5

VSS_G10

VSS_H1

VSS_H14

VSS_K1

VSS_K14

VSS_L5

VSS_L10

VSS_P10

VSS_T5

VSS_T10

+MVDD

B1

B3

B12

B14

D1

D3

D12

D14

E5

E10

F1

F3

F12

F14

G2

G13

H3

H12

K3

K12

L2

L13

M1

M3

M12

M14

N5

N10

P1

P3

P12

P14

T1

T3

T12

T14

+MVDD

C5

C10

D11

G1

G4

G11

G14

L1

L4

L11

L14

P11

R5

R10

A1

A3

A12

A14

C1

C3

C4

C11

C12

C14

E1

E3

E12

+MVDD

E14

F5

F10

H2

H13

K2

K13

M5

M10

N1

N3

N12

N14

R1

R3

R4

R11

R12

R14

V1

V3

V12

V14

B5

B10

D10

G5

G10

H1

H14

K1

K14

L5

L10

P10

T5

T10

R2400 120R 1%

+MVDD

+MVDD

+MVDD

15

DQB0 _<1 5>

3

BI

14

DQB0 _<1 4>

3

BI

12

DQB0 _<1 2>

3

BI

13

DQB0 _<1 3>

3

BI

8

DQB0 _<8 >

3

BI

10

DQB0 _<1 0>

3

BI

9

DQB0 _<9 >

3

BI

11

DQB0 _<1 1>

3

BI

7

DQB0 _<7 >

3

BI

3

DQB0 _<3 >

3

BI

6

DQB0 _<6 >

3

BI

5

DQB0 _<5 >

3

BI

0

DQB0 _<0 >

3

BI

1

DQB0 _<1 >

3

BI

4

DQB0 _<4 >

3

BI

2

DQB0 _<2 >

3

BI

19

DQB0 _<1 9>

3

BI

17

DQB0 _<1 7>

3

BI

18

DQB0 _<1 8>

3

BI

16

DQB0 _<1 6>

3

BI

21

DQB0 _<2 1>

3

BI

22

DQB0 _<2 2>

3

BI

20

DQB0 _<2 0>

3

BI

23

DQB0 _<2 3>

3

BI

24

DQB0 _<2 4>

3

BI

25

DQB0 _<2 5>

3

BI

27

DQB0 _<2 7>

3

BI

26

DQB0 _<2 6>

3

BI

31

DQB0 _<3 1>

3

BI

29

DQB0 _<2 9>

3

BI

30

DQB0 _<3 0>

3

BI

28

DQB0 _<2 8>

3

BI

8

MAB 0_ <8>

3

BI

7

MAB 0_ <7>

3

BI

6

MAB 0_ <6>

3

BI

5

MAB 0_ <5>

3

BI

4

MAB 0_ <4>

3

BI

3

MAB 0_ <3>

3

BI

2

MAB 0_ <2>

3

BI

1

MAB 0_ <1>

3

BI

0

MAB 0_ <0>

3

BI

WCKB0_1

3

IN

WCKB0B_1

3

IN

WCKB0_0

3

IN

WCKB0B_0

3

IN

EDCB0_1

3

OUT

EDCB0_0

3

OUT

EDCB0_2

3

OUT

EDCB0_3

3

OUT

3

3

3

3

1%60.4RR2403

1%60.4RR2404

DDBIB0_1

BI

DDBIB0_0

BI

DDBIB0_2

BI

DDBIB0_3

BI

RASB0B

3

IN

CASB0B

3

IN

CKEB0

3

IN

CLKB0B

3

IN

CLKB0

3

IN

CSB0B_0

3

IN

WEB0B

3

IN

DRAM_RST_B

3,4

IN

1%2.37KR2410

1%5.49KR2411

6.3V1uFC2400

1%2.37KR2412

1%5.49KR2413

6.3V1uFC2401

1%2.37KR2414

1%5.49KR2415

6.3V1uFC2402

ADBIB0

3

IN

M2

M4

N2

N4

T2

T4

V2

V4

M13

M11

N13

N11

T13

T11

V13

V11

F13

F11

E13

E11

B13

B11

A13

A11

F2

F4

E2

E4

B2

B4

A2

A4

J5

K4

K5

K10

K11

H10

H11

H5

H4

D4

D5

P4

P5

R2

R13

C13

C2

P2

P13

D13

D2

G3

L3

J3

J11

J12

G12

L12

J13

J10

J2

J1

A5

V5

A10

V10

J14

J4

DQ31__DQ7

DQ30__DQ6

DQ29__DQ5

DQ28__DQ4

DQ27__DQ3

DQ26__DQ2

DQ25__DQ1

DQ24__DQ0

DQ23__DQ15

DQ22__DQ14

DQ21__DQ13

DQ20__DQ12

DQ19__DQ11

DQ18__DQ10

DQ17__DQ9

DQ16__DQ8

DQ15__DQ23

DQ14__DQ22

DQ13__DQ21

DQ12__DQ20

DQ11__DQ19

DQ10__DQ18

DQ9__DQ17

DQ8__DQ16

DQ7__DQ31

DQ6__DQ30

DQ5__DQ29

DQ4__DQ28

DQ3__DQ27

DQ2__DQ26

DQ1__DQ25

DQ0__DQ24

RFU_A12_NC

A7_A8__A0_A10

A6_A11__A1_A9

A5_BA1__A3_BA3

A4_BA2__A2_BA0

A3_BA3__A5_BA1

A2_BA0__A4_BA2

A1_A9__A6_A11

A0_A10__A7_A8

WCK01__WCK23

WCK01#__WCK23#

WCK23__WCK01

WCK23#__WCK01#

EDC3__EDC0

EDC2__EDC1

EDC1__EDC2

EDC0__EDC3

DBI3#__DBI0#

DBI2#__DBI1#

DBI1#__DBI2#

DBI0#__DBI3#

RAS#__CAS#

CAS#__RAS#

CKE#

CK#

CK

CS#__WE#

WE#__CS#

ZQ

SEN

RESET#

MF

Vpp_NC

Vpp_NC1

VREFD1

VREFD2

VREFC

ABI#

U2400

VDDQ_B1

VDDQ_B3

VDDQ_B12

VDDQ_B14

VDDQ_D1

VDDQ_D3

VDDQ_D12

VDDQ_D14

VDDQ_E5

VDDQ_E10

VDDQ_F1

VDDQ_F3

VDDQ_F12

VDDQ_F14

VDDQ_G2

VDDQ_G13

VDDQ_H3

VDDQ_H12

VDDQ_K3

VDDQ_K12

VDDQ_L2

VDDQ_L13

VDDQ_M1

VDDQ_M3

VDDQ_M12

VDDQ_M14

VDDQ_N5

VDDQ_N10

VDDQ_P1

VDDQ_P3

VDDQ_P12

VDDQ_P14

VDDQ_T1

VDDQ_T3

VDDQ_T12

VDDQ_T14

VDD_C5

VDD_C10

VDD_D11

VDD_G1

VDD_G4

VDD_G11

VDD_G14

VDD_L1

VDD_L4

VDD_L11

VDD_L14

VDD_P11

VDD_R5

VDD_R10

VSSQ_A1

VSSQ_A3

VSSQ_A12

VSSQ_A14

VSSQ_C1

VSSQ_C3

VSSQ_C4

VSSQ_C11

VSSQ_C12

VSSQ_C14

VSSQ_E1

VSSQ_E3

VSSQ_E12

VSSQ_E14

VSSQ_F5

VSSQ_F10

VSSQ_H2

VSSQ_H13

VSSQ_K2

VSSQ_K13

VSSQ_M5

VSSQ_M10

VSSQ_N1

VSSQ_N3

VSSQ_N12

VSSQ_N14

VSSQ_R1

VSSQ_R3

VSSQ_R4

VSSQ_R11

VSSQ_R12

VSSQ_R14

VSSQ_V1

VSSQ_V3

VSSQ_V12

VSSQ_V14

VSS_B5

VSS_B10

VSS_D10

VSS_G5

VSS_G10

VSS_H1

VSS_H14

VSS_K1

VSS_K14

VSS_L5

VSS_L10

VSS_P10

VSS_T5

VSS_T10

+MVDD

B1

B3

B12

B14

D1

D3

D12

D14

E5

E10

F1

F3

F12

F14

G2

G13

H3

H12

K3

K12

L2

L13

M1

M3

M12

M14

N5

N10

P1

P3

P12

P14

T1

T3

T12

T14

+MVDD

C5

C10

D11

G1

G4

G11

G14

L1

L4

L11

L14

P11

R5

R10

A1

A3

A12

A14

C1

C3

C4

C11

C12

C14

E1

E3

E12

E14

F5

F10

H2

H13

K2

K13

M5

M10

N1

N3

N12

N14

R1

R3

R4

R11

R12

R14

V1

V3

V12

V14

B5

B10

D10

G5

G10

H1

H14

K1

K14

L5

L10

P10

T5

T10

VDDQ_B1

VDDQ_B3

VDDQ_B12

VDDQ_B14

VDDQ_D1

VDDQ_D3

VDDQ_D12

VDDQ_D14

VDDQ_E5

VDDQ_E10

VDDQ_F1

VDDQ_F3

VDDQ_F12

VDDQ_F14

VDDQ_G2

VDDQ_G13

VDDQ_H3

VDDQ_H12

VDDQ_K3

VDDQ_K12

VDDQ_L2

VDDQ_L13

VDDQ_M1

VDDQ_M3

VDDQ_M12

VDDQ_M14

VDDQ_N5

VDDQ_N10

VDDQ_P1

VDDQ_P3

VDDQ_P12

VDDQ_P14

VDDQ_T1

VDDQ_T3

VDDQ_T12

VDDQ_T14

VDD_C5

VDD_C10

VDD_D11

VDD_G1

VDD_G4

VDD_G11

VDD_G14

VDD_L1

VDD_L4

VDD_L11

VDD_L14

VDD_P11

VDD_R5

VDD_R10

VSSQ_A1

VSSQ_A3

VSSQ_A12

VSSQ_A14

VSSQ_C1

VSSQ_C3

VSSQ_C4

VSSQ_C11

VSSQ_C12

VSSQ_C14

VSSQ_E1

VSSQ_E3

VSSQ_E12

VSSQ_E14

VSSQ_F5

VSSQ_F10

VSSQ_H2

VSSQ_H13

VSSQ_K2

VSSQ_K13

VSSQ_M5

VSSQ_M10

VSSQ_N1

VSSQ_N3

VSSQ_N12

VSSQ_N14

VSSQ_R1

VSSQ_R3

VSSQ_R4

VSSQ_R11

VSSQ_R12

VSSQ_R14

VSSQ_V1

VSSQ_V3

VSSQ_V12

VSSQ_V14

VSS_B5

VSS_B10

VSS_D10

VSS_G5

VSS_G10

VSS_H1

VSS_H14

VSS_K1

VSS_K14

VSS_L5

VSS_L10

VSS_P10

VSS_T5

VSS_T10

+MVDD

B1

B3

B12

B14

D1

D3

D12

D14

E5

E10

F1

F3

F12

F14

G2

G13

H3

H12

K3

K12

L2

L13

M1

M3

M12

M14

N5

N10

P1

P3

P12

P14

T1

T3

T12

T14

+MVDD

C5

C10

D11

G1

G4

G11

G14

L1

L4

L11

L14

P11

R5

R10

A1

A3

A12

A14

C1

C3

C4

C11

C12

C14

E1

E3

E12

E14

F5

F10

H2

H13

K2

K13

M5

M10

N1

N3

N12

N14

R1

R3

R4

R11

R12

R14

V1

V3

V12

V14

B5

B10

D10

G5

G10

H1

H14

K1

K14

L5

L10

P10

T5

T10

U2600

16

DQB1 _<1 6>

3

BI

17

DQB1 _<1 7>

3

BI

19

DQB1 _<1 9>

3

BI

18

DQB1 _<1 8>

3

BI

23

DQB1 _<2 3>

3

BI

21

DQB1 _<2 1>

3

BI

22

DQB1 _<2 2>

3

BI

20

DQB1 _<2 0>

3

BI

26

DQB1 _<2 6>

3

BI

24

DQB1 _<2 4>

3

BI

25

DQB1 _<2 5>

3

BI

27

DQB1 _<2 7>

3

BI

28

DQB1 _<2 8>

3

BI

30

DQB1 _<3 0>

3

BI

29

DQB1 _<2 9>

3

BI

31

DQB1 _<3 1>

3

BI

14

DQB1 _<1 4>

3

BI

13

DQB1 _<1 3>

3

BI

15

DQB1 _<1 5>

3

BI

12

DQB1 _<1 2>

3

BI

11

DQB1 _<1 1>

3

BI

8

DQB1 _<8 >

3

BI

10

DQB1 _<1 0>

3

BI

9

DQB1 _<9 >

3

BI

7

DQB1 _<7 >

3

BI

6

DQB1 _<6 >

3

BI

4

DQB1 _<4 >

3

BI

5

DQB1 _<5 >

3

BI

0

DQB1 _<0 >

3

BI

2

DQB1 _<2 >

3

BI

1

DQB1 _<1 >

3

BI

3

DQB1 _<3 >

3

BI

8

MAB 1_ <8>

3

BI

0

MAB 1_ <0>

3

BI

1

MAB 1_ <1>

3

BI

3

MAB 1_ <3>

3

BI

2

MAB 1_ <2>

3

BI

5

MAB 1_ <5>

3

BI

4

MAB 1_ <4>

3

BI

6

MAB 1_ <6>

3

BI

7

MAB 1_ <7>

3

BI

WCKB1_0

3

IN

WCKB1B_0

3

IN

WCKB1_1

3

IN

WCKB1B_1

3

IN

EDCB1_2

3

OUT

EDCB1_3

3

OUT

EDCB1_1

3

OUT

EDCB1_0

3

OUT

3

3

3

3

+MVDD

R2600 1%120R

+MVDD

+MVDD

+MVDD

+MVDD

DDBIB1_2

BI

DDBIB1_3

BI

DDBIB1_1

BI

DDBIB1_0

BI

CASB1B

3

IN

RASB1B

3

IN

1%60.4RR2603

1%60.4RR2604

CKEB1

3

IN

CLKB1B

3

IN

CLKB1

3

IN

WEB1B

3

IN

CSB1B_0

3

IN

DRAM_RST_B

3,4

IN

1%2.37KR2610

1%5.49KR2611

6.3V1uFC2600

1%2.37KR2612

1%5.49KR2613

6.3V1uFC2601

1%2.37KR2614

1%5.49KR2615

6.3V1uFC2602

ADBIB1

3

IN

M2

M4

N2

N4

T2

T4

V2

V4

M13

M11

N13

N11

T13

T11

V13

V11

F13

F11

E13

E11

B13

B11

A13

A11

F2

F4

E2

E4

B2

B4

A2

A4

J5

K4

K5

K10

K11

H10

H11

H5

H4

D4

D5

P4

P5

R2

R13

C13

C2

P2

P13

D13

D2

G3

L3

J3

J11

J12

G12

L12

J13

J10

J2

J1

A5

V5

A10

V10

J14

J4

DQ31__DQ7

DQ30__DQ6

DQ29__DQ5

DQ28__DQ4

DQ27__DQ3

DQ26__DQ2

DQ25__DQ1

DQ24__DQ0

DQ23__DQ15

DQ22__DQ14

DQ21__DQ13

DQ20__DQ12

DQ19__DQ11

DQ18__DQ10

DQ17__DQ9

DQ16__DQ8

DQ15__DQ23

DQ14__DQ22

DQ13__DQ21

DQ12__DQ20

DQ11__DQ19

DQ10__DQ18

DQ9__DQ17

DQ8__DQ16

DQ7__DQ31

DQ6__DQ30

DQ5__DQ29

DQ4__DQ28

DQ3__DQ27

DQ2__DQ26

DQ1__DQ25

DQ0__DQ24

RFU_A12_NC

A7_A8__A0_A10

A6_A11__A1_A9

A5_BA1__A3_BA3

A4_BA2__A2_BA0

A3_BA3__A5_BA1

A2_BA0__A4_BA2

A1_A9__A6_A11

A0_A10__A7_A8

WCK01__WCK23

WCK01#__WCK23#

WCK23__WCK01

WCK23#__WCK01#

EDC3__EDC0

EDC2__EDC1

EDC1__EDC2

EDC0__EDC3

DBI3#__DBI0#

DBI2#__DBI1#

DBI1#__DBI2#

DBI0#__DBI3#

RAS#__CAS#

CAS#__RAS#

CKE#

CK#

CK

CS#__WE#

WE#__CS#

ZQ

SEN

RESET#

MF

Vpp_NC

Vpp_NC1

VREFD1

VREFD2

VREFC

ABI#

+MVDD +MVDD

6.3V1uFC2214

6.3V1uFC2215

6.3V1uFC2216

6.3V1uFC2217

6.3V0.1uFC2220

6.3V0.1uFC2221

6.3V0.1uFC2222

6.3V1uFC2010

6.3V1uFC2011

6.3V1uFC2012

6.3V1uFC2013

6.3V1uFC2014

6.3V1uFC2015

6.3V1uFC2016

6.3V1uFC2017

6.3V0.1uFC2020

6.3V0.1uFC2021

6.3V0.1uFC2022

6.3V0.1uFC2023

6.3V0.1uFC2024

6.3V0.1uFC2025

6.3V0.1uFC2026

6.3V0.1uFC2027

6.3V10uFC 2030

6.3V1uFC2210

6.3V1uFC2211

6.3V1uFC2212

D D

1

2

6.3V1uFC2213

6.3V0.1uFC2223

6.3V0.1uFC2224

6.3V0.1uFC2225

3

+MVDD +MVDD

6.3V1uFC2410

6.3V1uFC2411

6.3V1uFC2412

6.3V1uFC2413

6.3V1uFC2414

6.3V1uFC2415

6.3V0.1uFC2226

6.3V0.1uFC2227

6.3V10uFC 2230

6.3V1uFC2416

5

6

7

8

6.3V0.1uFC2623

6.3V0.1uFC2624

6.3V0.1uFC2625

6.3V0.1uFC2626

6.3V1uFC2417

6.3V0.1uFC2420

6.3V0.1uFC2421

6.3V0.1uFC2422

6.3V0.1uFC2423

6.3V0.1uFC2424

6.3V0.1uFC2425

6.3V0.1uFC2426

6.3V0.1uFC2427

6.3V10uFC 2430

6.3V1uFC2610

6.3V1uFC2611

6.3V1uFC2612

6.3V1uFC2613

6.3V1uFC2614

6.3V1uFC2615

6.3V1uFC2616

6.3V1uFC2617

6.3V0.1uFC2627

6.3V0.1uFC2620

6.3V10uFC 2630

6.3V0.1uFC2621

6.3V0.1uFC2622

4

1

8

8

8

2

7

7

7

3

6

6

6

4

5

6

345

345

345

7

2

2

2

8

1

1

1

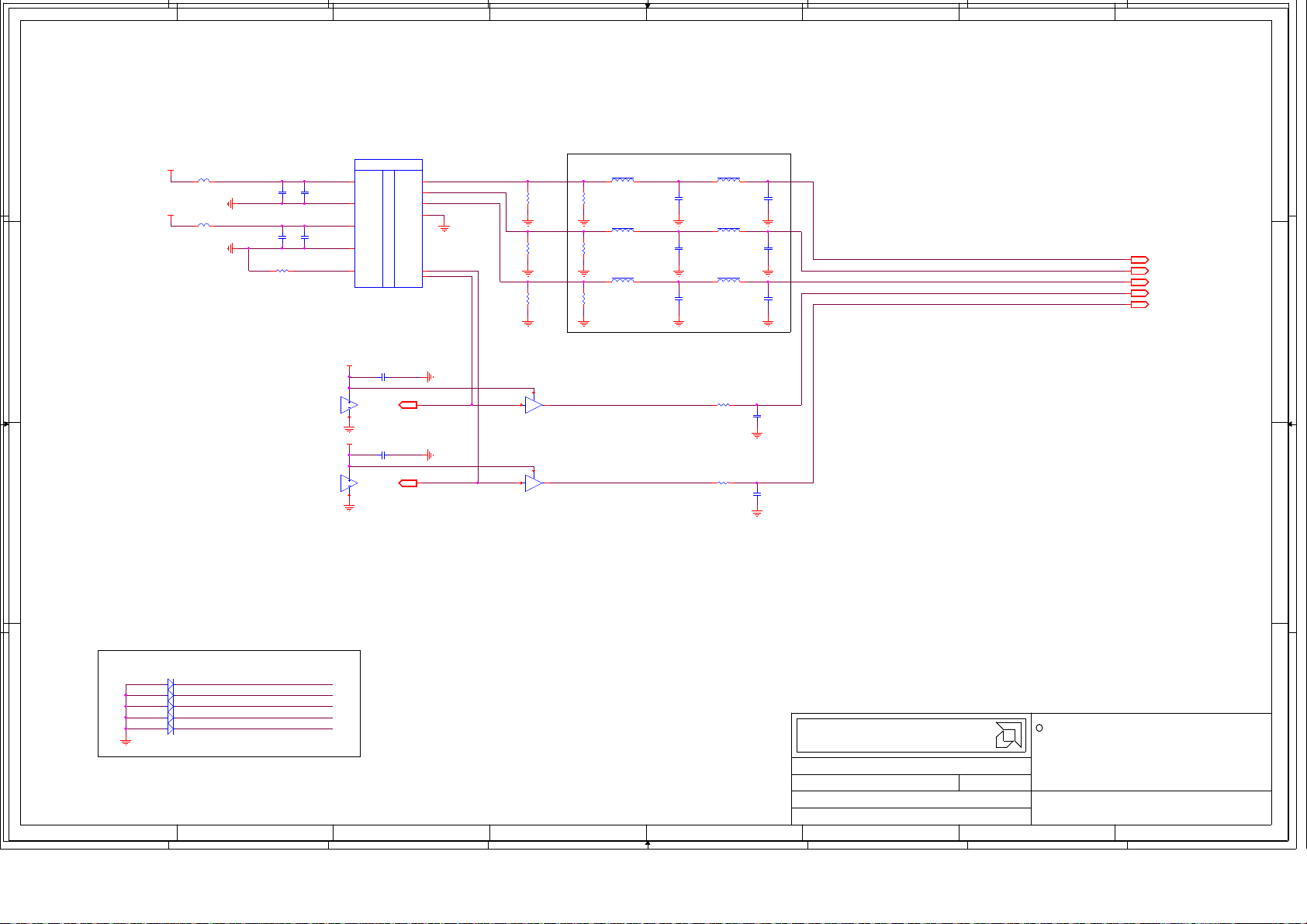

(5) TOBAGO GPIO MLPS PLL XTAL

U1E

+3.3V_BUS

+1.8V

A A

C

C

C

B B

+1.8V

SCL/SDA BUS:

I2C ADRS

R50

3.24K

1%

PS_0

R51

C50

5.62K

0.082uF

1%

16V

R54

4.53K

1%

PS_2

R55

C52

4.99K

0.68uF

1%

4V

DEVICE

AD5274 - DIGIT AL POT FOR MVDD0x5C

+1.8V

R52

8.45K

1%

PS_1

R53

C51

2K

0.082uF

1%

16V

DNI

+1.8V

R56

4.99K

1%

DNI

PS_3

C53

R57

0.68uF

4.75K

4V

1%

+1.8V

R2 1K 5%

+1.8V

17,1

OUT

1,17

BI

15,17

OUT

15,17

BI

11,15

OUT

11,15

IN

11

OUT

DNIR1 1K 5%

PS_0

PS_1

PS_2

PS_3

G_SMBCLK

G_SMBDAT

SCL

SDA

SVC

SVD

SVT

TEST_PG

BC37

BC39

BD37

C1

1uF

BD39

6.3V

AV34

AV36

AW34

C2

1uF

AW36

6.3V

BE43

BC41

BE41

BG41

AL51

AL53

BD21

BC21

BD17

BD19

BC17

BC49

BC48

BM20

BE19

BE39

BE15

BH43

BH27

BE23

BE17

BH25

BH29

BE21

C C

U1G

+1.8V

+0.95V

+1.8V

A

A

A

D D

120R

B1

120R

B2

220R

B3

1

C15

4.7uF

6.3V

8

8

8

+SPLL_PVDD

C11

C12

C10

1uF

0.1uF

4.7uF

6.3V

6.3V

6.3V

+SPLL_VDDC

C13

C14

1uF

0.1uF

6.3V

6.3V

+MPLL_PVDD

C18

C16

4.7uF

6.3V

DNI

C19

C17

1uF

0.1uF

4.7uF

6.3V

6.3V

6.3V

7

7

7

2

PART 7 OF 16

AW23

SPLL_PVDD

AV23

SPLL_PVSS

AW25

SPLL_VDDC

PLLS XTAL

AV21

MPLL_PVDD

AV20

MPLL_PVDD

SPLL_CLKTEST A

SPLL_CLKTEST B

PLL_ANALOG_IN

PLL_ANALOG_OUT

BONAIRE

XO_IN2

BH50

XO_IN2

XO_IN

BH52

XO_IN

XTALIN

BJ53

XTALIN

XTALOUT

BJ51

XTALOUT

CLKTESTA

BD15

CLKTESTB

BC15

PLL_ANALOGIN

BD23

PLL_ANALOGOUT

BC23

MAKE SURE THEY ARE ACCESSI BLE

AVOID NOISY AREA

VDDR3

VDDR3

VDDR3

VDDR3

VDD_CT

VDD_CT

VDD_CT

VDD_CT

MLPS_0

MLPS_1

MLPS_2

MLPS_3

SMBCLK

SMBDAT

SCL

SDA

GPIO_SVC

GPIO_SVD

GPIO_SVT

DDCVAGCLK

DDCVGADATA

TEST_PG

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

R24 33R 5%

R26 33R 5%

R25 33R 5%

R27 0R 5%

C30 0.1uF 6.3V

C31 0.1uF 6.3V

6

6

6

3

OPTIONAL CLOCK C HIP

KEEP THE CLOCK PATH

AS SHORT AS POSSIBLE

PART 5 OF 16

GPIO_0

GPIO_1

GPIO_2

GPIO_3

GPIO_4

GPIO_5_REGHOT_AC_BATT

GPIO_6_TACH

GPIO_7_BLON

GPIO_8_ROMSO

GPIO_9_ROMSI

GPIO_10_ROMSCK

GPIO_11

GPIO_12

GPIO_13

GPIO_14_HPD2

GPIO_15

GPIO_16

GPIO_17_THERMAL_INT

GPIO_18_HPD3

GPIO_19_CTF

GPIO_20

GPIO_21

GPIO_22_ROMCSB

GPIO_29

GPIO

GPIO_30

GENERICA

GENERICB

GENERICC

GENERICD

GENERICE_HPD 4

GENERICF_H PD5

GENERICG_HPD 6

HPD1

DIGON

VARY_BL

CLKREQB

WAKEB

NC_IDSC_AN ALOGOUT

NC_IDSC_I L0

NC_IDSC_PW M0

NC_IDSC_PW M1

NC_IDSC_C MON

NC_DSM_0

NC_DSM_1

NC_PS_4

BONAIRE

FOR SMALLER SIZ E - 502N270000G

C22 18pF 50V

CLK_100M

CLK_27M

3

1

R28

1M

1%

R30 51.1R 1%

R31 51.1R 1%

TP30

BG27

BH23

BN19

BG29

BE27

BH35

BC29

BA45

BG39

BH37

BH39

BE29

BC31

BD31

BK28

BG31

BG37

BD29

BK36

BC27

BH33

BH31

BH41

BE25

BG25

BE45

BC45

BG23

BL19

BK42

BA53

AW49

BM44

AW45

AW47

BK44

CEC

J47

AK52

G48

F47

F45

G45

F43

BG33

BG35

BC43

10

XTALOUT

5

100M_OUT

9

27M_OUT

C24 18pF 50V

4

Y2

27.000MHz

2

R29

0R

5%

C25 18pF 50V

16.2K 1%R32

DNI

GPIO_0

GPIO_2

GPIO_3

GPIO_5_VRHOTB

GPIO_6_TACH

GPIO_8_ROMSO

GPIO_9_ROMSI

GPIO_10_ROMSCK

GPIO_14_HPD2

GPIO_15

GPIO_18_HPD3

GPIO_19_CTF

GPIO_22_ROMCSB

GENERICA

GENERICG_HPD 6

HPD1

CEC

G_CLKREQB

Y1

123

4

27.000MHz

U20

SL16020DC

5

5

5

4

XTALIN

VDD_100M

VDD_27M

SS_SEL0

SS_SEL1

GND_100M

GND_27M

GND_PAD

1 2

C7

1uF

1 2

6.3V

TP1

TP2

TP3

DNIR3 221R 1%

0.1uF 6.3V DNIC8

+3.3V_BUS

120R

120R

+3.3V_BUS

R20

R21

5.1K

5.1K

5%

5%

DNI

DNI

R22

R23

5.1K

5.1K

5%

5%

DNI

DNI

+3.3V_BUS

R5

10K

5%

ROMSO

ROMSI

ROMSCK

ROMCSB

MR7 10K 5%

MR8 10K 5%

MR9 10K 5%

NS1

+VDDR4

AV38

AV39

NS2

GENLK_VSYNC

DVPCLK

DVPCNTL_0

DVPCNTL_2

AW38

AW39

BD33

BC33

BC35

BD35

BH9

BM18

BK18

BG9

BL11

BN11

VREFG

BK20

AMD - PLATFORM HARDWARE ENG

AMD - PLATFORM HARDWARE ENG

AMD - PLATFORM HARDWARE ENG

#48, No.1387, ZHANGDONG ROAD

#48, No.1387, ZHANGDONG ROAD

#48, No.1387, ZHANGDONG ROAD

SHANGHAI, CHINA 201203

SHANGHAI, CHINA 201203

SHANGHAI, CHINA 201203

TOBAGO GPIO MLPS PLL XTAL

TOBAGO GPIO MLPS PLL XTAL

TOBAGO GPIO MLPS PLL XTAL

SHEET:

SHEET:

SHEET:

Mon Nov 24 11:06:54 2014

Mon Nov 24 11:06:54 2014

Mon Nov 24 11:06:54 2014

DATE:

DATE:

DATE:

SHEET NUMBER:

SHEET NUMBER:

SHEET NUMBER:

DOCUMENT NUMBER:

DOCUMENT NUMBER:

DOCUMENT NUMBER:

+3.3V_BUS

3

2

5

6

1

+3.3V_BUS

DNI

DNI

DNI

U1F

VDDR4

VDDR4

VDDR4

VDDR4

SWAPLOCKA

SWAPLOCKB

GENLK_CLK

GENLK_VSYNC

DVPCLK

DVPCNTL_0

DVPCNTL_1

DVPCNTL_2

MVP_DVOCNTL_0

MVP_DVOCNTL_1

VREFG

5 19

5 19

5 19

105-C913xx-00B

105-C913xx-00B

105-C913xx-00B

3

3

3

VIDEO BIOS

FIRMWARE

U11

WP

SO

SI

SCK

CE

PM25LD010C-SCE

R7 10K 5%

R8 10K 5%

R9 10K 5%

PART 6 OF 16

DVP

BONAIRE

OF

OF

OF

6

VDD

HOLD

GND

+3.3V_BUS

8

7

4

PIN STRAPS

DNI

DVPDATA_0

DVPDATA_1

DVPDATA_2

DVPDATA_3

DVPDATA_4

DVPDATA_5

DVPDATA_6

DVPDATA_7

DVPDATA_8

DVPDATA_9

DVPDATA_10

DVPDATA_11

DVPDATA_12

DVPDATA_13

DVPDATA_14

DVPDATA_15

DVPDATA_16

DVPDATA_17

DVPDATA_18

DVPDATA_19

DVPDATA_20

DVPDATA_21

DVPDATA_22

DVPDATA_23

C4

0.1uF

6.3V

HSYNC

VSYNC

BH11

BG11

BH13

BG13

BH15

BG15

BH17

BG17

BH19

BG19

BH21

BG21

BM12

BK12

BN13

BL13

BM14

BK14

BN15

BL15

BM16

BK16

BN17

BL17

GENLK_VSYNC

BIOS1

BIOS

REV:

REV:

REV:

OUT

OUT

1.0

1.0

1.0

HSYNC = AUD[1], VSYNC = AUD[ 0]

[00] NO AU DIO FU NCTION

6

[01] AUDI O FOR D P ONLY

[10] AUDI O FOR D P AND H DMI IF DONGLE IS DETECTED

[11] AUDI O FOR BOTH DP AND HDMI

6

HDMI MUST ONLY BE ENABLED ON SYSTEMS THAT ARE LEGALLY

ENTITLED. IT IS THE RESPONSIBI LITY OF THE SYSTEM DESIGN ERS

TO SUPPORT THIS FEATUR E.

CEC_DIS

CONFIDENTIAL AND PROPRIETARY TO ADVANCED MICRO DEVICES INC.