Mitac 8050qma Service Manual

SERVICE MANUAL FOR

SERVICE MANUAL FOR

SERVICE MANUAL FOR

8050QMA

8050QMA

8050QMA

BY: ZX Xiao

Repair Technology Research Department /EDVD

Repair Technology Research Department /EDVD

Jun.2005 / R01

Contents

80

50QMA

80

50QMA

N/B Maintenance

N/B Maintenance

1. Hardware Engineering Specification ………………………………………………………………………

1.1 Introduction ………………………………………………………………………………………………………………..

1.2 System Hardware Parts …………………………………………………………………………………………………...

1.3 Other Functions ……………………………………………………………………………………………………………

1.4 Power Management ……………………………………………………………………………………………………….

1.5 Appendix 1 : Intel ICH6-M GPIO Definitions ………………………………………………………………………….

1.6 Appendix 2 : W83L950D KBC Pins Definitions …………………………………………………………………………

1.7 Appendix 3 : 8050QMA Product Spec ……………………………………………………………………………….. …

2. System View and Disassembly ……………………………………………………………………………...

2.1 System View ………………………………………………………………………………………………………………..

2.2 Tools Introduction …………………………………………………………………………………………………..…….

2.3 System Disassembly ………………………………………………………………………………………………………..

MiTac Secret

3. Definition & Location of Connectors / Switches …………………………………………………………..

4

4

7

32

39

42

44

46

49

49

52

53

74

3.1 Mother Board (Side A) ……………………………………………………………………………………………………

3.2 Mother Board (Side B) ……………………………………………………………………………………………………

Confidential Document

4. Definition & Location of Major Components ……………………………………………………………..

4.1 Mother Board (Side A) ……………………………………………………………………………………………………

4.2 Mother Board (Side B) ……………………………………………………………………………………………………

74

75

76

76

77

1

Contents

80

50QMA

80

50QMA

N/B Maintenance

N/B Maintenance

5. Pin Description of Major Component …….……………………………………………………………….

5.1 Intel 915PM North Bridge ……………………………………………………………………………………………….

5.2 Intel ICH6-M South Bridge ………………………………………………………………………………………………

6. System Block Diagram ………………………………………………………………………………………

7. Maintenance Diagnostics ……………………………………………………………………………………

7.1 Introduction ………………………………………………………………………………………………………………..

7.2 Maintenance Diagnostics…………………………………………………………………………………………………..

7.3 Error Codes ………………………………………………………………………………………………………………..

8. Trouble Shooting …………………………………………………………………………………………….

8.1 No Power ……………………………………………………………………………………………………………………

8.2 No Display ………………………………………………………………………………………………………………….

8.3 VGA Controller Failure LCD No Display ………………………………………………………………………………..

8.4 External Monitor No Display ……………………………………………………………………………………………..

8.5 Memory Test Error ………………………………………………………………………………………………………..

8.6 Keyboard (K/B) Touch-Pad (T/P) Test Error ……………………………………………………………………………

8.7 Hard Drive Test Error ……………………………………………………………………………………………………

Confidential Document

MiTac Secret

78

78

88

98

99

99

100

101

103

105

112

115

117

119

121

123

8.8 CD-ROM Drive Test Error ………………………………………………………………………………………………

8.9 USB Port Test Error ……………………………………………………………………………………………………….

8.10 Audio Failure ……………………………………………………………………………………………………………..

8.11 LAN Test Error …………………………………………………………………………………………………………..

125

127

129

132

2

Contents

80

50QMA

80

50QMA

N/B Maintenance

N/B Maintenance

8.12 PC Card Socket Failure …………………………………………………………………………………………………

9. Spare Parts List ……………………………………………………………………………… ……………...

10. Reference Material …...…………………………………………………………………………………….

MiTac Secret

134

136

150

Confidential Document

3

80

50QMA

80

50QMA

N/B Maintenance

N/B Maintenance

1. Hardware Engineering Specification

1.1 Introduction

1.1.1 General Description

This document describes the brief introduction for MiTAC 8050QMA portable notebook computer system.

1.1.2 System Overview

The MiTAC 8050Q model is designed for Intel Dothan processor with 533MHz FSB with Micro-FCPGA package.

This system is based on PCI architecture and is fully compatible with IBM PC/AT specification, which has

standard hardware peripheral interface. The power management complies with Advanced Configuration and Power

Interface. It also provides easy configuration through CMOS setup, which is built in system BIOS software and can

be pop-up by pressing F2 key at system start up or warm reset. System also provides icon LEDs to display system

status, such as AC Power indicator, Battery Power indicator, Battery status indicator, HDD,CD-ROM, NUM

LOCK, CAP LOCK, SCROLL LOCK, Wireless on/off Card Reader Accessing. It also equipped with LAN, 56K

Fax MODEM, 4 USB port, S-Video and audio line in/out , external microphone function.

The memory subsystem supports DDR or DDR2 SDRAM channels (64-bits wide).

The 915PM MCH Host Memory Controller integrates a high performance host interface for Intel Dothan processor,

a high performance PCI Express interface, a high performance memory controller and Direct Media Interface

Confidential Document

MiTac Secret

4

80

50QMA

80

50QMA

(DMI) connecting with Intel ICH6-M.

The Intel ICH6-M integrates three Universal Serial Bus 2.0 Host Controllers Interface (UHCI), the Audio

Controller with AC97 interface, the Ethernet includes a 32-bit PCI controller, the IDE Master/Slave controllers, the

SATA controller and Direct Media Interface technology.

The Realtek RTL8100CL is a highly integrated, cost-effective single-chip Fast Ethernet controller that provides 32-

bit performance, PCI bus master capability, and full compliance with IEEE 802.3u 100Base-T specifications and

IEEE 802.3x Full Duplex Flow Control. It also supports the Advanced Configuration Power management Interface

(ACPI).

The VT6301S is a single chip PCI Host Controller for IEEE 1394-1995 Release 1.0 and IEEE 1394a P2000. It

implements the Link and PHY layers for IEEE 1394-1995 High Performance Serial Bus specification release 1.0

N/B Maintenance

N/B Maintenance

and 1394a P2000. It is compliant with 1394 Open HCI 1.0 and 1.1 with DMA engine support for high performance

data transfer via a 32-bit bus master PCI host bus interface. The VT6301S supports 100, 200 and 400 Mbit/sec

MiTac Secret

transmission via an integrated 1-port PHY. The VT6301S services two types of data packets: asynchronous and

isochronous (real time). The 1394 link core performs arbitration requesting, packet generation and checking, and

bus cycle master operations. It also has root node capability and performs retry operations.

The ENE CB712 CardBus/Media Reader controller functions as a single slot PCI to Cardbus bridge and also PCI

interface MS/SD/MMC flash card reader. The CB712 provide one Cardbus slot and all reader interface may

operate simultaneously.

The W83L950D is a high performance microcontroller on-chip supporting functions optimized for embedded

control. These include ROM, RAM, four types of timers, a serial communication interface, optional I²C bus

interface, host interface, A/D converter, D/A converter, I/O ports and other functions needed in control system

Confidential Document

5

80

50QMA

80

50QMA

configurations, so that compact, high performance systems can be implemented easily.

A full set of software drivers and utilities are available to allow advanced operating systems such as Windows ME,

Windows 2000 and Windows XP to take full advantage of the hardware capabilities. Features such as bus mastering

IDE, Plug and Play, Advanced Power Management (APM) with application restart, software-controlled power

shutdown.

Following chapters will have more detail description for each individual sub-systems and functions.

N/B Maintenance

N/B Maintenance

MiTac Secret

Confidential Document

6

80

50QMA

80

50QMA

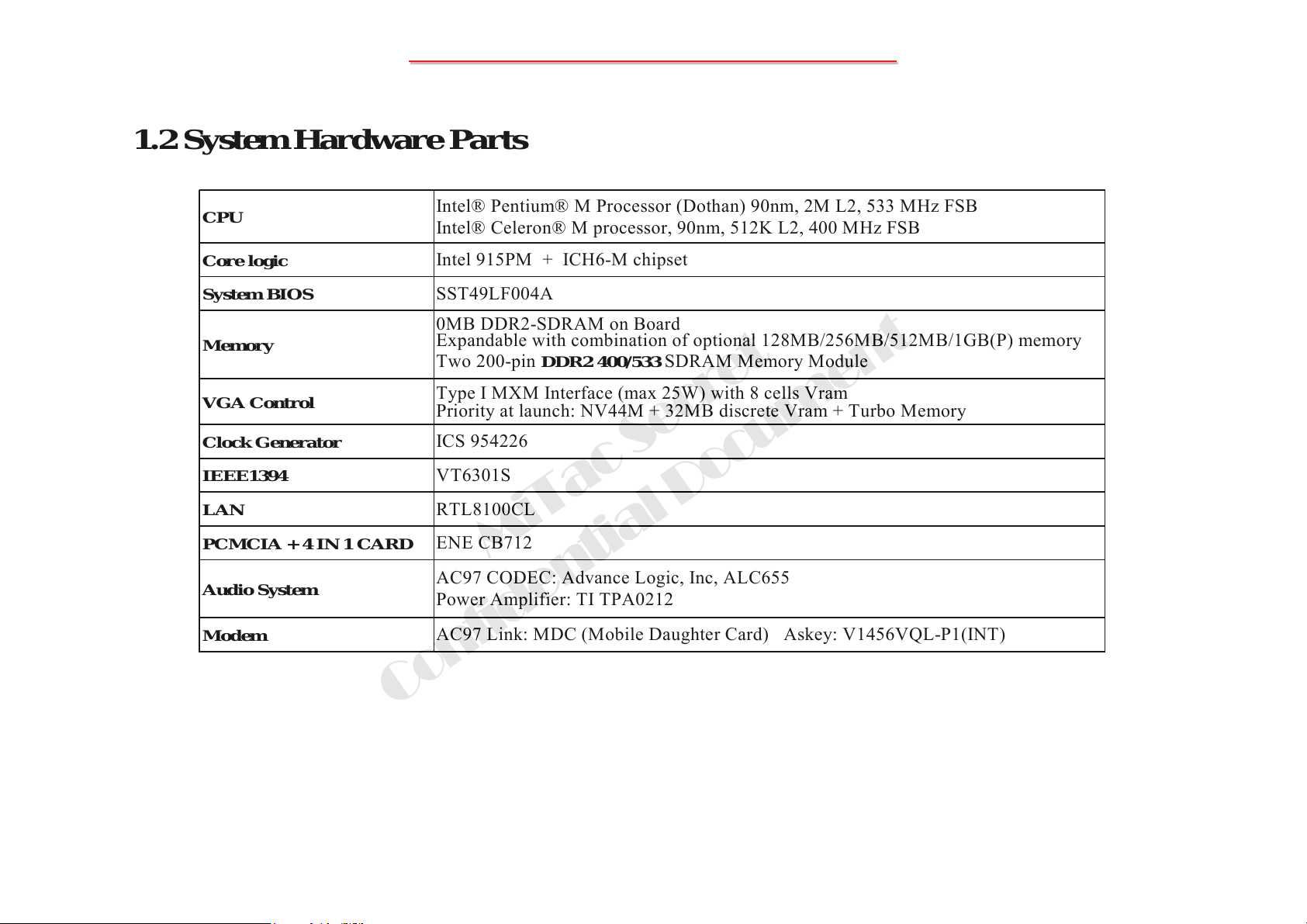

1.2 System Hardware Parts

N/B Maintenance

N/B Maintenance

CPU

Core logic

System BIO S

Memory

VGA Control

Clock Generator

IEEE1394

LAN

PCMCIA + 4 IN 1 CARD

Audio System

Modem

Intel® Pentium® M Processor (Dothan) 90nm, 2M L2, 533 MHz FSB

Intel® Celeron® M processor, 90nm, 512K L2, 400 MHz FSB

Intel 915PM + ICH6-M chipset

SST49LF004A

0MB DDR2-SDRAM on Board

Expandable with combination of optional 128MB/256MB/512MB/1GB(P) memory

Two 200-pin DDR2 400/533 SDRAM Memory Module

Type I MXM Interface (max 25W) with 8 cells Vram

Priority at launch: NV44M + 32MB discrete Vram + Turbo Memory

ICS 954226

VT6301S

RTL8100CL

ENE CB712

AC97 CODEC: Advance Logic, Inc, ALC655

Power Amplifier: TI TPA0212

AC97 Link: MDC (Mobile Daughter Card) Askey: V1456VQL-P1(INT)

MiTac Secret

Confidential Document

7

80

50QMA

80

50QMA

N/B Maintenance

N/B Maintenance

1.2.1 Intel Dothan Processors in Micro-FCBGA Package

Intel Dothan Processors with 479 pins Micro-FCBGA package.

It will be manufactured on Intel’s advanced 90 nanometer process technology with copper interconnect. It’s features

include Intel Architecture with Dynamic Execution, On-die primary 32-kB instruction cache and 32-kB write-back

data cache, on-die 2-MB second level cache with advanced Transfer Cache Architecture, Data Prefetch Logic,

Streaming SIMD Extensions 2 (SSE2), 533-MHz FSB.

The Streaming SIMD Extensions 2 (SSE2) enable break-through levels of performance in multimedia applications

including 3-D graphics, video decoding/encoding, and speech recognition.

Use Source-Synchronous Transfer (SST) of address and data to improve performance by transferring data four times

per bus clock.

Support Enhanced Intel SpeedStep technology, which enables real-time dynamic switching of the voltage and

frequency between two performance modes.

MiTac Secret

1.2.2 Clock Generator

Confidential Document

System frequency synthesizer: ICS954226 is a CK410M Compliant clock synthesizer. It provides a single-chip

solution for mobile systems built with Intel P4-M processors and Intel mobile chipsets. It is driven with a

14.318MHz crystal and generates CPU outputs up to 400MHz. It provides the tight ppm accuracy required by

Serial ATA and PCI-Express.

8

80

50QMA

80

50QMA

• Supports tight ppm accuracy clocks for Serial-ATA and SRC.

• Supports spread spectrum modulation, 0 to –0.5% down spread.

• Uses external 14.318MHz crystal, external crystal load caps are required for frequency tuning.

• Supports undriven differential CPU, SRC pair in PD# for power management.

N/B Maintenance

N/B Maintenance

1.2.3 The Mobile Intel 915PM Express Chipset

The Mobile Intel 915PM Express Chipset integras a memory controller hub (MCH) designed for use with the

Dothan, Yonah and Intel Celeron M Processor. It is PCI Express based Graphics.

The 915PM MCH integrates a system memory DDR/DDR2 controller with two, 64-bit wide interfaces. Only

Double Data Rate (DDR/DDR2) memory is supported; the buffers support DDR SSTL_2 and DDR2 SSTL_18

signaling interfaces. The memory controller interface is fully configurable through a set of control registers. It

integras a high performance transition interface PCI Express Interface. PCI Express operates at a data rate of 2.5

for 8050QMA project. GB/s. This allows a maximum theoretical bandwidth of 40 GB/s each direction. The 915PM

MCH integrates Direct media interface (DMI) chip-to-chip interconnect between the MCH and ICH6-M. DMI

supports DMI x2 and DMI x4 configuration.

Features:

Processor/FSB Support

Confidential Document

MiTac Secret

9

80

50QMA

80

50QMA

N/B Maintenance

N/B Maintenance

• Intel

• AGTL+ bus driver technology with integrated GTL termination resistors (gated AGTL+ receivers for reduced

• Supports 32-bit AGTL+ host bus addressing

• Supports system bus at 533MT/s (533 MHz) and 400MT/s (400 MHz)

• 2X Address, 4X data

• Host bus dynamic bus inversion HDINV support

• 12 deep, in-order queue

Memory System

®

power)

Dothan processor

MiTac Secret

• Directly supports to two DDR or DDR2 SDRAM channels, 64-bts wide.

• Supports SO-DIMMs of the same type (e.g.,all DDR or all DDR2), not mixed.

• Maximum of two, double-sided unbuffered SO-DIMMs (4 rows populated)

• Minimum amount of memory supported is 128 MB (16 MB x 16-b x 4 devices x 1 rows = 128 MB) using

256-MB technology

• Maximum amount of memory supported is 2 GB using 1-GB technology.

Confidential Document

10

80

50QMA

80

50QMA

• 256-MB, 512-MB and 1-GB technology using x8 and x16 devices.

• Three memory channel organizations are supported for DDR / DDR2 :

– Single channel

– Dual channel interleaved

– Dual channel asymmetric

• Supports DDR 333 devices and DDR2 400 /533 devices

– Supports on-die termination (ODT) for DDR2

• Supports Fast Chip Select mode

N/B Maintenance

N/B Maintenance

• Supports partial write to memory using Data Mask signal (DM)

• Supports high-density memory package for DDR or DDR2 type devices

PCI Express Interface

• One x16 (16 lanes) PCI Express port intended for graphics attach

MiTac Secret

Confidential Document

• Maximum theoretical realized bandwidth on interface of 4 GB/s in each direction simultaneously, for an

average of 8 GB/s when x16

• Automatic discovery, negotiation and training of link out of reset

• Supports traditional PCI style traffic (asynchronous snooped, PCI ordering)

11

80

50QMA

80

50QMA

• Supports only 1.5-V AGP electrics

• 32 deep AGP request queue

• Hierarchical PCI-compliant configuration mechanism for downstream devices

• Direct Media Interface (DMI)

– Chip-to-chip interconnect between the GMCH and ICH6-M

– DMI x2 and DMI x4 configuration supported

– Bit swapping is supported

– Lane reversal is not supported

N/B Maintenance

N/B Maintenance

1.2.4 I/O Controller Hub : Intel ICH6-M

The ICH6 provides extensive I/O support. Functions and capabilities include:

• PCI Express Base Specification, Revision 1.0a-compliant

MiTac Secret

Confidential Document

• PCI Local Bus Specification, Revision 2.3-compliant with support for 33 MHz PCI operations(supports up to

seven Req/Gnt pairs)

• ACPI Power Management Logic Support

• Enhanced DMA controller, interrupt controller and timer functions

12

80

50QMA

80

50QMA

• Integrated Serial ATA host controller with independent DMA operation on two ports and AHCI support

• Integrated IDE controller supports Ultra ATA100/66/33

• USB host interface with support for three USB ports; three UHCI host controllers; one EHCI high-speed

USB2.0 Host controller

• Integrated LAN controller

N/B Maintenance

N/B Maintenance

• System Management Bus (SMBus) Specification, Version 2.0 with additional support for I

• Supports Audio Codec ’97, Revision 2.3 Specification (a.k.a.,AC ’97 Component Specification, Revision 2.3)

which provides a link for Audio and Telephony codecs (up to 7 channels)

• Supports Intel High Definition Audio

• Low Pin Count (LPC) interface

• Firmware Hub (FWH) interface support

Confidential Document

1.2.5 CardBus: CB712

Features:

MiTac Secret

2

C devices

3.3V operation with 5V tolerant

LFBGA 169-ball package

13

80

50QMA

80

50QMA

Pin out Compatible with CB1410

• PCI Interface

– Compliant with PCI Local Bus Specification Revision 2.3

– Compliant with PCI Bus Power Management Interface Specification Revision 1.1

– Compliant with PCI Mobile Design Guide Version 1.1

– Compliant with Advanced Configuration and Power Interface Specification Revision 1.0

• CardBus Interface

– Compliant with PC Card Standard 8.0

– Support Standardized Zoomed Video Register Model

N/B Maintenance

N/B Maintenance

– Support SPKROUT CAUDIO and RIOUT#

MiTac Secret

• Secure Digital Interface

– Compliant with SD Host Controller Standard Specification Version 1.0

– Support SD Suspend/Resume Functionality

– Support DMA Mode to Minimize CPU Overhead

– Support High Speed with the SD Clock Frequency Up to 50Mhz

– Contain two 512-byte buffer to maximize the transfer speed

– Support Traffic LED Light

– Support Over Current Protection

Confidential Document

14

80

50QMA

80

50QMA

• Memory Stick Interface

– Compliant with Memory Stick PRO Format Specification Version 1.0

– Support 4-bit Parallel Data Transfer Mode

– Memory Stick Clock Frequency Up to 40Mhz

– Support DMA Mode to Minimize CPU Overhead

– Support Traffic LED Light

– Support Over Current Protection

• Interrupt Configuration

– Support Parallel PCI Interrupts

N/B Maintenance

N/B Maintenance

– Support Parallel IRQ and Parallel PCI Interrupts

– Support Serialized IRQ and Parallel PCI Interrupts

– Support Serialized IRQ and PCI Interrupts

• Power Management Control Logic

– Support CLKRUN# protocol

– Support SUSPEND#

– Support PCI PME# from D3, D2, D1 and D0

– Support PCI PME# from D3cold

• Support Zoomed Video port

Confidential Document

MiTac Secret

15

80

50QMA

80

50QMA

• Support parallel 4-wire power switch interface

N/B Maintenance

N/B Maintenance

1.2.6 AC’97 Audio System: Advance Logic, Inc, ALC655

The ALC655 is a 16-bit, full duplex AC'97 2.3 compatible six channels audio CODEC designed for PC multimedia

systems, including host/soft audio and AMR/CNR based designs. The ALC655 incorporates proprietary converter

technology to meet performance requirements on PC99/2001 systems. The ALC655 CODEC provides three pairs of

stereo outputs with 5-Bitvolume controls, a mono output, and multiple stereo and mono inputs, along with flexible

mixing, gain and mute functions to provide a complete integrated audio solution for PCs. The digital interface

circuitry of the ALC655 CODEC operates from a 3.3V power supply for use in notebook and PC applications. The

ALC655 integrates 50mW/20ohm headset audio amplifiers at

Front-Out and Surr-Out, built-in 14.318M 24.576MHz PLL and PCBEEP generator, those can save BOM costs. The

ALC655 also supports the S/PDIF input and output function, which can offer easy connection of PCs to consumer

electronic products, such as AC3 decoder/speaker and mini disk devices. ALC655 supports host/soft audio from Intel

ICH6 chipsets as well as audio controller based VIA/SIS/ALI/AMD/nVIDIA/ATI chipset. Bundled Windows series

drivers (WinXP/ME/2000/98/NT), EAX/

Direct Sound 3D/ I3DL2/ A3D compatible sound effect utilities (supporting Karaoke, 26-kind of environment sound

emulation,10-band equalizer), HRTF 3D positional audio and Sensaura™ 3D (optional) provide an excellent

entertainment package and game experience for PC users. Besides, ALC655 includes Realtek’s impedance sensing

techniques that makes device load on outputs and inputs can be detected.

Confidential Document

MiTac Secret

16

80

50QMA

80

50QMA

• Meets performance requirements for audio on PC99/2001 systems

• Meets Microsoft WHQL/WLP 2.0 audio requirements

• 16-bit Stereo full-duplex CODEC with 48KHz sampling rate

• Compliant with AC’97 2.3 specifications

– 14.318MHz- 24.576MHz PLL to save crystal

– 12.288MHz BITCLK input can be consumed

– Integrated PCBEEP generator to save buzzer

– Interrupt capability

N/B Maintenance

N/B Maintenance

• Three analog line-level stereo inputs with 5-bit volume control: LINE_IN, CD, AUX

• High quality differential CD input

• Two analog line-level mono input: PCBEEP,PHONE-IN

• Two software selectable MIC inputs applications (software selectable)

MiTac Secret

Confidential Document

• Boost preamplifier for MIC input 50mW/20 amplifier

• External Amplifier Power Down (EAPD) capability

• Power management and enhanced power saving features

17

80

50QMA

80

50QMA

• Stereo MIC record for AEC/BF application

• Supports Power Off CD function

• Adjustable VREFOUT control Supports double sampling rate (96KHz) of DVD audio playback

• Support 48KHz of S/PDIF output is compliant with AC’97 rev2.3 specification

• Power support: Digital: 3.3V; Analog: 3.3V/5V

N/B Maintenance

N/B Maintenance

1.2.7 MDC: Pctel Modem Daughter Card PCT2303W (Askey V1456VQL-P1)

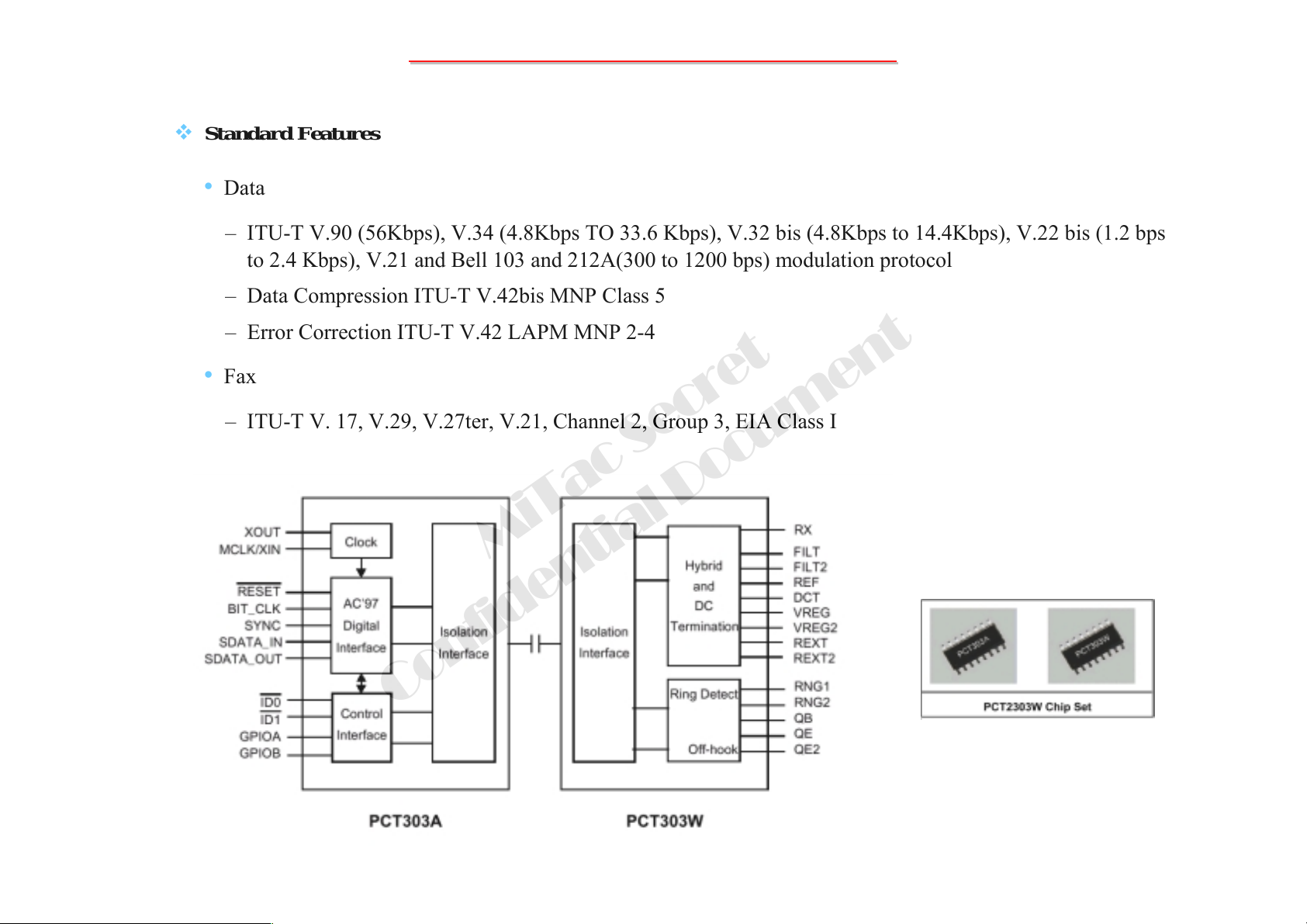

The PCT2303W chipset is designed to meet the demand of this emerging worldwide AMR/MDC market. The

combination of PC-TEL’s well proven PCT2303W chipset and the HSP56TM MR software modem driver allows

systems manufactures to implement modem functions in PCs at a lower bill of materials (BOM) while maintaining

higher system performance.

PC-TEL has streamlined the traditional modem into the Host Signal Processing (HSP) solution. Operating with the

Pentium class processors, HSP becomes part of the host computer’s system software. It requires less power to

MiTac Secret

Confidential Document

operate and less physical space than standard modem solutions. PC-TEL’s HSP modem is an easily integrated, cost-

effective communications solution that is flexible enough to carry you into the future.

The PCT2303W chip set is an integrated direct access arrangement (DAA) and Codec that provides a programmable

line interface to meet international telephone line requirements. The PCT2303W chip set is available in two 16-pin

18

80

50QMA

80

50QMA

small outline packages (AC’97 interface on PCT303A and phone-line interface on PCT303W). The chip set

eliminates the need for an AFE, an isolation transformer, relays, opto-isolators, and 2-to 4-wire hybrid. The

PCT2303W chip set dramatically reduces the number of discrete components and cost required to achieve

compliance with international regulatory requirements. The PCT2303W complies with AC’97 Interface specification

Rev. 2.1.

The chip set is fully programmable to meet world-wide telephone line interface requirements including those

described by CTR21, NET4, JATE, FCC, and various country-specific PTT specifications. The programmable

parameters of the PCT2303W chip set include AC termination, DC termination, ringer impedance, and ringer

threshold. The PCT2303W chip set has been designed to meet stringent world-wide requirements for out-of-band

energy, billing-tone immunity, lightning surges, and safety requirements.

N/B Maintenance

N/B Maintenance

Features:

Virtual com port with a DTE throughout up to 460.8Kbps.

G3 Fax compatible

Auto dial and auto answer

Ring detection

MiTac Secret

Confidential Document

Codec/DAA Features

• AC97 2.1 compliant

• 86dB dynamic range TX/RX paths

19

80

50QMA

80

50QMA

• 2-4-wire hybrid

• Integrated ring detector

• High voltage isolation of 4000V

• Support for “Caller ID”

• Compliant with FCC Part68, CTR21, Net4 and JATE

• Low power standby

• Low profile SOIC package 16 pins 10x3x1.55mm

N/B Maintenance

N/B Maintenance

• Low power consumption

• 10mA @ 3.3V operation

• 1mA @ 3.3V power down

• Integrated modem codec

Confidential Document

MiTac Secret

20

Standard Features

• Data

– ITU-T V.90 (56Kbps), V.34 (4.8Kbps TO 33.6 Kbps), V.32 bis (4.8Kbps to 14.4Kbps), V.22 bis (1.2 bps

to 2.4 Kbps), V.21 and Bell 103 and 212A(300 to 1200 bps) modulation protocol

– Data Compression ITU-T V.42bis MNP Class 5

– Error Correction ITU-T V.42 LAPM MNP 2-4

• Fax

– ITU-T V. 17, V.29, V.27ter, V.21, Channel 2, Group 3, EIA Class I

80

50QMA

80

50QMA

N/B Maintenance

N/B Maintenance

MiTac Secret

Confidential Document

21

80

50QMA

80

50QMA

1.2.8 IEEE1394 VT6301S

1.2.8.1 Overview

The VT6301S IEEE 1394 OHCI Host Controller provides high performance serial connectivity. It implements

the Link and Phy layers for IEEE 1394-1995 High Performance Serial Bus specification release 1.0 and 1394a-

2000. It is compliant with 1394 Open HCI 1.0 and 1.1 with DMA engine support for high performance data

transfer via a 32-bit bus master PCI host bus interface. The VT6301S supports 100, 200 and 400 Mbit/sec

transmission via an integrated 1-port PHY. The VT6301S services two types of data packets: asynchronous and

isochronous (real time). The 1394 link core performs arbitration requesting, packet generation and checking,

and bus cycle master operations. It also has root node capability and performs retry operations. The VT6301S is

ready to provide industry-standard IEEE 1394 peripheral connections for desktop and mobile PC platforms.

N/B Maintenance

N/B Maintenance

Support for the VT6301S is built into Microsoft Windows 98, Windows ME, Windows 2000 and Windows XP

MiTac Secret

1.2.8.2 Features

•

32 bit CRC generator and checker for receive and transmit data

• On-chip isochronous and asynchronous receive and transmit FIFOs for packets (2K for general

receive plus 2K for isochronous transmit plus 2K for asynchronous transmit)

• 8 isochronous transmit contexts

• 4 isochronous receive contexts

Confidential Document

22

80

50QMA

80

50QMA

• 3-deep physical post-write queue

• 2-deep physical response queue

• Dual buffer mode enhancements

• Skip Processing enhancements

• Block Read Request handling

• Ack_tardy processing

N/B Maintenance

N/B Maintenance

1.2.9 System Flash Memory (BIOS)

Firmware Hub for Intel® 810, 810E, 815, 815E,815EP, 820, 840, 850 Chipsets

Flexible Erase Capability

– Uniform 4 KByte Sectors

– Uniform 16 KByte overlay blocks for SST49LF002A

– Uniform 64 KByte overlay blocks for SST49LF004A

– Top boot block protection

– 16 KByte for SST49LF002A

– 64 KByte for SST49LF004A

Confidential Document

MiTac Secret

23

80

50QMA

80

50QMA

– Chip-Erase for PP Mode

Single 3.0-3.6V Read and Write Operations

Superior Reliability

Firmware Hub Hardware Interface Mode Supports Intel High Definition Audio

– 5-signal communication interface supporting byte Read and Write

– 33 MHz clock frequency operation

– WP# and TBL# pins provide hardware write protect for entire chip and/or top Boot Block

– Block Locking Register for all blocks

– Standard SDP Command Set

N/B Maintenance

N/B Maintenance

– Data# Polling and Toggle Bit for End-of-Write detection

– 5 GPI pins for system design flexibility

– 4 ID pins for multi-chip selection

1.2.10 Memory System

1.2.10.1 256MB, 512MB, 1GB (x64) 200-Pin DDR2 SDRAM SODIMMs

•

JEDEC-standard 200-pin, small-outline, dual in-line memory module (SODIMM)

• VDD=+1.8V±0.1V, VDDQ=+1.8V±0.1V

Confidential Document

MiTac Secret

24

80

50QMA

80

50QMA

• JEDEC standard 1.8V I/O (SSTL_18-compatible)

• Differential data strobe (DQS,DQS#) option

• Four-bit prefetch architecture

• Differential clock input (CK,CK#)

• Command entered on each rising CK edge

• DQS edge-aligned with data for Reads

• DQS center-aligned with data for Writes

N/B Maintenance

N/B Maintenance

• Duplicate output strobe (RDQS) option for x8 configuration

• DLL to align DQ and DQS transitions with CK

• Four internal banks for concurrent operation

• Data mask (DM) for masking write data

MiTac Secret

Confidential Document

• Programmable CAS Latency (CL) : 2,3,4 and 5

• Posted CAS additive latency (AL) : 0,1,2,3 and 4

• Write latency = Read latency – 1

t

CK

25

80

50QMA

80

50QMA

• Programmable burst lengths : 4 or 8

• Read burst interrupt supported by another READ

• Write burst interrupt supported by another WRITE

• Adjustable data – output drive strength

• Concurrent auto precharge option is supported

• Auto Refresh (CBS) and Self Refresh Mode

• 64ms, 8,192-cycle refresh

N/B Maintenance

N/B Maintenance

• Off-chip drive (OCD) impedance calibration

• On-die termination (ODT)

1.2.11 LAN PHY: RTL8100C(L)

General

The Realtek RTL8100C(L) is a highly integrated, cost-effective single-chip Fast Ethernet controller that provides 32-

bit performance, PCI bus master capability, and full compliance with IEEE 802.3u 100Base-T specifications and

IEEE 802.3x Full Duplex Flow Control. It also supports the Advanced Configuration Power management Interface

(ACPI), PCI power management for modern operating systems that are capable of Operating System Directed Power

Confidential Document

MiTac Secret

26

80

50QMA

80

50QMA

Management (OSPM) to achieve the most efficient power management possible. The RTL8100C(L) does not

support CardBus mode as the RTL8139C does. In addition to the ACPI feature, the RTL8100C(L) also supports

remote wake-up (including AMD Magic Packet, LinkChg, and Microsoft® wake-up frame) in both ACPI and APM

environments. The RTL8100C(L) is capable of performing an internal reset through the application of auxiliary

power. When auxiliary power is applied and the main power remains off, the RTL8100C(L) is ready and waiting for

the Magic Packet or Link Change to wake the system up. Also, the LWAKE pin provides 4 different output signals

including active high, active low, positive pulse, and negative pulse. The versatility of the RTL8100C(L) LWAKE

pin provides motherboards with Wake-On-LAN (WOL) functionality. The RTL8100C(L) also supports Analog

Auto-Power-down, that is, the analog part of the RTL8100C(L) can be shut down temporarily according to

user requirements or when the RTL8100C(L) is in a power down state with the wakeup function disabled. In

addition, when the analog part is shut down and the IsolateB pin is low (i.e. the main power is off), then both the

analog and digital parts stop functioning and the power consumption of the RTL8100C(L) will be negligible.

The RTL8100C(L) also supports an auxiliary power auto-detect function and will auto-configure related bits

N/B Maintenance

N/B Maintenance

of their own PCI power management registers in PCI configuration space.

MiTac Secret

• 128 pin QFP/LQFP

• Integrated Fast Ethernet MAC, Physical chip and transceiver in one chip

• 10 Mb/s and 100 Mb/s operation

• Supports 10 Mb/s and 100 Mb/s N-way Auto-negotiation operation

• PCI local bus single-chip Fast Ethernet controller

1. Compliant to PCI Revision 2.2

Confidential Document

27

80

50QMA

80

50QMA

2. Supports PCI clock 16.75MHz-40MHz

3. Supports PCI target fast back-to-back transaction

4. Provides PCI bus master data transfers and PCI memory space or I/O space mapped data transfers of

RTL8100C(L)'s operational registers

5. Supports PCI VPD (Vital Product Data)

6. Supports ACPI, PCI power management

• Supports 25MHz crystal or 25MHz OSC as the internal clock source. The frequency deviation of either crystal

or OSC must be within 50 PPM.

• Compliant to PC99/PC2001 standard

• Supports Wake-On-LAN function and remote wake-up (Magic Packet*, LinkChg and Microsoft® wake-up

N/B Maintenance

N/B Maintenance

frame)

MiTac Secret

• Supports 4 Wake-On-LAN (WOL) signals (active high, active low, positive pulse and negative pulse)

• Supports auxiliary power-on internal reset, to be ready for remote wake-up when main power still remains off

• Supports auxiliary power auto-detect, and sets the related capability of power management registers in PCI

configuration space

• Includes a programmable, PCI burst size and early Tx/Rx threshold

• Supports a 32-bit general-purpose timer with the external PCI clock as clock source, to generate timer-interrupt

• Contains two large (2Kbyte) independent receive and transmit FIFOs

Confidential Document

28

80

50QMA

80

50QMA

• Advanced power saving mode when LAN function or wakeup function is not used

• Uses 93C46 (64*16-bit EEPROM) to store resource configuration, ID parameter and VPD data

• Supports LED pins for various network activity indications

• Supports loop back capability

• Half/Full duplex capability

• Supports Full Duplex Flow Control (IEEE 802.3x)

N/B Maintenance

N/B Maintenance

1.2.12 Keyboard System: Winbond W83L950D

The Winbond Keyboard controller architecture consists of a Turbo 51 core controller surrounded by various registers,

nine general purpose I/O port, 2k+256 bytes of RAM, four timer/counters, dual serial ports, 40K MTP-ROM that is

divided into four banks, two SMBus interface for master and slave, Support 4 PWM channels, 2 D-A and 8 A-D

converters.

• 8051 uC based

• Keyboard Controller Embedded Controller

• Supply embedded programmable flash memory (internal ROM size: 40KB) and RAM size is 2 KB

• Support 4 Timer (8 bit) signal with 3 prescalers

Confidential Document

MiTac Secret

29

Loading...

Loading...