Mitac 8050d Service Manual

SERVICE MANUAL FOR

SERVICE MANUAL FOR

SERVICE MANUAL FOR

8050D

8050D

8050D8050D

8050D

8050D

8050D8050D

8050D

8050D

8050D8050D

BY:

Repair Technology Research Department /EDVD

Repair Technology Research Department /EDVD

Grass

Grass

Mar.2004

.Ren

.Ren

Contents

8050

8050

D N/B Maintenance

D N/B Maintenance

1. Hardware Engineering Specification …………………………………………………………………..

1.1 Introduce

1.2 System Overview ……………………………………………………………………………………….

1.3 System Hardware Parts …………………………………………………………………………………

1.4 Other Functions …………………………………………………………………………………….….

1.5 Power Management …………………………………………………………………………………….

………………………………………………………………………………………………

2. System View & Disassembly …………………………………………………………………………..

2.1 System View …………………………………………………………………………………………..

2.2 System Disassembly …………………………………………………………………………………….

3. Definition & Location of Connectors / Switches Setting ………………………………………………

4. Definition & Location of Major Component …………………………………………………………..

MiTac Secret

5. Pin Description of Major Component…………………………………………………………………..

5.1 Intel Pentium M (Banias) Processor ……………………………………………………………………..

5.2 Intel 855GM/GME North Bridge ………………………………………………………………….…….

5.3 Intel 82801 IDBM I/O Controller Hub 4 Mobile(ICH4-M) South Bridge …………………………………..

3

3

6

7

34

40

43

43

46

66

69

71

71

75

84

6. System Block Diagram ……………………………………………………….……………………….....

Confidential Document

7. Maintenance Diagnostics ………………………………………………………………………………..

7.1 Introduction ……………………………………………………………………………………………

7.2 Debug Card …………………………………… ………………………………………………………

7.3 Error code……………………………… ……………………………………………………………..

92

93

93

94

95

1

Contents

8050

8050

D N/B Maintenance

D N/B Maintenance

8. Trouble Shooting ……………………………………………………………………………………..….

8.1 No Power ……………………………………………………………………………………………….

8.2 Battery Can not Be Charged ……………………………………………………………………………..

8.3 No Display ………………………………… …………………………………………………………...

8.4 External Monitor No Display …………………………………………………………………………….

8.5 Memory Test Error ……………………………………………………………………………………..

8.6 Keyboard/Touch-pad Test Error ………………………………………………………………………...

8.7 USB Port Test error……………………………………………………………………………………...

8.8 Hard Disk Drive Test Error………………………………………………………………………………

8.9 CD-ROM Test Error …………………………………………………………………………………….

8.10 Audio Test Failure………………………………………………………………………………..….…

8.11 LAN Test Error ………………………………………………………………………………………..

8.12 Modem Test Error…………… …………………………………………………………………..……

8.13 Mini-PCI Test Error……….. ……… ………………………………………………………………....

8.14 Card Bus&Reader Test Error…………………………………………………………………………...

8.15 IEEE1394 Test Failure …………………………………………………………………………………

MiTac Secret

98

99

104

106

112

114

116

118

120

122

124

127

129

131

133

135

9. Spare Parts List ……………………………………………………………………………… ….…..…...

10. System Exploded View ……………………………………………………………………………...…..

Confidential Document

11. Circuit Diagram ………………………………………………………………………………………....

12. Reference Material …………………………………………………………………………………..….

137

148

149

183

2

8050

8050

D N/B Maintenance

D N/B Maintenance

1. Engineer Hardware Specification

1.1 Introduce

The MiTAC 8050D model is designed for Intel Banias processor with 400MHz FSB with Micro-FCPGA package.

It can support Banias 1.5G ~ 1.9GHz/Dothan 2.0GHz and above.

This system is based on PCI architecture and is fully compatible with IBM PC/AT specification, which has

standard hardware peripheral interface. The power management complies with Advanced Configuration and

Power Interface (ACPI) 2.0. It also provides easy configuration through CMOS setup, which is built in system

BIOS software and can be pop-up by pressing F2 key at system start up or warm reset. System also provides icon

LEDs to display system status, such as AC Power indicator, Battery Power indicator, Battery status indicator,

HDD,CD-ROM, NUM LOCK, CAP LOCK, SCROLL LOCK, RF on/off Card Reader indicator. It also equipped

with LAN, 56K Fax MODEM, 3 USB port, S-Video and audio line in/out , external microphone function.

The memory subsystem supports two expansion DDR SDRAM slot with unbuffered PC1600/PC2100 DDR-

SDRAM.

The Montara-GME GMCH Host Memory Controller integrates a high performance host interface for Intel Banias

processor, a high performance 2D/3D Graphic Engine, a high performance memory controller, Digital Video port

(DVOB & DVOC) interface, and Intel Hub interface Technology connecting with Intel 82801DBM ICH4-M.

The Intel ICH4-M integrates three Universal Serial Bus 2.0 Host Controllers Interface (UHCI), the Audio

Controller with AC97 interface, the Ethernet includes a 32-bit PCI controller, the IDE Master/Slave controllers,

and Intel Hub interface technology.

Confidential Document

MiTac Secret

3

8050

8050

The MOBILITY M10 provides one of the fastest and most advanced 2D, 3D, and multimedia graphics

performance for notebooks. It’s architecture introduces the latest achievements in the graphics industry, which

enable the use of the progressive new features in upcoming applications, but without compromising performance.

ATIs support of support of DirectX® 9 features, highly optimized Open GL® support, and flexible memory

configurations allow implementations targeted at the gaming enthusiast, consumer, business and workstation

platforms.

The Realtek RTL8100C(L) is a highly integrated, cost-effective single-chip Fast Ethernet controller that provides

32-bit performance, PCI bus master capability, and full compliance with IEEE 802.3u 100Base-T specifications

and IEEE 802.3x Full Duplex Flow Control. It also supports the Advanced Configuration Power management

Interface (ACPI).

The VT6307L is a single chip PCI Host Controller for IEEE 1394-1995 Release 1.0 and IEEE 1394a P2000. It

D N/B Maintenance

D N/B Maintenance

implements the Link and PHY layers for IEEE 1394-1995 High Performance Serial Bus specification release 1.0

and 1394a P2000. It is compliant with 1394 Open HCI 1.0 and 1.1 with DMA engine support for high

performance data transfer via a 32-bit bus master PCEI host bus interface. The VT6307L supports 100, 200 and

400 Mbit/sec transmission via an integrated 2-port PHY. The VT6307L services two types of data packets:

asynchronous and isochronous(real time). The 1394 link core performs arbitration requesting, packet generation

and checking, and bus cycle master operations. It also has root node capability and performs retry operations.

MiTac Secret

Confidential Document

The RICOH R5C592 CardBus/Media Reader controller functions as a single slot PCI to Cardbus bridge and also

PCI interface smart card and MS/SD/MMC flash card reader. The R5C592 provide one Cardbus slot and all reader

interface may operate simultaneously.

The CH7011A is a display controller device which accepts a digital graphics input signal, and encodes and

4

8050

8050

transmits data to a TV output (analog composite, s-video or RGB). The device accepts data over one 12-bit wide

variable voltage data port which supports five different data format including RGB and YcrCb. The TV-Out

processor will perform non-interlace to interlace conversion with scaling and flicker filters, and encode the data

into any of the NTSC or PAL video standards. The scaling and flicker filter is adaptive and programmable to

enable superior text display. Eight graphics resolutions are supported up to 1024 X 768 with full vertical and

horizontal underscan capability in all modes. A high accuracy low jitter phase locked loop is integrated to create

outstanding video quality. Support is provided for Macrovision and RGB bypass mode which enable driving a

VGA CRT with the input data.

The W83L950D is a high performance micro-controller on-chip supporting functions optimized for embedded

control. These include ROM, RAM, four types of timers, a serial communication interface, optional I²C bus

interface, host interface, A/D converter, D/A converter, I/O ports, and other functions needed in control system

configurations, so that compact, high performance systems can be implemented easily.

D N/B Maintenance

D N/B Maintenance

A full set of software drivers and utilities are available to allow advanced operating systems such as Windows ME,

Windows 2000 and Windows XP to take full advantage of the hardware capabilities. Features such as bus

mastering IDE, Plug and Play, Advanced Power Management (APM) with application restart, software-controlled

power shutdown.

Following chapters will have more detail description for each individual sub-systems and functions.

Confidential Document

MiTac Secret

5

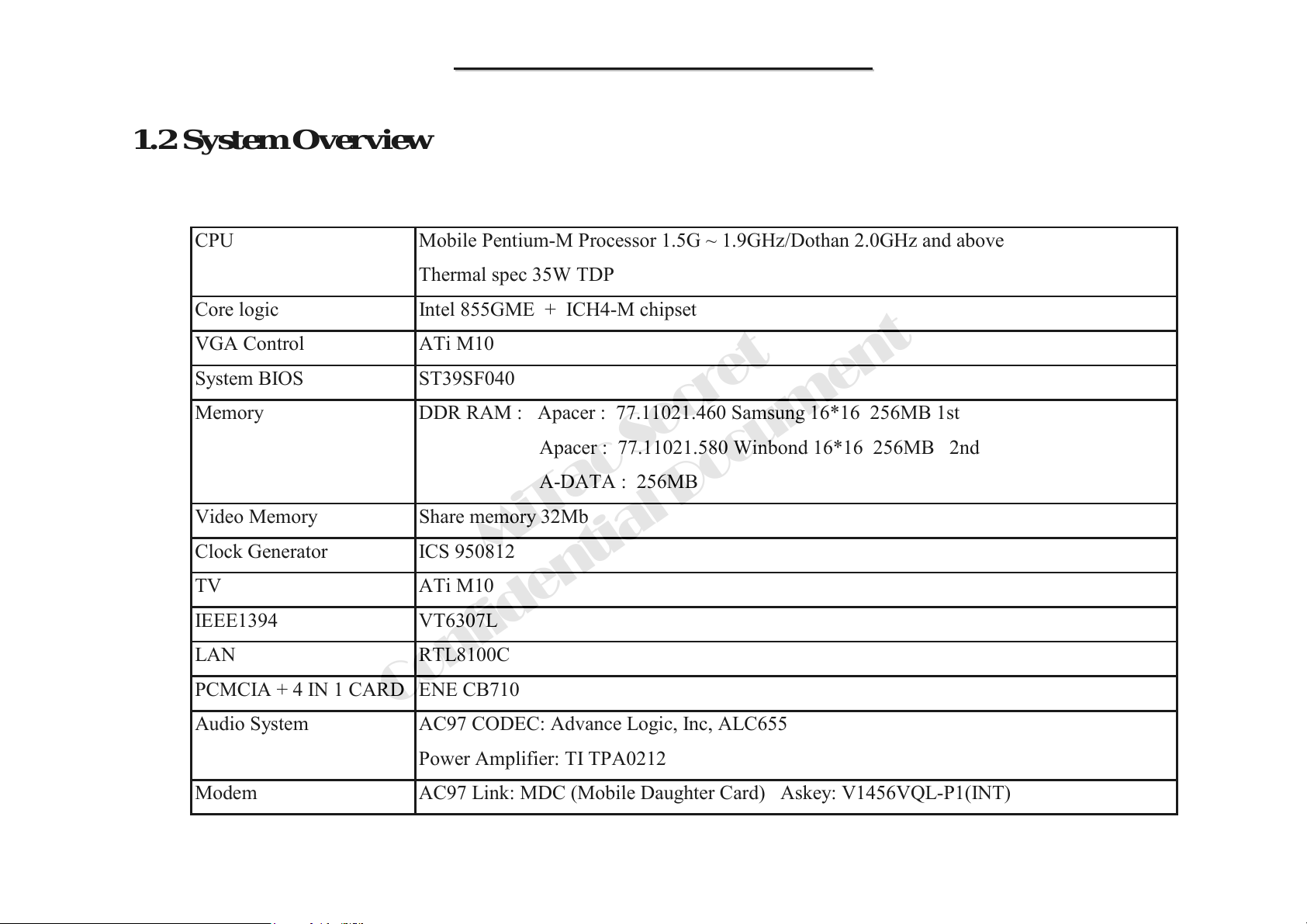

1.2 System Overview

8050

8050

D N/B Maintenance

D N/B Maintenance

CPU

Core logic Intel 855GME + ICH4-M chipset

VGA Control ATi M10

System BIOS ST39SF040

Memory

Video Memory Share memory 32Mb

Clock Generator ICS 950812

TV ATi M10

IEEE1394 VT6307L

LAN RTL8100C

PCMCIA + 4 IN 1 CARD ENE CB710

Audio System

Mobile Pentium-M Processor 1.5G ~ 1.9GHz/Dothan 2.0GHz and above

Thermal spec 35W TDP

DDR RAM : Apacer : 77.11021.460 Samsung 16*16 256MB 1st

Apacer : 77.11021.580 Winbond 16*16 256MB 2nd

A-DATA : 256MB

MiTac Secret

Confidential Document

AC97 CODEC: Advance Logic, Inc, ALC655

Power Amplifier: TI TPA0212

Modem AC97 Link: MDC (Mobile Daughter Card) Askey: V1456VQL-P1(INT)

6

8050

8050

D N/B Maintenance

D N/B Maintenance

1.3 System Hardware Parts

1.3.1 Intel Banias Processors in Micro-FCPGA Package

Intel Banias Processors with 478 pins Micro-FCPGA package.

The first Intel mobile processor with the Intel Net Burst micro-architecture which features include hyper-pipelined

technology, a rapid execution engine, a 400MHz system, an execution trace cache, advanced dynamic execution,

advanced transfer cache, enhanced floating point and multi-media unit, and Streaming SIMD Extensions 2 (SSE2).

The Streaming SIMD Extensions 2 (SSE2) enable break-through levels of performance in multimedia applications

including 3-D graphics, video decoding/encoding, and speech recognition.

Use Source-Synchronous Transfer (SST) of address and data to improve performance by transferring data four

times per bus clock.

Support Enhanced Intel Speed Step technology, which enables real-time dynamic switching of the voltage and

frequency between two performance modes.

MiTac Secret

Confidential Document

1.3.2 Clock Generator

System frequency synthesizer: ICS950812 Programmable output frequency, divider ratios, output rise/fall time,

output skew. Programmable spread percentage for EMI control. Watchdog timer technology to reset system if

7

8050

8050

system malfunctions. Programmable watchdog safe frequency. Support I2C Index read/write and block read/write

operations. Use external 14.318MHz crystal.

Provides standard frequencies and additional 5% and 10% over-clocked frequencies

Supports spread spectrum modulation: No spread, Center Spread (±0.35%, ±0.5%,or ±0.75%), or Down

Spread (- 0.5%, -1.0%, or -1.5%)

Offers adjustable PCI early clock via latch inputs

Selectable 1X or 2X strength for REF via I2C interface

Efficient power management scheme through PD#,CPU_STOP# and PCI_STOP#.

Uses external 14.318MHz crystal

D N/B Maintenance

D N/B Maintenance

Stop clocks and functional control available through

MiTac Secret

1.3.3 Montara-GME GMCH IGUI 3D Graphic DDR/SDR Chipset

Montara-GME GMCH IGUI Host Memory Controller integrates a high performance host interface for Intel

Banias processor, a high performance 2D/3D Graphic Engine, a high performance memory controller, an AGP

4Xinterface, and Intel®’ I/O Hub architecture INTEL 82801DBM ICH4-M

Montara-GME GMCH Host Interface features the AGTL & AGTL+ compliant bus driver technology with

integrated on-die termination to support Intel Banias processors. Montara-GME GMCH provides a 12-deep In

Confidential Document

8

8050

8050

-Order-Queue to support maximum outstanding transactions up to 12. It integrated a high performance 2D/3D

Graphic Engine, Video Accelerator and Advanced Hardware Acceleration MPEGI/MPEGII Video Decoder for

the Intel Banias series based PC systems. It also integrates a high performance 2.1GB/s DDR266 Memory

controller to sustain the bandwidth demand from the integrated GUI or external AGP master, host processor, as

well as the multi I/O masters. In addition to integrated GUI, Montara-GME GMCH also can support external AGP

slot with AGP 1X/2X/4X capability and Fast Write Transactions. A high bandwidth and mature Intel®’ I/O Hub

architecture is incorporated to connect Montara-GME GMCH and INTEL 82801DBM ICH4-M together. Intel®’

I/O Hub architecture is developed into three layers, the Multi-threaded I/O Link Layer delivering 1.2GB

bandwidth to connect embedded DMA Master devices and external PCI masters to interface to Multi-threaded I/O

Link layer, the Multi-threaded I/O Link Encoder/Decoder in INTEL 82801DBM ICH4-M to transfer data w/ 533

MB/s bandwidth from/to Multi-threaded I/O Link layer to/from Montara-GME GMCH, and the Multi-threaded

I/O Link Encoder/Decoder in Montara-GME GMCH to transfer data w/ 533 MB/s from/to Multi-threaded I/O

D N/B Maintenance

D N/B Maintenance

Link layer to/from INTEL 82801DBM ICH4-M.

An Unified Memory Controller supporting DDR266 DRAM is incorporated, delivering a high performance data

transfer to/from memory subsystem from/to the Host processor, the integrated graphic engine or external AGP

master, or the I/O bus masters. The memory controller also supports the Suspend to RAM function by retaining

the CKE# pins asserted in ACPI S3 state in which only AUX source deliver power. The Montara-GME GMCH

adopts the Shared Memory Architecture, eliminating the need and thus the cost of the frame buffer memory by

organizing the frame buffer in the system memory. The frame buffer size can be allocated from 8MB to 64MB.

Confidential Document

MiTac Secret

9

Features

8050

8050

D N/B Maintenance

D N/B Maintenance

Processor/Host Bus Support

Intel® Banias processor

2X Address, 4X data

Support host bus Dynamic Bus Inversion (DBI)

Supports system bus at 400MT/s (100 MHz)

Supports 64-bit host bus addressing

8-deep In-Order-Queue

AGTL+ bus driver technology with integrated GTL termination resistors and low voltage operation (1.05V)

MiTac Secret

Supports Enhanced Intel® Speed Step TM Technology (EIST) and Geyserville III

Support for DPWR# signal to Banias processor for PSB power management

Memory System

Confidential Document

Directly supports one DDR channel, 64-bits wide (72-b with ECC).

Supports 200-MHz and 266-MHz DDR devices with max of 2 Double-Sided SO-DIMMs(4 rows populated)

with unbuffered PC1600/PC2100 DDR(with ECC).

Supports 128-Mb, 256-Mb and 512-Mbit technologies providing maximum capacity of 1-GB with only x

10

8050

8050

16 devices.

All supported devices have 4 banks.

Supports up to 16 simultaneous open pages.

Supports page sizes of 2KB, 4KB, 8KB, and 16KB. Page size is individually selected for every row.

UMA support only.

System Interrupt

Supports 8259 and Processor System Bus interrupt delivery mechanism

Supports interrupts signaled as upstream Memory Writes from PCI and Hub interface

D N/B Maintenance

D N/B Maintenance

MSI sent to the CPU through the system Bus

MiTac Secret

From IOxAPIC in ICH4-M

Provides redirection for upstream interrupts to the System Bus

Video Stream Decoder

Improved HW Motion Compensation for MPEG2All format decoder (18 ATSC formats) supported

Dynamic Bob and Weave support for Video Streams

Software DVD at 60 fields/second and 30 frames/second full screen

Support for 720x480 pixel resolution DVD quality encoding at low CPU utilization

Confidential Document

11

8050

8050

Video Overlay

Single high quality scalable overlay and second Sprite to support second overlay

Multiple overay functionality provided via Arithmetic Stretch Blt

Direct YUV from Overlay to TV-out

Independent Gamma Correction

Independent Brightness / Contrast / Saturation

Independent Tint / Hue support

Destination Color keying

Source Chromakeying

D N/B Maintenance

D N/B Maintenance

Maximum source resolution of 1920x1080 pixels

Maximum overlay clock of 133 MHz/200 MHz provides a pixel resolution up to 1600x1200@ 60Hz or

1280x1024@ 85 Hz

Display

MiTac Secret

Confidential Document

Analog Display Support 350 MHz integrated 24-bit RAMDAC that can drive a standard progressive scan

analog monitor up to 1800x1350 @ 85 Hz accompanying I2C and DDC channels provided through

multiplexed interface hot plug and display support

Dual independent pipe with single display support Simultaneous: Same images and native display timings on

12

8050

8050

each display device

DVO (DVOB) support

Digital video out port DVOB with 165-MHz dot clock on 12-bit interface

Variety of DVO devices channel

Compliant with DVI Specification 1.0, thereby providing support for a flat panel up to 2048x1536 pixel

resolution, or digital CRT up to 1920x1080 pixel resolution

D N/B Maintenance

D N/B Maintenance

1.3.4 I/O Controller Hub : INTEL 82801DBM

The INTEL 82801DBM ICH4-M integrates three Universal Serial Bus 2.0 Host Controllers, the Audio Controller

with AC 97 Interface, the IDE Master/Slave controllers, and Intel®’ I/O Hub architecture. The PCI to LPC Bridge,

I/O Advanced Programmable Interrupt Controller, legacy system I/O and legacy power management

functionalities are integrated as well.

The integrated Universal Serial Bus Host Controllers features Dual Independent UHCI Compliant Host controllers

with six USB ports delivering 480 Mb/s bandwidth and rich connectivity. Besides, Legacy USB devices as well as

over current detection are also implemented.

The Integrated AC97 v2.3 compliance Audio Controller that features a 7-channels of audio speaker out and HSP

v.90 modem support. Additionally, the AC97 interface supports 4 separate SDATAIN pins that is capable of

supporting multiple audio codecs with one separate modem codec.

Confidential Document

MiTac Secret

13

8050

8050

The integrated IDE Master/Slave controllers features Dual Independent IDE channels supporting PIO mode

transfers up to 16 Mbytes/sec and Ultra DMA 33/66/100. It provides two separate data paths for the dual IDE

channels that sustain the high data transfer rate in the multitasking environment.

INTEL 82801DBM ICH4-M supports 6 PCI masters and complies with PCI 2.2 specification. It also incorporates

the legacy system I/O like: two 82C37 compatible DMA controllers, Channels 0-3 are hardwired to 8 bit, three

8254 compatible programmable 16-bit counters channels 5-7, hardwired keyboard controller and PS2 mouse

interface(not use in MiTAC 8050 model), Real Time clock with 512Bytes CMOS SRAM and two 82C59

compatible Interrupt controllers. Besides, the I/O APIC managing up to 14 interrupts with both Serial and FSB

interrupt delivery modes is supported.

The integrated power management module incorporates the ACPI 1.0b compliance functions, the APM 1.2

compliance functions, and the PCI bus power management interface spec. v1.1. Numerous power-up events and

D N/B Maintenance

D N/B Maintenance

power down events are also supported. 21 general purposed I/O pins are provided to give an easy to use logic for

specific application. In addition, the INTEL 82801DBM ICH4-M supports Deeper Sleep power state for Intel

Mobile processor.

A high bandwidth and mature Intel®’ I/O Hub architecture is incorporated to connect Montara and Intel

82801DBM ICH4-M Hub interface together. Intel®’ I/O Hub architecture is developed

MiTac Secret

Confidential Document

1.3.5 VGA Control

Introducing MOBILITY M10

14

8050

8050

The MOBILITY M10 provides one of the fastest and most advanced 2D, 3D, and multimedia graphics

performance for notebooks. Its architecture introduces the latest achievements in the graphics industry, which

enable the use of the progressive new features in upcoming applications, but without compromising performance.

ATI’s support of DirectX® 9 features, highly optimized OpenGL® support, and flexible memory configurations

allow implementations targeted at the gaming enthusiast, consumer, business and workstation platforms.

SMARTSHADER™ 2.0 — Advanced Shader Technology

Provides complete hardware-accelerated support for the new DirectX® 9 programmable shader model,

enabling more complex and realistic texture and lighting effects than ever before.

Significant improvement over first-generation shaders introduced in DirectX® 8, with a much more

powerful and intuitive instruction set.

D N/B Maintenance

D N/B Maintenance

Offers full support for this feature in OpenGL® applications.

MiTac Secret

MOOTHVISION™ 2.0 — Flexible Anti-Aliasing and Anisotropic Filtering

2x/4x/6x full-scene anti-aliasing modes

Confidential Document

Adaptive algorithm with programmable sample patterns

2x/4x/8x/16x anisotropic filtering modes

Adaptive algorithm with bi-linear (performance) and tri-linear (quality) options

15

8050

8050

High Performance Memory Support

Incorporates support for DDR SDRAM/SGRAM.

Features key items from ATI’s third generation HYPER Z™ III technology that conserves memory

bandwidth for improved performance in demanding applications.

Dual Display Support

Leading-edge technology, fully optimized with HYDRA VISION™, flexibly supports multiple

combinations of notebook LCD, traditional CRT monitors, flat panel displays and TV.

Features Dual Channel DVI support.

230MHz LVDS transmitter supports LCD panels up to QXGA (2048x1536) resolution.

D N/B Maintenance

D N/B Maintenance

Integrated 165MHz TMDS transmitter supports external flat panels up to UXGA (1600x1200) resolution.

High performance DAC speeds of 400MHz.

Features in Deta il

VIDEO Acceleration

M10 allows the integration of industry leading digital video features, including advanced de-interlacing

algorithms for unprecedented video quality and integrated digital TV decode capability. Includes

programmable,independent gamma control for the video overlay.

New FULLSTREAM™ technology removes blocky artifacts from streaming and Internet video and

Confidential Document

MiTac Secret

16

provides sharper image quality.

Integrated general purpose xDCT engine (capable of performing both forward and inverse discrete cosine

transform) and motion compensation (MC) support for the acceleration of MPEG encoding and decoding

as well as DV (digital video) encoding and decoding.

1.3.6 CardBus: CB710

Features

3.3V operation with 5V tolerant

208-pin LQFP / 209-ball LFBGA package for CB710

8050

8050

D N/B Maintenance

D N/B Maintenance

328-ball LFBGA package for CB720

MiTac Secret

PCI Interface compliant with

PCI Local Bus Specification, Revision 2.2

PCI Bus Power Management Interface Specification, Revision 1.1

PCI Mobile Design Guide, Version 1.1

Advanced Configuration and Power Interface Specification, Revision 1.0

CardBus Interface

Compliant with PC Card Standard 8.0Support Standardized Zoomed Video Register Model

Confidential Document

17

8050

8050

Support CardBay PC card interface

Smart Card Interface

Compliant with PC/SC Specification 1.0

Support ISO7816 T=0 and T=1 asynchronous communication protocols

Two power enable pins to support 5V and 3V smart cards

Support programmable card clock frequencies

Programmable F and D parameters to support different data rates

One traffic LED pin.

Secure Digital Interface

D N/B Maintenance

D N/B Maintenance

Compliant with SD Memory Card Specification Version 1.0

MiTac Secret

Support 4 parallel data lines

Has an optional reference clock source to control the operating clock frequency of SD card

Up to 10MByte/sec Read/Write rate when the optional reference clock source is used

Confidential Document

Contains 16 Bytes of data buffer to regulate the data flow between PCI interface and the SD card interface

Support Write Protect Switch

Support Card Detect either by DAT3 or by dedicated Card Detect Switch

One Traffic LED pin

18

8050

8050

One power enable pin.

Memory Stick Interface

Compliant with Memory Stick Standard Format Specification Version 1.3

Has an optional reference clock source to control the operating clock frequency of Memory Stick

Up to 2.5MByte/sec Read/Write rate when the optional reference clock source is used

Stick interface

One Traffic LED pin

One power enable pin

Smart Media Interface

D N/B Maintenance

D N/B Maintenance

One traffic LED pin

MiTac Secret

Interrupt configuration

Supports CLKRUN# protocol

Supports SUSPEND#

Confidential Document

Supports D3STATE#

Supports Zoomed Video port.

Power Switch Interface

Misc Control Logic

19

8050

8050

Supports socket activity LED

Supports 12 GPIOs and GPE#

Supports PCI LOCK

D N/B Maintenance

D N/B Maintenance

1.3.7 AC’97 AUDIO SYSTEM: Advance Logic, Inc, ALC655

The ALC655 is a 16-bit, full duplex AC'97 2.3 compatible six channels audio CODEC designed for PC

multimedia systems,including host/soft audio and AMR/CNR based designs. The ALC655 incorporates

proprietary converter technology to meet performance requirements on PC99/2001 systems. The ALC655

CODEC provides three pairs of stereo outputs with 5-Bitvolume controls, a mono output, and multiple stereo and

mono inputs, along with flexible mixing, gain and mute functions to provide a complete integrated audio solution

for PCs. The digital interface circuitry of the ALC655 CODEC operates from a 3.3V power supply for use in

notebook and PC applications. The ALC655 integrates 50mW/20ohm headset audio amplifiers at Front-Out and

Surr-Out, built-in 14.318M 24.576MHz PLL and PCBEEP generator, those can save BOM costs. The

ALC655also supports the S/PDIF input and output function, which can offer easy connection of PCs to consumer

electronic products, such as AC3 decoder/speaker and mini disk devices. ALC655 supports host/soft audio from

Intel ICHx chipsets as well as audio controller based VIA/SIS/ALI/AMD/nVIDIA/ATI chipset. Bundled

Windows series drivers (Win XP/ME/2000/98/NT), EAX/Direct Sound 3D/ I3DL2/ A3D compatible sound effect

utilities (supporting Karaoke, 26-kind of environment sound emulation,10-band equalizer), HRTF 3D positional

audio and Sensaura™ 3D (optional) provide an excellent entertainment package and game experience for PC users.

Besides, ALC655 includes Realtek’s impedance sensing techniques that makes device load on outputs and inputs

can be detected.

Confidential Document

MiTac Secret

20

8050

8050

Meets performance requirements for audio on PC99/2001 systems

Meets Microsoft WHQL/WLP 2.0 audio requirements

16-bit Stereo full-duplex CODEC with 48KHz sampling rate

Compliant with AC’97 2.3 specifications

14.318MHz- 24.576MHz PLL to save crystal

12.288MHz BITCLK input can be consumed

Integrated PCBEEP generator to save buzzer

Interrupt capability

Three analog line-level stereo inputs with 5-bit volume control: LINE_IN, CD, AUX

D N/B Maintenance

D N/B Maintenance

High quality differential CD input

MiTac Secret

Two analog line-level mono input: PCBEEP,PHONE-IN

Two software selectable MIC inputs applications (software selectable)

Boost preamplifier for MIC input

Confidential Document

50mW/20 amplifier

External Amplifier Power Down (EAPD) capability

Power management and enhanced power saving features.

Stereo MIC record for AEC/BF application

21

8050

8050

Supports Power Off CD function

Adjustable VREFOUT control Supports double sampling rate (96KHz) of DVD audio playback

Support 48KHz of S/PDIF output is compliant with AC’97 rev2.3 specification

Power support: Digital: 3.3V; Analog: 3.3V/5V

D N/B Maintenance

D N/B Maintenance

1.3.8 MDC:PCTEL MODEM DAUGHTER CARD PCT2303W (ASKEY

V1456VQL-P1)

The PCT2303W chipset is designed to meet the demand of this emerging worldwide AMR/MDC market. The

combination of PC-TEL’s well proven PCT2303W chipset and the HSP56TM MR software modem driver allows

systems manufactures to implement modem functions in PCs at a lower bill of materials (BOM) while maintaining

higher system performance.

PC-TEL has streamlined the traditional modem into the Host Signal Processing (HSP) solution. Operating with

the Pentium class processors, HSP becomes part of the host computer’s system software. It requires less power to

operate and less physical space than standard modem solutions. PC-TEL’s HSP modem is an easily integrated,

cost-effective communications solution that is flexible enough to carry you into the future.

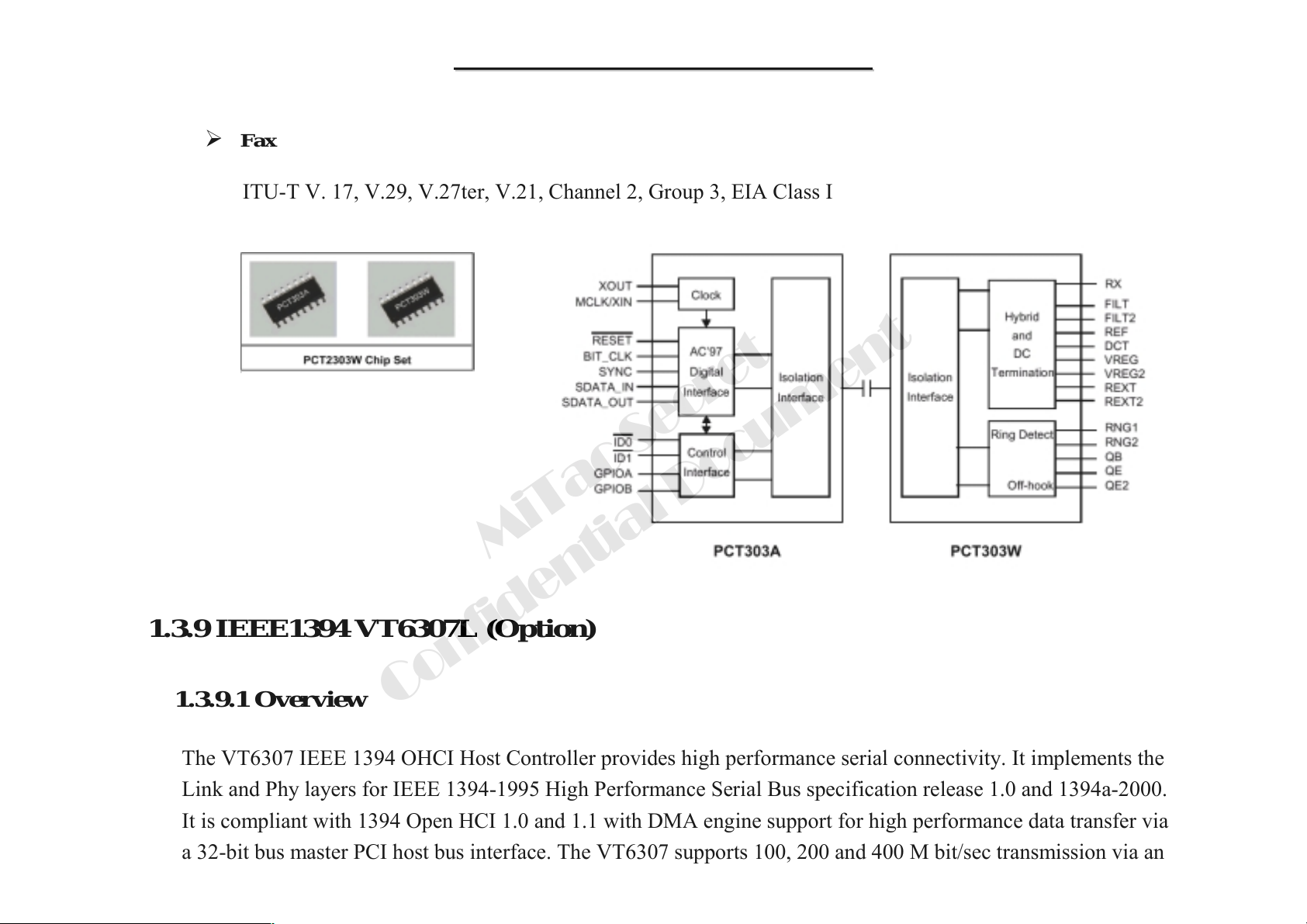

The PCT2303W chip set is an integrated direct access arrangement (DAA) and Codec that provides a

programmable line interface to meet international telephone line requirements. The PCT2303W chip set is

available in two 16-pin small outline packages (AC’97 interface on PCT303A and phone-line interface on

PCT303W). The chip set eliminates the need for an AFE, an isolation transformer, relays, opto-isolators, and 2-to

Confidential Document

MiTac Secret

22

8050

8050

4-wire hybrid. The PCT2303W chip set dramatically reduces the number of discrete components and cost

required to achieve compliance with international regulatory requirements. The PCT2303W complies with

AC’97 Interface specification Rev. 2.1.

The chip set is fully programmable to meet world-wide telephone line interface requirements including those

described by CTR21, NET4, JATE, FCC, and various country-specific PTT specifications. The programmable

parameters of the PCT2303W chip set include AC termination, DC termination, ringer impedance, and ringer

threshold. The PCT2303W chip set has been designed to meet stringent world-wide requirements for out-of-band

energy, billing-tone immunity, lightning surges, and safety requirements.

Features

D N/B Maintenance

D N/B Maintenance

Virtual com port with a DTE throughout up to 460.8Kbps.

G3 Fax compatible

Auto dial and auto answer

Ring detection

Codec/DAA Features

MiTac Secret

Confidential Document

AC97 2.1 compliant

86dB dynamic range TX/RX paths

2-4-wire hybrid

Integrated ring detector

23

8050

8050

High voltage isolation of 4000V

Support for “Caller ID”

Compliant with FCC Part68, CTR21, Net4 and JATE

Low power standby

Low profile SOIC package 16 pins 10x3x1.55mm

Low power consumption

10mA @ 3.3V operation

1mA @ 3.3V power down

Integrated modem codec

D N/B Maintenance

D N/B Maintenance

Standard Features

Data

ITU-T V.90 (56Kbps), V.34 (4.8Kbps TO 33.6 Kbps), V.32 bits (4.8Kbps to 14.4Kbps), V.22 bits (1.2 bps

to 2.4 Kbps), V.21 and Bell 103 and 212A(300 to 1200 bps) modulation protocol.

Data Compression ITU-T V.42bis MNP Class 5

Error Correction ITU-T V.42 LAPM MNP 2-4

Confidential Document

MiTac Secret

24

8050

8050

Fax

ITU-T V. 17, V.29, V.27ter, V.21, Channel 2, Group 3, EIA Class I

D N/B Maintenance

D N/B Maintenance

MiTac Secret

1.3.9 IEEE1394 VT6307L (Option)

1.3.9.1 Overview

The VT6307 IEEE 1394 OHCI Host Controller provides high performance serial connectivity. It implements the

Link and Phy layers for IEEE 1394-1995 High Performance Serial Bus specification release 1.0 and 1394a-2000.

It is compliant with 1394 Open HCI 1.0 and 1.1 with DMA engine support for high performance data transfer via

a 32-bit bus master PCI host bus interface. The VT6307 supports 100, 200 and 400 M bit/sec transmission via an

Confidential Document

25

8050

8050

integrated 2-port PHY. The VT6307 services two types of data packets: asynchronous and isochronous (real time).

The 1394 link core performs arbitration requesting, packet generation and checking, and bus cycle master

operations. It also has root node capability and performs retry operations. The VT6307 is ready to provide

industry-standard IEEE 1394 peripheral connections for desktop and mobile PC platforms. Support for the

VT6307 is built into Microsoft Windows 98, Windows ME, Windows 2000, and Windows XP.

1.3.9.2 Features

32 bit CRC generator and checker for receive and transmit data

On-chip isochronous and asynchronous receive and transmit FIFOs for packets (2K for general receive plus

2K for isochronous transmit plus 2K for asynchronous transmit)

D N/B Maintenance

D N/B Maintenance

8 isochronous transmit contexts

MiTac Secret

4 isochronous receive context

3-deep physical post-write queue

2-deep physical response queue

Dual buffer mode enhancements

Skip Processing enhancements

Block Read Request handling

Ack_tardy processing

Confidential Document

26

8050

8050

D N/B Maintenance

D N/B Maintenance

1.3.10 System Flash Memory (BIOS)

Firmware Hub for Intel® 810, 810E, 815, 815E,815EP, 820, 840, 850 Chipsets

Flexible Erase Capability

Uniform 4 K Byte Sectors

Uniform 16 K Byte overlay blocks for SST49LF002A

Uniform 64 K Byte overlay blocks for SST49LF004ATop boot block protection

16 K Byte for SST49LF002A

64 K Byte for SST49LF004A

Chip-Erase for PP Mode

MiTac Secret

Single 3.0-3.6V Read and Write Operations

Superior Reliability

Firmware Hub Hardware Interface Mode

5-signal communication interface supporting byte Read and Write

33 MHz clock frequency operation

WP# and TBL# pins provide hardware write protect for entire chip and/or top Boot Block

Confidential Document

27

8050

8050

Block Locking Register for all blocks

Standard SDP Command Set

Data# Polling and Toggle Bit for End-of-Write detection

5 GPI pins for system design flexibility

4 ID pins for multi-chip selection

D N/B Maintenance

D N/B Maintenance

1.3.11 Memory System

1.3.11.1 64MB, 128MB, 256MB, 512MB (x64) 200-Pin DDR SDRAM SODIMM

JEDEC-standard 200-pin, small-outline, dual in-line memory module (SODIMM)

Utilizes 200 Mb/s and 266 Mb/s DDR SDRAM components

64MB (8 Meg x 64 [H]); 128MB (16 Meg x 64, [H] and [HD]); 256MB (32 Meg x 64 [HD]); 512MB (64

Meg x 64 [HD])

MiTac Secret

Confidential Document

VDD= VDDQ= +2.5V ±0.2V

VDDSPD = +2.2V to +5.5V

2.5V I/O (SSTL_2 compatible)

Commands entered on each positive CK edge

28

8050

8050

DQS edge-aligned with data for READs; center-aligned with data for WRITEs

Internal, pipelined double data rate (DDR) architecture; two data accesses per clock cycle

Bidirectional data strobe (DQS) transmitted/received with data—i.e.,source-synchronous data capture

Differential clock inputs (CK and CK# - can be multiple clocks, CK0/CK0#, CK1/CK1#, etc.)

Four internal device banks for concurrent operation

Selectable burst lengths: 2, 4, or 8

Auto precharge option

Auto Refresh and Self Refresh Modes

15.6µs (MT4VDDT864H, MT8VDDT1664HD), 7.8125µs (MT4VDDT1664H, MT8VDDT3264HD,

D N/B Maintenance

D N/B Maintenance

MT8VDDT6464HD) maximum average periodic refresh interval

MiTac Secret

Serial Presence Detect (SPD) with EEPROM

Fast data transfer rates PC2100 or PC1600

Selectable READ CAS latency for maximum compatibility

Gold-plated edge contacts

Confidential Document

29

Loading...

Loading...