Mitac 8011 Service Manual

SERVICE MANUAL FOR

SERVICE MANUAL FOR

SERVICE MANUAL FOR

8011

8011

80118011

8011

8011

80118011

8011

8011

80118011

BY: Ally Yuan

Repair Technology Research Department /EDVD

Repair Technology Research Department /EDVD

Oct.2004

Contents

8011

8011

N/B Maintenance

N/B Maintenance

1. Hardware Engineering Specification …………………………………………………………………

1.1 Introduction …………………………………………………………………………………………………………..

1.2 Hardware System ……………………………………………………………………………………………………..

1.3 Other Functions ……………………………………………………………………………………………………….

1.4 Power Management Peripheral Components………………………………………………………………………..

1.5 Appendix 1 : Intel 82801DBM ICH4-M GPIO Definitions…………………………………………………………

1.6 Appendix 2 : W83L950D KBC Pins Definitions …………………………………………………………………….

1.7 Appendix 3 : MiTAC 8011 Product Specification …………………………………………………………………..

2. System View and Disassembly ………………………………………………………………………..

2.1 System View …………………………………………………………………………………………………………..

2.2 System Disassembly …………………………………………………………………………………………………..

MiTac Secret

3. Definition & Location of Connectors / Switches ……………………………………………………..

3.1 Mother Board …………………………………………………………………………………………………………

3.2 Transmitter Board ……………………………………………………………………………………………………

Confidential Document

4

4

8

31

37

40

41

44

46

46

49

71

71

73

4. Definition & Location of Major Components ………………………………………………………..

4.1 Mother Board …………………………………………………………………………………………………………

5. Pin Description of Major Component …….…………………………………………………………..

74

74

76

1

Contents

8011

8011

N/B Maintenance

N/B Maintenance

5.1 Intel Banias Pentium M Processor …………………………………………………………………………………..

5.2 Intel 82855GME Memory Controller Hub ………………………………………………………………………….

5.3 Intel 82801DBM I/O Controller Hub Mobile …………...…………………………………………………………..

6. System Block Diagram …………………………………………………………………………………

7. Maintenance Diagnostics ………………………………………………………………………………

7.1 Introduction …………………………………………………………………………………………………………..

7.2 Error Codes …………………………………………………………………………………………………………..

7.3 Debug Tool ……………………………………………………………………………………………………………

8. Trouble Shooting ……………………………………………………………………………………….

MiTac Secret

8.1 No Power ………………………………………………………………………………………………………………

8.2 No Display ……………………………………………………………………………………………………………..

8.3 VGA Controller Failure LCD No Display …………………………………………………………………………..

8.4 External Monitor No Display ………………………………………………………………………………………..

8.5 Memory Test Error …………………………………………………………………………………………………..

8.6 Keyboard (K/B) Touch-Pad (T/P) Test Error ………………………………………………………………………

8.7 Hard Driver Test Error ………………………………………………………………………………………………

8.8 CD-ROM Driver Test Error …………………………………………………………………………………………

8.9 USB Port Test Error ………………………………………………………………………………………………….

8.10 Audio Failure ………………………………………………………………………………………………………..

8.11 LAN Test Error ………………………………………………………………………………………………………

8.12 PC Card & 1394 Socket Failure …………………………………………………………………………………….

Confidential Document

76

80

89

97

98

98

99

101

102

104

109

112

114

116

118

120

122

124

126

129

131

2

Contents

8011

8011

N/B Maintenance

N/B Maintenance

9. Spare Parts List ……………………………………………………………………………… ………..

10. System Exploded Views ………………………………………………………………………………

11. Circuit Diagram ………………………………………………………………………………………

12. Reference Material ……………………………………………………………………………………

MiTac Secret

133

146

148

178

Confidential Document

3

8011

8011

N/B Maintenance

N/B Maintenance

1. Hardware Engineering Specification

1.1 Introduction

1.1.1 General Description

This document describes the brief introduction for MiTAC 8011 portable notebook computer system.

1.1.2 System Overview

The MiTAC 8011 model is designed for Intel Banias and Celeron processor with 400MHz FSB with Micro-FCPGA

package. It can support Banias 1.5G ~ 1.7GHz/Celeron-M 1.3G~1.5GHz/Dothan 1.5G~1.8GHz and 2.0GHz and

above.

MiTac Secret

This system is based on PCI architecture and is fully compatible with IBM PC/AT specification, which has standard

hardware peripheral interface. The power management complies with Advanced Configuration and Power Interface

(ACPI) 2.0. It also provides easy configuration through CMOS setup, which is built in system BIOS software and can

be pop-up by pressing F2 key at system start up or warm reset. System also provides icon LEDs to display system

status, such as AC Power indicator, Battery Power indicator, Battery status indicator, HDD,CD-ROM, NUM LOCK,

CAP LOCK, SCROLL LOCK, RF on/off. It also equipped with LAN, 56K Fax MODEM, FIR, 3 USB port,

IEEE1394, PCMCIA, DVI-D and audio SPDIF, external and internal microphone function.

The memory subsystem supports two expansion DDR SDRAM slot with unbuffered PC1600/PC2100/PC2700 DDR-

SDRAM.

Confidential Document

4

8011

8011

The Montara-GME GMCH Host Memory Controller integrates a high performance host interface for Intel Banias

processor, a high performance 2D/3D Graphic Engine, a high performance memory controller, Digital Video port

(DVOB & DVOC) interface, and Intel Hub interface Technology connecting with Intel 82801DBM ICH4-M.

The Intel ICH4-M integrates three Universal Serial Bus 2.0 Host Controllers Interface (UHCI), the Audio Controller

with AC97 interface, the Ethernet includes a 32-bit PCI controller, the IDE Master/Slave controllers, and Intel Hub

interface technology.

The Realtek RTL8100C(L) is a highly integrated, cost-effective single-chip Fast Ethernet controller that provides 32-

bit performance, PCI bus master capability, and full compliance with IEEE 802.3u 100Base-T specifications and IEEE

802.3x Full Duplex Flow Control. It also supports the Advanced Configuration Power management Interface (ACPI).

The VT6301S is a single chip PCI Host Controller for IEEE 1394-1995 Release 1.0 and IEEE 1394a P2000. It

N/B Maintenance

N/B Maintenance

implements the Link and PHY layers for IEEE 1394-1995 High Performance Serial Bus specification release 1.0 and

1394a P2000. It is compliant with 1394 Open HCI 1.0 and 1.1 with DMA engine support for high performance data

transfer via a 32-bit bus master PCEI host bus interface. The VT6301S supports 100, 200 and 400 Mbit/sec

transmission via an integrated 1-port PHY. The VT6301S services two types of data packets: asynchronous and

isochronous(real time). The 1394 link core performs arbitration requesting, packet generation and checking, and bus

cycle master operations. It also has root node capability and performs retry operations.

MiTac Secret

Confidential Document

The CB-1211/1410 is a high performance PCI-to-CardBus controller with package type of 144-pin LQFP, and

consisting of 3.3V core logic and 3.3V I/O buffers with 5V tolerance. All card signals are buffered internally to allow

hot insertion and removal without external buffering.

The ALC655 is a 16-bit, full duplex AC'97 2.3 compatible six channels audio CODEC designed for PC multimedia

5

8011

8011

systems, in cluding host/soft audio and AMR/CNR based designs. The ALC655 incorporates proprietary converter

technology to meet performance requirement s on PC99/2001 systems. The AL C655 CODEC provides three pairs of

stereo outputs w ith 5-Bit volume controls, a mono output, and multiple stereo and mono inputs, along with flexible

mixing, gain and mute functions to provide a complete integrated audio solution for PCs. The digital interface

circuitry of the ALC655 CODEC operates from a 3.3V power supply for use in notebook and PC applications.

The W83L517D prov ides one high-speed serial comm unication ports (UARTs), on e of which supports serial Infrared

communication. The UART includes a 16-byte send/receive FIFO, a programmable baud rate generator, complete

modem control capability, and a processor interrupt system. The UART provides legacy speed with baud rate up to

115.2k bps a nd also advanced speed with bau d rates of 230k, 460k, or 921k bps which support higher speed modems.

In addition, the W83L517D provides IR functions: IrDA 1.0 (SIR for 1.152K bps) and IrDA 1.1 (MIR for 1.152M bps

or FIR for 4M bps), TV remote IR, (Consumer IR, supporting NEC, RC-5, extended RC-5, and RECS-80 protocols).

N/B Maintenance

N/B Maintenance

The W83L950D is a high performance microcontroller on-chip suppor ting functions optimized for embedded co ntrol.

These include ROM, RAM, four types of tim ers, a serial communication interface, optional I²C bus interface, hos t

interface, A/D converter, D/A converter, I/O ports, and other functions needed in control sy stem configurations, so

that compact, high performance systems can be implemented easily.

A full set of software drivers and utilities are available to allow advanced operating systems such as Windows ME,

Windows 2000 and Windows XP to take full advantage of the hardware capabilities. Features such as bus mastering

IDE, Plug and Play, Adva nced Power Management (APM) with applicati on restart, software-controlled power

shutdown.

Following chapters will have more detail description for each individual sub-systems and functions.

Confidential Document

MiTac Secret

6

8011

8011

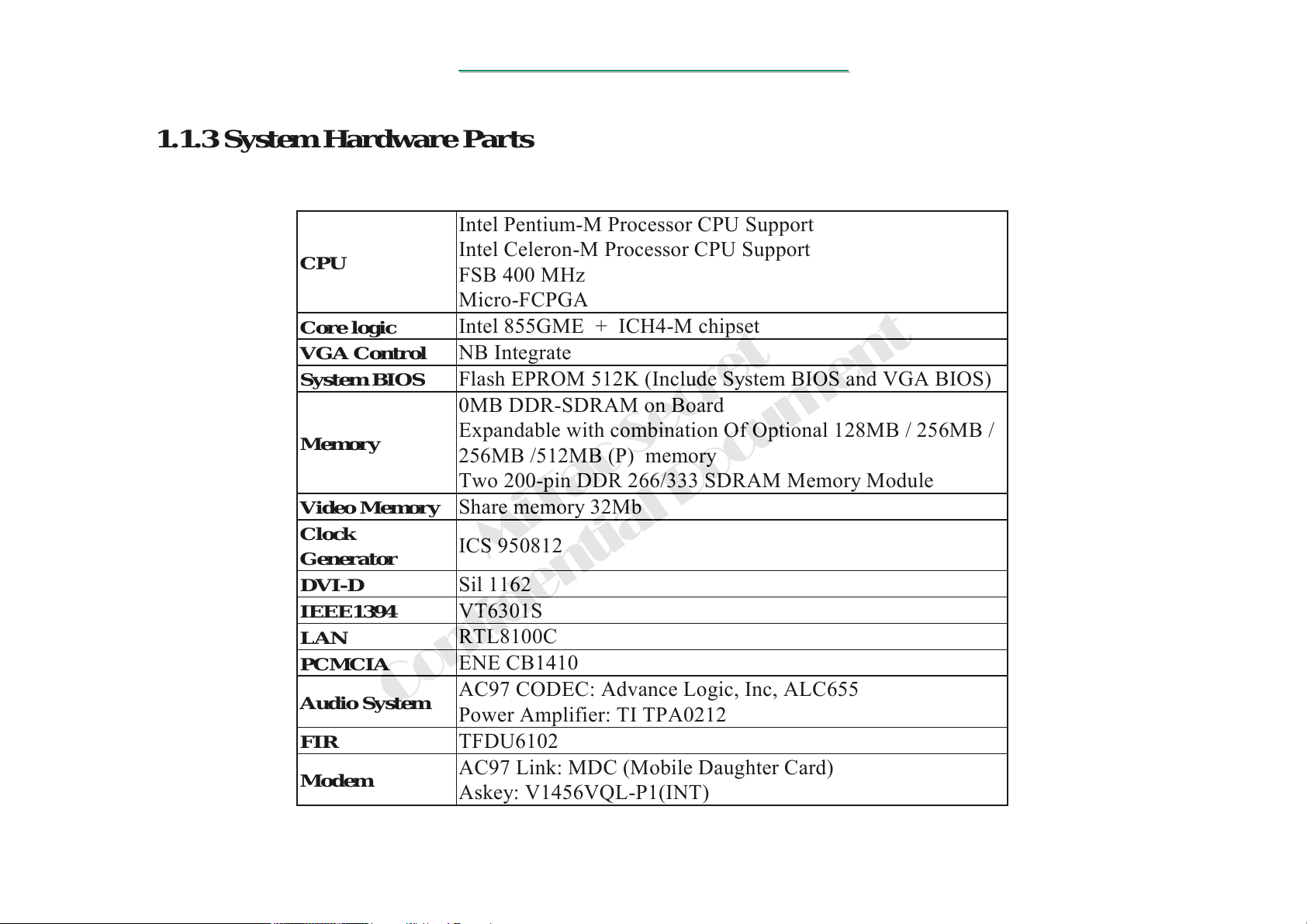

1.1.3 System Hardware Parts

Intel Pentium-M Processor CPU Support

CPU

Core log ic

VGA Control

System BIOS

Memory

Video Memory

Intel Celeron-M Processor CPU Support

FSB 400 MHz

Micro-FCPGA

Intel 855GME + ICH4-M chipset

NB Integrate

Flash EPROM 512K (Include System BIOS and VGA BIOS)

0MB DDR-SDRAM on Board

Expandable with combination Of Optional 128MB / 256MB /

256MB /512MB (P) memory

Two 200-pin DDR 266/333 SDRAM Memory Module

Share memory 32Mb

N/B Maintenance

N/B Maintenance

Clock

Generator

DVI-D

IEEE1394

LAN

PCMCIA

Audio System

FIR

Modem

Confidential Document

ICS 950812

MiTac Secret

Sil 1162

VT6301S

RTL8100C

ENE CB1410

AC97 CODEC: Advance Logic, Inc, ALC655

Power Amplifier: TI TPA0212

TFDU6102

AC97 Link: MDC (Mobile Daughter Card)

Askey: V1456VQL-P1(INT)

7

8011

8011

N/B Maintenance

N/B Maintenance

1.2 Hardware System

1.2.1 Intel Banias processors in Micro-FCPGA package.

Intel Banias/Dothan Processors with 478 pins Micro-FCPGA package .

The first Intel mobile processor with the Intel Net Burst micro-architecture which features include hyper-

pipelined technology, a rapid execution engine, a 400MHz system, an execution trace cache, advanced dynamic

execution, advanced transfer cache, enhanced floating point and multi-media unit, and Streaming SIMD

Extensions 2 (SSE2).

The Streaming SIMD Extensions 2 (SSE2) enable break-through levels of performance in multimedia

applications including 3-D graphics, video decoding/encoding, and speech recognition.

Use Source-Synchronous Transfer (SST) of address and data to improve performance by transferring data four

times per bus clock.

MiTac Secret

Support Enhanced Intel Speed Step technology, which enables real-time dynamic switching of the voltage and

frequency between two performance modes.

1.2.2 Synthesizer

Confidential Document

System frequency synthesizer: ICS950812 Programmable output frequency, divider ratios, output rise/fall time, output

skew. Programmable spread percentage for EMI control. Watchdog timer technology to reset system if system

malfunctions. Programmable watchdog safe frequency. Support I2C Index read/write and block read/write operations.

Use external 14.318MHz crystal.

8

8011

8011

Provides standard frequencies and additional 5% and 10% over-clocked frequencies

Supports spread spectrum modulation:No spread, Center Spread (±0.35%, ±0.5%, or ±0.75%), or Down Spread

(-0.5%, -1.0%, or -1.5%)

Offers adjustable PCI early clock via latch inputs

Selectable 1X or 2X strength for REF via I2C interface

Efficient power management scheme through PD#, CPU_STOP# and PCI_STOP#.

Uses external 14.318MHz crystal

Stop clocks and functional control available through

N/B Maintenance

N/B Maintenance

1.2.3 Montara-GME GMCH IGUI 3D Graphic DDR/SDR Chipset

Montara-GME GMCH IGUI Host Memory Controller integrates a high performance host interface for Intel Banias

processor, a high performance 2D/3D Graphic Engine, a high performance memory controller, an AGP 4X interface,

and Intel®’ I/O Hub architecture INTEL 82801DBM ICH4-M.

Montara-GME GMCH Host Interface features the AGTL & AGTL+ compliant bus driver technology with integrated

on-die termination to support Intel Banias processors. Montara-GME GMCH provides a 12-deep In-Order-Queue to

support maximum outstanding transactions up to 12. It integrated a high performance 2D/3D Graphic Engine, Video

Accelerator and Advanced Hardware Acceleration MPEGI/MPEGII Video Decoder for the Intel Banias series based

PC systems. It also integrates a high performance 2.1GB/s DDR266 Memory controller to sustain the bandwidth

demand from the integrated GUI or external AGP master, host processor, as well as the multi I/O masters. In addition

to integrated GUI, Montara-GME GMCH also can support external AGP slot with AGP 1X/2X/4X capability and Fast

Write Transactions. A high bandwidth and mature Intel®’ I/O Hub architecture is incorporated to connect

Confidential Document

MiTac Secret

9

8011

8011

Montara-GME GMCH and INTEL 82801DBM ICH4-M together. Intel®’ I/O Hub architecture is developed into

three layers, the Multi-threaded I/O Link Layer delivering 1.2GB bandwidth to connect embedded DMA Master

devices and external PCI masters to interface to Multi-threaded I/O Link layer, the Multi-threaded I/O Link

Encoder/Decoder in INTEL 82801DBM ICH4-M to transfer data w/ 533 MB/s bandwidth from/to Multi-threaded

I/O Link layer to/from Montara-GME GMCH, and the Multi-threaded I/O Link Encoder/Decoder in Montara-GME

GMCH to transfer data w/ 533 MB/s from/to Multi-threaded I/O Link layer to/from Intel 82801DBM ICH4-M.

An Unified Memory Controller supporting DDR266 DRAM is incorporated, delivering a high performance data

transfer to/from memory subsystem from/to the Host processor, the integrated graphic engine or external AGP

master, or the I/O bus masters. The memory controller also supports the Suspend to RAM function by retaining the

CKE# pins asserted in ACPI S3 state in which only AUX source deliver power. The Montara-GME GMCH adopts

the Shared Memory Architecture, eliminating the need and thus the cost of the frame buffer memory by organizing

the frame buffer in the system memory. The frame buffer size can be allocated from 8MB to 64MB.

N/B Maintenance

N/B Maintenance

Features :

Processor/Host Bus Support

-Intel

- 2X Address, 4X data

®

Banias processor

MiTac Secret

Confidential Document

- Support host bus Dynamic Bus Inversion (DBI)

- Supports system bus at 400MT/s (100 MHz)

- 8-deep In-Order-Queue

- AGTL+ bus driver technology with integrated GTL termination resistors and low voltage operation (1.05V)

- Support Enhanced Intel SpeedStep Technology and Geyserville III

10

8011

8011

- Support for DPWR# signal to Banias processor for PSB power management

Memory System

- Directly supports one DDR channel, 64-b wide (72-b with ECC).

- Supports 200-MHz , 266-MHz and 333-MHz DDR devices with max of 2 Double-Sided SO-DIMMs(4 rows

populated) with unbuffered PC1600/PC2100/PC2700 DDR(with ECC).

- Supports 128-Mb, 256-Mb and 512-M bit technologies providing maximum capacity of 1-GB with X16 devices

and up to 2-GB with dual stack DDP (using 512-M bit technology)

- All supported devices have 4 banks.

- Configurable optional ECC operation (Signal bit Error Correction and multiple bit Error Dectection).

- Encoding at low CPU utilization

N/B Maintenance

N/B Maintenance

System interrupt

- Support 8259 and processor system bus interrupt delivery mechanism

- Support interrupts signaled as upstream Memory Writes from PCI and Hub interface

- MSI send to the CPU through the System Bus

- From IOx APIC in ICH4-M provides redirection for urstream interrupts to the system bus

MiTac Secret

Confidential Document

Video stream decoder

- Improved HW Motion Compensation for MPEG2

- All format decoder (18 ATSC formats) supported

- Dynamic Bob and Weave support for Video Streams

11

8011

8011

- Software DVD at 60 fields/second and 30 frames/second full screen

- Support for standard definition DVD (i. e. NTSC pixel resolution of 720*480 etc.) quality encoding at low CPU

utilization

Video Overlay

- Single high quality scalable overlay and second Sprite to support second overlay

- Multiple overlay functionality provided via Arithmetic Stretch Blt

- 5-tap horizontal,3-tap vertical filtered scaling.

- Direct YUV from Overlay to TV-out

- Independent Gamma Correction

- Independent Brightness / Contrast / Saturation

- Independent Tint / Hue support

N/B Maintenance

N/B Maintenance

- Destination Color keying

MiTac Secret

- Source Chromakeying

- Maximum source resolution of 1920x1080 pixels

- Maximum overlay clock of 133 MHz/200 MHz (120-Mp/s) provides a pixel resolution up to 1600x1200 at 60-Hz

or 1280x1024 at 85 Hz (Please refer to the Montara GM SW PRD rev. 0.8 for detailed display information,i. e.

pixel depths,etc)

- Multiple hardware color cursor support (32-bit with alpha and legacy 2-bpp mode)

- Accompanying I2C and DDC channels provided through multiplexed interface.

Display

- Analog Display Support

Confidential Document

12

8011

8011

- 350 MHz integrated 24-bit RAMDAC that can drive a standard progressive scan analog monitor with pixel

resolution up to 1600 x1200 at 85Hz and 2048x1536 at 75Hz.

- Dual independent pipe support

- Concurrent Different image and native display timings on each display device.

- Simultaneous: Same image and native display timings on each display device.

- DVO (DVOB and DVOC) support

-- Digital video out port DVOB and DVOC with 165-MHz dot clock on each 12-bit interface;two 12-bit channels

can be combined to from one dual channel 24-bit interface with an effective dot clock of 330MHz.

-- The combined DVO B/C ports as well as individual DVO B/C port can drive a variety of DVO devices (TV-

Out Encoders.TMDS and LVDS transmitters.Etc.) with pixel resolution up to 1600x1200 at 85Hz and

2048x1536 at 75Hz.

-- Compliant with DVI Specifiction1.0

N/B Maintenance

N/B Maintenance

- Dedicated LFP (local flat panel) interface

-- Single or dual channel LVDS panel support up to UXGA panel resolution with frequency range from

25MHz to 112MHz (single channel/dual channel)

-- SSC support of 0.5%, 1.0%, and 2.5% center and down spread with external SSC clock

-- Supports data format of 18bpp

-- LCD panel power sequencing compliant with SPWG timing specification

-- Compliant with ANSI/TIA/EIA –644-1995 spec

-- Integrated PWM interface for LCD backlight inverter control

-- Bi-linear Panel fitting

- Tri-view support through LFP interface, DVOB/DVOC ports and CRT

Confidential Document

MiTac Secret

13

8011

8011

N/B Maintenance

N/B Maintenance

1.2.4 I/O Controller Hub : Intel 82801DBM

The Intel 82801DBM ICH4-M integrates three Universal Serial Bus 2.0 Host Controllers, the Audio Controller with

AC 97 Interface, the IDE Master/Slave controllers, and Intel®’ I/O Hub architecture. The PCI to LPC Bridge, I/O

Advanced Programmable Interrupt Controller, legacy system I/O and legacy power management functionalities are

integrated as well.

The integrated Universal Serial Bus Host Controllers features Dual Independent UHCI Compliant Host controllers

with six USB ports delivering 480 Mb/s bandwidth and rich connectivity. Besides, Legacy USB devices as well as

over current detection are also implemented.

The Integrated AC97 v2.3 compliance Audio Controller that features a 7-channels of audio speaker out and HSP v.90

modem support. Additionally, the AC97 interface supports 4 separate SDATAIN pins that is capable of supporting

multiple audio codecs with one separate modem codec.

MiTac Secret

The integrated IDE Master/Slave controllers features Dual Independent IDE channels supporting PIO mode transfers

up to 16 Mbytes/sec and Ultra DMA 33/66/100. It provides two separate data paths for the dual IDE channels that

sustain the high data transfer rate in the multitasking environment.

Intel 82801DBM ICH4-M supports 6 PCI masters and complies with PCI 2.2 specification. It also incorporates the

legacy system I/O like: two 82C37 compatible DMA controllers, Channels 0-3 are hardwired to 8 bit, three 8254

compatible programmable 16-bit counters channels 5-7, hardwired keyboard controller and PS2 mouse interface (not

use in MiTAC 8080 model), Real Time clock with 512Bytes CMOS SRAM and two 82C59 compatible Interrupt

controllers. Besides, the I/O APIC managing up to 14 interrupts with both Serial and FSB interrupt delivery modes is

supported.

Confidential Document

14

8011

8011

The integrated power management module incorporates the ACPI 1.0b compliance functions, the APM 1.2

compliance functions, and the PCI bus power management interface spec. v1.1. Numerous power-up events and

power down events are also supported. 21 general purposed I/O pins are provided to give an easy to use logic for

specific application. In addition, the Intel 82801DBM ICH4-M supports Deeper Sleep power state for Intel Mobile

processor.

A high bandwidth and mature Intel®’ I/O Hub architecture is incorporated to connect Montara and Intel 82801DBM

ICH4-M Hub interface together. Intel®’ I/O Hub architecture is developed.

Features :

PCI Bus Interface

Supports PCI Revision 2.2 Specification at 33 MHz

N/B Maintenance

N/B Maintenance

133 MB/sec maximum throughput

MiTac Secret

Supports up to six master devices on PCI

One PCI REQ/GNT pair can be given higher arbitration priority (intended for external 1394 host controller)

Support for 44-bit addressing on PCI using DAC protocol Integrated LAN Controller

WfM 2.0 and IEEE 802.3 compliant

LAN Connect Interface (LCI)

10/100 M bit/sec Ethernet support_ Integrated IDE Controller

Supports “Native Mode” register and interrupts

Independent timing of up to 4 drives, with separate primary and secondary IDE cable connections

Confidential Document

15

8011

8011

Ultra ATA/100/66/33, BMIDE and PIO modes

Tri-state modes to enable swap bay

USB

Includes three UHCI host controllers that support six external ports

New: Includes one EHCI high-speed USB 2.0 Host Controller that supports all six ports

New: Supports a USB 2.0 high-speed debug port

Supports wake-up from sleeping states S1–S5

Supports legacy keyboard/mouse software AC-Link for Audio and Telephony CODECs

Supports AC ’97 2.3

New: Third AC_SDATA_IN line for three codec support

N/B Maintenance

N/B Maintenance

New: Independent bus master logic for seven channels (PCM In/Out, Mic 1 input, Mic 2 input, modem in/out,

S/PDIF out)

Separate independent PCI functions for audio and modem

Support for up to six channels of PCM audio output (full AC3 decode)

Supports wake-up events Interrupt Controller

MiTac Secret

Confidential Document

Support up to eight PCI interrupt pins

Supports PCI 2.2 message signaled interrupts

Two cascaded 82C59 with 15 interrupts

Integrated I/O APIC capability with 24 interrupts

16

8011

8011

Supports processor system bus interrupt delivery New: 1.5 V operation with 3.3 V I/O

5V tolerant buffers on IDE, PCI, USB over current and legacy signals Timers Based on 82C54

System timer, refresh request, speaker tone output Power Management Logic

ACPI 2.0 compliant

ACPI-defined power states (C1–C2, S3–S5 )

Supports Desktop S1 state (like C2 state, only STPCLK# active)

ACPI power management timer

PCI PME# support

SMI# generation

All registers readable/restorable for proper resume from 0 V suspend states External Glue Integration

N/B Maintenance

N/B Maintenance

Integrated pull-up, pull-down and series termination resistors on IDE, processor interface

MiTac Secret

Integrated Pull-down and Series resistors on USB Enhanced Hub Interface Buffers Improve Routing flexibility

(Not available with all Memory Controller Hubs)

1.2.5 CardBus: CB1410

Confidential Document

Features :

3.3V operation with 5V tolerance,144-pin LQFP or 144-ball LFBGA package for CB1410 single slot Cardbus

controller

17

8011

8011

Compliant with

- PCI Local Bus Specification, Revision 2.2

- PCI Bus Power Management Interface Specification, Revision 1.1

- PCI Mobile Design Guide, Version 1.1

- Advanced Configuration and Power Interface Specification, Revision 1.0

- PC 99 System Design Guide

- PC Card Standard 8.0

Interrupt configuration

- Supports parallel PCI interrupts

- Supports parallel IRQ and parallel PCI interrupts

N/B Maintenance

N/B Maintenance

- Supports serialized IRQ and parallel PCI interrupts

- Supports serialized IRQ and PCI interrupts

Power Management Control Logic

- Supports CLKRUN# protocol

- Supports SUSPEND#

- Supports PCI PME# from D3, D2, D1 and D0

- Supports PCI PME# from D3Cold

- Supports D3STATE# (CB1410 only)

Confidential Document

MiTac Secret

18

8011

8011

Power Switch Interface

- CB1410 supports parallel 4 wire power switch interface

Misc Control Logic

- Supports serial EEPROM interface

- Supports socket activity LED

- Supports 5 GPIOs and GPE#

- Supports standard Zoomed Video Port

- Supports SPKROUT, CAUDIO and RIOUT#

- Supports PCI LOCK#

N/B Maintenance

N/B Maintenance

1.2.6 DVI

MiTac Secret

The SiI 1162 transmitter uses Panel Link Digital technology to support displays ranging from VGA to UXGA

resolution in a single link interface. The SiI 1162 transmitter uses a 12-bit interface, taking in one half-pixel per clock

edge. Designed to accommodate ultra high speed parallel interfaces such as the Intel DVO port, the SiI 1162

transmitter reduces pin count to a bare minimum and at the same time improves signal timing. The SiI 1162’s

innovative design eases board design requirements as well. Panel Link Digital technology simplifies PC design by

resolving many of the system level issues associated with high-speed mixed signal design, providing the system

designer with a digital interface solution that is quicker to market and lower in cost.

Confidential Document

19

8011

8011

Features :

Scaleable Bandwidth: 25 - 165 mega pixels per second

Flexible Input Clocking: Single Clock Dual edge or Differential Clock input mode

I2C Slave Programming Interface

Low Voltage Interface: 3.0V to 3.6V range and 1.0 tov1.9V range

Monitor Detection supported through Hot Plug and Receiver Detection

De-skewing Option: varies clock to data input timing

Cable Distance Support: over 5 meter DVI cable

DVI 1.0 Compliant with significantly greater margin than competitive solutions

Low pin count and smaller 48-pin TSSOP package

N/B Maintenance

N/B Maintenance

BIOS and driver compatible with SiI 164 transmitter

MiTac Secret

Fully programmable through serial port

Complete Windows and DOS driver support

Low voltage interface support to graphics device

Confidential Document

1.2.7 AC’97 AUDIO SYSTEM: Advance Logic, Inc, ALC655

The ALC655 is a 16-bit, full duplex AC'97 2.3 compatible six channels audio CODEC designed for PC multimedia

systems,including host/soft audio and AMR/CNR based designs. The ALC655 incorporates proprietary converter

technology to meet performance requirements on PC99/2001 systems. The ALC655 CODEC provides three pairs of

20

8011

8011

stereo outputs with 5-Bitvolume controls, a mono output, and multiple stereo and mono inputs, along with flexible

mixing, gain and mute functions to provide a complete integrated audio solution for PCs. The digital interface

circuitry of the ALC655 CODEC operates from a 3.3V power supply for use in notebook and PC applications. The

ALC655 integrates 50mW/20ohm headset audio amplifiers at Front-Out and Surr-Out, built-in 14.318M 24.576MHz

PLL and PCBEEP generator, those can save BOM costs. The ALC655 also supports the S/PDIF input and output

function, which can offer easy connection of PCs to consumer electronic products, such as AC3 decoder/speaker and

mini disk devices. ALC655 supports host/soft audio from Intel ICHx chipsets as well as audio controller based

VIA/SIS/ALI/AMD/nVIDIA/ATI chipset. Bundled Windows series drivers (WinXP/ME/2000/98/NT), EAX/Direct

Sound 3D/ I3DL2/ A3D compatible sound effect utilities (supporting Karaoke, 26-kind of environment sound

emulation,10-band equalizer), HRTF 3D positional audio and Sensaura™ 3D (optional) provide an excellent

entertainment package and game experience for PC users. Besides, ALC655 includes Realtek’s impedance sensing

techniques that makes device load on outputs and inputs can be detected

N/B Maintenance

N/B Maintenance

1.2.8 MDC: PCTEL MODEM DAUGHTER CARD PCT2303W (ASKEY

MiTac Secret

V1456VQL-P1)

The PCT2303W chipset is designed to meet the demand of this emerging worldwide AMR/MDC market. The

combination of PC-TEL’s well proven PCT2303W chipset and the HSP56TM MR software modem driver allows

systems manufactures to implement modem functions in PCs at a lower bill of materials (BOM) while maintaining

higher system performance.

PC-TEL has streamlined the traditional modem into the Host Signal Processing (HSP) solution. Operating with the

Pentium class processors, HSP becomes part of the host computer’s system software. It requires less power to operate

and less physical space than standard modem solutions. PC-TEL’s HSP modem is an easily integrated, cost-effective

Confidential Document

21

8011

8011

communications solution that is flexible enough to carry you into the future.

The PCT2303W chip set is an integrated direct access arrangement (DAA) and Codec that provides a programmable

line interface to meet international telephone line requirements. The PCT2303W chip set is available in two 16-pin

small outline packages (AC’97 interface on PCT303A and phone-line interface on PCT303W). The chip set eliminates

the need for an AFE, an isolation transformer, relays, opto-isolators, and 2-to 4-wire hybrid. The PCT2303W chip set

dramatically reduces the number of discrete components and cost required to achieve compliance with international

regulatory requirements. The PCT2303W complies with AC’97 Interface specification Rev. 2.1.

The chip set is fully programmable to meet world-wide telephone line interface requirements including those

described by CTR21, NET4, JATE, FCC, and various country-specific PTT specifications. The programmable

parameters of the PCT2303W chip set include AC termination, DC termination, ringer impedance, and ringer

threshold. The PCT2303W chip set has been designed to meet stringent world-wide requirements for out-of-band

N/B Maintenance

N/B Maintenance

energy, billing-tone immunity, lightning surges, and safety requirements.

MiTac Secret

Features :

Virtual com port with a DTE throughout up to 460.8Kbps.

G3 Fax compatible

Auto dial and auto answer

Ring detection

Codec/DAA Features :

AC97 2.1 compliant.

Confidential Document

22

8011

8011

86dB dynamic range TX/RX paths

2-4-wire hybrid

Integrated ring detector

High voltage isolation of 4000V

Support for “Caller ID”

Compliant with FCC Part68, CTR21, Net4 and JATE

Low power standby

Low profile SOIC package 16 pins 10x3x1.55mm

Low power consumption

10mA @ 3.3V operation

N/B Maintenance

N/B Maintenance

1mA @ 3.3V power down

MiTac Secret

Integrated modem codec

1.2.9 IEEE1394 VT6301S

The VT6301 IEEE 1394 OHCI Host Controller provides high performance serial connectivity. It implements the Link

and Phy layers for IEEE 1394-1995 High Performance Serial Bus specification release 1.0 and 1394a-2000. It is

compliant with 1394 Open HCI 1.0 and 1.1 with DMA engine support for high performance data transfer via a 32-bit

bus master PCI host bus interface. The VT6301 supports 100, 200 and 400 Mbit/sec transmission via an integrated 1-

port PHY. The VT6301 services two types of data packets: asynchronous and isochronous (real time). The 1394 link

core performs arbitration requesting, packet generation and checking, and bus cycle master operations. It also has root

Confidential Document

23

8011

8011

node capability and performs retry operations. The VT6301 is ready to provide industry-standard IEEE 1394

peripheral connections for desktop and mobile PC platforms. Support for the VT6301 is built into Microsoft Windows

98, Windows ME, Windows 2000, and Windows XP.

Features :

32 bit CRC generator and checker for receive and transmit data

On-chip isochronous and asynchronous receive and transmit FIFOs for packets (2K for general receive plus 2K for

isochronous transmit plus 2K for asynchronous transmit)

8 isochronous transmit contexts

4 isochronous receive contexts

3-deep physical post-write queue

N/B Maintenance

N/B Maintenance

2-deep physical response queue

Dual buffer mode enhancements

Skip Processing enhancements

Block Read Request handling

Ack_tardy processing

Confidential Document

MiTac Secret

24

8011

8011

N/B Maintenance

N/B Maintenance

1.2.10 System Flash Memory (BIOS)

Features :

Firmware Hub for Intel® 810, 810E, 815, 815E,815EP, 820, 840, 850 Chipsets

Flexible Erase Capability

Single 3.0-3.6V Read and Write Operations

Superior Reliability

Firmware Hub Hardware Interface Mode

1.2.11 Memory System

64MB, 128MB, 256MB, 512MB (x64) 200-Pin DDR SDRAM SODIMMs :

MiTac Secret

JEDEC-standard 200-pin, small-outline, dual in-line memory module (SODIMM)

Utilizes 200 Mb/s and 266 Mb/s DDR SDRAM components

64MB (8 Meg x 64 [H]); 128MB (16 Meg x 64, [H] and [HD]); 256MB (32 Meg x 64 [HD]); 512MB (64 Meg x

64 [HD])

Confidential Document

VDD= VDDQ= +2.5V ±0.2V

VDDSPD = +2.2V to +5.5V

2.5V I/O (SSTL_2 compatible)

Commands entered on each positive CK edge

DQS edge-aligned with data for READs; center-aligned with data for WRITEs

25

8011

8011

Internal, pipelined double data rate (DDR) architecture; two data accesses per clock cycle

Bidirectional data strobe (DQS) transmitted/received with data—i.e.,source-synchronous data capture

Differential clock inputs (CK and CK# - can be multiple clocks, CK0/CK0#, CK1/CK1#, etc.)

Four internal device banks for concurrent operation

Selectable burst lengths: 2, 4, or 8

Auto precharge option

Auto Refresh and Self Refresh Modes

15.6µs (MT4VDDT864H, MT8VDDT1664HD), 7.8125µs (MT4VDDT1664H, MT8VDDT3264HD,

MT8VDDT6464HD) maximum average periodic refresh interval

Serial Presence Detect (SPD) with EEPROM

N/B Maintenance

N/B Maintenance

Fast data transfer rates PC2100 or PC1600

Selectable READ CAS latency for maximum compatibility

Gold-plated edge contacts

MiTac Secret

1.2.12 LAN PHY: RTL8100C(L)

Confidential Document

The Realtek RTL8100C(L) is a highly integrated, cost-effective single-chip Fast Ethernet controller that provides 32-

bit performance, PCI bus master capability, and full compliance with IEEE 802.3u 100Base-T specifications and IEEE

802.3x Full Duplex Flow Control. It also supports the Advanced Configuration Power management Interface (ACPI),

PCI power management for modern operating systems that are capable of Operating System Directed Power

Management (OSPM) to achieve the most efficient power management possible. The RTL8100C(L) does not support

26

8011

8011

CardBus mode as the RTL8139C does. In addition to the ACPI feature, the RTL8100C(L) also supports remote wake-

up (including AMD Magic Packet, LinkChg, and Microsoft® wake-up frame) in both ACPI and APM environments.

The RTL8100C(L) is capable of performing an internal reset through the application of auxiliary power. When

auxiliary power is applied and the main power remains off, the RTL8100C(L) is ready and waiting for the Magic

Packet or Link Change to wake the system up. Also, the LWAKE pin provides 4 different output signals including

active high, active low, positive pulse, and negative pulse. The versatility of the RTL8100C(L) LWAKE pin provides

motherboards with Wake-On-LAN (WOL) functionality. The RTL8100C(L) also supports Analog Auto-Power-

down, that is, the analog part of the RTL8100C(L) can be shut down temporarily according to user requirements

or when the RTL8100C(L) is in a power down state with the wakeup function disabled. In addition, when the analog

part is shut down and the IsolateB pin is low (i.e. the main power is off), then both the analog and digital parts stop

functioning and the power consumption of the RTL8100C(L) will be negligible. The RTL8100C(L) also

supports an auxiliary power auto-detect function, and will auto-configure related bits of their own PCI power

N/B Maintenance

N/B Maintenance

management registers in PCI configuration space.

MiTac Secret

Features :

128 pin QFP/LQFP

Integrated Fast Ethernet MAC, Physical chip and transceiver in one chip

10 Mb/s and 100 Mb/s operation

Supports 10 Mb/s and 100 Mb/s N-way Auto-negotiation operation

PCI local bus single-chip Fast Ethernet controller

Supports 25MHz crystal or 25MHz OSC as the internal clock source. The frequency deviation of either crystal or

OSC must be within 50 PPM.

Confidential Document

27

8011

8011

Compliant to PC99/PC2001 standard

Supports Wake-On-LAN function and remote wake-up (Magic Packet*, LinkChg and Microsoft® wake-up frame)

Supports 4 Wake-On-LAN (WOL) signals (active high, active low, positive pulse, and negative pulse)

Supports auxiliary power-on internal reset, to be ready for remote wake-up when main power still remains off

Supports auxiliary power auto-detect, and sets the related capability of power management registers in PCI

configuration space.

Includes a programmable, PCI burst size and early Tx/Rx threshold.

Supports a 32-bit general-purpose timer with the external PCI clock as clock source, to generate timer-interrupt

Contains two large (2Kbyte) independent receive and transmit FIFOs

Advanced power saving mode when LAN function or wakeup function is not used

N/B Maintenance

N/B Maintenance

Uses 93C46 (64*16-bit EEPROM) to store resource configuration, ID parameter, and VPD data.

Supports LED pins for various network activity indications

Supports loopback capability

Half/Full duplex capability

Supports Full Duplex Flow Control (IEEE 802.3x)

MiTac Secret

Confidential Document

1.2.13 FIR TFDU6102

The TFDU6102 is a low–power infrared transceiver module compliant to the latest IrDA physical layer standard for

fast infrared data communication, supporting IrDA speeds up to 4.0 Mbit/s (FIR), HP-SIR[, Sharp ASK[ and carrier

based remote control modes up to 2 MHz. Integrated within the transceiver module are a photo PIN diode, an infrared

28

8011

8011

emitter (IRED), and a low–power CMOS control IC to provide a total front–end solution in a single package. Vishay

FIR transceivers are available in different package options, including this BabyFace package (TFDU6102), the

standard setting, once smallest FIR transceiver available on the market. This wide selection provides flexibility for a

variety of applications and space constraints. The transceivers are capable of directly interfacing with a wide variety of

I/O devices which perform the modulation/ demodulation function, including National Semiconductor’s PC87338,

PC87108 and PC87109, SMC’s FDC37C669, FDC37N769 and CAM35C44, and Hitachi’s SH3. At a minimum, a

VCC bypass capacitor are the only external components required implementing a complete solution. TFDU6102 has a

tri–state output and is floating in shut–down mode with a weak pull–up.

Features :

Compliant to the latest IrDA physical layer specification (Up to 4 Mbit/s), HP–SIR), Sharp ASK) and TV Remote

Control.

N/B Maintenance

N/B Maintenance

For 3.0 V and 5.0 V Applications

MiTac Secret

Operates from 2.7 V to 5.5 V within specification,

Low Power Consumption (< 3 mA Supply Current)

Power Shutdown Mode (< 5 _A Shutdown Current in Full Temperature Range)

Surface Mount Package

Confidential Document

Universal (9.7 × 4.7 × 4.0 mm3)

Tri–state–Receiver Output, floating in shutdown with a weak pull–up

High Efficiency Emitter

BabyFace (Universal) Package Capable of Surface Mount Soldering to Side and Top View Orientation

29

Loading...

Loading...