Page 1

Service

-

+

-+

-

+

+

Manual

PMD330 /N1M, /U1B, /F1B

PMD331 /N1M, /U1B, /F1B

PMD340 /N1M, /U1B, /F1M

PMD330/331/340

CD Player

PMD330

CD PLAYER

IR

TIME

21

POWER

LEVELHEADPHONE

MAXMIN

3

TEXT

8

6

7

MODE

5

4

PROG

PRESET

9

0

A-B PITCH

END

INDEX PITCH

CLEAREXIT

ON/OFF

ENTER

CONTRAST

PMD331 / 340

CD PLAYER

IR

216TIME

POWER

LEVELHEADPHONE

MAXMIN

3

TEXT

8

7

MODE

-

4

5

PROG

9

PRESET

0

A-B PITCH

END

INDEX PITCH BEND

--+

CLEAREXIT

ON/OFF

+

ENTER

CONTRAST PITCH / SEARCH

TABLE OF CONTENTS

SECTION PAGE

1. TECHNICAL SPECIFICATIONS ................................................................................................................. 1

2. SERVICE HINTS ....................................................................................................................................... 2

3. SERVICE TOOLS ..................................................................................................................................... 2

4. ADJUSTMENT AND SERVICE MODE .................................................................................................. 3

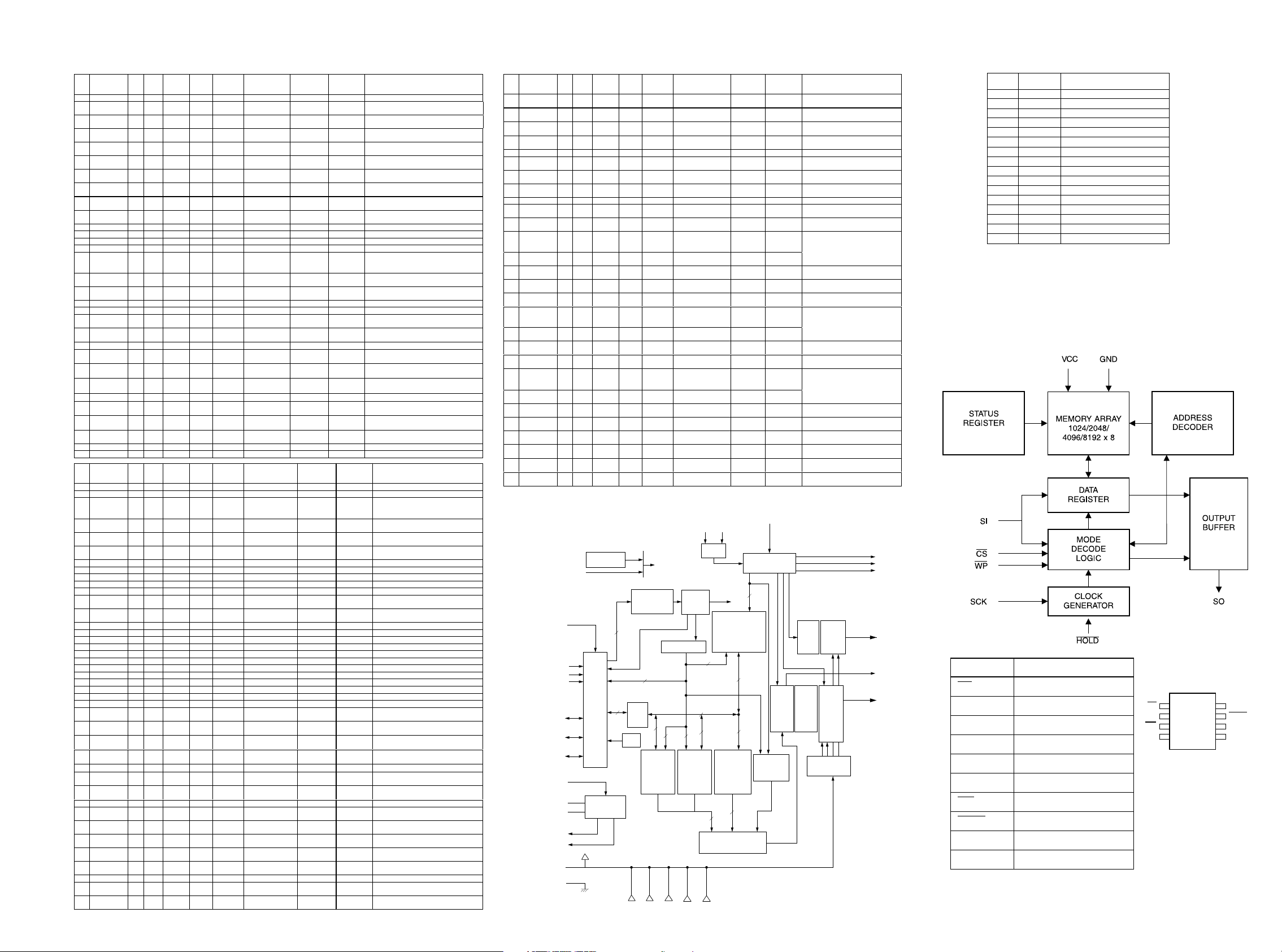

5. MICROPROCESSOR AND IC DATA..................................................................................................... 5

6. WIRING DIAGRAM ................................................................................................................................. 13

7. BLOCK DIAGRAM .................................................................................................................................. 15

8. SCHEMATIC DIAGRAM......................................................................................................................... 17

9. PARTS LOCATIONS .............................................................................................................................. 24

10. EXPLODED VIEW AND MECHANISM PARTS LIST......................................................................... 28

11. TECHNICAL DESCRIPTION ..................................................................................................................... 31

12. ELECTRICAL PARTS LIST ................................................................................................................... 33

Please use this service manual with referring to the user guide ( D.F.U. ) without fail.

PMD330 / 331 / 340

R

371K855010 MIT

3120 785 22250

First Issue 1999.12

Page 2

MARANTZ DESIGN AND SERVICE

MARANTZ AMERICA, INC.

WILDASH AUDIO SYSTEMS NZ

Using superior design and selected high grade components, MARANTZ company has created the ultimate in stereo sound.

Only original MARANTZ parts can insure that your MARANTZ product will continue to perform to the specifications for which

it is famous.

Parts for your

MARANTZ equipment are generally available to our National Marantz Subsidiary or Agent.

ORDERING PARTS :

Parts can be ordered either by mail or by Fax.. In both cases, the correct part number has to be specified.

The following information must be supplied to eliminate delays in processing your order :

1. Complete address

2. Complete part numbers and quantities required

3. Description of parts

4. Model number for which part is required

5. Way of shipment

6. Signature : any order form or Fax. must be signed, otherwise such part order will be considered as null and void.

USA

MARANTZ AMERICA, INC

440 MEDINAH ROAD

ROSELLE, ILLINOIS 60172

USA

PHONE : 630 - 307 - 3100

FAX : 630 - 307 - 2687

AMERICAS

SUPERSCOPE TECHNOLOGIES, INC.

MARANTZ PROFESSIONAL PRODUCTS

2640 WHITE OAK CIRCLE, SUITE A

AURORA, ILLINOIS 60504 USA

PHONE : 630 - 820 - 4800

FAX : 630 - 820 - 8103

AUSTRALIA

JAMO AUSTRALIA PTY LTD

1 EXPO COURT, P.O. BOX 350

MT. WAVERLEY VIC 3149

AUSTRALIA

PHONE : +61 - 3 - 9543 - 1522

FAX : +61 - 3 - 9543 - 3677

NEW ZEALAND

WILDASH AUDIO SYSTEMS NZ

14 MALVERN ROAD MT ALBERT

AUCKLAND NEW ZEALAND

PHONE : +64 - 9 - 8451958

FAX : +64 - 9 - 8463554

EUROPE / TRADING

MARANTZ EUROPE B.V.

P.O.BOX 80002, BUILDING SFF2

5600 JB EINDHOVEN

THE NETHERLANDS

PHONE : +31 - 40 - 2732241

FAX : +31 - 40 - 2735578

AUSTRALIA

TECHNICAL AUDIO GROUP PTY, LTD

558 DARLING STREET,

BALMAIN, NSW 2041,

AUSTRALIA

PHONE : 61 - 2 - 9810 - 5300

FAX : 61 - 2 - 9810 - 5355

THAILAND

MRZ STANDARD CO.,LTD

746 - 754 MAHACHAI ROAD.,

WANGBURAPAPIROM, PHRANAKORN,

BANGKOK, 10200 THAILAND

PHONE : +66 - 2 - 222 9181

FAX : +66 - 2 - 224 6795

TAIWAN

PAI- YUING CO., LTD.

6 TH FL NO, 148 SUNG KIANG ROAD,

TAIPEI, 10429, TAIWAN R.O.C.

PHONE : +886 - 2 - 25221304

FAX : +886 - 2 - 25630415

BRAZIL

PHILIP DA AMAZONIA IND. ELET. ITDA

CENTRO DE INFORMACOES AO

CEP 04698-970

SAO PAULO, SP, BRAZIL

PHONE : 0800 - 123123

FAX : +55 11 534. 8988

(Discagem Direta Gratuita)

CANADA

LENBROOK INDUSTRIES LIMITED

633 GRANITE COURT,

PICKERING, ONTARIO L1W 3K1

CANADA

PHONE : 905 - 831 - 6333

FAX : 905 - 831 - 6936

SINGAPORE

WO KEE HONG (S) PTE LTD

WO KEE HONG CENTRE

NO.23, LORONG 8, TOA PAYOH

SINGAPORE 319257

PHONE : +65 2544555

FAX : +65 2502213

MALAYSIA

WO KEE HONG ELECTRONICS SDN. BHD.

SUITE 8.1, LEVEL 8, MENARA GENESIS,

NO. 33, JALAN SULTAN ISMAIL,

50250 KUALA LUMPUR, MALAYSIA

PHONE : +60 3 - 2457677

FAX : +60 3 - 2458180

JAPAN

Technical

MARANTZ JAPAN, INC.

35- 1, 7- CHOME, SAGAMIONO

SAGAMIHARA - SHI, KANAGAWA

JAPAN 228-8505

PHONE : +81 42 748 1013

FAX : +81 42 741 9190

KOREA

MK ENTERPRISES LTD.

ROOM 604/605, ELECTRO-OFFICETEL, 16-58,

3GA, HANGANG-RO, YONGSAN-KU, SEOUL

KOREA

PHONE : +822 - 3232 - 155

FAX : +822 - 3232 - 154

SHOCK, FIRE HAZARD SERVICE TEST :

CAUTION : After servicing this appliance and prior to returning to customer, measure the resistance between either primary AC

cord connector pins ( with unit NOT connected to AC mains and its Power switch ON ), and the face or Front Panel of product and

controls and chassis bottom.

Any resistance measurement less than 1 Megohms should cause unit to be repaired or corrected before AC power is applied, and

verified before it is return to the user/customer.

Ref. UL Standard No. 813.

In case of difficulties, do not hesitate to contact the Technical

Department at above mentioned address.

991207MIT

Page 3

1. TECHNICAL SPECIFICATIONS

PMD330 PMD331 / PMD340

General specifications

System Compact Disc - Digital Audio

Number of channels 2

Compatible discs CD-DA, CD-R, CD-RW (12 cm, 8 cm)

Audio characteristics

Channels 2 channels

Frequency characteristics 20 Hz to 20 kHz +/- 0.3 dB

Dynamic range ≥ 90 dB (1 kHz)

S/N ratio ≥ 100 dB (1 kHz)

Total harmonic distortion (THD) 0.005 % (1 kHz)

Wow and flutter Quartz precision

Error correction method Cross-interleave Read-Solomon code (CIRC)

Analog output Pin jack,unbalanced (RCA) 2.0V RMS Stereo

XLR jack,balanced (XLR) +16 dBu /600 Ω, @ 0 dB FS

(variable range) (-11 dBu to +21 dBu, variable)

Digital output Pin jack (SPDIF) 0.5 Vp-p/75 Ω

XLR jack (SPDIF) 3.5 Vp-p/110 Ω

optical connector -19 dBm

Search precision 1 frame

Pitch control Maximum: +/-12% in 0.1% steps

Pitch bend control +/- 8 %

Strat timing 20 ms

Remote control

Infrared remote control input IN (IR sensor)

RC5 remote control input/output RCA IN (INT/EXT switch)/OUT

Remote control input/output D-SUB 25-Pin female

Optical anning method

Laser AlGaAs semiconductor

Wavelength 780 nm

Signal system

Sampling frequency 44.1 kHz

Quantization 16-bit linear/channel

Power supply section

AC power supply /F : 100V, AC 50/60Hz, /N : 230V, AC 50Hz, /U : 120V, AC 60Hz

Power consumption 12 W 17 W

Cabinet, etc.

External dimensions (W x H x D) 483 x 100 x 325 mm (19 x 3-15/16 x 12- 13/16 inches)

Weight 4.8 kg (10.6 lbs) 4.9 kg (10.8 lbs)

Operating temperature range + 5°C to + 35°C

Operating humidity range 5% to 90% (without dew)

Due to our continuing efforts to improve our products, the specifications and appearance of this product are subject to change without

prior notice.

2. SERVICE HINTS

3. SERVICE TOOLS

Audio signals disc 4822 397 30184

Disc without errors (SBC444)+

Disc with DO errors, black spots and fingerprints (SBC444A) 4822 397 30245

Disc (65 min 1kHz) without no pause 4822 397 30155

Max. diameter disc (58.0 mm) 4822 397 60141

Torx screwdrivers

Set (straight) 4822 395 50145

Set (square) 4822 395 50132

13th order filter 4822 395 30204

1 2

Page 4

4. ADJUSTMENT AND SERVICE MODE

FUNCTION

SW

Input

GPI *

Input

RC5

Input

FUNCTION

SW

Input

GPI *

Input

RC5

Input

Open/Close 28 -- 29 Preset 33 -- 34

Time 29 -- 30 Index + 17 8 18

CD-Text 30 -- 31 Index - 18 9 19

Mode 31 -- 32 0 1 -- 2

Stop *** -- -- -- 1 2 -- 3

Cue **** -- -- -- 2 3 -- 4

Play/Pause 11 -- -- 3 4 -- 5

Play -- 1 12 4 5 -- 6

Cue + Play 13 4 -- 5 6 -- 7

Pause -- 2 13 6 7 -- 8

Next 15 10 16 7 8 -- 9

Previous 16 11 17 8 9 -- 10

FF 19 6 20 9 10 -- 11

REW

20 7 21

Pitch Bend +*26 -- 27

END 22 -- 23 Pitch Bend - *27 -- 28

A-B Repeat 21 -- 22

Pitch + 24 ** 13 25

Service

-- -- 35

Pitch - 25 ** 14 26

Program 32 -- 33

Fader

(Normal)

--

Fader

Input

--

Pitch On/Off

23 15 24

Fader

(Invert)

--

Fader

Input

--

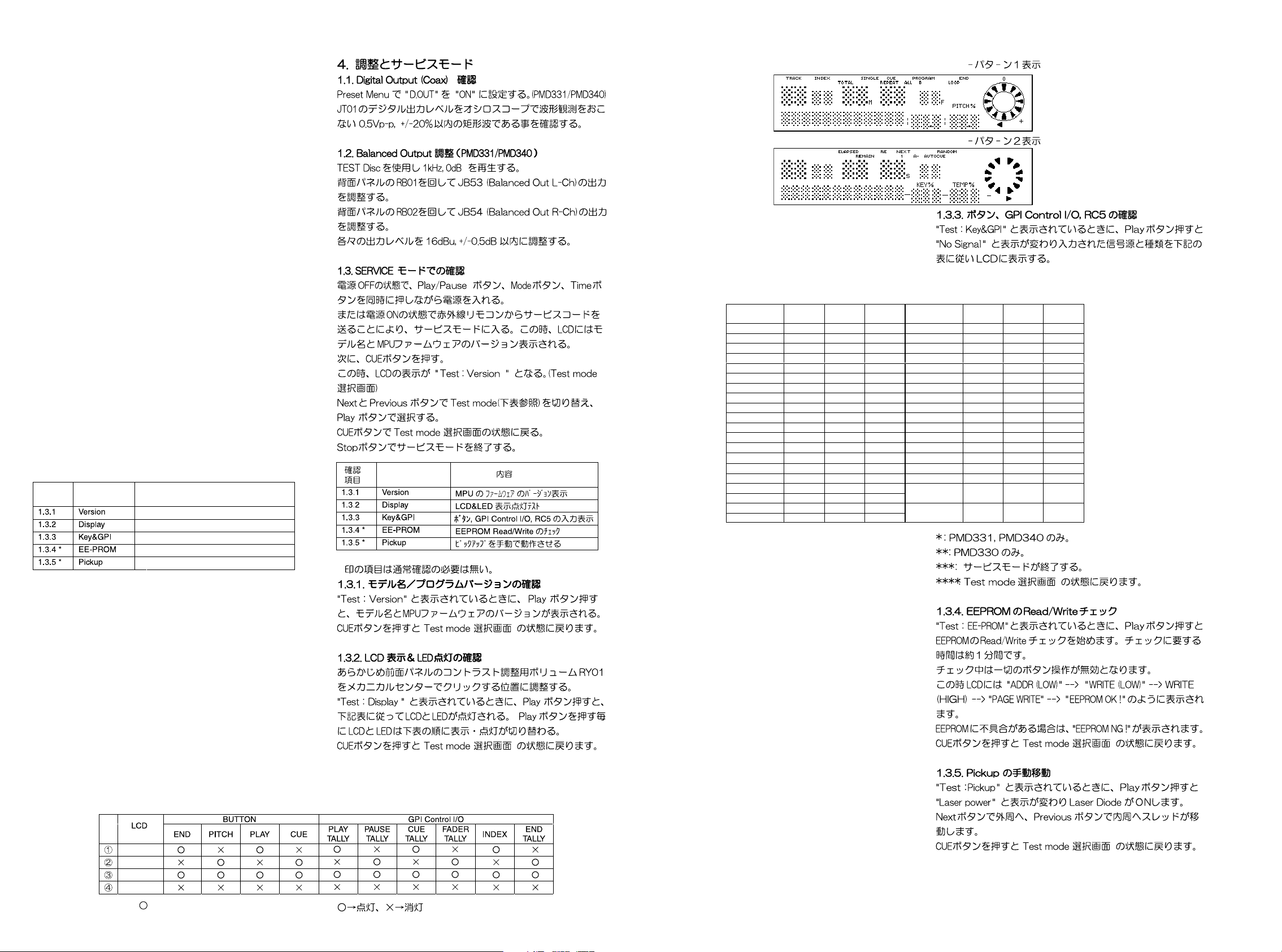

1.1. Digital Output (Coaxial) Check

On the preset menu, set "D.OUT" to "ON".(PMD331/PMD340)

Do waveform observation with the oscilloscope, and confirm

the digital output level of JT01 to be 0.5Vp-p, square wave

within ±20% .

1.2. Balanced Output Adjustment (PMD331/PMD340)

1kHz, 0 dB are played back by using TEST disc.

Turn RB01 on the rear panel, and adjust the output of JB53

(Balanced Out L-CH).

Turn RB02 on the rear panel, and adjust the output of JB54

(Balanced Out R-CH).

Adjust each output level to 16 dBu, within ±0.5dB.

1.3. Service Mode

1) With power off, simultaneously press the PLAY/PAUSE,

MODE and TIME buttons, and at the same time, press the

power button. At this time the LCD shows the model name

and firmware version.

2) Next, press CUE button.

3) At this time the LCD shows " Test : Version ". (TEST MODE

select menu)

4) The NEXT and PREVIOUS buttons change the TEST

MODE(refer to the chart below). The PLAY button selects it.

5) Pressing the CUE button returns to the TEST MODE select

menu.

6) Press the STOP button to exit the service mode.

INDEX

It is not usually necessary to confirm.

*

TEST

MODE

MPU firmware version check

LCD&LED test

Confirmation of Buttons, GPI Control I/O and RC5

Check of EEPROM Read/Write

Manual moving of the pickup

1.3.1. Model name and firmware version check

When the LCD shows "Test : Version", press the PLAY button,

to see the model name and the MPU firmware version.

Pressing the CUE button returns to the TEST MODE select

menu.

1.3.2. LCD and LED test

1) Set the LCD panel contrast adjustment screw to mechanical center. (you will feel a click.)

2) When the LCD shows "Test : Display", press the PLAY button.

3) The LCD and LED lights as the chart below.

4) Each time the PLAY/PAUSE button is pressed the LCD and

5) Pressing the CUE button returns to the TEST MODE select

LED change as shown in the chart below.

menu.

PATTERN 1

PATTERN 2

All light up

None light up

CONTENTS

: Light X : Not Light

3 4

*

Test mode

PATTERN 1

PATTERN 2

1.3.3. Confirmation of Buttons, GPI Control I/O and RC5

1) When the LCD shows "Test : Key&GPI", press the PLAY

button.

2) The LCD shows "No Signal".

3) Press a button, GPI Control I/O and RC5 are input, and the

LCD changes as shown in the chart below.

: PMD331, PMD340 only. ** : PMD330 only.

*

: The service mode is exited.

***

: The TEST MODE select menu is returned.

****

1.3.4. Check of EEPROM Read/Write

1) When the LCD shows "Test : EE-PROM", press the PLAY

button.

2) Check of EEPROM Read/Write begins. The check takes

about 1 minute. During the check pressing any button has

no effect.

3) At this time the LCD shows as the following order.

"ADDR (LOW)"--->"WRITE (LOW)"--->"WRITE (HIGH)"

--->"PAGE WRITE"--->"EEPROM OK!"

4) If there is an error in the EEPROM, the LCD shows

"EEPROM NG!".

5) Pressing the CUE button returns to the TEST MODE select menu.

1.3.5. Manual moving of Pick up

1) When the LCD shows "Test : Pickup", press the PLAY button.

2) The LCD shows "Laser power". The laser diode turns on.

3) Press the NEXT button. The sled will move to the outside.

4) Press the PREVIOUS button. The sled will move to the inside.

5) Pressing the CUE button returns to the TEST MODE select

menu.

Page 5

Pin Name Function

CS

Chip Select

SCK Serial Data Clock

SI Serial Data Input

SO Serial Data Output

GND Ground

VCC Power Supply

WP

Write Protect

HOLD

Suspends Serial Input

NC No Connect

DC Don’t Connect

1

2

3

4

8

7

6

5

CS

SO

WP

GND

VCC

HOLD

SCK

SI

5. MICROPROCESSOR AND IC DATA

PIN

PORT NAME

No.

1Vcc sys --- -- -- -- VCC Connected to the system power supply (+5V).

PB0

2

/TP8/TMO0

PB1

3

/TP9/TMIO1

PB2

4

/TP10/TMO2

PB3

5

/TP11/TMIO3

PB4

6

/TP12

PB5

7

/TP13

PB6

8

/TP14

PB7

9

/TP15

RESO

10

/ /_FWE

11 Vss sys -- -- -- -- VSS Connected to the system power supply (0V).

12 P90/TxD0 O O -- Low -- DEBUG_TXD TXD for debug mode.

13 P91/TxD1 O O -- Low -- FLASH_TXD TXD for FLASH MPU program.

14 P92/RxD0 I I -- Low -- DEBUG_RXD RXD debug mode.

15 P93/RxD1 I I -- High

P94

16

/SCK0/IRQ4

P95

17

/SCK1/IRQ5

18 P40 I/O O -- High OPEN ESA_SDTI RL5C357 SDTI Serial data output for ESA.

19 P41 I/O O -- High OPEN ESA_SCK RL5C357 SCK Serial clock data output for ESA.

20 P42 I/O O -- High OPEN ESA_XLT RL5C357 XLT

21 P43 I/O O Low High OPEN ESA_XSOE RL5C357 XSOE

22 Vss sys -- -- -- -- VSS Connected to the system power supply (0V).

23 P44 I/O O Low High OPEN ESA_XRST RL5C357 XRST

24 P45 I/O O Low High OPEN ESA_XWRE RL5C357 XWRE

25 P46 I/O O Low High OPEN ESA_XQOK RL5C357 XQOK

26 P47 I/O ! - High EXT_DW ESA_SDTO RL5C357 SDTO Serial data input from ESA.

27 P30 I/O

28 P31 I/O I High Low EXT_DW ESA_CHDT RL5C357 CHDT

29 P32 I/O O High Low -- CXD_RW_SEL CXD2585Q LOCK

30 P33 I/O O High Low -- CXD_LDON Laser diode ON/OFF control.

31 P34 I/O I Low -- CXD_FOK CXD2585Q FOK Focus lock detect input.

PIN

PORT NAME

No.

32 P35 I/O I Low Low -- CXD_LOCK CXD2585Q LOCK GFS l ock input.

33 P36 I/O I Low -- CXD_SSTP CXD2585Q SSTP Disc inside detect i nput.

34 P37 I/O O Low High -- CXD_XRST CXD2585Q XRST

35 Vcc sys -- -- -- -- V CC

36 P10 I/O O High Low -- CXD_DOUT_OFF CXD2585Q MD2

37 P11 I/O O High High -- CXD_MUTE CXD2585Q MUTE

38 P12 I/O O -- High -- CXD_DATA CXD2585Q DATA Serial data output for CXD2585Q.

39 P13 I/O O -- High -- CXD_XLAT CXD2585Q XLAT Serial latch data ou tput for CXD2585Q.

40 P14 I/O O -- High -- CXD_CLOK CXD2585Q CLOK Serial cl ock data output. For CXD2585Q

41 P15 I/O O -- High -- CXD_SCLK CXD2585Q SCLK Clock outp ut for SENS serial dat a read.

42 P16 I/O I -- Low -- CXD_SENS CXD2585Q SENS SENS signal inp ut.

43 P17 I/O I -- Low EXT_DW CXD_EMPH CXD2585Q EMPH

44 Vss sys -- -- -- -- VSS

45 P20 I/O I Low High EXT_UP SW_DATA0 KEY INPUT Key matrix signal input.

46 P21 I/O I Low High EXT_UP SW_DATA1 KEY INPUT Ditto.

47 P22 I/O I Low High EXT_UP SW_DATA2 KEY INPUT Ditto.

48 P23 I/O I Low High EXT_UP SW_DATA3 KEY INPUT Ditto.

49 P24 I/O I Low High EXT_UP SW_DATA4 KEY INPUT Ditto.

50 P25 I/O I Low High EXT_UP SW_DATA5 KEY INPUT Ditto.

51 P26 I/O I Low High EXT_UP SW_DATA6 KEY INPUT Ditto.

52 P27 I/O I Low High EXT_UP SW_DATA7 KEY INPUT Ditto.

53 P50 I/O O -- High -- SW_SCAN0 KEY SCAN Key matrix signal output.

54 P51 I/O O -- High -- SW_SCAN1 KEY SCAN Ditto.

55 P52 I/O O -- High -- SW_SCAN2 KEY SCAN Ditto.

56 P53 I/O O -- High -- SW_SCAN3 KEY SCAN Ditto.

57 Vss sys -- -- -- -- VSS

58 P60 I/O O -- Low -- SIF_ST 74HC4094 STR

59 P61 I/O O

60 P62 I/O O

61 P67/ -- -- OPEN PAI System clock output.

62 STBY/ sys I High High EXT_UP STBY

63 RES/ sys I Low High EXT_UP RES

64 NMI sys I -- Low EXT_DW NMI Not used.

65 Vss sys -- -- -- -- VSS

66 EXTAL sys I -- -- -- EXTAL X'tal

67 XTAL sys I -- -- -- XTAL X'tal

68 Vcc sys -- -- -- -- VCC

69 P63 I/O O -- Low -- SIF_CK

70 P64 I/O O -- Low -- DAC_DATA PCM17 10 MD/DM1 Serial data out put for D/A converter IC.

71 P65 I/O O

72 P66 I/O O

DEV

ICE

I/O

I/O O -- Low -- LCD_RS HD66712 RS

I/O O -- High -- LCD_RW HD66712 RW

I/O O -- Low -- LCD_E HD66712 E

I/O O Low High -- LCD_RESET HD66712 RESET

I/O I/O -- Low -- LCD_DB4 HD66712 DB4 LCD driver data bit 0.

I/O I/O -- Low -- LCD_DB5 HD66712 DB5 LCD driver data bit 1.

I/O I/O -- Low -- LCD_DB6 HD66712 DB6 LCD driver data bit 2.

I/O I/O -- Low -- LCD_DB7 HD66712 DB7 LCD driver data bit 3.

sys I Low Low EXT_DW FE W 74HC00

I/O I -- Low EXT_DW SIF_SO 74HC165 Parallel to serial IC (74HC165) data inpu t.

I/O O -- High

DEV

ICE

I/O

Φ

I/O ACTIVE INITIAL

!

Low High EXT_DW ESA_XWIH RL5C357 XWIH

I/O ACTIVE INITIAL

--

--

-- --

--

--

PULL

SIGNAL NAME

UP/DOWN

CXD_SQSO

INT UP

/FLASH_RXD

CXD_SQCK CXD2585Q SQCK Read out clock output for SQSO.

INT UP

PULL

UP/DOWN

Low OPEN SIF_LD 74HC165 LS/

Low -- SIF_SI 74HC4094 DA

Low -- DAC_CLK PCM1710 MC/DM2

Low -- DAC_LAT PCM1710 ML/DSD

SIGNAL NAME

CXD2585Q

/74HC00

CONNECT

DEVICE

NAME

CONNECT

DEVICE

NAME

74HC4094

74HC165CKCK

CONNECT

DEVICE

PORT NAME

SQSO

CONNECT

DEVICE

PORT

FUNCTION

LCD driver register select.

Instruction “L”, Data register “H”

LCD driver READ/WRITE.

READ “H”, WRITE “ L”

LCD driver enable.

Data READ/WRITE active signal.

LCD driver reset.

Normal “H” , Reset “L”

FLASH MPU program enable signal.

Enabled “H”

Sub-Q 80bit/PCM peak level data input &

CD-TEXT data input./RXD for FLASH MPU

program.

Serial latch data output for ESA.

Enabled signal for ESA serial data.

Enable “L ”

System reset output for ESA.

Reset “L ”

Write enable output for ESA.

Enable “L ”

Sub-code Q signal output for ESA.

OK “L”

Write enable signal from ESA.

Disable “L”

Data monitor input from ESA.

Monitoring “H ”

RF gain select for CD-RW

CD-RW “H”, CD-DA & CD-R “L”

FUNCTION

System reset output.

Reset “L”

Connected to the system power supply

(+5V).

Digital audio data output ON/OFF.

ON “H”

Mute control output.

Mute “H”

Emphasis enable/disable input.

Enable “H”, Disable “L”

Connected to the system power supply

(0V).

Connected to the system power supply

(0V).

Serial strobe data out put for serial to

parallel IC (74HC4094) .

Serial load data output for s erial to parallel

IC (74HC4094) .

Serial data output for serial to parallel IC

(74HC4094) .

Standby mode input for MPU.

Normal mode “H”

System reset input for MPU.

Reset “L ”

Connected to the system power supply

(0V).

System clock input.

Connected to 20MHz X' tal.

System clock output.

Connected to 20MHz X' tal.

Connected to the system power supply

(+5V).

Serial clock data output for por ts expand

IC

Serial clock data output for D/A c onverter

IC.

Serial latch data outpu t for D/A converter

IC.

PIN

PORT NAME

No.

73 MD0 sys I -- High EXT_UP MD0

74 MD1 sys I -- High EXT_UP MD1

75 MD2 sys I -- High EXT_UP MD2

76 Avcc sys I -- -- -- AV CC

77 Vref sys I -- -- -- VREF Ditto.

P70

78

/AN0

79 P71/AN1 I I Low High EXT_UP SW_SP1 KEY INPUT

80 P72/AN2 I I Low High EXT_UP SW_FADER KEY INPUT

81 P73/AN3 I I -- High EXT_UP EEPROM_SO AT 2 5 6 4 0 SO Serial data input for EEPROM.

82 P74/AN4 I I -- Low EXT_UP TRAY_SW_OPEN

83 P75/AN5 I I -- Low EXT_UP TRAY_SW_CLOSE

P76

84

/AN6/DA0

P77

85

/AN7/DA1

86 Avss sys I -- Low -- AVSS

P80

87

/IRQ0/

P81

88

/IRQ1/

P82

89

/IRQ2/

P83

90

/IRQ3/

91 P84 I/O O Low Low -- AUDIO_MUTE

92 Vss sys -- -- -- -- VSS

PA 0

93

/TP0/TCLKA

PA 1

94

/TP1/TCLKB

PA 2

95

/TP2/TIOCA0

PA 3

96

/TP3/TIOCB0

PA 4

97

/TP4/TIOCA1

PA 5

98

/TP5/TIOCB1

PA 6

99

/TP6/TIOCA2

PA 7

100

/TP7/TIOCB2

DEV

ICE

I/O ACTIVE INITIAL

I/O

I I Low High EXT_UP SW_SP0 KEY INPUT

I I -- Low UP/DW SYS_MODEL_SEL0 RU09,RU 05

I I -- Low UP/DW SYS_MODEL_SEL1 RU10,RU 11

I/O I -- Low -- CXD_SCOR CXD2585Q SCOR

I/O O Low High EXT_UP MONI_MUTE

I/O O High Low EXT_UP TRAY_DRV_OPEN LB1641 IN2

I/O O High Low EXT_UP TRAY_DRV_CLOSE LB1641 IN1

I/O I Low High EXT_DW ROT_DIAL_A DIAL(+)

I/O I Low High EXT_DW ROT_DIAL_B DIAL(-)

I/O O Low High -- RC5_MASK IR signal mas k SW.

I/O O -- Low -- RC5_OUTPUT RC5 signal output.

I/O I -- Low -- RC5_INPUT SPS-446-4 RC5 signal input.

I/O O High High EXT_UP EEPROM_CS AT2 5 6 4 0 CS

I/O O -- High EXT_UP EEPROM_SI

I/O O -- High EXT_UP EEPROM_CLK

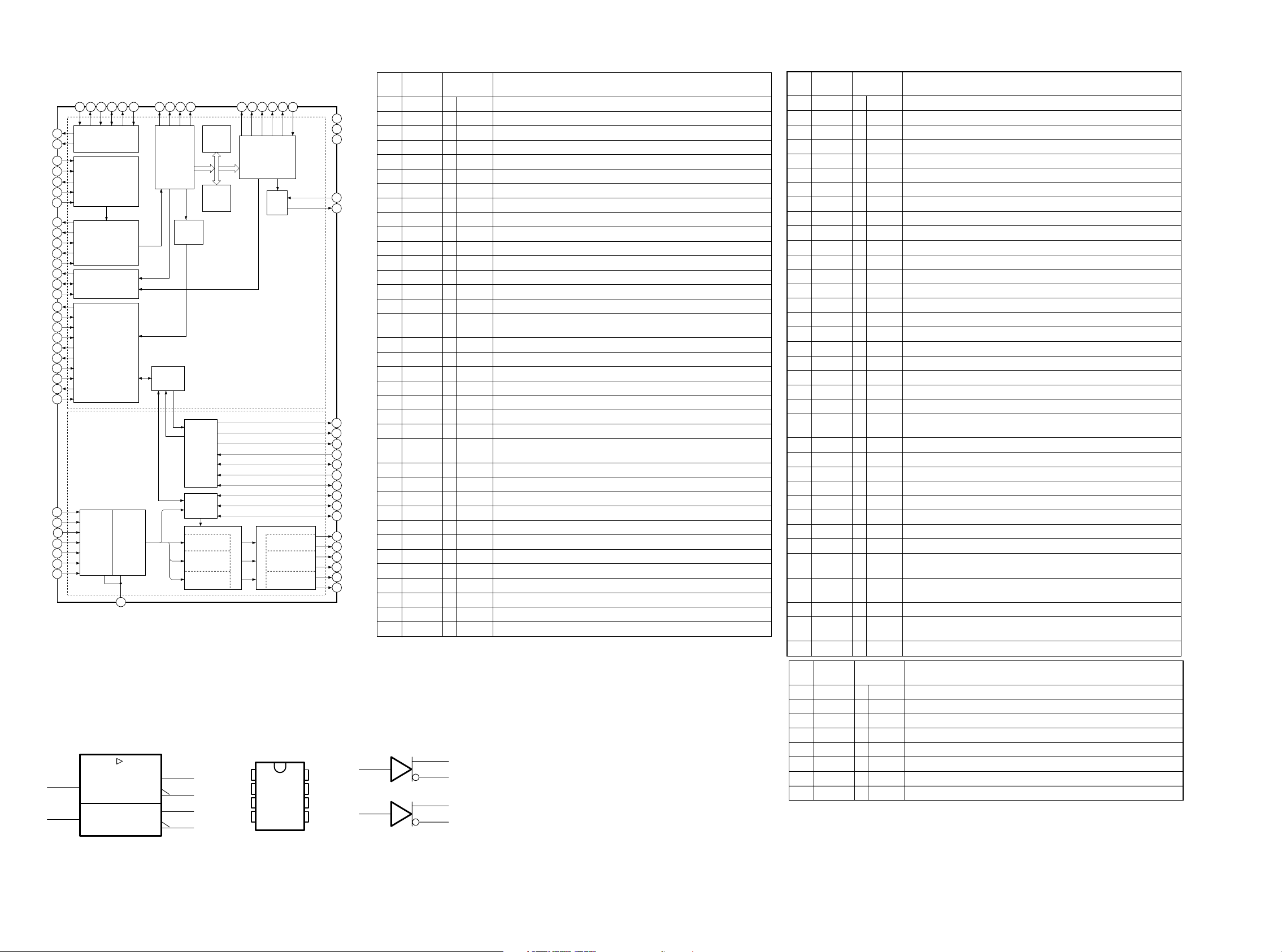

QY01 : HD66712

Reset circuit

ACL

*

RESET

IM

System

*

RS/CS

R/SCLK

RW/SID

DB4~DB7

DB3~DB0

DB0~SOD

Vci

C1

C2

V5OUT2

V5OUT3

V

CC

GND

interface

Serial

4 bits

8 bits

output

buffer

Booster

8

PULL

Address counter

8

3

RAM

SIGNAL NAME

Instruction

decoder

Character

generator

RAM

(CGRAM)

64 bytes

UP/DOWN

Instruction

register

(IR)

8

7

7

Data

register

(DR)

Busy

flag

Segment

(SGRAM)

16 bytes

V1 V2 V3 V4 V5

OSC1 OSC2

7

CONNECT

DEVICE

NAME

TRAY OPEN

SW

TRAY

CLOSE SW

AT2 5 6 4 0

AT2 5 6 4 0

CPG

Timing generator

Display data RAM

(DDRAM)

80x8 bits

7

8

8

Character

generator

ROM

(CGROM)

9,600 bits

5

5/6

Parallel/serial

converter

8

8

and smooth scroll circuit

CONNECT

DEVICE

PORT

Mode select input for MPU.

Mode7 “H”

Mode select input for MPU.

Mode7 “H”

Mode select input for MPU.

Mode7 “H” , FLASH MPU program “L”

Connected to the system power supply

(+5V).

PLAY/PAUSE button input.

Active “L

CUE button input.

Active “L”

FADER SW input.

Active “L”

Tray Open SW input.

Open “L”

Tray Close SW input.

Close “L”

( SEL0,SEL1);

PMD330=(0,0), PMD331=(0,1)

PMD340=(1,0)

Connected to the system power supply

(0V).

Detected from Sub code think signal.

Detected “H”

Audio pre-mute control output.

MUTE “L”

(IN1,IN2), (1,0) CW LOAD,

(0,1) CCW UNLOAD,

(0,0) or (1,1) STOP

Audio mute control output.

MUTE “L”

Connected to the system power supply

(0V).

Rotary encoder input.

CW (Froward) “H ”, CCW (Reverse) “L”

24puls/360˚

Chip select output for EEPROM.

60-bit

shift

register

Enable “H”, Disable “L”

34bit

shift

register

60-bit

latch

circuit

SI Serial data output for EEPROM.

SCK Serial clock data output for EEPROM.

EXT

7

Cursor and

blink

controller

FUNCTION

Common

signal

driver

Segment

signal

driver

LCD drive

voltage selector

CL1

CL2

M

COM0~

COM33

SEG1~

SEG60

D

5 6

Q201/Q202 : TDA7073AQU01 : H8/3062

PIN SYMBOL DESCRIPTION

1 IN1- negative input 1

2 IN1+ positive input 1

3 n.c. not connected

4 n.c. not connected

5 VP positive supply voltage

6 IN2+ positive input 2

7 IN2- negative input 2

8 n.c. not connected

9 OUT2+ positive output 2

10 GND2 ground 2

11 n.c. not connected

12 OUT2- negative output 2

13 OUT1- negative output 1

14 GND1 ground 1

15 n.c. not connected

16 OUT1+ positive output 1

QU03 : AT2560

Page 6

Pin

NO.

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

I

I

I

I

I

I

I

O

I

O

I

I

I

O

I

O

I

I

I/O

O

I

I

O

O

O

O

O

I

I

O

Analog

-

1, 0

Analog

1, Z, 0

1, 0

1, Z, 0

1, 0

1, 0

1, 0

1, 0

1, 0

Test. Normally, GND.

Center voltage input.

Focus error signal input.

Sled error signal input.

Tracking error signal input.

Center servo analog input.

RF signal input.

Test. No connected.

Analog GND.

Constant current input for operational amplifier.

Analog power supply.

EFM full-swing output. (Iow = Vss, high = VDD)

Asymmetry comparator voltage input.

EFM signal input.

Analog GND.

Multiplier VCO1 control voltage input.

Master PLL filter output (slave = digital PLL).

Master PLL filter input.

Master PLL charge pump output.

Analog power supply.

Asymmetry circuit constant current input.

Wide-band EFM PLL VC02 control voltage input.

Wide-band EFM PLL VC02 oscillation output. Serves as

wide-band EFM PLL clock input by switching with the command.

Wide-band EFM PLL charge pump output.

Digital power supply.

Asymmetry circuit on/off (low = oft, high = on).

Digital Out on/oft control (low = off, high = on).

Digital Out output.

D/A interface. LR clock output. f = Fs

D/A interface. Serial data output (two's complement, MSB first).

D/A interface. Bit clock output.

Outputs a high signal when the playback disc has emphasis, and a low

signal when there is no emphasis.

Crystal selection input. Low when the crystal is 16.9344MHz; high when it is

33.8688MHZ.

Digital GND.

Crystal oscillation circuit input. When the master clock is input externally,

input it from this pin.

Crystal oscillation circuit output.

TES1

VC

FE

SE

TE

CE

RFDC

ADIO

AV

SS

0

IGEN

AV

DD

0

ASYO

ASYI

RFAC

AV

SS

1

CLTV

FILO

FILI

PCO

AV

DD

1

BIAS

VCTL

V16M

VPCO

DV

DD

2

ASYE

MD2

DOUT

LRCK

PCMD

BCK

EMPH

XTSL

DV

SS

2

XTAI

XTAO

Symbol I/O Description

-

-

-

-

-

-

-

-

Pin

NO.

73

74

75

76

77

78

79

80

O

O

O

O

I

I

O

I

1, 0

1, 0

1, 0

1, 0

1, 0

Serial data output in servo block.

Serial data readout clock output in servo block.

Serial data latch output in servo block.

Sub-Q 80-bit, PCM peak or level data outputs. CD TEXT data output.

SQSO readout clock input.

GRSCOR resynchronization input.

Sub-Q P to W serial output.

SBSO readout clock input.

SOUT

SOCK

XOLT

SQSO

SQCK

SCSY

SBSO

EXCK

Symbol I/O Description

Notes)

* PCMD is a MSB first, two's complement output.

* GTOP is used to monitor the frame sync protection status. (High: sync protection window released.)

* XUGF is the frame sync obtained from the EFM signal, and is negative pulse. It is the signal before sync protection.

* XPCK is the inverse of the EFM PLL clock. The PLL is designed so that the falling edge and the EFM signal

Atransition point coincide.

* The GFS signal goes high when the frame sync and the insertion protection timing match.

* RFCK is derived from the crystal accuracy, and has a cycle of 136us. (during normal speed)

* C2PO represents the data error status.

* XROF is generated when the 32K RAM exceeds the +-28F jitter margin.

QD01 : CXD2585Q

Pin

Symbol I/O Description

V16M

XTAI

XTSL

VCTL

VPCO

XTAO

69

60

72

71

27

FSTO

C4M

16

50

RFAC

ASYI

49

ASYO

48

ASYE

62

BIAS

57

12

XPCK

53

FILO

FILI

54

PCO

55

52

CLTV

25

MDP

LOCK

24

PWMI

23

7

SENS

4

DATA

5

XLAT

6

CLOK

SCOR

15

SBSO

79

80

EXCK

SCSY

78

SQSO

76

SQCK

77

RFDC

43

CE

42

TE

41

SE

40

FE

39

VC

38

IGEN

46

QT52 : SN75158

3

1A

5

2A

Generator

Asymmetry

Corrector

Interface

OPAmp

Analog SW

58

Clock

Digital

PLL

Digital

CLV

CPU

59

11

demodurator

Sequencer

A/D

Converter

44

ADIO

XUGF

13

EFM

Servo

Auto

EMPH

GFS

68

10

Sub Code

Processor

FOCUS SERVO

SLED SERVO

2

1

6

7

WFCK

Corrector

SERVO

Interface

MIRR

DFCT

FOK

SERVO DSP

TRACKING

SERVO

1Y

1Z

2Y

2Z

Error

32K

RAM

17

1Z

1Y

1A

GND

WDCK

C2PO

LRCK

65

66

14

D/A

Interface

Digital

OUT

Signal processor biock

PWM GENERATOR

FOCUS PWM

GENERATOR

TRACKING PWM

GENERATOR

GENERATOR

1

2

3

4

MUTE

BCK

PCMD

67

3

Servo block

SLED PWM

8

7

6

5

TES1

37

TEST

36

XRST

2

63

MD2

DOUT

64

73

SOUT

74

SOCK

XOLT

75

SCLK

8

COUT

19

SSTP

26

ATSK

9

MIRR

20

21

DFCT

22

FOK

33

FFDR

34

FRDR

31

TFDR

32

TRDR

29

SFDR

30

SRDR

1A

V

CC

2Z

2Y

2A 7

2A

7 8

No.

1

DV

2

XRST

3

MUTE

4

DATA

5

XLAT

6

CLOK

7

SENS

8

SCLK

9

ATSK

10

WFCK

11

XUGF

12

XPCK

13

GFS

14

C2PO

15

SCOR

16

C4M

17

WDCK

18

DV

19

COUT

20

MIRR

21

DFCT

22

FOK

23

PWMI

24

LOCK

25

MDP

26

SSTP

27

FSTO

28

DV

29

SFDR

30

SRDR

31

TFDR

32

TRDR

33

FFDR

34

FRDR

35

DV

36

TEST

3

5

DD

0

I

I

I

I

I

O

I

I/O

O

O

O

O

O

O

O

Power supply.

System reset. Reset when low.

Mute input (low: off, high: on)

Serial data input from CPU.

Latch input from CPU. Serial data is latched at the falling edge.

Serial data transfer clock input from CPU.

SENS output to CPU.

1, 0

SENS serial data readout clock input.

Anti-shock input/output.

1, 0

WFCK output.

1, 0

XUGF output. MNTO or RFCK is output by switching with the command.

1, 0

XPCK output. MNTI is output by switching with the command.

1, 0

GFS output. MNT2 or XROF is output by switching with the command.

1, 0

C2P0 output. MNT3 or GTOP is output by switching with the command.

1, 0

Outputs a high signal when either subcode sync SO or S1 is detected.

1, 0

4.2336MHz output. 1/4 frequency division output for V16M in CAV-W mode

1, 0

or variable pitch mode.

Word clock output. f = 2Fs. GRSCOR is output by the command switching.

1, 0

O

-

SS

0

I/O

I/O

I/O

I/O

I

I/O

1, Z, 0

O

I

O

-

DD

1

O

O

O

O

O

O

-

SS

1

I

1Y

1

1Z

6

2Y

Digital GND.

Track count ,signal I/O.

1, 0

Mirror signal I/O.

1, 0

Detect signal I/O.

1, 0

Focus OK signal I/O.

1, 0

Spindle motor external control input.

GFS is sampled at 460Hz; when GFS is high, this pin outputs a high signal.

1, 0

If GFS is low eight consecutive samples, this pin outputs low. Input when LKIN=1.

Spindle motor servo control output.

Disc innermost track detection signal input.

2/3 frequency division output for XTAI pin.

1, 0

Digital power supply.

Sled drive output.

1, 0

Sled drive output.

1, 0

Tracking drive output.

1, 0

Tracking drive output.

1, 0

Focus drive output.

1, 0

Focus drive output.

1, 0

Digital GND.

Test. Normally, GND.

2Z

Page 7

Q501 : PCM1710

DIN

CLKO

XTI

XTO

V

2R

CC

OUT

1

2

3

4

5

6

7

8

DD

9

10

11

12

13

R

14

LRCIN

BCKIN

DGND

V

AGND2R

EXT1R

EXT2R

V

AGND1

Input

Interface

Timing

Control

5-Level ∆Σ DAC

Right

Digital

Filter

Noise

Shaper

Mode

Control

5-Level ∆Σ DAC

Left

Low-Pass

Filter-Left

Output

Amplifier

Left

28

27

26

25

24

23

22

21

20

19

18

17

16

15

ML/DSD

MC/DM2

MD/DM1

MUTE

MODE

CKSL

DGND

V

DD

2L

V

CC

AGND2L

EXT1L

EXT2L

L

V

OUT

1

V

CC

PIN NAME NUMBER FUNCTION

Input Interface Pins

LRCIN 1 Sample Rate Clock Input. Controls the update rate (fs).

DIN 2 Serial Data Input. MSB first, right justified format contains a frame of 16-bit or 20-bit data.

BCKIN 3 Bit Clock Input. Clocks in the data present on DIN input.

Mode Controls and Clock Signals

CLKO 4 Buffered Output of Oscillator. Equivalent to fs.

XTI 5 Oscillator Input (External Clock Input). For an internal clock, tie XTI to one side of the crystal oscillator. For an external clock,

tie XTI to the output of the chosen external clock.

XTO 6 Oscillator Output. When using the internal clock, tie to the opposite side (from pin 5) of the crystal oscillator. When using an

external clock, leave XTO open.

CKSL 23 System Clock Select. For 384fs, tie CKSL “High”. For 256fs, tie CKSL “Low”.

MODE 24 Operation Mode Select. For serial mode, tie MODE “High”. For parallel mode, tie MODE “Low”.

MUTE 25 Mute Control. To disable soft mute, tie MUTE “High”. To enable soft mute, tie MUTE “Low”.

MD/DM1 26 Mode Control for Data/De-emphasis. See “Mode Control Functions” on page 11.

MC/DM2 27 Mode Control for BCKIN/De-emphasis. See “Mode Control Functions” on page 11.

ML/DSD 28 Mode Control for WDCK/Double speed dubbing. See “Mode Control Functions” on page 11.

Analog Functions

V

R 13 Right Channel Analog Output.

OUT

L 16 Left Channel Analog Output.

V

OUT

Power Supply Connections

DGND 7, 22 Digital Ground.

V

DD

2R 9 Analog Power Supply (+5V), Right Channel DAC.

V

CC

AGND2R 10 Analog Ground (DAC), Right Channel.

EXT1R 11 Output Amplifier Common, Right Channel. Bypass to ground with a 10µF capacitor.

EXT2R 12 Output Amplifier Bias, Right Channel. Connect to EXT1R.

AGND 14 Analog Ground.

V

CC

EXT2L 17 Output Amplifier Bias, Left Channel. Connect to EXT1L.

EXT1L 18 Output Amplifier Common, Left Channel. Bypass to ground with a 10µF capacitor.

AGND2L 19 Analog Ground (DAC), Left Channel.

2L 20 Analog Power Supply (+5V), Left Channel DAC.

V

CC

8, 21 Digital Power Supply (+5V).

15 Analog Power Supply (+5V).

Q101 : TZA1022

AP5S

AP1S

AP4C

AP3C

AP2C

LG

MI

VGAP

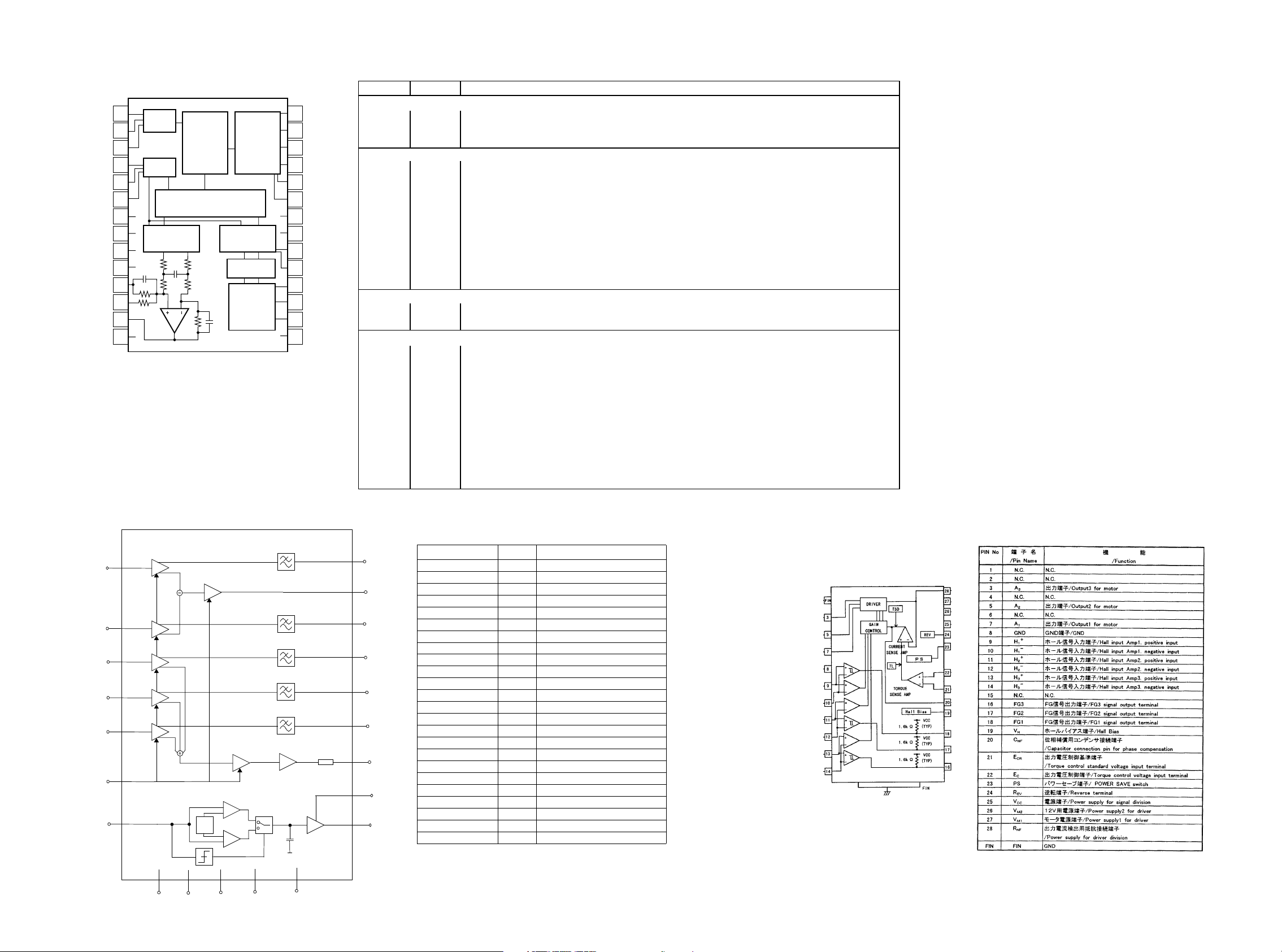

Q251 : BA6856FP

OD5

SYMBOL PIN DESCRIPTION

OD2 1 output photo diode amplifier 2

OD3 2 output photo diode amplifier 3

I/V

FTC

OD4 3 output photo diode amplifier 4

OD5 4 output photo diode amplifier 5

OD1 5 output photo diode amplifier 1

OD1

PWRON 6 power on switch

RF 7 output data signal

OD4

V

V

DDRF

DD

8 RF ampliÞer supply voltage

9 supply voltage

GND 10 ground

OD3

GND

V

DDL

RF

11 ground RF amplifier

12 laser supply voltage

LO 13 current output for the laser diode

OD2

MI 14 Monitor input

n.c. 15 not connected

n.c. 16 not connected

I/V

1k5

RF

AP1S 17 Input photo diode amplifier (satellite)

AP2C 18 Input photo diode amplifier (central)

n.c. 19 not connected

V

DDL

V/I

V/I

V/I

LO

FTC 20 output fast track counting

LG 21 CD/CDRW gain switch

AP3C 22 Input photo diode amplifier (central)

AP5S 23 Input photo diode amplifier (satellite)

AP4C 24 Input photo diode amplifier (central)

V

DDRF

GND

V

DD

GND

RF

PWRON

9 10

Page 8

Q301 : RL5C357

LOGIC

Pin PIN NAME I/O FUNCTION

HL

1 VCC -- POWER SUPPLY -- -2 XQOK Ipu SUB CODE-Q OK SIGNAL FROM CPU -- OK

3 XWRE Ipu WRITE ENABLE SIGNAL FROM CPU -- PERMIT

4 XEMP O READ INHIBIT SIGNAL TO CPU -- INHIBIT

5 XWIH O WRITE INHIBIT SIGNAL TO CPU -- INHIBIT

6 XCAS2 O DRAM CAS2 CONTROL -- --

7 CHDT

O

DATA COMPARATIVE MONITOR SIGNAL

OUTPUT TO CPU

COMPARE

-8 A10 O DRAM ADDRESS 10 -- -9 CLK I 16.9344MHz CLOCK INPUT -- --

10 GND -- GROUND -- -11 DATI Ics AUDIO DATA INPUT -- -12 LRCI Ics AUDIO L/R CLOCK INPUT Lch Rch

13 BCKI Ics AUDIO BIT CLOCK INPUT -- -14 BCKO O AUDIO BIT CLOCK OUTPUT -- -15 LRCO O AUDIO L/R CLOCK OUTPUT Lch Rch

16 DATO O AUDIO DATA OUTPUT -- --

17 XROF Ics RAM OVERFLOW FROM SIGNAL PROCESSOR IC --

OVER

FLOW

18 RFCK Ipu

FRAME CLOCK FROM SIGNAL PROCESSOR IC,

DERIVED FROM THE CRYSTAL ACCURACY

-- --

19 SCOR I

SUB CODE SYNC DETECT SIGNAL FROM

SIGNAL PROCESSOR IC

-- --

20 XRST Ics SYSTEM RESET -- RESET

21 SDTO O SERIAL DATA OUTPUT TO CPU -- --

22 XSOE Ipu

SERIAL DATA OUTPUT PERMISSION SIGNAL

INPUT FROM CPU

--

PERMIT

23 TEST Ipd TEST MODE -- -24 XLT Ics LATCH INPUT FROM CPU -- -25 SDTI Ics SERIAL DATA INPUT FROM CPU -- --

26 SCK Ics

SERIAL DATA TRANSFER CLOCK INPUT FROM

CPU

-- --

27 XCAS1/XOE O DRAM CAS1/OE CONTROL -- -28 XCAS0 O DRAM CAS0 CONTROL -- -29 D2 I/O DRAM DATA 2 -- -30 D3 I/O DRAM DATA 3 -- -31 D0 I/O DRAM DATA 0 -- -32 D1 I/O DRAM DATA 1 -- -33 XWE O DRAM WE CONTROL -- -34 XRAS O DRAM RAS CONTROL -- -35 A9 O DRAM ADDRESS 9

36 A8 O DRAM ADDRESS 8

37 A7 O DRAM ADDRESS 7

38 A6 O DRAM ADDRESS 6

39 A5 O DRAM ADDRESS 5

40 A4 O DRAM ADDRESS 4

41 A0 O DRAM ADDRESS 0

42 A1 O DRAM ADDRESS 1

43 A2 O DRAM ADDRESS 2

44 A3 O DRAM ADDRESS 3

PIN NO. SYMBOL NAME AND FUNCTION

1 STR strobe input

2 D serial input

3 CP clock input

4, 5, 6, 7,14, 13, 12, 11 QP

0

to QP

7

parallel outputs

8 GND ground (0 V)

9, 10 QS

1

,Q S

2

serial outputs

15 OE output enable input

16 V

CC

positive supply voltage

SCK

XROF XLT

BCKI XSOE

LRCI SDTI

DATI SDTO

SIGNAL

PROCESSOR

CPU I/F

I/F

XQOK ADPCM ADPCM

XWRE

ENCODER DECODER

CHDT CPU

XEMP I/F

XWIH DRAM CONTROLLER

DAC

I/F

DATO

LRCO

BCKO

CLK

XRST

TEST

XRAS

XCASO

XCAS1/XOE

XCAS2

XWE

A0 - A10

D0 - D3

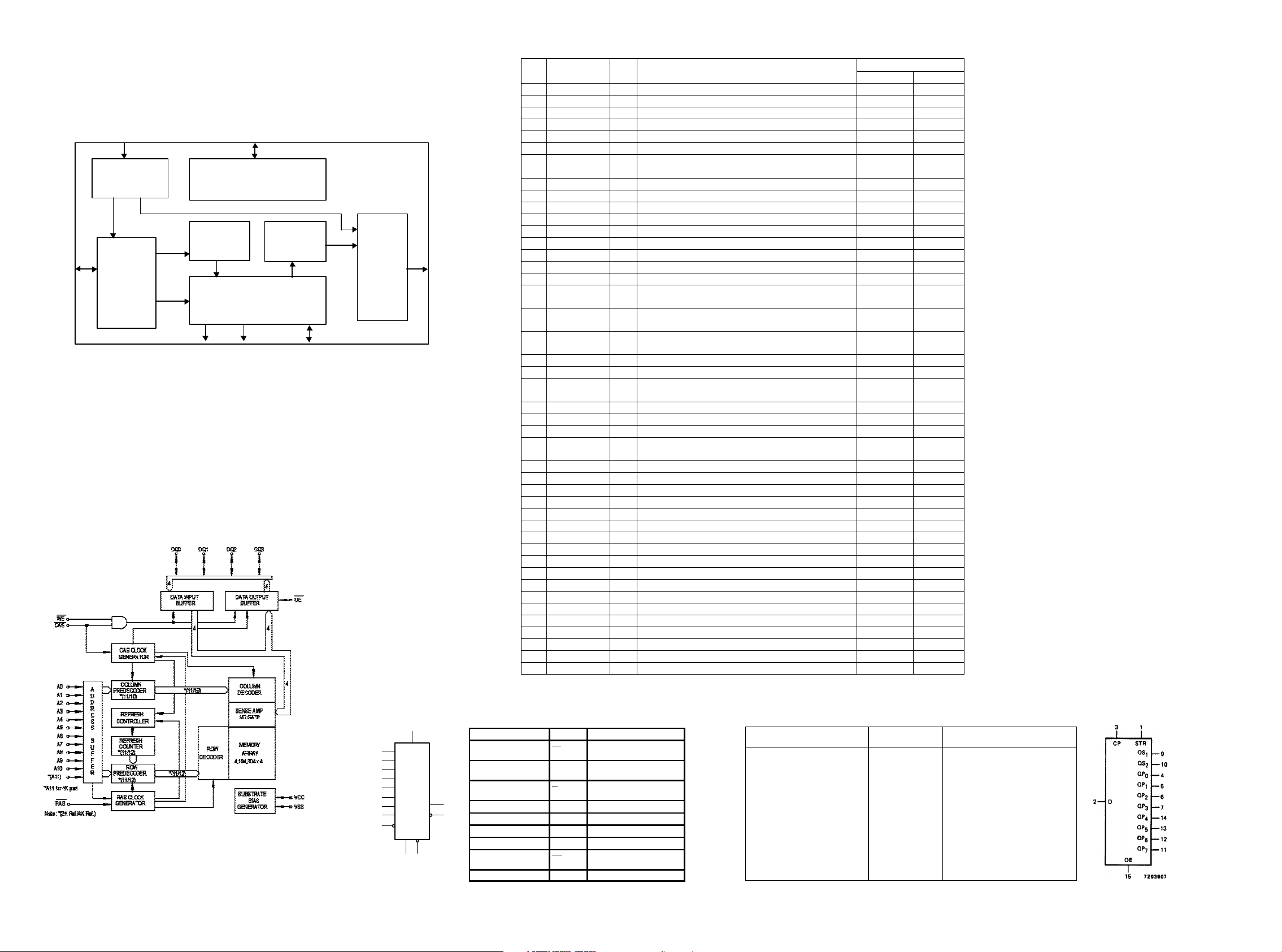

Q302 : HY5117400BJ-60

11 12

QU57 QU58 : 74HC165

11

12

13

14

3

4

5

6

1

D

0

D

1

D

2

D

3

D

4

D

5

D

6

D

7

PL

D

CP

215

10

S

CE

QU04 QU56 : 74HC4094

PIN NUMBER SYMBOL FUNCTION

1

2 CP

7 Q

9

Q

7

Q

7

8 GND Ground (0 V)

7

9 Q

10 D

11, 12, 13, 14, 3, 4, 5, 6 D0 to D7Parallel data inputs

15 CE

16 V

PL

Asynchronous parallel load

input (active LOW)

Clock input (LOW to

HIGH, edge-triggered)

Complementary output from

7

the last stage

Serial output from last stage

7

Serial data input

S

Clock enable input

(active LOW)

Positive supply voltage

CC

Page 9

6. WIRING DIAGRAM

SW PCB (P851)

31

J852

31

W802

31

31

J802

LIVE

NEUTRAL

TRANS PCB (P801)

001M

TRAY MOTOR

TRAY OUT

TRAY IN

31

J851

5

4

3

2

1

31

5

4

3

2

TRM+

TRM-

TROU

TRIN

W002

W801

COM

015M

NEUTRAL SIDE

WHT(U,F)

BLUE(N)

LIVE SIDE

RED (U,F)

BROWN(N)

NEUTRAL

J001

FG

LIVE

INSIDE VIEW

W003(ONLY PMD3xxU,PMD340N)

J801

5

5

4

3

2

11

AC9V

AC9V

4

3

AC20V

2

GND

AC20V

1

JM01

5

5

TRM+

4

3

2

1

TRM-

4

3

GND

2

TRAY_SW_OPEN

1

TRAY_SW_CLOSE

W001

3:+12VM

2:GND

1:+6VM

3P PLUG (PMD3xxU,PMD340N)

2P PLUG (PMD33xN,PMD3xxF)

8:SRDR

6:MDP

5:IN DET

4:GND

9:TFDR

7:SFDR

11:FFDR

10:TRDR

12:FRDR

14:VC

13:LD

16:FE

15:RF

17:TE

20:RW

19:+5VA

18:DOUT_OFF

(5PIN FFC)

MAIN PCB (PD01)

8:LCD_E

6:LCD_DB4

5:LCD_DB5

4:LCD_DB6

3:LCD_DB7

2:+5VDM

1:+6VM

9:LCD_RW

7:LCD_RESET

11:IR

10:LCD_RS

JT52

W054

JT03

16:PLAY

12:PLAY_LED

15:PITCH_LED

14:END_LED

13:CUE_LED

17:CUE

54321

54321

+5V

GND

+5V

D_OUT

24:SW_DATA5

22:SW_DATA7

26:SW_DATA3

25:SW_DATA4

23:SW_DATA6

21:SW_SCAN0

20:SW_SCAN1

19:SW_SCAN2

18:SW_SCAN3

XLR PCB (PB01)

(PMD331,PMD340)

JB52

54321

W053

(5PIN FFC)

JB32

GND

29:SW_DATA0

30:GND

28:SW_DATA1

27:SW_DATA2

5432154321

54321

54321

54321

GND

HOT

L

COLD

HOT

COLD

R

ROT_DIAL_B

ROT_DIAL_A

GND

JU02

3

2

1

WY51

3

2

1

VAM1202

(PMD330,PMD331)

VAM1250

(PMD340)

SERVO PCB (P101)

J101

J201

J202

(PMD340)

J102

-15V

+15V

JV01

HEAD PHONE PCB (PV01)

L

-15V

JD01

W051

(20PIN FFC)

JY41

IR SENS PCB (PY41)

R

L

GND

54321

54321

FG

FG

3

2

1

WY41

22

JY02

3

33

2

11

1

JU01

W052

(30PIN FFC)

JY01

+5V

IR

GND

DISPLAY PCB (PY01)

FGFG

+15V

R

GND

J502

54321

54321

WV51

DIAL(-)

DIAL(+)

GND

321

JY51

321

DIAL PCB (PY51)

(PMD331,PMD340)

WY02WY01

WV01 WV02

13 14

Page 10

7. BLOCK DIAGRAM

CDM

VAM1202(PMD330,PMD331)

VAM1250(PMD340)

001M

TRAY LM302

TRAY MOTOR

TRAY OUT

TRAY IN

JU51

RC5 INPUT & OUTPUT

TRM+

TRM-

GND

TROU

TRIN

HF AMP

Q101

TZA1022

(PMD330)

Q101

TZA1022

(PMD331)

Q102

NJM2137M

(PMD340)

MOTOR DRIVER

Q201,Q202

TDA7073AT X2

(PMD330,PMD331)

FOR HALL MOTOR

Q251

BA6856FP

TRAY CONTROL

2,10

Q102,Q103

NJM2100M X2

Q102

NJM2137M

Q103

NJM2100M

Q103

NJM2100M

(PMD340)

QM01

LB1641

5,6

89,90

97

96

XD01

16.9344MHZ

71,72

CD DECODER & DIGITAL SERVO

38-40

43,50

2-8

29-34

22,24,76,77

XU01

20MHZ

66,67

CONTROL U-COM

QU01

H8/3062

29-43

QD01

CXD2585Q

1715

64

18-28

65-67

59

DIGITAL FIL. & DAC

26-28

70-72

2-9

9,17

58,60,69

DRAM(16M)

Q302

HY5117400BJ-60

(PMD331,PMD340)

2-25

ESA

Q301

RL5C357

(PMD331/340)

2-7

20-26 14-16

1-3

Q501

PCM1710

27-44

1-3

13,16

JT02

OPTICAL_OUT

(PMD331,PMD340)

JT01

DIGITAL OUT

OUTPUT AMP

Q502

NJM4560

SO

QU04

74HC4094

11-14

DISPLAY CONTROL & DISPLAY

QY01

LCD DRIVER

HD66712SA02FS

INDICATOR

DY07 TO DY18

LED X10

QY05

LCD

BALANCED

DIGITAL LINE DRIVER

QT52

SN75158P

(PMD331,PMD340)

BALANCED OUTPUT AMP

QB01 TO QB04

NJM4560 X3

(PMD331,PMD340)

HEADPHONE AMP

WITH VOLUME CONTROL

QV01

NJM4556AM

JT53

BALANCED DIGITAL

(PMD331,PMD340)

JB53

BALANCED OUTPUT

(PMD331,PMD340)

JB54

BALANCED OUTPUT

(PMD331,PMD340)

JV02

HEADPHONE OUTPUT

J501

ANALOG LINE OUTPUT

OUTPUT

JU52

FADER START

JU53

GPI (CONTROL I/O)

25PIN

(PMD331,PMD340)

(PMD330)

PISO

QU57,QU58

74HC165 X2

QU56

74HC4094

(PMD331,PMD340)

15 16

80

16,59,69

58,60,69

97

IR SENSOR

QY41

SPS-446-4

93,94

98-100

EEPROM(64K)

FOR CD-TEXT & PRESET

PITCH DIAL

SY51

EC16B24102

(PMD331,PMD340)

78,79

45-56

QU03

AT25640

KEY AND CONTROL INPUT

SY01 TO SY30

POWER SUPPLY

+15VA

-15VA

+5VA

+5VD

+6VM

REGULATOR

Q803

NJM78M15A

Q804

NJM79M15FA

Q801

NJM7805FA

Q802

NJM7806FA

B.DIODE

D802

D2SBA20

D801

D3SB20

SW & FILTER

S851,L851

TRANSFORMER

L801

W001

Page 11

8. SCHEMATIC DIAGRAM

17 18

Page 12

20

0V

RW

19

5.0V

+5VA

DOUT_OFF

FRDR

FFDR

TRDR

TFDR

SRDR

SFDR

TO SERVO PCB (J102 VIA W051)

IN DET

+12VM

+6VM

+5VA

18

0V

17

2.5V

TE

16

2.5V

FE

15

2.5V

RF

14

2.5V

VC

13

5.0V

LD

12

0.3V

11

0V

10

0V

9

0V

8

0V

7

0V

6

2.9V

MDP

5

5.0V

4

GND

3

9.8V

+12VM

2

GND

1

6.0V

+6VM

JD01

001M

LM302

0MA

TRAY MOTOR

TRAY OUT

TRAY IN

RT04

CT04

0.1

75

LT02

1K

CT03

2200p

5.0V

CT08

47/10V

COAXIAL_

OUT

0.5VPP

JT01

OPTICAL_

OUT

JT02

JT03

GND

1

0V

2

D_OUT

3

GND

+5V

4

5.0V

TO XLR PCB (JT52 VIA W054)

+5V

DIGITAL OUT

+5VD

5

PMD331,PMD340 ONLY

+5VD

C304

0.1

5.0V

26

VCC

VSS

1

2.3V

DQ0

DQ1

WE

RAS

A10

A0

A1

2.6V

A2

A3 A4

5.0V

C303

0.1

2

DQ0

2.3V

3

DQ1

5.0V

4

WE

3.6V

5

RAS

6

A11

0V

8

A10

0.8V

9

A0

0.8V

10

A1

11

A2

2.6V

12

A3

VCC VSS

Q302

4X4M

HY5117400BJ-60

DQ3

DQ2

CAS

DRAM

2.5V

25

2.1V

24

4.8V

23

0V

22

OE

0V

21

A9

0V

A8

19

0V

18

A7

0V

A6

17

2.3V

16

A5

2.3V

15

A4

1413

C301

10/16V

MAA

015M

TRM+

5

5

TRM-

4

4

COM

3

3

TROU

2

2

TRIN

1

1

LT01

CT07

0.1

PMD331,

PMD340

ONLY

DQ3

DQ2

CAS

OE

A9

A8 A0

A7

A6

A5

+5VD

DRIVER

QM01

LB1641

JM01

*

0V

5

0V

4

3

TRAY_SW_OPEN

5V

2

TRAY_SW_CLOSE

0V

1

4

12

3

MG

CM01

0.022

DM02

8.2V

DOA

RT02

CT01

220

0.1

RT03

330

LT03

1K

+5VD

ESA

WE

DQ1

DQ3

DQ0

5.0V

2.3V

2.3V

2.5V

33 23

D1D0D3

XWE

34

RAS

XRAS

A9

A9

A8

A8

A7

A7

A6

A6

A5

A5

A4

A4

RL5C357

A0

A1

A1

A2

A2

A3

A3

44

XEMP

XWRE

XQOK

VCC

1

A10

0V

0V

5.0V

C302

0.1

ESA_XQOK

ESA_XWRE

MOTOR

LOGIC

INPUT

5

MG

DQ2

2.3V

D2

Q301

ESA

XWIH

5.0V

ESA_XWIH

RM02

680

CAS

4.8V

678

+5VA

OE

0V

XCAS0

XCAS2

0V

ESA_CHDT

DRIVER

PRE-

+12VM

2

ESA_SCK

0V0V0V

SCK

XOE/XCAS1

A10

CHDT

910

RM01

4.7

1/4W

4700/10V

5V

0V

ESA_SDTI

SDTI

CLK

2.5V

CXD_DOUT_OFF

TRAY_DRV_CLOSE

TRAY_DRV_OPEN

CD05

0.01

CD06

0.47

1500P

CD14

ESA_XLT

C305

0.047

5.0V

XLT

22

TEST

XSOE

SDTO

XRST

SCOR

RFCK

XROF

DATO

LRCO

BCKO

BCKI

LRCI

12

DATI

GND

11

0V

PCMD

RD06

100K

CD08

CD11

0.22

16MHz

PMD330

ONLY

R301

470k

4.9V

0V

5.0V

5.0V

5.0V

2.5V

2.5V

0V

2.5V

2.5V

0.8V

1.2V

RD05

10K

RD09

10K

RD20

1K

CD13

1/16V

T

PMD330

ONLY

CD21

18P

ESA_XSOE

ESA_SDTO

ESA_XRST

XROF

LRCK

EYEPATTERN

CD23

CD07

0.047

2

BCK

CU91

0.1

CD09

1000P

CD10

0.22

1

QD02

CD01

4700P

RD23

CD19

RD08

3.3K

R531

MD2

GND

0V

5.0V

MD2

FWE

RD10

LRCK

0

MONI_MUTE

FWE

+5V

RES

5.0V

5.0V

+5VD

RU28

470K

RES

RD02

15K

CD04

1000P

RD01

2.2k

RD13

33K

CD17

0.1

3.3K

RD07

1M

RD11

22K

LD01LD02

4.7µH4.7µH

PMD330:33P

PMD331:39P

PMD340:39P

BCK

PCMD

0

R532

C515

0.1

C516

10/16V

D502

1SS302

C513

0.1

-15VA

R541

100k

C541

0.1

5.0V

Q541

DTA114YUA

FOR FLASH MPU PROGRAM

RXD

GND

TXD

JU04

12345678

0V

5.0V

5.0V

123

VDD

4

QU91

567

74HC00

91011121314

8

VSS

DEA

RD04

470K

5.0V

2.5V

CD20

150P

CD02

0.047

CD03

1000P

+5VD

R533

CD12

0.1

0

BCK

10/16V

RD03

15K

40

VCFESE

SS

FFDR

FRDR

TES1

TEST

TE

4142434445464748495051525354555657585960

CE

RFDC

ADIO

AV 0

IGEN

AV 0

ASYO

ASY1

RFAC

AV 1

CLTV

FILO

FILI

PCO

AV 1

BIAS

VCTL

V16M

VPCO

SS

DD

SS

DD

5.0V

LD03LD04

0.47µH0.47µH

DV 1

QD02-CD23

RD23

THERMI. 10k

THERMI. 10k

18k

15k

PMD330

PMD331

PMD340

CXD2585Q

CD DECORDER & DIGITAL SERVO

DOUT

PCMD

DV 2DDASYE

MD2

LRCK

BCK

61626364656667686970717273747576777879

RD22

0

EMPH

2.5V

5.0V

z

H

M

4

4

3

.9

6

1

CD15

18P

34

PCMD

LRCK

CXD_EMPH

CXD_DOUT_OFF

DIGITAL FIL. & DAC

Q501

PCM1710

2.5V 5.0V

ML/DSD

1

LRCIN

2.5V

MC/DM2

2

DIN

2.5V

MD/DM1

BCKIN

3

+5VD

2.5V

MUTE

CLKO

4

1.9V

MODE

XTI

5

CKSL

XTO

6

DGND

DGND

7

5.0V

VDD

VDD

8

5.0V

VCC2L

VCC2R

9

20

AGND2L

AGND2R

10

C519

+5VA

1.1VRMS

R544

1k

+5VA

2.5V

C520

10/16V

2.5V

C501

10/16V

R542

2.2k

R543

2.2k

C502

10/16V

EXT1L

EXT1R

11

EXT2L

EXT2R

12

VOUTL

13

VOUTR

AGND1

14 15

R501

10k

R503

4.7k

R502

R504

10k

4.7k

VCC1

1.1VRMS

R505

18k

2SC2878

2SC2878

R506

18k

19

18

17

16

Q542

A/B

Q543

A/B

DAC

FOR DEBUG

JU03

*

12345

RD12

SOCK

C517

0.1

+5VA

C522

FSTO

SOCK

+5VD

C514

0.1

+5VD

MDP

SSTP

XOLT

SQSO

CXD_SQSO

CXD_SQCK

XOLT

JD02

-15VA

5 678

R510

12k

5.0V

RU31

470K

+5VD

PWMI

LOCK

SQCK

SCSY

SOUT

123

SOUT

BAL_OUT(R)

BAL_OUT(L)

VSS

+

-

5.0V

DEBUG_TXD

+5VD

FOK

(XROF)

(RFCK)

SBSO

SOCK

XOLT

SOCK

RB02

10K

ADJ

RB04

220

RB01

10K

ADJ

RB03

220

12k

R509

+

R512

10k

C504

22p

5.0V

DEBUG_RXD

5.0V

RD19

10K

CXD_SSTP

CXD_LOCK

CXD_FOK

21222324252627282930313233343536373839

DFCT

MIRR

COUT

DV 0

WDCK

SCOR

C2PO

XPCK

XUGF

WFCK

ATS K

SCLK

SENS

CLOK

XLAT

DATA

MUTE

XRST

DV 0

EXCK

80

XOLT

RB08

6.8K

1234

VCC

+15VA

RU05XRU10

PMD330

X

PMD331

PMD340

QU03

AT25640

EEPROM

5.0V

VSSSI

SCK

WP

78SO

HOLD

VCC

CS

RU26

10K

RU27

10K

10K

RD17

SS

C4M

CXD_SCOR

GFS

CXD_SCLK

CXD_SENS

CXD_CLOK

CXD_XLAT

CXD_DATA

CXD_MUTE

CXD_XRST

1 2 3 4 5 6 7 8 9 101112 13141516171819 20

DD

0V

RD15

CD18

470K

0.047

+5VD

JD03

123

+5V

GND

GND

FOR ERROR RATE COUNTER

RB07

6.8K

-15VA

VSS

+

+

-

5678

RB06

CB19

22P

C503

22p

R511

10k

C509

Q502

100/16V

NJM4560

C523

100/16V

C510

100/16V

3456

2

1

XROF

RFCK

+5VD

JD04

+15VA

10K

+5VD

RU91

470K

RU92

470K

FLASH_TXD

FLASH_RXD

CXD_SQSO

PMD330:0

PMD331:10K

PMD340:47K

CD22

1000P

PMD340 ONLY

PMD331,

+5VD

5.0V

DD

SFDR

SRDR

TFDR

TRDR

DV 1

100p

100p

QD01

SS

XTSL

DV 2

XTAI

XTAO

SOUT

2.2V

2.2V

XD01

CD16

15P

SOUT

DAC_LAT

DAC_CLK

DAC_DATA

28

5.0V

27

0V

26

C518

25

10/16V

5.0V

24

23

22

21

5.0V

C521

2.5V

10/16V

2.5V

5.0V

10/16V

C505

150p

R507

33k

C507

150p

C524

100/16V

C508

150p

R508

33k

C506

150p

X

0

RU10

X

5.0V

5.0V

5.0V

RU01

10K

TRAY_SW_OPEN

TRAY_SW_CLOSE

PMD330 ONLY

+5VD

DEBUG_TXD

FLASH_TXD

DEBUG_RXD

FLASH_RXD

CXD_SQSO

CXD_SQCK

ESA_SDTI

ESA_SCK

10K

RD18

ESA_XLT

ESA_XSOE

ESA_XRST

ESA_XWRE

ESA_XQOK

RFCK

XPCK

12345

MNT0

MNT1

CB18

22P

CB01

RB05

100/16V

10K

CB12

1234

100/16V

VCC

QB01

NJM4560

NJM4560

CB02

100/16V

+6VM

LCD_DB7

+5VD

LCD_DB6

2

1

345678910 11 12 13 14 15 161718 19

5.0V

5.0V

5.0V

6.0V

+6VM

LCD_DB6

LCD_DB7

+5VD

10K

RU11

0

RU05

SYS_MODEL_SEL1

SYS_MODEL_SEL0

10K

RU02

RU32

FWE

10K

CXD_SQSO

C2PO

XPCK

10K

RD16

XROF

C2PO

GND

MNT2

MNT3

RB09

22K

-15VA

VSS

+

+

-

5678

QB02

+15VA

100/16V

RB12

RB10

22K

R513

22k

R514

22k

C526

0.1

LCD_RESET

LCD_E

LCD_DB4

LCD_DB5

5.0V

5.0V

LCD_E

LCD_RESET

LCD_DB4

LCD_DB5

5.0V

OE

10K

RU09

VDD

STRDACKQ0Q1

12345678

SIF_SI

SIF_ST

+5VD

LCD_RS

LCD_RW

LCD_E

LCD_RESET

LCD_DB4

LCD_DB5

LCD_DB6

LCD_DB7

0V

SIF_SO

AUDIO_MUTE

RB13

4.7K

CB20

22P

RB15

RB11

4.7K

22K

1234

RB19

4.7K

VCC

RB18

4.7K

CB13

22K

CB21

22P

9.8V

D501

ISS301

C525

15.0V

0.1

J502

LCD_RS

LCD_RW

0V

5.0V0V5.0V

LCD_RW

LCD_RS

Q4

OE

74HC4094

SIF_CK

12345678910111213141516171819202122232425

LCD_RS

LCD_RW

LCD_E

LCD_RESET

LCD_DB4

LCD_DB5

LCD_DB6

LCD_DB7

FWE

VSS

DEBUG_TXD

FLASH_TXD

DEBUG_RXD

CXD_SQSO

SIF_SO

CXD_SQCK

ESA_SDTI

ESA_SCK

ESA_XLT

ESA_XSOE

VSS

ESA_XRST

ESA_XWRE

ESA_XQOK

RB17

4.7K

-15VA

CB16

22P

RB14

4.7K

-15VA

RB16

4.7K

RB20

4.7K

+15VA

-15VA

-15.0V

12345

-15V

+15V

IR

PLAY_LED

5.0V

5.0V

IR

Q7

Q5

Q6

Q2Q3VSS

QU04

74HC4094

EEPROM_SI

EEPROM_CLK

99

100

VCC

26272829303133323435363738394041424344454647484950

ESA_SDTO

ESA_XWIH

ESA_CHDT

ESA_SDTO

ESA_XWIH

34

POWER ON

5V

5

0

VSS

+

+

-

5 678

RB23

VSS

+

+

-

5 678

RB24

END_LED

CUE_LED

0V0V0V

910111213141516

QS

QS'

RC5_INPUT

RC5_OUTPUT

RC5_INPUT

EEPROM_CS

(FLASH_RXD)

CXD_RW_SEL

ESA_CHDT

2.0V

4.0V

5.0V

CB14

22P

RB21

4.7K

1234

VCC

+15VA

4.7K

4.7K

RB22

1234

VCC

+15VA

4.7K

CB17

22P

PITCH_LED

CUE

PLAY

5.0V

5.0V

PLAY

CUE

QS

RC5_MASK

ROT_DIAL_B

RC5_MASK

ROT_DIAL_B

RC5_OUTPUT

CXD_LDON

CXD_FOK

CXD_LOCK

CXD_FOK

CXD_LOCK

QU42

DTC114EU

RB25

47

CB03

10/16V

QB03

NJM4560

RB29

4.7K

RB27

47

CB15

22P

RB26

47

CB04

10/16V

QB04

NJM4560

RB30

4.7K

RB28

47

SW_SCAN3

0V

0V

SW_SCAN3

+5VD

ROT_DIAL_A

ROT_DIAL_A

CXD_SSTP

CXD_SSTP

SW_SCAN2

SW_SCAN1

20 21

0V

0V

SW_SCAN2

SW_SCAN1

SW_SCAN0

10K

10K

RU24

RU25

ROT_DIAL_B

RC5_INPUT

AUDIO_MUTE

TRAY_DRV_CLOSE

VSS

AUDIO_MUTE

CONTROL µ-COM

VCC

CXD_XRST

+5VD

CXD_XRST

CXD_DOUT_OFF

CU41

0.1U

RU41

4.7K

0V

RU42

4.7K

RB31

4.7K

CB05

10/16V

100/16V

RB32

4.7K

CB06

10/16V

R515

150

SW_SCAN0

SW_DATA7

22 23

5.0V

5.0V

SW_DATA6

SW_DATA7

10K

RU23

ROT_DIAL_A

MONI_MUTE

TRAY_DRV_OPEN

TRAY_DRV_OPEN

TRAY_DRV_CLOSE

QU01

H8/3062

CXD_MUTE

CXD_DOUT_OFF

CXD_MUTE

CXD_DATA

CB07

100/16V

RB33

10K

RB35

10K

CB09

100/16V

CB08

RB34

10K

RB36

10K

CB10

100/16V

L501

R516

R519

470

R520

0V

0V

L

R

GND

150

470

HEADPHONE OUT

TO HEADPHONE PCB (JV01 VIA WV01)

SW_DATA6

SW_DATA2

SW_DATA3

SW_DATA5

SW_DATA4

24 25 26 27 28 29 30

5.0V

5.0V

5.0V

5.0V

SW_DATA3

SW_DATA4

SW_DATA2

SW_DATA5

10K

10K

10K

10K

RU21

RU19

RU20

RU18

PLAY

CUE

SW_DATA7

SW_DATA6

CXD_SCOR

SYS_MODEL_SEL0

SYS_MODEL_SEL1

AVSS

CXD_SCOR

SYS_PWR_DOWN

SYS_MODEL_SEL0

SYS_MODEL_SEL1

MONI_MUTE

CXD_CLOK

CXD_SCLK

CXD_XLAT

CXD_SENS

CXD_DATA

CXD_CLOK

CXD_SCLK

CXD_SENS

CXD_XLAT

+15VA

+12VM

-15VA

9.8V

+5VA

+5VD

QU41

2SA1036K

+6VM

9.8V

DB01

ISS301

BAL

9.8V

DB02

ISS301

R517

47k

R518

47k

TO DISPLAY PCB (JY01 VIA W052)

JU01

GND

SW_DATA0

SW_DATA1

5.0V

5.0V

SW_DATA0

SW_DATA1

5.0V

10K

10K

10K

10K

10K

10K

RU12

RU14

RU13

RU16

RU17

RU15

SW_DATA0

SW_DATA1

SW_DATA2

SW_DATA3

SW_DATA4

SW_DATA5

CUE

PLAY

SW_FADER

TRAY_SW_OPEN

TRAY_SW_CLOSE

SW_SP0

SW_SP1

SW_FADER

EEPROM_SO

TRAY_SW_OPEN

DAC_LAT

TRAY_SW_CLOSE

DAC_CLK

DAC_DATA

3

4

SW_SCAN3

SW_SCAN2

SW_SCAN1

SW_SCAN0

SW _D ATA 7

SW _D ATA 6

SW_DATA2

CXD_EMPH

SW_DATA1

SW_DATA0

VSS

5.0V

5.0V

5.0V

5.0V

SW_DATA3

SW_DATA0

SW_DATA1

SW_DATA2

SW_DATA3

CXD_EMPH

RES

15.0V

C814

C812

470/16V

0.1

C813

0.1

C815

470/16V

-15.0V

5.0V

C803

0.1

C804

470/10V

NJM7806FA

6.0V

C807

470/10V

C806

MG

0.1

C511

1000p

C512

1000p

+5VD

7677787980818283848586878889909192939495969798

AVCC

VREF

MD2

MD1

MD0

SIF_CK

VCC

XTAL

EXTAL

VSS

NMI

RES

STBY

PAI

SIF_SI

SIF_LD

SIF_ST

VSS

SW_DATA5

SW_DATA4

SW_DATA4

SW_DATA5

NJM78M15FA

Q803

15V

OUT

GND

GND

Q804

-15V

NJM79M15FA

NJM7805FA

Q801

5V

OUT

GND

Q802

6V

OUT

GND

LB01

LB02

2VRMS

2VRMS

SW_FADER

RC5_OUTPUT

IR

RC5_MASK

RC5_INPUT

SIF_CK

5.0V

SIF_SI

SIF_LD

SIF_ST

DA227

51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75

OE

5.0V

IN

INOUT

IN

IN

DU02

TO ROTARY PCB (JY51 VIA WY51)

PMD331,

JU02

GND

ROT_DIAL_A

ROT_DIAL_B

*

PMD340

123

ONLY

5.0V

5.0V

DU51

ROT_DIAL_B

ROT_DIAL_A

ISS301

4.7V

QU52

DTC114EU

5.0V

4.7V

MD2

CU03

0.1

CU01

15P

CU02

15P

RES

5

0.1

CU04

SW_SCAN3

SW_SCAN2

SW_SCAN1

SW_SCAN0

SW_DATA7

SW_DATA6

+5VD

R804

4.7k

R803

4.7k

Q806

DTC114EU

-25.0V

C801

6800/16V

00/16V

00/16V

JB32

*

R

BALNCED OUT

GND

TO XLR PCB (JB52 VIA W053)

L

J501

*

OE

25.3V

9.8V

9.8V

ONLY

RU07RU08

470K470K

RU06

470K

DAC_LAT

DAC_CLK

DAC_DATA

+5VD

2.2V

2.2V

XU01

20.000MHz

RU04

470K

+5VD

DU01

DA227

5.0V

DU03

ISS301

C808

2200/35V

C810

0.1

C811

0.1

C809

2200/35V

+12VM

C802

0.1

C805

0.1

PMD330:

PMD331:100

PMD340:100

16DBU

PMD331,PMD340

COLD

1

HOT

2

3

COLD

4

HOT

5

16DBU

L

RCA OUT

R

O-END

O-INDEX

SIF_SO

NEXT

PREV

END

PITCH+

PAUSE

STOP

+5VD

+5VD+5VD

PLAY

CUE

0V

D802

D2SBA20

D801

D3SB20

4.8V

RU22

470K

SU51

SSSU

EXTINT

+5VD

RU30

1M

CU05

1/50V

910111213141516

QS

QS'

Q7

Q6

Q5

Q4

OE

VDD

91011121314

QH

S-IN

A

B

C

D

INH

1516

VDD

91011121314

QH

S-IN

A

B

C

D

INH

1516

VDD

Q805

DTC114EU

PDC

(

PMD3XXU, PMD340N

DU52

ISS301

QU51

2SC4081(Q,R)

VSS

78

Q3

6

Q2

5

Q1

4

Q0

3

CK

74HC4094

QS

2

DA

SIF_ST

1

STR

QU56

VSS

78

QH

6

H

5

G

PITCH_SW

4

F

74HC165

PITCH-

3

E

2

CK

1

L

S/

QU57

VSS

78

QH

INDEX-

6

H

INDEX+

5

G

FR

4

F

74HC165

FF

3

E

2

CK

1

L

S/

QU58

C816

1/50V

WHT(U,F)

BLUE(N)

L851

W002

W003

O-FADER

O-PAUSE

SIF_LD

J802

J852

RU53

18K

O-CUE

O-PLAY

13.2V

13

)

SIF_CK

RU55

RU52

47K

31

1K

R805

4.7k

9V

13

13

13

13

J851

NEUTRAL

LIVE

INSIDE VIEW

D803

ISS301

W802

LIVE SIDENEUTRAL SIDE

RED (U,F)

BROWN(N)

S851

*

J001

DTA114YUA

O-END

O-INDEX

O-FADER

PITCH_SW

PITCH-

PITCH+

END

PREV

NEXT

INDEX-

INDEX+

FR

FF

STOP

CUE

O-CUE

PAUSE

O-PAUSE

PLAY

O-PLAY

SW PCB (P851)

LCA

+5VD

QU55

+5VD

RU74

RU73

RU72

RU71

RU70

RU69

RU68

RU67

RU66

RU65

RU64

RU63

RU62

RU60

R801

4.7k

MAIN PCB (PD01)

12345

J801

12345

*

W801

*

12345

20V

20V

L801

U801

U802

PDT

TRANS PCB (P801)

PAC

C851

0.01

3P PLUG (PMD3XXU, PMD340N)

2P PLUG (PMD33XN, PMD3XXF)

W001

+5VD

RU58

10K

+5VD

CU53

RU54

47

QU53

DTA114YUA

CU51

10/16V

RU51

5.0V

PMD330

*

5.0V

0.1

0

ONLY

FADER

IN

JU52

JU51

0V

RC5

PMD331,

PMD340

47K

47K

47K

47K

47K

U

N

F

47K

RU85

1000P

CU67

47K

47K

RU86

RU87

1000P

1000P

CU69

CU68

QU59

DTC114EU

DTC114EU

U801 U802

47K

RU89

RU88

1000P

1000P

CU71

CU70

CU61

1000P

QU60

QU61

DTC114EU

DTC114EU

X

X

X

47K

RU90

1000P

CU72

CU63

1000P

QU62

DTC114EU

47K

47K

RU93

RU94

1000P

1000P

CU74

CU73

CU65CU66

1000P1000P

QU63

QU64

DTC114EU

47K

RU95

1000P

CU75

1000P

CU76

ONLY

JU53

CU80

0.1U

+5VD

GPI PORT

13

FG

25

COMMON

5.0V

12

+5V

24

END TALLY

11

INDEX TALLY

23

FADER(INVERT)

10

FADER(NORMAL)

22

FADER TALLY

9

PITCH ON OFF

21

PITCH-

8

PITCH+

20

END

7

PREVIOUS

19

NEXT

6

INDEX-

18

INDEX+

5

FR