Page 1

5

4

3

2

1

Matanzas

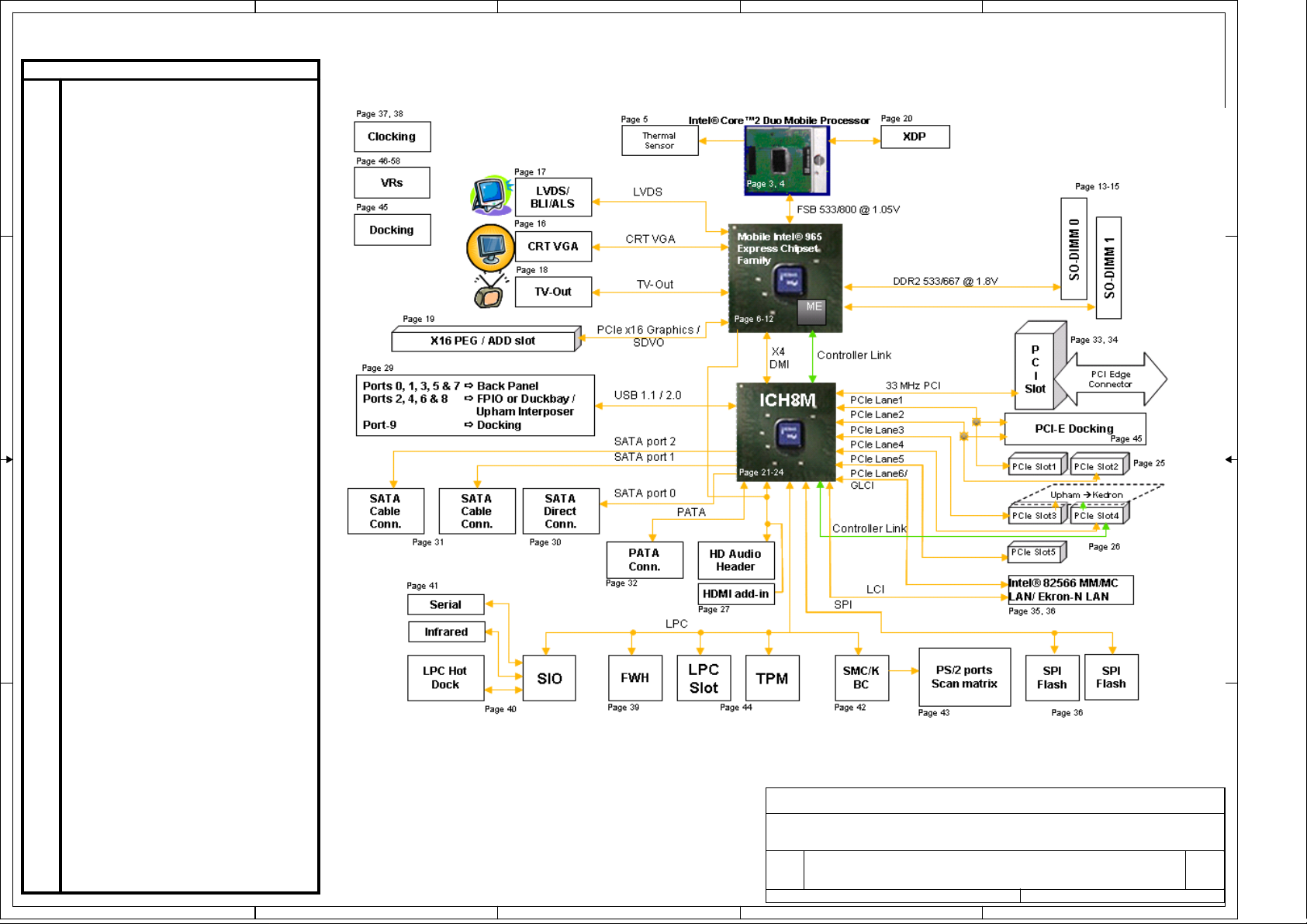

Table of Contents

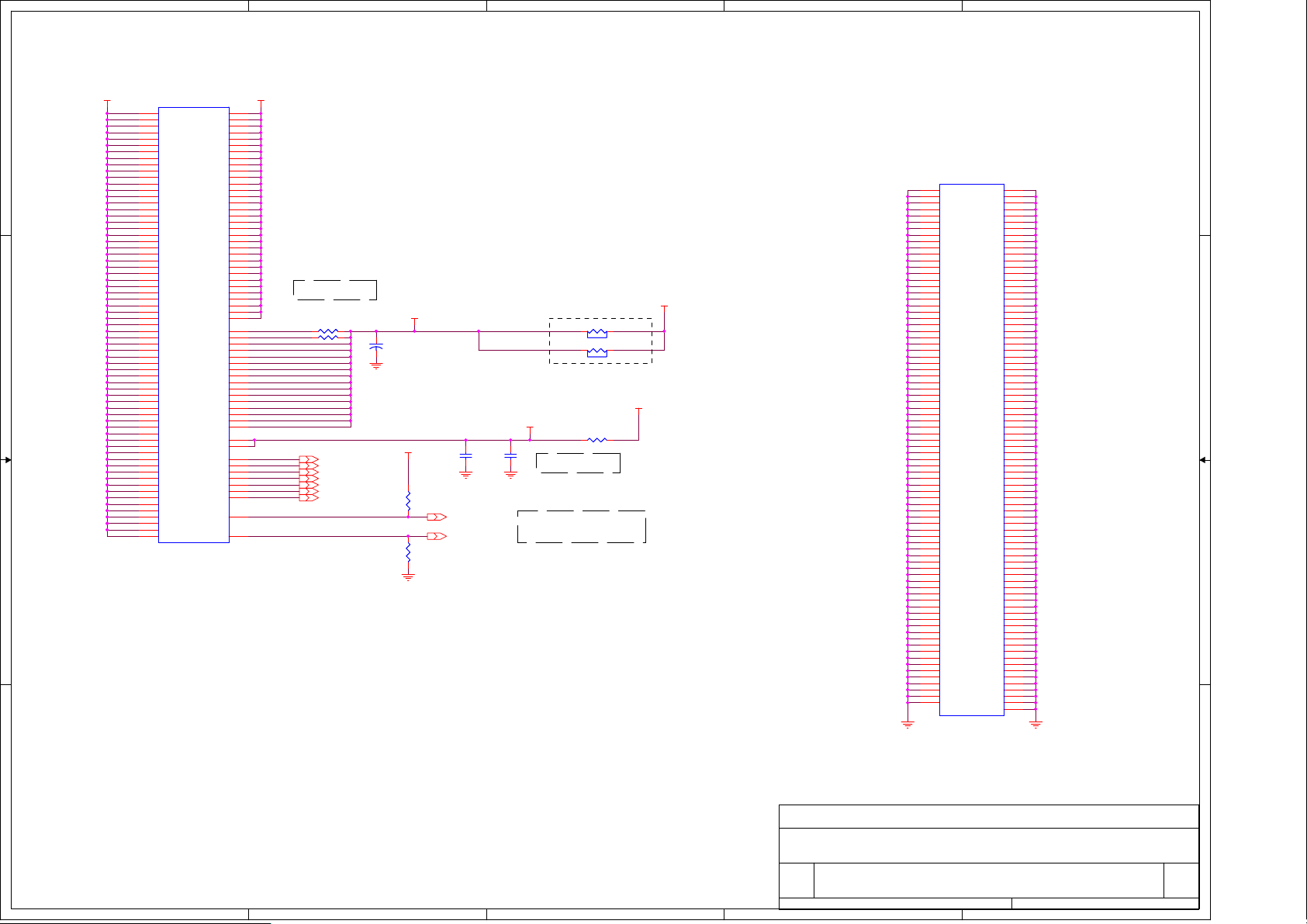

Page Description

1a

This Page

1b

Revision History

2

D D

C C

B B

NOTES

3

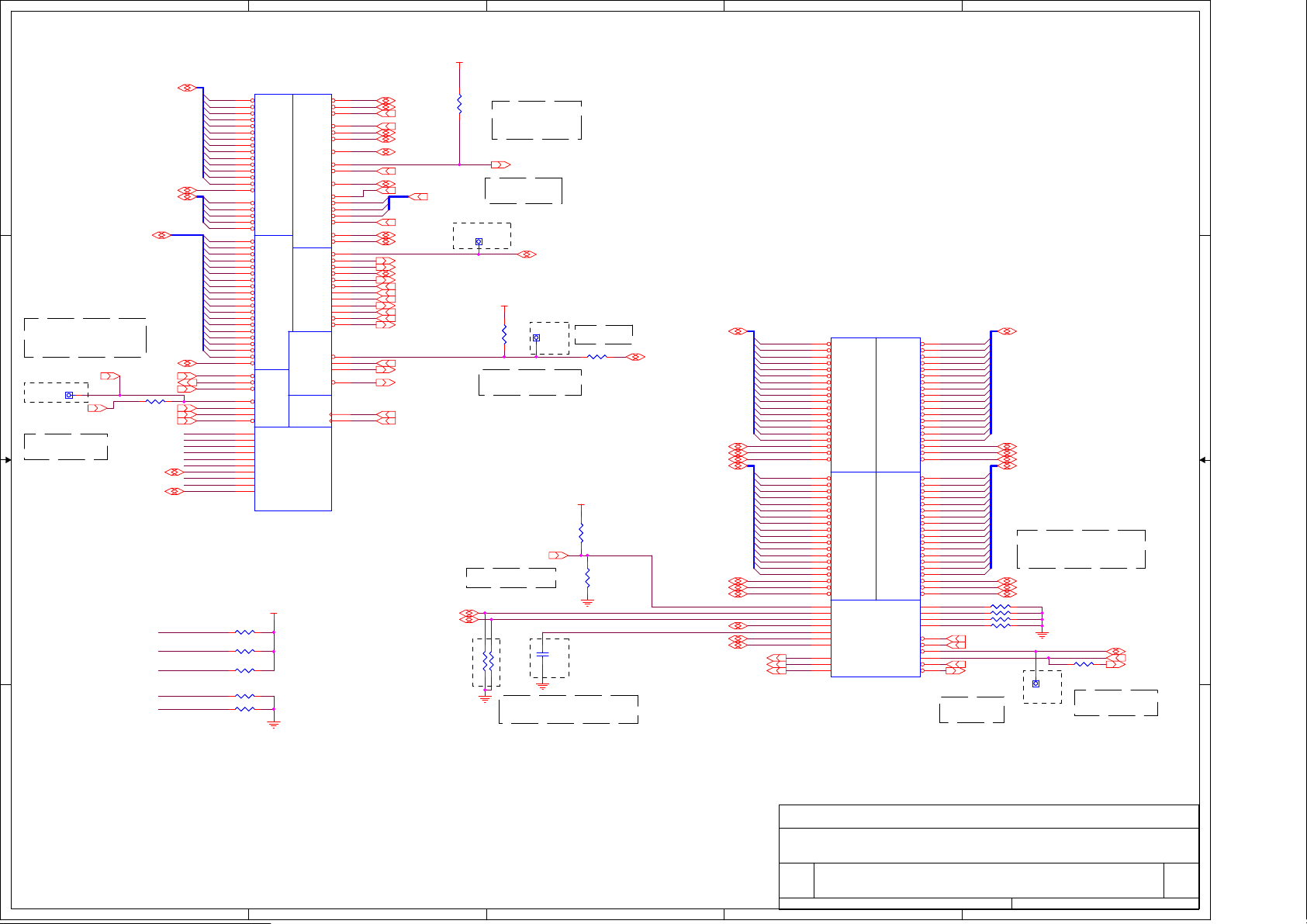

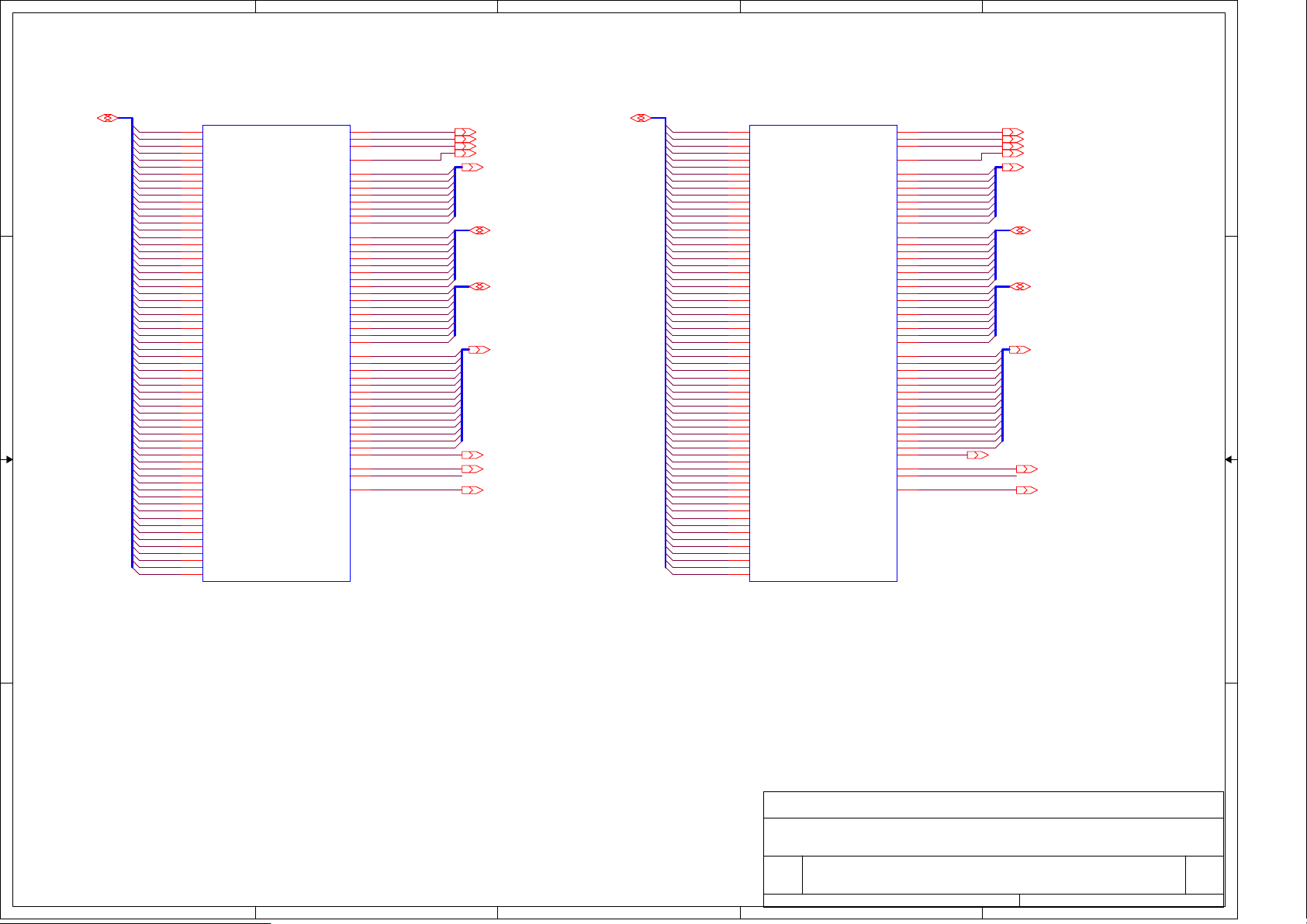

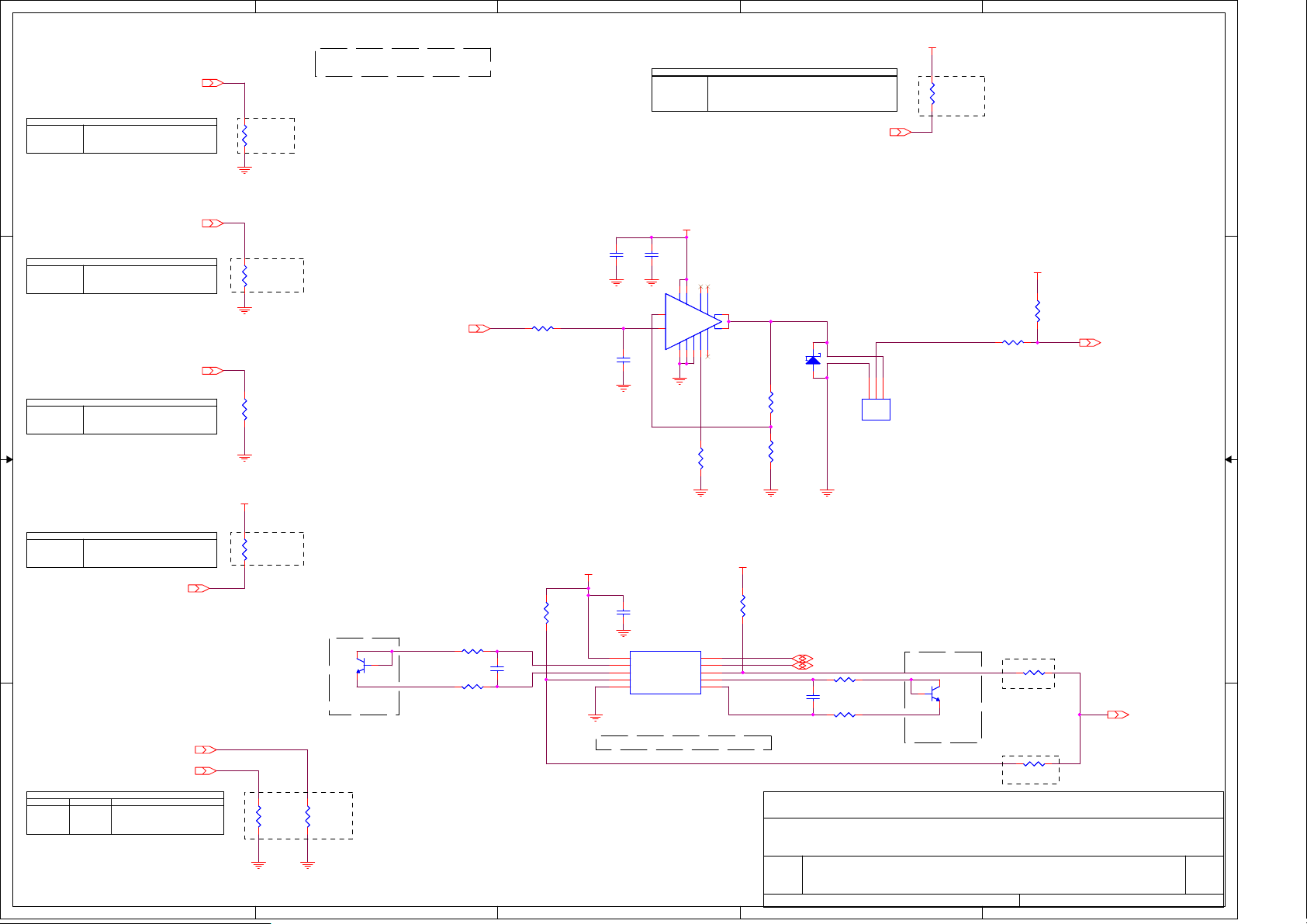

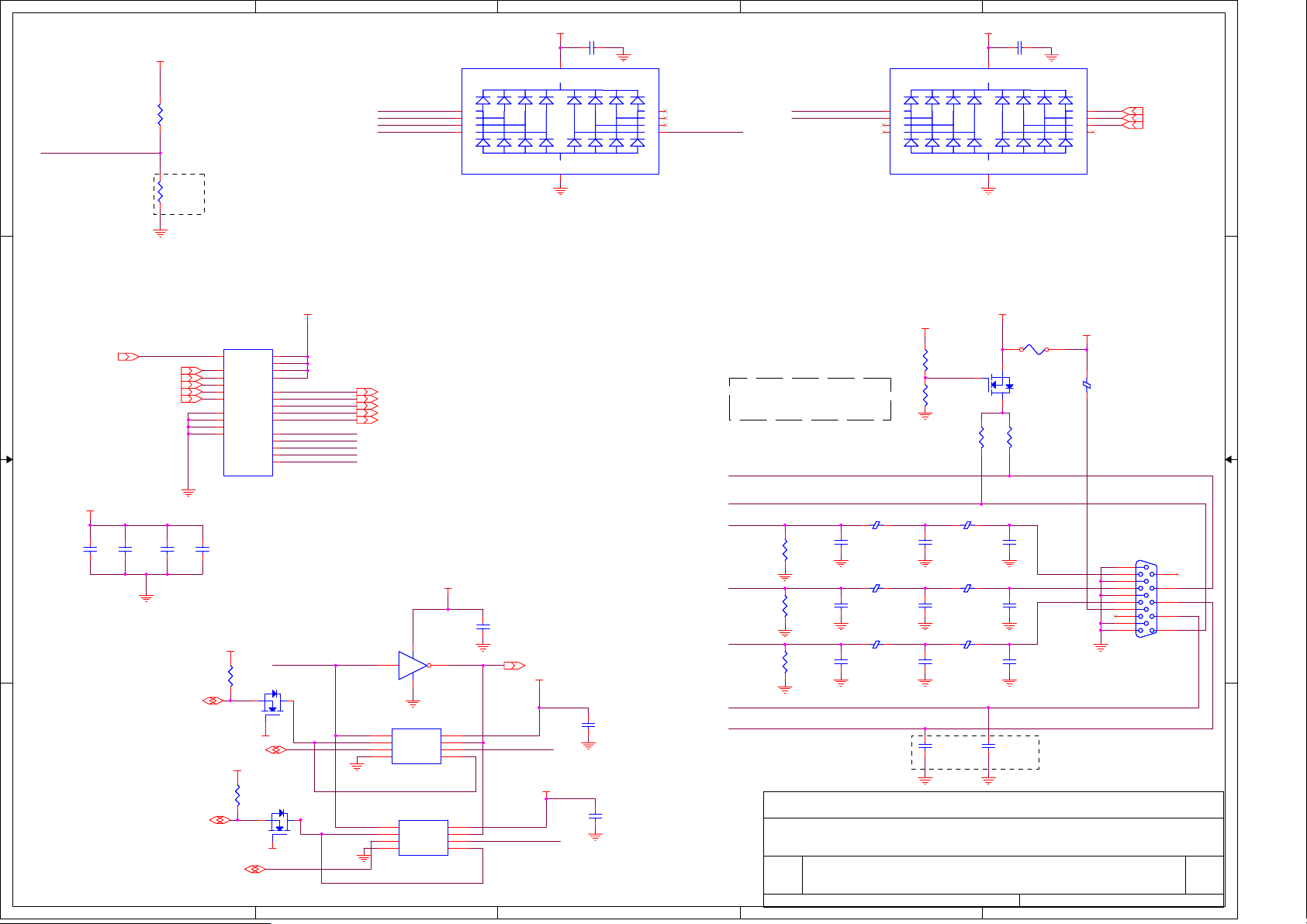

Intel® Core™2 Duo Mobile Processor (1 of 2)

4

Intel® Core™2 Duo Mobile Processor (2 of 2)

5

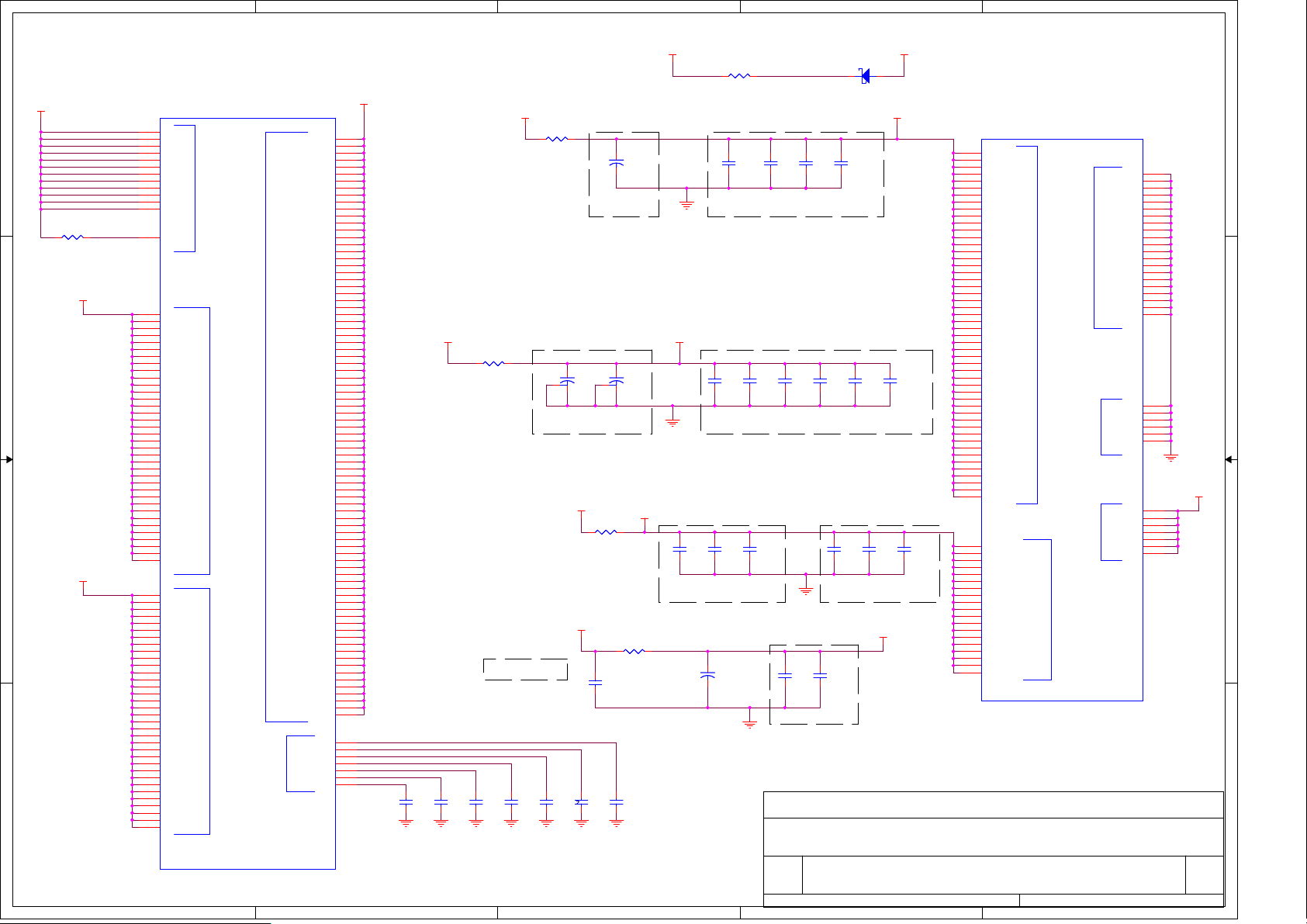

CPU Thermal Sensor & Fan

6

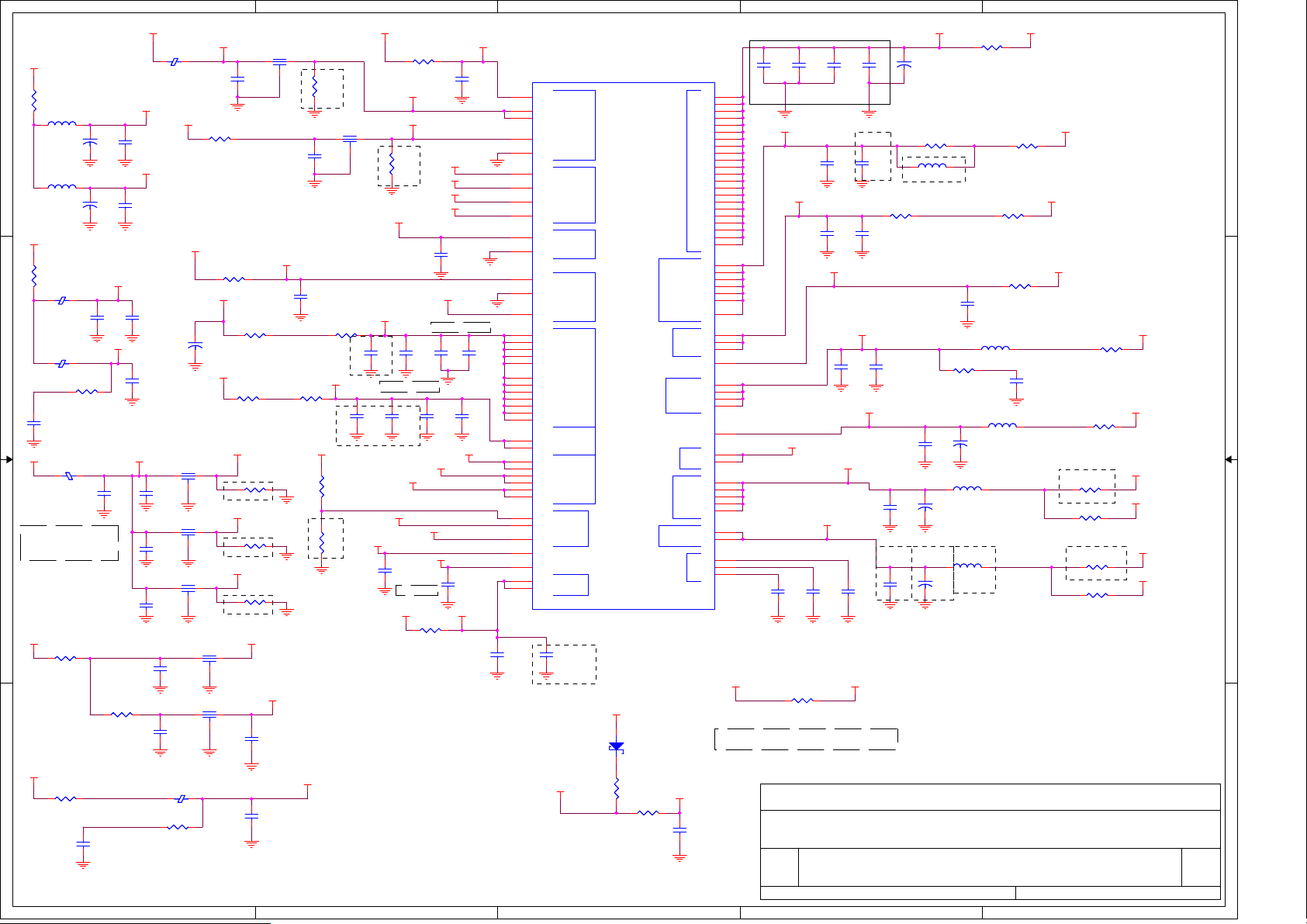

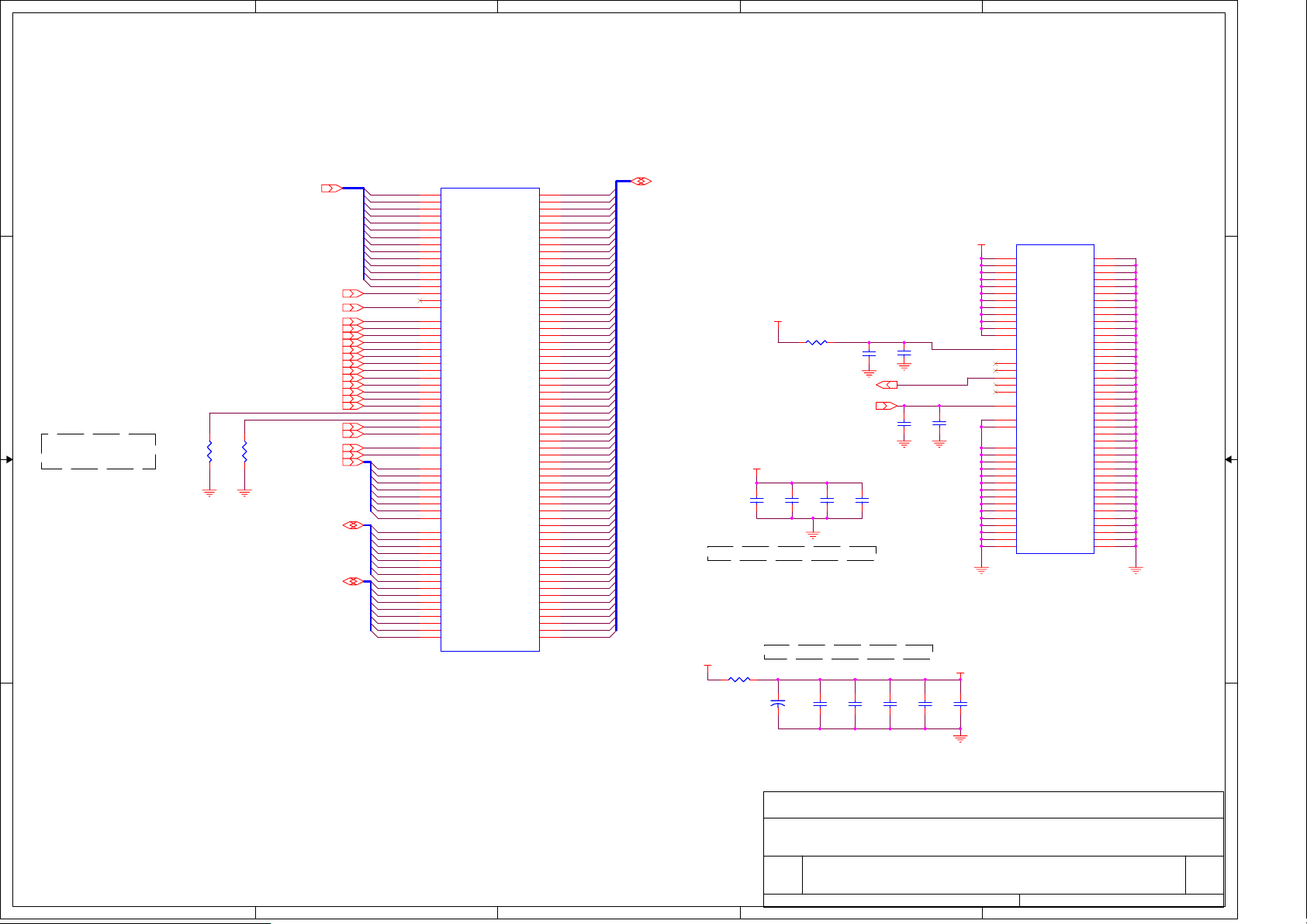

Mobile Intel® 965 Express Chipset Family (1 OF 6)

7

Mobile Intel® 965 Express Chipset Family (2 OF 6)

8

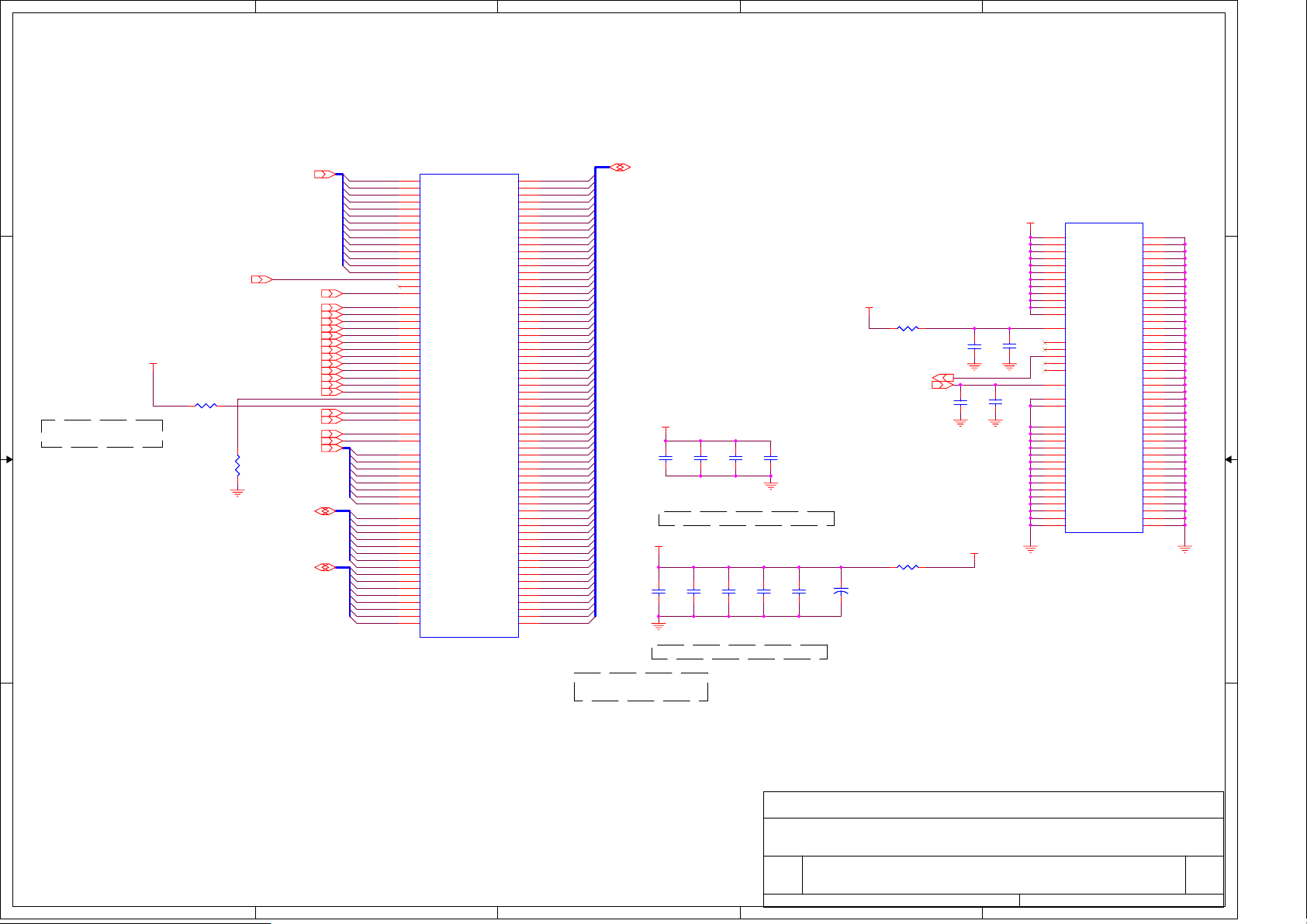

Mobile Intel® 965 Express Chipset Family (3 OF 6)

9

Mobile Intel® 965 Express Chipset Family (4 OF 6)

10

Mobile Intel® 965 Express Chipset Family (5 OF 6)

11

Mobile Intel® 965 Express Chipset Family (6 OF 6)

12

Mobile Intel® 965 Express Chipset Family Strapping

13

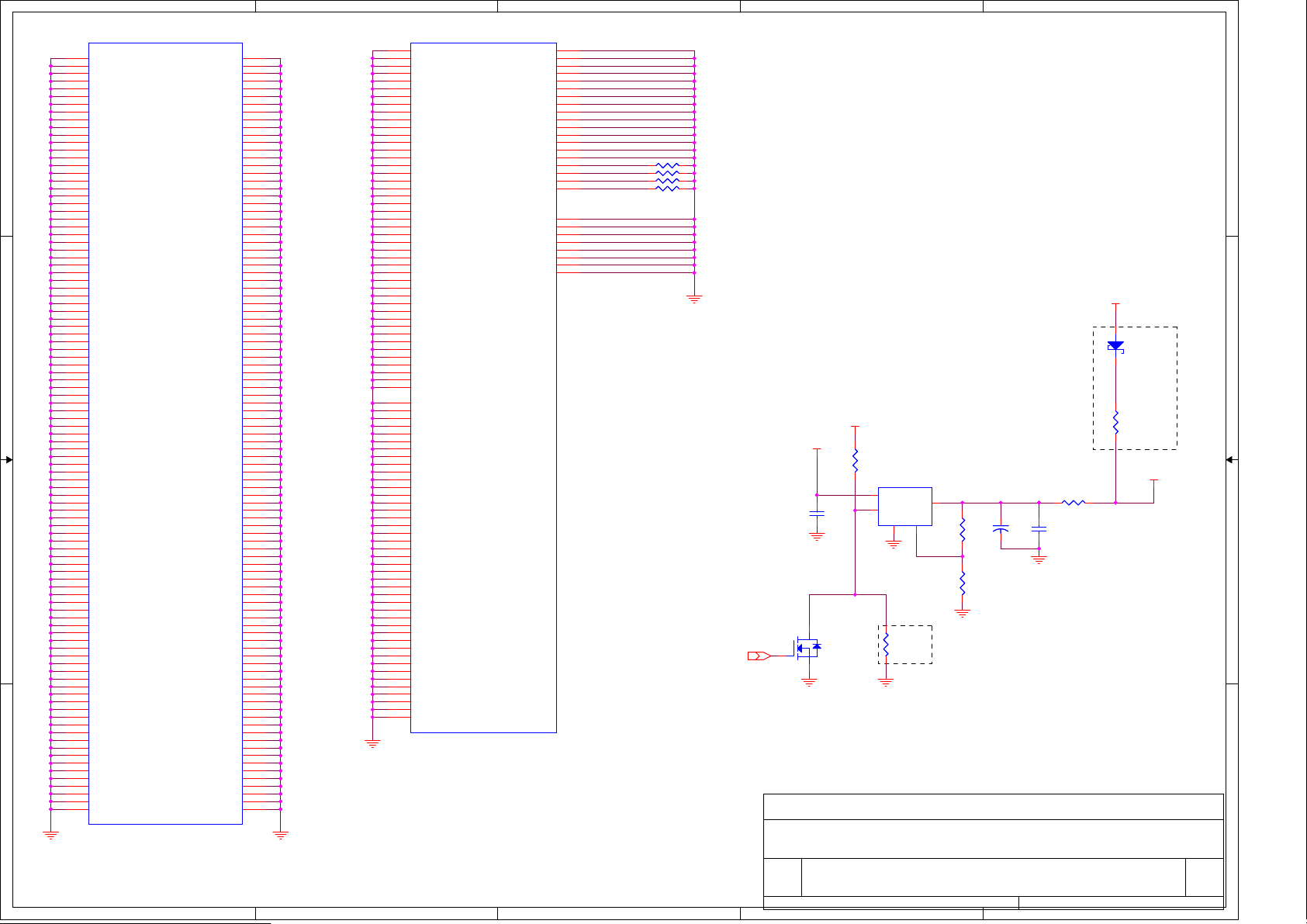

DDR2 SODIMM 0

14

DDR2 SODIMM 1

15

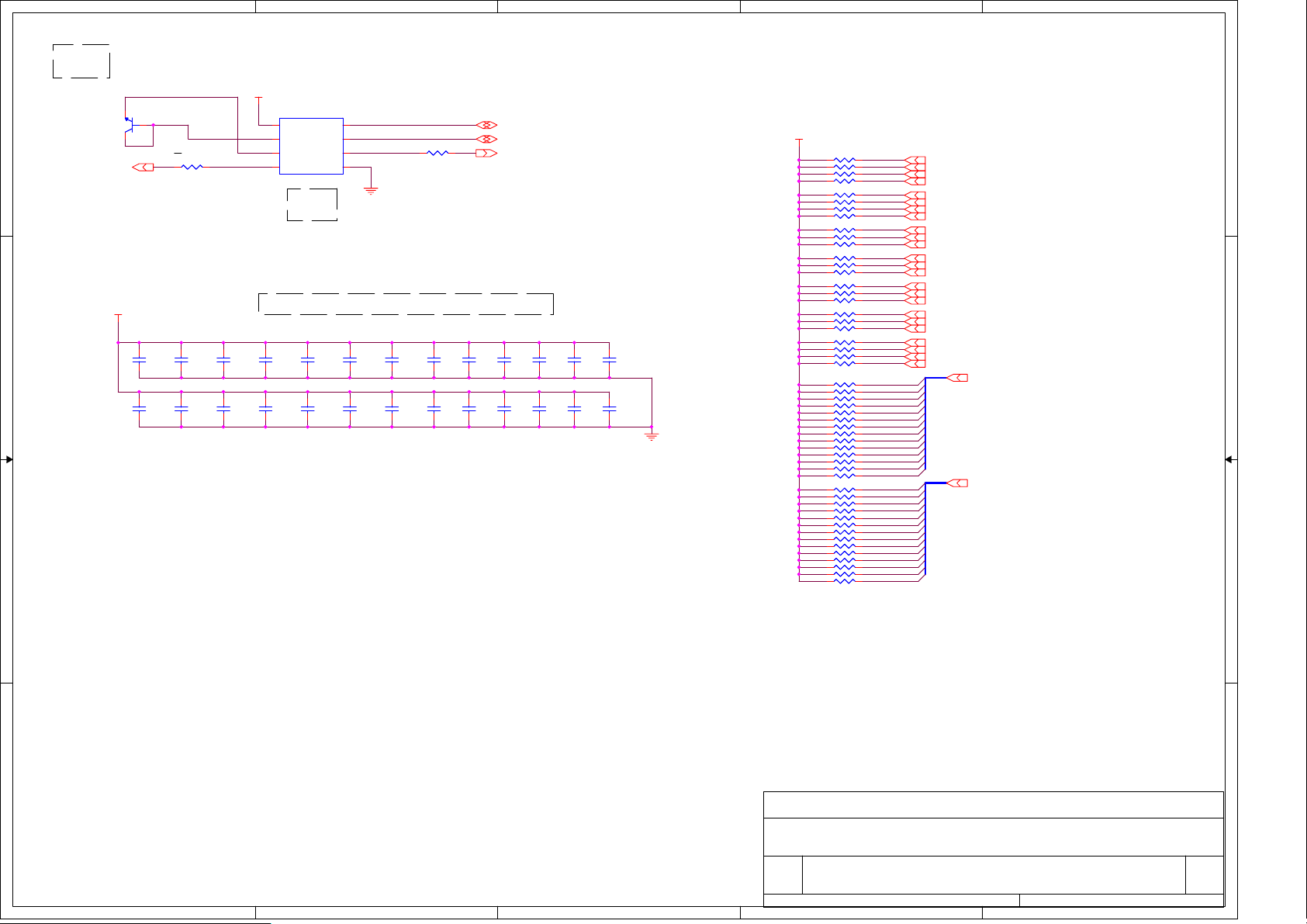

DDR2 TERMINATION AND THERMAL SENSOR

16

CRT

17

LVDS

18

TV

19

PCIE GRAPHICS

20

XDP

21

ICH8M (1 of 4)

22

ICH8M (2 of 4)

23

ICH8M (3 of 4)

24

ICH8M (4 of 4)

25

PCI-E Slots (1 & 2)

26

PCI-E Slots (3,4 & 5)

27

High Definition Audio

28

HDA Power Supply

29

USB 1.1/2.0

30

SATA (1 of 3)

31

SATA (2 and 3 of 3)

32

IDE

33

PCI Slot 3

34

PCI Edge Connector (Goldfinger)

35

Intel® 82566 MM/MC LAN & Ekron-N Option

36

LAN Docking and SPI

37

CK505

38

DB800 & Buffers

39

FWH and I/O Port Expander

40

SIO

41

Legacy Support

42

H8 2104 KBC

43

PS2

44

LPC Slot, TPM Header, and EMA

45

Docking

46

TPS51120 System Power

47

DDR VR

48

Crestline VR

49

Graphics Core VR

50

DDR2 VREF

51

System Charger VR

52

IMVP-6

53

IMVP-6 Core VR

54

CPU Decoupling

55

Start Up Sequence

56

DISCHARGE CIRCUITS

57

Sleep control

58

POWER SEQUENCING TIMING BLOCK DIAGRAM

Intel® Core™2 Duo Mobile Processor, Mobile Intel® 965 Express Chipset Family and ICH8M

Customer Reference Board

Rev 1.5

A A

5

4

3

Matanzas

Matanzas

Matanzas

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

A

A

A

TITLE PAGE

TITLE PAGE

TITLE PAGE

NDA

NDA

NDA

2

Intel Confidential

Intel Confidential

Intel Confidential

1a 58Thursday, November 30, 2006

1a 58Thursday, November 30, 2006

1a 58Thursday, November 30, 2006

1

1.5

1.5

1.5

of

of

of

Page 2

5

4

3

2

1

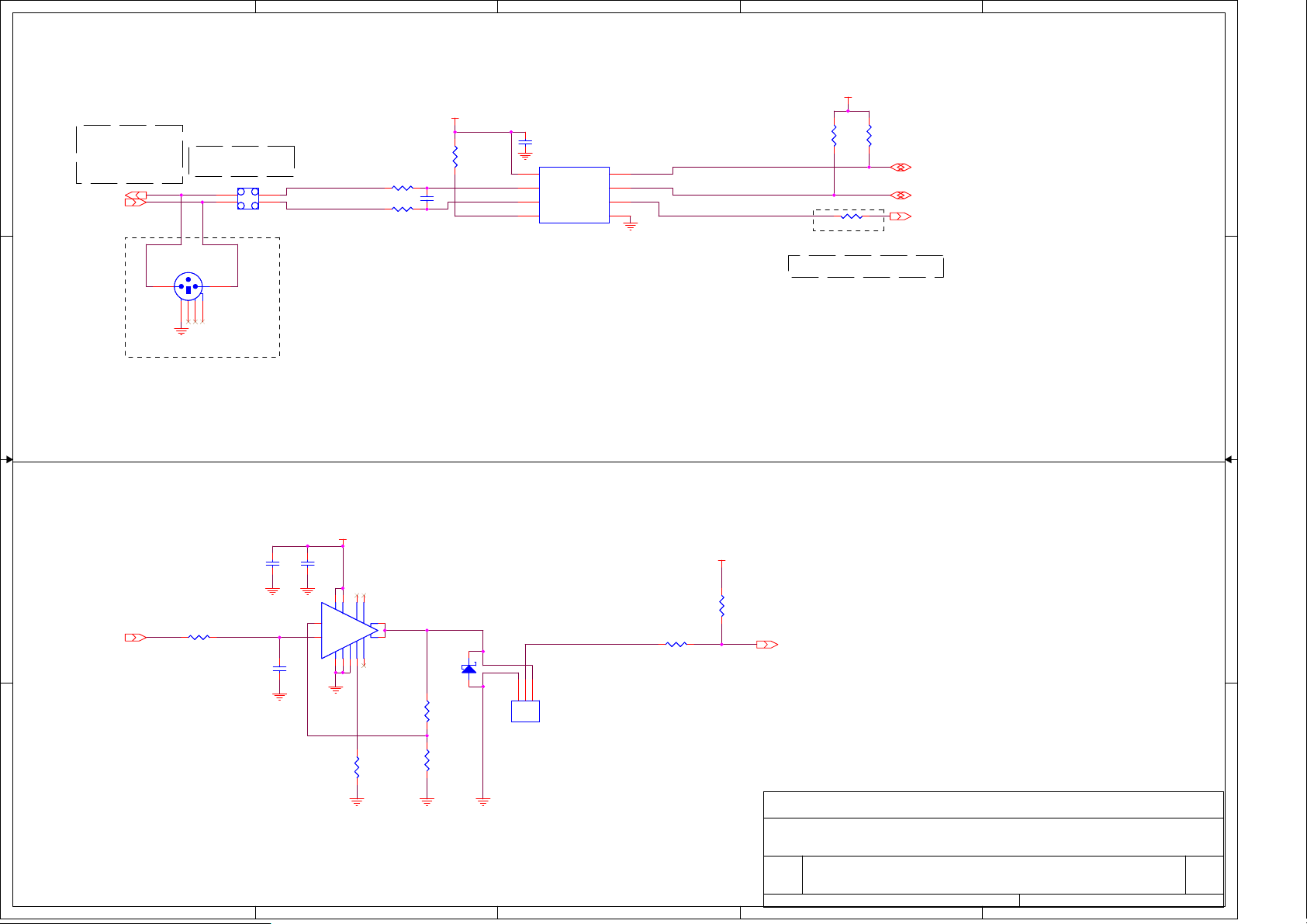

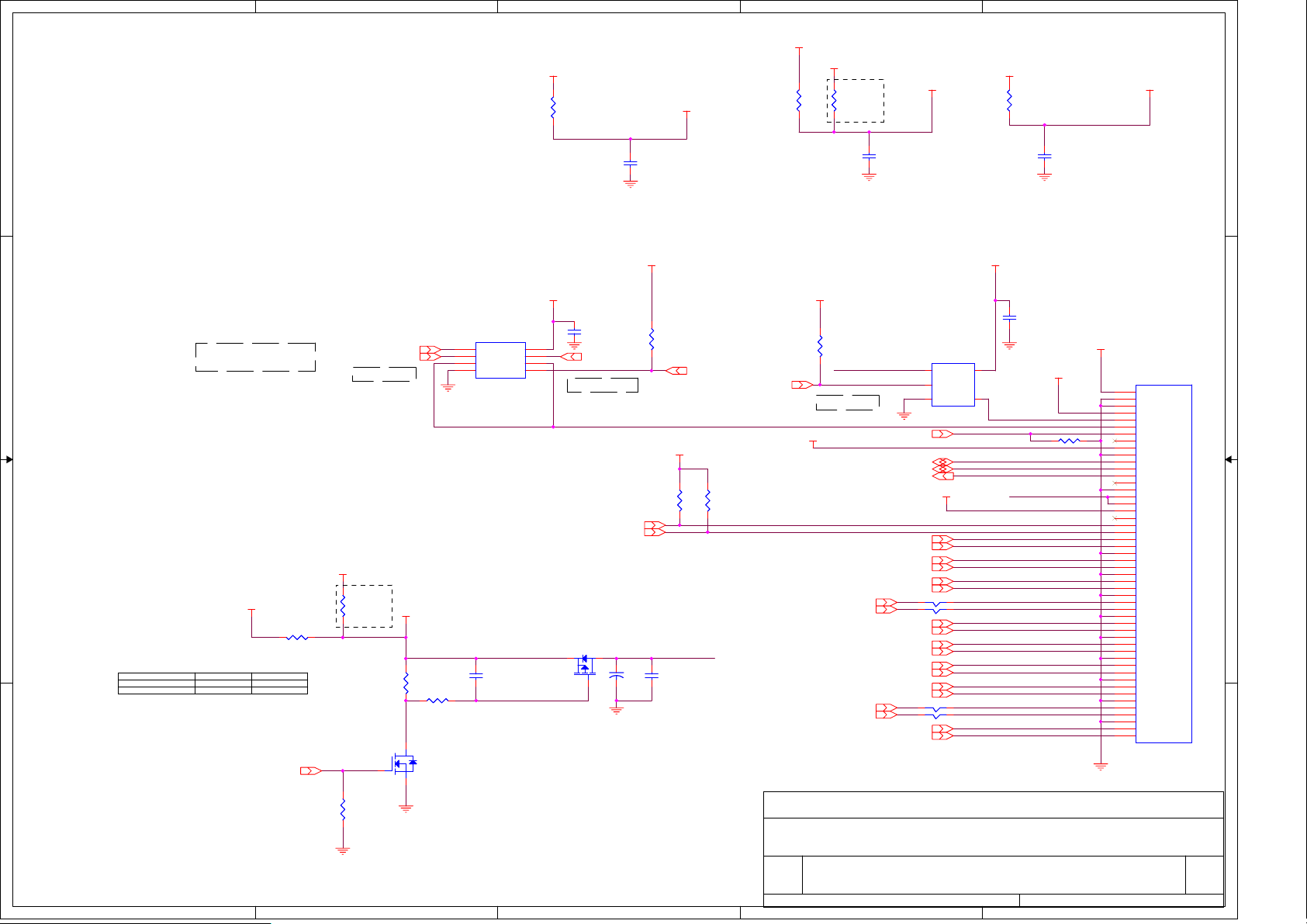

Rev 1.5 (Changes from Rev 1.301)

Note: Revision 1.5 of the CRB Schematics is based on Fab 3 of Matanzas boards.

D D

Page:3

-The PROCHOT signal pull up value changed from 75 Ohms to 1K Ohms,1%. This fixes the PROCHOT# failure when driven by thermal

sensor on the CRB.

Page:7

-Updated Crestline symbol to indicate LVDSB_DATA_3 and LVDSB_DATA#3 pins to support Dual Channel 24-bit LVDS Support.

Page:10

-Crestline CRT/TV QDAC Filter Change (Refer to WW44 Santa Rosa MOW)

-Changed FB5T1 to R5U20 Resistor 100 ohms, 5%,1/16W

-Changed no-stuff R5T5 with C5T20 1.0uF,20%

Page:13

-Corrected net name RSVD-M_A_A14 to M_A_A14

Page:14

-Corrected net name RSVD-M_B_A14 to M_B_A14

Page:17

-LVDS Connector updated to indicate LVDSB_DATA_3 and LVDSB_DATA#3 pins

Page:21

-Added a note that ICH8M Internal VR should not be disabled.

Page:22

C C

-Added strapping configuration information for PCIe x2

Page:23

-Removed the pull-up to +V3.3S circuit on CRB_SV_DET. Customer platforms should pull-up CRB_SV_DET (if used) to

+V3.3A via 10k Ohm resistor.

Page 31:

-Clarified SATA Port 1 impact with J7J2 No Shunt

Page:36

-Auto Connect Battery Saver Energy Detect Circuit Update: R5A3 changed from 3.92KOhms to 1.87KOhms. This is an update to the

recommendation in the WW44 Santa Rosa MOW.

Page:41

If SPI Descriptor Lock is removed, a 1k Ohms resistor is required between pins 9 and 7 of J8F1 to avoid damage to I/Os.

Page:44

-ME_SMC_ALERT# should be pulled-up to +V3.3A instead of +V3.3M. On the CRB,R6G17 is made no-stuff & the internal pull up on

the H8 is enabled. Customer platforms need to pull this signal to +V3.3A.

-Added note on ME_SMC_ALERT# assertion/de-assertion indication

Page:48

-499 Ohms value of R5G10 causes +V1.05S to be +V1.09S. R5G10 changed from 499Ohms to 0Ohms.

Page:49

B B

-R3G13, R3G12, R3G11, R3G9, R3G10 stuff with 20K resistors

-R3G14 stuff with 30K resistor

-R2G16 value changed to 100K resistor

-J2G1 – Removed jumper shunts. No shunts to be installed.

-The pull up on GVR_VID3 (R3G10) and GVR_VR_EN (R3G14) should be connected to +V3.3S instead of +V3.3

-Modified sheet Graphics Controller symbol

Page:52 & 53

-Modified sheet IMVP Controller and FET Symbols

Page:55

-J3G1 Pin1 and 2 should be shorted for ME support in G3 state.

-Corrected net name XDP_DBRESET#_R to XDP_DBRESET#

A A

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

5

4

3

Date: Sheet

Revision History

Revision History

Revision History

NDA 1.5

A

NDA 1.5

A

NDA 1.5

A

of

1b 58Friday, December 08, 2006

1b 58Friday, December 08, 2006

2

1b 58Friday, December 08, 2006

1

Page 3

5

4

3

2

1

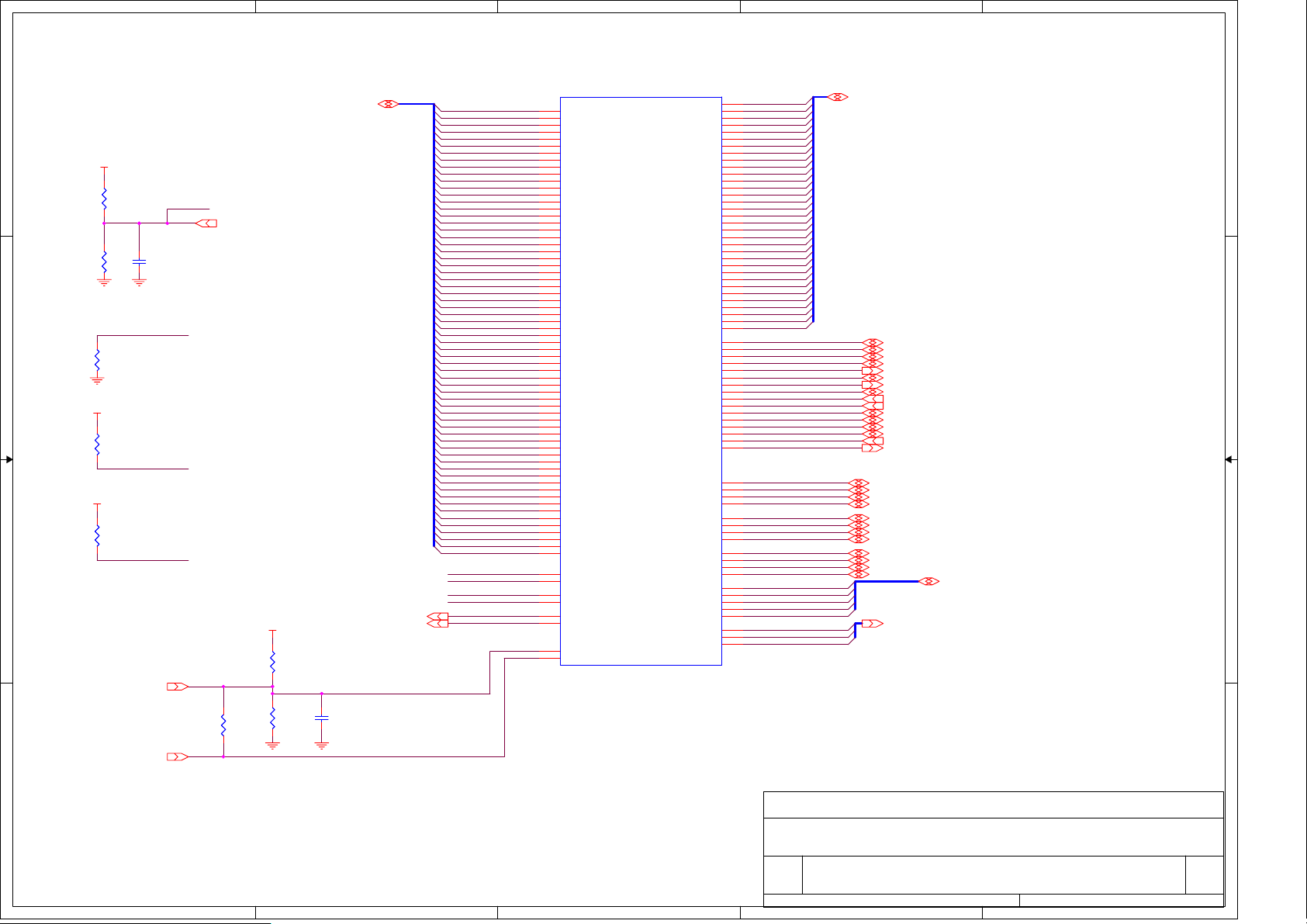

SANTA ROSA CUSTOMER REFERENCE PLATFORM

SCHEMATIC ANNOTATIONS AND BOARD INFORMATION

D D

Voltage Rails

+VBATA

+VBAT

+VBATS

+V12S

-V12A

-V12S

+V5A

+V5

+V5S

+V3.3A

+V3.3M

+V3.3M_CK505

+V3.3

+V3.3S

+V1.8

+V1.5S

+V1.25M

+V1.25S

+V1.05M

+V1.05S

+V0.9

+VCC_CORE

+VCC_GFXCORE

VOLTAGE DESCRIPTIONACTIVE INPOWER PLANE

9V-12.5V

9V-12.5V

9V-12.5V

12V

-12V

-12V

5V

5V

5V

3.3V

3.3V

3.3V

3.3V

3.3V

1.8V

1.5V

1.25V

1.25V

1.05V

1.05V

0.9V

0.700V-1.77V

0.7V-1.25V

S0/M0, (S3-S5)/M1, (S3-S5)/M-off

S0/M0, (S3-S5)/M1, (S3-S5)/M-off

S0/M0

S0/M0

S0/M0, (S3-S5)/M1, (S3-S5)/M-off

S0/M0

S0/M0, (S3-S5)/M1, (S3-S5)/M-off

S0/M0,° 3/M1, S3/M-off

ٛ

S0/M0

S0/M0, (S3-S5)/M1, (S3-S5)/M-off

S0/M0, (S3-S5)/M1, S3/(M-off w/WOL_EN)

S0/M0, (S3-S5)/M1

S0/M0, S3/M1, S3/M-off

S0/M0

S0/M0, (S3-S5)/M1, S3/M-off

S0/M0

S0/M0, (S3-S5)/M1

S0/M0

S0/M0, (S3-S5)/M1

S0/M0

S0/M0, (S3-S5)/M1, S3/M-off

S0/M0

S0/M0

Battery Rail in Mobile Power Mode

Battery Rail in Mobile Power Mode

Battery Rail in Mobile Power Mode

Only on in DT Power Mode

Only on in DT Power Mode

Only on in DT Power Mode

LAN

Clock, MCH

DDR core

GMCH, ICH core, and FSB rail

DDR command & control pull up.

CPU core rail

GMCH Graphics core rail

2

I C / SMB Addresses

Clock Generator

DB800 Clock Buffer

SO-DIMM0

SO-DIMM1

SO-DIMM0 Thermal Sensor

SO-DIMM1 Thermal Sensor

DDR Thermal Sensor

I2C Bus Expander

Ambient Lighr Sensor

EMA Display

CPU Thermal Sensor

IMVP6 Amb. Temp. Sensor

Battery A

Battery B

Board ID Port Expander

Docking Port Expander

Skin Temperature Sensor

H8

PCI-Slot3

PCI-Gold Finger

PCI-Express Slot1-5

Docking

PCIe x16 Slot (PEG)

TPM Header

ITP-XDP

AddressDevice

1101 001x

1101 110x

1010 000x

1010 010x

0011 000x

0011 010x

0100 110x

0011 xxxx

0111 001x

0011 110x

1001 100x

1001 101x

0001 011x

0001 111x

0011 000x

0011 001x

1001 100x

TBD

TBD

TBD

TBD

TBD

TBD

TBD

TBD

BusHex PageJumper DescriptionDefault

D2

SMB_ICH_M3

DC

SMB_ICH_M3

A0

SMB_ICH_M2

A4

SMB_ICH_M2

30

SMB_ICH_M2

34

SMB_ICH_M2

4C

SMB_ICH_M2

3x

SMB_ICH

72

ALS

3C

EMA

98

SMB_THRM

9A

SMB_THRM

16

SMB_BS

1E

SMB_BS

30

SMB_BS

32

SMB_BS

98

SMB_BS

TBD

SMB_ME

TBD

SMB_ICH_A1

TBD

SMB_ICH_A1

TBD

SMB_ICH_A1

TBD

SMB_ICH_A1

TBD

SMB_ICH_S4

TBD

SMB_ICH_S4

TBD

SMB_ICH_S4

C C

Buses labeled SMB_ICH_xx come out of ICH, via an I2C expander.

The rest come out of EC.

Jumper / Switch Settings

J1G2

1-2

J1G5

J1G8

J2G1

J2G1

J2G1

J2G1

J2G1

J2H1

J3B2

J3G1

J4H1

J5H2

J6H2

J7D1

J7J2

J8B1

J8B2

J8E2

J8F2

J9F1

J9G2

J9H1

J9H2

J9H3

J9H4

J9H5

J9H6

J9H7

J9H8

J9H9

BSEL0

1-2

BSEL1

1-2

BSEL2

1-2

GFX CORE

3-4

GFX CORE

5-6

GFX CORE

7-8

GFX CORE

11-12

GFX CORE

1-X

Force Shutdown

1-2, 3-4

CPU thermal sensor

1-X

Power ON Latch

1-X

ME G3 to M1

1-X

CMOS Clear

1-2

CRB/SV Detect

1-2

SIO Reset

1-2

SATA Power Enable

1-2

In-circuit SMC Programming

1-2

In-circuit SMC Programming

1-X

Boot BIOS Strap

1-X

BIOS recovery

1-2

KSC Enable

1-2

Boot Block Programming

1-X

Virtual Docking

1-X

NMI

1-X

KBC disable

1-2

SMC MD0

1-2

SATA device detect

1-X

SMC MD2

1-2

SMC MD1

1-X

LID Position

1-X

Virtual Battery

37

37

37

49

49

49

49

49

55

5

55

55

21

23

40

31

41

41

22

23

42

43

42

43

42

42

31

42

42

42

42

Changes for Matanzas with PM GMCH SKU

SL No NO_STUFF STUFF

U6E2, U6E3, U6E4

1

L5F1

2

3

4

5

6

R5E5, R5F9, R5T16,

R5U3, R5U11, R5U14,

R5U21, R6V1

C5E8, C5E9, C5E11,

C5E12, C5E13, C5E14,

C5E15, C5T12, C5T13,

C5U1, C5U2, C5U3

FB5F1, FB5F2, FB5T1

J2G1(3 4), J2G1(5 6),

R5E4, R5T5, R5T8,

R5T9, R5T10,

R5T12, R5T17

C5E8,C5E9,C5T13,C5U3

with 0 Ohm 0402 size res

IPN A93549-001

J2G1(1 2), J2G1(13 14)

PCI Devices

PageSwitch Default Description

42

42

42

Wake Events

Wake Events

RI# from serial port

PME# from PCI, mini PCI slot/device, LPC slot/device

PCI Express, mini PCI Express, Express-card wake event

Wake on LAN

LID switch attached to SMC

USB

HDA wake on ring

SmLink for AOLII

Hot Key from Scan matrix keyboard

PS/2 Keyboard/mouse

PWRBTN#

Netdetect

PCB Footprints

1

2

SOT-23

3

As seen from top

1

2

3

2

State Supported

S3

S3

S3

S3/M1

S3

S3

S3

S3

S3

S3

S3

S3, S4, S5 / M1

SOT23-5

5

4

Intel Confidential

Intel Confidential

Intel Confidential

1.5

1.5

1.5

258Wednesday, December 06, 2006

258Wednesday, December 06, 2006

258Wednesday, December 06, 2006

of

of

of

1

SLP_S4#

HIGH

HIGH

HIGH

HIGH

HIGH

HIGH

LOW

LOW

Interrupts

SLP_S5#

HIGH

HIGH

HIGH

HIGH

HIGH

LOW

HIGH

LOW

SLP_M#

HIGH

HIGH

LOW

LOW

HIGH

HIGH

LOW

LOW

+V*A

ON

ON

ON

ON

ON

ON

ON

ON

+V3.3M

ON

ON

OFF

ON

ON

ON

OFF

OFF

+V1.25M/

+V1.05M

ON

ON

OFF

OFF

ON

ON

OFF

OFF

4

+V3.3M_CK505

ON

ON

OFF

OFF

ON

ON

OFF

OFF

+V1.8/+V0.9

ON

ON

ON

ON

ON

ON

OFF

OFF

+V5/+V3.3

ON

ON

ON

ON

OFF

OFF

OFF

OFF

+V*S

ON

OFF

OFF

OFF

OFF

OFF

OFF

OFF

Clocks

ON

only MCH BCLK

OFF

OFF

only MCH BCLK

only MCH BCLK

OFF

OFF

3

SW9H1

1 - 2

1 - 2

1 - 2

Virtual Docking

Virtual Battery

LID Switch

SW9H2

SW9J1

LEDs and Switches

LED

xTA Activity

VID0

VID1

VID2

VID3

VID4

VID5

VID6

Num Lock

Scroll Lock

Caps Lock

S3

M0/M1

S4

S5

S0

System Power Good

Switch Page Reference

Power Button

Reset Button

Net Detect

Virtual Docking

Virtual Battery

LID Switch

21

41

41

41

41

41

41

41

42

42

42

57

57

57

57

57

57

55

55

55

42

42

42

Matanzas

Matanzas

Matanzas

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

ReferencePage

CR6J1

CR1B1

CR1B2

CR1B3

CR1B4

CR1B5

CR1B6

CR1B7

CR9G1

CR9G2

CR9G3

CR3G2

CR4H1

CR5H3

CR5H4

CR5H5

CR5J1

SW1C1

SW1C2

SW8E1

SW9H1

SW9H2

SW9J1

NOTES

NOTES

NOTES

A

A

A

NDA

NDA

NDA

Device

LAN

IDSEL #

AD18 D, C, A, BSlot 3

(AD24 internal)

REQ/GNT #

22

Net Naming Conventions

Suffix

# = Active Low Signal

Prefix

H = Host

M = DDR Memory

TP = Test Point (does not connect anywhere else)

B B

Power States

S0 (Full on)/M0

S3 (Suspend to RAM)/M1

S3 (Suspend to RAM)/Moff

S3 (Susp to RAM)/Moff w/WOL_EN

S4 (Suspend to Disk)/M1

S5 (Soft Off)/M1

S4 (Suspend to Disk)/Moff

S5 (Soft Off)/Moff

SLP_S3#

HIGH

LOW

LOW

LOW

LOW

LOW

LOW

LOW

S4_STATE#

HIGH

HIGH

HIGH

HIGH

LOW

LOW

LOW

LOW

A A

5

Page 4

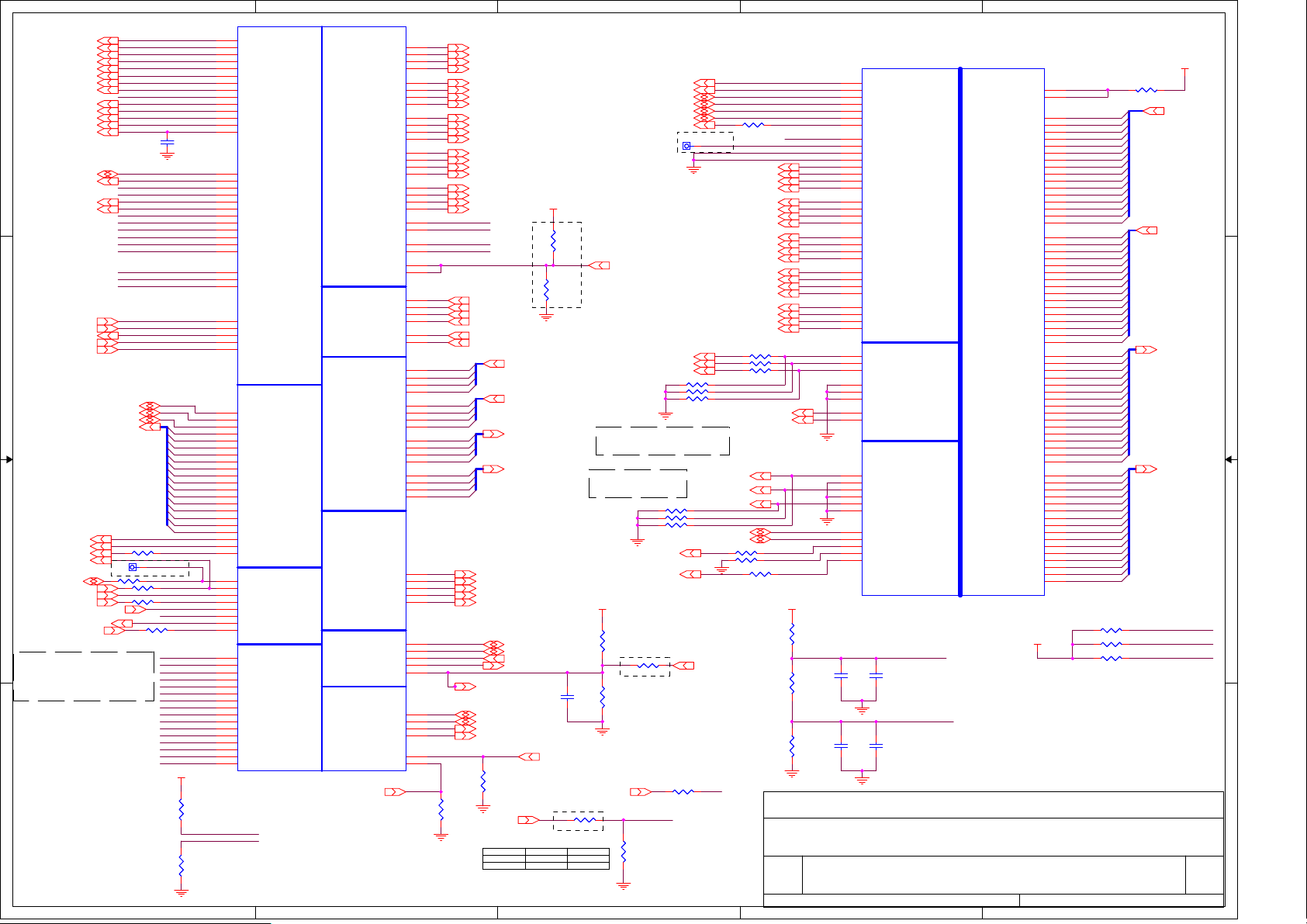

5

4

+V1.05S_CPU4,20,37,41,44,54

3

2

1

H_A#[35:3]6

D D

H_ADSTB#06

H_REQ#[4:0]6

H_A#[35:3]6

Layout note:

no stub on H_STPCLK TP.

H_STPCLK# to be routed in daisy

chain fashion from ICH to LPC slot

and then to CPU.

C C

H_STPCLK#_R

TP1E1NO_STUFF TP1E1NO_STUFF

H_STPCLK#21,44

Layout Note:

TP1E1 should be placed

close to J1F4

H_ADSTB#16

H_A20M#21

H_FERR#21

H_IGNNE#21

R2U4 0

R2U4 0

H_INTR21

H_NMI21,44

H_SMI#21,44

CPU_RSVD07

CPU_RSVD10

.

.

TP_CPU_RSVD01

TP_CPU_RSVD02

TP_CPU_RSVD03

TP_CPU_RSVD04

TP_CPU_RSVD05

TP_CPU_RSVD06

TP_CPU_RSVD08

TP_CPU_RSVD09

B B

XDP_TMS

XDP_TDI

XDP_BPM#5

XDP_TCK

XDP_TRST#

H_A#3

H_A#4

L5

H_A#5

L4

H_A#6

K5

H_A#7

M3

H_A#8

N2

H_A#9

H_A#10

N3

H_A#11

P5

H_A#12

P2

H_A#13

L2

H_A#14

P4

H_A#15

P1

H_A#16

R1

M1

H_REQ#0

K3

H_REQ#1

H2

H_REQ#2

K2

H_REQ#3

H_REQ#4

L1

H_A#17

Y2

H_A#18

U5

H_A#19

R3

H_A#20

W6

H_A#21

U4

H_A#22

Y5

H_A#23

U1

H_A#24

R4

H_A#25

T5

H_A#26

T3

H_A#27

W2

H_A#28

W5

H_A#29

Y4

H_A#30

U2

H_A#31

V4

H_A#32

W3

H_A#33

AA4

H_A#34

AB2

H_A#35

AA3

V1

A6

A5

C4

D5

C6

B4

A3

M4

N5

T2

V3

B2

C3

D2

D22

D3

F6

R1R5 54.9

R1R5 54.9

R2R3 54.9

R2R3 54.9

R1R4 54.9

R1R4 54.9

R2R4 54.9

R2R4 54.9

R2R5 649

R2R5 649

U2E1A

U2E1A

J4

A[3]#

A[4]#

A[5]#

A[6]#

A[7]#

A[8]#

J1

A[9]#

A[10]#

A[11]#

A[12]#

A[13]#

A[14]#

A[15]#

A[16]#

ADSTB[0]#

REQ[0]#

REQ[1]#

REQ[2]#

J3

REQ[3]#

REQ[4]#

A[17]#

A[18]#

A[19]#

A[20]#

A[21]#

A[22]#

A[23]#

A[24]#

A[25]#

A[26]#

A[27]#

A[28]#

A[29]#

A[30]#

A[31]#

A[32]#

A[33]#

A[34]#

A[35]#

ADSTB[1]#

A20M#

FERR#

IGNNE#

STPCLK#

LINT0

LINT1

SMI#

RSVD[01]

RSVD[02]

RSVD[03]

RSVD[04]

RSVD[05]

RSVD[06]

RSVD[07]

RSVD[08]

RSVD[09]

RSVD[10]

Merom Ball-out Rev 1a

Merom Ball-out Rev 1a

+V1.05S_CPU4,20,37,41,44,54

1%

1%

1%

1%

1%

1%

1%

1%

1%

1%

.

.

ADDR GROUP 0 ADDR GROUP 1

ADDR GROUP 0 ADDR GROUP 1

ADS#

BNR#

BPRI#

DEFER#

DRDY#

DBSY#

BR0#

IERR#

INIT#

LOCK#

CONTROL

CONTROL

RESET#

RS[0]#

RS[1]#

RS[2]#

TRDY#

HIT#

HITM#

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

PRDY#

PREQ#

TCK

TDI

TDO

TMS

XDP/ITP SIGNALS

XDP/ITP SIGNALS

TRST#

DBR#

THERMAL

THERMAL

PROCHOT#

THERMDA

THERMDC

ICH

ICH

THERMTRIP#

H CLK

H CLK

BCLK[0]

BCLK[1]

RESERVED

RESERVED

H1

E2

G5

H5

F21

E1

F1

D20

B3

H4

C1

H_RS#0

F3

H_RS#1

F4

H_RS#2

G3

G2

G6

E4

AD4

AD3

AD1

AC4

AC2

AC1

AC5

AA6

AB3

AB5

AB6

C20

H_PROCHOT#_D

D21

A24

B25

C7

A22

A21

H_ADS# 6

H_BNR# 6

H_BPRI# 6

H_DEFER# 6

H_DRDY# 6

H_DBSY# 6

H_BREQ# 6

H_INIT# 21

H_LOCK# 6

H_CPURST# 6,20

H_RS#[2:0] 6

H_TRDY# 6

H_HIT# 6

H_HITM# 6

XDP_BPM#1 37

XDP_BPM#2 37

XDP_BPM#3 37

XDP_BPM#4 20

XDP_BPM#5 20

XDP_TCK 20

XDP_TDI 20

XDP_TDO 20

XDP_TMS 20

XDP_TRST# 20

XDP_DBRESET# 20, 55

H_THERMDA 5

H_THERMDC 5

PM_THRMTRIP# 7,21

CLK_CPU_BCLK 37

CLK_CPU_BCLK# 37

CPU_TEST1

CPU_TEST2

R2U956R2U9

56

Connect H_IERR# with no

stub to the connector

J2F3 and then connect

to the 56 ohm pull up

Resistor R2U9.

H_IERR#

Place testpoint on

H_IERR# with a GND

0.1" away

NO_STUFF

NO_STUFF

TP1D1

TP1D1

XDP_BPM#0 20

+V1.05S_CPU4,20,37,41,44,54

TP2F1

TP2F1

R3E1

R3E1

1K

1K

1%

1%

.

.

NO_STUFF

NO_STUFF

PM_THRMTRIP# should connect

to ICH8 and GMCH without

T-ing (No stub)

H_GTLREF

Layout note: Zo=55 ohm,

0.5" max for GTLREF.

C3R1

C3R1

0.1uF

0.1uF

10%

10%

NO_STUFF

NO_STUFF

NO_STUFF

R2U7 1K

R2U7 1K

NO_STUFF

NO_STUFF

NO_STUFF

R2U6 1K

R2U6 1K

Place C3R1 close to the CPU_TEST4 pin.

Make sure CPU_TEST4 routing is reference

to GND and away from other noisy signals.

Place TP close

to CPU.

+V1.05S_CPU4,20,37,41,44,54

R3R5

R3R5

1K

1K

1%

1%

.

.

R3R4

R3R4

2K

2K

1%

1%

.

.

R2F30R2F3

0

H_PROCHOT# 52

H_DSTBN#06

H_DSTBP#06

H_DINV#06

H_D#[63:0]6

CPU_TEST3

CPU_TEST5

CPU_TEST6

H_D#[63:0]6

H_DSTBN#16

H_DSTBP#16

H_DINV#16

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

CPU_TEST4

CPU_TEST6

CPU_BSEL037

CPU_BSEL137

CPU_BSEL237

U2E1B

U2E1B

E22

D[0]#

F24

D[1]#

E26

D[2]#

G22

D[3]#

F23

D[4]#

G25

D[5]#

E25

D[6]#

E23

D[7]#

K24

D[8]#

G24

D[9]#

J24

D[10]#

J23

D[11]#

H22

D[12]#

F26

D[13]#

K22

D[14]#

H23

D[15]#

J26

DSTBN[0]#

H26

DSTBP[0]#

H25

DINV[0]#

N22

D[16]#

K25

D[17]#

P26

D[18]#

R23

D[19]#

L23

D[20]#

M24

D[21]#

L22

D[22]#

M23

D[23]#

P25

D[24]#

P23

D[25]#

P22

D[26]#

T24

D[27]#

R24

D[28]#

L25

D[29]#

T25

D[30]#

N25

D[31]#

L26

DSTBN[1]#

M26

DSTBP[1]#

N24

DINV[1]#

AD26

GTLREF

C23

TEST1

D25

TEST2

C24

TEST3

AF26

TEST4

AF1

TEST5

A26

TEST6

B22

BSEL[0]

B23

BSEL[1]

C21

BSEL[2]

Merom Ball-out Rev 1a

Merom Ball-out Rev 1a

DATA GRP 0

DATA GRP 0

DATA GRP 2DATA GRP 3

DATA GRP 2DATA GRP 3

DSTBN[2]#

DSTBP[2]#

DATA GRP 1

DATA GRP 1

DSTBN[3]#

DSTBP[3]#

MISC

MISC

PWRGOOD

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

D[41]#

D[42]#

D[43]#

D[44]#

D[45]#

D[46]#

D[47]#

DINV[2]#

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[60]#

D[61]#

D[62]#

D[63]#

DINV[3]#

COMP[0]

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

DPWR#

SLP#

PSI#

Y22

AB24

V24

V26

V23

T22

U25

U23

Y25

W22

Y23

W24

W25

AA23

AA24

AB25

Y26

AA26

U22

AE24

AD24

AA21

AB22

AB21

AC26

AD20

AE22

AF23

AC25

AE21

AD21

AC22

AD23

AF22

AC23

AE25

AF24

AC20

R26

U26

AA1

Y1

E5

B5

D24

D6

D7

AE6

Layout: Connect

test point TP3E1

with no stub

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

COMP0

COMP1

COMP2

COMP3

H_DPRSTP# 7,21,44,52

H_DPSLP# 21,44

H_CPUSLP# 6,44

PSI# 52

R3T1 27.4 1%R3T1 27.4 1%

R3R6 54.9 1%R3R6 54.9 1%

R2R7 27.4 1%R2R7 27.4 1%

R2R6 54.9 1%R2R6 54.9 1%

H_D#[63:0] 6

H_DSTBN#2 6

H_DSTBP#2 6

H_DINV#2 6

H_D#[63:0] 6

Layout note:

Comp0,2 connect with Zo=27.4ohm, make

trace length shorter than 0.5".

Comp1,3 connect with Zo=55ohm, make

trace length shorter than 0.5".

H_DSTBN#3 6

H_DSTBP#3 6

H_DINV#3 6

H_DPWR# 6

TP3E1

TP3E1

NO_STUFF

NO_STUFF

R2T3 1K

R2T3 1K

.

.

Place Series Resistor

on H_PWRGD_XDP Without

Stub

5%

5%

H_PWRGD 21,44

H_PWRGD_XDP 20

A A

Intel Confidential

Intel Confidential

358Tuesday, December 05, 2006

358Tuesday, December 05, 2006

358Tuesday, December 05, 2006

1

Intel Confidential

1.5

1.5

1.5

of

of

of

Matanzas

Matanzas

Matanzas

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

5

4

3

Date: Sheet

Intel® Core™2 Duo Mobile Processor (1 of 2)

Intel® Core™2 Duo Mobile Processor (1 of 2)

Intel® Core™2 Duo Mobile Processor (1 of 2)

NDA

NDA

NDA

2

Page 5

5

4

3

2

1

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

+VCC_CORE53,54,56

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

CPU_G21

G21

CPU_V6

V6

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

B26

C26

AD6

AF5

AE5

AF4

AE3

AF3

AE2

AF7

AE7

.

.

R2T1 and R3T3 are for

testing purposes only

R3T3 0

R3T3 0

R2T1 0

R2T1 0

.

.

.

.

H_VID0 52

H_VID1 52

H_VID2 52

H_VID3 52

H_VID4 52

H_VID5 52

H_VID6 52

C3T1

C3T1

270uF

270uF

20%

20%

.

.

+V1.05S_CPU3,20,37,41,44,54

+VCC_CORE53,54,56

R2R1

R2R1

100

100

1%

1%

.

.

R2R2

R2R2

100

100

1%

1%

.

.

C3T4

C3T4

0.01uF

0.01uF

10%

10%

.

.

VCCSENSE 52

VSSSENSE 52

R3T2

R3T2

0

0

R3R7

R3R7

0

0

+VCCA_PROC

C3T3

C3T3

10uF

10uF

20%

20%

.

.

Layout Note:

Route VCCSENSE and VSSSENSE traces at

27.4 Ohms with 50 mil spacing.

Place PU and PD within 1 inch of CPU.

R3U1 0.01

R3U1 0.01

Layout Note:

Place C3T4 near pin-B26

12

NO_STUFF

NO_STUFF

12

NO_STUFF

NO_STUFF

1%

1%

+V1.05S9,10,24,48,56

+V1.5S10,11,24,28,48,56

U2E1D

U2E1D

A4

VSS[001]

A8

VSS[002]

A11

VSS[003]

A14

VSS[004]

A16

VSS[005]

A19

VSS[006]

A23

VSS[007]

AF2

VSS[008]

B6

VSS[009]

B8

VSS[010]

B11

VSS[011]

B13

VSS[012]

B16

VSS[013]

B19

VSS[014]

B21

VSS[015]

B24

VSS[016]

C5

VSS[017]

C8

VSS[018]

C11

VSS[019]

C14

VSS[020]

C16

VSS[021]

C19

VSS[022]

C2

VSS[023]

C22

VSS[024]

C25

VSS[025]

D1

VSS[026]

D4

VSS[027]

D8

VSS[028]

D11

VSS[029]

D13

VSS[030]

D16

VSS[031]

D19

VSS[032]

D23

VSS[033]

D26

VSS[034]

E3

VSS[035]

E6

VSS[036]

E8

VSS[037]

E11

VSS[038]

E14

VSS[039]

E16

VSS[040]

E19

VSS[041]

E21

VSS[042]

E24

VSS[043]

F5

VSS[044]

F8

VSS[045]

F11

VSS[046]

F13

VSS[047]

F16

VSS[048]

F19

VSS[049]

F2

VSS[050]

F22

VSS[051]

F25

VSS[052]

G4

VSS[053]

G1

VSS[054]

G23

VSS[055]

G26

VSS[056]

H3

VSS[057]

H6

VSS[058]

H21

VSS[059]

H24

VSS[060]

J2

VSS[061]

J5

VSS[062]

J22

VSS[063]

J25

VSS[064]

K1

VSS[065]

K4

VSS[066]

K23

VSS[067]

K26

VSS[068]

L3

VSS[069]

L6

VSS[070]

L21

VSS[071]

L24

VSS[072]

M2

VSS[073]

M5

VSS[074]

M22

VSS[075]

M25

VSS[076]

N1

VSS[077]

N4

VSS[078]

N23

VSS[079]

N26

VSS[080]

VSS[081]P3VSS[162]

Merom Ball-out Rev 1a

Merom Ball-out Rev 1a

VSS[082]

VSS[083]

VSS[084]

VSS[085]

VSS[086]

VSS[087]

VSS[088]

VSS[089]

VSS[090]

VSS[091]

VSS[092]

VSS[093]

VSS[094]

VSS[095]

VSS[096]

VSS[097]

VSS[098]

VSS[099]

VSS[100]

VSS[101]

VSS[102]

VSS[103]

VSS[104]

VSS[105]

VSS[106]

VSS[107]

VSS[108]

VSS[109]

VSS[110]

VSS[111]

VSS[112]

VSS[113]

VSS[114]

VSS[115]

VSS[116]

VSS[117]

VSS[118]

VSS[119]

VSS[120]

VSS[121]

VSS[122]

VSS[123]

VSS[124]

VSS[125]

VSS[126]

VSS[127]

VSS[128]

VSS[129]

VSS[130]

VSS[131]

VSS[132]

VSS[133]

VSS[134]

VSS[135]

VSS[136]

VSS[137]

VSS[138]

VSS[139]

VSS[140]

VSS[141]

VSS[142]

VSS[143]

VSS[144]

VSS[145]

VSS[146]

VSS[147]

VSS[148]

VSS[149]

VSS[150]

VSS[151]

VSS[152]

VSS[153]

VSS[154]

VSS[155]

VSS[156]

VSS[157]

VSS[158]

VSS[159]

VSS[160]

VSS[161]

VSS[163]

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

A2

AF6

AF8

AF11

AF13

AF16

AF19

AF21

A25

AF25

.

.

+VCC_CORE53,54,56

D D

C C

U2E1C

U2E1C

A7

VCC[001]

A9

VCC[002]

A10

VCC[003]

A12

VCC[004]

A13

VCC[005]

A15

VCC[006]

A17

VCC[007]

A18

VCC[008]

A20

VCC[009]

B7

VCC[010]

B9

VCC[011]

B10

VCC[012]

B12

VCC[013]

B14

VCC[014]

B15

VCC[015]

B17

VCC[016]

B18

VCC[017]

B20

VCC[018]

C9

VCC[019]

C10

VCC[020]

C12

VCC[021]

C13

VCC[022]

C15

VCC[023]

C17

VCC[024]

C18

VCC[025]

D9

VCC[026]

D10

VCC[027]

D12

VCC[028]

D14

VCC[029]

D15

VCC[030]

D17

VCC[031]

D18

VCC[032]

E7

VCC[033]

E9

VCC[034]

E10

VCC[035]

E12

VCC[036]

E13

VCC[037]

E15

VCC[038]

E17

VCC[039]

E18

VCC[040]

E20

VCC[041]

F7

VCC[042]

F9

VCC[043]

F10

VCC[044]

F12

VCC[045]

F14

VCC[046]

F15

VCC[047]

F17

VCC[048]

F18

VCC[049]

F20

VCC[050]

AA7

VCC[051]

AA9

VCC[052]

AA10

VCC[053]

AA12

VCC[054]

AA13

VCC[055]

AA15

VCC[056]

AA17

VCC[057]

AA18

VCC[058]

AA20

VCC[059]

AB9

VCC[060]

AC10

VCC[061]

AB10

VCC[062]

AB12

VCC[063]

AB14

VCC[064]

AB15

VCC[065]

AB17

VCC[066]

AB18

VCC[067]

Merom Ball-out Rev 1a

Merom Ball-out Rev 1a

VCC[068]

VCC[069]

VCC[070]

VCC[071]

VCC[072]

VCC[073]

VCC[074]

VCC[075]

VCC[076]

VCC[077]

VCC[078]

VCC[079]

VCC[080]

VCC[081]

VCC[082]

VCC[083]

VCC[084]

VCC[085]

VCC[086]

VCC[087]

VCC[088]

VCC[089]

VCC[090]

VCC[091]

VCC[092]

VCC[093]

VCC[094]

VCC[095]

VCC[096]

VCC[097]

VCC[098]

VCC[099]

VCC[100]

VCCP[01]

VCCP[02]

VCCP[03]

VCCP[04]

VCCP[05]

VCCP[06]

VCCP[07]

VCCP[08]

VCCP[09]

VCCP[10]

VCCP[11]

VCCP[12]

VCCP[13]

VCCP[14]

VCCP[15]

VCCP[16]

VCCA[01]

VCCA[02]

VCCSENSE

VSSSENSE

B B

A A

Intel Confidential

Intel Confidential

458Tuesday, November 21, 2006

458Tuesday, November 21, 2006

458Tuesday, November 21, 2006

1

Intel Confidential

1.5

1.5

1.5

of

of

of

Matanzas

Matanzas

Matanzas

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

5

4

3

Date: Sheet

Intel® Core™2 Duo Mobile Processor (2 of 2)

Intel® Core™2 Duo Mobile Processor (2 of 2)

Intel® Core™2 Duo Mobile Processor (2 of 2)

NDA

NDA

NDA

2

Page 6

5

4

3

2

1

D D

C C

Layout Note:

Route H_THERMDA and

H_THERMDC on same layer w/

10 mil trace & 10 mil

spacing. Route away from

noise sources with ground

guard tracks on each side.

H_THERMDA3

H_THERMDC3

GND0

GND0

GND1

GND1

Thermal Diode Connector

J3B2

Default Stuffing: 1-2 3-4

Option Stuffing: 1-X 3-X

1

3

J4A1

J4A1

3Pin_Recepticle

3Pin_Recepticle

12

THERMDNTHERMDP

THERMDNTHERMDP

GND2

GND2

3 4 5 6

GND3

GND3

J3B2

J3B2

2X2HDR

2X2HDR

NO_STUFF

NO_STUFF

THERM_DXP

2

4

THERM_DXN

R3N26 499

R3N26 499

R3N25 499

R3N25 499

+V3.3S7,10,12,16..26,28,30..32,34,37..42,44,45,49,50,52,55..57

R3N21

R3N21

10K

10K

5%

5%

.

.

1%

1%

.

.

1%

1%

.

.

ADT_THERM_DXP

C3N10

C3N10

1000pF

1000pF

ADT_THERM_DXN

5%

5%

.

.

ADT_THM# THRM_ALERT#

CPU Thermal Sensor

C3N9

C3N9

0.1uF

0.1uF

20%

20%

.

.

U3B4

U3B4

1

VDD

2

D+

3

D-

ALRT#/THM2#

4

THM#

ADT7461A-TEMP MON

ADT7461A-TEMP MON

SCLK

SDATA

GND

8

7

6

5

+V3.3S7,10,12,16..26,28,30..32,34,37..42,44,45,49,50,52,55..57

R3N19

R3N19

R3N22

R3N22

10K

10K

10K

10K

5%

5%

5%

5%

.

.

.

.

SMB_THRM_CLK 12,42,44

SMB_THRM_DATA 12,42,44

R3N20 0

R3N20 0

NO_STUFF

NO_STUFF

Note: No-Stuff R3N20 for normal operation,

No Stuff (R9G18 P42) if R3N20 is stuffed

PM_THRM# 12,23,42,44

CPU Fan Power Control

+V5S11,12,16..18,24,30..32,34,41,49,50,52,53,55..57

C3N3

C3N3

C3N5

C3N5

0.1uF

0.1uF

4.7uF

4.7uF

10%

10%

10%

B B

R3N14 15K

CPU_PWM_FAN42,44

R3N14 15K

OPA567_POSIN

1%

1%

.

.

10%

.

.

.

.

1

101112

EU3B1

EU3B1

V+

V+

_

C3B4

C3B4

1uF

1uF

10%

10%

.

.

_

8

OPA567

OPA567

9

+

+

V-

V-

456

HS

HS

TF

TF

EN

EN

IF

IF

IS

IS

13

OPA567_ISIN_R

2

OUT

OUT

3

.

.

7

OPA567_NEGIN

R3N7

R3N7

20K

20K

5%

5%

.

.

VOUT_OPAMP

CR2N1

CR2N1

BAT54

BAT54

R3N8

R3N8

1.74K

1.74K

1%

1%

.

.

R3N10

R3N10

3.32K

3.32K

1%

1%

.

.

2

CPU_TACHO_R_FAN

11332

3

1

J2B3

J2B3

CONN3_HDR

CONN3_HDR

.

.

R2N5 0

R2N5 0

A A

5

4

3

+V3.3S7,10,12,16..26,28,30..32,34,37..42,44,45,49,50,52,55..57

R2N8

R2N8

1K

1K

1%

1%

.

.

CPU_TACHO_FAN 42,44

.

.

Intel Confidential

Intel Confidential

558Tuesday, December 05, 2006

558Tuesday, December 05, 2006

558Tuesday, December 05, 2006

1

Intel Confidential

1.5

1.5

1.5

of

of

of

Matanzas

Matanzas

Matanzas

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

CPU Thermal Sensor & Fan

CPU Thermal Sensor & Fan

CPU Thermal Sensor & Fan

A

A

A

NDA

NDA

NDA

2

Page 7

5

D D

+VCCP_GMCH10

R4E5

R4E5

221

221

1%

1%

.

.

R4E4

R4E4

100

100

1%

1%

.

.

R4E3

C C

R4E3

24.9

24.9

1%

1%

.

.

+VCCP_GMCH10

R4E2

R4E2

54.9

54.9

1%

1%

+VCCP_GMCH10

R4E1

R4E1

54.9

54.9

1%

1%

C4E10

C4E10

0.1uF

0.1uF

20%

20%

.

.

H_RCOMP

H_SCOMP

H_SCOMP#

H_SWING

H_SWING

B B

+VCCP_GMCH10

R4F7

R4F7

1K

1K

1%

1%

.

H_AVREF

H_DVREF

R4F4

R4F4

0

0

.

.

.

R4F2

R4F2

2K

2K

1%

1%

.

.

C4E12

C4E12

0.1uF

0.1uF

10%

10%

4

U5E1A

M10

W10

AD12

AE3

AD9

AC9

AC7

AC14

AD11

AC11

AB2

AD7

AB1

AC6

AE2

AC5

AG3

AH8

AJ14

AE9

AE11

AH12

AH5

AE7

AE5

AH2

AH13

E2

G2

G7

M6

H7

H3

G4

F3

N8

H2

N12

N9

H5

P13

K9

M2

Y8

V4

M3

J1

N5

N3

W6

W9

N2

Y7

Y9

P4

W3

N1

Y3

AJ9

AJ5

AJ6

AJ7

AJ2

AJ3

B3

C2

W1

W2

B6

E5

B9

A9

U5E1A

H_D#_0

H_D#_1

H_D#_2

H_D#_3

H_D#_4

H_D#_5

H_D#_6

H_D#_7

H_D#_8

H_D#_9

H_D#_10

H_D#_11

H_D#_12

H_D#_13

H_D#_14

H_D#_15

H_D#_16

H_D#_17

H_D#_18

H_D#_19

H_D#_20

H_D#_21

H_D#_22

H_D#_23

H_D#_24

H_D#_25

H_D#_26

H_D#_27

H_D#_28

H_D#_29

H_D#_30

H_D#_31

H_D#_32

H_D#_33

H_D#_34

H_D#_35

H_D#_36

H_D#_37

H_D#_38

H_D#_39

H_D#_40

H_D#_41

H_D#_42

H_D#_43

H_D#_44

H_D#_45

H_D#_46

H_D#_47

H_D#_48

H_D#_49

H_D#_50

H_D#_51

H_D#_52

H_D#_53

H_D#_54

H_D#_55

H_D#_56

H_D#_57

H_D#_58

H_D#_59

H_D#_60

H_D#_61

H_D#_62

H_D#_63

H_SWING

H_RCOMP

H_SCOMP

H_SCOMP#

H_CPURST#

H_CPUSLP#

H_AVREF

H_DVREF

CRESTLINE_1p0

CRESTLINE_1p0

H_D#[63:0]3

H_CPURST#3,20

H_CPUSLP#3,44

.

.

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_SWING

H_RCOMP

H_SCOMP

H_SCOMP#

3

HOST

HOST

H_A#_3

H_A#_4

H_A#_5

H_A#_6

H_A#_7

H_A#_8

H_A#_9

H_A#_10

H_A#_11

H_A#_12

H_A#_13

H_A#_14

H_A#_15

H_A#_16

H_A#_17

H_A#_18

H_A#_19

H_A#_20

H_A#_21

H_A#_22

H_A#_23

H_A#_24

H_A#_25

H_A#_26

H_A#_27

H_A#_28

H_A#_29

H_A#_30

H_A#_31

H_A#_32

H_A#_33

H_A#_34

H_A#_35

H_ADS#

H_ADSTB#_0

H_ADSTB#_1

H_BNR#

H_BPRI#

H_BREQ#

H_DEFER#

H_DBSY#

HPLL_CLK

HPLL_CLK#

H_DPWR#

H_DRDY#

H_HIT#

H_HITM#

H_LOCK#

H_TRDY#

H_DINV#_0

H_DINV#_1

H_DINV#_2

H_DINV#_3

H_DSTBN#_0

H_DSTBN#_1

H_DSTBN#_2

H_DSTBN#_3

H_DSTBP#_0

H_DSTBP#_1

H_DSTBP#_2

H_DSTBP#_3

H_REQ#_0

H_REQ#_1

H_REQ#_2

H_REQ#_3

H_REQ#_4

H_RS#_0

H_RS#_1

H_RS#_2

J13

B11

C11

M11

C15

F16

L13

G17

C14

K16

B13

L16

J17

B14

K19

P15

R17

B16

H20

L19

D17

M17

N16

J19

B18

E19

B17

B15

E17

C18

A19

B19

N19

G12

H17

G20

C8

E8

F12

D6

C10

AM5

AM7

H8

K7

E4

C6

G10

B7

K5

L2

AD13

AE13

M7

K3

AD2

AH11

L7

K2

AC2

AJ10

M14

E13

A11

H13

B12

E12

D7

D8

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

2

H_A#[35:3] 3

H_DINV#0 3

H_DINV#1 3

H_DINV#2 3

H_DINV#3 3

H_DSTBN#0 3

H_DSTBN#1 3

H_DSTBN#2 3

H_DSTBN#3 3

H_DSTBP#0 3

H_DSTBP#1 3

H_DSTBP#2 3

H_DSTBP#3 3

H_ADS# 3

H_ADSTB#0 3

H_ADSTB#1 3

H_BNR# 3

H_BPRI# 3

H_BREQ# 3

H_DEFER# 3

H_DBSY# 3

CLK_MCH_BCLK 37

CLK_MCH_BCLK# 37

H_DPWR# 3

H_DRDY# 3

H_HIT# 3

H_HITM# 3

H_LOCK# 3

H_TRDY# 3

H_RS#[2:0] 3

1

H_REQ#[4:0] 3

A A

5

4

3

Matanzas

Matanzas

Matanzas

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Mobile Intel® 965 Express Chipset Family (1 OF 6)

Mobile Intel® 965 Express Chipset Family (1 OF 6)

Mobile Intel® 965 Express Chipset Family (1 OF 6)

A

A

A

NDA

NDA

NDA

2

658Tuesday, December 05, 2006

658Tuesday, December 05, 2006

658Tuesday, December 05, 2006

1

Intel Confidential

Intel Confidential

Intel Confidential

1.5

1.5

1.5

of

of

of

Page 8

5

U5E1B

U5E1B

P36

MCH_RSVD_1

MCH_RSVD_2

MCH_RSVD_3

MCH_RSVD_4

MCH_RSVD_5

MCH_RSVD_6

MCH_RSVD_7

MCH_RSVD_8

MCH_RSVD_10

MCH_RSVD_11

MCH_RSVD_12

MCH_RSVD_13

D D

MCH_RSVD_14

MCH_RSVD_20

MCH_RSVD_21

MCH_RSVD_24

MCH_RSVD_25

MCH_RSVD_41

MCH_RSVD_42

MCH_RSVD_43

MCH_RSVD_44

MCH_RSVD_45

C C

MCH_CFG_[17:3]12

MCH_CFG_18

MCH_CFG_1912

MCH_CFG_2012,19

PM_DPRSTP#_R

B B

PM_BMBUSY#23

H_DPRSTP#3,21,44,52

PM_EXTTS#013,15

PM_EXTTS#114,15

DELAY_VR_PWRGOOD23,52

PM_THRMTRIP#3,21

PM_DPRSLPVR23,44,52

PM_BM_BUSY# is renamed as PMSYNC# in

Mobile Intel® 965 Express

Chipset Family EDS

A A

TP_MCH_RSVD9

TP_MCH_RSVD22

TP_MCH_RSVD23

TP_MCH_RSVD26

TP_MCH_RSVD27

TP_MCH_RSVD28

TP_MCH_RSVD29

TP_MCH_RSVD30

TP_MCH_RSVD31

TP_MCH_RSVD34

TP_MCH_RSVD35

TP_MCH_RSVD36

MCH_BSEL037

MCH_BSEL137

MCH_BSEL237

R5F13 0R5F13 0

TP5U1 NO_STUFFTP5U1 NO_STUFF

R5U22 0R5U22 0

R5U23 0R5U23 0

R5T4 0R5T4 0

MCH_CFG_20_R

PM_BMBUSY#_R

PM_DPRSTP#_R

PM_EXTTS#1_R

RST_IN#_MCH

R5U15 0R5U15 0

TP_MCH_NC1

TP_MCH_NC2

TP_MCH_NC3

TP_MCH_NC4

TP_MCH_NC5

TP_MCH_NC6

TP_MCH_NC7

TP_MCH_NC8

TP_MCH_NC9

TP_MCH_NC10

TP_MCH_NC11

TP_MCH_NC12

TP_MCH_NC13

TP_MCH_NC14

TP_MCH_NC15

TP_MCH_NC16

C5T18

C5T18

0.1uF

0.1uF

10%

10%

.

.

MCH_CFG_3

MCH_CFG_4

MCH_CFG_5

MCH_CFG_6

MCH_CFG_7

MCH_CFG_8

MCH_CFG_9

MCH_CFG_10

MCH_CFG_11

MCH_CFG_12

MCH_CFG_13

MCH_CFG_14

MCH_CFG_15

MCH_CFG_16

MCH_CFG_17

DPRSLPVR_R

+V1.8_GMCH9,10

R4D2

R4D2

20

20

.

.

1%

1%

R4D1

R4D1

20

20

.

.

1%

1%

P37

R35

N35

AR12

AR13

AM12

AN13

J12

AR37

AM36

AL36

AM37

D20

H10

B51

BJ20

BK22

BF19

BH20

BK18

BJ18

BF23

BG23

BC23

BD24

BH39

AW20

BK20

A35

B37

B36

B34

C34

P27

N27

N24

C21

C23

F23

N23

G23

J20

C20

R24

L23

J23

E23

E20

K23

M20

M24

L32

N33

L35

G41

L39

L36

J36

AW49

AV20

N20

G36

BJ51

BK51

BK50

BL50

BL49

BL3

BL2

BK1

BJ1

E1

A5

C51

B50

A50

A49

BK2

CRESTLINE_1p0

CRESTLINE_1p0

SM_RCOMP

SM_RCOMP#

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD20

RSVD21

RSVD22

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

RSVD28

RSVD29

RSVD30

RSVD31

RSVD34

RSVD35

RSVD36

RSVD41

RSVD42

RSVD43

RSVD44

RSVD45

CFG_0

CFG_1

CFG_2

CFG_3

CFG_4

CFG_5

CFG_6

CFG_7

CFG_8

CFG_9

CFG_10

CFG_11

CFG_12

CFG_13

CFG_14

CFG_15

CFG_16

CFG_17

CFG_18

CFG_19

CFG_20

PM_BM_BUSY#

PM_DPRSTP#

PM_EXT_TS#_0

PM_EXT_TS#_1

PWROK

RSTIN#

THERMTRIP#

DPRSLPVR

NC_1

NC_2

NC_3

NC_4

NC_5

NC_6

NC_7

NC_8

NC_9

NC_10

NC_11

NC_12

NC_13

NC_14

NC_15

NC_16

CFGRSVD

CFGRSVD

PM

PM

NC

NC

5

4

AV29

SM_CK_0

BB23

SM_CK_1

BA25

SM_CK_3

AV23

SM_CK_4

AW30

SM_CK#_0

BA23

SM_CK#_1

AW25

SM_CK#_3

AW23

SM_CK#_4

BE29

SM_CKE_0

AY32

SM_CKE_1

BD39

SM_CKE_3

BG37

SM_CKE_4

BG20

SM_CS#_0

BK16

SM_CS#_1

BG16

SM_CS#_2

BE13

SM_CS#_3

BH18

SM_ODT_0

BJ15

SM_ODT_1

BJ14

SM_ODT_2

BE16

SM_ODT_3

BL15

SM_RCOMP

SM_VREF_0

SM_VREF_1

PEG_CLK

PEG_CLK#

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

GFX_VID_0

GFX_VID_1

GFX_VID_2

GFX_VID_3

CL_CLK

CL_DATA

CL_PWROK

CL_RST#

CL_VREF

CLK_REQ#

ICH_SYNC#

TEST_1

TEST_2

BK14

BK31

BL31

AR49

AW4

B42

C42

H48

H47

K44

K45

AN47

AJ38

AN42

AN46

AM47

AJ39

AN41

AN45

AJ46

AJ41

AM40

AM44

AJ47

AJ42

AM39

AM43

E35

A39

C38

B39

E36

AM49

AK50

AT43

AN49

AM50

H35

K36

G39

G40

A37

R32

SM_RCOMP#

SM_RCOMP_VOH

SM_RCOMP_VOL

DDR MUXINGCLK

DDR MUXINGCLK

DPLL_REF_CLK

DPLL_REF_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

DMI

DMI

GFX_VR_EN

GRAPHICS VID

GRAPHICS VID

ME

ME

SDVO_CTRL_CLK

SDVO_CTRL_DATA

MISC

MISC

MCH_TEST_2

4

SM_RCOMP

SM_RCOMP#

SM_RCOMP_VOH

SM_RCOMP_VOL

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

R5T7

R5T7

20K

20K

5%

5%

.

.

3

M_CLK_DDR0 13

M_CLK_DDR1 13

M_CLK_DDR3 14

M_CLK_DDR4 14

M_CLK_DDR#0 13

M_CLK_DDR#1 13

M_CLK_DDR#3 14

M_CLK_DDR#4 14

M_CKE0 13,15

M_CKE1 13,15

M_CKE3 14,15

M_CKE4 14,15

M_CS#0 13,15

M_CS#1 13,15

M_CS#2 14,15

M_CS#3 14,15

M_ODT0 13,15

M_ODT1 13,15

M_ODT2 14,15

M_ODT3 14,15

DREFCLK 37

DREFCLK# 37

DREFSSCLK 37

DREFSSCLK# 37

CLK_PCIE_3GPLL 37

CLK_PCIE_3GPLL# 37

DFGT_VID_0 49

DFGT_VID_1 49

DFGT_VID_2 49

DFGT_VID_3 49

DFGT_VR_EN 49

MCH_CLVREF

SDVO_CTRLCLK 19

SDVO_CTRLDATA 19

CLK_MCH_OE# 37

MCH_ICH_SYNC# 23

R5T130R5T13

0

EPOT_WIPER

Default

For EVMC No_Stuff

+V1.8_GMCH9,10

R5R2

R5R2

1K

1K

1%

1%

NO_STUFF

NO_STUFF

R5R3

R5R3

1K

1K

1%

1%

NO_STUFF

NO_STUFF

DMI_TXN[3:0] 22

DMI_TXP[3:0] 22

DMI_RXN[3:0] 22

DMI_RXP[3:0] 22 PEG_TX[15:0] 19

CL_CLK0 23

CL_DATA0 23

MPWROK 23,47

CL_RST#0 23

MCH_TEST_1

R7N4

No_Stuff

Stuff

Layout Note:

Place 150 Ohm termination resistors

and jumpers close to GMCH

Layout Note:

Place 150 Ohm termination

resistors close to GMCH

+V1.25M_AXD10

C5D7

C5D7

0.1uF

0.1uF

10%

10%

PLT_RST#19,22,25,26,39,40,42,57

R7N4 0

R7N4 0

NO_STUFF

NO_STUFF

R7N2

Stuff

L_BKLT_CTRL17

L_BKLT_EN17

L_CTRL_CLK17,20

L_CTRL_DATA17,20

LVDS_DDC_CLK17

LVDS_DDC_DATA17

LVDS_VDD_EN17

M_VREF_MCH 47,50

TVA_DAC18

TVB_DAC18

TVC_DAC18

R5U7 150R5U7 150

R5U5 150R5U5 150

R5U6 150R5U6 150

CRT_HSYNC16

CRT_VSYNC16

R5D6

R5D6

1K

1K

1%

1%

R5D7 0

R5D7 0

NO_STUFF

NO_STUFF

R5D8

R5D8

392

392

1%

1%

R5R4

R5R4

LVDS_IBG

R7N2

R7N2

2.37K

2.37K

1%

1%

.

.

3

TP6E1

TP6E1

NO_STUFF

NO_STUFF

R5U12 150 1%R5U12 150 1%

R5U4 150 1%R5U4 150 1%

R5U13 150 1%R5U13 150 1%

CRT_BLUE16

CRT_GREEN16

CRT_RED16

CRT_DDC_CLK_MCH16

CRT_DDC_DATA_MCH16

R5U16

R5U16

EV_VCC_V1.25_AXD

RST_IN#_MCH

100

100

R5U27 0R5U27 0

LVDSA_CLK#17

LVDSA_CLK17

LVDSB_CLK#17

LVDSB_CLK17

LVDSA_DATA#017

LVDSA_DATA#117

LVDSA_DATA#217

LVDSA_DATA#317

LVDSA_DATA017

LVDSA_DATA117

LVDSA_DATA217

LVDSA_DATA317

LVDSB_DATA#017

LVDSB_DATA#117

LVDSB_DATA#217

LVDSB_DATA#317

LVDSB_DATA017

LVDSB_DATA117

LVDSB_DATA217

LVDSB_DATA317

R5U11 0R5U11 0

R5U3 0R5U3 0

R5U14 0R5U14 0

TV_DCONSEL0_MCH18

TV_DCONSEL1_MCH18

R5U17 30.1

R5U17 30.1

R5U18 30.1

R5U18 30.1

L_VDD_EN_R

LVDS_IBG

LVDS_VBG

MCH_TVA_DAC

MCH_TVB_DAC

MCH_TVC_DAC

HSYNC

.

.

CRTIREF

1.3k_5%

1.3k_5%

VSYNC

.

.

+V1.8_GMCH9,10

R5R1

R5R1

1K

1K

0.10%

0.10%

R5D5

R5D5

3.01k

3.01k

R5D3

R5D3

1K

1K

0.10%

0.10%

Matanzas

Matanzas

Matanzas

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A

A

A

Date: Sheet

Date: Sheet

Date: Sheet

2

U5E1C

U5E1C

J40

L_BKLT_CTRL

H39

L_BKLT_EN

E39

L_CTRL_CLK

E40

L_CTRL_DATA

C37

L_DDC_CLK

D35

L_DDC_DATA

K40

L_VDD_EN

L41

LVDS_IBG

L43

LVDS_VBG

N41

LVDS_VREFH

N40

LVDS_VREFL

D46

LVDSA_CLK#

C45

LVDSA_CLK

D44

LVDSB_CLK#

E42

LVDSB_CLK

G51

LVDSA_DATA#_0

E51

LVDSA_DATA#_1

F49

LVDSA_DATA#_2

C48

LVDSA_DATA#_3

G50

LVDSA_DATA_0

E50

LVDSA_DATA_1

F48

LVDSA_DATA_2

D47

LVDSA_DATA_3

G44

LVDSB_DATA#_0

B47

LVDSB_DATA#_1

B45

LVDSB_DATA#_2

B44

LVDSB_DATA#_3

E44

LVDSB_DATA_0

A47

LVDSB_DATA_1

A45

LVDSB_DATA_2

C44

LVDSB_DATA_3

E27

TVA_DAC

G27

TVB_DAC

K27

TVC_DAC

F27

TVA_RTN

J27

TVB_RTN

L27

TVC_RTN

M35

TV_DCONSEL_0

P33

TV_DCONSEL_1

H32

CRT_BLUE

G32

CRT_BLUE#

K29

CRT_GREEN

J29

CRT_GREEN#

F29

CRT_RED

E29

CRT_RED#

K33

CRT_DDC_CLK

G35

CRT_DDC_DATA

F33

CRT_HSYNC

C32

CRT_TVO_IREF

E33

CRT_VSYNC

CRESTLINE_1p0

CRESTLINE_1p0

SM_RCOMP_VOH

C5R5

C5R5

C5R6

C5R6

2.2uF

2.2uF

0.01uF

0.01uF

10%

10%

10%

10%

402

402

SM_RCOMP_VOL

C5D4

C5D4

C5D3

C5D3

0.01uF

0.01uF

2.2uF

2.2uF

10%

10%

10%

10%

402

402

Mobile Intel® 965 Express Chipset Family (2 OF 6)

Mobile Intel® 965 Express Chipset Family (2 OF 6)

Mobile Intel® 965 Express Chipset Family (2 OF 6)

NDA

NDA

NDA

LVDS

LVDS

TV VGA

TV VGA

PEG_COMPO

PEG_RX#_10

PEG_RX#_11

PEG_RX#_12

PEG_RX#_13

PEG_RX#_14

PEG_RX#_15

PEG_TX#_10

PEG_TX#_11

PCI-EXPRESS GRAPHICS

PCI-EXPRESS GRAPHICS

PEG_TX#_12

PEG_TX#_13

PEG_TX#_14

PEG_TX#_15

PEG_COMPI

PEG_RX#_0

PEG_RX#_1

PEG_RX#_2

PEG_RX#_3

PEG_RX#_4

PEG_RX#_5

PEG_RX#_6

PEG_RX#_7

PEG_RX#_8

PEG_RX#_9

PEG_RX_0

PEG_RX_1

PEG_RX_2

PEG_RX_3

PEG_RX_4

PEG_RX_5

PEG_RX_6

PEG_RX_7

PEG_RX_8

PEG_RX_9

PEG_RX_10

PEG_RX_11

PEG_RX_12

PEG_RX_13

PEG_RX_14

PEG_RX_15

PEG_TX#_0

PEG_TX#_1

PEG_TX#_2

PEG_TX#_3

PEG_TX#_4

PEG_TX#_5

PEG_TX#_6

PEG_TX#_7

PEG_TX#_8

PEG_TX#_9

PEG_TX_0

PEG_TX_1

PEG_TX_2

PEG_TX_3

PEG_TX_4

PEG_TX_5

PEG_TX_6

PEG_TX_7

PEG_TX_8

PEG_TX_9

PEG_TX_10

PEG_TX_11

PEG_TX_12

PEG_TX_13

PEG_TX_14

PEG_TX_15

+V3.3S5,10,12,16..26,28,30..32,34,37..42,44,45,49,50,52,55..57

N43

M43

J51

L51

N47

T45

T50

U40

Y44

Y40

AB51

W49

AD44

AD40

AG46

AH49

AG45

AG41

J50

L50

M47

U44

T49

T41

W45

W41

AB50

Y48

AC45

AC41

AH47

AG49

AH45

AG42

N45

U39

U47

N51

R50

T42

Y43

W46

W38

AD39

AC46

AC49

AC42

AH39

AE49

AH44

M45

T38

T46

N50

R51

U43

W42

Y47

Y39

AC38

AD47

AC50

AD43

AG39

AE50

AH43

2

PEG_COMP

PEG_RX#0

PEG_RX#1

PEG_RX#2

PEG_RX#3

PEG_RX#4

PEG_RX#5

PEG_RX#6

PEG_RX#7

PEG_RX#8

PEG_RX#9

PEG_RX#10

PEG_RX#11

PEG_RX#12

PEG_RX#13

PEG_RX#14

PEG_RX#15

PEG_RX0

PEG_RX1

PEG_RX2

PEG_RX3

PEG_RX4

PEG_RX5

PEG_RX6

PEG_RX7

PEG_RX8

PEG_RX9

PEG_RX10

PEG_RX11

PEG_RX12

PEG_RX13

PEG_RX14

PEG_RX15

PEG_TX#0

PEG_TX#1

PEG_TX#2

PEG_TX#3

PEG_TX#4

PEG_TX#5

PEG_TX#6

PEG_TX#7

PEG_TX#8

PEG_TX#9

PEG_TX#10

PEG_TX#11

PEG_TX#12

PEG_TX#13

PEG_TX#14

PEG_TX#15

PEG_TX0

PEG_TX1

PEG_TX2

PEG_TX3

PEG_TX4

PEG_TX5

PEG_TX6

PEG_TX7

PEG_TX8

PEG_TX9

PEG_TX10

PEG_TX11

PEG_TX12

PEG_TX13

PEG_TX14

PEG_TX15

R5F6 10KR5F6 10K

R5P1 10KR5P1 10K

R5P4 10KR5P4 10K

758Tuesday, December 05, 2006

758Tuesday, December 05, 2006

758Tuesday, December 05, 2006

1

1

+VCC_PEG10

R5T2 24.9

R5T2 24.9

1%

1%

PEG_RX#[15:0] 19

PEG_RX[15:0] 19

PEG_TX#[15:0] 19

CLK_MCH_OE#

PM_EXTTS#0

PM_EXTTS#1

Intel Confidential

Intel Confidential

Intel Confidential

1.5

1.5

1.5

of

of

of

Page 9

5

4

3

2

1

M_A_DQ[63:0]13

D D

C C

B B

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

AR43

AW44

BA45

AY46

AR41

AR45

AT42

AW47

BB45

BF48

BG47

BJ45

BB47

BG50

BH49

BE45

AW43

BE44

BG42

BE40

BF44

BH45

BG40

BF40

AR40

AW40

AT39

AW36

AW41

AY41

AV38

AT38

AV13

AT13

AW11

AV11

AU15

AT11

BA13

BA11

BE10

BD10

BG10

AW9

AN10

AN11

BD8

AY9

BD7

BB9

BB5

AY7

AT5

AT7

AY6

BB7

AR5

AR8

AR9

AN3

AM8

AT9

AN9

AM9

U5E1D

U5E1D

SA_DQ_0

SA_DQ_1

SA_DQ_2

SA_DQ_3

SA_DQ_4

SA_DQ_5

SA_DQ_6

SA_DQ_7

SA_DQ_8

SA_DQ_9

SA_DQ_10

SA_DQ_11

SA_DQ_12

SA_DQ_13

SA_DQ_14

SA_DQ_15

SA_DQ_16

SA_DQ_17

SA_DQ_18

SA_DQ_19

SA_DQ_20

SA_DQ_21

SA_DQ_22

SA_DQ_23

SA_DQ_24

SA_DQ_25

SA_DQ_26

SA_DQ_27

SA_DQ_28

SA_DQ_29

SA_DQ_30

SA_DQ_31

SA_DQ_32

SA_DQ_33

SA_DQ_34

SA_DQ_35

SA_DQ_36

SA_DQ_37

SA_DQ_38

SA_DQ_39

SA_DQ_40

SA_DQ_41

SA_DQ_42

SA_DQ_43

SA_DQ_44

SA_DQ_45

SA_DQ_46

SA_DQ_47

SA_DQ_48

SA_DQ_49

SA_DQ_50

SA_DQ_51

SA_DQ_52

SA_DQ_53

SA_DQ_54

SA_DQ_55

SA_DQ_56

SA_DQ_57

SA_DQ_58

SA_DQ_59

SA_DQ_60

SA_DQ_61

SA_DQ_62

SA_DQ_63

CRESTLINE_1p0

CRESTLINE_1p0

BB19

SA_BS_0

BK19

SA_BS_1

BF29

SA_BS_2

BL17

SA_CAS#

SA_DM_0

SA_DM_1

SA_DM_2

SA_DM_3

SA_DM_4

SA_DM_5

SA_DM_6

SA_DM_7

SA_DQS_0

SA_DQS_1

SA_DQS_2

SA_DQS_3

SA_DQS_4

SA_DQS_5

SA_DQS_6

SA_DQS_7

SA_DQS#_0

SA_DQS#_1

SA_DQS#_2

SA_DQS#_3

SA_DQS#_4

SA_DQS#_5

SA_DQS#_6

SA_DQS#_7

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_MA_14

SA_RAS#

SA_RCVEN#

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

SA_WE#

AT45

BD44

BD42

AW38

AW13

BG8

AY5

AN6

AT46

BE48

BB43

BC37

BB16

BH6

BB2

AP3

AT47

BD47

BC41

BA37

BA16

BH7

BC1

AP2

BJ19

BD20

BK27

BH28

BL24

BK28

BJ27

BJ25

BL28

BA28

BC19

BE28

BG30

BJ16

BJ29

BE18

AY20

BA19

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

TP_SA_RCVEN#

M_A_BS1 13,15

M_A_BS2 13,15

M_A_CAS# 13,15

M_A_DM[7:0] 13

M_A_DQS[7:0] 13

M_A_DQS#[7:0] 13

M_A_A[13:0] 13,15

M_A_A14 14 M_B_A14 15

M_A_RAS# 13,15

M_A_WE# 13,15

M_B_DQ[63:0]14

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

AP49

AR51

AW50

AW51

AN51

AN50

AV50

AV49

BA50

BB50

BA49

BE50

BA51

AY49

BF50

BF49

BJ50

BJ44

BJ43

BL43

BK47

BK49

BK43

BK42

BJ41

BL41

BJ37

BJ36

BK41

BJ40

BL35

BK37

BK13

BE11

BK11

BC11

BC13

BE12

BC12

BG12

BJ10

BK10

BK5

BK9

BF4

BH5

BG1

BC2

BK3

BE4

BD3

BA3

BB3

AR1

AT3

AY2

AY3

AU2

AT2

BL9

BL5

BJ8

BJ6

BJ2

U5E1E

U5E1E

SB_DQ_0

SB_DQ_1

SB_DQ_2

SB_DQ_3

SB_DQ_4

SB_DQ_5

SB_DQ_6

SB_DQ_7

SB_DQ_8

SB_DQ_9

SB_DQ_10

SB_DQ_11

SB_DQ_12

SB_DQ_13

SB_DQ_14

SB_DQ_15

SB_DQ_16

SB_DQ_17

SB_DQ_18

SB_DQ_19

SB_DQ_20

SB_DQ_21

SB_DQ_22

SB_DQ_23

SB_DQ_24

SB_DQ_25

SB_DQ_26

SB_DQ_27

SB_DQ_28

SB_DQ_29

SB_DQ_30

SB_DQ_31

SB_DQ_32

SB_DQ_33

SB_DQ_34

SB_DQ_35

SB_DQ_36

SB_DQ_37

SB_DQ_38

SB_DQ_39

SB_DQ_40

SB_DQ_41

SB_DQ_42

SB_DQ_43

SB_DQ_44

SB_DQ_45

SB_DQ_46

SB_DQ_47

SB_DQ_48

SB_DQ_49

SB_DQ_50

SB_DQ_51

SB_DQ_52

SB_DQ_53

SB_DQ_54

SB_DQ_55

SB_DQ_56

SB_DQ_57

SB_DQ_58

SB_DQ_59

SB_DQ_60

SB_DQ_61

SB_DQ_62

SB_DQ_63

CRESTLINE_1p0

CRESTLINE_1p0

AY17

SB_BS_0

BG18

SB_BS_1

BG36

SB_BS_2

BE17

SB_CAS#

SB_DM_0

SB_DM_1

SB_DM_2

SB_DM_3

SB_DM_4

SB_DM_5

SB_DM_6

SB_DM_7

SB_DQS_0

SB_DQS_1

SB_DQS_2

SB_DQS_3

SB_DQS_4

SB_DQS_5

SB_DQS_6

SB_DQS_7

SB_DQS#_0

SB_DQS#_1

SB_DQS#_2

SB_DQS#_3

SB_DQS#_4

SB_DQS#_5

SB_DQS#_6

SB_DQS#_7

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

SB_MA_14

SB_RAS#

SB_RCVEN#

DDR SYSTEM MEMORY B

DDR SYSTEM MEMORY B

SB_WE#

AR50

BD49

BK45

BL39

BH12

BJ7

BF3

AW2

AT50

BD50

BK46

BK39

BJ12

BL7

BE2

AV2

AU50

BC50

BL45

BK38

BK12

BK7

BF2

AV3

BC18

BG28

BG25

AW17

BF25

BE25

BA29

BC28

AY28

BD37

BG17

BE37

BA39

BG13

BE24

AV16

AY18

BC17

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

TP_SB_RCVEN#

M_B_BS0 14,15M_A_BS0 13,15

M_B_BS1 14,15

M_B_BS2 14,15

M_B_CAS# 14,15

M_B_DM[7:0] 14

M_B_DQS[7:0] 14

M_B_DQS#[7:0] 14

M_B_A[13:0] 14,15

M_B_RAS# 14,15

M_B_WE# 14,15

A A

5

4

3

Matanzas

Matanzas

Matanzas

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Mobile Intel® 965 Express Chipset Family (3 OF 6)

Mobile Intel® 965 Express Chipset Family (3 OF 6)

Mobile Intel® 965 Express Chipset Family (3 OF 6)

A

A

A

NDA

NDA

NDA

2

858Tuesday, December 05, 2006

858Tuesday, December 05, 2006

858Tuesday, December 05, 2006

1

Intel Confidential

Intel Confidential

Intel Confidential

1.5

1.5

1.5

of

of

of

Page 10

5

4

3

2

1

+V3.3S_SYNC10 +VCC_GMCH

R5U21 10

R5U21 10

1 2

T17

T18

T19

T21

T22

T23

T25

U15

U16

U17

U19

U20

U21

U23

U26

V16

V17

V19

V20

V21

V23

V24

Y15

Y16

Y17

Y19

Y20

Y21

Y23

Y24

Y26

Y28

Y29

AA16

AA17

AB16

AB19

AC16

AC17

AC19

AD15

AD16

AD17

AF16

AF19

AH15

AH16

AH17

AH19

AJ16

AJ17

AJ19

AK16

AK19

AL16

AL17

AL19

AL20

AL21

AL23

AM15

AM16

AM19

AM20

AM21

AM23

AP15

AP16

AP17

AP19

AP20

AP21

AP23

AP24

AR20

AR21

AR23

AR24

AR26

V26

V28

V29

Y31

AW45

BC39

BE39

BD17

BD4

AW8

AT6

+VGFX_CORE49

VCCSM_LF1

VCCSM_LF2

VCCSM_LF3

VCCSM_LF4

VCCSM_LF5

VCCSM_LF6

VCCSM_LF7

4

C4R7

C4R7

0.1uF

0.1uF

10%

10%

.

.

R3F8 0.002

R3F8 0.002

C4R8

C4R8

0.1uF

0.1uF

10%

10%

.

.

R6E1 0.002

R6E1 0.002

1%

1%

Place C5C7 where LVDS

and DDR2 taps.

C4R6

C4R6

C4R5

C4R5

0.22uF

0.22uF

0.22uF

0.22uF

1%

1%

12

C4T2

C4T2

+

+

330uF

330uF

3

20%

20%

370mils from the Edge Cavity Capacitors

C5R12

C5R12

0.47uF

0.47uF

C5E3

C5E3

270uF

270uF

20%

20%

308 mils from

the Edge

+VGFX_CORE49+VCC_GFXCORE49

12

C4T1