Page 1

查询DJIXEEAD0QE000供应商

Intel® LXT9785 and Intel® LXT9785E

Advanced 8-Port 10/100 Mbps PHY

Transceivers

The Intel® LXT9785 and Intel® LXT9785E are 8-port Fast Ethernet PHY Transceivers

supporting IEEE 802.3 physical layer applications at 10 Mbps and 100 Mbps. These devices

provide Serial/Source Synchronous Serial Media Independent Interfaces (SMII/SS-SMII) and

Reduced Media Independent Interface (RMII) for switching and other independent port

applications. The LXT9785 and LXT9785E are identical except for the IP telephony features

included in the LXT9785E transceiver. The LXT9785E is an enhanced version of the LXT9785

that detects Data Terminal Equipment (DTE) requiring power from the switch over a CAT5

cable. The system uses the information collected by the LXT97985E to apply power if the DTE

at the far end requires power over the cable, such as an IP telephone.

Datasheet

Each network port can provide a twisted-pair (TP) or Low-Voltage Positive Emitter Coupled

Logic (LVPECL) interface. The twisted-pair interface supports 10 Mbps and 100 Mbps

(10BASE-T and 100BASE-TX) Ethernet over twisted-pair. The LVPECL interface supports

100 Mbps (100BASE-FX) Ethernet over fiber-optic media.

The LXT9785/LXT9785E provides three discrete LED driver outputs for each port. The devices

support both half-duplex and full-duplex operation at 10 Mbps and 100 Mbps and require only a

single 2.5 V power supply.

Applications

Enterprise switches

IP telephony switches

Storage Area Networks

Multi-port Network Interface Cards (NICs)

Product Features

Eight IEEE 802.3-compliant 10BASE-T or

100BASE-TX ports with integrated filters.

100BASE-FX fiber-optic capability on all

ports.

2.5 V operation.

Low power consumption; 250 mW per port

typical.

Multiple RMII or SMII/SS-SMII ports for

independent PHY port operation.

Auto MDI/MDIX crossover capability.

Proprietary Optimal Signal Processing™

architecture improves SNR by 3 dB over

ideal analog filters.

Optimized for dual-high stacked RJ-45

applications.

MDIO sectionalization into 2x4 or 1x8

configurations.

Supports both auto-negotiation systems and

legacy systems without auto-negotiation

capability.

Robust baseline wander correction.

Configurable through the MDIO port or

external control pins.

JTAG boundary scan.

208-pin PQFP: LXT9785HC,

LXT9785EHC, LXT9785HE.

241-ball BGA: LXT9785BC,

LXT9785EBC.

196-ball BGA: LXT9785MBC

DTE detection for remote powering

applications (LXT9785E only).

Extended temperature operation of -40

o

+85

C (LXT9785HE).

o

C to

Document Number: 249241

Revision Number: 007

Revision Date: August 28, 2003

Page 2

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY

ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN

INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS

ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES

RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER

INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined.” Intel reserves these for

future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

®

The Intel

published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling

1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

AnyPoint, AppChoice, BoardWatch, BunnyPeople, CablePort, Celeron, Chips, CT Media, Dialogic, DM3, EtherExpress, ETOX, FlashFile, i386, i486,

i960, iCOMP, InstantIP, Intel, Intel Centrino, Intel logo, Intel386, Intel486, Intel740, IntelDX2, IntelDX4, IntelSX2, Intel Create & Share, Intel GigaBlade,

Intel InBusiness, Intel Inside, Intel Inside logo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel Play, Intel Play logo, Intel SingleDriver, Intel

SpeedStep, Intel StrataFlash, Intel TeamStation, Intel Xeon, Intel XScale, IPLink, Itanium, MCS, MMX, MMX logo, Optimizer logo, OverDrive,

Paragon, PC Dads, PC Parents, PDCharm, Pentium, Pentium II Xeon, Pentium III Xeon, Performance at Your Command, RemoteExpress, SmartDie,

Solutions960, Sound Mark, StorageExpress, The Computer Inside., The Journey Inside, TokenExpress, VoiceBrick, VTune, and Xircom are

trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

*Other names and brands may be claimed as the property of others.

Copyright © 2003, Intel Corporation

LXT9785 and Intel® LXT9785E may contain design defects or errors known as errata which may cause the product to deviate from

2 Datasheet

Document Number: 249241

Revision Number: 007

Revision Date: August 28, 2003

Page 3

Contents

Contents

1.0 Introduction.................................................................................................................................. 18

1.1 What You Will Find in This Document ................................................................................ 18

1.2 Related Documents ............................................................................................................18

2.0 Block Diagram ............................................................................................................................. 19

3.0 Pin/Ball Assignments and Signal Descriptions........................................................................ 20

3.1 PQFP Pin Assignments ...................................................................................................... 20

3.1.1 PQFP Pin Assignments – RMII Configuration ....................................................... 21

3.1.2 PQFP Pin Assignments – SMII Configuration........................................................ 26

3.1.3 PQFP Pin Assignments – SS-SMII Configuration.................................................. 31

3.2 PQFP Signal Descriptions .................................................................................................. 36

3.2.1 Signal Name Conventions ..................................................................................... 36

3.2.2 PQFP Signal Descriptions – RMII, SMII, and SS-SMII Configurations.................. 36

3.3 BGA23 Ball Assignments.................................................................................................... 51

3.3.1 RMII BGA23 Ball List ............................................................................................. 52

3.3.2 SMII BGA23 Ball List ............................................................................................. 62

3.3.3 SS-SMII BGA23 Ball List ....................................................................................... 72

3.4 BGA23 Signal Descriptions ................................................................................................ 82

3.4.1 Signal Name Conventions ..................................................................................... 82

3.4.2 Signal Descriptions – RMII, SMII, and SS-SMII Configurations............................. 82

3.5 BGA15 Ball Assignments.................................................................................................... 98

3.5.1 BGA15 Ball List...................................................................................................... 99

3.6 BGA15 Signal Descriptions .............................................................................................. 109

3.6.1 Signal Name Conventions ................................................................................... 109

3.6.2 Signal Descriptions – SMII and SS-SMII Configurations ..................................... 109

4.0 Functional Description..............................................................................................................116

4.1 Introduction ....................................................................................................................... 116

4.1.1 OSP™ Architecture .............................................................................................116

4.1.2 Comprehensive Functionality .............................................................................. 117

4.1.2.1 Sectionalization.................................................................................... 117

4.2 Interface Descriptions .......................................................................................................117

4.2.1 10/100 Network Interface..................................................................................... 117

4.2.1.1 Twisted-Pair Interface .......................................................................... 118

4.2.1.2 MDI Crossover (MDIX)......................................................................... 119

4.2.1.3 Fiber Interface......................................................................................119

4.3 Media Independent Interface (MII) Interfaces................................................................... 119

4.3.1 Global MII Mode Select .......................................................................................119

4.3.2 Internal Loopback ................................................................................................ 120

4.3.3 RMII Data Interface..............................................................................................120

4.3.4 Serial Media Independent Interface (SMII) and Source Synchronous-

Serial Media Independent Interface (SS-SMII) .................................................... 121

4.3.4.1 SMII Interface....................................................................................... 121

4.3.4.2 Source Synchronous-Serial Media Independent Interface ..................121

4.3.5 Configuration Management Interface .................................................................. 121

4.3.6 MII Isolate ............................................................................................................ 121

Datasheet 3

Document Number: 249241

Revision Number: 007

Revision Date: August 28, 2003

Page 4

Contents

4.3.7 MDIO Management Interface .............................................................................. 121

4.3.8 MII Sectionalization.............................................................................................. 123

4.3.9 MII Interrupts........................................................................................................ 123

4.3.10 Global Hardware Control Interface ...................................................................... 124

4.3.11 FIFO Initial Fill Values.......................................................................................... 124

4.4 Operating Requirements................................................................................................... 125

4.4.1 Power Requirements ........................................................................................... 125

4.4.2 Clock/SYNC Requirements ................................................................................. 125

4.4.2.1 Reference Clock .................................................................................. 125

4.4.2.2 TxCLK Signal (SS-SMII only)............................................................... 125

4.4.2.3 TxSYNC Signal (SMII/SS-SMII)........................................................... 125

4.4.2.4 RxSYNC Signal (SS-SMII only) ........................................................... 125

4.4.2.5 RxCLK Signal (SS-SMII only) .............................................................. 126

4.5 Initialization ....................................................................................................................... 126

4.5.1 MDIO Control Mode............................................................................................. 126

4.5.2 Hardware Control Mode....................................................................................... 126

4.5.3 Power-Down Mode .............................................................................................. 127

4.5.3.1 Global (Hardware) Power Down .......................................................... 128

4.5.3.2 Port (Software) Power Down ............................................................... 128

4.5.4 Reset ................................................................................................................... 128

4.5.5 Hardware Configuration Settings......................................................................... 129

4.6 Link Establishment............................................................................................................ 129

4.6.1 Auto-Negotiation.................................................................................................. 129

4.6.1.1 Base Page Exchange .......................................................................... 129

4.6.1.2 Manual Next Page Exchange .............................................................. 130

4.6.1.3 Controlling Auto-Negotiation................................................................ 130

4.6.1.4 Link Criteria.......................................................................................... 130

4.6.1.5 Parallel Detection................................................................................. 131

4.6.1.6 Reliable Link Establishment While Auto MDI/MDIX is

Enabled in Forced Speed Mode .......................................................... 131

4.7 Serial MII Operation.......................................................................................................... 132

4.7.1 SMII Reference Clock .......................................................................................... 135

4.7.2 TxSYNC Pulse (SMII/SS-SMII)............................................................................ 135

4.7.3 Transmit Data Stream.......................................................................................... 135

4.7.3.1 Transmit Enable................................................................................... 135

4.7.3.2 Transmit Error ...................................................................................... 135

4.7.4 Receive Data Stream........................................................................................... 136

4.7.4.1 Carrier Sense....................................................................................... 136

4.7.4.2 Receive Data Valid .............................................................................. 136

4.7.4.3 Receive Error ....................................................................................... 136

4.7.4.4 Receive Status Encoding..................................................................... 136

4.7.5 Collision ............................................................................................................... 136

4.7.6 Source Synchronous-Serial Media Independent Interface .................................. 137

4.8 RMII Operation ................................................................................................................. 141

4.8.1 RMII Reference Clock.......................................................................................... 141

4.8.2 Transmit Enable................................................................................................... 142

4.8.3 Carrier Sense & Data Valid.................................................................................. 142

4.8.4 Receive Error ....................................................................................................... 142

4.8.5 Out-of-Band Signaling ......................................................................................... 142

4.8.6 4B/5B Coding Operations .................................................................................... 142

4.9 100 Mbps Operation ......................................................................................................... 145

4 Datasheet

Document Number: 249241

Revision Number: 007

Revision Date: August 28, 2003

Page 5

Contents

4.9.1 100BASE-X Network Operations ......................................................................... 145

4.9.2 100BASE-X Protocol Sublayer Operations.......................................................... 145

4.9.2.1 PCS Sublayer ...................................................................................... 145

4.9.3 PMA Sublayer ......................................................................................................147

4.9.3.1 Link ......................................................................................................148

4.9.3.2 Link Failure Override............................................................................ 148

4.9.3.3 Carrier Sense/Data Valid (RMII) .......................................................... 148

4.9.3.4 Carrier Sense (SMII) ............................................................................148

4.9.3.5 Receive Data Valid (SMII).................................................................... 148

4.9.3.6 Twisted-Pair PMD Sublayer ................................................................. 149

4.9.3.7 Fiber PMD Sublayer............................................................................. 149

4.10 10 Mbps Operation ...........................................................................................................150

4.10.1 Preamble Handling .............................................................................................. 150

4.10.2 Dribble Bits .......................................................................................................... 151

4.10.3 Link Test ..............................................................................................................151

4.10.3.1 Link Failure .......................................................................................... 151

4.10.4 Jabber.................................................................................................................. 151

4.11 DTE Discovery Process.................................................................................................... 152

4.11.1 Definitions ............................................................................................................ 152

4.11.2 Interaction between Processor, MAC, and PHY .................................................. 153

4.11.3 Management Interface and Control .....................................................................153

4.11.4 DTE Discovery Process Flow .............................................................................. 154

4.11.5 DTE Discovery Behavior...................................................................................... 155

4.12 Monitoring Operations ......................................................................................................157

4.12.1 Monitoring Auto-Negotiation ................................................................................ 157

4.12.2 Per-Port LED Driver Functions ............................................................................ 157

4.12.3 Out-of-Band Signaling ......................................................................................... 158

4.12.4 Boundary Scan Interface ..................................................................................... 159

4.12.5 State Machine...................................................................................................... 159

4.12.6 Instruction Register .............................................................................................. 159

4.12.7 Boundary Scan Register......................................................................................159

4.13 Cable Diagnostics Overview ............................................................................................. 160

4.13.1 Features............................................................................................................... 160

4.13.2 Operation ............................................................................................................. 160

4.13.2.1 Short and Long Cable Testing Requirements...................................... 160

4.13.2.2 Precision ..............................................................................................160

4.13.3 Implementation Considerations ........................................................................... 161

4.13.4 Basic Implementation .......................................................................................... 161

4.14 Link Hold-Off Overview.....................................................................................................162

4.14.1 Features............................................................................................................... 162

4.14.2 Operation ............................................................................................................. 163

5.0 Application Information ............................................................................................................ 164

5.1 Design Recommendations................................................................................................ 164

5.2 General Design Guidelines...............................................................................................164

5.2.1 Power Supply Filtering ......................................................................................... 164

5.2.2 Power and Ground Plane Layout Considerations................................................165

5.2.2.1 Chassis Ground ................................................................................... 165

5.2.3 MII Terminations .................................................................................................. 165

5.2.4 Twisted-Pair Interface .......................................................................................... 165

5.2.4.1 Magnetic Requirements ....................................................................... 166

Datasheet 5

Document Number: 249241

Revision Number: 007

Revision Date: August 28, 2003

Page 6

Contents

5.2.5 The Fiber Interface .............................................................................................. 166

5.2.6 LED Circuit........................................................................................................... 167

5.3 Typical Application Circuits............................................................................................... 168

6.0 Test Specifications.................................................................................................................... 173

7.0 Register Definitions................................................................................................................... 199

8.0 Package Specifications............................................................................................................. 221

9.0 Ordering Information................................................................................................................. 227

Figures

1 Intel® LXT9785/LXT9785E Block Diagram ................................................................................. 19

2 Intel

3 Intel

4 Intel

5 Intel® LXT9785/LXT9785E 241-Ball BGA23 Assignments (Top View) ...................................... 51

6 Intel

7 Intel

8 Intel

9 Intel

10 Intel

11 Intel

12 Intel

13 Intel

14 Intel

15 Intel

16 Intel

17 Intel

18 Intel

19 Intel

20 Intel

21 Intel

22 Intel

23 Intel

24 Intel

25 Intel

26 Intel

27 Intel

28 Intel

29 Typical IP Telephone System Connection................................................................................ 152

30 Intel

31 Intel

32 Intel

33 LED Circuit ............................................................................................................................... 167

34 Intel

35 Intel

36 Recommended Intel

37 Recommended Intel

38 ON Semiconductor Triple PECL-to-LVPECL Translator .......................................................... 172

®

LXT9785 and Intel® LXT9785E RMII 208-Pin PQFP Assignments .................................. 21

®

LXT9785/LXT9785E SMII 208-Pin PQFP Assignments ................................................... 26

®

LXT9785/LXT9785E SS-SMII 208-Pin PQFP Assignments ............................................. 31

®

LXT9785MBC 196-Ball BGA15 Assignments (Top View) ................................................ 98

®

LXT9785/LXT9785E Interfaces ...................................................................................... 118

®

LXT9785/LXT9785E Internal Loopback.......................................................................... 120

®

LXT9785/LXT9785E Management Interface Read Frame Structure.............................. 122

®

LXT9785/LXT9785E Management Interface Write Frame Structure .............................. 122

®

LXT9785/LXT9785E Port Address Scheme ................................................................... 123

®

LXT9785/LXT9785E Interrupt Logic ............................................................................... 124

®

LXT9785/LXT9785E Initialization Sequence .................................................................. 127

®

LXT9785/LXT9785E Auto-Negotiation Operation........................................................... 131

®

LXT9785/LXT9785E Typical SMII Interface Diagram ..................................................... 133

®

LXT9785/LXT9785E Typical SMII Quad Sectionalization Diagram ................................ 134

®

LXT9785/LXT9785E 100 Mbps Serial MII Data Flow ..................................................... 135

®

LXT9785/LXT9785E Serial MII Transmit Synchronization ............................................. 136

®

LXT9785/LXT9785E Serial MII Receive Synchronization .............................................. 137

®

LXT9785/LXT9785E Typical SS-SMII Interface Diagram ............................................... 139

®

LXT9785/LXT9785E Typical SS-SMII Quad Sectionalization Diagram .......................... 140

®

LXT9785/LXT9785E SS-SMII Transmit Timing .............................................................. 141

®

LXT9785/LXT9785E SS-SMII Receive Timing ............................................................... 141

®

LXT9785/LXT9785E RMII Data Flow ............................................................................. 142

®

LXT9785/LXT9785E Typical RMII Interface Diagram..................................................... 143

®

LXT9785/LXT9785E Typical RMII Quad Sectionalization Diagram................................ 144

®

LXT9785/LXT9785E 100BASE-X Frame Format ...........................................................145

®

LXT9785/LXT9785E Protocol Sublayers ........................................................................ 146

®

LXT9785E Negotiation Flow Chart ................................................................................. 156

®

LXT9785/LXT9785E LED Pulse Stretching .................................................................... 158

®

LXT9785/LXT9785E RMII Programmable Out-of-Band Signaling.................................. 158

®

LXT9785/LXT9785E Power and Ground Supply Connections ....................................... 168

®

LXT9785/LXT9785E Typical Twisted-Pair Interface ....................................................... 169

®

LXT9785/LXT9785E-to-3.3 V Fiber Transceiver Interface Circuitry...... 170

®

LXT9785/LXT9785E-to-5 V Fiber Transceiver Interface Circuitry......... 171

6 Datasheet

Document Number: 249241

Revision Number: 007

Revision Date: August 28, 2003

Page 7

Contents

39 Intel® LXT9785/LXT9785E SMII - 100BASE-TX Receive Timing.............................................178

40 Intel

41 Intel

42 Intel

43 Intel

44 Intel

45 Intel

46 Intel

47 Intel

48 Intel

49 Intel

50 Intel

51 Intel

52 Intel

53 Intel

54 Intel

55 Intel

56 Intel

57 Intel

58 Intel

59 Intel

60 Intel

61 Intel

62 Intel

®

LXT9785/LXT9785E SMII - 100BASE-TX Transmit Timing............................................ 179

®

LXT9785/LXT9785E SMII - 100BASE-FX Receive Timing.............................................180

®

LXT9785/LXT9785E SMII - 100BASE-FX Transmit Timing............................................ 181

®

LXT9785/LXT9785E SMII - 10BASE-T Receive Timing ................................................. 182

®

LXT9785/LXT9785E SMII - 10BASE-T Transmit Timing ................................................ 183

®

LXT9785/LXT9785E SS-SMII - 100BASE-TX Receive Timing....................................... 184

®

LXT9785/LXT9785E SS-SMII - 100BASE-TX Transmit Timing...................................... 185

®

LXT9785/LXT9785E SS-SMII - 100BASE-FX Receive Timing....................................... 186

®

LXT9785/LXT9785E SS-SMII - 100BASE-FX Transmit Timing...................................... 187

®

LXT9785/LXT9785E SS-SMII - 10BASE-T Receive Timing ........................................... 188

®

LXT9785/LXT9785E SS-SMII - 10BASE-T Transmit Timing ..........................................189

®

LXT9785/LXT9785E RMII - 100BASE-TX Receive Timing ............................................190

®

LXT9785/LXT9785E RMII - 100BASE-TX Transmit Timing ...........................................191

®

LXT9785/LXT9785E RMII - 100BASE-FX Receive Timing ............................................192

®

LXT9785/LXT9785E RMII - 100BASE-FX Transmit Timing ...........................................193

®

LXT9785/LXT9785E RMII - 10BASE-T Receive Timing................................................. 194

®

LXT9785/LXT9785E RMII - 10BASE-T Transmit Timing................................................ 195

®

LXT9785/LXT9785E Auto-Negotiation and Fast Link Pulse Timing ...............................196

®

LXT9785/LXT9785E Fast Link Pulse Timing .................................................................. 196

®

LXT9785/LXT9785E MDIO Write Timing (MDIO Sourced by MAC) ............................... 197

®

LXT9785/LXT9785E MDIO Read Timing (MDIO Sourced by PHY) ...............................197

®

LXT9785/LXT9785E Power-Up Timing........................................................................... 198

®

LXT9785/LXT9785E Reset Recovery Timing ................................................................. 198

63 PHY Identifier Bit Mapping........................................................................................................203

64 Intel

65 Intel

66 Intel

67 Intel

®

LXT9785/LXT9785E 208-Pin PQFP Plastic Package Specification ...............................221

®

LXT9785/LXT9785E 241-Ball BGA23 Package Specs - Top/Side View (LXT9785BC) .222

®

LXT9785/LXT9785E 241-Ball BGA23 Package Specs - Bottom View (LXT9785BC) ....223

®

LXT9785MBC 196-Ball BGA15 Package Specs - Top/Side View (LXT9785MBC) ........225

68 Ordering Information - Sample .................................................................................................228

Tables

1 Intel® LXT9785/LXT9785E Signal Type Descriptions.................................................................20

2 Intel

3 Intel

4 Intel

5 Intel

6 Intel

7 Intel

8 Intel

9 Intel

10 Intel

11 Intel

12 Intel

13 Intel

14 Intel

15 Intel

16 Intel

17 Intel

Datasheet 7

Document Number: 249241

Revision Number: 007

Revision Date: August 28, 2003

®

LXT9785/LXT9785E RMII PQFP Pin List ......................................................................... 22

®

LXT9785/LXT9785E SMII PQFP Pin List ......................................................................... 27

®

LXT9785/LXT9785 SS-SMII PQFP Pin List......................................................................32

®

LXT9785/LXT9785E RMII Signal Descriptions – PQFP ................................................... 36

®

LXT9785/LXT9785E SMII / SS-SMII Common Signal Descriptions – PQFP ................... 39

®

LXT9785/LXT9785E SMII Specific Signal Descriptions – PQFP...................................... 39

®

LXT9785/LXT9785E SS-SMII Specific Signal Descriptions – PQFP ................................ 40

®

LXT9785/LXT9785E MDIO Control Interface Signals – PQFP ......................................... 41

®

LXT9785/LXT9785E Signal Detect – PQFP ..................................................................... 42

®

LXT9785/LXT9785E Network Interface Signal Descriptions – PQFP............................... 42

®

LXT9785/LXT9785E JTAG Test Signal Descriptions – PQFP..........................................43

®

LXT9785/LXT9785E Miscellaneous Signal Descriptions – PQFP .................................... 43

®

LXT9785/LXT9785E LED Signal Descriptions – PQFP.................................................... 47

®

LXT9785/LXT9785E Power Supply Signal Descriptions – PQFP..................................... 48

®

LXT9785/LXT9785E Unused/Reserved Pins – PQFP ...................................................... 50

®

LXT9785/LXT9785E Receive FIFO Depth Considerations............................................... 50

Page 8

Contents

18 Intel® LXT9785/LXT9785E RMII BGA23 Ball List in Alphanumeric Order by Signal Name ...... 52

19 Intel® LXT9785/LXT9785E RMII BGA23 Ball List in Alphanumeric Order by Ball Location ...... 57

20 Intel® LXT9785/LXT9785E SMII BGA23 Ball List in Alphanumeric Order by Signal Name....... 62

21 Intel® LXT9785/LXT9785E SMII BGA23 Ball List in Alphanumeric Order by Ball Location....... 67

22 Intel® LXT9785/LXT9785E SS-SMII BGA23 Ball List in Alphanumeric Order by Signal Name.72

23 Intel® LXT9785/LXT9785E SS-SMII BGA23 Ball List in Alphanumeric Order by Ball Location. 77

24 Intel

25 Intel

26 Intel

27 Intel

28 Intel

29 Intel

30 Intel

31 Intel

32 Intel

33 Intel

34 Intel

35 Intel

36 Intel

®

LXT9785/LXT9785E RMII Signal Descriptions – BGA23 ................................................. 82

®

LXT9785/LXT9785E SMII / SS-SMII Common Signal Descriptions – BGA23 ................. 85

®

LXT9785/LXT9785E SMII Specific Signal Descriptions – BGA23 .................................... 85

®

LXT9785/LXT9785E SS-SMII Specific Signal Descriptions – BGA23 .............................. 86

®

LXT9785/LXT9785E MDIO Control Interface Signals – BGA23 ....................................... 87

®

LXT9785/LXT9785E Signal Detect – BGA23 ................................................................... 88

®

LXT9785/LXT9785E Network Interface Signal Descriptions – BGA23............................. 88

®

LXT9785/LXT9785E JTAG Test Signal Descriptions – BGA23........................................ 89

®

LXT9785/LXT9785E Miscellaneous Signal Descriptions – BGA23 .................................. 90

®

LXT9785/LXT9785E LED Signal Descriptions – BGA23 .................................................. 94

®

LXT9785/LXT9785E Power Supply Signal Descriptions – BGA23................................... 95

®

LXT9785/LXT9785E Unused/Reserved Pins – BGA23 .................................................... 97

®

LXT9785/LXT9785E Receive FIFO Depth Configurations ............................................... 97

37 Intel® LXT9785MBC BGA15 Ball List in Alphanumeric Order by Signal Name ......................... 99

38 Intel® LXT9785MBC BGA15 Ball List in Alphanumeric Order by Ball Location

(SMII/SS-SMII) ......................................................................................................................... 103

39 Intel

40 Intel

41 Intel

42 Intel

43 Intel

44 Intel

45 Intel

®

LXT9785 BGA15 Signal Descriptions ............................................................................ 109

®

LXT9785/LXT9785E MDIX Selection ............................................................................. 119

®

LXT9785/LXT9785E MII Mode Select ............................................................................ 120

®

LXT9785/9785E Global Hardware Configuration Settings ............................................. 129

®

LXT9785/LXT9785E SMII Signal Summary ................................................................... 132

®

LXT9785/LXT9785E RX Status Encoding Bit Definitions ............................................... 137

®

LXT9785/LXT9785E SS-SMII ......................................................................................... 138

46 4B/5B Coding ........................................................................................................................... 147

47 Next Page Message #5 Code Word Definitions ....................................................................... 155

48 BSR Mode of Operation ........................................................................................................... 159

49 Supported JTAG Instructions ...................................................................................................159

50 Intel

51 Intel

52 Intel

53 Intel

54 Intel

55 Intel

56 Intel

57 Intel

58 Intel

59 Intel

60 Intel

61 Intel

62 Intel

63 Intel

64 Intel

65 Intel

66 Intel

®

LXT9785/LXT9785E Magnetics Requirements .............................................................. 166

®

LXT9785/LXT9785E Absolute Maximum Ratings .......................................................... 173

®

LXT9785/LXT9785E Operating Conditions .................................................................... 173

®

LXT9785/LXT9785E Digital I/O DC Electrical Characteristics (VCCIO = 2.5 V +/- 5%) . 174

®

LXT9785/LXT9785E Digital I/O DC Electrical Characteristics (VCCIO = 3.3 V +/- 5%) . 175

®

LXT9785/LXT9785E Digital I/O DC Electrical Characteristics – SD Pins ....................... 175

®

LXT9785/LXT9785E Required Clock Characteristics ..................................................... 175

®

LXT9785/LXT9785E 100BASE-TX Transceiver Characteristics ....................................176

®

LXT9785/LXT9785E 100BASE-FX Transceiver Characteristics ....................................176

®

LXT9785/LXT9785E 10BASE-T Transceiver Characteristics......................................... 177

®

LXT9785/LXT9785E SMII - 100BASE-TX Receive Timing Parameters......................... 178

®

LXT9785/LXT9785E SMII - 100BASE-TX Transmit Timing Parameters ........................ 179

®

LXT9785/LXT9785E SMII - 100BASE-FX Receive Timing Parameters......................... 180

®

LXT9785/LXT9785E SMII - 100BASE-FX Transmit Timing Parameters ........................ 181

®

LXT9785/LXT9785E SMII - 10BASE-T Receive Timing Parameters .............................182

®

LXT9785/LXT9785E SMII-10BASE-T Transmit Timing Parameters ..............................183

®

LXT9785/LXT9785E SS-SMII - 100BASE-TX Receive Timing Parameters................... 184

8 Datasheet

Document Number: 249241

Revision Number: 007

Revision Date: August 28, 2003

Page 9

Contents

67 Intel® LXT9785/LXT9785E SS-SMII - 100BASE-TX Transmit Timing...................................... 185

68 Intel

69 Intel

70 Intel

71 Intel

72 Intel

73 Intel

74 Intel

75 Intel

76 Intel

77 Intel

78 Intel

79 Intel

80 Intel

81 Intel

82 Intel

®

LXT9785/LXT9785E SS-SMII - 100BASE-FX Receive Timing Parameters ................... 186

®

LXT9785/LXT9785E SS-SMII - 100BASE-FX Transmit Timing Parameters ..................187

®

LXT9785/LXT9785E SS-SMII - 10BASE-T Receive Timing Parameters .......................188

®

LXT9785/LXT9785E SS-SMII - 10BASE-T Transmit Timing Parameters ......................189

®

LXT9785/LXT9785E RMII - 100BASE-TX Receive Timing Parameters......................... 190

®

LXT9785/LXT9785E RMII - 100BASE-TX Transmit Timing Parameters........................ 191

®

LXT9785/LXT9785E RMII - 100BASE-FX Receive Timing Parameters......................... 192

®

LXT9785/LXT9785E RMII - 100BASE-FX Transmit Timing Parameters........................ 193

®

LXT9785/LXT9785E RMII - 10BASE-T Receive Timing Parameters .............................194

®

LXT9785/LXT9785E RMII - 10BASE-T Transmit Timing Parameters ............................195

®

LXT9785/LXT9785E Auto-Negotiation and Fast Link Pulse Timing Parameters............196

®

LXT9785/LXT9785E MDIO Timing Parameters..............................................................197

®

LXT9785/LXT9785E Power-Up Timing Parameters ....................................................... 198

®

LXT9785/LXT9785E Reset Recovery Timing Parameters .............................................198

®

LXT9785/LXT9785E Register Set................................................................................... 199

83 Control Register (Address 0) ....................................................................................................200

84 Status Register (Address 1)......................................................................................................201

85 PHY Identification Register 1 (Address 2) ................................................................................203

86 PHY Identification Register 2 (Address 3) ................................................................................203

87 Auto-Negotiation Advertisement Register (Address 4) .............................................................204

88 Auto-Negotiation Link Partner Base Page Ability Register (Address 5) ................................... 205

89 Auto-Negotiation Expansion Register (Address 6) ...................................................................206

90 Auto-Negotiation Next Page Transmit Register (Address 7) .................................................... 206

91 Auto-Negotiation Link Partner Next Page Receive Register (Address 8) ................................. 207

92 Port Configuration Register (Address 16, Hex 10) ................................................................... 207

93 Quick Status Register (Address 17, Hex 11) ............................................................................ 209

94 Interrupt Enable Register (Address 18, Hex 12).......................................................................211

95 Interrupt Status Register (Address 19, Hex 13)........................................................................212

96 LED Configuration Register (Address 20, Hex 14) ................................................................... 213

97 Receive Error Count Register (Address 21, Hex 15)................................................................ 214

98 RMII Out-of-Band Signaling Register (Address 25, Hex 19) .................................................... 215

99 Trim Enable Register (Address 27, Hex 1B)............................................................................. 216

100 Cable Diagnostics Register (Address 29, Hex 1D) ................................................................... 217

101 Intel

®

LXT9785/LXT9785E Register Bit Map............................................................................219

102 Intel® LXT9785MBC 196-Ball BGA15 Package Dimensions ................................................... 226

103 Product Information .................................................................................................................. 227

Datasheet 9

Document Number: 249241

Revision Number: 007

Revision Date: August 28, 2003

Page 10

Contents

Revision History

Page Description

21 Modified Figure 2 “Intel® LXT9785 and Intel® LXT9785E RMII 208-Pin PQFP Assignments”.

22 Modified Table 2 “Intel® LXT9785/LXT9785E RMII PQFP Pin List”.

26 Modified Figure 3 “Intel® LXT9785/LXT9785E SMII 208-Pin PQFP Assignments”.

27 Modified Table 3 “Intel® LXT9785/LXT9785E SMII PQFP Pin List”.

31 Modified Figure 4 “Intel® LXT9785/LXT9785E SS-SMII 208-Pin PQFP Assignments”.

32 Modified Table 4 “Intel® LXT9785/LXT9785 SS-SMII PQFP Pin List”.

36 Modified Table 5 “Intel® LXT9785/LXT9785E RMII Signal Descriptions – PQFP”.

40 Modified Table 8 “Intel® LXT9785/LXT9785E SS-SMII Specific Signal Descriptions – PQFP”.

43 Modified Table 13 “Intel® LXT9785/LXT9785E Miscellaneous Signal Descriptions – PQFP”.

50 Modified Table 16 “Intel® LXT9785/LXT9785E Unused/Reserved Pins – PQFP”.

Replaced old Figures 5, 6, and 7 with Figure 5 “Intel® LXT9785/LXT9785E 241-Ball BGA23

51

Assignments (Top View)”.

Modified Table 18 “Intel® LXT9785/LXT9785E RMII BGA23 Ball List in Alphanumeric Order by

52

Signal Name”.

Modified Table 19 “Intel® LXT9785/LXT9785E RMII BGA23 Ball List in Alphanumeric Order by Ball

57

Location”.

Modified Table 20 “Intel® LXT9785/LXT9785E SMII BGA23 Ball List in Alphanumeric Order by

62

Signal Name”.

Modified Table 21 “Intel® LXT9785/LXT9785E SMII BGA23 Ball List in Alphanumeric Order by Ball

67

Location”

Modified Table 22 “Intel® LXT9785/LXT9785E SS-SMII BGA23 Ball List in Alphanumeric Order by

72

Signal Name”.

Modified Table 23 “Intel® LXT9785/LXT9785E SS-SMII BGA23 Ball List in Alphanumeric Order by

77

Ball Location”.

Modified Table 23 “Intel® LXT9785/LXT9785E SS-SMII BGA23 Ball List in Alphanumeric Order by

82

Ball Location”.

86 Modified Table 27 “Intel® LXT9785/LXT9785E SS-SMII Specific Signal Descriptions – BGA23”.

90 Modified Table 32 “Intel® LXT9785/LXT9785E Miscellaneous Signal Descriptions – BGA23”.

97 Modified Table 35 “Intel® LXT9785/LXT9785E Unused/Reserved Pins – BGA23”.

Added Section 3.5, “BGA15 Ball Assignments” (including Figure 6 “Intel® LXT9785MBC 196-Ball

98

BGA15 Assignments (Top View)”, Table 37 “Intel® LXT9785MBC BGA15 Ball List in Alphanumeric

Order by Signal Name” through Table 39 “Intel® LXT9785 BGA15 Signal Descriptions”.

116 Added second paragraph under Section 4.1, “Introduction”.

117 Added note under Section 4.1.2.1, “Sectionalization”.

119 Added note under Table 40 “Intel® LXT9785/LXT9785E MDIX Selection”.

119 Added note under Section 4.3, “Media Independent Interface (MII) Interfaces”.

120 Added note to Table 41 “Intel® LXT9785/LXT9785E MII Mode Select”.

Revision Number: 007

Revision Date: August 28, 2003

10 Datasheet

Document Number: 249241

Revision Number: 007

Revision Date: August 28, 2003

Page 11

Contents

Revision Number: 007

Revision Date: August 28, 2003

Page Description

120 Modified/added text under Section 4.3.2, “Internal Loopback”.

121 Modified text under Section 4.3.6, “MII Isolate”.

Section 4.3.7, “MDIO Management Interface”:

121

Added note under second paragraph.

Added last paragraph.

123 Added note under Section 4.3.8, “MII Sectionalization”.

124 Added new Section 4.3.11, “FIFO Initial Fill Values”

125 Modified paragraph three under Section 4.4.1, “Power Requirements”.

127 Added notes under second and last paragraphs under Section 4.5.3, “Power-Down Mode”.

128 Modified last bullet under Section 4.5.3.1, “Global (Hardware) Power Down”.

128 Added last paragraph to Section 4.5.4, “Reset”.

129 Modified Table 42 “Intel® LXT9785/9785E Global Hardware Configuration Settings”.

130 Change heading and modified last line under Section 4.6.1.2, “Manual Next Page Exchange”.

Section 4.6.1.4, “Link Criteria”:

Changed scrambler to descrambler in first line.

130

Modified second paragraph.

Added two new paragraphs.

131 Added second paragraph under Section 4.6.1.5, “Parallel Detection”.

Modified paragraphs under Section 4.6.1.6, “Reliable Link Establishment While Auto MDI/MDIX is

131

Enabled in Forced Speed Mode”.

136 Changed “1110” to “0101” under Section 4.7.4.3, “Receive Error”.

141 Added note under first paragraph of Section 4.8, “RMII Operation”

Changed “asynchronously” to “synchronously” in second paragraph under Section 4.9.3.3, “Carrier

148

Sense/Data Valid (RMII)”.

148 Modified last sentence in first paragraph under Section 4.9.3.4, “Carrier Sense (SMII)”.

149 Modified paragraph under Section 4.9.3.6.3, “Polarity Correction”.

149 Added note under Section 4.9.3.7, “Fiber PMD Sublayer”.

149 Added second paragraph under Section 4.9.3.7.1, “Far End Fault Indications”.

150 Modified/added text under Section 4.10.1, “Preamble Handling”.

151 Modified text under Section 4.10.4, “Jabber”.

152 Modified first paragraph under Section 4.11, “DTE Discovery Process”.

153 Modified Item 1 of Section 4.11.2, “Interaction between Processor, MAC, and PHY”.

154 Modified second paragraph under Section 4.11.4, “DTE Discovery Process Flow”.

155 Added Section 4.11.5, “DTE Discovery Behavior”

Added BGA15 information into first paragraph under Section 4.12.2, “Per-Port LED Driver

157

Functions”.

Added last sentence to first paragraph and note under first paragraph under Section 4.12.3, “Out-of-

158

Band Signaling”.

160 Added Section 4.13, “Cable Diagnostics Overview”.

161 Modified/added text under Section 4.13.3, “Implementation Considerations”.

Datasheet 11

Document Number: 249241

Revision Number: 007

Revision Date: August 28, 2003

Page 12

Contents

Revision Number: 007

Revision Date: August 28, 2003

Page Description

162 Added Section 4.14, “Link Hold-Off Overview”.

173 Modified Table 52 “Intel® LXT9785/LXT9785E Operating Conditions”

176 Modified Table 58 “Intel® LXT9785/LXT9785E 100BASE-FX Transceiver Characteristics”

178-

Added note to Table 60 “Intel® LXT9785/LXT9785E SMII - 100BASE-TX Receive Timing

Parameters” through Table 77 “Intel® LXT9785/LXT9785E RMII - 10BASE-T Transmit Timing

195

Parameters”.

Added table note to Table 60 “Intel® LXT9785/LXT9785E SMII - 100BASE-TX Receive Timing

178

Parameters”.

Added table note to Table 66 “Intel® LXT9785/LXT9785E SS-SMII - 100BASE-TX Receive Timing

184

Parameters”.

Added table note to Table 72 “Intel® LXT9785/LXT9785E RMII - 100BASE-TX Receive Timing

190

Parameters”

Added software power-down and note to Table 80 “Intel® LXT9785/LXT9785E Power-Up Timing

198

Parameters”.

199 Modified paragraphs and added last paragraph under Section 7.0, “Register Definitions”.

199 Modified Table 82 “Intel® LXT9785/LXT9785E Register Set”.

200 Modified Table 83 “Control Register (Address 0)”.

201 Modified Table 84 “Status Register (Address 1)”.

203 Modified Table 85 “PHY Identification Register 1 (Address 2)”.

203 Modified Table 86 “PHY Identification Register 2 (Address 3)”

204 Modified Table 87 “Auto-Negotiation Advertisement Register (Address 4)”

205 Modified Table 88 “Auto-Negotiation Link Partner Base Page Ability Register (Address 5)”.

206 Modified Table 89 “Auto-Negotiation Expansion Register (Address 6)”.

206 Modified Table 90 “Auto-Negotiation Next Page Transmit Register (Address 7)”.

206 Modified Table 91 “Auto-Negotiation Link Partner Next Page Receive Register (Address 8)”.

207 Modified Table 92 “Port Configuration Register (Address 16, Hex 10)”. (Register bits 16.6, 16.4:3)

209 Modified Table 93 “Quick Status Register (Address 17, Hex 11)”. (Register bit 17.8)

211 Modified Table 94 “Interrupt Enable Register (Address 18, Hex 12)”

212 Modified Table 95 “Interrupt Status Register (Address 19, Hex 13)”

213 Modified Table 96 “LED Configuration Register (Address 20, Hex 14)”

214 Modified Table 97 “Receive Error Count Register (Address 21, Hex 15)”.

215 Modified Table 98 “RMII Out-of-Band Signaling Register (Address 25, Hex 19)”.

216 Modified Table 99 “Trim Enable Register (Address 27, Hex 1B)”. (Register bit 27.6)

217 Added Table 100 “Cable Diagnostics Register (Address 29, Hex 1D)”.

219 Modified Table 101 “Intel® LXT9785/LXT9785E Register Bit Map”.

226 Added Figure 102 “Intel® LXT9785MBC 196-Ball BGA15 Package Dimensions”

227 Modified table and figure under Section 9.0, “Ordering Information”.

12 Datasheet

Document Number: 249241

Revision Number: 007

Revision Date: August 28, 2003

Page 13

Contents

Revision Number: 006 (INTERNAL RELEASE)

Page Description

Changed "pseudo-ECL (PECL)" to "Low Voltage Positive Emitter Coupled Logic (LVPECL)" in the

1

second paragraph, front page.

Modified Table 5 “Intel® LXT9785/LXT9785E RMII Signal Descriptions – PQFP”. Added last

36

sentence to RXER0 through RXER7 signal description.

42 Modified Table 10 “Intel® LXT9785/LXT9785E Signal Detect – PQFP”.

42 Modified Table 11 “Intel® LXT9785/LXT9785E Network Interface Signal Descriptions – PQFP”,

Modified Table 13 “Intel® LXT9785/LXT9785E Miscellaneous Signal Descriptions – PQFP”. Added

43

note to PREASEL signal description.

Modified Section 4.1, “Introduction”. Changed "Pseudo-ECL (PECL)" to "Low Voltage PECL

116

(LVPECL)" in the first paragraph, second sentence.

119 Replace text under Section 4.2.1.3, “Fiber Interface”.

120 Modified Section 4.3.2, “Internal Loopback”.

130 Modified last sentence under Section 4.6.1.4, “Link Criteria”.

131 Modified text under Section 4.6.1.5, “Parallel Detection”. Added second paragraph.

136 Modified text under Section 4.7.4.3, “Receive Error”.

Changed "PECL" to "LVPECL in third paragraph, first sentence under Section 4.9.1, “100BASE-X

145

Network Operations”.

146 Modified

Modified Section 4.9.3.3, “Carrier Sense/Data Valid (RMII)”. Changed “asynchronously to

148

“synchronously.”

148 Modified text under Section 4.9.3.4, “Carrier Sense (SMII)”. Revised last sentence in first paragraph.

149 Modified paragraph under Section 4.9.3.6.3, “Polarity Correction”.

149 Replaced text under Section 4.9.3.7, “Fiber PMD Sublayer”.

150 Modified Section 4.10.1, “Preamble Handling”. Added text to last paragraph.

151 Modified first sentence under Section 4.10.4, “Jabber”.

152 Modified first paragraph of Section 4.11, “DTE Discovery Process”.

153 Modified Item 1 of Section 4.11.2, “Interaction between Processor, MAC, and PHY”.

158 Modified Section 4.12.3, “Out-of-Band Signaling”. Added sentence to end of first paragraph.

166 Replaced text under Section 5.2.5, “The Fiber Interface”.

Replaced Figure 36 “Recommended Intel® LXT9785/LXT9785E-to-3.3 V Fiber Transceiver

170

Interface Circuitry”.

Replaced Figure 37 “Recommended Intel® LXT9785/LXT9785E-to-5 V Fiber Transceiver Interface

171

Circuitry”.

173 Modified Table 52 “Intel® LXT9785/LXT9785E Operating Conditions”.

Modified Table 53 “Intel® LXT9785/LXT9785E Digital I/O DC Electrical Characteristics (VCCIO =

174

2.5 V +/- 5%)”.

Modified Table 54 “Intel® LXT9785/LXT9785E Digital I/O DC Electrical Characteristics (VCCIO =

175

3.3 V +/- 5%)”.

175 Added Table 55 “Intel® LXT9785/LXT9785E Digital I/O DC Electrical Characteristics – SD Pins”.

176 Modified Table 58 “Intel® LXT9785/LXT9785E 100BASE-FX Transceiver Characteristics”.

Figure 28 “Intel® LXT9785/LXT9785E Protocol Sublayers”.

Revision Date: June 10, 2003

Datasheet 13

Document Number: 249241

Revision Number: 007

Revision Date: August 28, 2003

Page 14

Contents

Revision Number: 006 (INTERNAL RELEASE)

Page Description

200 Modified Table 83 “Control Register (Address 0)”.

201 Modified Table 84 “Status Register (Address 1)”.

204 Modified Table 87 “Auto-Negotiation Advertisement Register (Address 4)”.

205 Modified Table 88 “Auto-Negotiation Link Partner Base Page Ability Register (Address 5)”.

207 Modified Table 91 “Auto-Negotiation Link Partner Next Page Receive Register (Address 8)”.

207 Modified Table 92 “Port Configuration Register (Address 16, Hex 10)”.

209 Modified Table 93 “Quick Status Register (Address 17, Hex 11)”.

211 Modified Table 94 “Interrupt Enable Register (Address 18, Hex 12)”

Modified Table 95 “Interrupt Status Register (Address 19, Hex 13)”. Changed all references of RO/

212

SC to R/LH.

214 Modified Table 97 “Receive Error Count Register (Address 21, Hex 15)”.

Modified Table 98 “RMII Out-of-Band Signaling Register (Address 25, Hex 19)”. Added note to

215

Register bit 25.0.

216 Modified Table 99 “Trim Enable Register (Address 27, Hex 1B)”.

227 Modified Table 103 “Product Information”.

Revision Date: June 10, 2003

Revision Number: 005

Revision Date: January 2002

Page Description

1 Added bullet to Product Features

Modified Table 12 “Intel® LXT9785/LXT9785E Miscellaneous Signal Descriptions” (Added

49

FIFOSEL1 and FIFOSEL0)

Added Section 2.6.1.6, “Reliable Link Establishment While Auto MDI/MDIX is Enabled in Forced

70

Speed Mode”

109

110

111 Added Figure 40 “ON Semiconductor Triple PECL-to-LVPECL Translator”

112 Modified Table 28 “Absolute Maximum Ratings”

112 Modified Table 29 “Operating Conditions”

114

129

131

133

Modified Figure 38 “Recommended Intel® LXT9785/LXT9785E-to-3.3 V Fiber Transceiver

Interface Circuitry”

Added Figure 39 “Recommended Intel® LXT9785/LXT9785E-to-5 V Fiber Transceiver Interface

Circuitry”

Modified Table 31 “Digital I/O DC Electrical Characteristics (VCCIO = 3.3 V +/- 5%)”(Output low

voltage SD pins - Max)

Modified Figure 53 “RMII - 100BASE-TX Receive Timing” and Table 49 “RMII - 100BASE-TX

Receive Timing Parameters”

Modified Figure 55 “RMII - 100BASE-FX Receive Timing” and Table 51 “RMII - 100BASE-FX

Receive Timing Parameters”

Modified Figure 57 “RMII - 10BASE-T Receive Timing” and Table 53 “RMII - 10BASE-T Receive

Timing Parameters”

14 Datasheet

Document Number: 249241

Revision Number: 007

Revision Date: August 28, 2003

Page 15

Revision Number: 005

Revision Date: January 2002

Page Description

146 Modified Table 69 “Port Configuration Register (Address 16, Hex 10)” (Bits 16.5 and 16.6)

148 Modified Table 71 “Interrupt Enable Register (Address 18, Hex 12)”

168 Added product ordering table and diagram.

Revision Number: 003

Revision Date: April 2001

Page Description

1 Modified and added new language to front page.

61 Reset: Modified language in first paragraph.

85 Added new section on DTE discovery.

93 Supported JTAG Instructions table: replaced long hit streams with hex.

97 LED Circuit: Modified paragraph language.

97 LED Circuit diagram: Modified diagram.

99 Replaced Typical Fiber Interface diagram.

102

122 Auto-Negotiation and Fast Link Pulse Timing Parameters: FLP burst width under Typ = 2.

126 Control Register table: Modified table and table notes.

128 PHY Identification Register 2 (Address 3): Modified table.

128 PHY Identifier Bit Mapping: Modified diagram.

131 Auto-Negotiation Expansion: Modified table and table notes.

133 Port Configuration Register table: Modified table and table notes.

140 Trim Enable Register: Modified table (DTE Discovery).

141 Modified Register Bit Map table.

Required Clock Characteristics table: Replaced SMII Input frequency and RMII Input frequency

symbol with “f”.

Contents

Datasheet 15

Document Number: 249241

Revision Number: 007

Revision Date: August 28, 2003

Page 16

LXT9785 and LXT9785E Advanced 8-Port 10/100 Mbps PHY Transceivers

1.0 Introduction

This document contains information on the Intel® LXT9785/LXT9785E Advanced 8-port

10/100 Mbps Fast Ethernet transceivers.

1.1 What You Will Find in This Document

This document contains the following sections:

• Section 3.0, “Pin/Ball Assignments and Signal Descriptions” on page 20

This section contains pin/ball assignments and signal descriptions for the following:

— Section 3.1, “PQFP Pin Assignments” on page 20

— Section 3.2, “PQFP Signal Descriptions” on page 36

— Section 3.3, “BGA23 Ball Assignments” on page 51

— Section 3.4, “BGA23 Signal Descriptions” on page 82

— Section 3.5, “BGA15 Ball Assignments” on page 98

— Section 3.6, “BGA15 Signal Descriptions” on page 109

• Section 4.0, “Functional Description” on page 116

• Section 5.0, “Application Information” on page 164

• Section 6.0, “Test Specifications” on page 173

• Section 7.0, “Register Definitions” on page 199

• Section 8.0, “Package Specifications” on page 221

• Section 9.0, “Ordering Information” on page 227

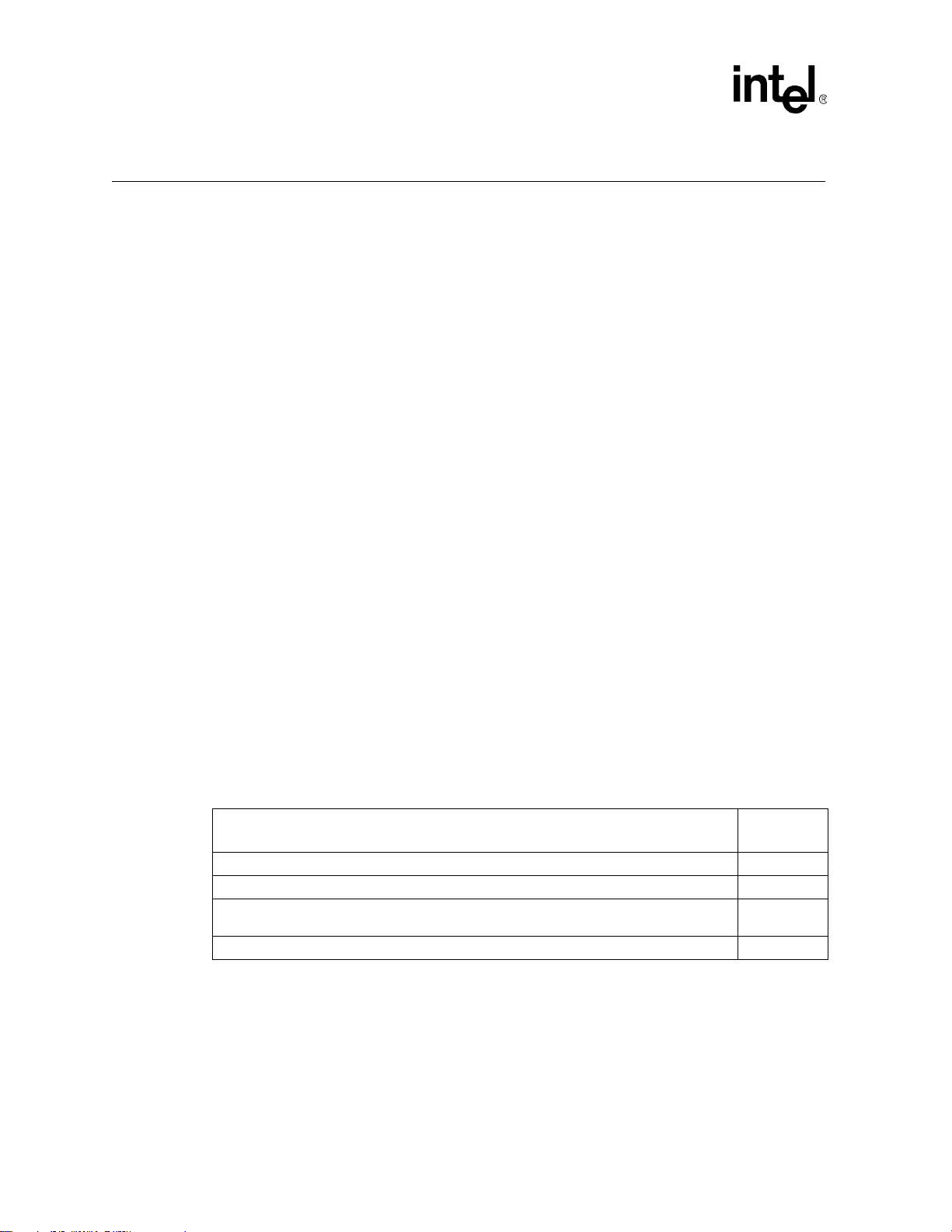

1.2 Related Documents

Document

®

Intel

LXT9785/LXT9785E Design and Layout Guide 249509

®

LXT9785/LXT9785E Specification Update 249357

Intel

®

Intel

LXT9785/LXT9785E 100BASE-FX Fiber Optic Transceivers: Connecting a PECL/

LVPECL Interface

IP Telephony and DTE Discovery Using Intel Ethernet

Document

Number

250781

®

PHYs 249611

18 Datasheet

Document Number: 249241

Revision Date: August 28, 2003

Revision Number: 007

Page 17

LXT9785 and LXT9785E Advanced 8-Port 10/100 Mbps PHY Transceivers

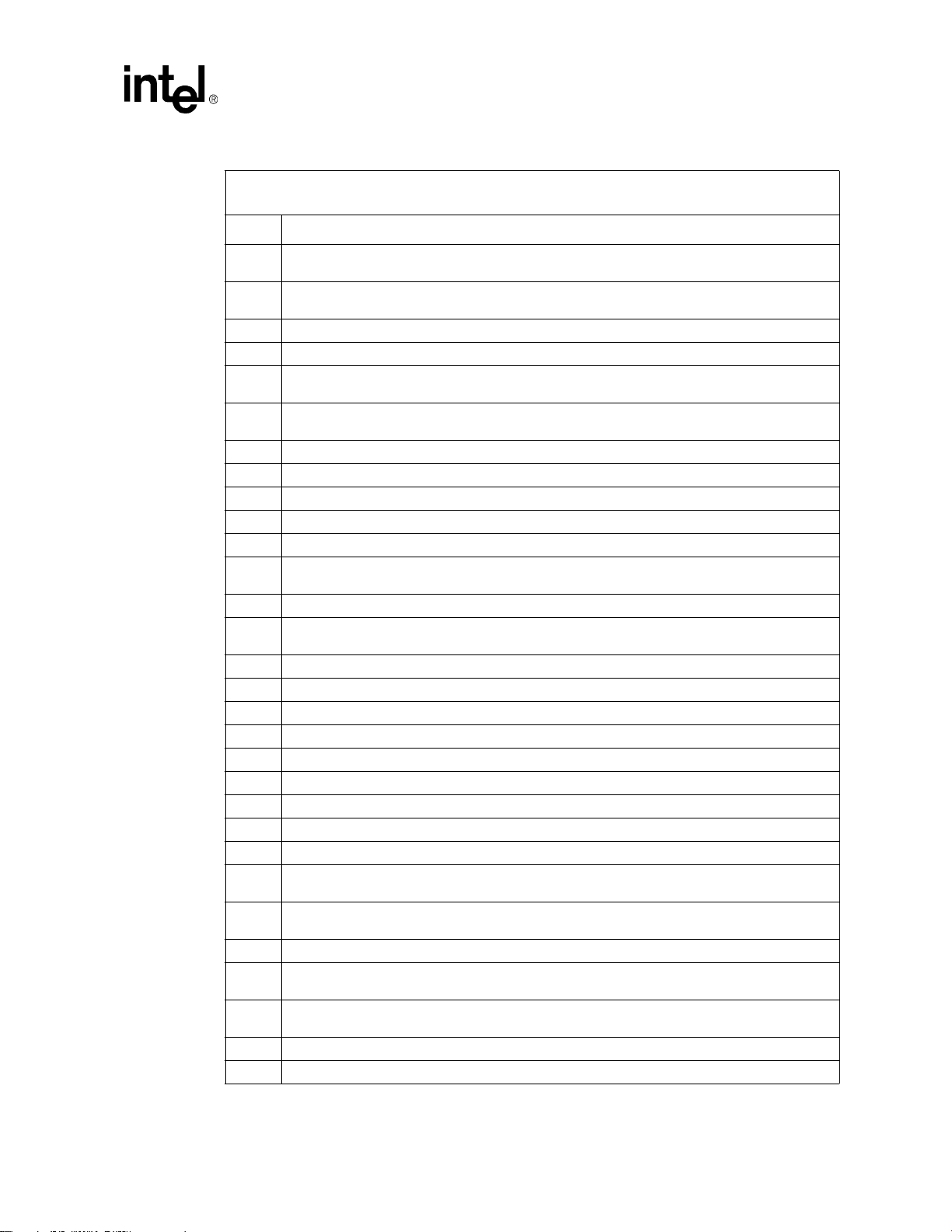

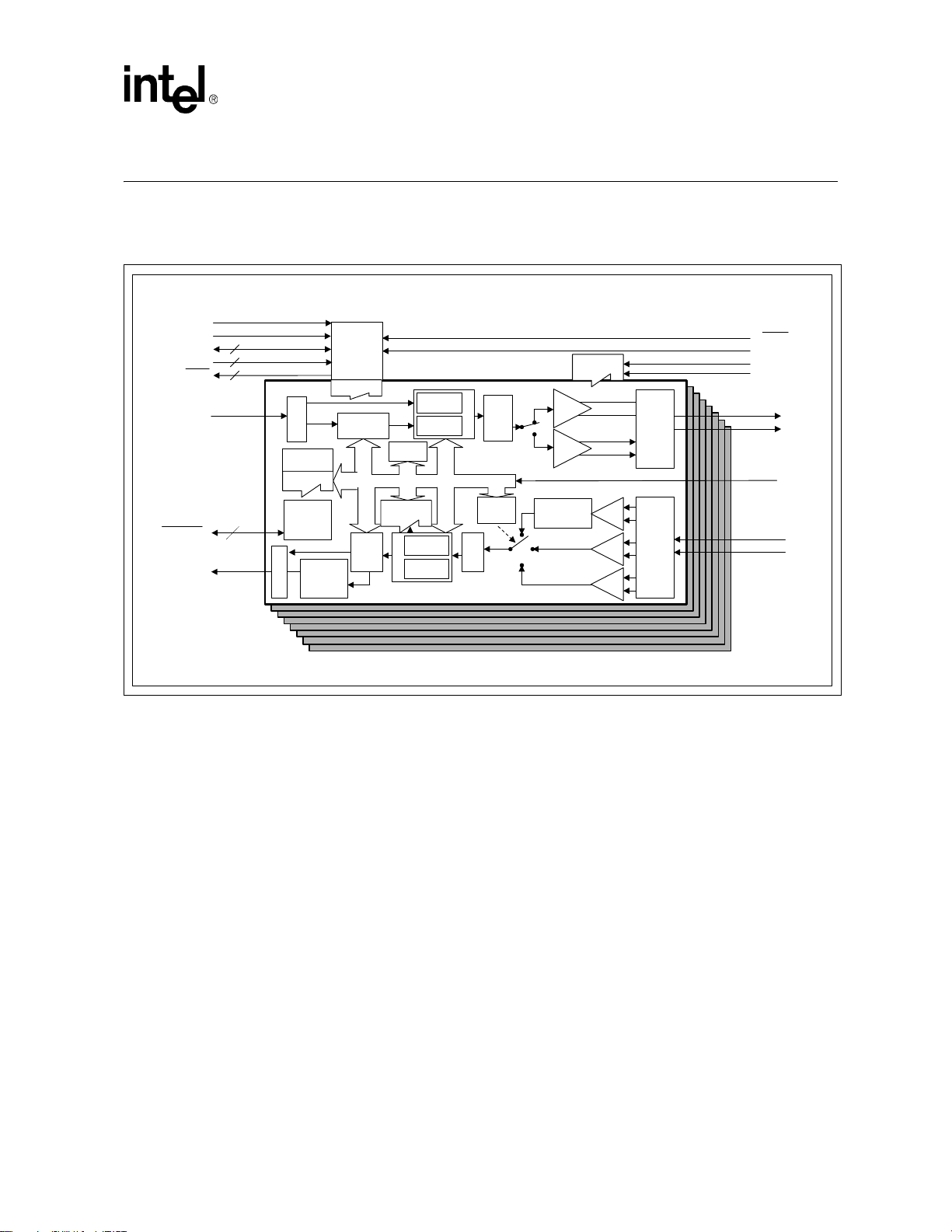

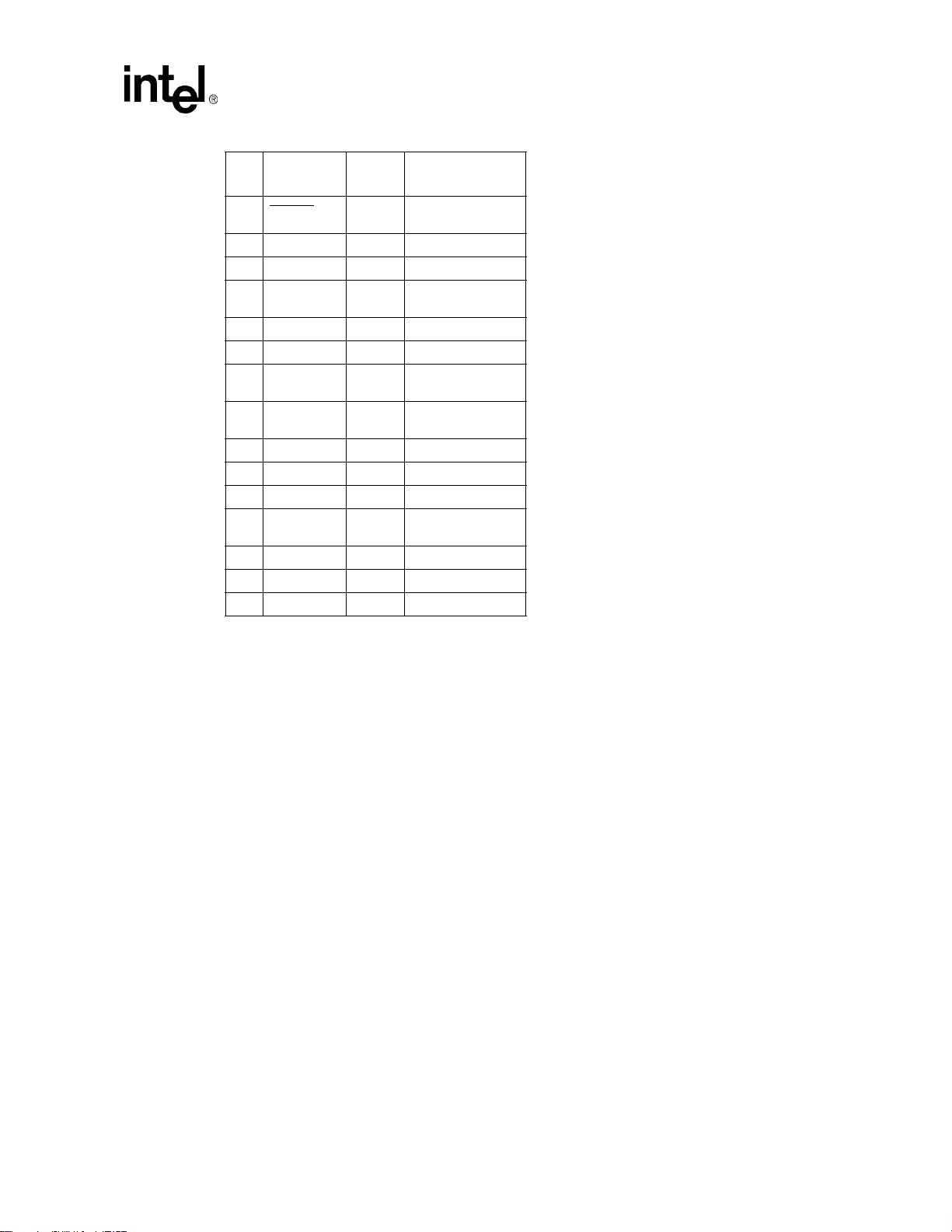

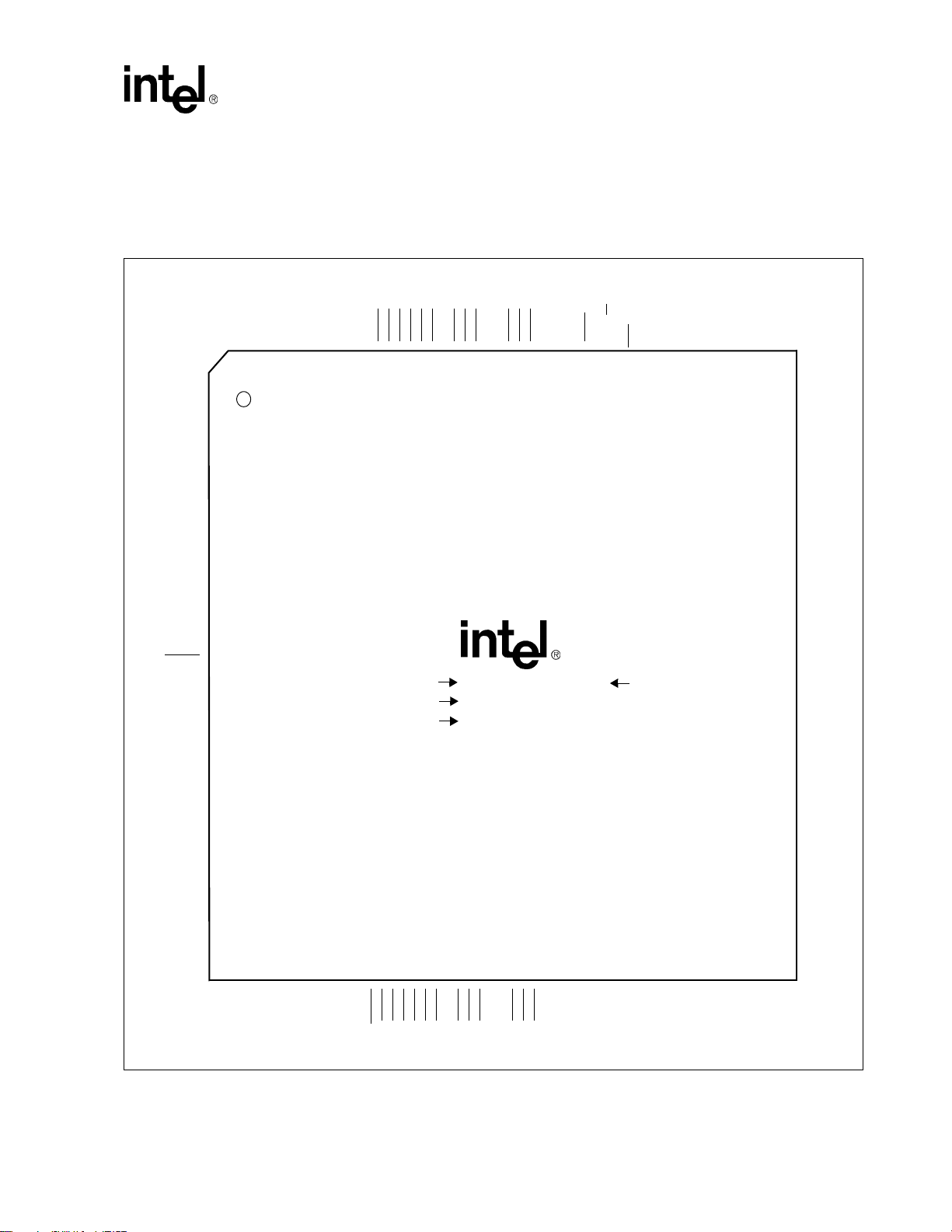

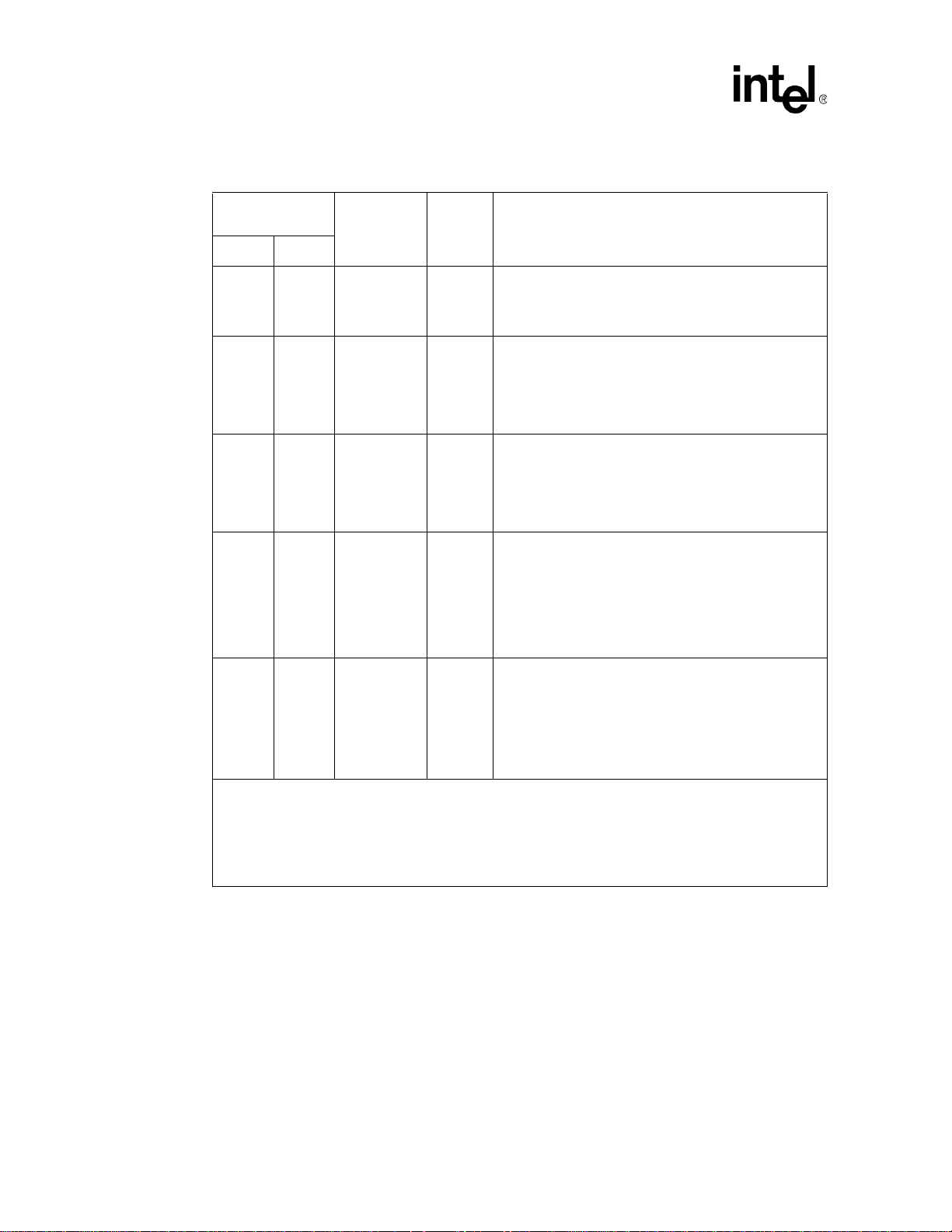

2.0 Block Diagram

Figure 1 provides the LXT9785/LXT9785E block diagram.

Figure 1. Intel

®

LXT9785/LXT9785E Block Diagram

RMII/SMII Contr

ADD_<4:0>

MDIO

MDC

MDINT

TxDatan

LEDn_<2:0>

RxDatan

8-Port Global

Functions

Management /

TX PCS

Mgmt

Counters

Register Set

Port LED

Drivers

Carrier Sense

Data Valid

Error Detect

Mode Selec t

Logic & LED

Drivers

Register Set

Parallel/Serial

Converter

Serial to

Parallel

Converter

Manchester

Encoder

Scrambler

& Encoder

Auto

Negotiation

Clock Generator

Manchester

10

Decoder

Decoder &

100

Descrambler

Per-Port Functions

10

100

Slicer

Pulse

Shaper

Media

Select

TP

Driver

ECL

Driver

Adaptive EQ with BL

Wander Cancellation

PORT 0

PORT 1

PORT 2

PORT 3

Clock

Generator

+

-

+

-

PORT 4

PORT 5

PORT 6

100TX

100FX

10BT

PORT 7

+

-

+

-

+

-

TP /

Fiber

Out

TP /

Fiber In

2

2

2

3

RX PCS

RESET

PWRDN

REFCLK

SYNC (SMII only)

TPFOPn

TPFONn

Fiber

select n

TPFIPn

TPFINn

Datasheet 19

Document Number: 249241

Revision Number: 007

Revision Date: August 28, 2003

Page 18

Intel® LXT9785 and Intel® LXT9785E Advanced 8-Port 10/100 Mbps PHY Transceivers

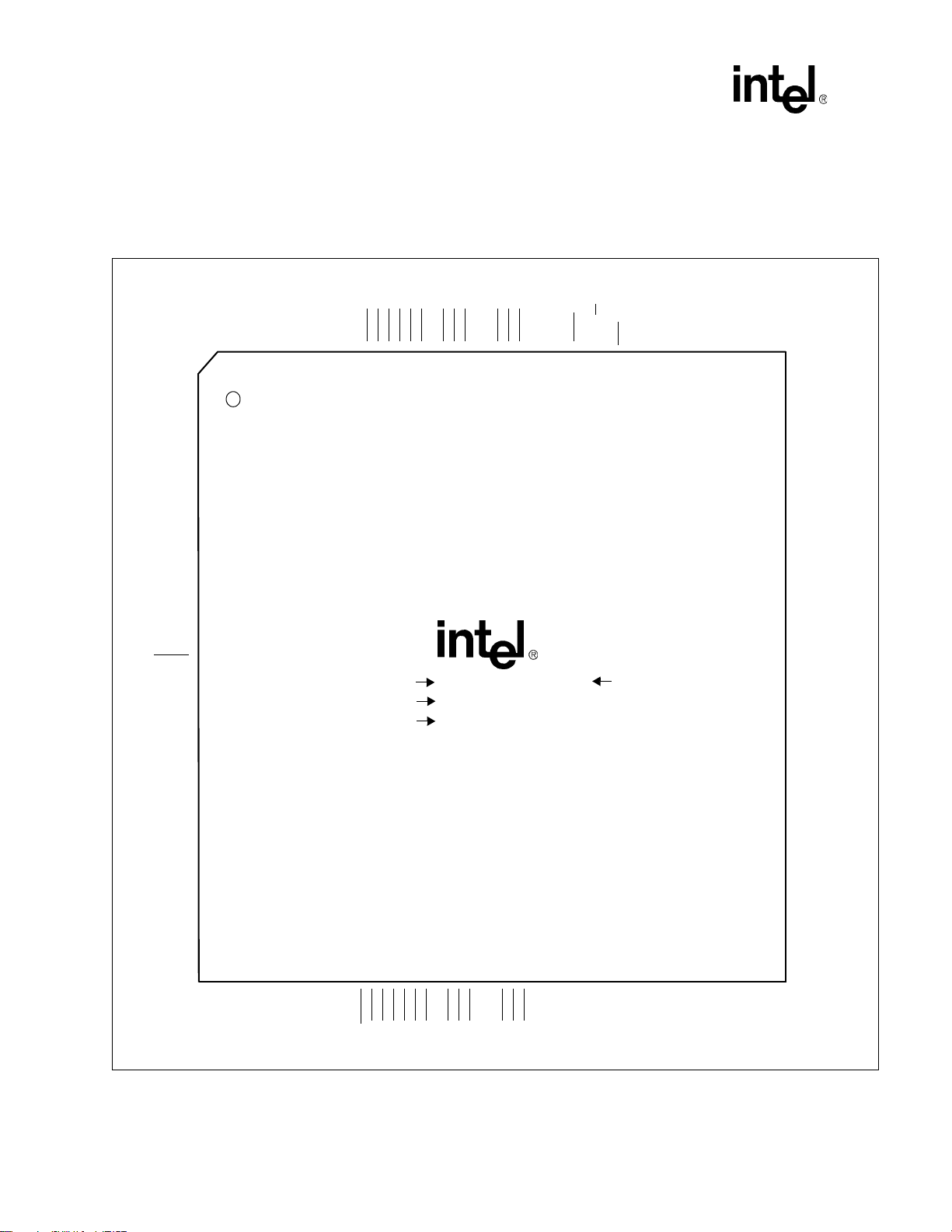

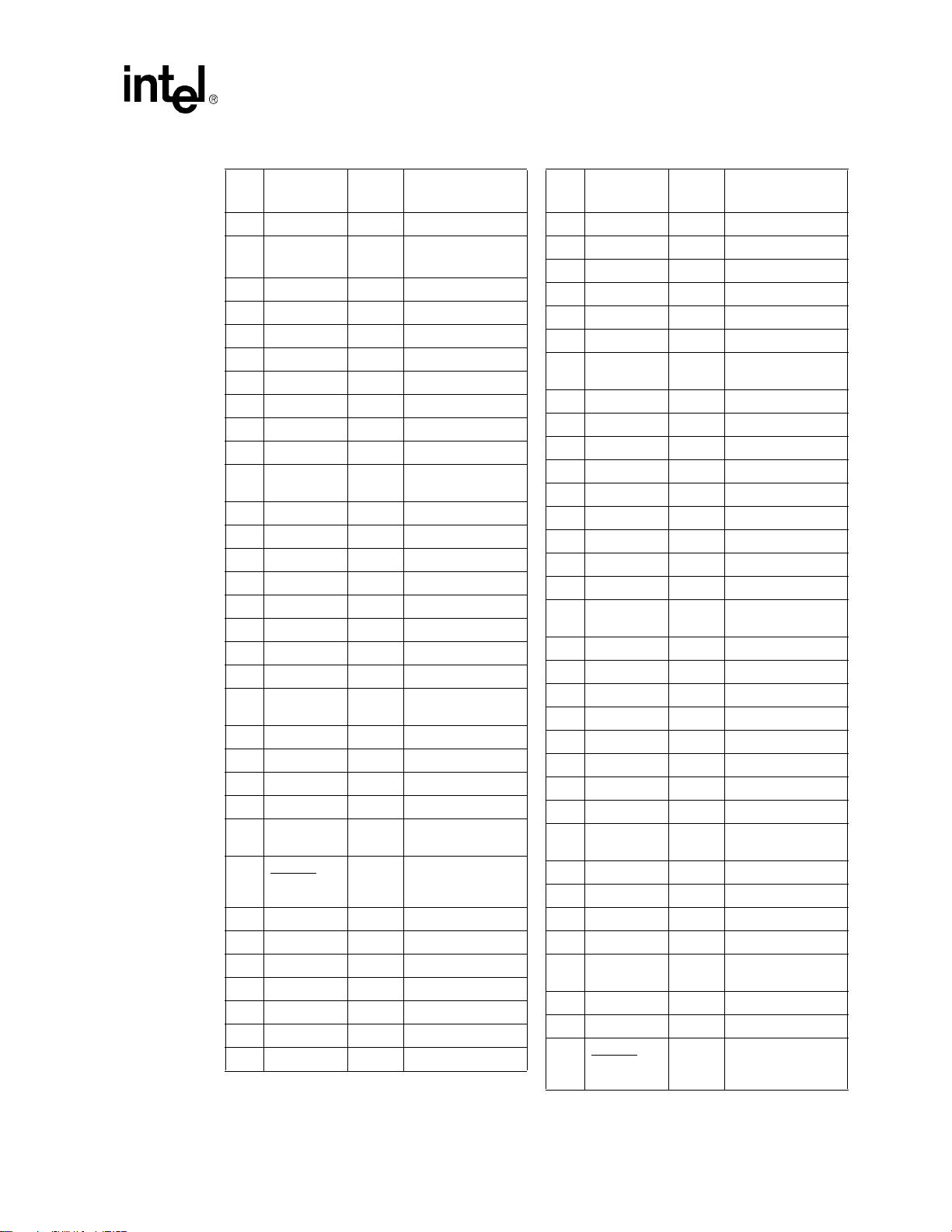

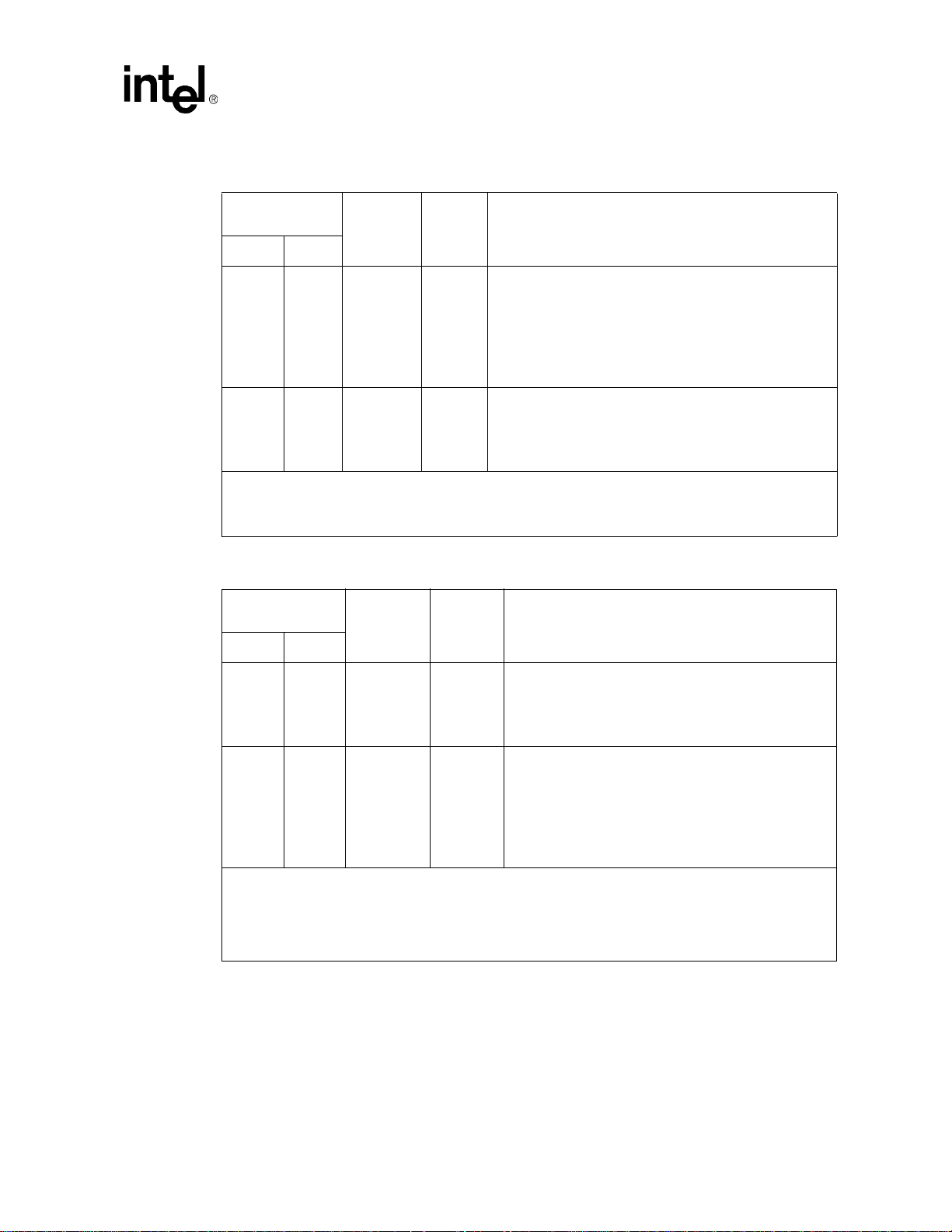

3.0 Pin/Ball Assignments and Signal Descriptions

3.1 PQFP Pin Assignments

The following sections show PQFP pin assignments and signal descriptions:

• Section 3.1.1, “PQFP Pin Assignments – RMII Configuration” on page 21

• Section 3.1.2, “PQFP Pin Assignments – SMII Configuration” on page 26

• Section 3.1.3, “PQFP Pin Assignments – SS-SMII Configuration” on page 31

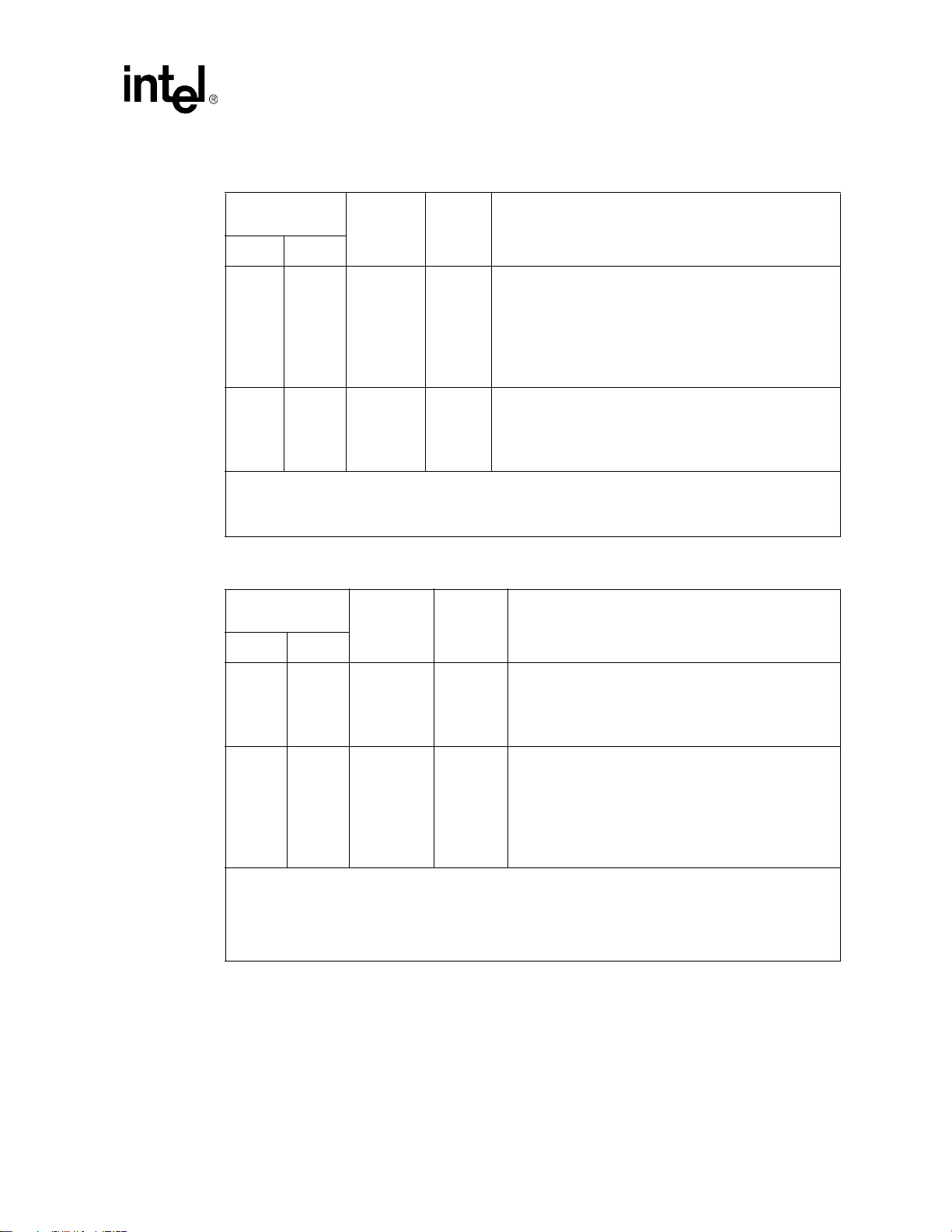

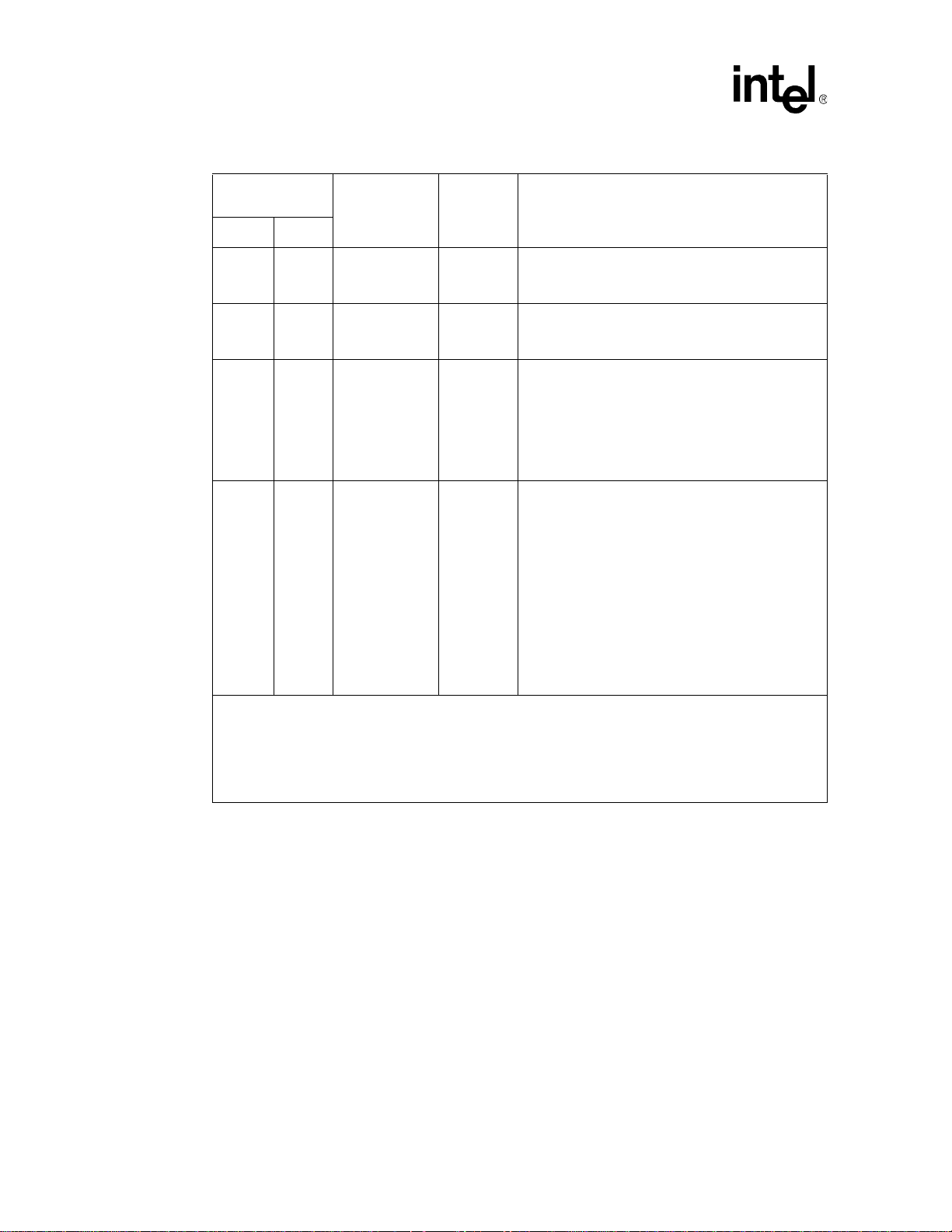

Table 1 lists the acronyms and descriptions for signal types.

Table 1. Intel

Acronym Description

®

LXT9785/LXT9785E Signal Type Descriptions

AI Analog Input

AO Analog Output

I Input

O Output

OD Open Drain Output

ST Schmitt Triggered Input

TS Three-State-able Output

SL Slew-rate Limited Output

IP Weak Internal Pull-Up

ID Weak Internal Pull-Down

20 Datasheet

Document Number: 249241

Revision Date: August 28, 2003

Revision Number: 007

Page 19

Intel® LXT9785 and Intel® LXT9785E Advanced 8-Port 10/100 Mbps PHY Transceivers

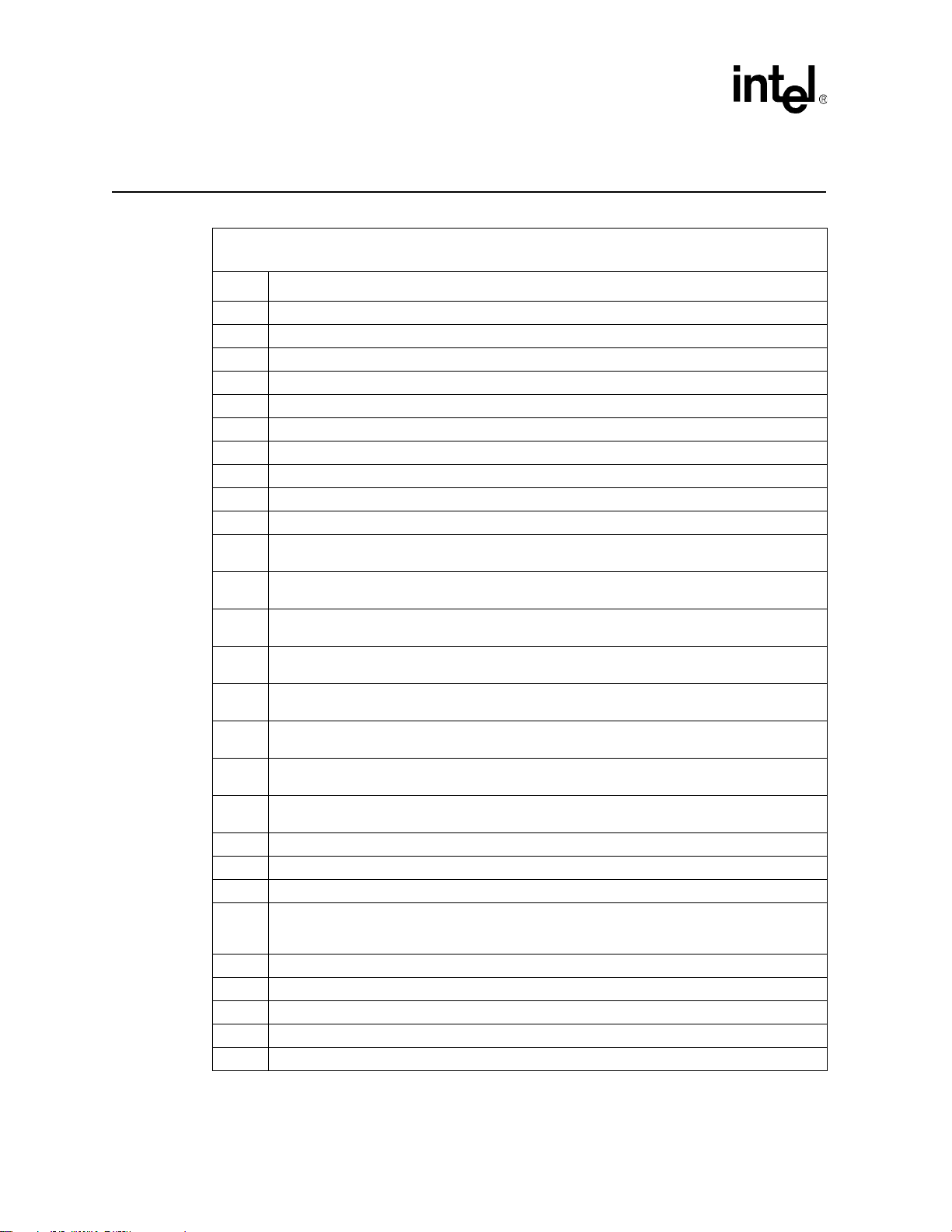

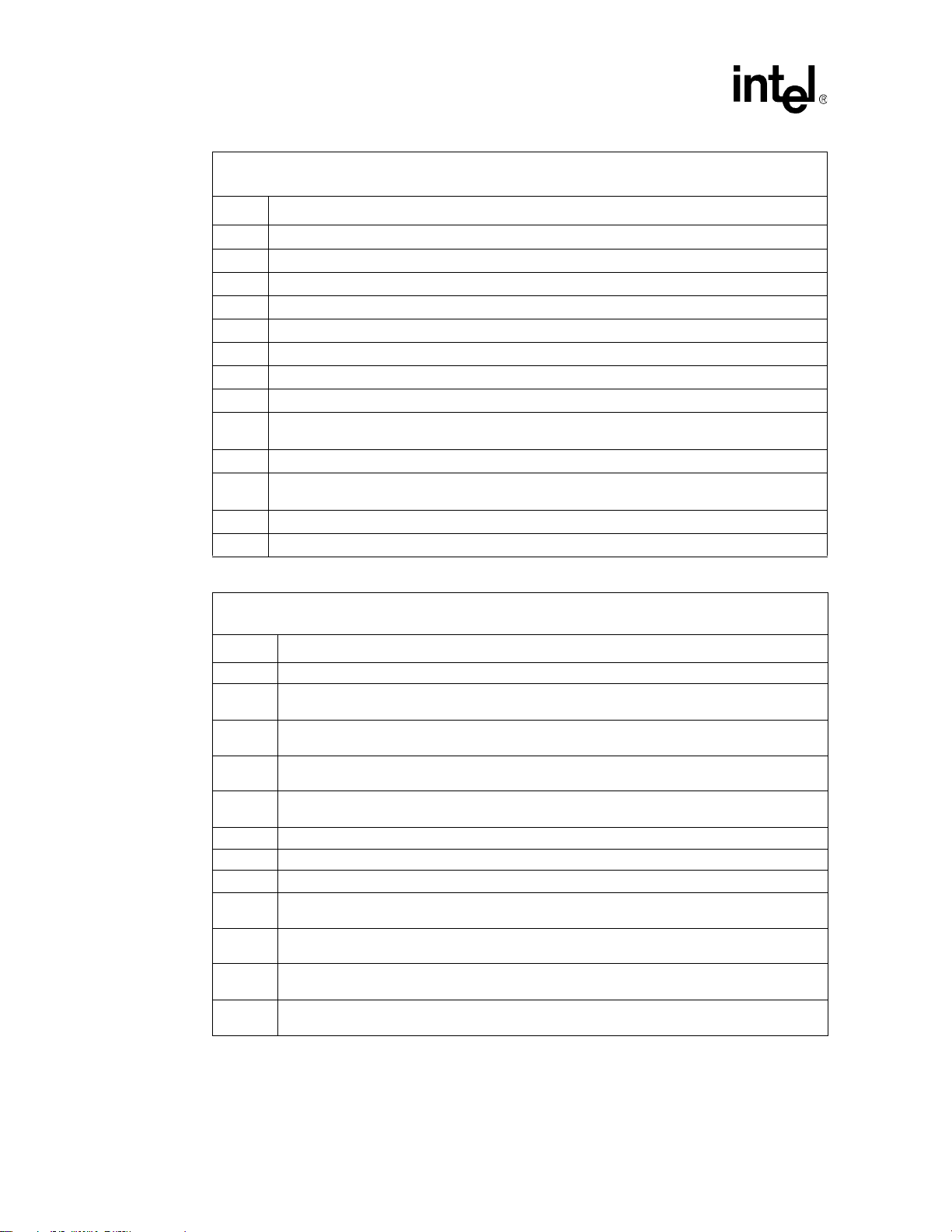

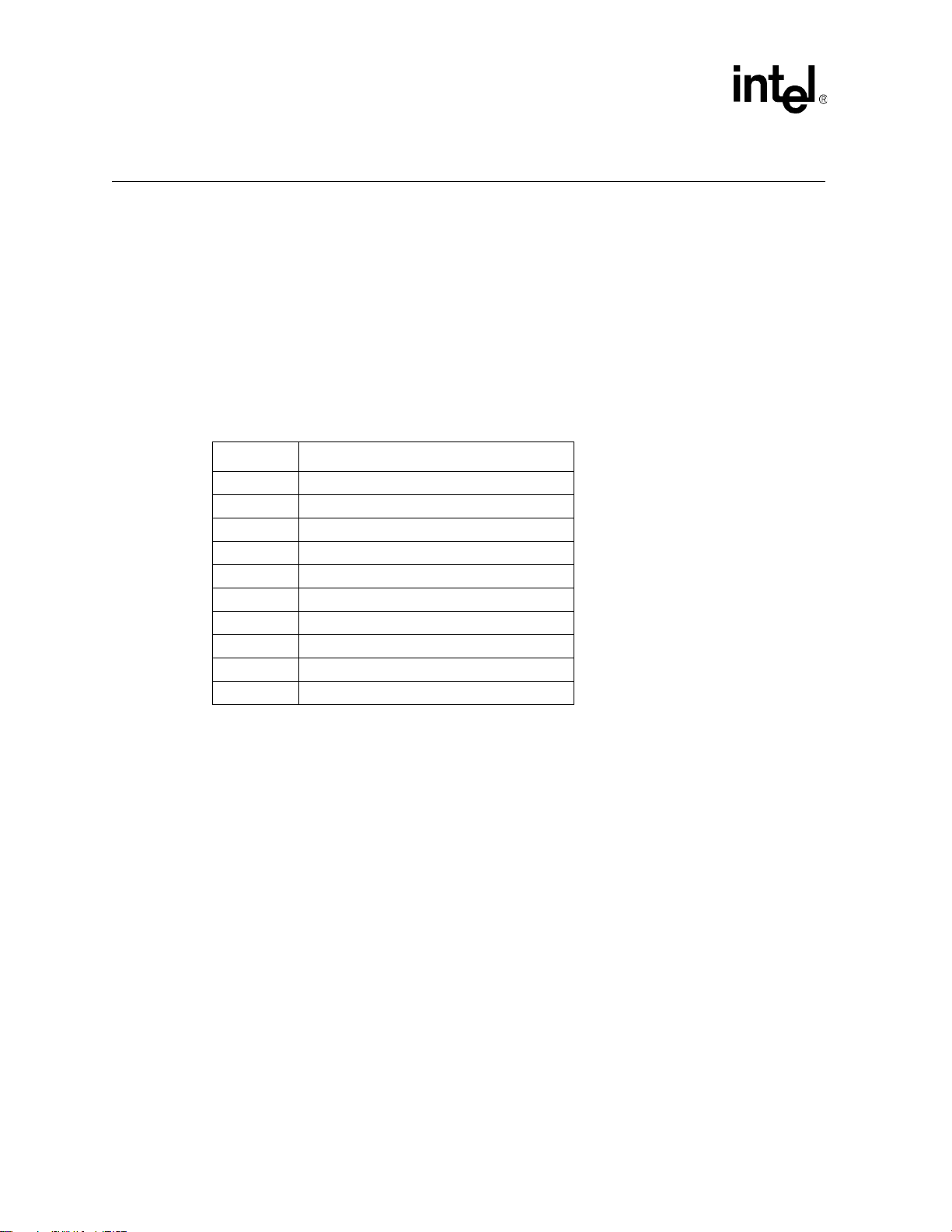

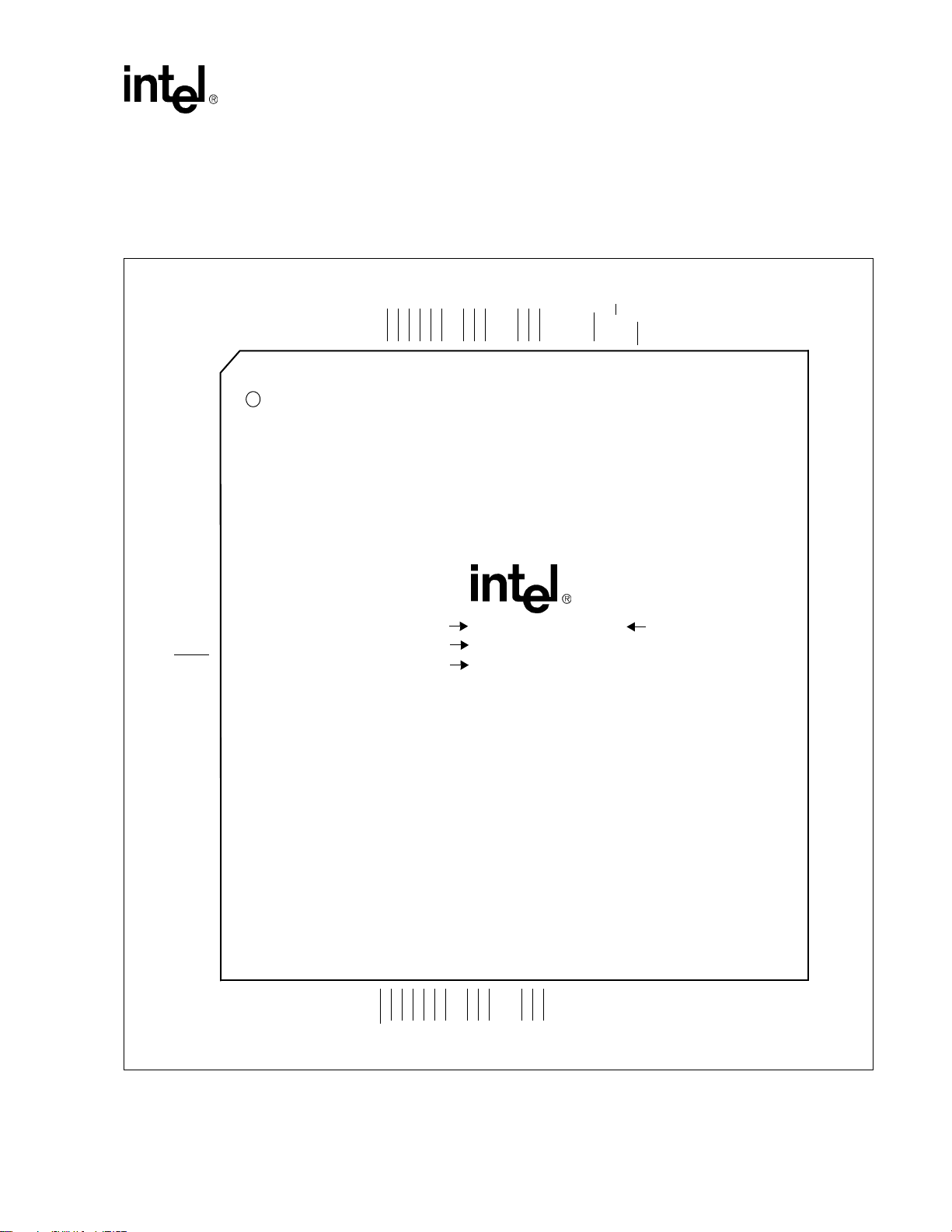

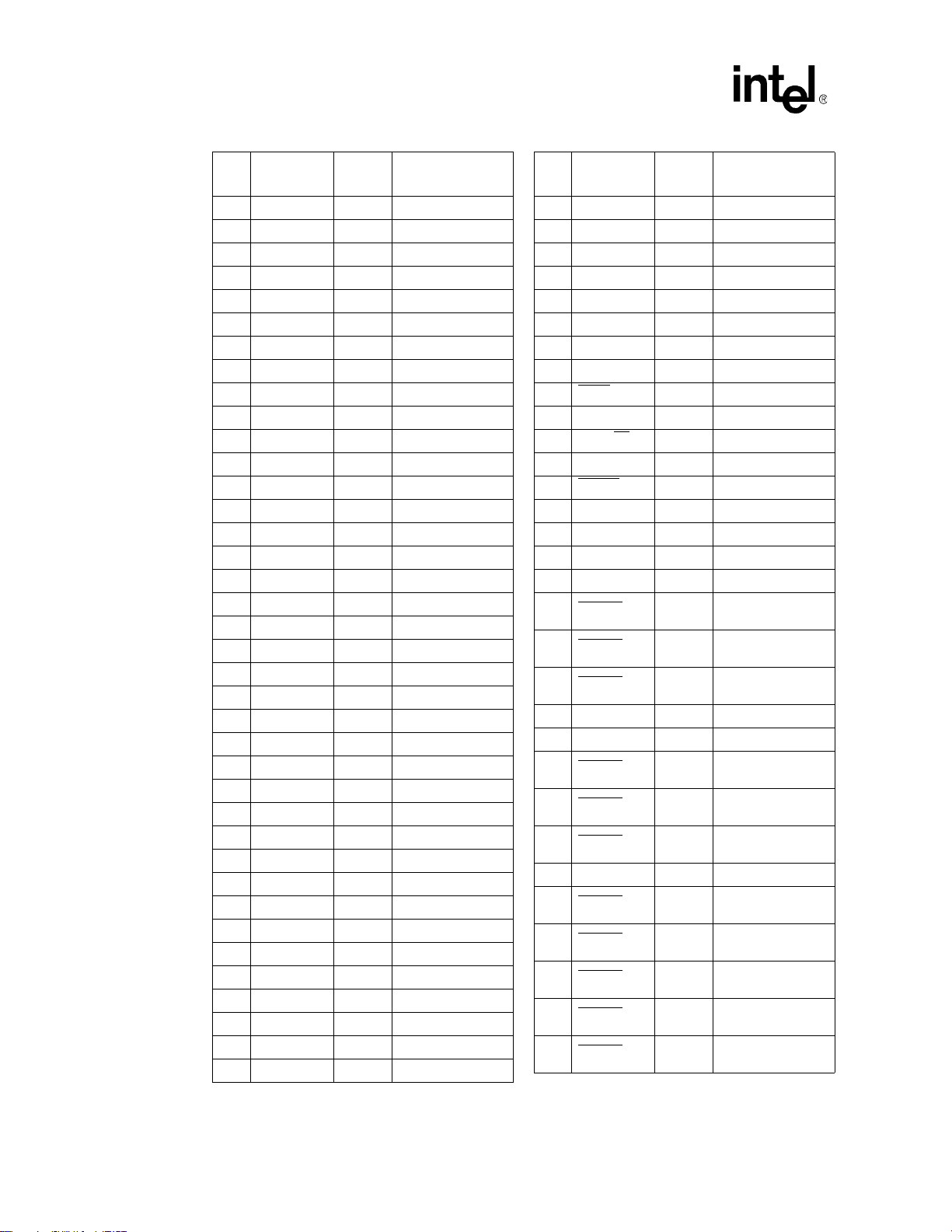

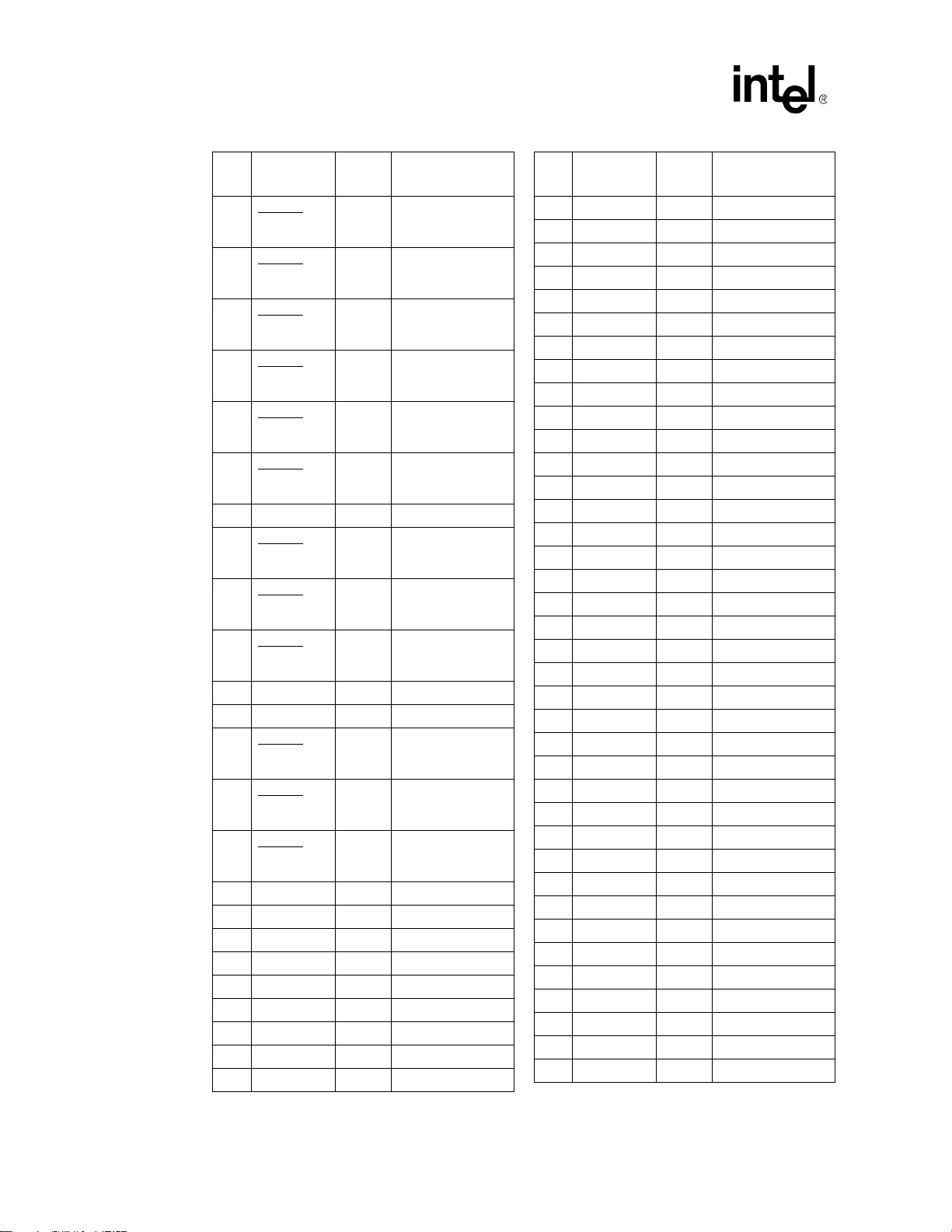

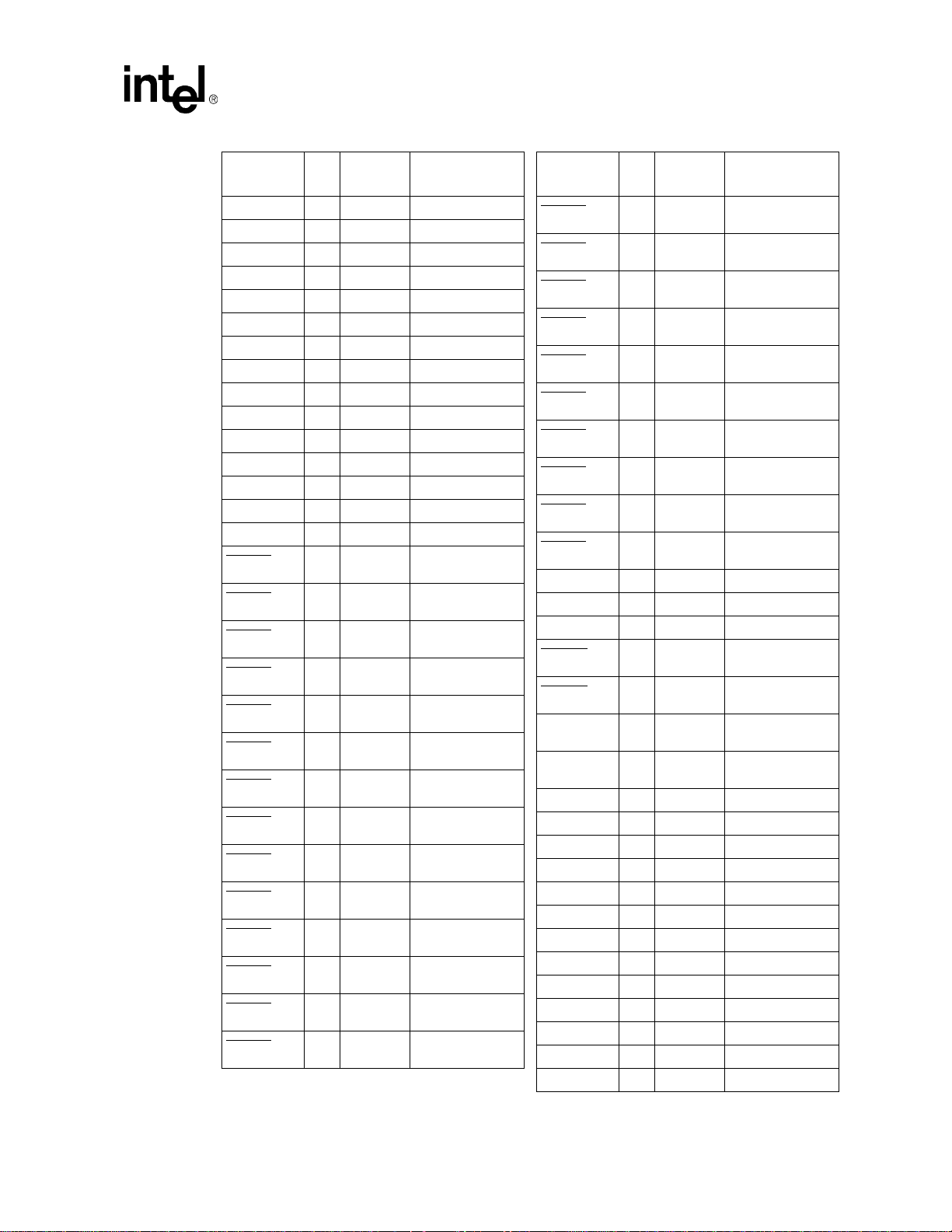

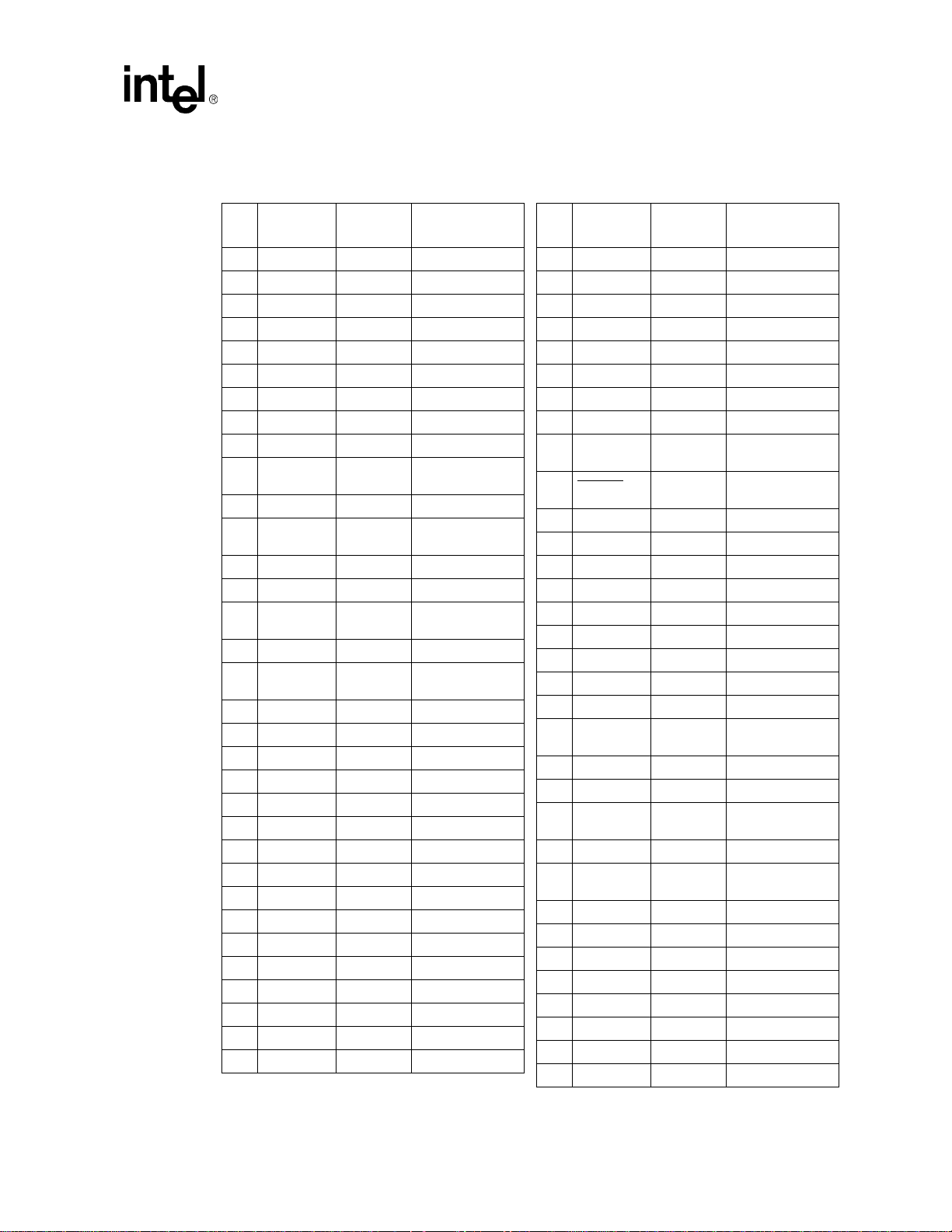

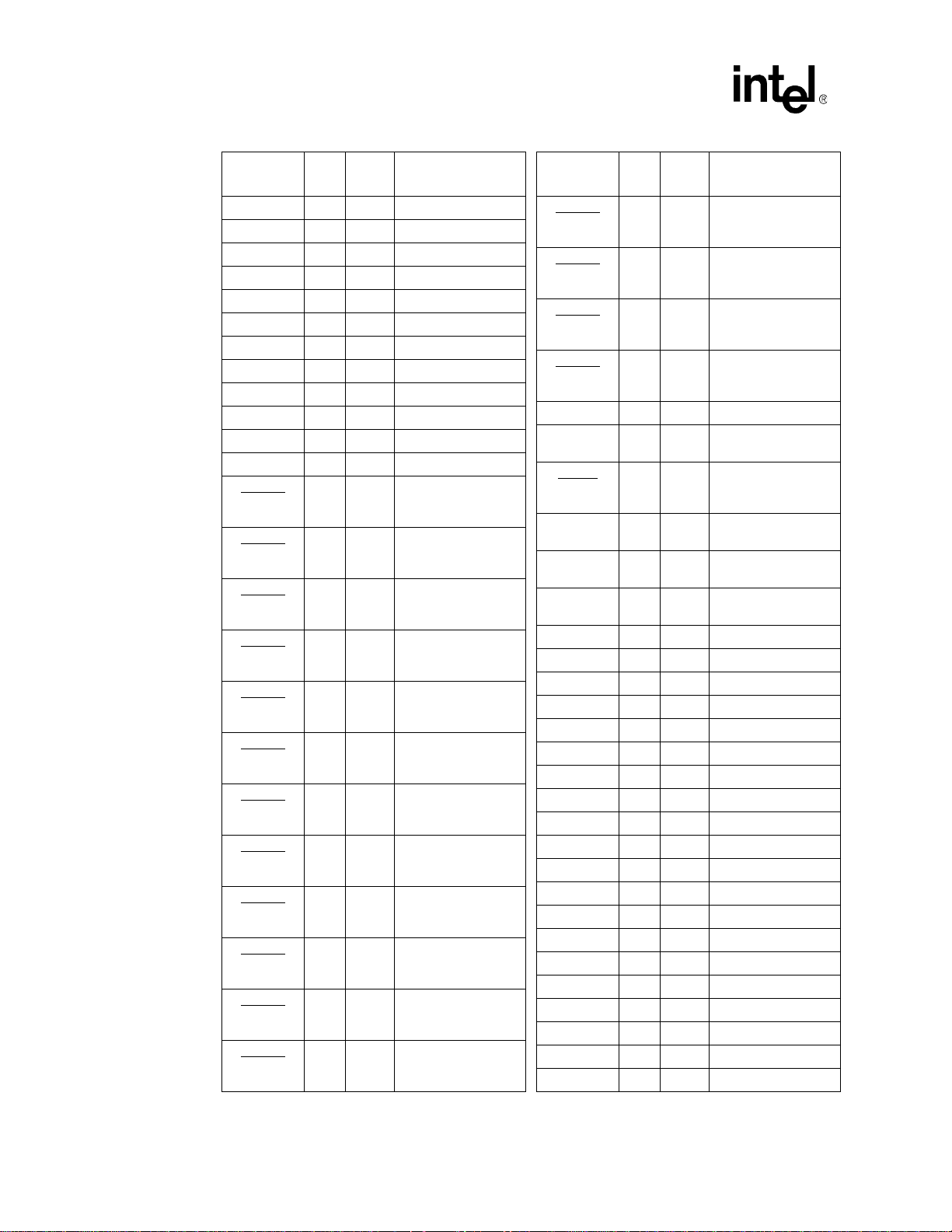

3.1.1 PQFP Pin Assignments – RMII Configuration

Figure 2 and Table 2, “Intel® LXT9785/LXT9785E RMII PQFP Pin List” on page 22 provide

LXT9785/LXT9785 RMII PQFP pin assignments.

Figure 2. Intel

CRS_DV6.......1

RxER6/LINKHOLD.. 2

TxEN6.......3

TxData6_0.......4

TxData6_1.......5

REFCLK1.......6

RxData5_1.......7

RxData5_0.......8

GNDIO.......9

CRS_DV5.......10

RxER5/FIFOSEL1.....11

TxEN5.......12

TxData5_0.......13

TxData5_1.......14

RxData4_1.......15

RxData4_0.......16

CRS_DV4.......17

VCCIO.......18

GNDIO.......19

RxER4/FIFOSEL0.....20

TxEN4.......21

TxData4_0.......22

TxData4_1.......23

MDC1.......24

MDIO1.......25

MDINT1.......26

RxData3_1.......27

RxData3_0.......28

VCCIO.......29

GNDIO.......30

CRS_DV3.......31

RxER3.......32

TxEN3.......33

TxData3_0.......34

TxData3_1.......35

RxData2_1.......36

RxData2_0.......37

GNDIO.......38

CRS_DV2.......39

RxER2/PREASEL .....40

TxEN2.......41

TxData2_0.......42

TxData2_1.......43

REFCLK0.......44

RxData1_1.......45

RxData1_0.......46

VCCIO.......47

GNDIO.......48

CRS_DV1.......49

RxER1/PAUSE.......50

TxEN1.......51

TxData1_0.......52

®

LXT9785 and Intel® LXT9785E RMII 208-Pin PQFP Assignments

208 ........ VCCIO

207 ........ GNDIO

206 ........ RxData6_0

205 ........ RxData6_1

204 ........ TxData7_1

203 ........ TxData7_0

202 ........ TxEN7

201 ........ RxER7

200 ........ CRS_DV7

199 ........ GNDIO

198 ........ RxData7_0

197 ........ RxData7_1

196 ........ VCCD

195 ........ GNDD

194 ........ LED7_3

193 ........ LED7_2

192 ........ LED7_1

191 ........ LED6_3

190 ........ LED6_2

189 ........ LED6_1

188 ........ GNDIO

187 ........ LED5_3

186 ........ LED5_2

185 ........ LED5_1

184 ........ VCCD

183 ........ GNDD

182 ........ LED4_3

181 ........ LED4_2

180 ........ LED4_1

179 ........ SGND

178 ........ ModeSel1

177 ........ ModeSel0

176 ........ Section

175 ........ RESET

Part #

LOT #

FPO #

LXT9785/9785E XX

XXXXXX

XXXXXXXX

174 ........ PWRDWN

173 ........ G_FX/TP

172 ........ N/C

171....... TRST

170 ........ TCK

169 ........ TMS

Rev #

168 ........ TDO

167 ........ TDI

166 ........ SD7

165 ........ SD6

164 ........ VCCPECL

163 ........ GNDPECL

162 ........ SD5

161 ........ SD4

160 ........ N/C

159 ........ N/C

158 ........ VCCR7

157 ........ TPFIP7

156 .........TPFIN7

155 .........GNDR7

154 .........TPFOP7

153 .........TPFON7

152 .........VCCT6/7

151 .........TPFON6

150 .........TPFOP6

149 .........GNDR6

148 .........GNDT6/7

147 .........TPFIN6

146 .........TPFIP6

145 .........VCCR6

144 .........VCCR5

143 .........TPFIP5

142 .........TPFIN5

141 .........GNDR5

140 .........TPFOP5

139 .........TPFON5

138 .........VCCT4/5

137 .........TPFON4

136 .........TPFOP4

135 .........GNDR4

134 .........GNDT4/5

133 .........TPFIN4

132 .........TPFIP4

131 .........VCCR4

130 .........VCCR3

129 .........TPFIP3

128 .........TPFIN3

127 .........GNDT2/3

126 .........GNDR3

125 .........TPFOP3

124 .........TPFON3

123 .........VCCT2/3

122 .........TPFON2

121 .........TPFOP2

120 .........GNDR2

119 .........TPFIN2

118 .........TPFIP2

117 .........VCCR2

116 .........VCCR1

115 .........TPFIP1

114 .........TPFIN1

113 .........GNDT0/1

112 .........GNDR1

111 .........TPFOP1

110 .........TPFON1

109 .........VCCT0/1

108 .........TPFON0

107 .........TPFOP0

106 .........GNDR0

105 .........TPFIN0

SD0 ...... 96

MDC0 ...... 63

VCCD ...... 65

TxEN0 ...... 60

VCCIO ...... 56

GNDIO ...... 57

TxData1_1 ...... 53

CRS_DV0 ...... 58

RxData0_1 ...... 54

RxData0_0 ...... 55

TxData0_0 ...... 61

RxER0/MDIX ...... 59

GNDD ...... 66

MDIO0 ...... 64

LED3_3 ......68

LED3_2 ......69

LED3_1 ......70

LED2_3 ......71

LED2_2 ......72

TxData0_1 ...... 62

MDINT0 ......67

LED2_1 ......73

VCCD ...... 78

GNDIO ...... 74

GNDD ...... 79

LED1_3 ......75

LED1_2 ......76

LED1_1 ......77

LED0_3 ......80

CFG_3 ...... 85

CFG_2 ...... 86

CFG_1 ...... 87

ADD_4 ......88

ADD_3 ......89

ADD_2 ......90

ADD_1 ......91

MDDIS ...... 84

LED0_2 ......81

LED0_1 ......82

AMDIX_EN ...... 83

ADD_0 ......92

SD1 ...... 97

SD_2P5V ...... 95

TxSlew_1 ...... 93

TxSlew_0 ...... 94

N/C ...... 102

SD2 ...... 100

SD3 ...... 101

TPFIP0 ...... 104

VCCPECL ...... 98

VCCR0 ...... 103

GNDPECL ...... 99

Datasheet 21

Document Number: 249241

Revision Number: 007

Revision Date: August 28, 2003

Page 20

Intel® LXT9785 and Intel® LXT9785E Advanced 8-Port 10/100 Mbps PHY Transceivers

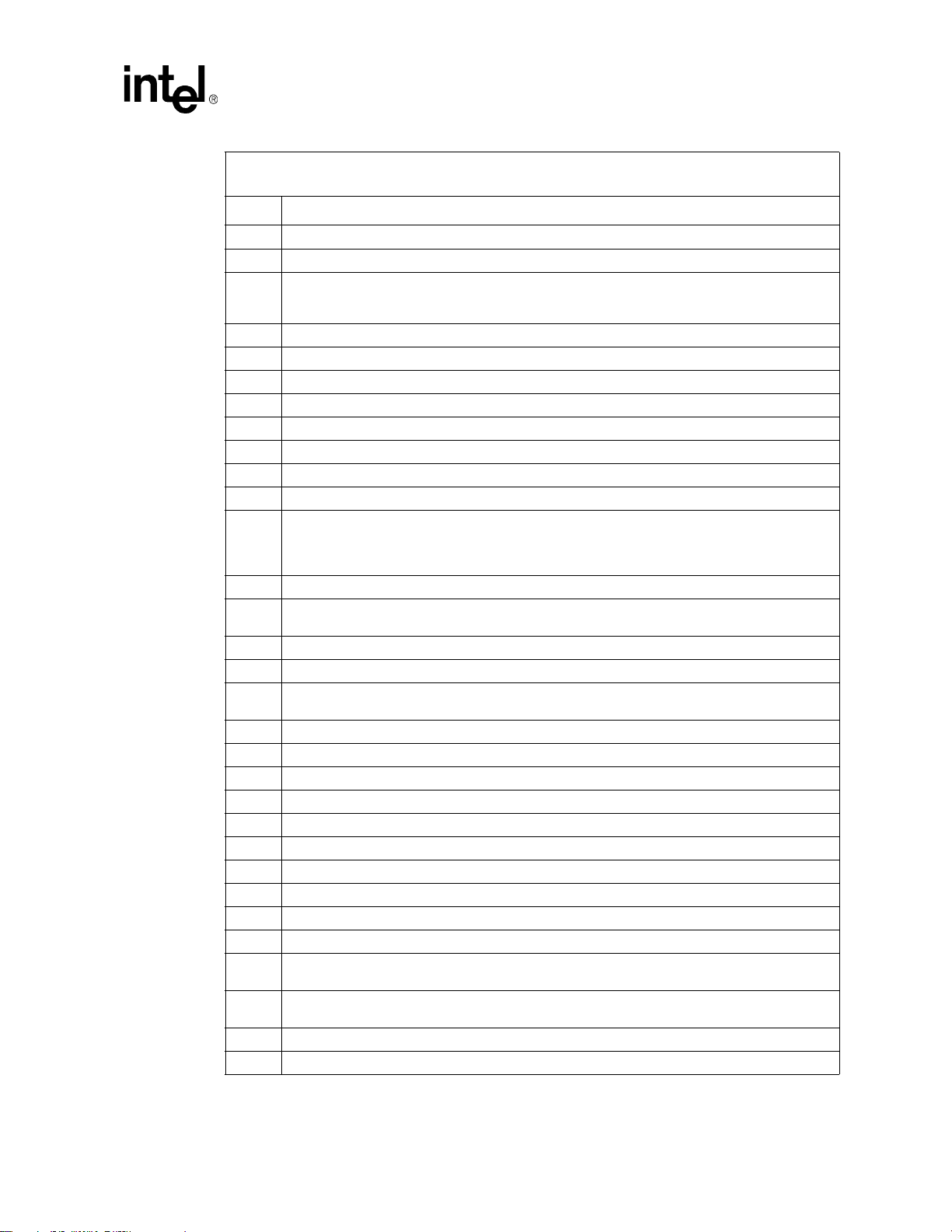

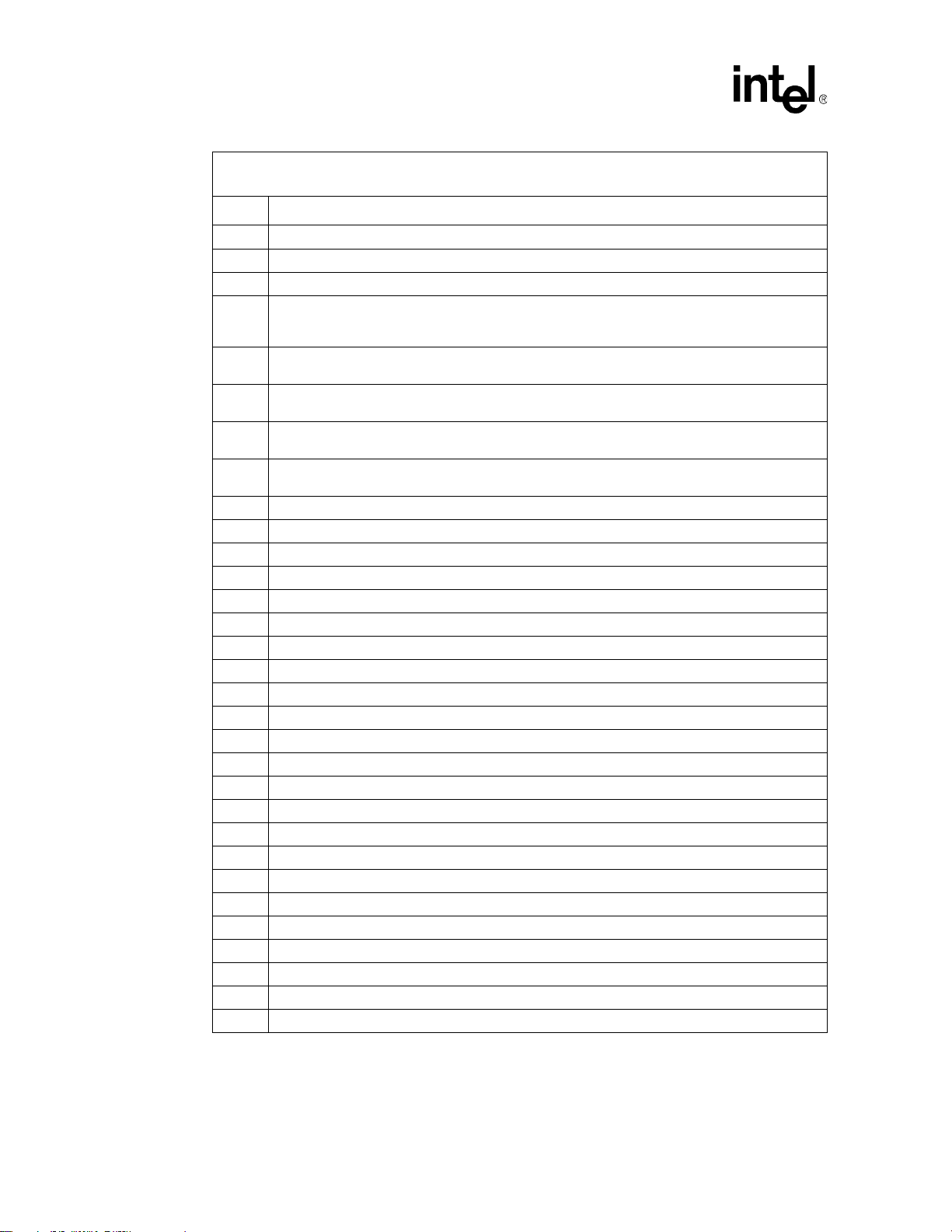

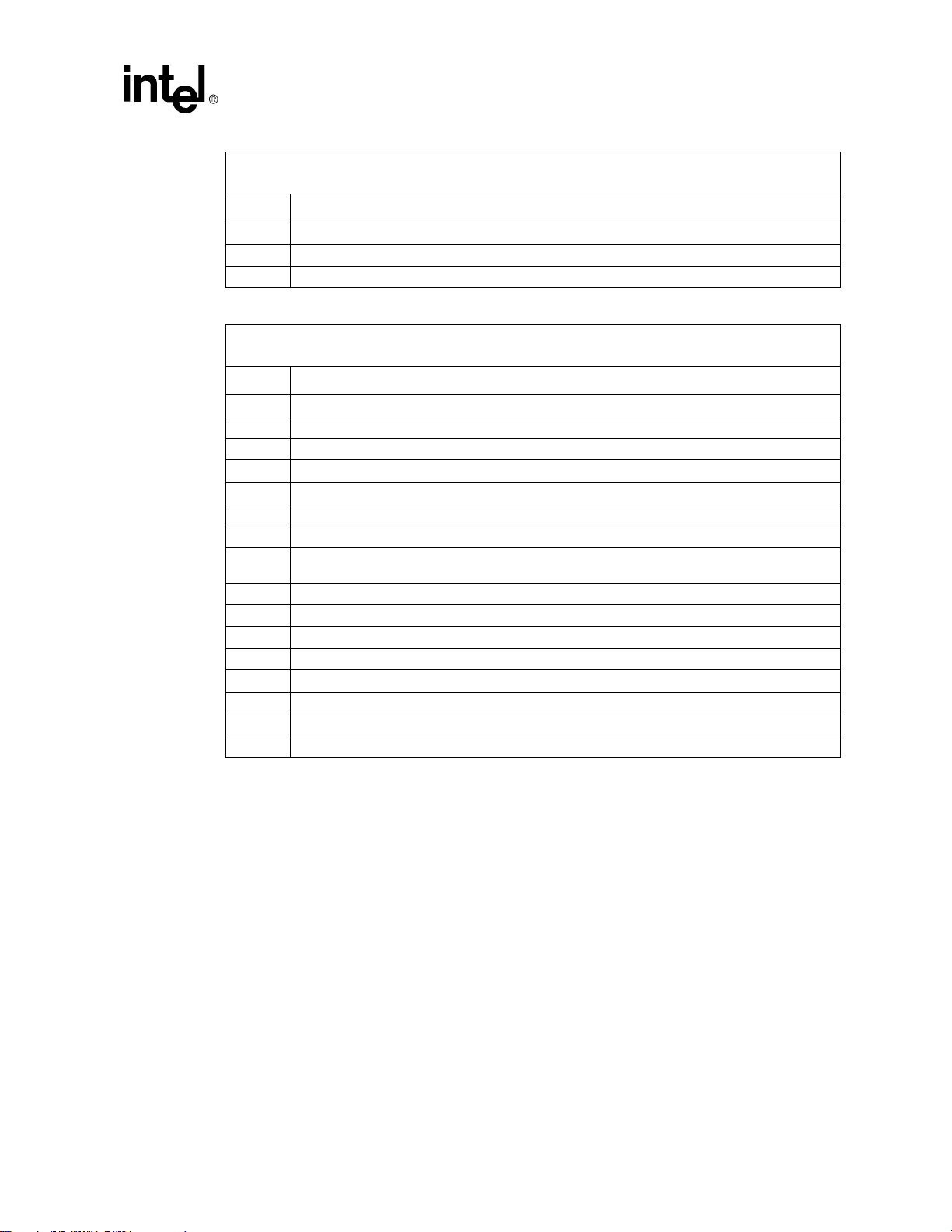

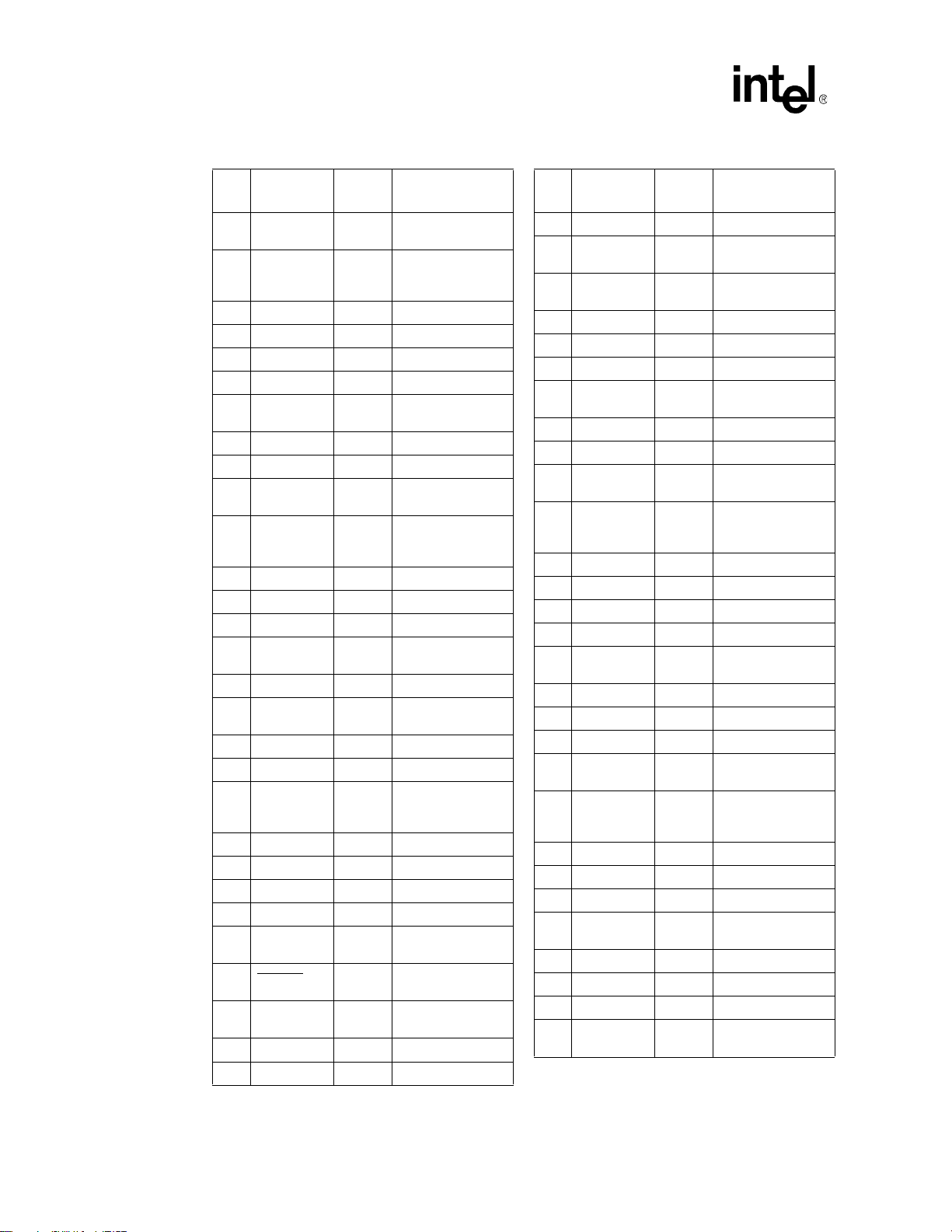

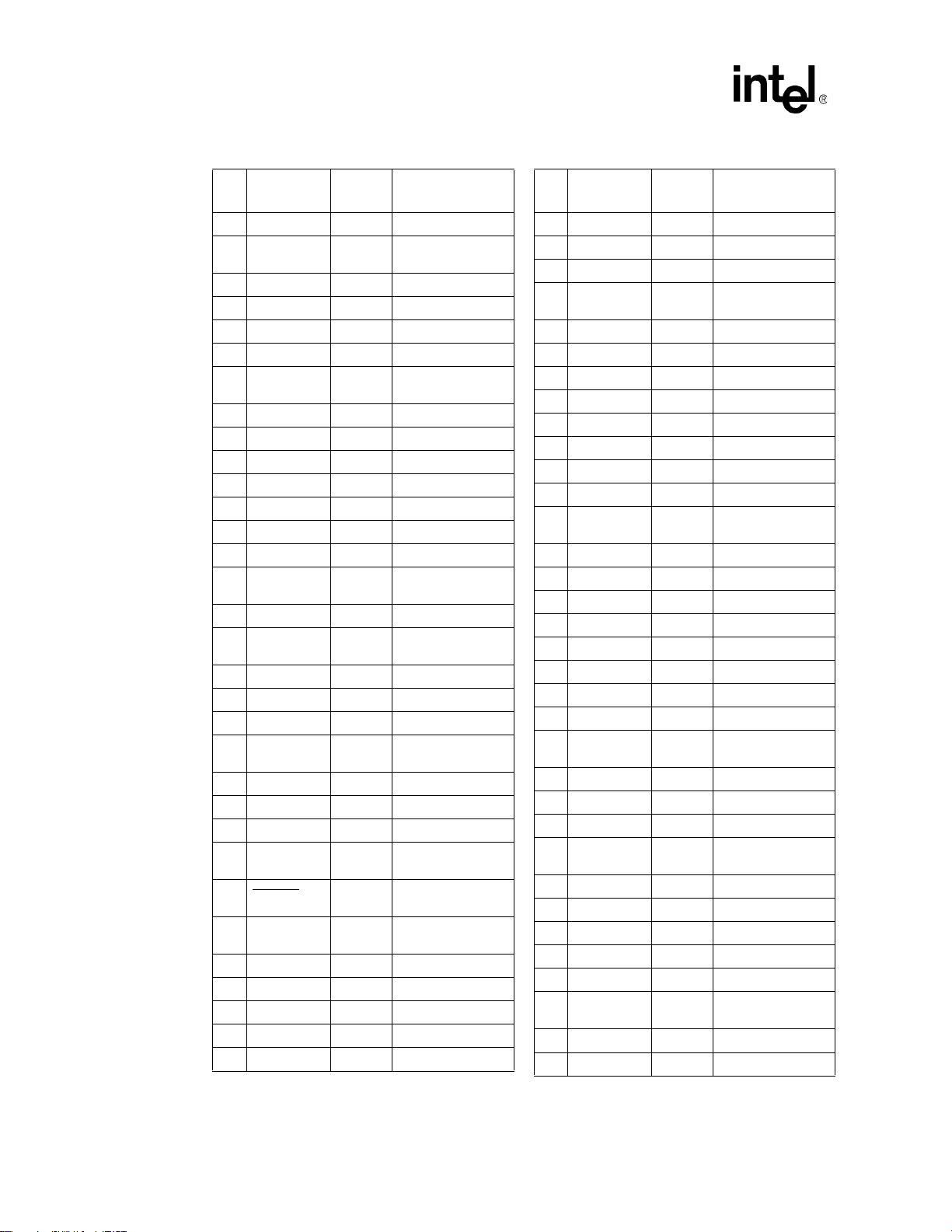

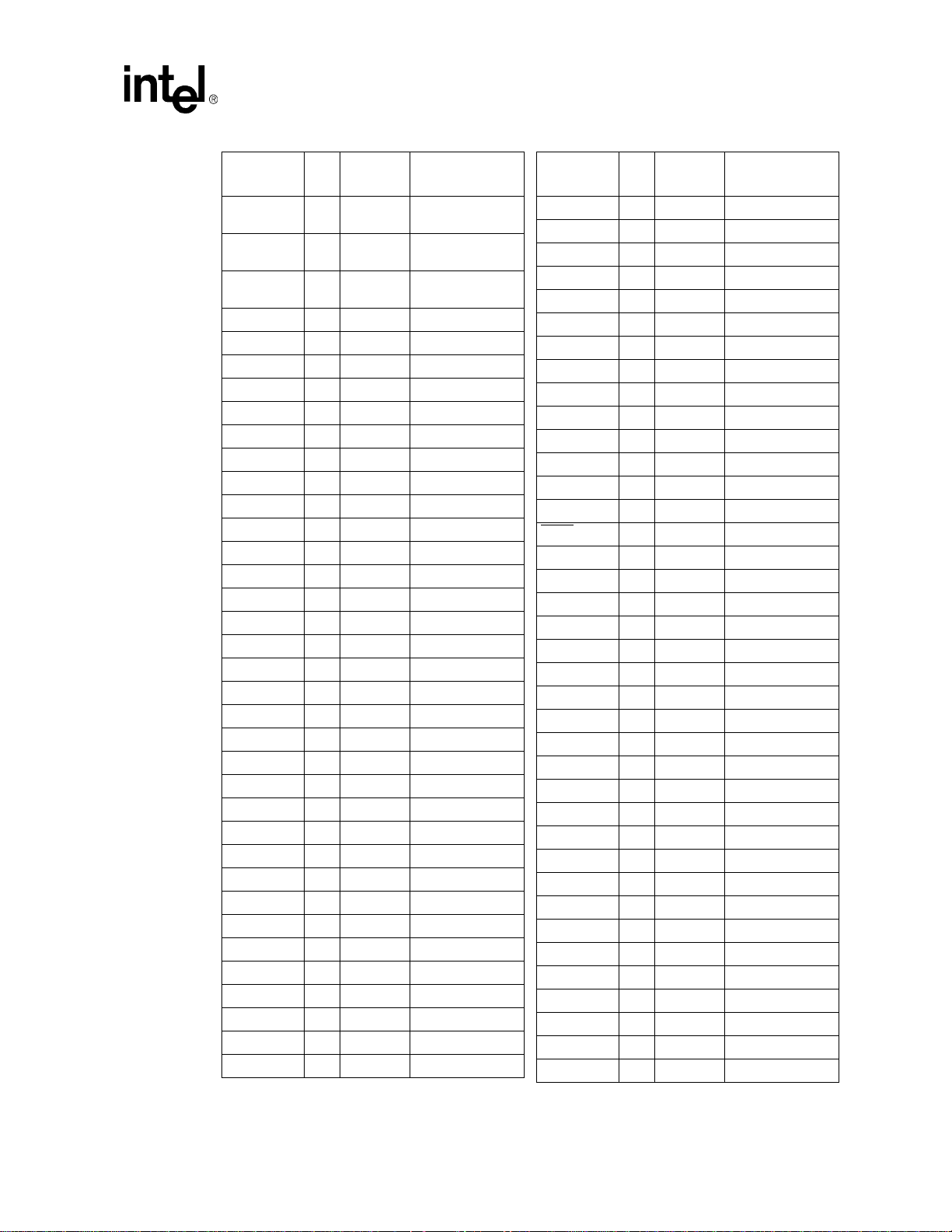

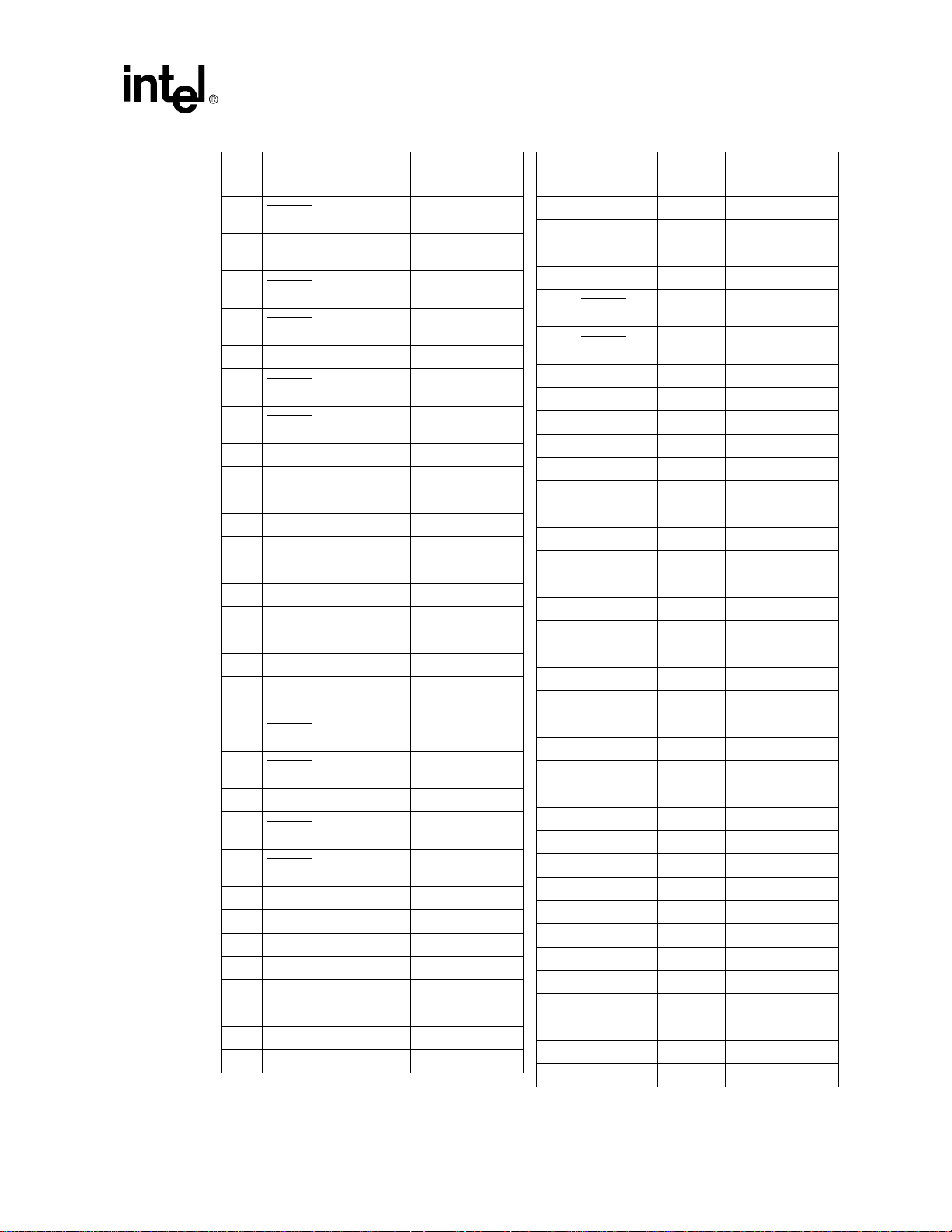

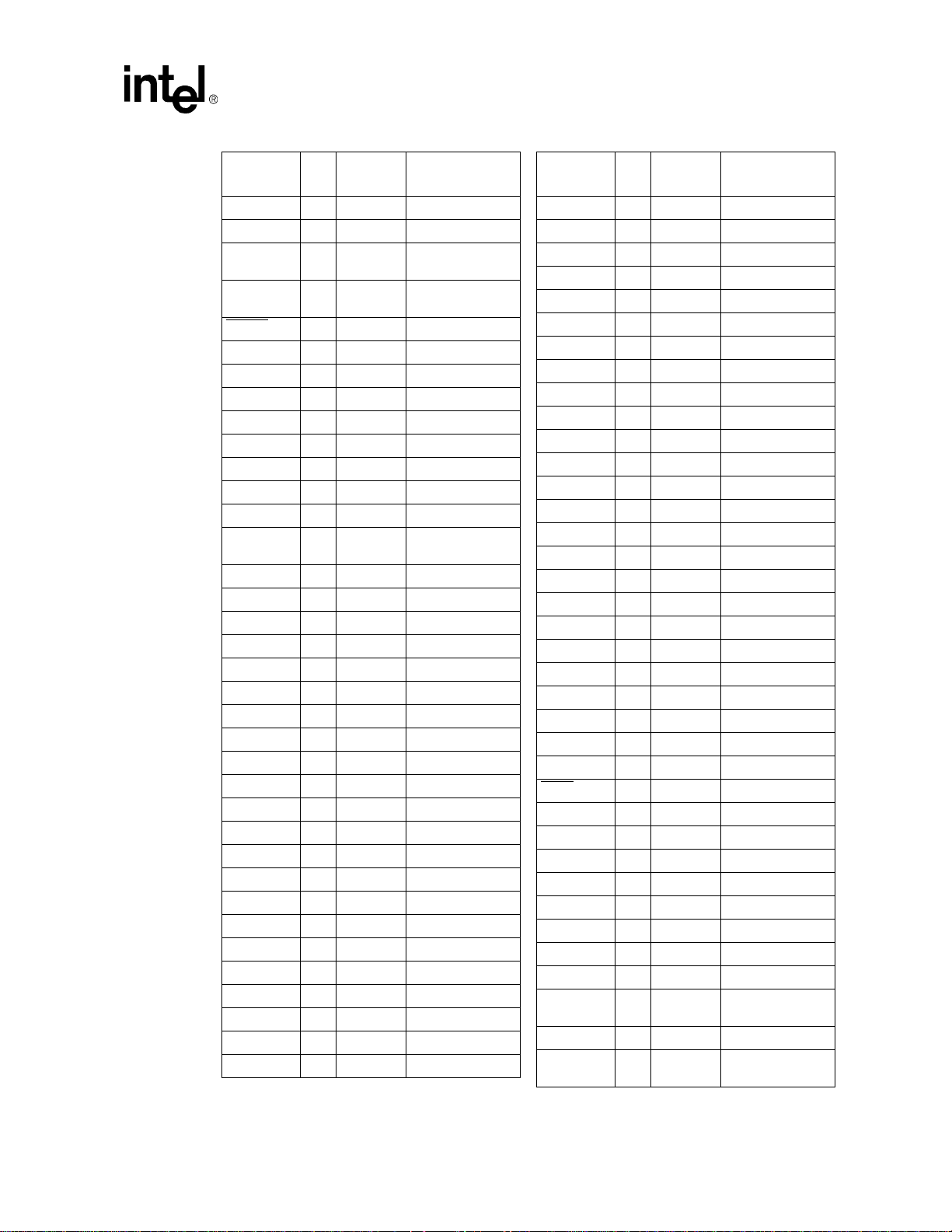

Table 2. Intel® LXT9785/LXT9785E RMII PQFP Pin List

Pin Symbol Type

Reference for Full

Description

Pin Symbol Type

Reference for Full

Description

1 CRS_DV6

RxER6/

2

LINKHOLD

3 TxEN6 I, ID Table 5 (page 36)

4 TxData6_0 I, ID Table 5 (page 36)

5 TxData6_1 I, ID Table 5 (page 36)

6 REFCLK1 I Table 5 (page 36)

7 RxData5_1

8 RxData5_0 O, TS Table 5 (page 36)

9GNDIO – Table 15 (page 48)

10 CRS_DV5

RxER5 /

11

FIFOSEL1

12 TxEN5 I, ID Table 5 (page 36)

13 TxData5_0 I, ID Table 5 (page 36)

14 TxData5_1 I, ID Table 5 (page 36)

15 RxData4_1

16 RxData4_0 O, TS Table 5 (page 36)

17 CRS_DV4

18 VCCIO – Table 15 (page 48)

19 GNDIO – Table 15 (page 48)

RxER4 /

20

FIFOSEL0

21 TxEN4 I, ID Table 5 (page 36)

22 TxData4_0 I, ID Table 5 (page 36)

23 TxData4_1 I, ID Table 5 (page 36)

24 MDC1 I, ST, ID Table 8 (page 40)

25 MDIO1

26 MDINT1

27 RxData3_1

28 RxData3_0 O, TS Table 5 (page 36)

29 VCCIO – Table 15 (page 48)

O, TS,

SL

O, TS,

SL, ID,

I, ST

O, TS,

ID

O, TS,

SL

O, TS,

SL, ID,

I, ST

O,

TS,ID

O, TS,

SL

O, TS,

SL, ID,

I, ST

I/O, TS,

SL, IP

OD, TS,

SL, IP

O, TS,

ID

Table 5 (page 36)

Table 5 (page 36)

Table 5 (page 36)

Table 5 (page 36)

Table 5 (page 36)

Table 5 (page 36)

Table 5 (page 36)

Table 5 (page 36)

Table 8 (page 40)

Table 8 (page 40)

Table 5 (page 36)

30 GNDIO – Table 15 (page 48)

31 CRS_DV3

32 RxER3

33 TxEN3 I, ID Table 5 (page 36)

34 TxData3_0 I, ID Table 5 (page 36)

35 TxData3_1 I, ID Table 5 (page 36)

36 RxData2_1

37 RxData2_0 O, TS Table 5 (page 36)

38 GNDIO – Table 15 (page 48)

39 CRS_DV2

RxER2

40

(PREASEL)

41 TxEN2 I, ID Table 5 (page 36)

42 TxData2_0 I, ID Table 5 (page 36)

43 TxData2_1 I, ID Table 5 (page 36)

44 REFCLK0 I Table 5 (page 36)

45 RxData1_1

46 RxData1_0 O, TS Table 5 (page 36)

47 VCCIO – Table 15 (page 48)

48 GNDIO – Table 15 (page 48)

49 CRS_DV1

RxER1/

50

PAU SE

51 TxEN1 I, ID Table 5 (page 36)

52 TxData1_0 I, ID Table 5 (page 36)

53 TxData1_1 I, ID Table 5 (page 36)

54 RxData0_1

55 RxData0_0 O, TS Table 5 (page 36)

56 VCCIO – Table 15 (page 48)

57 GNDIO – Table 15 (page 48)

58 CRS_DV0

O, TS,

SL

O, TS,

SL, ID

O, TS,

ID

O, TS,

SL

O, TS,

SL, ID,

I, ST

O, TS,

ID

O, TS,

SL

O, TS,

SL, ID,

I, ST

O, TS,

ID

O, TS,

SL

Table 5 (page 36)

Table 5 (page 36)

Table 5 (page 36)

Table 5 (page 36)

Table 5 (page 36)

Table 5 (page 36)

Table 5 (page 36)

Table 5 (page 36)

Table 5 (page 36)

Table 5 (page 36)

22 Datasheet

Document Number: 249241

Revision Date: August 28, 2003

Revision Number: 007

Page 21

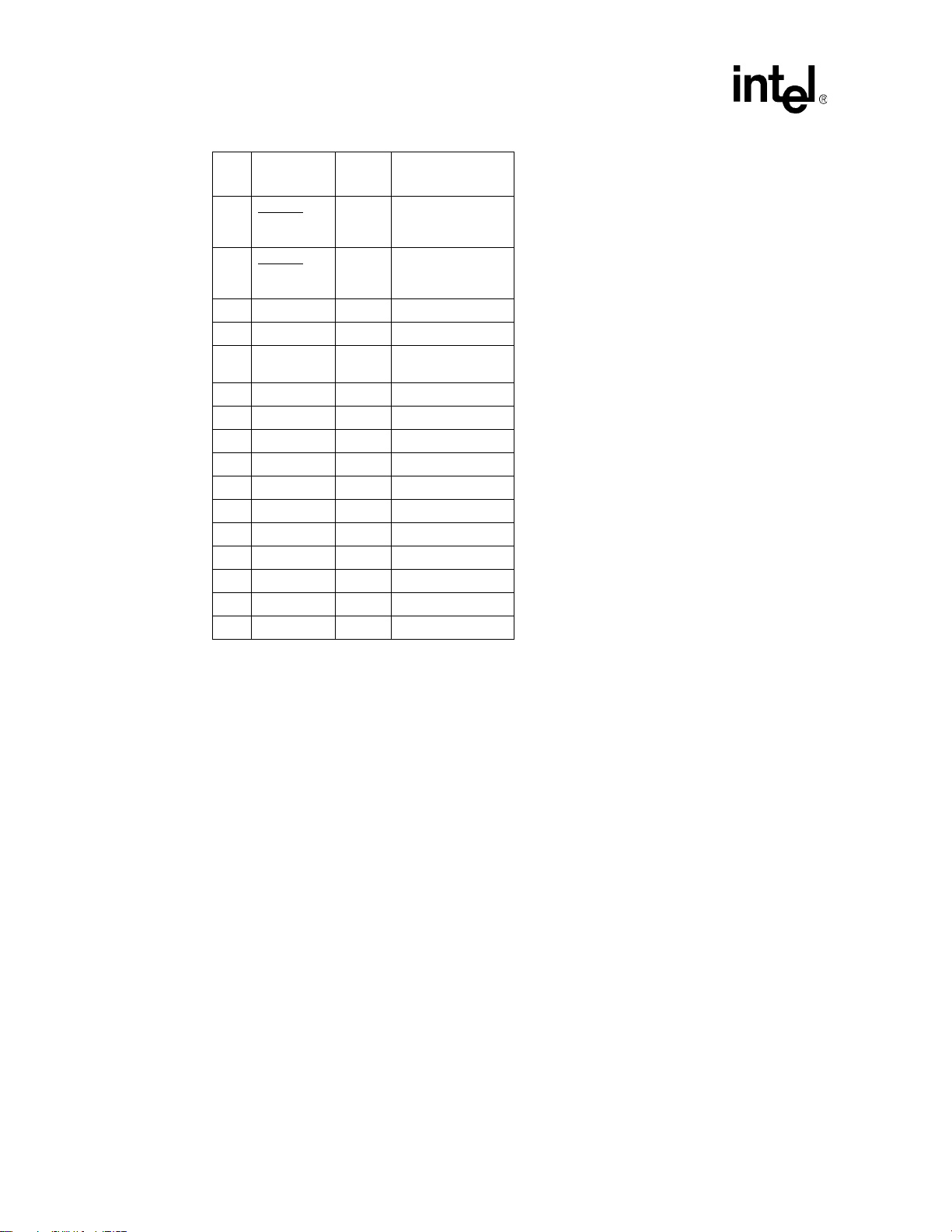

Intel® LXT9785 and Intel® LXT9785E Advanced 8-Port 10/100 Mbps PHY Transceivers

Pin Symbol Type

RxER0/

59

MDIX

60 TxEN0 I, ID Table 5 (page 36)

61 TxData0_0 I, ID Table 5 (page 36)

62 TxData0_1 I, ID Table 5 (page 36)

63 MDC0 I, ST, ID Table 8 (page 40)

64 MDIO0

65 VCCD – Table 15 (page 48)

66 GNDD – Table 15 (page 48)

67 MDINT0

68 LED3_3

69 LED3_2

70 LED3_1

71 LED2_3

72 LED2_2

73 LED2_1

74 GNDIO – Table 15 (page 48)

75 LED1_3

76 LED1_2

77 LED1_1

78 VCCD – Table 15 (page 48)

79 GNDD – Table 15 (page 48)

80 LED0_3

81 LED0_2

82 LED0_1

83 AMDIX_EN I, ST, IP Table 13 (page 43)

84 MDDIS I, ST, ID Table 9 (page 41)

85 CFG_3 I, ST, ID Table 13 (page 43)

86 CFG_2 I, ST, ID Table 13 (page 43)

O, TS,

SL, ID,

I, ST

I/O, TS,

SL, IP

OD, TS,

SL, IP

OD, TS,

SO, IP

OD, TS,

SL, IP

OD, TS,

SL, IP

OD, TS,

SL, IP

OD, TS,

SL, IP

OD, TS,

SL, IP

OD, TS,