Page 1

Intel® 5000 Series Chipsets

Server Board Family

Datasheet

Intel order number D38960-004

Revision 1.1

June 01, 2006

Enterprise Platforms and Services Division

Page 2

Revision History Intel® 5000 Series Chipsets Server Board Family Datasheet

Revision History

Date Revision

Number

31 May 06 1.1 Initial Document Release.

Modifications

Revision 1.1

ii

Intel order number D38960-004

Page 3

Intel® 5000 Series Chipsets Server Board Family Datasheet Disclaimers

Disclaimers

Information in this document is provided in connection with Intel® products. No license, express

or implied, by estoppel or otherwise, to any intellectual property rights is granted by this

document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel

assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to

sale and/or use of Intel products including liability or warranties relating to fitness for a particular

purpose, merchantability, or infringement of any patent, copyright or other intellectual property

right. Intel products are not intended for use in medical, life saving, or life sustaining

applications. Intel may make changes to specifications and product descriptions at any time,

without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked

"reserved" or "undefined." Intel reserves these for future definition and shall have no

responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel® 5000 Series Chipsets Server Board Family Datasheet may contain design defects or

errors known as errata which may cause the product to deviate from published specifications.

Current characterized errata are available on request.

The information in this manual is furnished for informational use only, is subject to change

without notice, and should not be construed as a commitment by Intel Corporation. Intel

Corporation assumes no responsibility or liability for any errors or inaccuracies that may appear

in this document or any software that may be provided in association with this document.

Intel, Pentium, Itanium, and Xeon are trademarks or registered trademarks of Intel Corporation.

*Other brands and names may be claimed as the property of others.

Copyright © Intel Corporation 2006. All rights reserved.

Revision 1.1

Intel order number D38960-004

iii

Page 4

Table of Contents Intel® 5000 Series Chipsets Server Board Family Datasheet

Table of Contents

1. Introduction...........................................................................................................................1

1.1 Server Product References......................................................................................1

1.2 Chapter Outline........................................................................................................1

2. Functional Architecture .......................................................................................................2

2.1 Intel® 5000 MCH Components.................................................................................4

2.1.1 Memory Controller Hub (Intel® 5000 MCH)..............................................................4

2.1.2 Intel® 631xESB / 632xESB I/O Controller Hub (ESB2) ............................................7

2.2 Processor Sub-system...........................................................................................11

2.2.1 Processor Support .................................................................................................12

2.2.2 Processor Population Rules...................................................................................12

2.2.3 Processor EVRD....................................................................................................12

2.2.4 GTL2007................................................................................................................12

2.2.5 Common Enabling Kit (CEK) Design Support........................................................12

2.3 Memory Sub-system..............................................................................................13

2.3.1 Fully-buffered DIMM (FBDIMM).............................................................................14

2.3.2 Supported Memory.................................................................................................15

2.4 I/O Sub-system ......................................................................................................17

2.4.1 PCI Sub-system.....................................................................................................17

2.4.2 Scan Order.............................................................................................................17

2.4.3 Resource Assignment............................................................................................17

2.4.4 Automatic IRQ Assignment....................................................................................17

2.4.5 Legacy Option ROM Support.................................................................................18

2.4.6 EFI PCI APIs..........................................................................................................18

2.4.7 Legacy PCI APIs....................................................................................................18

2.4.8 Dual Video..............................................................................................................18

2.4.9 Parallel ATA (PATA) Support.................................................................................18

2.4.10 Serial ATA (SATA) Support....................................................................................19

2.4.11 SATA RAID Functionality.......................................................................................20

2.4.12 Serial Attached SCSI .............................................................................................20

2.4.13 Video Controller .....................................................................................................20

2.4.14 Network Interface Controller (NIC).........................................................................20

2.4.15 USB Support..........................................................................................................20

Revision 1.1

iv

Intel order number D38960-004

Page 5

Intel® 5000 Series Chipsets Server Board Family Datasheet Table of Contents

2.4.16 Native USB Support...............................................................................................21

2.4.17 Legacy USB Support..............................................................................................21

2.4.18 Super I/O................................................................................................................21

2.4.19 BIOS Flash.............................................................................................................22

2.5 Clock Generation and Distribution .........................................................................23

3. System BIOS .......................................................................................................................24

3.1 BIOS Identification String.......................................................................................24

3.2 Processors.............................................................................................................25

3.2.1 CPUID....................................................................................................................25

3.2.2 Multiple Processor Initialization..............................................................................25

3.2.3 Mixed Processor Steppings ...................................................................................26

3.2.4 Mixed Processor Families......................................................................................26

3.2.5 Mixed Processor System Bus Speeds...................................................................26

3.2.6 Mixed Processor Cache Sizes...............................................................................26

3.2.7 Microcode Update..................................................................................................26

3.2.8 Processor Cache....................................................................................................26

3.2.9 Mixed Processor Configuration..............................................................................26

3.2.10 Hyper-Threading Technology.................................................................................28

3.2.11 Intel SpeedStep® Technology ................................................................................28

3.2.12 Intel® Extended Memory 64 Technology (Intel® EM64T)........................................28

3.2.13 Execute Disable Bit Feature...................................................................................29

3.2.14 Enhanced Halt State (C1E)....................................................................................29

3.2.15 Multi-Core Processor Support................................................................................29

3.2.16 Intel® Virtualization Technology..............................................................................30

3.2.17 Acoustical Fan Speed Control................................................................................30

3.3 Memory..................................................................................................................30

3.3.1 Memory Sizing and Configuration..........................................................................30

3.3.2 POST Error Codes.................................................................................................31

3.3.3 Publishing System Memory....................................................................................31

3.3.4 Mixed Speed Memory Modules..............................................................................32

3.3.5 Memory Test ..........................................................................................................33

3.3.6 Memory Scrub Engine............................................................................................33

3.3.7 Memory Map and Population Rules.......................................................................34

3.3.8 Memory Modes of Operation..................................................................................36

3.3.9 Memory RAS..........................................................................................................36

Revision 1.1

Intel order number D38960-004

v

Page 6

Table of Contents Intel® 5000 Series Chipsets Server Board Family Datasheet

3.3.10 Memory Error Handling..........................................................................................40

3.4 Platform Control.....................................................................................................53

3.4.1 FBDIMM Open Loop Throughput Throttling...........................................................54

3.4.2 Fan Speed Control.................................................................................................55

3.5 Flash ROM.............................................................................................................57

3.6 BIOS User Interface...............................................................................................57

3.6.1 Logo / Diagnostic Screen.......................................................................................57

3.7 BIOS Setup Utility ..................................................................................................58

3.7.1 Operation ...............................................................................................................58

3.7.2 Server Platform Setup Screens..............................................................................62

3.8 Loading BIOS Defaults...........................................................................................85

3.9 Security..................................................................................................................85

3.9.1 Operating Model.....................................................................................................85

3.9.2 Password Protection..............................................................................................86

3.9.3 Password Clear Jumper.........................................................................................86

3.10 BIOS Update Flash Procedures.............................................................................86

3.10.1 Intel Iflash32 BIOS Update Utility...........................................................................86

3.10.2 Intel® One Boot Flash Update Utility ......................................................................87

3.11 BIOS Bank Select and One Boot Flash Update.....................................................89

3.11.1 BIOS Bank Select Jumper in Normal Mode (Jumper Pins 2 - 3 connected)..........89

3.11.2 BIOS Bank Select Jumper in Bank 0 Mode (Jumper pins 1 - 2 connected)...........90

3.12 OEM Binary............................................................................................................90

3.12.1 Splash Logo...........................................................................................................90

3.13 Boot Device Selection............................................................................................90

3.13.1 Server Managment Boot Device Control ................................................................91

3.14 Operating System Support.....................................................................................91

3.14.1 Windows Compatibility...........................................................................................91

3.14.2 Advanced Configuration and Power Interface (ACPI)............................................91

3.15 Front Control Panel Support ..................................................................................92

3.15.1 Power Button..........................................................................................................92

3.15.2 Reset Button ..........................................................................................................92

3.15.3 Non-Maskable Interrupt (NMI) Button ....................................................................93

3.16 Sleep and Wake Support.......................................................................................93

3.16.1 System Sleep States..............................................................................................93

3.16.2 Wake Events / SCI Sources...................................................................................93

Revision 1.1

vi

Intel order number D38960-004

Page 7

Intel® 5000 Series Chipsets Server Board Family Datasheet Table of Contents

3.17 Non-Maskable Interrupt Handling ..........................................................................94

3.18 BIOS Server Management.....................................................................................94

3.19 IPMI........................................................................................................................94

3.20 Console Redirection...............................................................................................95

3.20.1 Serial Configuration Settings..................................................................................95

3.20.2 Keystroke Mappings...............................................................................................95

3.20.3 Limitations..............................................................................................................96

3.20.4 Interface to Server Management............................................................................96

3.21 IPMI Serial Interface...............................................................................................96

3.21.1 Channel Access Modes .........................................................................................96

3.21.2 Interaction with BIOS Console Redirection............................................................96

3.22 Wired For Management (WFM)..............................................................................97

3.22.1 PXE BIOS Support.................................................................................................97

3.23 System Management BIOS (SMBIOS) ..................................................................98

4. System Management..........................................................................................................99

4.1 Feature Support.....................................................................................................99

4.1.1 Legacy Features ....................................................................................................99

4.1.2 New Features.......................................................................................................101

4.2 Power System......................................................................................................101

4.3 BMC Reset Control..............................................................................................103

4.3.1 BMC Exits Firmware Update Mode......................................................................103

4.4 System Initialization .............................................................................................103

4.4.1 Fault Resilient Booting (FRB)...............................................................................103

4.5 Integrated Front Panel User Interface..................................................................105

4.5.1 Power LED...........................................................................................................105

4.5.2 System Status LED..............................................................................................105

4.5.3 Chassis ID LED....................................................................................................107

4.5.4 Front Panel / Chassis Inputs................................................................................107

4.5.5 Front Panel Lock-out Operation...........................................................................108

4.6 Private Management I2C Buses ..........................................................................109

4.7 Watchdog Timer...................................................................................................109

4.8 System Event Log (SEL)......................................................................................109

4.8.1 Servicing Events ..................................................................................................110

4.8.2 SEL Erasure.........................................................................................................110

Revision 1.1

Intel order number D38960-004

vii

Page 8

Table of Contents Intel® 5000 Series Chipsets Server Board Family Datasheet

4.8.3 Timestamp Clock .................................................................................................110

4.9 Sensor Data Record (SDR) Repository................................................................111

4.9.1 Initialization Agent................................................................................................111

4.10 Field Replaceable Unit (FRU) Inventory Device...................................................111

4.11 Diagnostics and Beep Code Generation..............................................................112

4.12 NMI.......................................................................................................................112

4.12.1 Signal Generation ................................................................................................113

4.13 Processor Sensors...............................................................................................113

4.13.1 Processor Status Sensors....................................................................................114

4.13.2 Processor VRD Over-Temperature Sensor..........................................................114

4.13.3 ThermTrip Monitoring...........................................................................................115

4.13.4 Platform Enviroment Control Interface (PECI) Support........................................115

4.13.5 PROCHOT Support..............................................................................................115

4.13.6 IERR Monitoring...................................................................................................116

4.13.7 Dynamic Processor Voltage Monitoring...............................................................116

4.13.8 Processor Temperature Monitoring......................................................................116

4.13.9 Processor Thermal Control Monitoring (Prochot).................................................117

4.13.10 CPU Population Error Sensor ..............................................................................117

4.14 Standard Fan Management .................................................................................118

4.14.1 Nominal Fan Speed .............................................................................................119

4.14.2 Stepwise Linear....................................................................................................119

4.14.3 Clamp...................................................................................................................120

4.14.4 Sleep State Fan Control.......................................................................................120

4.14.5 Fan Redundancy Detection..................................................................................120

4.14.6 Hot Swap Fan Support.........................................................................................121

4.15 Acoustic Management..........................................................................................121

4.15.1 Fan Profiles..........................................................................................................121

4.15.2 Interactions with DIMM Thermal Management.....................................................121

4.16 PSMI Support.......................................................................................................121

4.17 System Memory RAS and Bus Error Monitoring..................................................122

4.17.1 SMI Timeout Sensor ............................................................................................122

4.17.2 Memory Sensor....................................................................................................122

4.17.3 Critical Interrupt Sensor .......................................................................................123

4.17.4 DIMM Status Sensors ..........................................................................................123

4.17.5 System Memory Redundancy Monitoring ............................................................124

Revision 1.1

viii

Intel order number D38960-004

Page 9

Intel® 5000 Series Chipsets Server Board Family Datasheet Table of Contents

4.17.6 System Memory Monitoring and System Boot.....................................................127

4.18 PCI Express* Support ..........................................................................................127

4.18.1 PCI Express Link Sensors ...................................................................................127

4.18.2 BMC Self-test....................................................................................................... 127

4.19 Field Replaceable Unit (FRU) / Fault LED Control...............................................128

4.20 Hot-swap Backplane (HSBP) Support .................................................................128

4.21 Intel® Remote Management Module (Intel® RMM) Support .................................128

4.21.1 Discovery Sequence............................................................................................128

4.21.2 Division of Network Traffic ...................................................................................129

4.21.3 Event Forwarding.................................................................................................129

4.21.4 Serial Routing.......................................................................................................130

4.21.5 Messaging Interfaces...........................................................................................130

4.22 Channel Management..........................................................................................131

4.23 User Model...........................................................................................................131

4.24 Session Support...................................................................................................131

4.25 Media Bridging.....................................................................................................131

4.26 Host to BMC Communication Interface................................................................132

4.26.1 LPC / KCS Interface.............................................................................................132

4.26.2 Receive Message Queue.....................................................................................132

4.26.3 Server Management Software (SMS) Interface ...................................................132

4.26.4 SMM Interface......................................................................................................132

4.27 IPMB Communication Interface ...........................................................................133

4.27.1 PCI System Management Bus (SMBus)..............................................................133

4.27.2 BMC as I2C Master Controller on IPMB...............................................................133

4.27.3 IPMB LUN Routing...............................................................................................134

4.28 Emergency Management Port (EMP) Interface ...................................................136

4.28.1 COM2 Port Switching...........................................................................................136

4.28.2 Basic Mode ..........................................................................................................136

4.28.3 Terminal Mode.....................................................................................................136

4.28.4 Invalid Password Handling...................................................................................138

4.28.5 Serial Ping Message Behavior.............................................................................138

4.29 LAN Interface.......................................................................................................139

4.29.1 IPMI 1.5 Messaging .............................................................................................139

4.29.2 IPMI 2.0 Messaging .............................................................................................140

4.29.3 Intel® 631xESB / 632xESB I/O Controller Hub Embedded LAN Channels ..........141

Revision 1.1

Intel order number D38960-004

ix

Page 10

Table of Contents Intel® 5000 Series Chipsets Server Board Family Datasheet

4.29.4 Address Resolution Protocol Support..................................................................141

4.29.5 Internet Control Message Protocol Support.........................................................141

4.29.6 Serial-over-LAN (SOL) 2.0...................................................................................141

5. Error Reporting and Handling .........................................................................................142

5.1 Fault Resilient Booting (FRB)...............................................................................142

5.1.1 BSP POST Failures (FRB-2)................................................................................142

5.1.2 Operating System Load Failures (OS Boot Timer)...............................................142

5.2 Error Handling and Logging.................................................................................143

5.2.1 Error Sources and Types.....................................................................................143

5.2.2 Error Logging via SMI Handler.............................................................................143

5.2.3 Timestamp Clock Event .......................................................................................144

5.3 Error Messages and Error Codes ........................................................................145

5.3.1 Diagnostic LEDs...................................................................................................145

5.3.2 POST Code Checkpoints.....................................................................................146

5.3.3 POST Error Messages and Handling...................................................................149

5.3.4 POST Error Beep Codes......................................................................................151

5.3.5 POST Error Pause Option....................................................................................151

Glossary...................................................................................................................................152

Reference Documents ............................................................................................................155

Revision 1.1

x

Intel order number D38960-004

Page 11

Intel® 5000 Series Chipsets Server Board Family Datasheet List of Figures

List of Figures

Figure 1. Intel® 5000 MCH Functional Architechture.....................................................................3

Figure 2. CEK Processor Mounting.............................................................................................13

Figure 3. FBD Topology..............................................................................................................15

Figure 4. Identifying Banks of Memory........................................................................................16

Figure 5. General BIOS Screen Display Layout..........................................................................59

Figure 6. Setup Utility — Main Screen Display ...........................................................................62

Figure 7. Setup Utility — Advanced Screen Display...................................................................64

Figure 8. Setup Utility — Processor Configuration Screen Display.............................................65

Figure 9. Setup Utility — Specific Processor Information Screen Display ..................................66

Figure 10. Setup Utility — Memory Configuration Screen Display..............................................67

Figure 11. Setup Utility — IDE Controller Configuration Screen Display ....................................69

Figure 12. Setup Utility — Mass Storage Configuration Screen Display.....................................72

Figure 13. Setup Utility — Serial Port Configuration Screen Display..........................................73

Figure 14. Setup Utility — USB Controller Configuration Screen Display...................................74

Figure 15. Setup Utility — PCI Configuration Screen Display.....................................................76

Figure 16. Setup Utility — System Acoustic and Performance Configuration Screen Display....77

Figure 17. Setup Utility — Security Configuration Screen Display..............................................78

Figure 18. Setup Utility — Server Management Configuration Screen Display ..........................80

Figure 19. Setup Utility — Console Redirection Screen Display.................................................81

Figure 20. Setup Utility — Server Management System Information Screen Display.................82

Figure 21. Setup Utility — Error Manager Screen Display..........................................................83

Figure 22. Setup Utility — Exit Screen Display...........................................................................84

Figure 23. Intel® 631xESB / 632xESB I/O Controller Hub Power / Reset Signals ....................102

Figure 24. DIMM Grouping........................................................................................................124

Figure 25. BMC IPMB Message Reception...............................................................................135

Figure 26. Location of Diagnostic LEDs on Server Board.........................................................146

Revision 1.1

Intel order number D38960-004

xi

Page 12

List of Tables Intel® 5000 Series Chipsets Server Board Family Datasheet

List of Tables

Table 1. DIMM Module Capacities..............................................................................................16

Table 2. NIC2 Status LED...........................................................................................................20

Table 3. Supported Processor Configurations ............................................................................25

Table 4. Mixed Processor Configurations ...................................................................................27

Table 5. Memory Errors Captured by Error Manager..................................................................45

Table 6. DIMM Fault Indicator LEDs...........................................................................................45

Table 7. System Status Indicator LEDs.......................................................................................46

Table 8. NMI Generation.............................................................................................................47

Table 9. Mirroring Mode Errors ...................................................................................................48

Table 10. POST Memory Error Handling.....................................................................................49

Table 11. Runtime Memory Error Handling, No Redundancy.....................................................50

Table 12. Runtime Error Handling, with Redundancy.................................................................51

Table 13. BIOS Setup Page Layout............................................................................................60

Table 14. BIOS Setup: Keyboard Command Bar........................................................................61

Table 15. Setup Utility — Main Screen Fields.............................................................................63

Table 16. Setup Utility — Processor Configuration Screen Fields..............................................65

Table 17. Setup Utility — Specific Processor Information Screen Fields....................................67

Table 18. Setup Utility — Memory Configuration Screen Fields .................................................68

Table 19. Setup Utility — IDE Controller Configuration Screen Fields........................................70

Table 20. Setup Utility — Mass Storage Configuration Screen Fields........................................72

Table 21. Setup Utility — Serial Ports Configuration Screen Fields............................................74

Table 22. Setup Utility — USB Controller Configuration Screen Fields ......................................75

Table 23. Setup Utility — PCI Configuration Screen Fields........................................................76

Table 24. Setup Utility — System Acoustic and Performance Configuration Screen Fields.......78

Table 25. Setup Utility — Security Configuration Screen Fields.................................................79

Table 26. Setup Utility — Server Management Configuration Screen Fields..............................80

Table 27. Setup Utility — Console Redirection Configuration Fields..........................................81

Table 28. Setup Utility — Server Management System Information Fields.................................83

Table 29. Setup Utility — Error Manager Screen Fields .............................................................83

Table 30. Setup Utility — Exit Screen Fields...............................................................................84

Table 31. Security Features Operating Model.............................................................................85

Table 32. NMI Error Messages ...................................................................................................94

Table 33. Console Redirection Escape Sequences for Headless Operation..............................96

Revision 1.1

xii

Intel order number D38960-004

Page 13

Intel® 5000 Series Chipsets Server Board Family Datasheet List of Tables

Table 34. BMC Reset Sources and Actions..............................................................................103

Table 35. Power LED Indicator States......................................................................................105

Table 36. System Status LED Indicator States.........................................................................106

Table 37. Chassis ID LED Indicator States...............................................................................107

Table 38. Secure Mode versus ACPI State...............................................................................109

Table 39. BMC Beep Codes......................................................................................................112

Table 40. Processor Sensors....................................................................................................113

Table 41. Requirements for Processor Status ..........................................................................114

Table 42. Standard Channel Assignments................................................................................131

Table 43. Keyboard Controller Style Interfaces.........................................................................132

Table 44. BMC IPMB LUN Routing...........................................................................................134

Table 45. Terminal Mode Commands.......................................................................................137

Table 46. Supported RMCP+ Cipher Suites..............................................................................140

Table 47. Supported RMCP+ Payload Types ...........................................................................140

Table 48. POST Progress Code LED Example.........................................................................145

Table 49. POST Code Checkpoints..........................................................................................146

Table 50. POST Error Messages and Handling........................................................................149

Table 51. POST Error Beep Codes...........................................................................................151

Revision 1.1

Intel order number D38960-004

xiii

Page 14

List of Tables Intel® 5000 Series Chipsets Server Board Family Datasheet

This page intentionally left blank

Revision 1.1

xiv

Intel order number D38960-004

Page 15

Intel® 5000 Series Chipsets Server Board Family Datasheet Introduction

1. Introduction

This datasheet provides information about features and regulatory information that is common

to Intel

This is a companion document to the technical product specifications that are available for

each server or workstation board that uses the Intel

®

server boards and Intel® workstation boards that use the Intel® 5000 Series Chipset.

®

5000 MCH. To fully understand all

features of a particular server or workstation board that uses this chipset, you need to use

both this datasheet and the technical product specification that is available for your server

board or workstation board.

The target audience for this document is anyone wishing to obtain more in depth detail of the

server board or workstation board than that which is available in the User’s Guide or the

board-specific technical product specification. This is a technical document that is meant to

assist people with understanding and learning more about the specific features of the board.

1.1 Server Product References

This document applies to both specific Intel® server boards and to specific Intel® workstation

boards. Unless otherwise noted, all references to “Intel boards” or “board” apply to both server

boards and workstation boards that use this chipset.

1.2 Chapter Outline

This document is divided into the following chapters

Chapter 1 - Introduction

Chapter 2 - Functional Architecture

Chapter 3 - System BIOS

Chapter 4 - System Management

Chapter 5 - Error Reporting and Handling

Revision 1.1

Intel order number D38960-004

1

Page 16

Functional Architecture Intel® 5000 Series Chipsets Server Board Family Datasheet

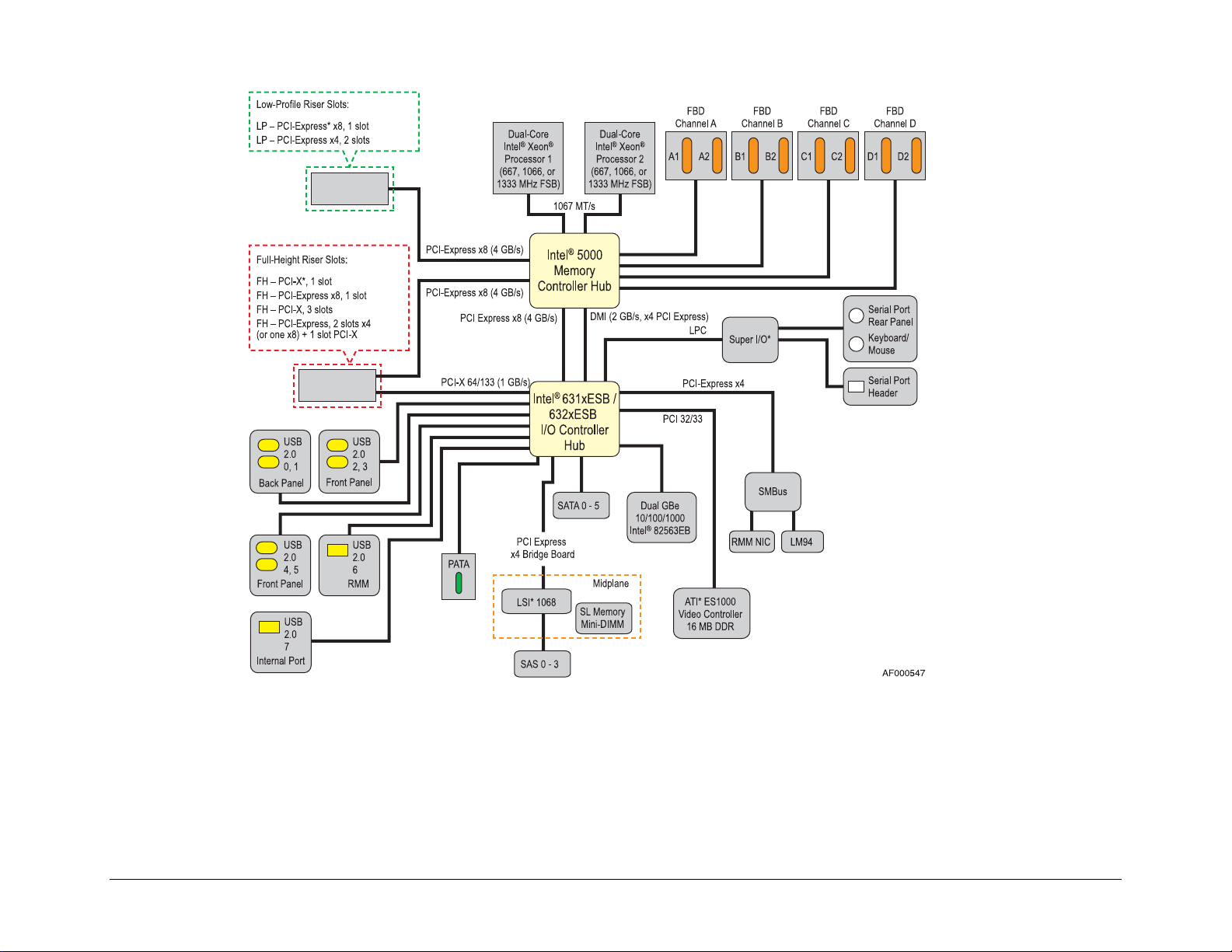

2. Functional Architecture

This chapter provides a detailed description of the functionality associated with the

architectural blocks that comprise the Intel

®

5000 MCH. A diagram of the chipset functional

architecture is on the following page.

Revision 1.1

2

Intel order number D38960-004

Page 17

Intel® 5000 Series Chipsets Server Board Family Datasheet Functional Architecture

Figure 1. Intel® 5000 MCH Functional Architechture

Revision 1.1

3

Intel order number D38960-004

Page 18

Functional Architecture Intel® 5000 Series Chipsets Server Board Family Datasheet

2.1 Intel® 5000 MCH Components

The chipsets consist of two components that together are responsible for providing the interface

between all major sub-systems found on the Intel

®

server or workstation board. These sub-

systems include the processor, memory, and I/O sub-systems. These components are:

Intel

Intel

®

5000 Memory Controller Hub (Intel® 5000 MCH)

®

Enterprise South Bridge 2 (Intel® 631xESB / 632xESB I/O Controller Hub)

The following sub-sections provide an overview of the primary functions and supported features

of each chipset component used on the Intel

®

boards that utilize the Intel® 5000 MCH. Later

sections in this chapter provide more detail on how each sub-system is implemented.

Note: See the Intel

®

server board or workstation board technical product specification that

applies to your product for feature-specific support information.

2.1.1 Memory Controller Hub (Intel® 5000 MCH)

The Intel® 5000 MCH is a 1432-ball FC-BGA package configured to support the following

interfaces:

CPU dual, independent system bus at 667-, 1066-, or 1333-MHz operation.

Four fully-buffered DIMM (FBD) channels supporting fully-buffered DDR2 DIMMs

(FBDIMMs), 24-lane serial bus at 6.4 GB/s (533 MT/s) and 8 GB/s (667 MT/s) peak

theoretical bandwidth per channel. This allows a total of 25.6 GB/s and 64.6 GB/s peak

theoretical bandwidth for all four Channels combined.

One PCI Express* x8 port with an aggregate bandwidth of 4 GB/s interface to the Intel®

631xESB / 632xESB I/O Controller Hub.

One PCI Express x8 port with an aggregate bandwidth of 4 GB/s interface to x8 PCI

Express Connector.

One PCI Express x8 port with an aggregate bandwidth of 4 GB/s interface to x8 PCI

Express Connector.

One PCI Express x4 ESI port with an aggregate bandwidth of 2 GB/s interface to the

Intel® 631xESB / 632xESB I/O Controller Hub.

2.1.1.1 System Bus

The Intel

Xeon

system bus frequency of 266 MHz and 333 MHz for Intel

®

5000 MCH supports either single- or dual-processor configurations using the Intel®

®

5000 Sequence processor with a 2x 2 MB cache. The Intel® 5000 MCH supports a base

®

5000 Series Chipsets. The address

and request interface is double-pumped to 533 MHz, and the 64-bit data interface (+ parity) is

quad-pumped to 1066 MHz. This provides a matched system bus address and data bandwidths

of 8.5 GB/s.

Revision 1.1

4

Intel order number D38960-004

Page 19

Intel® 5000 Series Chipsets Server Board Family Datasheet Functional Architecture

®

2.1.1.2 Intel

®

The Intel

5000 MCH provides an integrated memory controller for direct connection to four

5000 MCH Memory Sub-System Overview

channels of registered fully-buffered DIMM (FBD) DDR2 533/667 MHz memory (stacked or

unstacked). Peak theoretical memory data bandwidth using FBD 533/667 MHz technology is 6.4

and 8 GB/s, respectively.

When all four memory channels are populated and operating, they function in lock-step mode.

The maximum supported FBD DDR2 533/667 MHz memory configuration is 64 GB.

The Intel

®

5000 MCH memory interface provides several reliability, availability, serviceability,

usability, and manageability (RASUM) features, including:

Memory mirroring allows two copies of all data in the memory subsystem (one on each

channel) to be maintained.

Memory sparing allows one DIMM per channel to be held in reserve and brought on-line

if another FBDIMM in the channel becomes defective.

Hardware periodic memory scrubbing, including demand scrub support.

Retry on uncorrectable memory errors.

Intel

®

x4/x8 Single Device Data Correction (SDDC) for memory error detection and

correction of any number of bit failures in a single x4/x8 memory device.

Note: Memory sparing and memory mirroring are mutually exclusive.

Note: Memory sparing and mirroring features are currently disabled and will be made available

after production launch.

2.1.1.3 PCI Express* Interface

®

The Intel

bandwidth. The scalable PCI Express interface of the Intel

5000 MCH supports the PCI Express* high-speed serial I/O interface for superior I/O

®

5000 MCH complies with the PCI

Express Interface Specification, Revision 1.0a.

The Intel

®

5000 MCH provides three x8 PCI Express* interfaces, each with a maximum

theoretical bandwidth of 4.2 GB/s. Each of these x8 PCI Express interfaces may alternatively be

configured as two independent x4 PCI Express interfaces. A PCI Express interface/port is

defined as a collection of lanes. Each lane (x1) consists of two striped differential pairs in each

direction (transmit and receive). The raw bit-rate on the data pins of 2.5 Gb/s, results in a real

bandwidth of 250 MB/s per pair, given the 8/10 bit encoding used to transmit data across this

interface.

The Intel

Specification. The PCI Express* interfaces of the Intel

®

5000 MCH is a root-class component as defined in the PCI Express Interface

®

5000 MCH support connections to a

variety of bridges and devices that are compliant with the same revision of the specification.

Revision 1.1

Intel order number D38960-004

5

Page 20

Functional Architecture Intel® 5000 Series Chipsets Server Board Family Datasheet

2.1.1.3.1 PCI Express* Training

To establish a connection between PCI Express* endpoints, the endpoints participate in a

sequence of steps called training. This sequence establishes the operational width of the link

and adjusts skews of the various lanes within a link so that the data sample points can correctly

take a data sample from the link.

In the case of a x8 port, the x4 link-pairs first attempt to train independently, and will collapse to

a single link at the x8 width upon detection of a single device returning link ID information

upstream. Once the number of links has been established, they negotiate to train at the highest

common width, and step down in its supported link widths to succeed in training. The result may

be that the link has trained as a x1 link.

Although the bandwidth of this link size is substantially lower than a x8 link or a x4 link, it allows

communication between the two devices. Software can then interrogate the device at the other

end of the link to determine why it failed to train at a higher width. This would not be possible

without support for the x1 link width.

Width negotiation is done only during training or retraining, not during recovery.

2.1.1.3.2 PCI Express* Retry

The PCI Express* interface incorporates a link-level retry mechanism. The hardware detects a

corrupted transmission packet and performs a retry of that packet and all following packets.

Although this causes a temporary interruption in the delivery of packets, the retry helps to

maintain the link integrity.

2.1.1.3.3 PCI Express* Link Recovery

If excessive errors occur, the hardware can determine that the quality of the connection is in

question and the end points can enter a quick training sequence, known as recovery. The width

of the connection will not be renegotiated, but the adjustment of skew between lanes of the link

might occur. This occurs without any software intervention, but the software might be notified.

2.1.1.3.4 PCI Express* Data Protection

The PCI Express* high-speed serial interface uses traditional CRC protection. The data packets

use a 32-bit CRC protection scheme, the same CRC-32 used by Ethernet. The smaller link

packets use a 16-bit CRC scheme. Since packets utilize 8B/10B encoding, and not all

encodings are used; this provides further data protection, as illegal codes can be detected. If

errors are detected on the reception of data packets due to various transients, these data

packets can be retransmitted. Hardware logic supports this link-level retry without software

intervention.

Revision 1.1

6

Intel order number D38960-004

Page 21

Intel® 5000 Series Chipsets Server Board Family Datasheet Functional Architecture

2.1.1.3.5 PCI Express* Retrain

If the hardware is unable to perform a successful recovery, then the link automatically reverts to

the polling state and initiates a full retraining sequence. This is a drastic event with an implicit

reset to the downstream device and all subordinate devices, and is logged by the Intel

®

5000

MCH as a "Link Down" error. If escalation of this event is enabled, software is notified of the link

DL_DOWN condition. If software is involved, then data is probably lost, and processes need to

be restarted. This is preferred over the taking down the system or going offline for an extended

time.

2.1.1.4 Enterprise South Bridge Interface (ESI)

A PCI interface is provided for a connection to the memory controller hub (Intel

®

5000 MCH).

Maximum realized bandwidth on this interface is 2 GB/s in each direction simultaneously, for an

aggregate of 4 GB/s. This PCI Express* interface is compliant with the PCI Express Base

Specification Revision 1.0a, and supports x4 and x8 bandwidths.

2.1.2 Intel® 631xESB / 632xESB I/O Controller Hub (ESB2)

The Intel® 631xESB / 632xESB I/O Controller Hub is a multi-function device that provides an

upstream hub interface for access to several embedded I/O functions and features, including:

Compliant with the PCI Express Base Specification, Revision 1.0a, with support for four

PCI Express* root ports (module-based hot-plug support) and two 1x4 downstream ports

(connector-based hot-swap support)

Compliant with the PCI-X Addendum to the PCI Local Bus Specification, Revision 1.0b

Compliant with the PCI Local Bus Specification, Revision 2.3 with support for 33 MHz

PCI operations

Compliant with the PCI Standard Hot-Plug Controller and Subsystem Specification,

Revision 1.0

ACPI 2.0 power management logic support

Enhanced DMA controller, interrupt controller, and timer functions

Integrated IDE controller with support for Ultra ATA100 / 66 / 33

Integrated SATA controller

Baseboard management controller (BMC)

USB host interface with support for eight USB 2.0 ports; via four UHCI host controllers;

and one EHCI high-speed host controller

Compliant with the System Management Bus (SMBus) Specification, Version 2.0 with

additional support for I

Support for the Audio Codec ‘97, Revision 2.3 Specification

Low pin count (LPC) interface

2

C devices

Each function within the Intel

®

631xESB / 632xESB I/O Controller Hub has its own set of

configuration registers. Once configured, each appears to the system as a distinct hardware

controller that shares the same PCI bus interface.

Revision 1.1

Intel order number D38960-004

7

Page 22

Functional Architecture Intel® 5000 Series Chipsets Server Board Family Datasheet

2.1.2.1 PCI Interface

®

The Intel

2.3-compliant implementation. All PCI signals are 5-V tolerant, except for PME#. An integrated

PCI arbiter supports up to six external PCI bus masters in addition to the internal Intel

631xESB / 632xESB I/O Controller Hub requests. On Intel

631xESB / 632xESB I/O Controller Hub PCI interface supports a 33-MHz, Revision

®

®

boards that use the Intel® 5000

MCH, this PCI interface is used to support one on-board PCI device: the ATI* ES1000 video

controller.

2.1.2.2 PCI Express* Interface

The Intel

®

631xESB / 632xESB I/O Controller Hub provides PCI Express* root ports that are

compliant with the PCI Express Base Specification Revision 1.0a. The PCI Express root ports

can be statically configured as four x1 ports or ganged together to form one x4 port. Each root

port supports 250 MB/s bandwidth in each direction (500 MB/s concurrent).

The Intel

®

631xESB / 632xESB I/O Controller Hub implements two x4 downstream ports. The

maximum realized bandwidth on this interface is 1 GB/s in each direction simultaneously, for an

aggregate of 2 GB/s. These two ports can be configured as one x8 PCI Express* port. This PCI

Express interface is compliant with the PCI Express Base Specification Revision 1.0a.

2.1.2.3 PCI-X* Bus Interface

The Intel

conventional PCI and PCI-X Mode 1. The PCI-X interfaces on the Intel

®

631xESB / 632xESB I/O Controller Hub provides a PCI-X* bus interface that supports

®

631xESB / 632xESB

I/O Controller Hub are compliant with the following:

“PCI-X Addendum” to the PCI Local Bus Specification Revision 1.0b

“Mode 1” sections of the “PCI-X Electrical and Mechanical Addendum” to the PCI Local

Bus Specification Revision 2.0a

“PCI-X Protocol Addendum” to the PCI Local Bus Specification Revision 2.0a

The Intel

®

631xESB / 632xESB I/O Controller Hub supports PCI bus frequencies of 66 MHz,

100 MHz, and 133 MHz.

2.1.2.4 IDE Interface (Bus Master Capability and Synchronous DMA Mode)

The Intel

®

631xESB / 632xESB I/O Controller Hub has an integrated IDE controller with an

independent IDE signal channel that supports up to two IDE devices. This integrated

functionality provides the interface for IDE hard disks and ATAPI devices. Each IDE device can

have independent timings. The IDE interface supports PIO IDE transfers of up to 16 MB/s and

Ultra ATA transfers of up 100 MB/s. The IDE interface integrates 16x32-bit buffers for optimal

transfers and does not consume any ISA DMA resources. The IDE signal channels in the Intel

®

631xESB / 632xESB I/O Controller Hub can be configured to primary and secondary channels.

Revision 1.1

8

Intel order number D38960-004

Page 23

Intel® 5000 Series Chipsets Server Board Family Datasheet Functional Architecture

2.1.2.5 Serial ATA (SATA) Host Controller

The SATA host controller supports a combination of up to six SATA or four serial attached SCSI

(SAS) devices. This provides an interface for SATA hard disks and ATAPI devices. The SATA

interface supports PIO IDE transfers up to 16 MB/s and Serial ATA transfers up to 3.0 Gb/s (300

MB/s).

The SATA system for the Intel

®

631xESB / 632xESB I/O Controller Hub contains six

independent SATA signal ports that can be independently electrically isolated. Each SATA

device can have independent timings. They can be configured to the standard primary and

secondary channels. In addition, the controller hub offers the Intel

®

Embedded Server RAID

Technology that enables data striping (RAID Level 0) for higher-performance or data mirroring

(RAID Level 1) for fault-tolerance between the two SATA drives, alleviating disk bottlenecks by

taking advantage of the dual, independent SATA controllers integrated in the Intel

®

631xESB /

632xESB I/O Controller Hub.

Note: See the Intel

®

server board or workstation board technical product specification that

applies to your product for more information.

2.1.2.6 Baseboard Management Controller (BMC)

®

The BMC component of the Intel

631xESB / 632xESB I/O Controller Hub is provided by an

embedded ARC* controller and associated peripheral functionality that is used to provide the

baseboard management controller functionality that is required for IPMI-based server

management. The following is a summary of the Intel

®

631xESB / 632xESB I/O Controller Hub

management hardware features utilized by the BMC:

ARC4 processor with 16 Kb I-cache and D-cache

256 Kb of internal SRAM with dual port (one for code accesses and one for all other

accesses).

Expansion bus, allowing connection to external Flash PROM (asynchronous or

synchronous), an external SRAM or an external SDRAM.

Serial flash interface

Five SMB ports, two that support FML (either master or slave)

RS-232 serial port (UART)

Cryptographic module, supporting AES and RC4 encryption algorithms and SHA1 and

MD5 authentication algorithms with internal DMA and raw checksum support.

Two keyboard controller style (KCS) interfaces residing on the LPC bus

General-purpose input/output (GPIO) interface

MAC CSR interface

Timer interface

Host DMA interface

Revision 1.1

Intel order number D38960-004

9

Page 24

Functional Architecture Intel® 5000 Series Chipsets Server Board Family Datasheet

2.1.2.7 Low Pin Count (LPC) Interface

®

The Intel

the Low Pin Count Interface Specification, Revision 1.1. The low pin count (LPC) bridge function

of the Intel

631xESB / 632xESB I/O Controller Hub implements an LPC Interface as described in

®

631xESB / 632xESB I/O Controller Hub resides in PCI Device 31: Function 0. In

addition to the LPC bridge interface function, D31:F0 contains other functional units including

DMA, interrupt controllers, timers, power management, system management, GPIO, and RTC.

2.1.2.8 Compatibility Modules (DMA Controller, Timer/Counters, Interrupt

Controller)

The DMA controller incorporates the logic of two 82C37 DMA controllers, with seven

independently programmable channels. Channels 0–3 are hardwired to 8-bit, count-by-byte

transfers, and channels 5 through 7 are hardwired to 16-bit, count-by-word transfers. Any two of

the seven DMA channels can be programmed to support fast Type-F transfers.

The Intel

DMA use the Intel

®

631xESB / 632xESB I/O Controller Hub supports LPC DMA. LPC DMA and PC/PCI

®

631xESB / 632xESB I/O Controller Hub’s DMA controller. LPC DMA is

handled through the use of the LDRQ# lines from peripherals and special encoding on LAD[3:0]

from the host. Single, demand, verify, and increment modes are supported on the LPC

interface. Channels 0–3 are 8 bit channels. Channels 5 through 7 are 16-bit channels. Channel

4 is reserved as a generic bus master request.

The timer / counter block contains three counters that are equivalent in function to those found

in one 82C54 programmable interval timer. These three counters are combined to provide the

system timer function, and speaker tone. The 14.31818-MHz oscillator input provides the clock

source for these three counters.

The Intel

®

631xESB / 632xESB I/O Controller Hub provides an ISA-compatible programmable

interrupt controller (PIC) that incorporates the functionality of two 82C59 interrupt controllers.

The two interrupt controllers are cascaded so that 14 external and two internal interrupts are

possible. In addition, the I/O Controller Hub supports a serial interrupt scheme. All of the

registers in these modules can be read and restored. This is required to save and restore the

system state after power has been removed and restored to the platform.

2.1.2.9 Advanced Programmable Interrupt Controller (APIC)

In addition to the standard ISA-compatible PIC described in the previous section, the Intel

®

631xESB / 632xESB I/O Controller Hub incorporates the Advanced Programmable Interrupt

Controller (APIC).

2.1.2.10 Universal Serial Bus (USB) Controller

The Intel

®

631xESB / 632xESB I/O Controller Hub contains an enhanced host controller

interface that supports USB high-speed signaling. High-speed USB 2.0 allows data transfers up

to 480 Mb/s, which is 40 times faster than full-speed USB. The I/O Controller Hub also contains

four universal host controller interface (UHCI) controllers that support USB full-speed and lowspeed signaling.

The Intel

®

631xESB / 632xESB I/O Controller Hub supports eight USB 2.0 ports. All eight ports

capable of high-speed, full-speed, and low-speed.

Revision 1.1

10

Intel order number D38960-004

Page 25

Intel® 5000 Series Chipsets Server Board Family Datasheet Functional Architecture

2.1.2.11 Real-time Clock (RTC)

®

The Intel

631xESB / 632xESB I/O Controller Hub contains a Motorola* MC146818A-compatible

real-time clock with 256 bytes of battery-backed RAM. The real-time clock performs two key

functions: keeping track of the time of day and storing system data, even when the system is

powered down. The RTC operates on a 32.768-KHz crystal and a separate 3-V lithium battery.

The RTC supports two lockable memory ranges. By setting bits in the configuration space, two

8-byte ranges can be locked to read and write accesses. This prevents unauthorized reading of

passwords or other system security information.

2.1.2.12 General-purpose Input/Output (GPIO)

General-purpose inputs and outputs are provided for custom system designs. The number of

inputs and outputs depends on the Intel

®

631xESB / 632xESB I/O Controller Hub configuration.

All unused GPI pins must be pulled high or low, so they are at a predefined level and do not

cause problems.

Note: See the Intel

®

server board or workstation board technical product specification that

applies to your product for more information.

2.1.2.13 System Management Bus (SMBus 2.0)

®

The Intel

the processor to communicate with SMBus slaves. This interface is compatible with most I

devices. Special I

631xESB / 632xESB I/O Controller Hub contains a SMBus host interface that allows

2

C commands are implemented. The SMBus host controller for the I/O

2

C

Controller Hub provides a mechanism for the processor to initiate communications with SMBus

peripherals (slaves).

The Intel

®

631xESB / 632xESB I/O Controller Hub supports slave functionality, including the

Host Notify protocol. The host controller supports eight command protocols of the SMBus

interface: Quick Command, Send Byte, Receive Byte, Write Byte/Word, Read Byte/Word,

Process Call, Block Read/Write, and Host Notify.

See the System Management Bus (SMBus) Specification, Version 2.0 for more information.

2.2 Processor Sub-system

The support circuitry for the processor sub-system consists of the following:

Dual LGA771 zero insertion force (ZIF) processor sockets

Processor host bus AGTL+ support circuitry

Reset configuration logic

Processor module presence detection logic

BSEL detection capabilities

CPU signal level translation

Common enabling kit (CEK) CPU retention support

Revision 1.1

Intel order number D38960-004

11

Page 26

Functional Architecture Intel® 5000 Series Chipsets Server Board Family Datasheet

2.2.1 Processor Support

Intel® boards that use the Intel® 5000 MCH support one or two Intel® Xeon® 5000 sequence

processors that utilize a 667, 1066, or 1333 MHz system bus with frequencies starting at 3.67

GHz. Previous generations of the Intel

®

Xeon® processors are not supported on these boards.

2.2.2 Processor Population Rules

When two processors are installed, both must be of identical revision, core voltage, and

bus/core speed. When only one processor is installed, it must be in the socket labeled CPU1.

The other socket must be empty.

Processors must be populated in sequential order. Processor socket 1 (CPU1) must be

populated before processor socket 2 (CPU2). No terminator is required in the second processor

socket when using a single processor configuration.

The board is designed to provide up to 130 A of current per processor. Processors with higher

current requirements are not supported.

2.2.3 Processor EVRD

EVRD11.0, Enterprise Voltage Regulator Down, is a DC-to-DC converter that meets the

processor power requirements server platform. Processors supported by this VR are: Intel

®

5000 sequence processors and future processor technologies

EVRD11.0 incorporates functional changes from prior EVRD design guidelines.

2.2.4 GTL2007

The GTL2007 is a customized translator between dual Intel® Xeon® 5000 sequence processors,

system health management, Intel

LVTTL and GTL signals. The GTL2007 is a 12-bit translator to interface between the 3.3-V

LVTTL chipset I/O and the Dual-Core Intel

GTL / GTL+ I/O. The device is designed for platform health management in dual-processor

applications.

®

631xESB / 632xESB I/O Controller Hub, and power supply

®

Xeon® 5000 processor sequence processor GTL- /

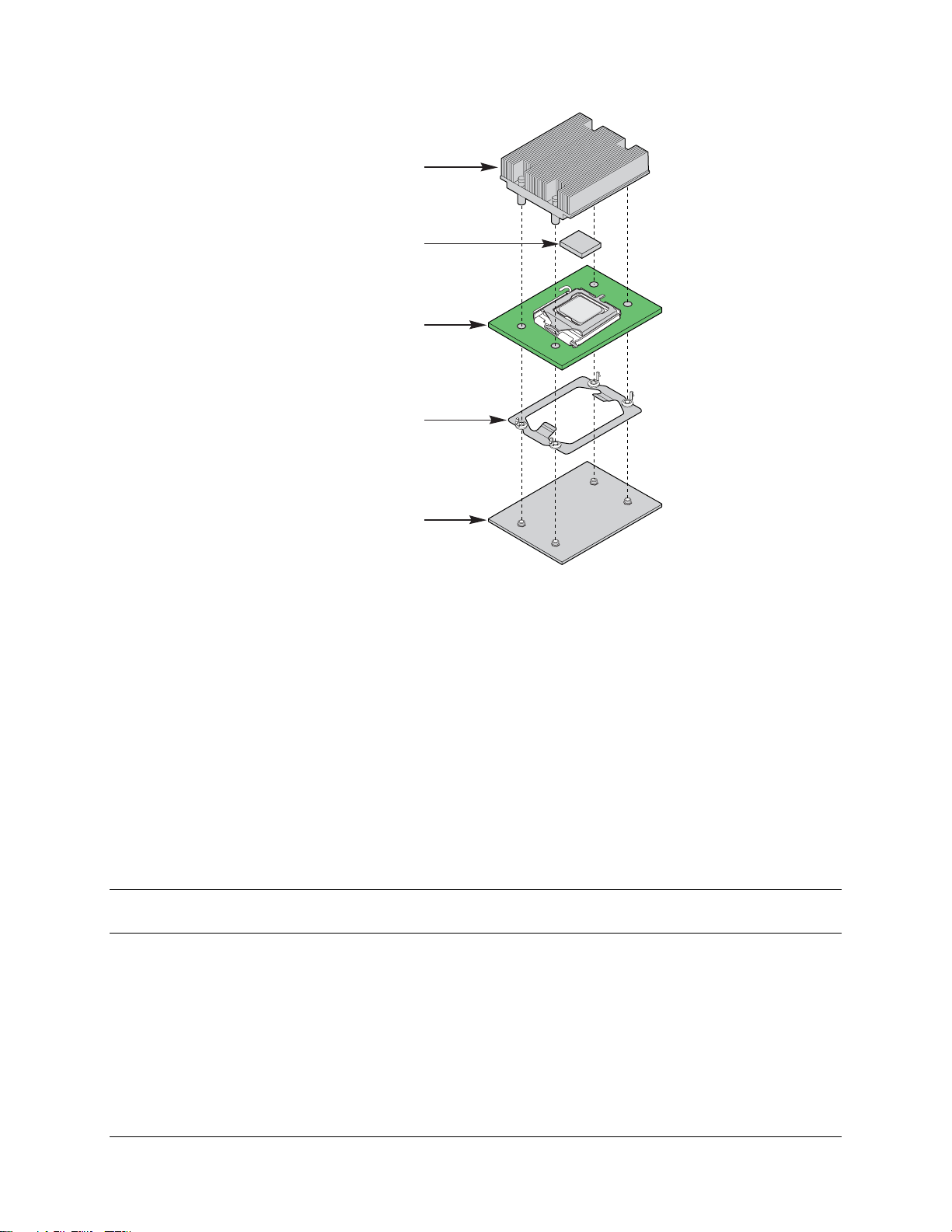

2.2.5 Common Enabling Kit (CEK) Design Support

The Intel® board complies with the Intel® Common Enabling Kit (CEK) processor mounting and

thermal solution. The server board ships from Intel’s factory with a CEK spring snapped onto the

underside of the board beneath each processor socket. The CEK spring is removable to allow

the use of non-Intel heat sink retention solutions.

Revision 1.1

12

Intel order number D38960-004

Page 27

Intel® 5000 Series Chipsets Server Board Family Datasheet Functional Architecture

Heatsink assembly

Thermal Interface

Material (TIM)

Server Board

CEK Spring

Chassis

Figure 2. CEK Processor Mounting

TP02091

AF000196

2.3 Memory Sub-system

The Intel® boards that use the Intel® 5000 MCH support several fully-buffered (FBD) memory

modes of operation.

Single-channel mode (single DIMM mode)

Single-branch / dual-channel mode

Dual-branch / dual-channel mode (four channels)

Memory sparing mode

Memory mirroring mode

Note: Memory sparing and mirroring features are currently disabled and will be made available

after production launch.

The Intel® 5000 MCH provides an integrated memory controller for direct connection to four

channels routed to eight connectors supporting registered DDR2-533 and DDR2-667 FBDIMM

memory (stacked or unstacked). Peak theoretical memory data bandwidth is 6.4 GB/s with

DDR2-533 and 8.0 GB/s with DDR2-667.

A pair of channels is a branch. Branch 0 consists of channel A and channel B, Branch 1

consists of channel C and channel D. A DIMM can have two ranks; a channel supports a

maximum of eight ranks.

Revision 1.1

Intel order number D38960-004

13

Page 28

Functional Architecture Intel® 5000 Series Chipsets Server Board Family Datasheet

In non-mirrored operation, the two DDR2 channels within a branch operate in lock-step and the

branches operate independently. When memory mirroring is configured, the channels operate in

lock-step under normal conditions, but independently under failure and recovery conditions.

The Intel

®

5000 MCH supports a burst length of four in either single-channel mode or dualchannel mode. In dual-channel mode this results in eight 64-bit chunks (64-byte cache line)

from a single read or write. In single-channel mode, two reads or writes are required to access a

cache line of data.

Memory between 32 GB, and 32 GB minus 512 MB, is not accessible for use by the operating

system and may be lost to the user. This area is reserved for the BIOS, APIC configuration

space, PCI adapter interface, and virtual video memory space. This means that if 32 GB of

memory is installed, 31.5 GB of this memory is usable. The chipset should allow the remapping

of unused memory above the 32 GB address, but this memory may not be accessible to an

operating system that has a 32 GB memory limit.

To boot the system, the system BIOS uses a dedicated I

needed to program the Intel

®

5000 MCH memory registers.

2

C bus to retrieve DIMM information

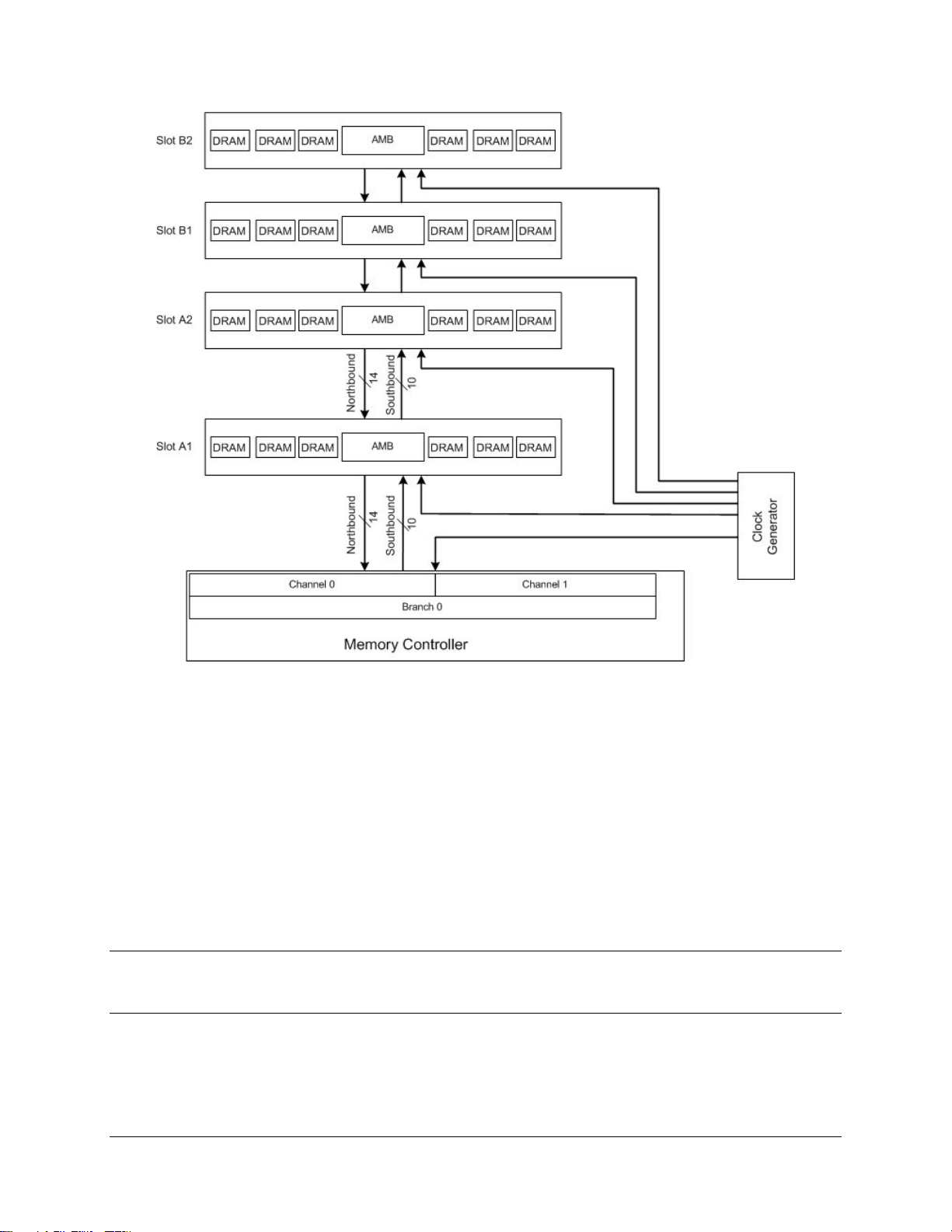

2.3.1 Fully-buffered DIMM (FBDIMM)

The fully-buffered DIMM (FBDIMM) memory interface provides a high-bandwidth, large-capacity

channel solution that has a narrow host interface. FBDIMMs use commodity DRAMs isolated

from the channel behind an advanced memory buffer (AMB) on the DIMM that allows a greater

number of devices per channel without loading the interconnect and affecting performance.

Memory capacity remains at a maximum of 36 devices per DIMM and total memory capacity

scales with DRAM bit density.

FBD is a differential pair, point-to-point interface. The interface consists primarily of 10

southbound differential pairs (outputs from the Intel

northbound differential pairs (inputs to the Intel

®

5000 MCH to the DIMMs) and 14

®

5000 MCH from the DIMMs). The Intel® 5000

MCH is connected only to the closest FBDIMM in the channel and communicates with the AMB

on that FBDIMM. The AMB on the closest FBDIMM communicates with the AMB on the next

FBDIMM in the channel, and so on. This point-to-point solution eliminates problems associated

with a “stub-bus” architecture and allows memory capacity to increase without loading the

channel. The figure below shows the FBD topology.

Revision 1.1

14

Intel order number D38960-004

Page 29

Intel® 5000 Series Chipsets Server Board Family Datasheet Functional Architecture

Figure 3. FBD Topology

2.3.2 Supported Memory

The Intel® 5000 MCH supports single-channel DIMM operation in which only one FBDIMM is

installed in DIMM socket A1. Population in other DIMM banks is not supported for singlechannel operation.

The server and workstation boards provide the maximum memory capacities outlined in

Table 1, based on the number of DIMM slots provided and maximum supported memory loads

by the chipset. The minimum memory supported with the system running in single-channel

memory mode is 512 MB, using a single DIMM in the DIMM A1 socket.

Note: All Intel memory qualification is done by testing with complete memory banks of identical

memory modules in all DIMM sockets. Memory qualification does not include testing of singlechannel memory mode, mixed DIMM type and/or vendors.

Supported DIMM capacities are 512 MB, 1 GB, 2 GB, and 4 GB.

Revision 1.1

Intel order number D38960-004

15

Page 30

Functional Architecture Intel® 5000 Series Chipsets Server Board Family Datasheet

Table 1. DIMM Module Capacities

SDRAM Parts / SDRAM Technology Used 512Mb 1Gb 2Gb 4Gb

X8, single row 512MB 1GB 2GB 4GB

X8, double row 1GB 2GB 4GB 8GB

X4, single row 512MB 1GB 2GB 4GB

X4, Stacked, double row 1GB 2GB 4GB 8GB

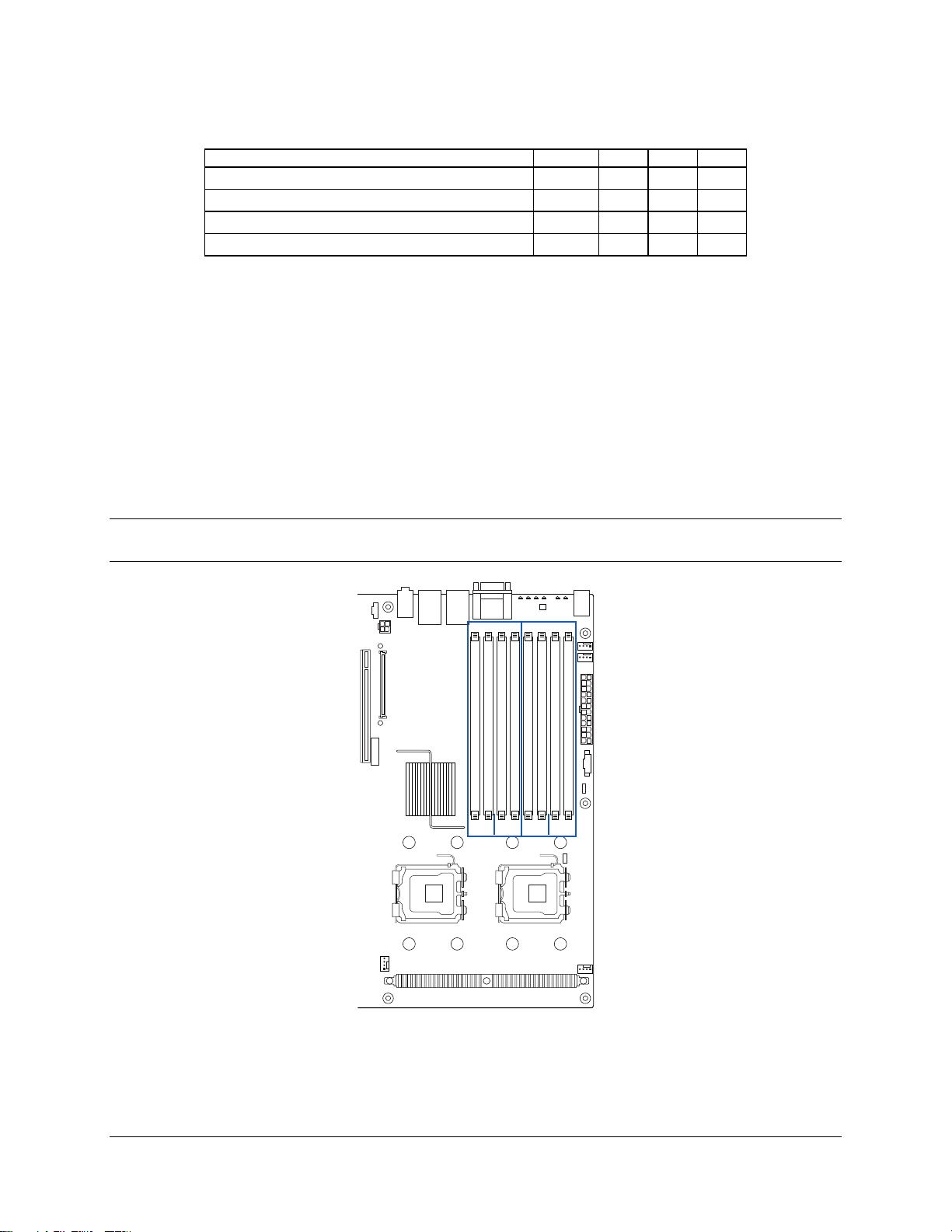

DIMMs on channel A are paired with DIMMs on channel B to configure 4-way interleaving. Each

DIMM pair is referred to as a bank. The bank can be further divided into two rows, based on

single-sided or double-sided DIMMs. If both DIMMs in a bank are single-sided, only one row is

said to be present. For double-sided DIMMs, both rows are said to be present.

The server and workstation boards have eight DIMM slots, or four DIMM channels. Both DIMMs

in a channel should be identical (same manufacturer, CAS latency, number of rows, columns

and devices, timing parameters, etc.). Although DIMMs within a channel must be identical, the

BIOS supports various DIMM sizes and configurations, allowing the channels of memory to be

different. Memory sizing and configuration is guaranteed only for qualified DIMMs approved by

Intel.

Note: Some boards vary in memory capacity. See the server or workstation Technical Product

Specification that applies to your product for more information.

Branch 1 Branch 2

DIMM A1

DIMM A2

DIMM B1

DIMM B2

DIMM C1

DIMM C2

DIMM D1

DIMM D2

Ch 1 Ch 2 Ch 3 Ch 4

AF000169

Figure 4. Identifying Banks of Memory

Revision 1.1

16

Intel order number D38960-004

Page 31

Intel® 5000 Series Chipsets Server Board Family Datasheet Functional Architecture

2.4 I/O Sub-system

The I/O sub-system consists of several components:

PCI sub-system

Serial ATA (SATA) support

Serial-attached SCSI (SAS)

RAID support

Parallel ATA (PATA) support

Video controller

Network interface controller (NIC)

USB 2.0 support

Super I/O support

This section describes the function of each I/O interface and how they operate.

2.4.1 PCI Sub-system

2.4.2 Scan Order

The BIOS assigns PCI bus numbers in a depth-first hierarchy, in accordance with the PCI Local

Bus Specification, Revision 2.2. The bus number is incremented when BIOS locates a bridge

device that is not part of the chipset. Scanning continues on the secondary side of the bridge

until all subordinate buses are assigned numbers. PCI bus number assignments may vary from

boot to boot with varying presence of PCI devices with PCI-PCI bridges. If a device with a

bridge with a single bus behind it is inserted into a PCI bus, all subsequent PCI bus numbers

below the current bus are increased by one.

The bus assignments occur once, early in the BIOS boot process, and never change during the

pre-boot phase.

2.4.3 Resource Assignment

The BIOS resource manager assigns the PIC-mode interrupt for the devices that are accessed

by the legacy code. The BIOS will ensure the PCI BAR registers and the command register for

all devices are correctly set up to match the behavior of the legacy BIOS after booting to a

legacy operating system. Any legacy code cannot make any assumption about the scan order of

devices or the order in which resources are allocated to them.

In legacy mode, the BIOS supports the INT 1Ah PCI BIOS interface calls.

2.4.4 Automatic IRQ Assignment

The BIOS automatically assigns IRQs to devices in the system for legacy compatibility. No

method is provided to manually configure the IRQs for devices.