Page 1

A

B

C

D

E

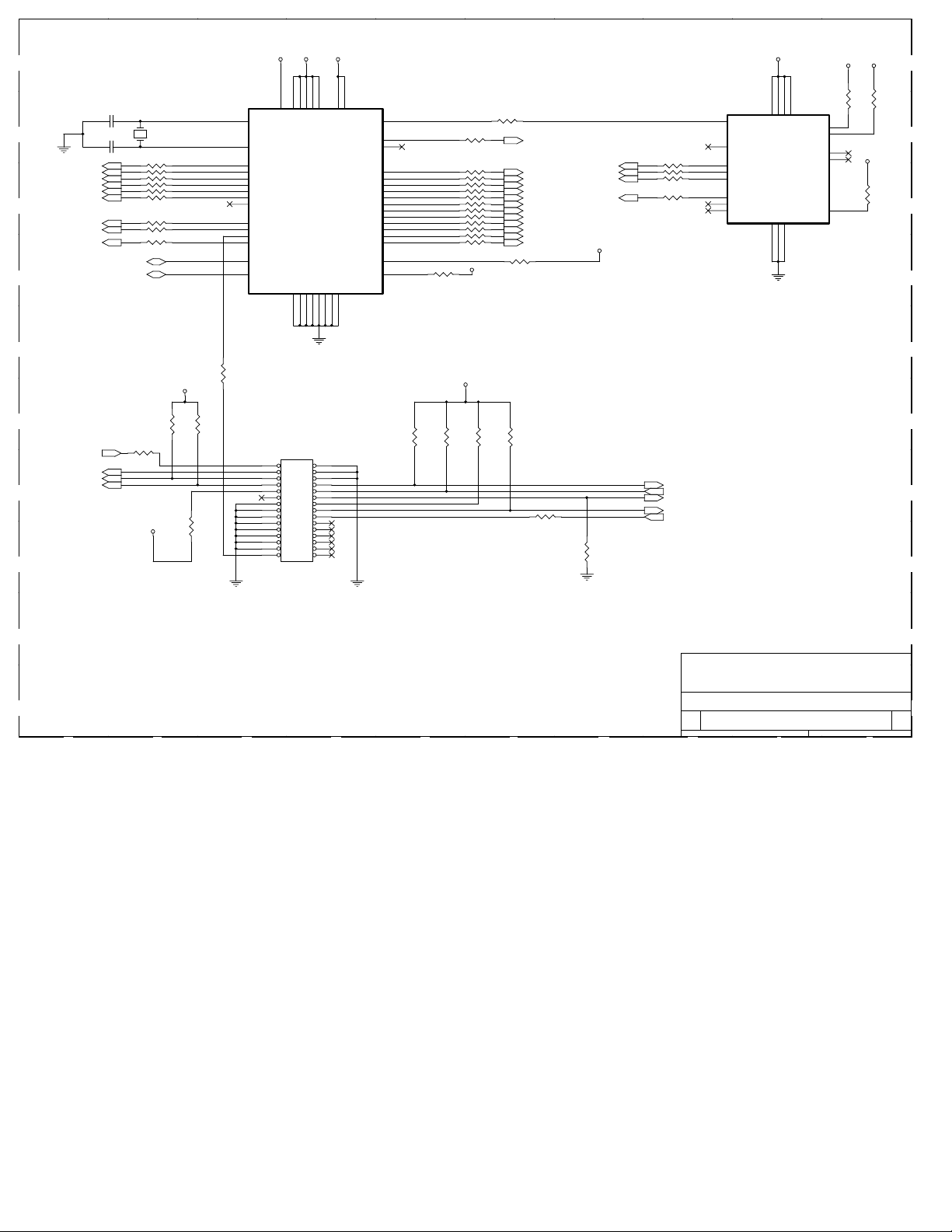

440LX CUSTOMER REFERENCE DESIGN

4 4

TITLE

COVER SHEET

BLOCK DIAGRAM

SLOT1 CONN.

CLK SYNTHESIZER

PAC

DIMM SOCKETS

3 3

2 2

1 1

PIIX4

ULTRA I/O

AGP CONN.

PCI CONN.

ISA CONN.

IDE CONN.

USB CONN

FLASH BIOS

PARALLEL

SERIAL/FLOPPY

KEYBD/MOUSE

VRM

PWR CONN

GTL TERMINATION

PCI/AGP PULLUPS

ISA PULLUPS

PAC DECOUP

BULK DECOUP

VREF PAGE

REVISION HISTORY

PAGE

1

2

3,4

5

6,7,8

9,10,11

12,13

14

15

16,17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

THESE SCHEMATICS ARE PROVIDED "AS IS" WITH NO

WARRANTIES WHATSOEVER, INCLUDING ANY WARRANTY

OF MERCHANTABILITY, FITNESS FOR ANY PARTICULAR

PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT

OF PROPOSAL, SCHEMATIC OR SAMPLE.

No license, express or implied, by

estoppel or otherwise, to any

intellectual property rights is granted

herein.

Intel disclaims all liability, including

liability for infringement of any

proprietary rights, relating to use of

information in this specification. Intel

does not warrant or represent that such

use will not infringe such rights.

I2C is a two-wire communications

bus/protocol developed by Philips. SMBus

is a subset of the I2C bus/protocol and

was developed by Intel. Implementations

of the I2C bus/protocol or the SMBus

bus/protocol may require licenses from

various entities, including Philips

Electronics N.V. and North American

Philips Corporation.

*Third-party brands and names are the property of their

respective owners.

Copyright * Intel Corporation 1996

INTEL CORPORATION

PCI COMPONENTS DIVISION

1900 PRAIRIE CITY RD. FM5-62

FOLSOM, CA 95630

Title

Size Document Number Rev

A

Intel 440LX PCIset 1.4

A

B

C

Date: Sheet of

D

133

E

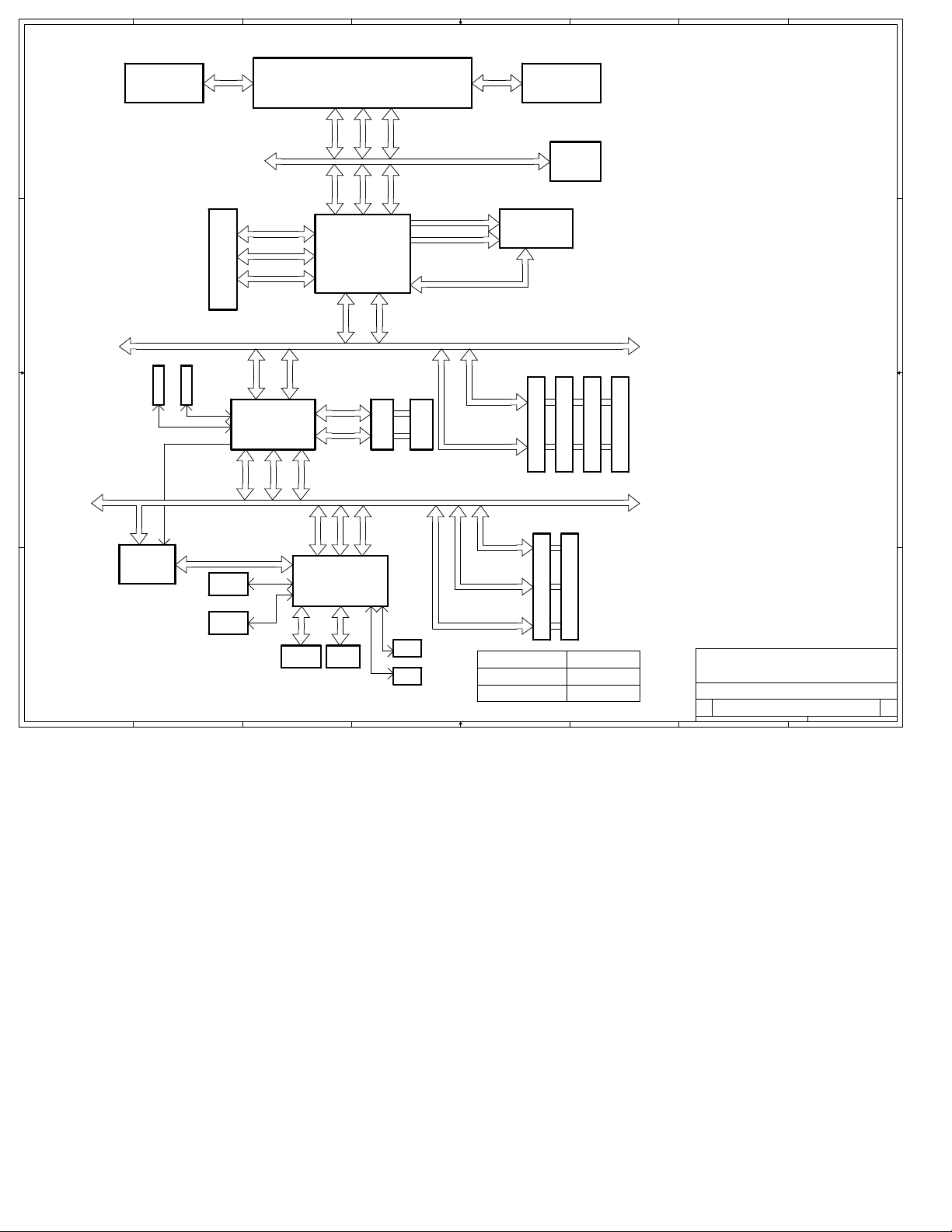

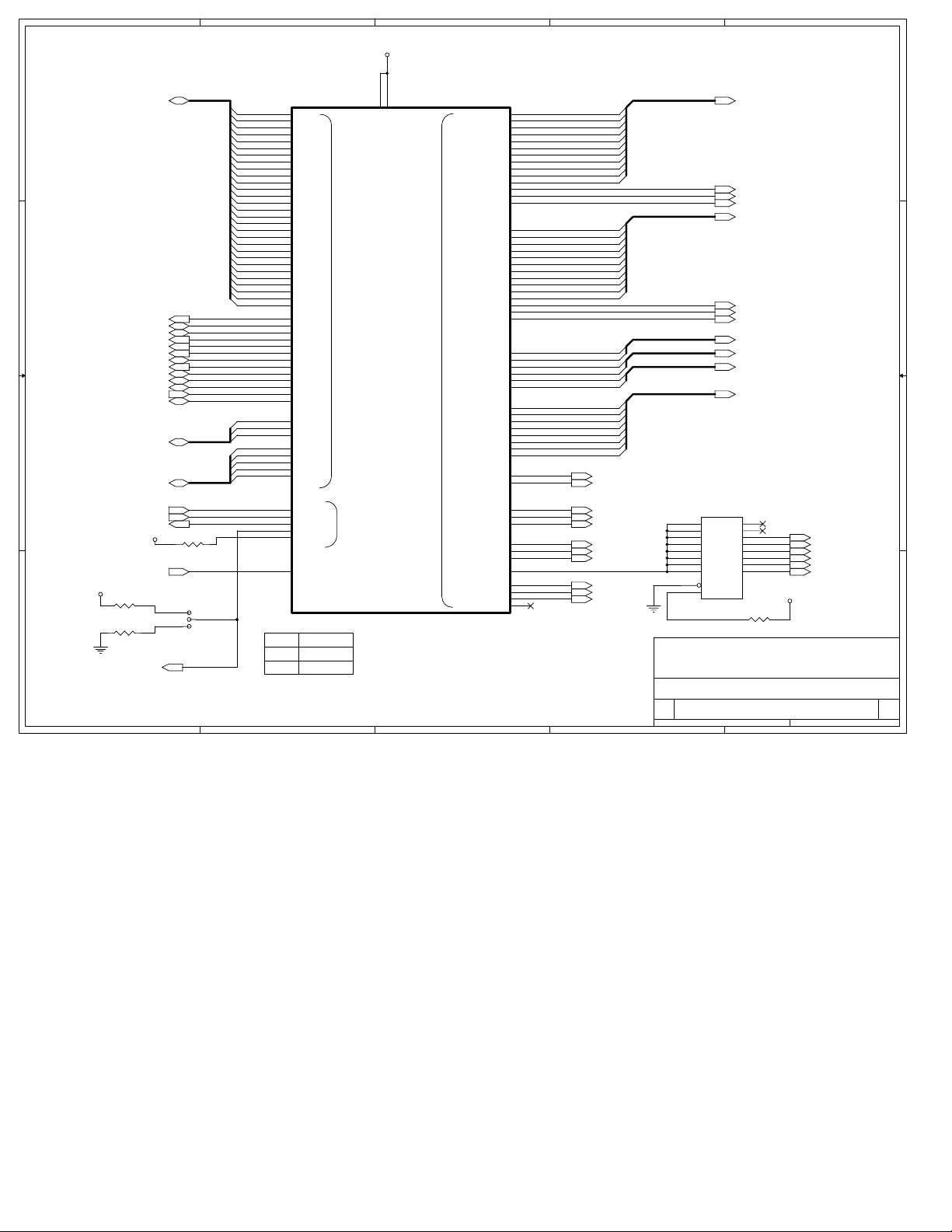

Page 2

1

VTT GEN.

A A

VRM

PG. 25

2

3

KLAMATH ’SLOT 1’

CONNECTOR

PG. 3,4

ADDR

CNTL

ADDR

CNTL

4

DATA

HOST BUS

DATA

5

CLOCK

ITP CON.

PG. 5

GTL

TERM.

PG. 27

6

7

THIS DRAWING CONTAINS INFORMATION

WHICH HAS NOT BEEN VERIFIED FOR

MANUFACTURING AN END USER PRODUCT.

INTEL IS NOT RESPONSIBLE FOR THE

MISUSE OF THIS INFORMATION.

8

DATA

MEMORY

3 DIMM

MODULES

PGS. 9-11

ADDR/DATA

AGP

CONN.

B B

PG. 15

CNTL

AGP SIDEBAND

ADD/DATA

PAC

82443LX

492 BGA

PG. 6-8

CNTL

CNTL

ADDR

PCI BUS

ADDR

ADD/DATA

PIIX4

82371AB

324 BGA

PGS. 12,13

CNTL

CNTL

ADDR/DATA

CNTL

DATA

2 PCI IDE

CONNECTORS

PRIMARY

IDE

PG. 19

SECONDARY

IDE

CNTL

ADDR/DATA

PGS. 16,17

PCI CONN

PCI CONN

PCI CONN

PCI CONN

PG. 20

2 USB CONN.

C C

USB

CONTROL

USB

ISA BUS

CNTL

DATA

FLOPPY

CONN.

PG. 23

3

ADDR

ULTRA

I/O

PG.14

PARA.

CONN.

PG. 22

SER.

CONN.

PG .23

SER.

CONN.

ADDR

CNTL

DATA

RESET, POWER CONNECTORS

ISA, PCI RESISTORS

DECOUPLING CAPACITORS

4

ADDR

FLASH

BIOS

PG. 21

D D

1

DATA

2

X-BUS

KEYBOARD

PG. 24

MOUSE

PG.24

PG 18

ISA

CONN

ISA

CONN

PG. 26

PG. 28,29

PGS. 30-32

5

6

INTEL CORPORATION

PCI COMPONENTS DIVISION

1900 PRAIRIE CITY RD. FM5-62

FOLSOM, CA 95630

Title

Intel 440LX PCIset Block Diagram

Size Document Number Rev

Intel 440LX PCISET 1.4

Custom

Date: Sheet of

7

233Thursday, May 07, 1998

8

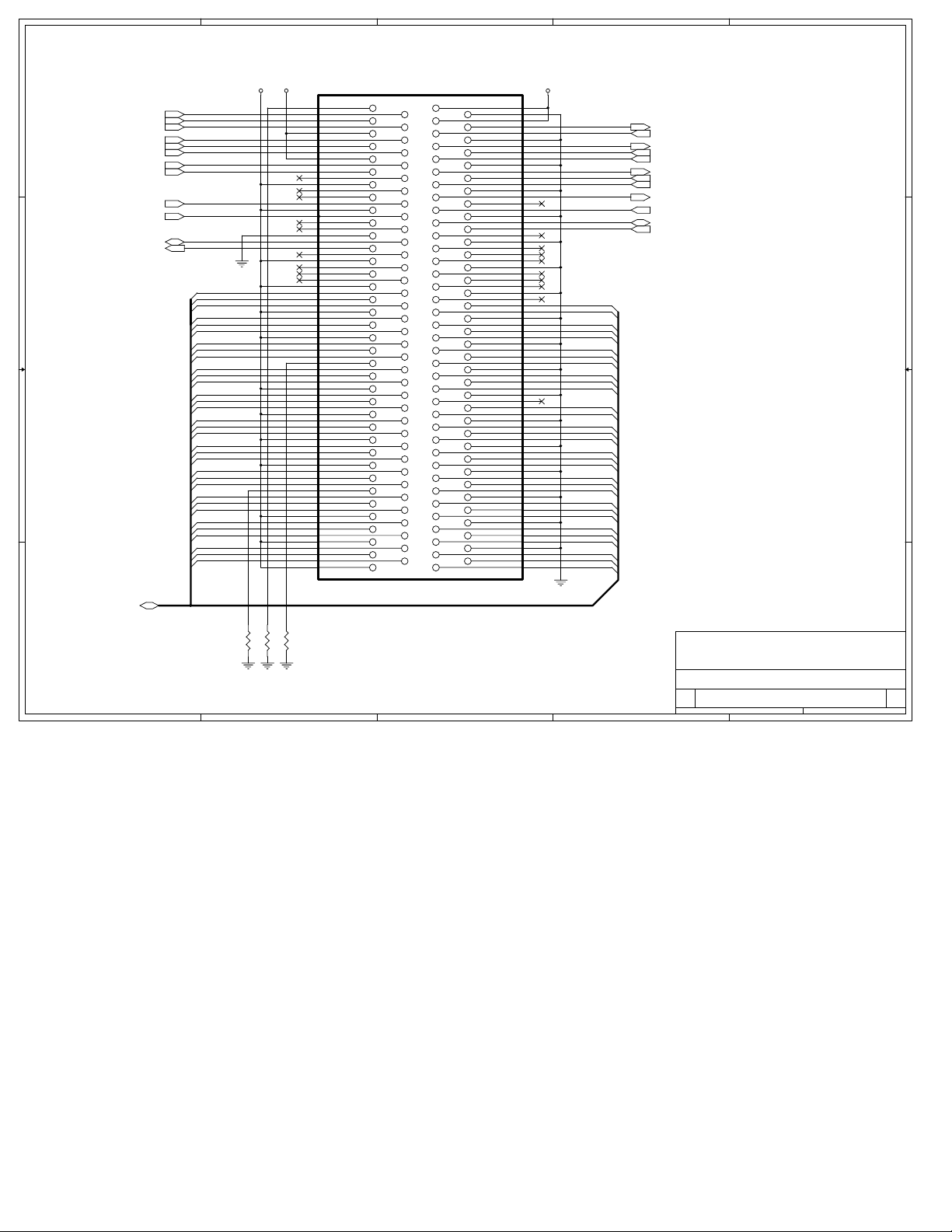

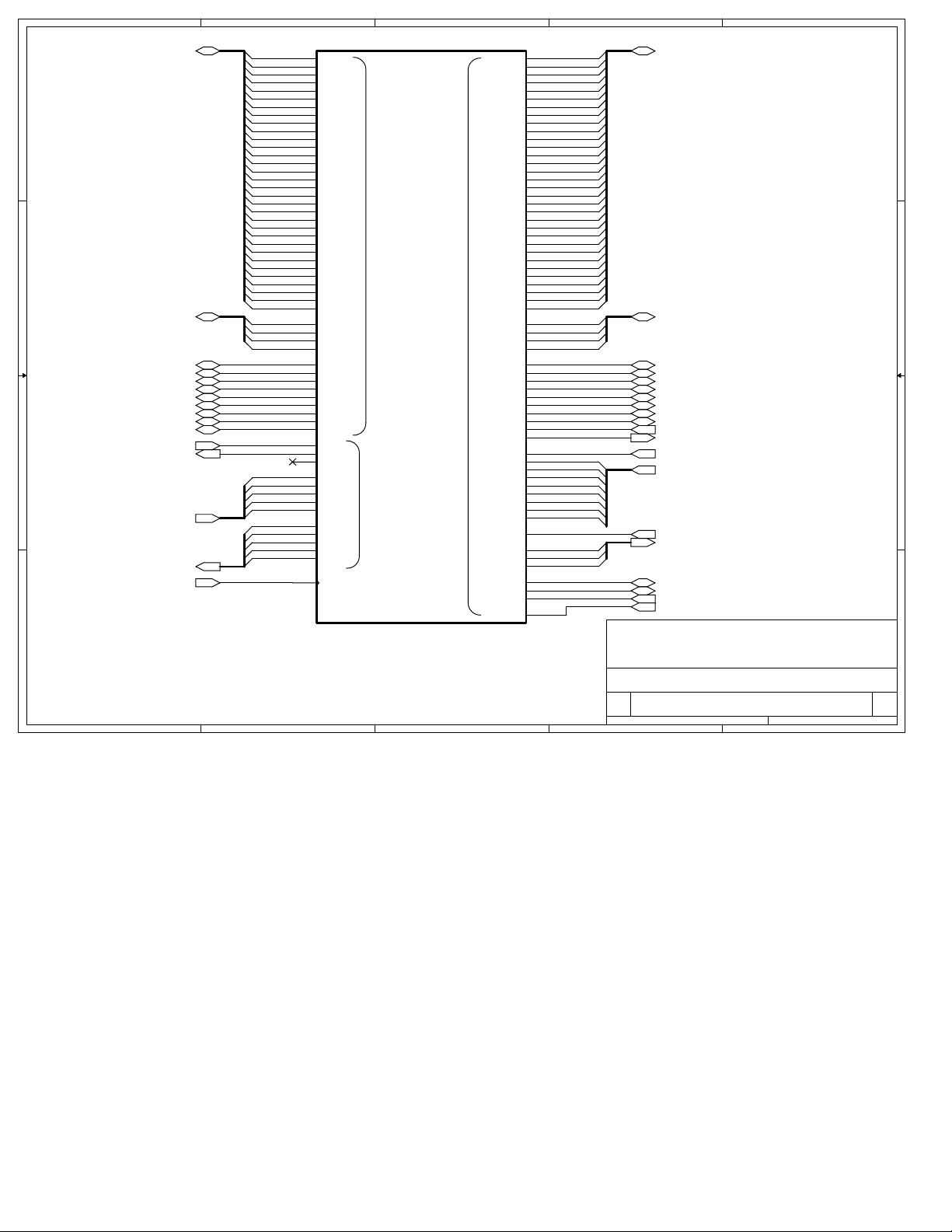

Page 3

A

B

C

D

E

IERR#

A20M#

FERR#

LINT[0]

PICD[0]

PREQ#

BP#[3]

BINIT#

D#[61]

D#[55]

D#[60]

D#[53]

D#[57]

D#[46]

D#[49]

D#[51]

D#[42]

D#[45]

D#[39]

D#[43]

D#[37]

D#[33]

D#[35]

D#[31]

D#[30]

D#[27]

D#[24]

D#[23]

D#[21]

D#[16]

D#[13]

D#[11]

D#[10]

D#[14]

VTT

A01

A02

GND

A03

A04

A05

A06

GND

A07

A08

A09

TDI

A10

GND

A11

TDO

A12

A13

A14

GND

A15

A16

A17

A18

GND

A19

A20

A21

A22

GND

A23

A24

A25

A26

GND

A27

A28

A29

A30

GND

A31

A32

HD#61

A33

HD#55

A34

GND

A35

HD#60

A36

HD#53

A37

HD#57

A38

GND

A39

HD#46

A40

HD#49

A41

HD#51

A42

GND

A43

HD#42

A44

HD#45

A45

HD#39

A46

GND

A47

A48

HD#43

A49

HD#37

A50

GND

A51

HD#33

A52

HD#35

A53

HD#31

A54

GND

A55

HD#30

A56

HD#27

A57

HD#24

A58

GND

A59

HD#23

A60

HD#21

A61

HD#16

A62

GND

A63

HD#13

A64

HD#11

A65

HD#10

A66

GND

A67

D#[9]

D#[8]

GND

D#[5]

D#[3]

D#[1]

HD#14

A68

HD#9

A69

HD#8

A70

A71

HD#5

A72

HD#3

A73

HD#1

IERR_PU 28

A20M# 25,28

FERR# 13,28

IGNNE# 25,28

TDI 5

TDO 5

POWERGOOD 26

TESTHI_PU 28

THERMTRIP# 28

LINT0 25,28

PICD0 28

PREQ#0 5

VTT

VCCVID

4 4

FLUSH#28

SMI#13,28

HINIT#6,13,28

STPCLK#13,28

TCK5

SLP#13,28

TMS5

TRST#5

LINT125,28

PICCLK5

PICD128

PRDY#05,27

3 3

2 2

HD#62

HD#58

HD#63

HD#56

HD#50

HD#54

HD#59

HD#48

HD#52

HD#41

HD#47

HD#44

HD#36

HD#40

HD#34

HD#38

HD#32

HD#28

HD#29

HD#26

HD#25

HD#22

HD#19

HD#18

HD#20

HD#17

HD#15

HD#12

HD#7

HD#6

HD#4

HD#2

HD#0

EMI_PD3

EMI_PD2

J1A

B01

EMI

B02

FLUSH#

B03

SMI#

B04

INIT#

B05

VCC_VTT

B06

STPCLK#

B07

TCK

B08

SLP#

B09

VCC_VTT

B10

TMS

B11

TRST#

B12

RESERVED

B13

VCC_VID

B14

THRMDA

B15

THRMDC

B16

LINT[1]

B17

VCC_VID

B18

PICCLK

B19

BP#[2]

B20

RESERVED

B21

100/66#

B22

PICD[1]

B23

PRDY#

B24

BPM#[1]

B25

VCC_VID

B26

DEP#[2]

B27

DEP#[4]

B28

DEP#[7]

B29

VCC_VID

B30

D#[62]

B31

D#[58]

B32

D#[63]

B33

VCC_VID

B34

D#[56]

B35

D#[50]

B36

D#[54]

B37

VCC_VID

B38

D#[59]

B39

D#[48]

B40

D#[52]

B41

EMI

B42

D#[41]

B43

D#[47]

B44

D#[44]

B45

VCC_VID

B46

D#[36]

B47

D#[40]

B48

D#[34]

B49

VCC_VID

B50

D#[38]

B51

D#[32]

B52

D#[28]

B53

VCC_VID

B54

D#[29]

B55

D#[26]

B56

D#[25]

B57

VCC_VID

B58

D#[22]

B59

D#[19]

B60

D#[18]

B61

EMI

B62

D#[20]

B63

D#[17]

B64

D#[15]

B65

VCC_VID

B66

D#[12]

B67

D#[7]

B68

D#[6]

B69

VCC_VID

B70

D#[4]

B71

D#[2]

B72

D#[0]

B73

VCC_VID

EMI_PD1

SLOT1_0.7

VCC_VTT

VCC_VTT

IGNNE#

PWRGOOD

TESTHI1

THERMTRIP#

RESERVED

BPM#[0]

DEP#[0]

DEP#[1]

DEP#[3]

DEP#[5]

DEP#[6]

RESERVED

SLOT 1a

HD#[63:0]8,27

1 1

A

R40R30R5

0

B

C

INTEL CORPORATION

PCI COMPONENTS DIVISION

1900 PRAIRIE CITY RD. FM5-62

FOLSOM, CA 95630

Title

SLOT 1 (PART I)

Size Document Number Rev

Intel 440LX PCISET 1.4

Custom

Date: Sheet of

D

333Thursday, May 07, 1998

E

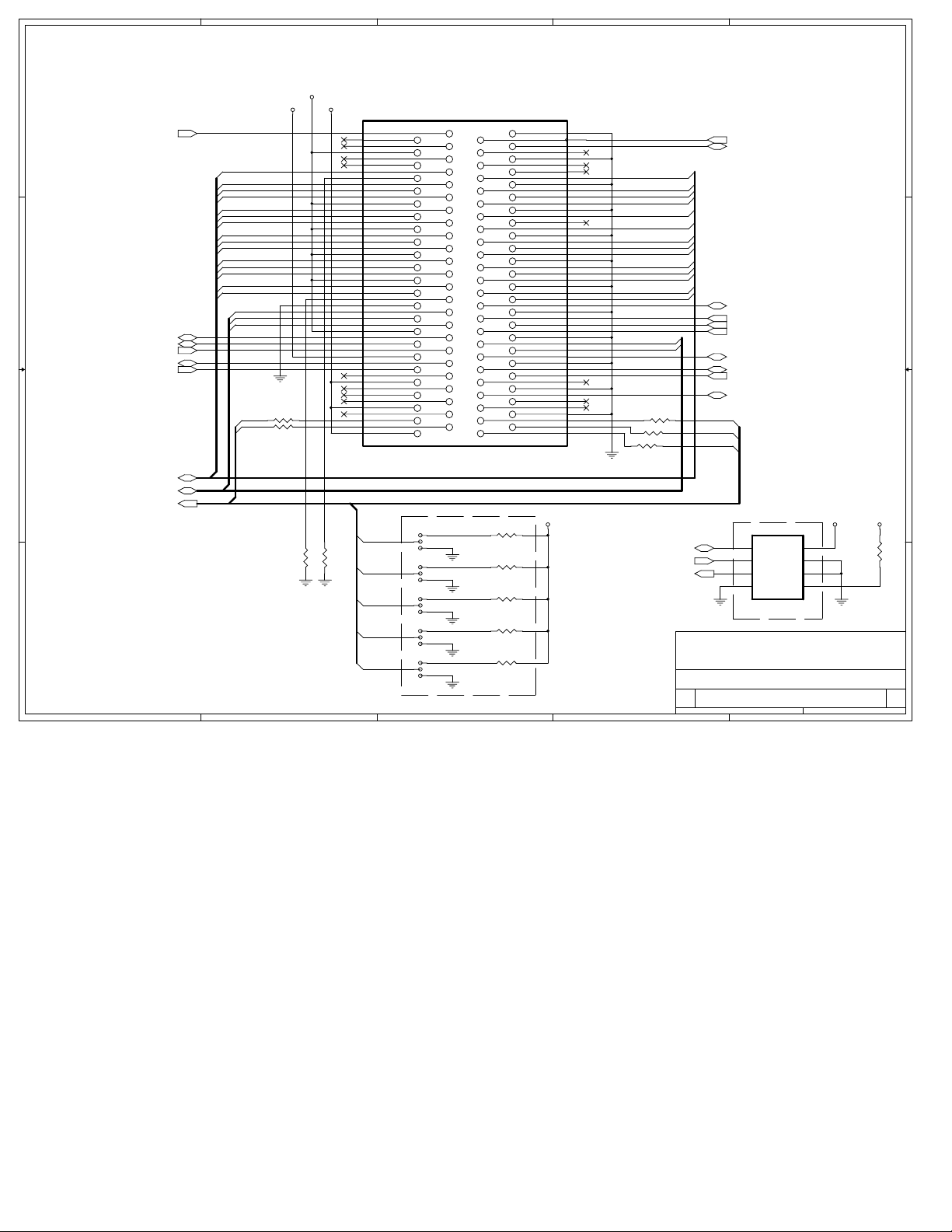

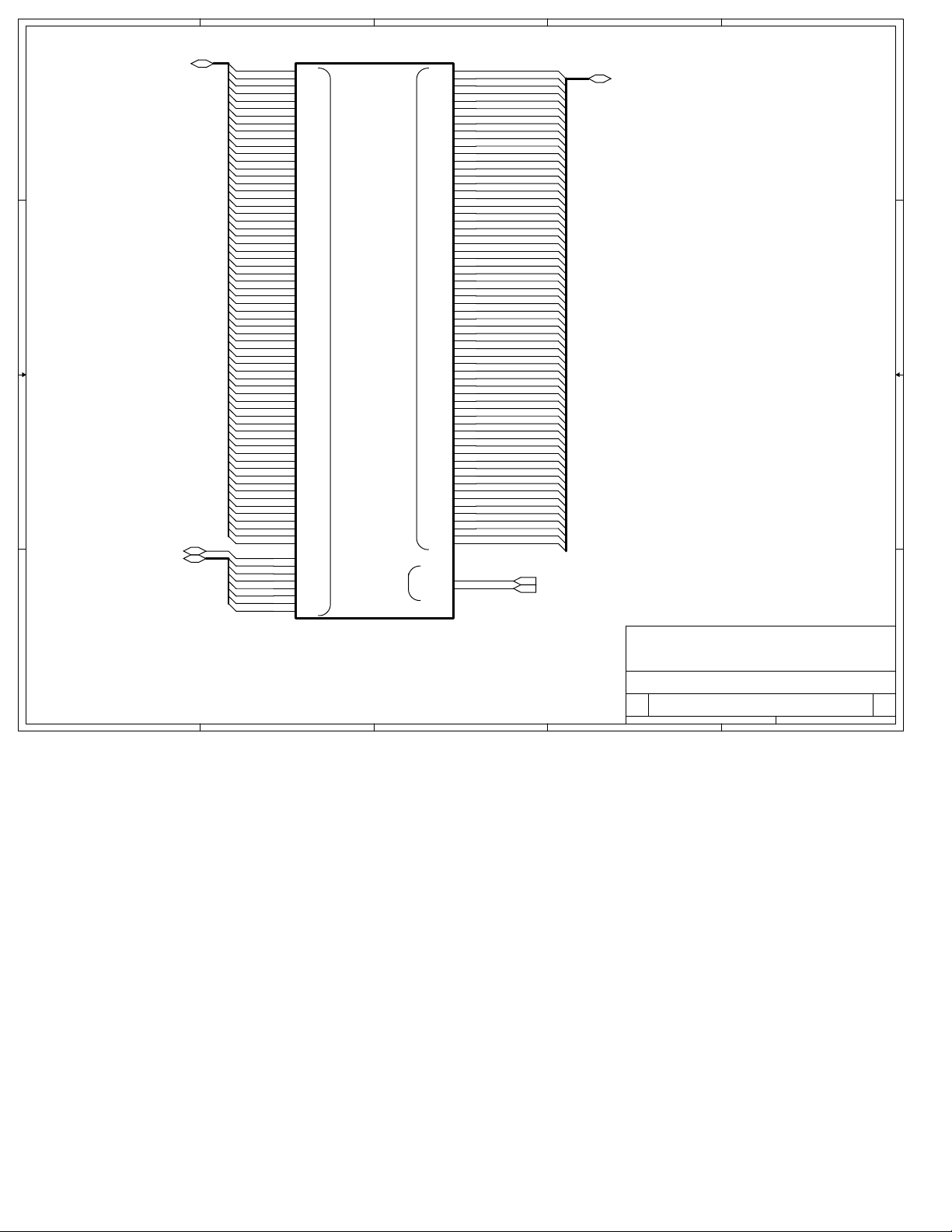

Page 4

A

4 4

HRESET#5,6,27

HA#29

HA#26

HA#24

HA#28

HA#20

HA#21

HA#25

HA#15

HA#17

HA#11

HA#12

HA#8

HA#7

3 3

HLOCK#6,27

DRDY#6,27

RS#06,27

HIT#6,27

RS#26,27

2 2

HA#[31:3]6,27

HREQ#[4:0]6,27

HA#3

HA#6

HREQ#0

HREQ#1

HREQ#4

VID[4:0]25

1 1

A

VID3

VID0

R220

R222

B

VCCVID

VCC3

VCC

C

D

E

J1B

B74

RESET#

B75

BREQ1#

B76

FRCERR#

B77

VCC_VID

B78

A#[35]

B79

A#[32]

B80

A#[29]

B81

EMI

B82

A#[26]

B83

A#[24]

B84

A#[28]

B85

VCC_VID

B86

A#[20]

B87

A#[21]

B88

A#[25]

B89

VCC_VID

B90

A#[15]

B91

A#[17]

B92

A#[11]

B93

VCC_VID

B94

A#[12]

B95

A#[8]

B96

A#[7]

B97

VCC_VID

B98

A#[3]

B99

A#[6]

B100

EMI

B101

S_O#

B102

REQ#[0]

B103

REQ#[1]

B104

REQ#[4]

B105

VCC_VID

B106

LOCK#

B107

DRDY#

B108

RS#[0]

B109

VCC_5

B110

HIT#

B111

RS#[2]

B112

RESERVED

B113

VCC_3

B114

RP#

B115

RSP#

B116

AP#[1]

B117

VCC_3

B118

B119

B120

B121

AERR#

VID[3]

VID[0]

VCC_3

SLOT1_0.7

SLOT 1b

0

RV3

RV0

0

BREQ0#

BERR#

RESERVED

TRDY#

DEFER#

REQ#[2]

REQ#[3]

DBSY#

RESERVED

RESERVED

A#[33]

A#[34]

A#[30]

A#[31]

A#[27]

A#[22]

A#[23]

A#[19]

A#[18]

A#[16]

A#[13]

A#[14]

A#[10]

BPRI#

HITM#

RS#[1]

AP#[0]

VID[2]

VID[1]

VID[4]

A74

GND

A75

BCLK

A76

A77

A78

GND

A79

A80

A81

A82

GND

A83

A84

A85

A86

GND

A87

A88

A89

A90

GND

A91

A92

A93

A94

GND

A95

A96

A97

A#[5]

A98

GND

A99

A#[9]

A100

A#[4]

A101

BNR#

A102

GND

A103

A104

A105

A106

GND

A107

A108

A109

A110

GND

A111

A112

A113

A114

GND

A115

ADS#

A116

A117

A118

GND

A119

RV2

A120

RV1

A121

RV4

HREQ#2

HREQ#3

R223

R224

HA#30

HA#31

HA#27

HA#22

HA#23

HA#19

HA#18

HA#16

HA#13

HA#14

HA#10

HA#5

HA#9

HA#4

R221

0

0

0

VID2

VID1

VID4

CPUHCLK 5

BREQ#0 6,27

BNR# 6,27

BPRI# 6,27

HTRDY# 6,27

DEFER# 6,27

HITM# 6,27

DBSY# 6,27

RS#1 6,27

ADS# 6,27

NOTE :

U25 IS DEFAULT NO STUFF DEVICE.

LM75 IS 3.3 VOLT THERMAL SENSOR.

LOCATE NEAR THE CPU AND PAC.

SLAVE ADDRESS = 1001100b

EMI_PD4

EMI_PD5

JP14

SEL_VID0

R70R6

0

VID1

VID2

VID3

VID4

B

VID0

1

2

3

JP15

SEL_VID1

1

2

3

JP16

SEL_VID2

1

2

3

JP17

SEL_VID3

1

2

3

JP18

SEL_VID4

1

2

3

R207

8.2K

R209

8.2K

R210

8.2K

R211

8.2K

R212

8.2K

C

JP14 - JP18 , R207 AND R209 - R212

ARE DEFAULT NO-STUFF

NOTE :

SMBDATA5,9,10,11,13,28

SMBCLK5,9,10,11,13,28

THERM#13,28

INTEL CORPORATION

PCI COMPONENTS DIVISION

1900 PRAIRIE CITY RD. FM5-62

FOLSOM, CA 95630

Title

SLOT 1 (PART II)

Size Document Number Rev

Custom

Date: Sheet of

D

U25

1

SDAT

2

SCLK

3

OTS

4

GND

LM75_0.1

Intel 440LX PCISET 1.4

VCC3

VCC3 VCC3VCC

8

7

SA0

6

SA1

5

SA2

R208

8.2K

TW_PU1

433Thursday, May 07, 1998

E

Page 5

A

10 10

9 9

PX4PCLK13

PCONNCLK116

PCONNCLK216

PCONNCLK317

PCONNCLK417

PACPCLK7

8 8

CPUHCLK4

PACHCLK6

AGPHCLK15

SMBDATA4,9,10,11,13,28

7 7

SMBCLK4,9,10,11,13,28

NOTE :

SLAVE ADDR. = 1101010b

C1

10pF

C3

10pF

R171 33

R172 33

R174

R176 33

R178 33

R180 33

R185 33

R187

R190 33

B

Y1

14.318

C

VCC3

U1

1

XTLI1

XTLO1

R_PCLKF

R_PCLK0

33

R_PCLK1

R_PCLK2

R_PCLK3

R_PCLK4

R_CCLK0

33

R_CCLK1

4

XTALIN

VDD

5

XTALOUT

7

PCI_F

8

PCI0

10

PCI1

11

PCI2

12

13

15

44

43

41

40

23

24

R_CCLK2 ITP_CLK

PCI3

PCI4

PCI5

CPU0

CPU1

CPU2

CPU3

SDATA

SCLOCK

CK3D_0.9

48 SSOP

VCC2.5

VCC3

6

14

19

30

VDDQ3

VDDQ3

VDDQ3

SDRAM5/PWR_DWN#

SDRAM6/CPU_STOP#

SDRAM7/PCI_STOP#

GND

GND

GND

GND

GND33GND

3

9

16

22

27

D

SEL_66/60#

GND

GND

45

39

REFOUT

VDDQ248VDDQ242VDDQ336VDDQ3

IOAPIC0

IOAPIC1

SDRAM0

SDRAM1

SDRAM2

SDRAM3

SDRAM4

SDRAM8

SDRAM9

SDRAM10

SDRAM11

MODE

E

2

R_IO_XTALIN IO_XTALIN

R_ACLK0

R_DCLK0

R_DCLK1

R_DCLK2

R_DCLK3

R_DCLK4

R_DCLK5

R_DCLK6

R_DCLK7

R_DCLK8

R_DCLK9

R_DCLK10

R_DCLK11R_CCLK3

MPU

R170 33

R173

R175

R177

R179 22

R181

R182

R183

R184

R186

R188

R189

R191

FSEL1

R16

10K

47

46

38

37

35

34

32

31

29

28

21

20

18

17

26

25

VCC3

F

R198 22

22

22

22

22

22

22

22

22

22

22

22

PICCLK 3

DIMMHCLK0 9

DIMMHCLK1 9

DIMMHCLK2 9

DIMMHCLK3 9

DIMMHCLK4 10

DIMMHCLK5 10

DIMMHCLK6 10

DIMMHCLK7 10

DIMMHCLK8 11

DIMMHCLK9 11

DIMMHCLK10 11

DIMMHCLK11 11

R15

8.2K

VCC3

G

OSC013

OSC118

OSC314

48MHz13

R194

R195

R196

R197

H

2

3

22

17

C1

22

19

C2

22

20

C3

22

14

C4

15

12

U20

XTALIN

XTALOUT

SREF0

REF1

REF2

48MHz

48MHz

24MHz

CKIO

I

VCC3

1

18

8

13

VDD

VDD

VDD

VDD

0.5X AUDIO

1X AUDIO

20 SSOP

GND

GND

GND

4

11

16

SEL0

SEL1

OE

VCC3 VCC3

R10

10K

9

RS0

10

RS1

7

6

5

RO1

J

VCC3

R11

10K

R14

10K

6 6

R192

VCC2.5

R18

5 5

HRESET#4,6,27

DBRESET#26

TCK3

4 4

TMS3

100

R27

240

VTT

3 3

33

R19

150

OPTIONAL

ITP TEST

CONNECTOR

ITP_RST

ITP_PON

R29

1K

5%

J2

1 2

3 4

5 6

7 8

9 10

11 12

13 14

15 16

17 18

19 20

21 22

23 24

25 26

27 28

29 30

ITP CONN

BSEN_PU1

R_PRDY#0

VCC2.5

R20

R21

330

150

R23

R22

330

330

TDI 3

TDO 3

TRST# 3

PREQ#0 3

R28 240

R30

470

PRDY#0 3,27

2 2

INTEL CORPORATION

PCI COMPONENTS DIVISION

1900 PRAIRIE CITY RD. FM5-62

FOLSOM, CA 95630

Title

1 1

A

B

C

D

E

F

G

CLOCK SYNTHESIZER

Size Document Number Rev

Intel 440LX PCISET 1.4

Custom

Date: Sheet of

H

I

533Thursday, May 07, 1998

J

Page 6

A

VCC3

HA#[31:3]4,27

HRESET#4,5,27

ADS#4,27

BNR#4,27

HINIT#3,13,28

BREQ#04,27

BPRI#4,27

DBSY#4,27

DEFER#4,27

DRDY#4,27

HIT#4,27

HITM#4,27

HLOCK#4,27

HTRDY#4,27

RS#[2:0]4,27

HREQ#[4:0]4,27

PACHCLK5

PCIRST#9,12,15,16,17

CRESET#25

VCC3

VREF5V13

R32

8.2K

R236

5.6K

JP2 DEFAULT = 2-3

FOR MAX IOQ DEPTH.

ECCERR#26

A

R31

8.2K

JP2

1

3

NOTE :

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

2

4 4

3 3

2 2

1 1

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

RS#0

RS#1

RS#2

R_TS1

M22

W26

AE25

M26

N26

N23

N24

M25

M24

N25

M23

L24

L25

L23

K22

K25

K24

L22

J26

J24

J25

H25

J23

H23

K21

G26

H24

J21

G25

H21

H22

K26

P26

P24

A13

L26

R24

V25

R22

R26

U26

U25

B25

P23

T24

U22

P25

R23

T23

T25

R25

AE2

V23

U23

JP2

2-3

B

U3-1

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

CPURST#

ADS#

BNR#

INIT#

BREQ0#

BPRI#

DBSY#

DEFER#

DRDY#

HIT#

HITM#

HLOCK#

HTRDY#

RS#0

RS#1

RS#2

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

T2

B2

MISC

HCLKIN

RSTIN#

CRESET#

ECC_ERR#

TESTIN#

A1, A26, AA6, AA7-10, AA17, AA20,

AA21, AB5, AB13, AB22, AF1, AF26,

C15, E5, E22, F6, F8, F9, F17,

REF5V

F19, F21, G21, H6, J6, K6, L12-16,

M12-16, N22, N12-16, P13-16, R5,

R14-16 , T4, U21, V6, W6, W21

PAC_1.0

IOQ DEPTH

1-2

1

MAX

B

VTT

F23

U24

VTT

VTT

VCC3 PINS:

C3, E13, F20, G6, L11,

M11, N11, P11, P12, P22,

R3, R4, R11-13, T11-16,

AD3, AD12, AD24

82443LX

492 BGA

HOST INTERFACE

VSS PINS:

RCSA6# / MAB2

RCSA7# / MAB3

SCAS3# / MAB4

SRAS3# / MAB5

RCSB0# / MAB6

RCSB1# / MAB7

RCSB2# / MAB8

RCSB3# / MAB9

RCSB4# / MAB10

RCSB5# / MAB11

RCSB6# / MAB12

RCSB7# / MAB13

DRAM INTERFACE

82443LXa

C

AC13

MAA0

AE13

MAA1

AB12

MAA2

AD13

MAA3

AC14

MAA4

AD15

MAA5

AC15

MAA6

AD16

MAA7

AC17

MAA8

AE17

MAA9

AA18

MAA10

AE18

MAA11

AE19

MAA12

AF19

MAA13

AD14

MAB0

AF14

MAB1

AE14

AB14

AE15

AF15

AA19

AF16

AB19

AE16

AF18

AD18

AB18

AD17

AB20

RCSA0#

AE20

RCSA1#

AF20

RCSA2#

AC20

RCSA3#

AC19

RCSA4#

AB17

RCSA5#

AD9

CDQA0#

AC9

CDQA1#

AF21

CDQA2#

AD21

CDQA3#

AD11

CDQA4#

AE11

CDQA5#

AE21

CDQA6#

AC21

CDQA7#

AF12

CDQB1#

AE12

CDQB5#

AF11

SRAS0#

AC10

SRAS1#

AF13

SRAS2#

AD10

SCAS0#

AE9

SCAS1#

AF10

SCAS2#

AD20

AF8

AE10

AF9

AC12

CKE

WE#0

WE#1

WE#2

WE#3

CKE

NOTE:

CKE IS PULLED DOWN BY DEFAULT

FOR CONFIGURATION 2.

SCHEMATICS WITH CONFIGURATION

1 NEED A PULL-UP TO VCC3

C

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12MAA12

MAA13MAA13MAA13

MAB0

MAB1

MAB2

MAB3

MAB4

MAB5

MAB6

MAB7

MAB8

MAB9

MAB10

MAB11

MAB12MAB12

MAB13MAB13MAB13

RCSA#0

RCSA#1

RCSA#2

RCSA#3

RCSA#4

RCSA#5

CDQA#0

CDQA#1

CDQA#2

CDQA#3

CDQA#4

CDQA#5

CDQA#6

CDQA#7

CDQB#1 9

CDQB#5 9

SRAS#0 11

SRAS#1 10

SRAS#2 9

SCAS#0 11

SCAS#1 10

SCAS#2 9

WE#0 11

WE#1 10

WE#2 9

D

MAA[10:0] 10,11

MAA11 10,11

MAA12 10,11

MAA13 10,11

MAB[10:0] 9

MAB11 9

MAB12 9

MAB13 9

RCSA#[1:0] 11

RCSA#[3:2] 10

RCSA#[5:4] 9

CDQA#[7:0] 9,10,11

E

NOTE :

MUST USE CMOS BUFFER TO AVOID

OVERIDE OF INTERNAL PULLDOWN

ON CKE SIGNAL.

U22

2

3

4

5

6

7

8

9

19

1

R_CKEBUF

INTEL CORPORATION

PCI COMPONENTS DIVISION

1900 PRAIRIE CITY RD. FM5-62

FOLSOM, CA 95630

Title

PAC HOST AND DRAM INTERFACES

Size Document Number Rev

Intel 440LX PCISET 1.4

Custom

Date: Sheet of

D

A1

A2

A3

A4

A5

A6

A7

A8

G

DIR

74LVC245

18

B1

17

B2

16

B3

15

B4

14

B5

13

B6

12

B7

11

B8

R164

8.2K

VCC3

B_CKE0 11

B_CKE1 11

B_CKE2 10

B_CKE3 10

B_CKE4 9

B_CKE5 9

633Thursday, May 07, 1998

E

Page 7

A

AD[31:0]12,16,17

4 4

3 3

C/BE#[3:0]12,16,17

FRAME#12,16,17,28

DEVSEL#12,16,17,28

IRDY#12,16,17,28

TRDY#12,16,17,28

STOP#12,16,17,28

PAR12,16,17

PERR#16,17,28

SERR#12,16,17,28

PLOCK#16,17,28

PHLD#12,28

2 2

1 1

PHLDA#12,28

NOTE :

REQ#4 IS UNUSED.

PULLED UP ONLY.

REQ#[4:0]16,17,28

GNT#[4:0]16,17,28

PACPCLK5

A

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

C/BE#0

C/BE#1

C/BE#2

C/BE#3

REQ#0

REQ#1

REQ#2

REQ#3

REQ#4

GNT#0

GNT#1

GNT#2

GNT#3

GNT#4

B

U3-2

H4

AD0

G4

AD1

G5

AD2

F4

AD3

E3

AD4

F5

AD5

E4

AD6

D4

AD7

E6

AD8

D5

AD9

C2

AD10

F7

AD11

C1

AD12

B3

AD13

B1

AD14

B4

AD15

C8

AD16

D7

AD17

B8

AD18

E8

AD19

D8

AD20

C9

AD21

B9

AD22

E9

AD23

D9

AD24

D10

AD25

C10

AD26

F10

AD27

B10

AD28

E10

AD29

B11

AD30

E11

AD31

C4

C/BE0#

A2

C/BE1#

A7

C/BE2#

A9

C/BE3#

C7

FRAME#

C6

DEVSEL#

A6

IRDY#

B6

TRDY#

A5

STOP#

A3

PAR

C5

PERR#

A4

SERR#

B5

PLOCK#

E7

PHLD#

A8

PHLDA#

V24

WSC#

A12

REQ0#

E12

REQ1#

C13

REQ2#

B13

REQ3#

D13

REQ4#

A11

GNT0#

D11

GNT1#

C11

GNT2#

B12

GNT3#

D12

GNT4#

C12

PCLKIN

PAC_1.0

B

VCC3 PINS :

C3, E13, F20, G6, L11,

M11, N11, P11, P12,

P22, R3, R4, R11-13,

T11-16, AD12, AD3,

AD24

82443LX

492 BGA

PCI INTERFACE

PCI ARB.

VSS PINS :

A1, A26, AA6, AA7-10,

AA17, AA20, AA21, AB5,

AB13, AB22, AF1, AF26,

C15, E5, E22, F6, F8, F9,

F17, F19, F21, G21, H6,

J6, K6, L12-16, M12-16,

N22, N12-16, P13-16, R5,

R14-16 , T4, U21, V6, W6,

W21

C

GAD0

GAD1

GAD2

GAD3

GAD4

GAD5

GAD6

GAD7

GAD8

GAD9

GAD10

GAD11

GAD12

GAD13

GAD14

GAD15

GAD16

GAD17

GAD18

GAD19

GAD20

GAD21

GAD22

GAD23

GAD24

GAD25

GAD26

GAD27

GAD28

GAD29

GAD30

GAD31

GC/BE0#

GC/BE1#

GC/BE2#

GC/BE3#

GFRAME#

GDEVSEL#

GIRDY#

GTRDY#

GSTOP#

GPAR

GPERR#

GSERR#

AGP INTERFACE

GREQ#

GGNT#

PIPE#

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

DBF#

ST0

ST1

ST2

ADSTB-A

ADSTB-B

SBSTB

AGPREFV

82443LXb

C

AB2

AB1

AA3

AA2

AA1

Y2

W5

W3

W1

V5

V3

V1

V2

U6

U4

T5

N5

N4

N3

N2

M4

L5

M2

L4

L1

K5

K2

J3

J1

J2

H2

H1

W2

U5

M1

L2

P1

N1

P5

U2

R1

P2

P4

P3

G1

D2

AC1

E2

E1

F2

F1

G3

J5

K4

J4

W4

F3

D1

H5

Y1

K1

G2

T1

GAD0

GAD1

GAD2

GAD3

GAD4

GAD5

GAD6

GAD7

GAD8

GAD9

GAD10

GAD11

GAD12

GAD13

GAD14

GAD15

GAD16

GAD17

GAD18

GAD19

GAD20

GAD21

GAD22

GAD23

GAD24

GAD25

GAD26

GAD27

GAD28

GAD29

GAD30

GAD31

GC/BE#0

GC/BE#1

GC/BE#2

GC/BE#3

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

ST0

ST1

ST2

D

GAD[31:0] 15

GC/BE#[3:0] 15

GFRAME# 15,28

GDEVSEL# 15,28

GIRDY# 15,28

GTRDY# 15,28

GSTOP# 15,28

GPAR 15,28

GPERR# 15,28

GSERR# 15,28

GREQ# 15,28

GGNT# 15,28

PIPE# 15,28

SBA[7:0] 15

RBF# 15,28

ST[2:0] 15

ADSTB-0 15,28

ADSTB-1 15,28

SBSTB 15,28

AGP_REFV 32

INTEL CORPORATION

PCI COMPONENTS DIVISION

1900 PRAIRIE CITY RD. FM5-62

FOLSOM, CA 95630

Title

PAC PCI AND AGP INTERFACES

Size Document N u m b er Rev

Date: Sheet of

Intel 440LX PCISET 1.4

Custom

D

E

733Thursday, May 07, 1998

E

Page 8

A

B

C

D

E

AF23

AC22

AC23

AF25

AD25

AC24

AC26

AB23

AA22

AA24

AA25

W24

W25

AE23

AF24

AD23

AE26

AD26

AC25

AB24

AB25

AB26

AA26

W22

W23

AF22

AB21

AE22

AD22

AD1

AC5

AD6

AC7

AC2

AC4

AD2

AD4

AD5

AD7

AD8

AC8

AA5

AB4

AB6

AE1

AE3

AF3

AF4

AE5

AF6

AB8

Y22

Y24

Y25

AB3

AA4

AB7

AF2

AE4

AF5

AE6

AE7

AF7

Y21

Y26

V22

V21

AE8

AB9

U3-3

Y3

MD0

Y5

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

Y6

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

MECC0

MECC1

MECC2

MECC3

MECC4

MECC5

MECC6

MECC7

PAC_1.0

B

VCC3 PINS :

C3, E13, F20, G6,

L11, M11, N11, P11,

P12, P22, R3, R4,

R11-13, T11-16, AD12,

AD3, AD24

82443LX

492 BGA

MEMORY DATA BUS

VSS PINS :

A1, A26, AA6, AA7-10,

AA17, AA20, AA21,

AB5, AB13, AB22, AF1,

AF26, C15, E5, E22,

F6, F8, F9, F17, F19,

F21, G21, H6, J6, K6,

L12-16, M12-16, N22,

N12-16, P13-16, R5,

R14-16 , T4, U21, V6,

W6, W21

82443LXc

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HOST DATA BUS

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

GTL_REF

GTL_REF

G22

G23

F25

G24

F24

F26

E25

E24

F22

E26

D25

C25

D26

B26

E23

D24

B24

A25

A23

A22

A24

B23

B22

D23

D22

C22

B21

A21

D20

E21

D21

C21

E20

B20

A19

A20

B19

D19

C20

F18

E18

C18

D17

E19

C19

B18

B17

E17

C17

A17

B15

D16

D18

C16

E16

D15

A14

B16

C14

A16

A15

D14

E15

B14

C24

T22

C

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

PAC_GTLREF1 32

PAC_GTLREF2 32

HD#[63:0] 3,27

INTEL CORPORATION

PCI COMPONENTS DIVISION

1900 PRAIRIE CITY RD. FM5-62

FOLSOM, CA 95630

Title

PAC DATA BUSES

Size Document Number Rev

Custom

Intel 440LX PCISET 1.4

Date: Sheet of

D

833Thursday, May 07, 1998

E

MD[63:0]9,10,11

4 4

3 3

2 2

MECC09,10,11

MECC[7:1]9,10,11

1 1

A

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

MECC0MECC0

MECC1

MECC2

MECC3

MECC4

MECC5

MECC6

MECC7

Page 9

A

B

C

D

E

DIMM CONNECTOR 0

MD[63:0]8,10,11

4 4

PAC AND DIMM SOCKET LOCATIONS.

DIMM

DIMM

CONN.

CONN.

012

DIMM

CONN.

MAB[13:0]

PAC

MAA[13:0]

3 3

MAB[10:0]6

MAB136

MAB126

CDQA#06,10,11

CDQB#16

CDQA#26,10,11

CDQA#36,10,11

CDQA#46,10,11

CDQB#56

CDQA#66,10,11

2 2

PCIRST#6,12,15,16,17

CDQA#76,10,11

MAB116

U14C

5 6

WE#26

VCC3

R237

8.2K

74ALS05

MAB0

MAB1

MAB2

MAB3

MAB4

MAB5

MAB6

MAB7

MAB8

MAB9

MAB10

MAB13

MAB12

MD0

MD1

MD2

MD3

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MAB11

MAB12

2

3

4

5

7

8

9

10

11

13

14

15

16

17

19

20

86

87

88

89

91

92

93

94

95

97

98

99

100

101

103

104

33

117

34

118

35

119

36

120

37

121

38

123

126

132

28

29

46

47

112

113

130

131

122

39

24

25

31

44

48

50

51

61

80

81

109

108

145

SDRAM/EDO DIMM

VCC3 VCC3

J3

40

18

DQ0

DQ1

VCC6VCC26VCC

VCC

DQ2

DQ3

DQ4

DQ5

DQ6

NOTE:

DQ7

EDO PINS NAMES, IF THEY

ARE DIFFERENT FROM SDRAM,

DQ8

APPEAR ON THE INSIDE.

DQ9

DQ10

DIFFERENT PIN NAMES DO

DQ11

NOT NECESSARILY DENOTE

DQ12

DIFFERENT FUNCTIONALITY.

DQ13

DQ14

DQ15

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10(AP)

A11 A13

A12 DU

A13 DU

DQMB0 /CAS0

DQMB1 /CAS1

DQMB2 /CAS2

DQMB3 /CAS3

DQMB4 /CAS4

DQMB5 /CAS5

DQMB6 /CAS6

DQMB7 /CAS7

BA0 A11

BA1 A12

NC

NC

NC /OE0

NC /OE2

NC /WE2

NC

NC

NC

NC

NC

NC

NC

NC

VSS1VSS

12

102

124

110

VCC41VCC90VCC

VCC

VCC

VSS23VSS32VSS85VSS96VSS

VSS43VSS54VSS64VSS68VSS78VSS

107

133

VCC49VCC59VCC73VCC84VCC

VCC

/RAS0 /S0

/RAS1 /S1

/RAS2 /S2

/RAS3 /S3

VSS

VSS

VSS

116

127

138

148

152

143

157

168

VCC

DU NC

DU NC

DU CKE0

NC CKE1

DU /CAS

DU /RAS

DU CK0

DU CK1

DU CK2

DU CK3

VSS

VSS

162

VCC

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

/WE0

55

MD16

56

MD17

57

MD18

58

MD19

60

MD20MD4

65

MD21

66

MD22

67

MD23

69

MD24

70

MD25

71

MD26

72

MD27

74

MD28

75

MD29

76

MD30

77

MD31

139

MD48

140

MD49

141

MD50

142

MD51

144

MD52

149

MD53

150

MD54

151

MD55

153

MD56

154

MD57

155

MD58

156

MD59

158

MD60

159

MD61

160

MD62

161

MD63

134

NC

135

NC

146

147

NC

164

NC

62

128

63

21

MECC0

CB0

22

MECC1

CB1

52

MECC2

CB2

53

MECC3

CB3

105

MECC4

CB4

106

MECC5

CB5

136

MECC6

CB6

137

MECC7

CB7

165

SA0

166

SA1

167

SA2

82

SDA

83

SCL

30

114

45

129

27

111

115

42

125

79

163

B_CKE4 6

B_CKE5 6

MECC0 8,10,11

MECC[7:1] 8,10,11

SLAVE ADDRESS = 1010000b

SMBDATA 4,5,10,11,13,28

SMBCLK 4,5,10,11,13,28

RCSA#4 6

RCSA#5 6

SCAS#2 6

SRAS#2 6

DIMMHCLK0 5

DIMMHCLK1 5

DIMMHCLK2 5

DIMMHCLK3 5

1 1

THIS DRAWING CONTAINS INFORMATION

WHICH HAS NOT BEEN VERIFIED FOR

MANUFACTURING AN END USER PRODUCT.

INTEL IS NOT RESPONSIBLE FOR THE

MISUSE OF THIS INFORMATION.

A

B

B_PCIRST 10,11

INTEL CORPORATION

PCI COMPONENTS DIVISION

1900 PRAIRIE CITY RD. FM5-62

FOLSOM, CA 95630

Title

FIRST DIMM SOCKET

Size Document Number Rev

Custom

Intel 440LX PCISET 1.4

C

D

Date: Sheet of

933Thursday, May 07, 1998

E

Page 10

A

B

C

D

E

DIMM CONNECTOR 1

VCC3 VCC3

4 4

3 3

2 2

THIS DRAWING CONTAINS INFORMATION

WHICH HAS NOT BEEN VERIFIED FOR

1 1

MANUFACTURING AN END USER PRODUCT.

INTEL IS NOT RESPONSIBLE FOR THE

MISUSE OF THIS INFORMATION.

A

MD[63:0]8,9,11

J4

40

102

124

18

2

MD0 MD16

DQ0

3

MD1 MD17

DQ1

4

MD2 MD18

DQ2

5

MD3 MD19

DQ3

7

MD4 MD20

DQ4

8

MD5 MD21

DQ5

9

MD6 MD22

DQ6

10

MD7 MD23

DQ7

11

MD8 MD24

DQ8

13

MD9 MD25

DQ9

14

MD10 MD26

DQ10

15

MD11 MD27

DQ11

16

MD12 MD28

DQ12

17

MD13 MD29

DQ13

19

MD14 MD30

DQ14

20

MD15 MD31

DQ15

86

MD32 MD48

DQ32

87

MD33 MD49

DQ33

88

MD34 MD50

DQ34

89

MD35 MD51

DQ35

91

MD36 MD52

DQ36

92

MD37 MD53

DQ37

93

MD38 MD54

DQ38

94

MD39 MD55

DQ39

95

MD40 MD56

DQ40

97

MD41 MD57

DQ41

98

MD42 MD58

DQ42

99

MD43 MD59

DQ43

100

MD44 MD60

DQ44

101

MD45 MD61

DQ45

103

MD46 MD62

DQ46

104

MAA[10:0]6,11

MAA136,11

MAA126,11

CDQA#[7:0]6,9,11

MAA116,11

B_PCIRST9,11

WE#16

MD47 MD63

DQ47

33

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA13

MAA12

CDQA#0

CDQA#1

CDQA#3

CDQA#4

CDQA#5

CDQA#6

CDQA#7

MAA11

MAA12

B

A0

117

A1

34

A2

118

A3

35

A4

119

A5

36

A6

120

A7

37

A8

121

A9

38

A10(AP)

123

A11 A13

126

A12 DU

132

A13 DU

28

DQMB0 /CAS0

29

DQMB1 /CAS1

46

DQMB2 /CAS2

47

DQMB3 /CAS3

112

DQMB4 /CAS4

113

DQMB5 /CAS5

130

DQMB6 /CAS6

131

DQMB7 /CAS7

122

BA0 A11

39

BA1 A12

24

NC

25

NC

31

NC /OE0

44

NC /OE2

48

NC /WE2

50

NC

51

NC

61

NC

80

NC

81

NC

109

NC

108

NC

145

NC

SDRAM/EDO DIMM

110

VCC6VCC26VCC

VCC41VCC90VCC

VCC

VCC

VCC

NOTE:

EDO PINS NAMES, IF THEY

ARE DIFFERENT FROM SDRAM,

APPEAR ON THE INSIDE.

DIFFERENT PIN NAMES DO

NOT NECESSARILY DENOTE

DIFFERENT FUNCTIONALITY.

VSS1VSS

VSS23VSS32VSS85VSS96VSS

VSS43VSS54VSS64VSS68VSS78VSS

12

VCC49VCC59VCC73VCC84VCC

VSS

107

116

127

138

VSS

VSS

148

143

157

133

VCC

DU NC

DU NC

DU CKE0

NC CKE1

/RAS0 /S0

/RAS1 /S1

/RAS2 /S2

/RAS3 /S3

DU /CAS

DU /RAS

DU CK0

DU CK1

DU CK2

DU CK3

VSS

VSS

152

162

C

168

55

DQ16

56

DQ17

57

VCC

VCC

DQ18

58

DQ19

60

DQ20

65

DQ21

66

DQ22

67

DQ23

69

DQ24

70

DQ25

71

DQ26

72

DQ27

74

DQ28

75

DQ29

76

DQ30

77

DQ31

139

DQ48

140

DQ49

141

DQ50

142

DQ51

144

DQ52

149

DQ53

150

DQ54

151

DQ55

153

DQ56

154

DQ57

155

DQ58

156

DQ59

158

DQ60

159

DQ61

160

DQ62

161

DQ63

134

NC

135

NC

146

147

NC

164

NC

62

/WE0

128

63

21

MECC0

CB0

22

MECC1

CB1

52

MECC2

CB2

53

MECC3

CB3

105

MECC4

CB4

106

MECC5

CB5

136

MECC6

CB6

137

MECC7CDQA#2

CB7

165

R_SA0

SA0

166

SA1

167

SA2

82

SDA

83

SCL

30

114

45

129

27

111

115

42

125

79

163

B_CKE2 6

B_CKE3 6

MECC0 8,9,11

MECC[7:1] 8,9,11

VCC3

R33

4.7K

SMBDATA 4,5,9,11,13,28

SMBCLK 4,5,9,11,13,28

RCSA#2 6

RCSA#3 6

SCAS#1 6

SRAS#1 6

DIMMHCLK4 5

DIMMHCLK5 5

DIMMHCLK6 5

DIMMHCLK7 5

SLAVE ADDRESS = 1010001b

INTEL CORPORATION

PCI COMPONENTS DIVISION

1900 PRAIRIE CITY RD. FM5-62

FOLSOM, CA 95630

Title

SECOND DIMM SOCKET

Size Document Number Rev

Custom

D

Date: Sheet of

Intel 440LX PCISET 1.4

10 33Thursday, May 07, 1998

E

Page 11

A

B

C

D

E

DIMM CONNECTOR 2

VCC3VCC3

4 4

3 3

2 2

THIS DRAWING CONTAINS INFORMATION

WHICH HAS NOT BEEN VERIFIED FOR

1 1

MANUFACTURING AN END USER PRODUCT.

INTEL IS NOT RESPONSIBLE FOR THE

MISUSE OF THIS INFORMATION.

A

MD[63:0]8,9,10

J5

40

102

124

18

2

MD0

MD1 MD17

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

B

MD47

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA13

MAA12

CDQA#0

CDQA#1

CDQA#2

CDQA#3

CDQA#4

CDQA#5

CDQA#6

CDQA#7

MAA11

MAA12

MAA[10:0]6,10

MAA136,10

MAA126,10

CDQA#[7:0]6,9,10

MAA116,10

B_PCIRST9,10

WE#06

DQ0

3

DQ1

4

DQ2

5

DQ3

7

DQ4

8

DQ5

9

DQ6

10

DQ7

11

DQ8

13

DQ9

14

DQ10

15

DQ11

16

DQ12

17

DQ13

19

DQ14

20

DQ15

86

DQ32

87

DQ33

88

DQ34

89

DQ35

91

DQ36

92

DQ37

93

DQ38

94

DQ39

95

DQ40

97

DQ41

98

DQ42

99

DQ43

100

DQ44

101

DQ45

103

DQ46

104

DQ47

33

A0

117

A1

34

A2

118

A3

35

A4

119

A5

36

A6

120

A7

37

A8

121

A9

38

A10(AP)

123

A11 A13

126

A12 DU

132

A13 DU

28

DQMB0 /CAS0

29

DQMB1 /CAS1

46

DQMB2 /CAS2

47

DQMB3 /CAS3

112

DQMB4 /CAS4

113

DQMB5 /CAS5

130

DQMB6 /CAS6

131

DQMB7 /CAS7

122

BA0 A11

39

BA1 A12

24

NC

25

NC

31

NC /OE0

44

NC /OE2

48

NC /WE2

50

NC

51

NC

61

NC

80

NC

81

NC

109

NC

108

NC

145

NC

SDRAM/EDO DIMM

110

VCC6VCC26VCC

VCC41VCC90VCC

VCC

VCC

VCC

NOTE:

EDO PINS NAMES, IF THEY

ARE DIFFERENT FROM SDRAM,

APPEAR ON THE INSIDE.

DIFFERENT PIN NAMES DO

NOT NECESSARILY DENOTE

DIFFERENT FUNCTIONALITY.

VSS1VSS

VSS23VSS32VSS85VSS96VSS

VSS43VSS54VSS64VSS68VSS78VSS

12

VCC49VCC59VCC73VCC84VCC

VSS

107

116

127

138

VSS

148

C

143

133

VCC

DU CKE0

NC CKE1

/RAS0 /S0

/RAS1 /S1

/RAS2 /S2

/RAS3 /S3

DU /CAS

DU /RAS

DU CK0

DU CK1

DU CK2

DU CK3

VSS

VSS

VSS

152

162

157

168

VCC

VCC

DU NC

DU NC

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

/WE0

55

MD16

56

57

MD18

58

MD19

60

MD20

65

MD21

66

MD22

67

MD23

69

MD24

70

MD25

71

MD26

72

MD27

74

MD28

75

MD29

76

MD30

77

MD31

139

MD48

140

MD49

141

MD50

142

MD51

144

MD52

149

MD53

150

MD54

151

MD55

153

MD56

154

MD57

155

MD58

156

MD59

158

MD60

159

MD61

160

MD62

161

MD63

134

NC

135

NC

146

147

NC

164

NC

62

128

63

21

MECC0

CB0

22

MECC1

CB1

52

MECC2

CB2

53

MECC3

CB3

105

MECC4

CB4

106

MECC5

CB5

136

MECC6

CB6

137

MECC7

CB7

165

SA0

166

R_SA1

SA1

167

SA2

82

SDA

83

SCL

30

114

45

129

27

111

115

42

125

79

163

B_CKE0 6

B_CKE1 6

MECC0 8,9,10

MECC[7:0] 8,9,10

VCC3

R166

4.7K

SLAVE ADDRESS = 1010010b

SMBDATA 4,5,9,10,13,28

SMBCLK 4,5,9,10,13,28

RCSA#0 6

RCSA#1 6

SCAS#0 6

SRAS#0 6

DIMMHCLK8 5

DIMMHCLK9 5

DIMMHCLK10 5

DIMMHCLK11 5

D

INTEL CORPORATION

PCI COMPONENTS DIVISION

1900 PRAIRIE CITY RD. FM5-62

FOLSOM, CA 95630

Title

THIRD DIMM SOCKET

Size Document Number Rev

Custom

Intel 440LX PCISET 1.4

Date: Sheet of

11 33Thursday, May 07, 1998

E

Page 12

A

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

CLKRUN#

R_AD18

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

C/BE#0

C/BE#1

C/BE#2

C/BE#3

SDA0

SDA1

SDA2

PDA0

PDA1

PDA2

PDD0

PDD1

PDD2

PDD3

PDD4

PDD5

PDD6

PDD7

PDD8

PDD9

PDD10

PDD11

PDD12

PDD13

PDD14

PDD15

4 4

AD18

VCC3

R35

100

3 3

2 2

1 1

R36

1K

AD[31:0]7,16,17

C/BE#[3:0]7,16,17

DEVSEL#7,16,17,28

FRAME#7,16,17,28

IRDY#7,16,17 ,28

PAR7,16,17

PCIRST#6,9,15,16,17

PHLD#7,28

PHLDA#7,28

SERR#7,16,17,28

STOP#7,16,17,28

TRDY#7,16,17,28

PU_REQ#028

PU_REQ#128

PU_REQ#228

PU_REQ#328

SDA[2:0]19

PDDACK#19

SDDACK#19

PDREQ19

SDREQ19

PDIOR#19

PDIOW#19

PIORDY19

SDIOR#19

SDIOW#19

SIORDY19

PDA[2:0]19

PDD[15:0]19

A

B10

A10

D9

C9

B9

A9

D8

E8

B8

A8

D7

C7

B7

A7

D6

E6

E4

C4

B4

A4

D3

E3

C3

B3

E2

C2

B2

A2

D1

E1

C1

B1

C8

C6

D4

D2

C10

E5

A5

A3

B5

B6

A1

B12

A12

A6

D5

C5

E10

A11

B11

C11

C17

B17

A18

G19

A17

F18

A16

F17

F16

G20

C16

B16

D16

G16

G18

G17

F20

E18

E20

D18

D20

C20

B20

A20

A19

B19

C19

D19

D17

E19

E17

F19

B

U4A

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

C/BE#0

C/BE#1

C/BE#2

C/BE#3

CLOCKRUN#

DEVSEL#

FRAME#

IDSEL

IRDY#

PAR

PCIRST#

PHOLD#

PHOLDA#

SERR#

STOP#

TRDY#

REQ0#

REQ1#

REQ2#

REQ3#

SDA0

SDA1

SDA2

PDDACK#

SDDACK#

PDREQ

SDREQ

PDIOR#

PDIOW#

PIORDY

SDIOR#

SDIOW#

SIORDY

PDA0

PDA1

PDA2

PDD0

PDD1

PDD2

PDD3

PDD4

PDD5

PDD6

PDD7

PDD8

PDD9

PDD10

PDD11

PDD12

PDD13

PDD14

PDD15

PIIX4_14

B

PCI BUS

INTERFACE

PIIX4

IDE

SIGNALS

C

IDE

SIGNALS

ISA/EIO

SIGNALS

C

SDD10

SDD11

SDD12

SDD13

SDD14

SDD15

SCS3#

PCS3#

SCS1#

PCS1#

MEMCS16#

MEMR#

MEMW#

SMEMR#

SMEMW#

SYSCLK

IOCHK#

REFRESH#

IOCS16#

ZEROWS#

SBHE#

RSTDRV

IOCHRDY

SDD0

SDD1

SDD2

SDD3

SDD4

SDD5

SDD6

SDD7

SDD8

SDD9

SA10

SA11

SA12

SA13

SA14

SA15

SA16

SA17

SA18

SA19

SD10

SD11

SD12

SD13

SD14

SD15

LA17

LA18

LA19

LA20

LA21

LA22

LA23

BALE

IOR#

IOW#

D

E15

SDD0

B15

SDD1

D14

SDD2

C14

SDD3

A14

SDD4

C13

SDD5

A13

SDD6

C12

SDD7

D12

SDD8

B13

SDD9

D13

SDD10

B14

SDD11

E14

SDD12

A15

SDD13

C15

SDD14

D15

SDD15

C18

H16

B18

H17

U11

SA0

SA1

SA2

SA3

SA4

SA5

SA6

SA7

SA8

SA9

SD0

SD1

SD2

SD3

SD4

SD5

SD6

SD7

SD8

SD9

AEN

SA0

T11

SA1

W11

SA2

Y11

SA3

T10

SA4

W10

SA5

U9

SA6

V9

SA7

Y9

SA8

T8

SA9

W8

SA10

U7

SA11

V7

SA12

Y7

SA13

V6

SA14

Y6

SA15

T5

SA16

W5

SA17

U4

SA18

V4

SA19

V3

SD0

W3

SD1

U2

SD2

T2

SD3

W2

SD4

Y2

SD5

T1

SD6

V1

SD7

W16

SD8

T16

SD9

Y17

SD10

V17

SD11

Y18

SD12

W18

SD13

Y19

SD14

W19

SD15

Y15

LA17

T14

LA18

W14

LA19

U13

LA20

V13

LA21

Y13

LA22

T12

LA23

Y12

V15

U15

W4

U3

T7

U10

Y1

W7

V12

Y3

W12

W1

Y5

T4

T3

Y4

D

SDD[15:0] 19

SCS3# 19

PCS3# 19

SCS1# 19

PCS1# 19

SA[19:0] 14,18,21,29

SD[16:0] 14,18,29

LA[23:17] 18,29

MEMCS16# 18,29

MEMR# 18,21,29

MEMW# 18,21,29

SMEMR# 18

SMEMW# 18

SYSCLK 18

BALE 18

IOCHK# 18,29

REFRESH# 18,29

IOCS16# 18,29

ZEROWS# 18,29

SBHE# 18

RSTDRV 14,26

IOR# 14,18,29

IOW# 14,18,29

IOCHRDY 14,18,29

AEN 14,18

INTEL CORPORATION

PCI COMPONENTS DIVISION

1900 PRAIRIE CITY RD. F M5 -6 2

FOLSOM, CA 95630

Title

PIIX4 (PART I)

Size Docum ent Number Rev

Intel 440LX PCISET 1.4

Custom

Date: Sheet of

E

12 33Thursday, May 07, 1998

E

Page 13

A

DACK#[3:0]14,18

4 4

3 3

MMBD354LT1

VB2

MMBD354LT1

1 3

VB1

12

BT1

2

3V_STBY

2

13

D2

R38

1K

C8

0.1 uF

D3

R232

CLEAR CMOS

JP19 CONFIG

1 -2 NORMAL

2 - 3 CLEAR CMOS

A

R165

8.2K

1

3

CMOS_CLR

1K

2 2

1 1

DACK#[7:5]18

DRQ014,18,29

DRQ114,18,29

DRQ214,18,29

DRQ314,18,29

DRQ518,29

DRQ618,29

DRQ718,29

REQ#A28

REQ#B28

REQ#C28

TC14,18

APICREQ#28

IRQ114,29

IRQ31 4,18,29

IRQ41 4,18,29

IRQ51 4,18,29

IRQ61 4,18,29

IRQ71 4,18,29

IRQ#814,29

IRQ91 4,18,29

IRQ1014,18,29

IRQ1114,18,29

IRQ1214,18,29

IRQ1414,18,19,29

IRQ1514,18,19,29

GPI728

PIRQ#A15,16,17,28

PIRQ#B15,16,17,28

PIRQ#C16,17,28

PIRQ#D16,17,28

SLP#3,28

FERR#3,28

PX4_IGNNE#25,28

HINIT#3,6,28

PX4_INTR25,28

A20GATE14,28

PX4_NMI25,28

SMI#3,28

STPCLK#3,28

KBRST#14,28

PX4_A20M#25,28

PWROK26

SPKR26

TEST#28

PX4_CFG128

XOE#14

XDIR#14

BIOSCS#21

JP19

2

R234

0

32.768KHz

C9

22pF

Y3

RTC_BAT 14

PX4_VBAT

R235

0

12

C10

22pF

48Mhz5

OSC05

PX4PCLK5

RTCX2

RTCX1

DACK#0

DACK#1

DACK#2

DACK#3

DACK#5

DACK#6

DACK#7

R_CFG2

PIRQ#A

PIRQ#B

PIRQ#D

B

U14

W6

Y10

V5

T15

V16

W17

W15

U6

V2

U5

Y16

U16

U17

M1

N2

P3

N1

P2

P4

V10

J17

H18

K18

H20

J20

T9

W9

U8

V8

Y8

Y20

U1

U12

W13

T13

V14

Y14

J19

R3

R4

P5

G1

K20

M19

K19

L17

L18

L19

P1

L20

P20

J18

N20

M20

M18

K17

V18

R17

R18

M4

M3

M2

L1

K2

K1

L16

R20

N19

P17

L3

V11

D11

B

U4B

DACK0#

DACK1#

DACK2#

DACK3#

DACK5#

DACK6#

DACK7#

DREQ0

DREQ1

DREQ2

DREQ3

DREQ5

DREQ6

DREQ7

REQA#/GPI2

REQB#/GPI3

REQC#/GPI4

GNTA#/GPO9

GNTB#/GPO10

GNTC#/GPO11

TC

APICACK#/GPO12

APICCS#/GPO13

APICREQ#/GPI5

IRQ0/GPO14

IRQ1

IRQ3

IRQ4

IRQ5

IRQ6

IRQ7

IRQ8/GPI6

IRQ9

IRQ10

IRQ11

IRQ12

IRQ14

IRQ15

SERIRQ/GPI7

PIRQA#

PIRQB#

PIRQC#

PIRQD#

SLP#

CPURST

FERR#

IGNNE#

INIT

INTR

A20GATE

NMI

SMI#

STPCLK#

RCIN#

A20M#

PWROK

SPKR

TEST#

CONFIG1

CONFIG2

XOE#/GPO23

XDIR#/GPO22

BIOSCS#

RTCALE/GPO25

RTCCS#/GPO24

KBCCS#/GPO26

VBAT

RTCX2

RTCX1

SUSCLK

48Mhz

OSC

PCICLK

PIIX4_14

3V_STBY

E11

F15

R15

VCC

VCC

VCCR6VCC

DMA/IRQ

SIGNALS

E12

VCCPE9VCCP

VCC3

E16

VCCP

F14

VCCPF5VCCP

VCCPG6VCCPR7VCCP

POWER

MGMT.

P15

T6

VCCP

VCC3

F6

VCC

DMA

SIGNALS

PIIX4

IRQ

SIGNALS

GPO/GPI/GPIO/SCAN

CPU

INTERFACE

SYSTEM/TEST

X-BUS

GND: D10,E7,E13,J9,J10,J11,J12,K9,K10,K11,K12

L9,L10,L11,L12,M9,M10,M11,M12

VSSUSB: J5

PROG CHIP SEL.

C

VCC3

R16

N16

VCCSUS

C

K5

USB

VCCSUS

VCCUSB

GPO17/CPU_STP#

GPO18/PCI_STP#

GPO20/SUS_STAT1#

GPO21/SUS_STAT2#

GPI9/BATLOW#

GPI11/SMBALERT#

USBP1+

USBP1-

USBP0+

USBP0-

EXTSMI#

GPO15/SUSB#

GPO16/SUSC#

GPO19/ZZ

GPI8/THERM#

RSMRST#

PWRBT#

GPI10/LID

SMBDATA

SMBCLK

GPI12/RI#A

MCCS#

PGCS0#

PGCS1#

SUSA#

VREF

GPI13

GPI14

GPI15

GPI16

GPI17

GPI18

GPI19

GPI20

GPI21

GPO0

GPO8

GPO27

GPO28

GPO29

GPO30

D

F1

H2

G2

H3

J1

OC0

J2

OC1

V20

W20

V19

U18

R1

R2

K16

T17

T18

H19

U19

M17

U20

P16

T20

R19

N17

P18

J16

P19

GPI1

L2

GPI13

J3

GPI14

L5

GPI15

K3

GPI16

K4

GPI17PIRQ#C

H1

GPI18

H4

GPI19

H5

GPI20

G3

GPI21

G4

T19

GPO8

G5

GPO27

F2

GPO28

F3

F4

J4

N/C

N18

N/C

N3

N/C

M5

N/C

M16

N/C

R5

N/C

N4

L4

PGCS#0

N5

PGCS#1

SUSC#

USBP1+ 20

USBP1- 20

USBP0+ 20

USBP0- 20

OC#0 20

OC#1 20

EXTSMI# 26,28

C5

0.01 uF

THERM# 4,28

BATLOW# 28

RSMRST# 26

PWRBT# 26

LID 28

SMBDATA 4,5,9,10,11,28

SMBCLK 4,5,9,10,11,28

SMBALERT# 28

RI#A 28

GPI1 28

GPI[21:13] 28

1

TP2

1

TP3

1

TP4

1

TP5

1

TP6

Title

Size Document Number Rev

D

Date: Sheet of

5VSB

14

U5A

1 2

7

74HCT14

VCC3

2

13

D1

MMBD354LT1

C6

C7

+

1.0 uF

0.1 uF

FAN_ON 26

INTEL CORPORATION

PCI COMPONENTS DIVISION

1900 PRAIRIE CITY RD. FM5-62

FOLSOM, CA 95630

PIIX4 (PART II)

Custom

Intel 440LX PCISET 1.4

B_SUSC# 26

VCC

E

R37

1K

VREF5V 6

13 33Thursday, May 07, 1998

E

Page 14

1

R199

A A

1M

B B

C C

D D

NS3

32.763KHz

NS4

22 pF

KBCLK#24

KBDAT#24

MSCLK#24

MSDAT#24

THIS DRAWING CONTAINS INFORMATION

WHICH HAS NOT BEEN VERIFIED FOR

MANUFACTURING AN END USER PRODUCT.

INTEL IS NOT RESPONSIBLE FOR THE

MISUSE OF THIS INFORMATION.

1

NS5

22 pF

DO NOT INSTALL

NS3, NS4 & NS5

IRQ#813,29

SA[19:0]12,18,21,29

VCC

R43

8.2K

VCC

XD[7:0]21

XOE#13

XDIR#13

DRQ[7:0]13,18,29

DACK#[3:0]13,18

IRQ[7:0]13,18,29

RP1

1 8

2 7

3 6

4 5

4.7K

2

NOTE: NS6 IS DEFAULT NO-STUFF

RTC_BAT13

OSC35

IOR#12,18,29

IOW#12,18,29

AEN12,18

RSTDRV12,26

IOCHRDY12,18,29

SD[15:0]12,18,29

TC13,18

U24C

56

74AS07

IRQ913,18,29

IRQ1013,18,29

IRQ1113,18,29

IRQ1213,18,29

IRQ1413,18,19,29

IRQ1513,18,19,29

2

TP19

TP21

TP23

TP12

TP13

TP14

TP16

TP18

3

0

NS6

R_RTCBAT

SIO_XTAL1

SIO_XTAL2

SD0

SD1

SD2

SD3

SD4

SD5

SD6

SD7

DRQ0

DRQ1

DRQ2 TP090

DRQ3

DACK#0

DACK#1

DACK#2

DACK#3

IRQ1

IRQ3

IRQ4

IRQ5

IRQ6

IRQ7

B_IRQ#8

IRQ9

IRQ10

IRQ11

IRQ12

IRQ14

IRQ15

SA0

SA1

SA2

SA3

SA4

SA5

SA6

SA7

SA8

SA9

SA10

SA11

SA12

SA13

SA14

SA15

SIO_PU2

1

TP080

1

TP081

1

TP082 TP092

1

TP083 TP091

1

TP084

1

TP079 TP073

1

TP078 TP072

1

TP085 TP087

XD0

XD1

XD2

XD3

XD4

XD5

XD6

XD7

3

4

U8

121

VBAT

122

XTAL1

124

XTAL2

22

14CLOCKI

68

IOR#

69

IOW#

70

AEN

80

RSTDRV

90

IOCHRDY

72

SD0

73

SD1

74

SD2

75

SD3

76

SD4

77

SD5

78

SD6

79

SD7

89

TC

82

DRQ0

84

DRQ1

86

DRQ2

88

DRQ3

81

DACK0

83

DACK1

85

DACK2

87

DACK3

67

IRQ1

66

IRQ3

65

IRQ4

64

IRQ5

63

IRQ6

62

IRQ7

61

IRQ8#

59

IRQ9

58

IRQ10

57

IRQ11

56

IRQ12

55

IRQ14

54

IRQ15

41

SA0

42

SA1

43

SA2

44

SA3

45

SA4

46

SA5

47

SA6

48

SA7

49

SA8

50

SA9

51

SA10

52

SA11

53

SA12/CS

27

SA13/HDCS2#

28

SA14/HDCS3#

29

SA15/IDE2_IRQ

26

IDE1_IRQ

23

IDE1_OE#

24

HDCS0#

25

HDCS1#

30

IOROP#

31

IOWOP#

34

IDE_A0

33

IDE_A1

32

IDE_A2

92

KCLK

91

KDAT

94

MSCLK

93

MSDAT

111

RD0

112

RD1

113

RD2

114

RD3

115

RD4

116

RD5

117

RD6

118

RD7

119

ROMCS#

120

ROMOE#

FDC37C932FR_1.2

VCC PINS :

21, 60, 101,

125, 139

FDC37C932FR

160 PIN QFP

GND PINS :

1, 8, 40, 71,

95, 123, 130

ULTRA I/O

4

5

14CLK01

14CLK02

14CLK03

INDEX#

STEP#

WDATA#

WGATE#

RDATA#

SIDE1#

DSKCHG#

MTR0#

MTR1#

DRVSEL0#

DRVSEL1#

DRVDEN0

DRVDEN1

MEDID0

MEDID1

DTR1#

DSR1#

DCD1#

DTR2#

DSR2#

DCD2#

GP10/IRQIN

GP11/IRQIN

GP12/IRRX

GP13/IRTX

GP14/RS

GP15/WS

GP16/JOYRS

GP17/JSWS

GP20/IDE2_OE

GP21/EEDIN

GP22/EDOUT

GP23/EECLK

GP24/EEEN

GP25/8042_P21

5

16CLK

24CLK

TRK0#

WPT#

SLIN#

INIT#

AFD#

STB#

BUSY

ACK#

SLCT

ERR#

RXD1

TXD1

RTS1#

CTS1#

RXD2

TXD2

RTS2#

CTS2#

DIR#

6

37

38

39

TP076

36

TP077

TP088

35

14

9

10

11

12

15

16

17

13

18

4

7

6

5

2

3

20

19

IRR4_MODEIRR4_MODE

138

PDR0

PD0

137

PDR1

PD1

136

PDR2

PD2

135

PDR3

PD3

134

PDR4

PD4

133

PDR5

PD5

132

PDR6

PD6

131

PDR7

PD7

140

141

143

144

128

129

127

PE

126

142

145

146

148

149

150

147

152

151

RI1#

155

156

158

159

160

157

154

153

RI2#

96

97

98

IRRX

99

IRTX

100

102

103

104

TP075

105

106

R_GP21

107

TP071

108

TP070

109

TP069

110

1

TP7

1

TP8

1

TP9

INDEX# 23

DIR# 23

STEP# 23

WDATA# 23

WGATE# 23

TRK0# 23

WPT# 23

RDATA# 23

SIDE1# 23

DSKCHG# 23

MOTEA# 23

MOTEB# 23

DRVSA# 23

DRVSB# 23

REDWC# 23

DRATE0 23

PDR[7:0] 22

SLIN#R 22

INIT#R 22

AFD#R 22

STB#R 22

BUSY 22

ACK# 22

PE 22

SLCT 22

ERR# 22

RX0 23

TX0 23

CTS0# 23

DTR0# 23

DSR0# 23

RLSD0# 23

RI0# 23

RX1 23

TX1 23

RTS1# 23

CTS1# 23

DTR1# 23

DSR1# 23

RLSD1# 23

RI1# 23

1

TP15

1

TP17

1

TP20

1

TP22

1

TP24

1

TP25

KBRST# 13,28

1

TP26

1

TP27

1

TP28

A20GATE 13,28

VCC

R162

8.2K

INTEL CORPORATION

PCI COMPONENTS DIVISION

1900 PRAIRIE CITY RD. FM5-62

FOLSOM, CA 95630

Title

Size Document Number Rev

Custom

Date: Sheet of

6

7

1

TP10

INSTALL FOR 370 CONFIG.

REMOVE FOR 3F0 CONFIG.

INSTALL FOR 3F0 CONFIG.

REMOVE FOR 370 CONFIG.

R41

10K

R42

1K

C11

470pF

RTS0# 23

VCC

8

VCC

KEY

C15

0.1 uF

INFRARED HDR

14 33Thursday, May 07, 1998

8

C12

470pF

I/O CONTROLLER (ULTRA I/O)

Intel 440LX PCISET 1.4

C13

470pF

C14

0.1 uF

7

JP4

6

5

4

3

2

1

Page 15

A

SBA[7:0]7

ST[2:0]7

4 4

PIRQ#B13,16,17,28

USBAGP+20

12

74AS07

AGPHCLK5

U24A

GREQ#7,28

RBF#7,28

SBSTB7,28

B

C

J6

VCC +12V

B1

R204

4.7K

ST0

ST2

SBA0

SBA2

SBA4

SBA6

SPARE

B2

5V

B3

5V

B4

USB+

B5

GND

B6

INTB#

B7

CLK

B8

REQ#

B9

VCC3.3

B10

ST0

B11

ST2

B12

RBF#

B13

GND

B14

SPARE

B15

SBA0

B16

VCC3.3

B17

SBA2

B18

SB_STB

B19

GND

B20

SBA4

B21

SBA6

SPARE

RESERVED

VCC3.3

RESERVED

SPARE

VCC3.3

RESERVED

USB-

INTA#

RST#

GNT#

PIPE#

SBA1

SBA3

SBA5

SBA7

GND

GND

GND

D

E

VCC3VCC3VCC3 VCC3

A1

12V

A2

A3

A4

A5

A6

A7

A8

A9

A10

ST1

A11

ST1

A12

A13

R203

4.7K

USBAGP- 20

B_PIRQA#B_PIRQB#

PCIRST# 6,9,12,16,17

GGNT# 7,28

PIPE# 7,28

U24B

3 4

74AS07

PIRQ#A 13,16,17,28

A14

A15

SBA1

A16

A17

SBA3

A18

A19

A20

A21

SBA5

SBA7

3 3

GAD31

GAD29

GAD27

GAD25

ADSTB-17,28

GAD23

GAD21

GAD19

GAD17

GC/BE#2

GIRDY#7,28

2 2

GDEVSEL#7,28

GPERR#7,28

GSERR#7,28

GC/BE#1

GAD14

GAD12

GAD10

GAD8

ADSTB-07,28

GAD7

GAD5

GAD3

GAD1

B26

AD31

B27

AD29

B28

VCC3.3

B29

AD27

B30

AD25

B31

GND

B32

AD_STB1

B33

AD23

B34

Vddq3.3

B35

AD21

B36

AD19

B37

GND

B38

AD17

B39

C/BE2#

B40

Vddq3.3

B41

IRDY#

B42

SPARE

B43

GND

B44

SPARE

B45

VCC3.3

B46

DEVSEL#

B47

Vddq3.3

B48

PERR#

B49

GND

B50

SERR#

B51

C/BE1#

B52

Vddq3.3

B53

AD14

B54

AD12

B55

GND

B56

AD10

B57

AD8

B58

Vddq3.3

B59

AD_STB0

B60

AD7