Page 1

A

y

y

y

y

g

y

y

y

g

y

y

yrig

j

B

C

D

E

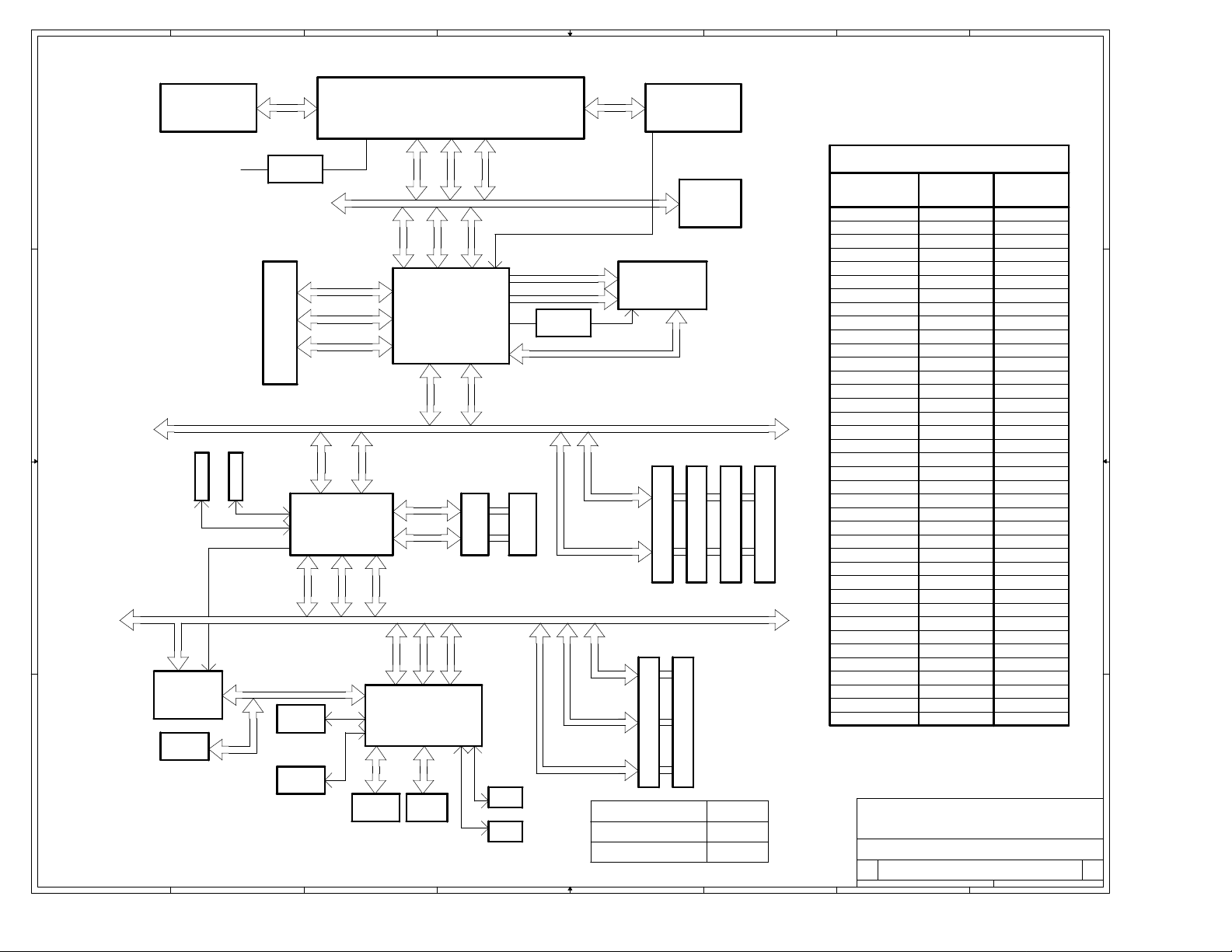

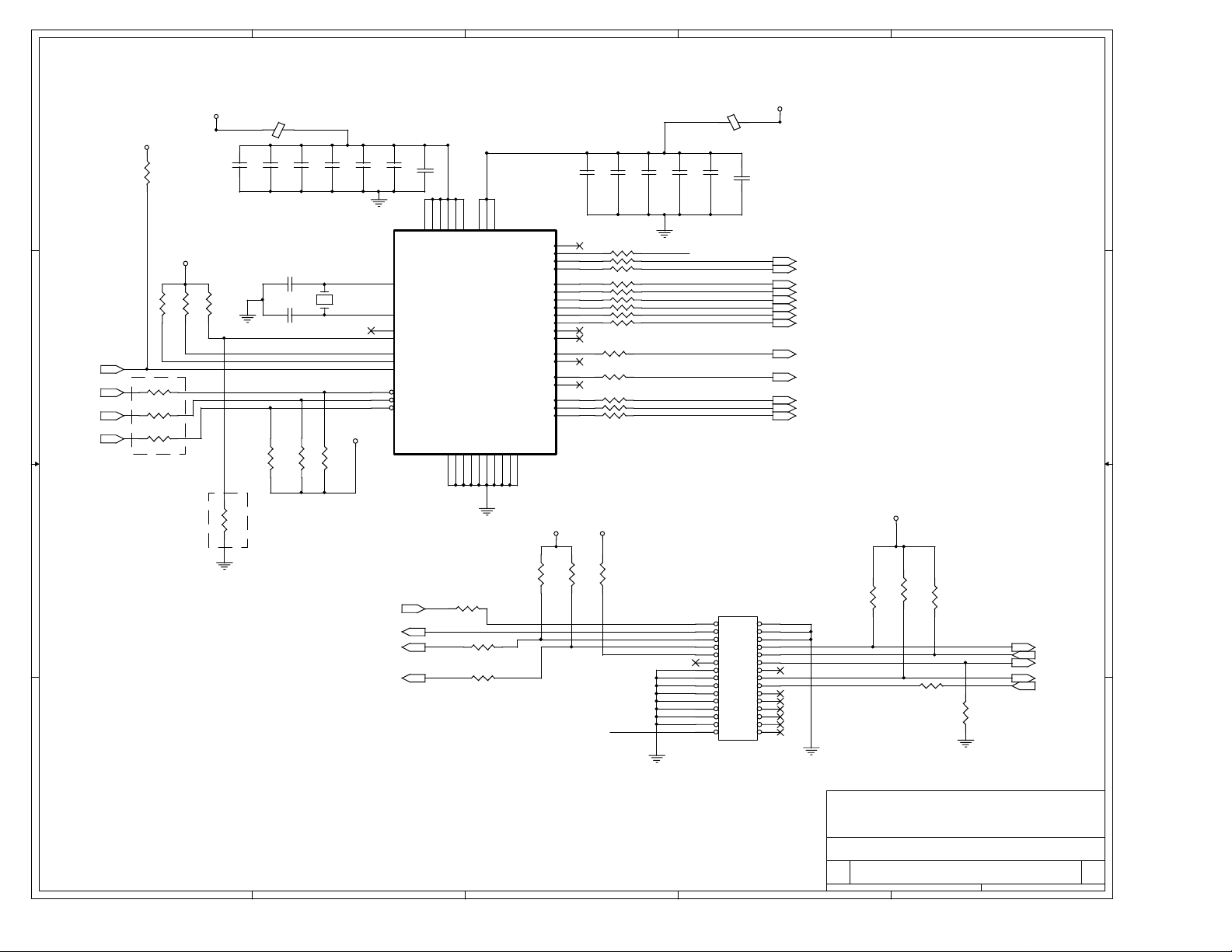

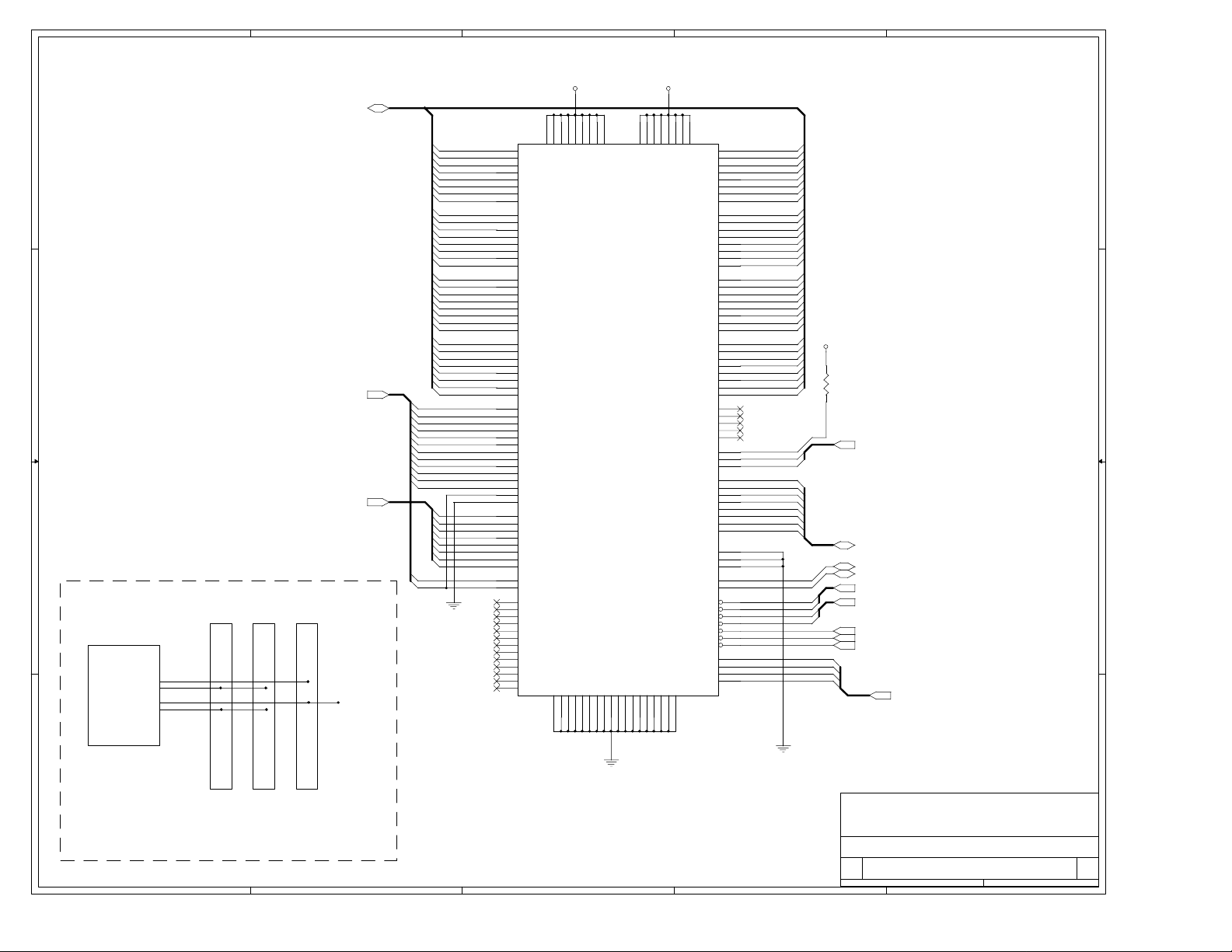

Intel 100 MHz Pentium(tm) II processor/440BX AGPset

Uniprocessor Customer Reference Schematics

4 4

Revision 1.0

** Please note that these schematics are sub

TITLE

ect to change.

PAGE

COVER SHEET 1

BLOCK DIAGRAM

SLOT 1 CONNECTOR 3,4

CLOCK SYNTHESIZER 5

82443BX 6,7,8

3 3

DIMM SOCKETS 9,10,11

PIIX4E 12,13

2

THIS SCHEMATIC IS PROVIDED "AS IS" WITH NO WARRANTIES

WHATSOEVER, INCLUDING ANY WARRANTY OF

MERCHANTABILITY, FITNESS FOR ANY PARTICULAR PURPOSE,

OR A N Y WARRANTY OTHERWISE ARISING OUT OF PROPOSAL,

SPECIFICATION OR SAMPLE.

No license, express or implied, b

intellectual property rights is granted herein.

to an

estoppel or otherwise,

ULTRA I/O 14

AGP CONNECTOR 15

PCI CONNECTORS 16,17

ISA CONNECTORS 18

IDE CONNECTORS 19

USB CONNECTORS 20

FLASH BIOS 21

2 2

PA RALLEL 22

SERIAL/FLOPPY 23

KEYBOARD/MOUSE 24

VRM 25

POWER CONNECTOR 26

GTL+ TERMINATION 27

PCI/AGP PULLUPS/PULLDOWNS 28

ISA PULLUPS/PULLDOWNS 29

82443BX DECOUPLING 30

1 1

BULK DECOUPLING 31

TERMINATION DECOUPLING 32

LM79 33

REVISION HISTORY 34

A

B

C

Intel disclaims all liabilit

an

proprietary rights , relating to use of information in this

specification. Intel does not warrant or represent that such

use will not infrin

I2C is a two-wire communications bus/protocol developed

b

Philips. SMBus is a subset of the I2C bus/protocol and

was developed b

bus/protocol or the SMBus bus/protocol ma

licenses from various entities, includin

N.V. and North American Philips Corporation.

*Third-part

brands and names are the propert

of their respective owners.

ht * Intel Corporation 1997, 1998

Cop

INTEL CORPORATION

PLATFORM COMPONENTS DIVISION

1900 PRAIRIE CITY RD. FM5-62

FOLSOM, CA 95630

Title

Intel 100MHz Pentium(tm) II processor/440BX AGPset Uni-Processor Cover Sheet

Size Document Number Rev

A

Date: Sheet of

, including liability for infringement of

e such rights.

Intel. Implementations of the I2C

require

Philips Electronics

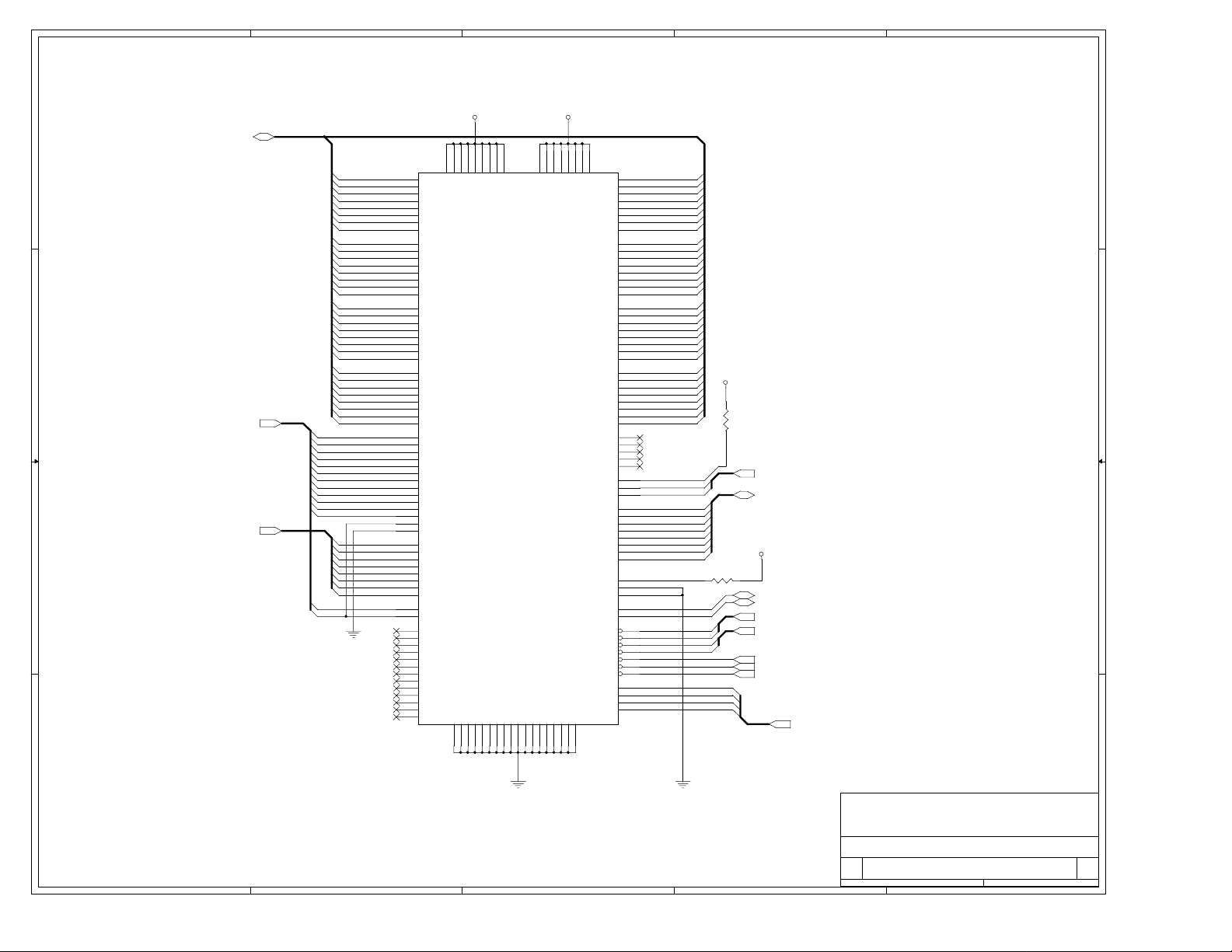

Intel(R) 440BX AGPset

134Thursday, April 09, 1998

D

1.0

E

Page 2

1

2

3

4

5

6

7

8

VRM

VTT GEN.

PG. 25

A A

SMBus

Interface

MAX1617 ME

PG. 3

PENTIUM(tm) II

PROCESSOR

(SLOT 1)

PG. 3,4

ADDR

CNTL

DATA

SYSTEM BUS

ADDR

CNTL

DATA

AGP

CONN.

B B

PG. 15

ADDR/DATA

CNTL

AGP SIDEBAND

82443BX

492 BGA

PG. 6-8

ADD/DATA

CNTL

CNTL

ADDR

CKBF

PG. 6

DATA

CK100

&

ITP CON.

PG. 5

TERM.

MEMORY

3 SDRAM DIMM

MODULES

PG. 9-11

GTL

PG. 27

PCI BUS

2 USB CONN.

PG. 20

USB

USB

ADD/DATA

CNTL

CNTL

2 PCI IDE

CONNECTORS

PG. 19

PRIMARY

IDE

SECONDARY

IDE

CNTL

PG. 16-17

PCI CONN

PCI CONN

PCI CONN

PCI CONN

82371EB

324 BGA

PG. 12-13

ADDR

FLASH

BIOS

PG. 21

LM79

PG. 33

CONTROL

2

DATA

ADDR

X-BUS

KEYBOARD

PG. 24

MOUSE

PG. 24

CNTL

DATA

C C

D D

1

ADDR

ULTRA I/O

FLOPPY

CONN.

PG. 23

3

ADDR/DATA

CNTL

PG.14

PARA.

CONN.

PG. 20

DATA

SER.

CONN.

PG .23

SER.

CONN.

ADDR/DATA

ISA BUS

PG 18

ADDR

CNTL

DATA

RESET, POWER CONNECTORS

ISA, PCI RESISTORS

DECOUPLING CAPACITORS

4

ISA CONN

ISA CONN

5

PG. 26

PG. 28-29

PG. 30-32

6

THIS DRAWING CONTAINS INFORMATION WHICH HAS NOT

BEEN VERIFIED FOR MANUFACTURING AN END USER

PRODUCT. iNTEL IS NOT RESPONSIBLE FOR THE MISUSE

OF THIS INFORMATION.

DEVICE TABLE

DEVICE

TYPE

FUSES F1,F2,F3,F4 20,24

ITP Connector J2 5

DIMM Sockets J4,J5,J6 9,10,11

IDE Connectors J14, J15

USB Connectors J16, J17

VRM8.2 J24 25

Slot 1 Connector J33 A,B 3,4

AGP Connector J32 15

PCI Connectors J34-37 16,17

BLM31A700S L1-L6,L7-L13 20,24

CK100 U1 5

74LVC14 U5 A,B,C,D,E,F 13,26

74AS07 U7 A,B,C,D,E,F 15,26,29

74HCT14 U8 A,B,C,D,E,F 21,25,26

E28F002BC-T(FLASH) U9 21

74F07 U12 A,B,C,D,E,F 25,26,29

74LVC3244 U13 25

74ALS08 U16 A,B,C,D 26,29

74HC10 U17 A,B,C 13,26,29

82443BX U19-1,2,3 6,7,8

CKBF U20 6

LM79 U21 33

74F07 U28 A,B,C,D,E,F 13,26,29

82371EB (PIIX4E) U23 A,B 12,13

MAX1617 ME U24 3

74HC112 U27 A,B 13

LT1585 VR1 25

LT1575 VR2

Crystal (14.318MHz) Y1 5

Crystal(32.768KHz) Y2

INTEL CORPORATION

PLATFORM COMPONENTS DIVISION

1900 PRAIRIE CITY RD. FM5-62

FOLSOM, CA 95630

Title

INTEL 100MHz Pentium(tm) II processor/440BX AGPset Block Diagram

Size Document Number Rev

Custom

Date: Sheet of

3VSB

5VSB

5VSB

REFERENCE

DESIGNATOR

J12, J13ISA Connectors

U6FDC37C932FR

Intel(R) 440BX AGPset

7

PAGE #

18

19

20

14

25

13

234Thursday, April 09, 1998

8

1.0

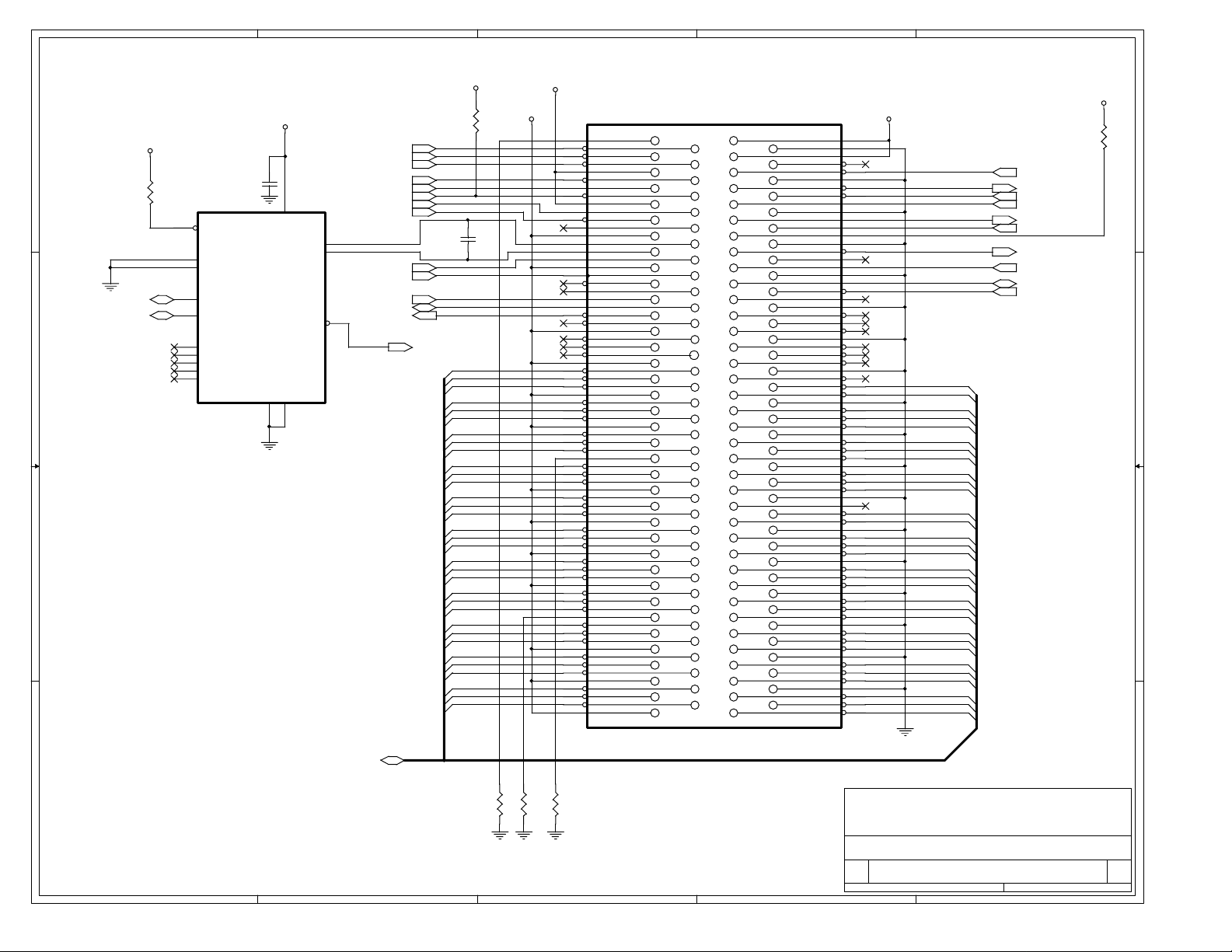

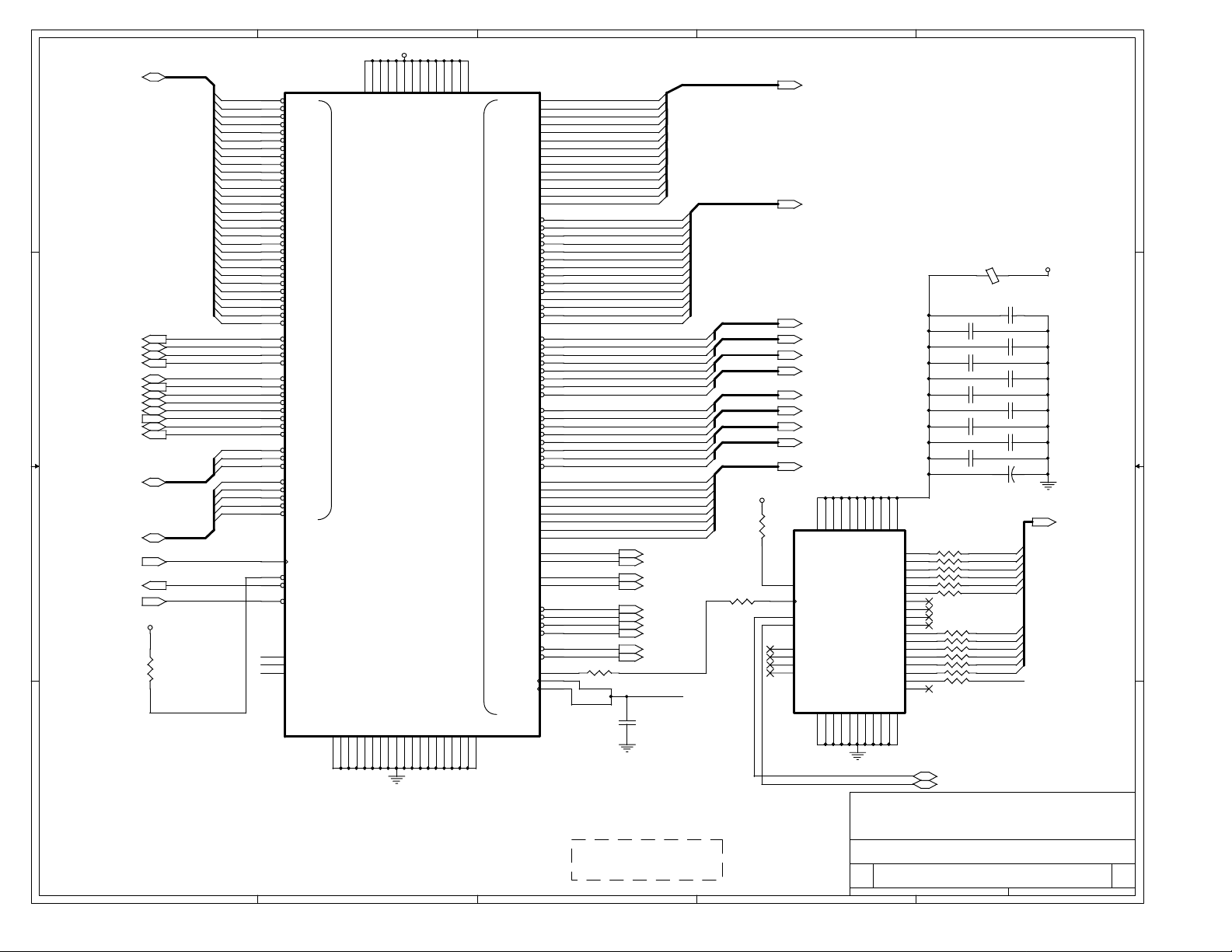

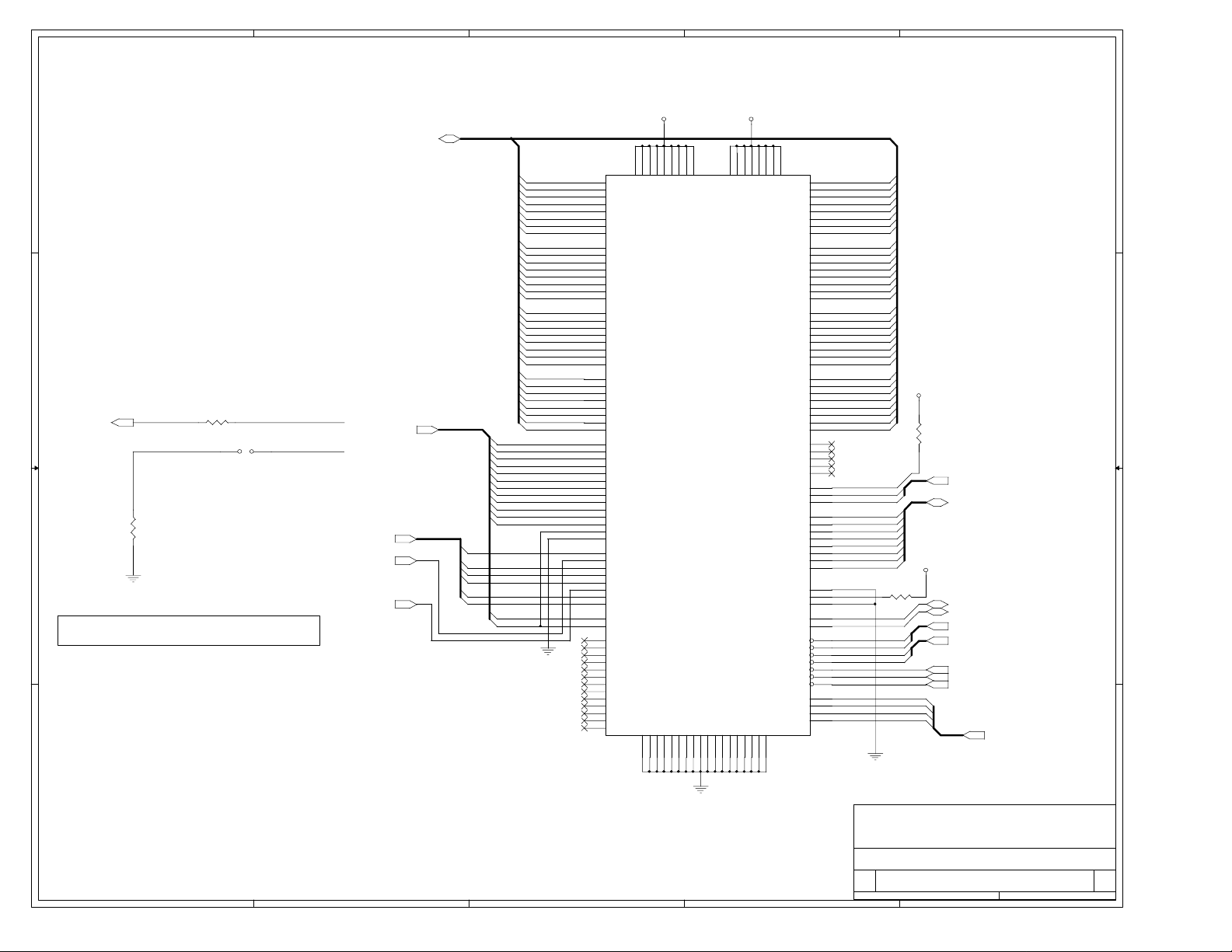

Page 3

A

y

(R)

(

)

y

]

B

C

D

E

VTTVCC2.5

* Note: This strong pullup resistor on

3

D+

4

D-

11

SLP# is necessar

LAI.

VCC3

4 4

SM B SLAVE

ADDRESS

= 0011000b

3 3

VCC3

R239

4.7K

15

6

10

SM BDATA6,9,10,11,13,28,33

SMBCLK6,9,10,11,13,28,33

12

14

1

5

9

13

16

C164

0.1 uF

U24

STBY#

ADD1

ADD0

MAX1617 ME

16p QSOP

SMBDATA

SMBCLK

RESV

RESV

RESV

RESV

RESV

2

V+

SMB_ALERT#

FLUSH#28

PX4_SMI#13,28

HINIT#13,28

STPCLK#13,28

TCK5

SLP#13

TMS5

TRST#5

LINT125,28

PICCLK5

100/66#5,11

PICD128

PRDY#05,27

when using an

2200pF

THERM# 13,28

GND7GND

MAX1617_2

2 2

8

HD#[63:0

8,27

R1

330

C188

HD#62

HD#58

HD#63

HD#56

HD#50 HD#60

HD#54

HD#59

HD#52

HD#41

HD#47

HD#44

HD#36

HD#40

HD#34

HD#38

HD#32

HD#28

HD#29

HD#26

HD#25

HD#22

HD#19

HD#18

HD#20

HD#17

HD#15

HD#12

HD#7

HD#6

HD#4

HD#2

HD#0

J33A

B01 A01

EMI

B02 A02

FLUSH#

B03

SMI#

B04

INIT#

B05

VCC_VTT

B06

STPCLK#

B07

TCK

B08

SLP#

B09

VCC_VTT

B10

TMS

B11

TRST#

B12

RESERVED

B13

VCC_CORE

B14

RESERVED

B15

RESERVED

B16

LINT[1]

B17

VCC_CORE

B18

PICCLK

B19

BP#[2]

B20

RESERVED

B21

100/66#

B22

PICD[1]

B23

PRDY#

B24

BPM#[1]

B25

VCC_CORE

B26

DEP#[2]

B27

DEP#[4]

B28

DEP#[7]

B29

VCC_CORE

B30

D#[62]

B31

D#[58]

B32

D#[63]

B33

VCC_CORE

B34

D#[56]

B35

D#[50]

B36

D#[54]

B37

VCC_CORE

B38

D#[59]

B39

D#[48]

B40

D#[52]

B41

EMI

B42

D#[41]

B43

D#[47]

B44

D#[44]

B45

VCC_CORE

B46

D#[36]

B47

D#[40]

B48

D#[34]

B49

VCC_CORE

B50

D#[38]

B51

D#[32]

B52

D#[28]

B53

VCC_CORE

B54

D#[29]

B55

D#[26]

B56

D#[25]

B57

VCC_CORE

B58

D#[22]

B59

D#[19]

B60

D#[18]

B61

EMI

B62

D#[20]

B63

D#[17]

B64

D#[15]

B65

VCC_CORE

B66

D#[12]

B67

D#[7]

B68

D#[6]

B69

VCC_CORE

B70

D#[4]

B71

D#[2]

B72

D#[0]

B73

VCC_CORE

SLOT1_0.8

VCC_VTT

GND

VCC_VTT

IERR#

A20M#

GND

FERR#

IGNNE#

TDI

GND

TDO

PWRGOOD

TESTHI1

GND

THERMTRIP#

RESERVED

LINT[0]

GND

PICD[0]

PREQ#

BP#[3]

GND

BPM#[0]

BINIT#

DEP#[0]

GND

DEP#[1]

DEP#[3]

DEP#[5]

GND

DEP#[6]

D#[61]

D#[55]

GND

D#[60]

D#[53]

D#[57]

GND

D#[46]

D#[49]

D#[51]

GND

D#[42]

D#[45]

D#[39]

GND

RESERVED

D#[43]

D#[37]

GND

D#[33]

D#[35]

D#[31]

GND

D#[30]

D#[27]

D#[24]

GND

D#[23]

D#[21]

D#[16]

GND

D#[13]

D#[11]

D#[10]

GND

D#[14]

D#[9]

D#[8]

GND

D#[5]

D#[3]

D#[1]

SLOT 1a

A03

A04

A05

A06

A07

A08

A09

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

A24

A25

A26

A27

A28

A29

A30

A31

A32

A33

A34

A35

A36

A37

A38

A39

A40

A41

A42

A43

A44

A45

A46

A47

A48

A49

A50

A51

A52

A53

A54

A55

A56

A57

A58

A59

A60

A61

A62

A63

A64

A65

A66

A67

A68

A69

A70

A71

A72

A73

VTTVCCCORE

A20M# 25,28

FERR# 13,28

IGNNE# 25,28

TDI 5

TDO 5

PW RGOOD 21,26

THERMTRIP# 28

LINT0 25,28

PICD0 28

ITPREQ# 5

HD#61

HD#55

HD#53

HD#57

HD#46HD#48

HD#49

HD#51

HD#42

HD#45

HD#39

HD#43

HD#37

HD#33

HD#35

HD#31

HD#30

HD#27

HD#24

HD#23

HD#21

HD#16

HD#13

HD#11

HD#10

HD#14

HD#9

HD#8

HD#5

HD#3

HD#1

VCC2.5

R3

4.7K

1 1

R4

0

R6

R5

0

0

* P lease place as close to the connector as possible

A

B

C

INTEL CORPORATION

PLATFORM COMPONENTS DIVISION

1900 PRAIRIE CITY RD. FM5-62

FOLSOM, CA 95630

Title

Size Document Number Rev

Custom

Date: Sheet of

D

SLOT 1

PART I

Intel

, April 09, 1998

440BX AGPset

E

334Thursda

1.0

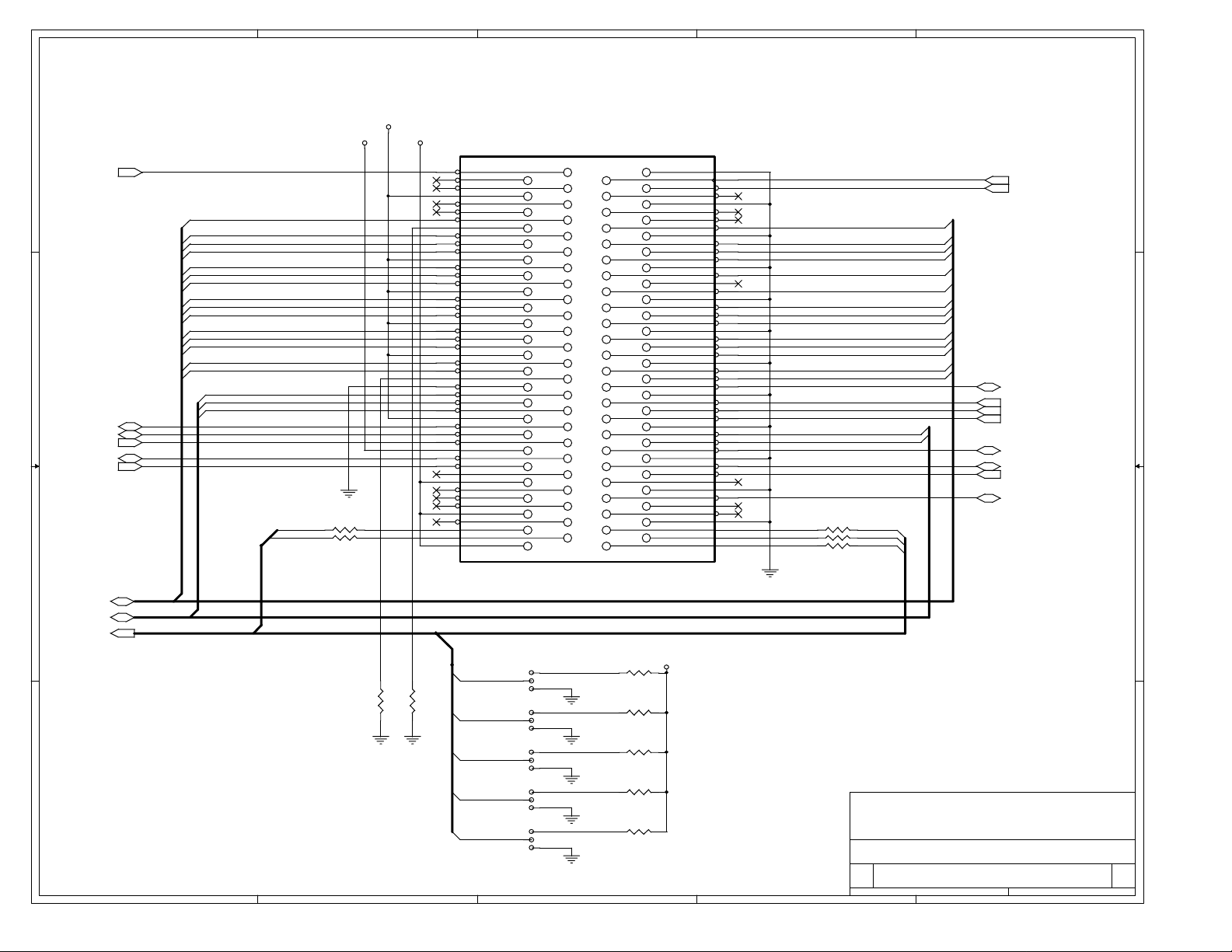

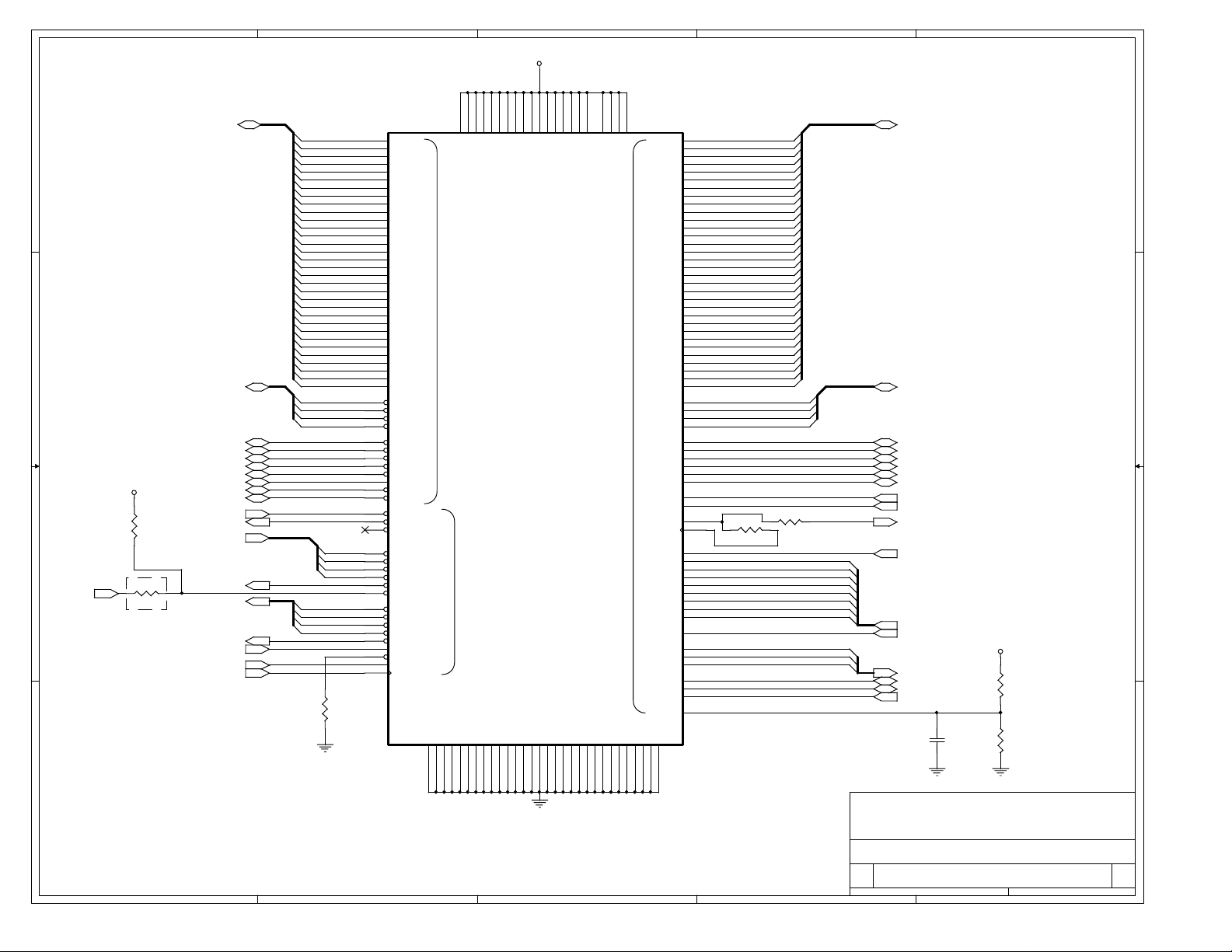

Page 4

A

(

)

y

]

]

]

B

C

D

E

VCCCORE

4 4

VCC

HRE SET#5,6,27

HA#29

HA#26

HA#24

HA#28

HA#20

HA#21

HA#25

HA#15

HA#17

HA#11

HA#12

HA#8

HA#7

3 3

HLOCK#6,27

DRDY#6,27

RS#06,27

HIT#6,27

RS#26,27

2 2

HA#3

HA#6

HREQ#0

HREQ#1

HREQ#4

VID3

VID0

R219 0

R221

0

VCC3

J33B

B74 A74

RESET#

B75 A75

BREQ1#

B76

FRCERR#

B77

VCC_CORE

B78

A#[35]

B79

A#[32]

B80

A#[29]

B81

EMI

B82

A#[26]

B83

A#[24]

B84

A#[28]

B85

VCC_CORE

B86

A#[20]

B87

A#[21]

B88

A#[25]

B89

VCC_CORE

B90

A#[15]

B91

A#[17]

B92

A#[11]

B93

VCC_CORE

B94

A#[12]

B95

A#[8]

B96

A#[7]

B97

VCC_CORE

B98

A#[3]

B99

A#[6]

B100

EMI

B101

SLOTOCC#

B102

REQ#[0]

B103

REQ#[1]

B104

REQ#[4]

B105

VCC_CORE

B106

LOCK#

B107

DRDY#

B108

RS#[0]

B109

VCC_5

B110

HIT#

B111

RS#[2]

B112

RESERVED

B113

VCC_3

B114

RP#

B115

RSP#

B116

AP#[1]

B117

VCC_3

B118

AERR#

B119

VID[3]

B120

VID[0]

B121

VCC_3

SLOT1_0.8

SLOT 1b

BREQ0#

BERR#

A#[33]

A#[34]

A#[30]

A#[31]

A#[27]

A#[22]

A#[23]

RESERVED

A#[19]

A#[18]

A#[16]

A#[13]

A#[14]

A#[10]

BPRI#

TRDY#

DEFER#

REQ#[2]

REQ#[3]

HITM#

DBSY#

RS#[1]

RESERVED

RESERVED

AP#[0]

VID[2]

VID[1]

VID[4]

GND

BCLK

GND

GND

GND

GND

GND

A#[5]

GND

A#[9]

A#[4]

BNR#

GND

GND

GND

GND

ADS#

GND

A76

A77

A78

A79

A80

A81

A82

A83

A84

A85

A86

A87

A88

A89

A90

A91

A92

A93

A94

A95

A96

A97

A98

A99

A100

A101

A102

A103

A104

A105

A106

A107

A108

A109

A110

A111

A112

A113

A114

A115

A116

A117

A118

A119

A120

A121

R220 0

R222 0

R223 0

HREQ#2

HREQ#3

VID2

VID1

VID4

HA#30

HA#31

HA#27

HA#22

HA#23

HA#19

HA#18

HA#16

HA#13

HA#14

HA#10

HA#5

HA#9

HA#4

CPUHCLK 5

BREQ0# 6,27

BNR # 6,27

BP RI# 6,27

HTRDY# 6,27

DE F ER # 6,27

HITM# 6,27

DBSY# 6,27

RS#1 6, 27

ADS# 6,27

HA#[31:3

6,27

HREQ#[4:0

6,27

VID[4:0

25,33

JP1

1

JP2

JP3

JP4

JP5

3

1

3

1

3

1

3

1

3

SE L _VID0

SE L _VID1

SE L _VID2

SE L _VID3

SE L _VID4

C

2

VID0

* Please place as close to

the connector as possible

1 1

A

B

R9

R8

0

0

VID1

VID2

VID3

VID4

2

2

2

2

R7

8.2K

R10

8.2K

R11

8.2K

R12

8.2K

R13

8.2K

VCC

VRM optional override

jumpers & resistors

Jumper position 1-2 is

stuffed as the default. To

override, R219-223 must

be removed.

INTEL CORPORATION

PLATFORM COMPONENTS DIVISION

1900 PRAIRIE CITY RD. FM5-62

FOLSOM, CA 95630

Title

Size Document Number Rev

Custom

Date: Sheet of

D

SLOT 1

PART II

Intel(R) 440BX AGPset 1.0

, April 09, 1998

434Thursda

E

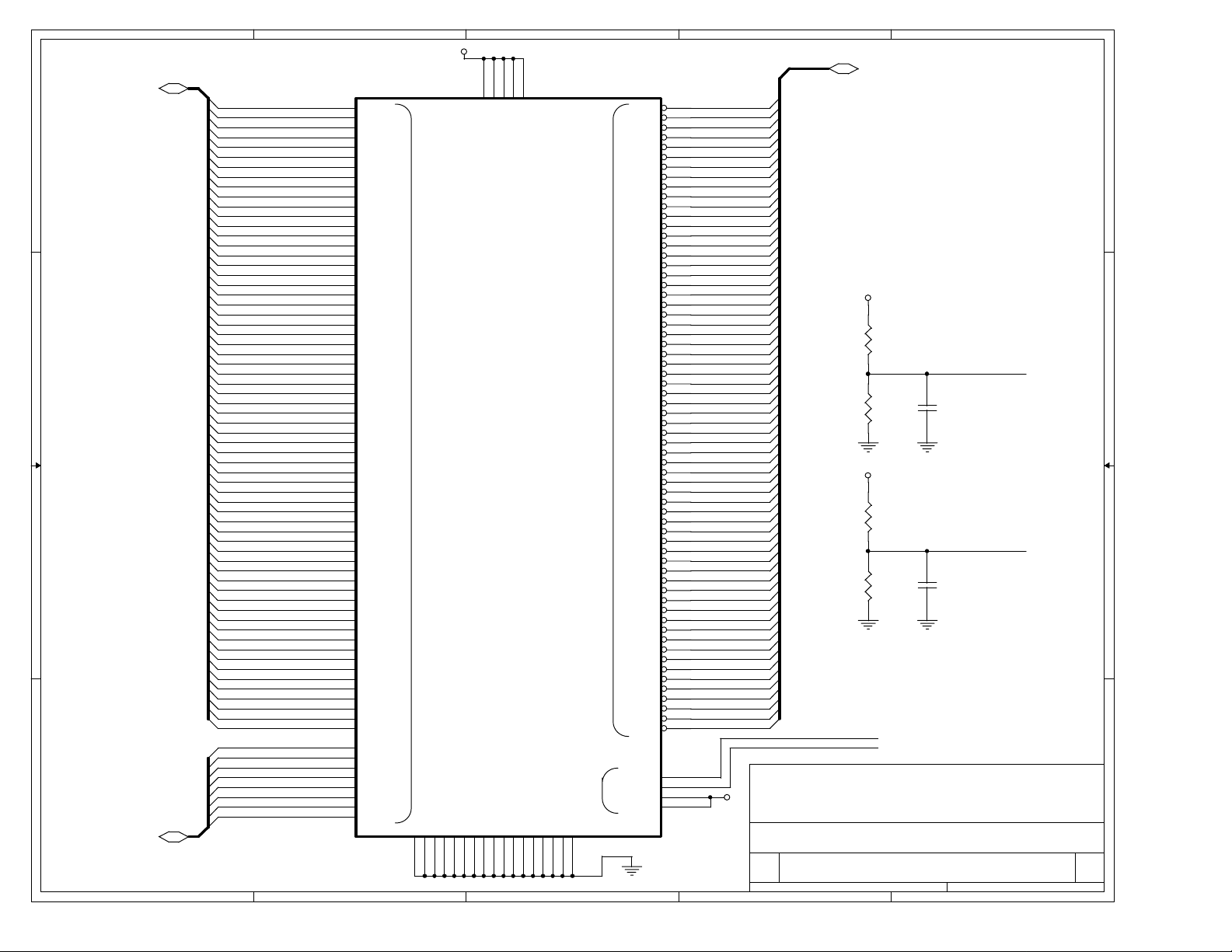

Page 5

A

g

g

g

B

C

D

E

CLOCK SYNTHESIZER

CD94

0.01uF

16V

L14

2 1

FBHS01L

CD95

0.01uF

16V

VCC3

4 4

3 3

100/66#3,11

PCI_STP#13

CPU_STP#13

SUSA#13

VCC3

R176

200

R264

0

R265

0

R266

0

R18

8.2K

VCC3

R19

8.2K

R20

8.2K

DO NOT STUFF

option to enable the

Stuffin

of the CPUCLKs,

stoppin

PCICLKs, and the powerdown of

the CK100. Please note that the

resistors are not stuffed.

FBHS01L

CD85

0.01 uF

16V

R224

0

L15

CD86

0.01 uF

16V

R242

10K

21

C1

10pF

C2

10pF

CD87

0.01uF

16V

R249

10K

CD88

100pF

16V

Y1

14.318MHz

VCC3

R250

10K

CD89

100pF

16V

XTLI1

XTLO1

CD90

100pF

16V

U1

4

XTALIN

5

XTALOUT

42

RESV

28

RESV

27

SEL0

26

SEL1

25

SEL_100/66#

31

PCI_STP#

30

CPU_STP#

29

PWRDWN#

CK100_05

C168

+

22uF

9

15

19

VDDPCI0

VDDPCI1

VDDCORE0

48

33

21

VDDQREF

VDD48MHZ

VDDCORE1

CK100

VSSREF

VS S PCI06VSSPCI1

3

12

46

41

37

VDDAPIC

VDDCPU0

VDDCPU1

VSSCORE1

VSS48MHZ

VSS CORE0

VSSPCI218VSSCPU0

32

24

20

CPUCLK0

CPUCLK1

CPUCLK2

CPUCLK3

PCICLK_F

PCICLK_1

PCICLK_2

PCICLK_3

PCICLK_4

PCICLK_5

PCICLK_6

PCICLK_7

48MHZ_0

48MHZ_1

APICCLK_0

APICCLK_1

VSSAPIC

VSSCPU1

43

38

34

40

39

36

35

7

8

10

11

13

14

16

17

22

23

45

44

1

REF0

2

REF1

47

REF2

VCC2.5 VTT

CD91

CD92

100pF

100pF

16V

16V

R27

R14 22

R15 22

R16 22

R17 22

R22 22

R23 22

R24 22

R25 22

R26

22

R177 22

R178

22

R179

22

R180

22

CD93

0.01uF

16V

22

ITPCLK

C169

+

22uF

VCC2.5

BXHCLK 6

CPUHCLK 4

PXPCLK 13

PCLK1 16

PCLK2 16

PCLK3 17

PCLK4 17

BXPCLK 7

48Mhz_0 13

PICCLK 3

OSC1 18

OSC2 13

OSC3 14

* Note * This is a stuffing option: 10-15

pF caps to ground may be desirable to

redu ce t he effects of EMI.

* Note * For power managed systems, the PIIX4 must be

connected to PCICLK_F of the CK100 which is a free

PCLK not affected by the assertion of

runnin

PCISTOP#.

VCC2.5

R29

2 2

1 1

Stuffing option to enable Spread#

function for possible EMI reduction.

A

240

HRESET#4,6,27

DBRESET#26

TCK3

TMS3

B

R34

R237

47

R238

47

R28

1K

R36

1K

1K

5%

ITP_RST

ITP_PON

ITPCLK

C

OPTIONAL ITP

TEST

CONNECTOR

J2

1 2

3 4

5 6

7 8

9 10

11 12

13 14

15 16

17 18

19 20

21 22

23 24

25 26

27 28

29 30

ITP CONN

D

R33

R30

330

PRDY0_R#

INTEL CORPORATION

PLATFORM COMPONENTS DIVISION

1900 PRAIRIE CITY RD. FM5-62

FOLSOM, CA 95630

Title

CLOCK SYNTHESIZER

Size Document Number Rev

Custom

Date: Sheet of

R32

330

150

240

R35

Intel(R) 440BX AGPset

R37

680

E

TDI 3

TDO 3

TR ST# 3

ITPREQ# 3

PRDY#0 3,27

534Thursday, April 09, 1998

1.0

Page 6

A

g

y

]

]

]

HA#[31:3

4,27

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

4 4

HRE SET#4,5,27

ADS#4,27

3 3

2 2

1 1

BNR#4,27

BPRI#4,27

DBSY#4,27

DEFER#4,27

DRDY#4,27

HIT#4,27

HITM#4,27

HLOCK#4,27

HTRDY#4,27

BREQ0#4,27

RS#[2:0

4,27

HREQ#[4:0

4,27

BXHCLK5

CR ESET#25

PCI RST#12 ,15,16,17

** TESTIN# pullup may be removed after

validation has been completed.

CR ESET# CKE1

VCC3

R39

8.2K

A

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

RS#0

RS#1

RS#2

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

G25

H22

G23

H23

G24

F26

G26

G22

F22

F23

F24

F25

E23

E26

E25

D25

D26

B25

C26

A25

C25

A24

D24

C23

B24

C24

A23

E22

D23

B23

K21

H24

H26

L23

J26

K23

L24

L22

K22

H25

B26

K26

L26

L25

J22

J23

K24

K25

J25

N23

M25

M26

AE22

AE23

P22

A3

U19-1

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

CPURST#

ADS#

BNR#

BPRI#

DBSY#

DEFER#

DRDY#

HIT#

HITM#

HLOCK#

HTRDY#

BREQ0#

RS#0

RS#1

RS#2

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HCLKIN

TE S TIN#

CRESET#

PCI RST#

RESVA

RE SVB

RESVC

443 BX_10

B

VCC3

V21

Y21

F18

F20

G21

J21

AA7

VDD

VDD

VDDF7VDDF9VDD

VDD

VDDG6VDD

VDDJ6VDD

82443BX

492 BGA

SYSTEM INTERFACE

VSSA1VSS

VSS

VSSC5VSSC9VSS

VSS

VSSE3VSS

VSS

VSS

VSSF6VSSF8VSS

A14

A26

C18

C22

B

E12

E15

E24

F19

F21

AA9

VDD

VSS

AA18

VDD

VDD

VSSH6VSS

H21

AA20

VDD

CKE2/CSA6#

CKE3/CSA7#

DRAM INTERFACE

CKE4/CSB6#

CKE5/CSB7#

VSSJ3VSS

J24

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

MAA13

MAB0#

MAB1#

MAB2#

MAB3#

MAB4#

MAB5#

MAB6#

MAB7#

MAB8#

MAB9#

MAB10

MAB11#

MAB12#

MAB13

CSA0#

CSA1#

CSA2#

CSA3#

CSA4#

CSA5#

CSB0#

CSB1#

CSB2#

CSB3#

CSB4#

CSB5#

DQMA0

DQMA1

DQMA2

DQMA3

DQMA4

DQMA5

DQMA6

DQMA7

DQMB1

DQMB5

CKE0/FENA

CKE1/GCKE

SRAS_A#

SRAS_B#

SCAS_A#

SCAS_B#

WE_A#

WE_B#

DCLKO

DCLKWR

DCLKRD

C

AF17

AB16

AE17

AC17

AF18

AE19

AF19

AC18

AC19

AE20

AD20

AF21

AC21

AF25

AD16

AC16

AD17

AB17

AE18

AD19

AB18

AB19

AF20

AC20

AB20

AE21

AD21

AF22

AB14

AF15

AE15

AC15

AD15

AE16

AE24

AD23

AE25

AD24

AD26

AC24

AC26

AB23

AC23

AF24

AD13

AC13

AC25

AB26

AE14

AC14

AA22

AA24

AE13

AD14

AC22

AF23

AF16

AA17

AF12

AB13

AE12

AC12

AB21

AD25

AB22

**Locate R280 close to CKBF and

R281 close to 443BX.

**Locate "T" and cap close to BX.

** Pl ea se make DCLKREF trace length equal to 2.5" more

than the DCLK outputs to the DIMMs. DCLK outputs to

the DIMMs should all be the same recommended len

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

MAA13

MAB#0

MAB#1

MAB#2

MAB#3

MAB#4

MAB#5

MAB#6

MAB#7

MAB#8

MAB#9

MAB10

MAB#11

MAB#12

MAB13

CS_A#0

CS_A#1

CS_A#2

CS_A#3

CS_A#4

CS_A#5

CKE2

CKE3

CS_B#0

CS_B#1

CS_B#2

CS_B#3

CS_B#4

CS_B#5

CKE4

CKE5

DQMA0

DQMA1

DQMA2

DQMA3

DQMA4

DQMA5

DQMA6

DQMA7

DQMB1

DQMB5

CKE0

R281

22

Example: if DCLK[0-11] = 2.5"

then DCLKREF = 2.5" + 2.5".

C

DQMB1 11

DQMB5 11

CKE0 9

CKE1 9

SRA S_A# 9,10

SR AS_B# 11

SCA S_A# 9,10

SC AS_B# 11

WE_A# 9,10

WE_B# 11

DCLKREF

C162

20pF

R38

4.7k

R280

47

VCC3

D

MAA[13:0]9,10

MAB#[13:0]11

CS_A#[1:0]9

CS_A#[3:2]10

CS_A#[5:4]11

CKE[3:2]10

CS_B#[1:0]9

CS_B#[3:2]10

CS_B#[5:4]11

CKE[5:4]11

DQMA[7:0]9,10,11

U20

38

OE

11

BUF_IN

25

SCLOCK

24

SDATA

1

RESV

2

RESV

47

RESV

48

RESV

CKBF

th.

D

E

L16

2 1

FBHS01L

100pF

.01uF

C175

100pF

.01uF

C177

100pF

.01uF

C179

100pF

.01uF

C181

100pF

.01uF

C183

22uF

3

23

VDD

VDD7VDD12VDD16VDD20VDD29VDD33VDD37VDD42VDD

VDDIIC

CKBF

VSS6VSS10VSS

VSSIIC

15

26

Title

Size Document Number Rev

Date: Sheet of

46

R181 0

4

SDRAM0

5

SDRAM1

8

SDRAM2

9

SDRAM3

13

SDRAM4

14

SDRAM5

17

SDRAM6

18

SDRAM7

31

SDRAM8

32

SDRAM9

35

SDRAM10

36

SDRAM11

40

SDRAM12

41

SDRAM13

44

SDRAM14

45

SDRAM15

21

SDRAM16

28

SDRAM17

VSS19VSS22VSS27VSS30VSS34VSS39VSS

43

INTEL CORPORATION

PLATFORM COMPONENTS DIVISION

1900 PRAIRIE CITY RD. FM5-62

FOLSOM, CA 95630

82443BX SYSTEM AND DRAM INTERFACES

Custom

, April 09, 1998

0

R182

R183 0

R184 0

R185 0

R186 0

R187 0

R188 0

R189 0

R190 0

R191 0

R193 0

R194 0

slave address =

1101001b

SMBCLK 3,9,10,11,13,28,33

SM BDATA 3,9,10,11,13,28,33

Intel(R) 440BX AGPset 1.0

DCLK9

DCLK8

DCLK5

DCLK4

DCLK0

DCLK1

DCLK11

DCLK10

DCLK7

DCLK6

DCLK3

DCLK2

DCLKREF

VCC3

C174

C176

C178

C180

C182

+

C184

**Please Note **

These clock

assignments may

not be optimum.

*The unused SDRAM

clocks may be disabled

using the SMBus

interface.

634Thursda

E

DCLK[11:0]9,10,11

Page 7

A

g

g

y

]

]

]

]

B

VCC3

C

D

E

AD[31:0

12 ,16,17

4 4

3 3

C/BE#[3:0

12,16,17

FRAME#12, 16,17,28

DEVSEL#12, 16,17,28

IRDY#12, 16,17,28

TRDY#12, 16,17,28

STOP#12,16,17,28

16,17,28

16 ,17,28

PAR12 ,16,17

SERR#12, 16,17,28

PLOCK#16 ,17,28

PHLD#12,28

PHLDA#12,28

PREQ#[3:0

PREQ#428

PGNT#[3:0

VCC3

R196

10K

2 2

SUSTAT#13

R282

0

DO NOT STUFF

Stuffing option to enable and test

the POS state.

1 1

A

PG NT#428

PWROK13,26

VREF5V13

BXPCLK5

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

C/BE#0

C/BE#1

C/BE#2

C/BE#3

PREQ#0

PREQ#1

PREQ#2

PREQ#3

PREQ#4

PG NT#0

PG NT#1

PG NT#2

PG NT#3

PG NT#4

R255

100

U19-2

K6

AD0

K2

AD1

K4

AD2

K3

AD3

K5

AD4

J1

AD5

J2

AD6

H2

AD7

H1

AD8

J5

AD9

H3

AD10

H5

AD11

H4

AD12

G1

AD13

G2

AD14

G4

AD15

D1

AD16

D3

AD17

D2

AD18

C1

AD19

A2

AD20

C3

AD21

B3

AD22

D4

AD23

E5

AD24

A4

AD25

D5

AD26

B4

AD27

B5

AD28

A5

AD29

E6

AD30

C6

AD31

J4

C/BE0#

G3

C/BE1#

E4

C/BE2#

C4

C/BE3#

E2

FRAME#

F3

DEVSEL#

E1

IRDY#

F5

TRDY#

F4

STOP#

G5

PAR

F1

SERR#

F2

PLOCK#

B6

PHOLD#

D6

PHLDA#

AE3

WSC#

A6

PR EQ0#/IOREQ#

C7

PREQ1#

F10

PREQ2#

D8

PREQ3#

D10

PREQ4#

AD4

SUSTAT#

E7

PGNT0#/IOGNT#

D7

PG NT1#

E10

PG NT2#

E8

PG NT3#

E9

PG NT4#

AF3

BX-PWROK

AC4

CLKRUN#

C2

REFVCC5

B2

PCLKIN

443 BX_10

B

L14

L13

L11

VDD

VDD

PCI INTERFACE

PCI ARB & PWR MGT

VSSN1VSSM5VSS

VSS

VSS

VSS

L12

L15

M11

M13

M14

N11

M15

M12

L16

VDD

VDD

VDD

VDD

82443BX

VSS

VSS

VSS

VSS

N12

N13

M16

M22

N16

P11

P16

VDD

VDD

VDD

492 BGA

VSS

VSS

VSS

N14

N15

P12

VDD

VSS

R12

VDD

VSS

P13

R15

P14

T11

VDD

VSS

P15

T13

VDD

VSS

P26

T14

VDD

VSS

T12

T16

VDD

VSS

T15

N26

VDD

VSS

C

VDD

VSSR5VSS

R11

P1

R13

AE1

VDD

VSS

R14

VDD

VSS

V6

Y6

GAD0

GAD1

VDD

VDD

GAD2

GAD3

GAD4

GAD5

GAD6

GAD7

GAD8

GAD9

GAD10

GAD11

GAD12

GAD13

GAD14

GAD15

GAD16

GAD17

GAD18

GAD19

GAD20

GAD21

GAD22

GAD23

GAD24

GAD25

GAD26

GAD27

GAD28

GAD29

GAD30

GAD31

GC/BE0#

GC/BE1#

GC/BE2#

GC/BE3#

GFRAME#

GDEVSEL#

GIRDY#

GTRDY#

AGP INTERFACE

GSTOP#

GPAR

GREQ#

GGNT#

GCLKOUT

GCLKIN

PIPE#

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

RBF#

GADSTB-A

GADSTB-B

SB-STB

AGPREFV

VSS

VSS

VSSV3VSS

VSSW6VSS

V24

R16

R22

W21

ST0

ST1

ST2

AB5

AE2

AD3

AD2

AD1

AC3

AC1

AB4

AB1

AA5

AA3

AA4

AA2

AA1

Y5

Y3

W1

V2

W2

U5

V1

U4

U3

U1

T3

T4

T2

T1

U6

R3

R4

R2

AB2

Y4

V4

U2

W3

W5

V5

W4

Y1

Y2

L5

L3

P5

N5

M3

K1

M2

M1

N2

P2

P4

P3

R1

M4

L4

L2

L1

AC2

T5

N3

N4

GAD0

GAD1

GAD2

GAD3

GAD4

GAD5

GAD6

GAD7

GAD8

GAD9

GAD10

GAD11

GAD12

GAD13

GAD14

GAD15

GAD16

GAD17

GAD18

GAD19

GAD20

GAD21

GAD22

GAD23

GAD24

GAD25

GAD26

GAD27

GAD28

GAD29

GAD30

GAD31

GCBE#0

GCBE#1

GCBE#2

GCBE#3

R241

22

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

ST0

ST1

ST2

R240

22

** Place as close to

443BX as possible.

D

GAD[31:0]15

GC/BE#[3:0]15

GFRAME# 15,28

GDEVSEL# 15,28

GIRDY# 15,28

GTRDY# 15,28

GSTOP# 15,28

GP AR 15,28

GREQ# 15,28

GG NT# 15 ,28

GC LKOUT 15

PIPE# 15,28

** Note** Please make the

GCLKIN trace length 3.3"

more than the GCLKOUT

recommended trace length.

Stub to tee should be 1"

MAX.

SBA[7:0]15

RB F# 15,28

ST[2:0]15

AD S TB-A 15,28

ADSTB-B 15,28

SBSTB 15,28

INTEL CORPORATION

PLATFORM COMPONENTS DIVISION

1900 PRAIRIE CITY RD. FM5-62

FOLSOM, CA 95630

Title

82443BX PCI AND AGP INTERFACES

Size Document Number Rev

Custom

Date: Sheet of

Intel(R) 440BX AGPset 1.0

, April 09, 1998

C157

0.001uF

VCC3

R174

150

** It is

1%

recommended that

the tolerance on

the se resistors be

R175

1% i n order to meet

100

1%

the mar

reference volta

734Thursda

E

ins of this

e.

Page 8

A

y

]

]

B

VCC3

C

D

E

HD#[63:0]3,27

AF4

AE4

AF5

AD6

AE6

AB7

AC7

AF7

AB8

AB9

AC9

AE9

AB10

AC10

AF10

AD11

Y24

Y25

W23

W24

W26

W25

V26

U24

U23

T22

T23

T26

R24

R25

P23

N25

AC5

AE5

AB6

AC6

AF6

AD7

AE7

AC8

AD8

AF8

AE8

AF9

AD10

AE10

AB11

AC11

Y23

Y26

W22

V22

V23

V25

U22

U25

U26

T24

T25

U21

R23

R26

P24

P25

AE11

AA10

AA23

AA26

AF11

AD12

AA25

Y22

U19-3

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

MECC0

MECC1

MECC2

MECC3

MECC4

MECC5

MECC6

MECC7

443BX_10

B

MEMORY DATA BUS

VSS

N24

AB25

VSS

AA6

VSS

AA8

VSS

AA19

VSS

AA21

MD[63:0

9,10,11

MD0

MD1

MD2

MD3

4 4

3 3

2 2

1 1

MECC[7:0

9,10,11

A

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

MECC0

MECC1

MECC2

MECC3

MECC4

MECC5

MECC6

MECC7

AF2

AE26

N22

AF14

VDDB1VDD

VDD

VDD

VDD

82443BX

492 BGA

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AB3

AD5

AD9

AB12

AB15

AB24

AD18

VSS

AF1

AD22

VSS

VSS

AF13

VSS

AF26

C

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HOST DATA BUS

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

GTLREFA

GTLREFB

VTTA

VTTB

B22

D22

E21

A22

D21

C21

A21

C20

B21

E20

A20

E19

B20

E18

D20

D19

D18

C19

B19

A18

A19

B18

C17

E17

D17

B17

C16

A17

C15

B16

D16

A16

B15

A15

D14

D15

B13

C14

E14

D13

A13

D12

B12

B14

C13

E13

D11

A12

B11

A11

B7

C12

C8

B10

A10

A9

A7

E11

D9

C11

C10

B8

A8

B9

M23

E16

M24

F17

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

VTT

VTT

GTLREF2

GTLREF1

R170

75

1%

R171

150

1%

R172

75

1%

R173

150

1%

C155

0.001uF

C156

0.001uF

GTLREF1

GTLREF2

INTEL CORPORATION

PLATFORM COMPONENTS DIVISION

VTT

1900 PRAIRIE CITY RD. FM5-62

FOLSOM, CA 95630

Title

82443BX MD/HD BUS

Size Document Number Rev

Custom

Date: Sheet of

D

Intel(R) 440BX AGPset

, April 09, 1998

834Thursda

E

1.0

Page 9

A

y

B

C

D

E

DIMM SOCKET 0

VCC3VCC3

MD[63:0]8,10,11

40

102

4 4

3 3

MAA[13:0]6,10

DQMA[7:0]6,10,11

2 2

DIMM 0 DIMM 1 DIMM 2

CONTROL B

824 43BX

CONTROL A

MAB

MAA

STRAPS

MD0

MD1

MD2

MD3

MD4

MD5 MD21

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

100

MD44

101

MD45

103

MD46

104

MD47

MAA0

MAA1

117

MAA2

118

MAA3

MAA4

MAA5

119

MAA6

120

MAA7

MAA8

121

MAA9

MAA10

MAA13

123

126

132

DQMA0

DQMA1

DQMA2

DQMA3

DQMA4

112

DQMA5

113

DQMA6

130

131

DQMA7

MAA11

122

MAA12

109

108

145

2

3

4

5

7

8

9

10

11

13

14

15

16

17

19

20

86

87

88

89

91

92

93

94

95

97

98

99

33

34

35

36

37

38

28

29

46

47

39

24

25

31

44

48

50

51

61

80

81

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10 (AP)

A11

A12

A13

DQMB0

DQMB1

DQMB2

DQMB3

DQMB4

DQMB5

DQMB6

DQMB7

BA0

BA1

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

J4

DIMM REF

18

VCC6VCC26VCC

VCC

VSS1VSS

124

110

VCC41VCC90VCC

VCC

VCC

VSS23VSS32VSS85VSS96VSS

VSS43VSS54VSS64VSS68VSS78VSS

12

VCC49VCC59VCC73VCC84VCC

VSS

107

116

127

138

VSS

143

157

168

133

VCC

VSS

VSS

148

152

162

VSS

VCC

VCC

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

REGE

CKE0

CKE1

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

SA0

SA1

SA2

SDA

SCL

/WE0

/CAS

/RAS

CK0

CK1

CK2

CK3

55

MD16

56

MD17

57

MD18

58

MD19

60

MD20

65

66

MD22

67

MD23

69

MD24

70

MD25

71

MD26

72

MD27

74

MD28

75

MD29

76

MD30

77

MD31

139

MD48

140

MD49

141

MD50

142

MD51

144

MD52

149

MD53

150

MD54

151

MD55

153

MD56

154

MD57

155

MD58

156

MD59

158

MD60

159

MD61

160

MD62

161

MD63

134

NC

135

NC

146

NC

164

NC

62

NC

147

128

CKE0

63

CKE1

21

MECC0

22

MECC1

52

MECC2

53

MECC3

105

MECC4

106

MECC5

136

MECC6

137

MECC7

165

166

167

82

83

30

CS_A#0

/S0

114

CS_A#1

/S1

45

CS_B#0

/S2

129

CS_B#1

/S3

27

111

115

42

125

79

163

Slave address = 1010000b

DCLK8

DCLK9

DCLK10

DCLK11

**NOTE ON ALL DIMM SOCKETS**

VCC3

Pin 147 should be pulled to a high state

to accommodate registered DIMMs.

R252

0 ohm

CKE[1:0] 6

MECC[7:0] 8,10,11

SMBDATA 3,6,10,11,13,28,33

SMBCLK 3,6,10,11,13,28,33

CS_A#[1:0] 6

CS_B#[1:0] 6

WE_A# 6,10

SCAS_A# 6,10

SRAS_A# 6,10

DCLK[11:0] 6,10,11

1 1

Block diagram for 3 DIMM MA and control connection.

A

B

C

D

INTEL CORPORATION

PLATFORM COMPONENTS DIVISION

1900 PRAIRIE CITY RD. FM5-62

FOLSOM, CA 95630

Title

DIMM SOCKET 0

Size Document Number Rev

Custom

Date: Sheet of

Intel(R) 440BX AGPset

, April 09, 1998

934Thursda

E

1.0

Page 10

A

y

B

C

D

E

DIMM SOCKET 1

VCC3 VCC3

4 4

3 3

2 2

MD[63:0]8,9,11

40

102

MD0 MD16

MD1 MD17

MD2 MD18

MD3 MD19

MD4 MD20

MD5 MD21

MD6 MD22

MD7 MD23

MD8 MD24

MD9 MD25

MD10 MD26

MD11 MD27

MD12 MD28

MD13 MD29

MD14 MD30

MD15 MD31

MD32 MD48

MD33 MD49

MD34 MD50

MD35 MD51

MD36 MD52

MD37 MD53

MD38 MD54

MD39 MD55

MD40 MD56

MD41 MD57

MD42 MD58

MD43 MD59

MD44 MD60

MD45 MD61

MD46 MD62

MAA[13:0]6,9

DQMA[7:0]6,9,11

MD47 MD63

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA13

DQMA0

DQMA1

DQMA2

DQMA3

DQMA4

DQMA5

DQMA6

DQMA7

MAA11

MAA12

3

4

5

7

8

9

10

11

13

14

15

16

17

19

20

86

87

88

89

91

92

93

94

95

97

98

99

100

101

103

104

33

117

34

118

35

119

36

120

37

121

38

123

126

132

28

29

46

47

112

113

130

131

122

39

24

25

31

44

48

50

51

61

80

81

109

108

145

DIMM REF

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10 (AP)

A11

A12

A13

DQMB0

DQMB1

DQMB2

DQMB3

DQMB4

DQMB5

DQMB6

DQMB7

BA0

BA1

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

J5

VCC6VCC26VCC

VCC

18

2

124

110

VCC41VCC90VCC

VCC

VCC

VSS1VSS

VSS23VSS32VSS85VSS96VSS

VSS43VSS54VSS64VSS68VSS78VSS

12

VCC49VCC59VCC73VCC84VCC

VSS

VSS

107

116

127

138

143

157

168

133

VCC

VSS

VSS

148

152

162

VSS

VCC

VCC

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

REGE

CKE0

CKE1

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

SDA

SCL

/WE0

/CAS

/RAS

CK0

CK1

CK2

CK3

SA0

SA1

SA2

55

56

57

58

60

65

66

67

69

70

71

72

74

75

76

77

139

140

141

142

144

149

150

151

153

154

155

156

158

159

160

161

134

NC

135

NC

146

NC

164

NC

62

NC

147

128

CKE2

63

CKE3

21

MECC0

22

MECC1

52

MECC2

53

MECC3

105

MECC4

106

MECC5

136

MECC6

137

MECC7

165

R_SA0

166

167

82

83

30

CS_A#2

/S0

114

CS_A#3

/S1

45

CS_B#2

/S2

129

CS_B#3

/S3

27

111

115

42

125

79

163

DCLK4

DCLK5

DCLK6

DCLK7

VCC3

R253

**NOTE ON ALL DIMM SOCKETS**

0 ohm

Pin 147 should be pulled to a high state

to accommodate registered DIMMs.

CKE[3:2] 6

MECC[7:0] 8,9,11

VCC3

R42

4.7K

Slave address = 1010001b

SMBDATA 3,6,9,11,13,28,33

SMBCLK 3,6,9,11,13,28,33

CS_A#[3:2] 6

CS_B#[3:2] 6

WE_A# 6,9

SCAS_A# 6,9

SRAS_A# 6,9

DCLK[11:0] 6,9,11

1 1

A

B

C

D

INTEL CORPORATION

PLATFORM COMPONENTS DIVISION

1900 PRAIRIE CITY RD. FM5-62

FOLSOM, CA 95630

Title

DIMM SOCKET 1

Size Document Number Rev

Custom

Date: Sheet of

Intel(R) 440BX AGPset

, April 09, 1998

10 34Thursda

E

1.0

Page 11

A

B

C

D

E

DIMM SOCKET 2

VCC3VCC3

4 4

3 3

100/66#3,5

R199

10K

2 2

R200

10K

JP19

IOQ DEPTH SEL

MAB#12

MAB#11

MAB#11: 1 = IOQ depth of 4 (default), 0 = IOQ depth of 1

MD[63:0]8,9,10

40

102

18

MD0

MD1 MD17

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

DQMA0

DQMA2

DQMA3

DQMA4

DQMA6

DQMA7

MAB#11

MAB#12

MD47

MAB#0

MAB#1

MAB#2

MAB#3

MAB#4

MAB#5

MAB#6

MAB#7

MAB#8

MAB#9

MAB10

MAB13

MAB#[13:0]6

DQMA[7:0]6,9,10

DQMB16

DQMB56

2

3

4

5

7

8

9

10

11

13

14

15

16

17

19

20

86

87

88

89

91

92

93

94

95

97

98

99

100

101

103

104

33

117

34

118

35

119

36

120

37

121

38

123

126

132

28

29

46

47

112

113

130

131

122

39

24

25

31

44

48

50

51

61

80

81

109

108

145

DIMM REF

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10 (AP)

A11

A12

A13

DQMB0

DQMB1

DQMB2

DQMB3

DQMB4

DQMB5

DQMB6

DQMB7

BA0

BA1

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

J6

VCC6VCC26VCC

VCC

VSS1VSS

124

110

VCC41VCC90VCC

VCC

VCC

VSS23VSS32VSS85VSS96VSS

VSS43VSS54VSS64VSS68VSS78VSS

12

VCC49VCC59VCC73VCC84VCC

VSS

VSS

107

116

127

138

148

VSS

133

152

VCC

VSS

143

162

VSS

157

168

VCC

DQ16

DQ17

VCC

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

REGE

CKE0

CKE1

/WE0

/CAS

/RAS

NC

NC

NC

NC

NC

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

SA0

SA1

SA2

SDA

SCL

/S0

/S1

/S2

/S3

CK0

CK1

CK2

CK3

55

56

57

58

60

65

66

67

69

70

71

72

74

75

76

77

139

140

141

142

144

149

150

151

153

154

155

156

158

159

160

161

134

135

146

164

62

147

128

63

21

22

52

53

105

106

136

137

165

166

167

82

83

30

114

45

129

27

111

115

42

125

79

163

MD16

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

CKE4

CKE5

MECC0

MECC1

MECC2

MECC3

MECC4

MECC5

MECC6

MECC7

R_SA1

CS_A#4

CS_A#5

CS_B#4

CS_B#5

**NOTE ON ALL DIMM SOCKETS**

Pin 147 should be pulled to a high state

to accommodate registered DIMMs.

VCC3

R254

0 ohm

CKE[5:4] 6

MECC[7:0] 8,9,10

VCC3

R43

4.7K

DCLK0

DCLK1

DCLK2

DCLK3

Slave address = 1010010b

SMBDATA 3,6,9,10,13,28,33

SMBCLK 3,6,9,10,13,28,33

CS_A#[5:4] 6

CS_B#[5:4] 6

WE_B# 6

SCAS_B# 6

SRAS_B# 6

DCLK[11:0] 6,9,10

1 1

A

B

C

D

INTEL CORPORATION

PLATFORM COMPONENTS DIVISION

1900 PRAIRIE CITY RD. FM5-62

FOLSOM, CA 95630

Title

DIMM SOCKET 2

Size Document Number Rev

Custom

Date: Sheet of

Intel(R) 440BX AGPset

11 34Thursday, April 09, 1998

E

1.0

Page 12

A

(

)

y

]

]

]

]

]

]

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

R_ AD18

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

C/BE#0

C/BE#1

C/BE#2

C/BE#3

SDA0

SDA1

SDA2

PDA0

PDA1

PDA2

PDD0

PDD1

PDD2

PDD3

PDD4

PDD5

PDD6

PDD7

PDD8

PDD9

PDD10

PDD11

PDD12

PDD13

PDD14

PDD15

4 4

AD[31:0

7,16,17

3 3

2 2

1 1

R256

100

AD18

7,16,17

C/BE#[3:0

R45

100

7,1 6,17,28

19

19

A

DE VSEL#7, 16,17,28

FRAME#7, 1 6,17,28

IRDY#7,16,17,28

PCIRST#6, 1 5,16,17

PHLD#7,28

PHLDA#7,28

SERR#7,1 6,17,28

STOP#7 , 1 6,17,28

TRDY#7 , 16,17,28

PREQ#[3:0

SDA[2:0

19

PDDACK#19

SDDACK#19

PDREQ19

SDREQ19

PDIOR#19

PDIOW#19

PIORDY19

SDIOR#19

SDIOW#19

SIORDY19

PDA[2:0

PDD[15:0

PAR7 ,16,17

B10

A10

C10

B12

A12

E10

A11

B11

C11

C17

B17

A18

G19

A17

F18

A16

F17

F16

G20

C16

B16

D16

G16

G18

G17

F20

E18

E20

D18

D20

C20

B20

A20

A19

B19

C19

D19

D17

E19

E17

F19

D9

C9

B9

A9

D8

E8

B8

A8

D7

C7

B7

A7

D6

E6

E4

C4

B4

A4

D3

E3

C3

B3

E2

C2

B2

A2

D1

E1

C1

B1

C8

C6

D4

D2

E5

A5

A3

B5

B6

A1

A6

D5

C5

B

U23A

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

C/BE#0

C/BE#1

C/BE#2

C/BE#3

CLOCKRUN#

DE VSEL#

FRAME#

IDSEL

IRDY#

PAR

PCIRST#

PHOLD#

PHOLDA#

SERR#

STOP#

TRDY#

REQ0#

REQ1#

REQ2#

REQ3#

SDA0

SDA1

SDA2

PDDACK#

SDDACK#

PDREQ

SDREQ

PDIOR#

PDIOW#

PIORDY

SDIOR#

SDIOW#

SIORDY

PDA0

PDA1

PDA2

PDD0

PDD1

PDD2

PDD3

PDD4

PDD5

PDD6

PDD7

PDD8

PDD9

PDD10

PDD11

PDD12

PDD13

PDD14

PDD15

PIIX4_15

B

PCI BUS INTERFACE

82371EB

IDE SIGNALS

C

E15

SDD0

B15

SDD1

D14

SDD2

C14

SDD3

A14

SDD4

C13

SDD5

A13

SDD6

C12

SDD7

D12

SDD8

B13

SDD9

D13

SDD10

B14

SDD11

E14

SDD12

A15

SDD13

C15

SDD14

D15

SDD15

IDE SIGNALS

ISA/EIO SIGNALS

MEMCS16#

REFRESH#

ZEROWS#

C

SCS3#

PCS3#

SCS1#

PCS1#

SA0

SA1

SA2

SA3

SA4

SA5

SA6

SA7

SA8

SA9

SA10

SA11

SA12

SA13

SA14

SA15

SA16

SA17

SA18

SA19

SD0

SD1

SD2

SD3

SD4

SD5

SD6

SD7

SD8

SD9

SD10

SD11

SD12

SD13

SD14

SD15

LA17

LA18

LA19

LA20

LA21

LA22

LA23

MEMR#

MEMW#

SMEMR#

SMEMW#

SYSCLK

BALE

IOCHK#

IOCS16#

SBHE#

RSTDRV

IOR#

IOW#

IOCHRDY

AEN

C18

H16

B18

H17

U11

T11

W11

Y11

T10

W10

U9

V9

Y9

T8

W8

U7

V7

Y7

V6

Y6

T5

W5

U4

V4

V3

W3

U2

T2

W2

Y2

T1

V1

W16

T16

Y17

V17

Y18

W18

Y19

W19

Y15

T14

W14

U13

V13

Y13

T12

Y12

V15

U15

W4

U3

T7

U10

Y1

W7

V12

Y3

W12

W1

Y5

T4

T3

Y4

SA0

SA1

SA2

SA3

SA4

SA5

SA6

SA7

SA8

SA9

SA10

SA11

SA12

SA13

SA14

SA15

SA16

SA17

SA18

SA19

SD0

SD1

SD2

SD3

SD4

SD5

SD6

SD7

SD8

SD9

SD10

SD11

SD12

SD13

SD14

SD15

LA17

LA18

LA19

LA20

LA21

LA22

LA23

D

SDD0

SDD1

SDD2

SDD3

SDD4

SDD5

SDD6

SDD7

SDD8

SDD9

SDD10

SDD11

SDD12

SDD13

SDD14

SDD15

SA[19:0]14, 18,21,29,33

SD[15:0]14 ,18,29

LA[23:17]18,29

MEMCS16# 18,29

MEMR# 18,21,29

MEMW# 18,21,29

SMEMR# 18

SMEMW# 18

SY S CLK 18,33

BALE 18

IOCHK# 18,29

REFRESH# 18,29

IOCS16# 18,29

ZEROWS# 18,29

SBHE# 18

RSTDRV 14,26

IOR# 14 , 18,29,33

IOW# 1 4 ,18,29,33

IOCHRDY 14,18,29

AEN 14,18

INTEL CORPORATION

PLATFORM COMPONENTS DIVISION

1900 PRAIRIE CITY RD. FM5-62

FOLSOM, CA 95630

Title

Size Document Number Rev

Custom

Date: Sheet of

D

82371EB

PART I

, April 09, 1998

SDD[15:0]19

SCS3# 19

PCS3# 19

SCS1# 19

PCS1# 19

Intel(R) 440BX AGPset 1.0

E

12 34Thursda

E

Page 13

A

B

3VSB

VCC3

VCC3

VCC3

C

D

E

DACK#[3:0]14,18

4 4

3 3

2 2

R48

VB2

1K

D3

SCHOTTKY

BAR43

VB1

12

1 1

BT1

DACK#[7:5]18

APICREQ#28

GPI728

PIRQ#A15,16,17,28

PIRQ#B15,16,17,28

PIRQ#C16,17,28

PIRQ#D16,17,28

3VSB

D2

SCHOTTKY

BAR43

C6

0.1 uF

R49

CLEAR CMOS

JP6 CONFIG

DRQ014,18,29

DRQ114,18,29

DRQ214,18,29

DRQ314,18,29

DRQ518,29

DRQ618,29

DRQ718,29

REQ#A28

REQ#B28

REQ#C28

TC14,18

IRQ114,29

IRQ314,18,29

IRQ414,18,29

IRQ514,18,29

IRQ614,18,29

IRQ714,18,29

IRQ#829

IRQ914,18,29

IRQ1014,18,29

IRQ1114,18,29

IRQ1214,18,29

IRQ1414,18,19,29

IRQ1514,18,19,29

FERR#3,28

PX4_IGNNE#25,28

HINIT#3,28

PX4_INTR25,28

A20GATE14,28

PX4_NMI25,28

PX4_SMI#3,28

KBRST#14,28

PX4_A20M#25,28

PWROK7,26

SPKR26

TEST#28

1

3

CMOS_CLR

1K

JP6

XOE#14

XDIR#14

BIOSCS#21

2

R244

0

Y2

32.768KHz

C7

18pF

PIRQ#A

PIRQ#B

PIRQ#C

PIRQ#D

RTC_BAT

12

C8

18pF

DACK#0

DACK#1

DACK#2

DACK#3

DACK#5

DACK#6

DACK#7

48Mhz_05

OSC25

PXPCLK5

RTCX2

RTCX1

U23B

U14

DACK0#

W6

DACK1#

Y10

DACK2#

V5

DACK3#

T15

DACK5#

V16

DACK6#

W17

DACK7#

W15

DREQ0

U6

DREQ1

V2

DREQ2

U5

DREQ3

Y16

DREQ5

U16

DREQ6

U17

DREQ7

M1

REQA#/GPI2

N2

REQB#/GPI3

P3

REQC#/GPI4

N1

GNTA#/GPO9

P2

GNTB#/GPO10

P4

GNTC#/GPO11

V10

TC

J17

APICACK#/GPO12

H18

APICCS#/GPO13

K18

APICREQ#/GPI5

H20

IRQ0/GPO14

J20

IRQ1

T9

IRQ3

W9

IRQ4

U8

IRQ5

V8

IRQ6

Y8

IRQ7

Y20

IRQ8/GPI6

U1

IRQ9

U12

IRQ10

W13

IRQ11

T13

IRQ12

V14

IRQ14

Y14

IRQ15

J19

SERIRQ/GPI7

R3

PIRQA#

R4

PIRQB#

P5

PIRQC#

G1

PIRQD#

M19

CPURST

K19

FERR#

L17

IGNNE#

L18

INIT

L19

INTR

P1

A20GATE

L20

NMI

P20

SMI#

N20

RCIN#

M20

A20M#

M18

PWROK

K17

SPKR

V18

TEST#

M4

XOE#/GPO23

M3

XDIR#/GPO22

M2

BIOSCS#

L1

RTCALE/GPO25

K2

RTCCS#/GPO24

K1

KBCCS#/GPO26

L16

VBAT

R20

RTCX2

N19

RTCX1

L3

48Mhz

V11

OSC

D11

PCICLK

PIIX4_15

DMA SIGNALS

IRQ SIGNALS

CPU INTERFACE

X-BUS

VSS

VSSE7VSS

VSSJ9VSS

E13

D10

E12

E11

F15

VCC

VCC

R15

VCCR6VCC

E16

VCCPE9VCCP

F6

VCC

82371EB

VSS

VSS

VSSK9VSS

VSS

VSS

VSSL9VSS

J10

J11

J12

L10

K10

K11

K12

VCCP

VCCPF5VCCP

VSS

L11

1 -2 NORMAL

2 - 3 CLEAR CMOS

A

B

F14

VCCPG6VCCPR7VCCP

VSS

VSSM9VSS

L12

M10

P15

M11

T6

VSS

M12

VCCP

VSS

J5

R16

N16

K5

VCCSUS

VCCSUS

VCCUSB

VSS_USB

USBP1+

USBP1-

USBP0+

USBP0-

USB

EXTSMI#

SUSA#

GPO15/SUSB#

GPO16/SUSC#

GPO17/CPU_STP#

GPO18/PCI_STP#

GPO19/ZZ

GPI8/THERM#

GPI9/BATLOW#

RSMRST#

PWRBT#

GPI10/LID

SMBDATA

SMBCLK

GPI11/SMBALERT#

GPI12/RI#A

POWER MANAGEMENT

SUSCLK

GPO20/SUS_STAT1#

GPO21/SUS_STAT2#

STPCLK#

SLP#

VREF

GPI1

GPI13

GPI14

GPI15

GPI16

GPI17

GPI18

GPI19

GPI20

GPI21

GPO0

GPO8

GPO27

GPO28

GPO29

GPO /GPI/GPIO/SCAN

GPO30

MCCS#

PGCS0#

PGCS1#

CONFIG1

CONFIG2

C

OC0

OC1

N/C

N/C

N/C

N/C

N/C

N/C

F1

H2

G2

H3

J1

J2

V20

W20

V19

U18

R1

R2

K16

H19

U19

M17

U20

P16

T20

R19

N17

P18

P17

T17

T18

J18

K20

J16

P19

L2

J3

L5

K3

K4

H1

H4

H5

G3

G4

T19

G5

F2

F3

F4

N4

L4

N5

J4

N18

N3

M5

M16

R5

R17

R18

GPI13

GPI14

GPI15

GPI16

GPI17

GPI18

GPI19

GPI20

GPI21

GPO8

GPO27

GPO28

PGCS#0

PGCS#1

SUSC#

PS_POK26

PX4_CFG1 28

R47

8.2K

USBP1+ 20

USBP1- 20

USBP0+ 20

USBP0- 20

OC#0 20

OC#1 20

EXTSMI# 28,33

SUSA# 5

CPU_STP# 5

PCI_STP# 5

THERM# 3,28

BATLOW# 28

RSMRST# 26

PWRBT# 26

LID 26,28

SMBDATA 3,6,9,10,11,28,33

SMBCLK 3,6,9,10,11,28,33

SMBALERT# 28

AGP_PME# 15,28

SUSTAT# 7

STPCLK# 3,28

SLP# 3

PCI_PME# 16,17,28

GPI[20:13] 28

GPI21 23

FAN_LED 26

1

TP3

1

TP4

1

TP5

PGCS#1 28,33

R268

1K

R269

1.5K

3VSB

14

U5F

13 12

7

74LVC14

+

5VSB

SUSC#

C3

0.01 uF

C4

1.0 uF

RTC_BAT

GPO8#

D

3VSB

14

U5A

1 2

7

74LVC14

VCC3

D1

SCHOTTKY

BAR43

C5

0.1 uF

5VSB

U17B

14

3

4

5

7

74HC10

C165

0.1uF

5VSB

5VSB

U28A

14

1 2

7

74F07

**External logic shown

is used to handle

power loss condition.

VCC

R46

1K

5VSB

SP3

R243

6

SPS2

R291

8.2K

4

16

VCC

3

J

PR

1

CLK

2

K

CL

8

GND

15

R245

8.2K

10K

R267

10K

U27A

5

Q

6

Q

74HC112

JK_CLR

RTC_BAT

INTEL CORPORATION

PL A TFORM COMPONENTS DIVISION

1900 PRAIRIE CITY RD. FM5-62

FOLSOM, CA 95630

Title

82371EB (PART II)

Size Document Number Rev

Custom

Date: Sheet of

R290

10K

3

1

VREF5V 7

1

3

3

1

16

11

13

12

8

RSMRST#

Intel(R) 440BX AGPset 1.0

JP21

JMP_3P

Q8

2N7002

Q6

VCC

J

CLK

K

GND

1-2

2-3

2

2

2N7002

2

10

PR

CL

74HC112

14

E

U27B

Q

Q

JP21 CONFIG.

SAVE STATE ON

POWER DOWN.

PIIX4 POWERS ON SYS.

AT POWER-UP.

B_SUSC 26

WOLLID 26

POWER-ON 26

9

10K

7

R292

2

13 34Thursday, April 09, 1998

5VSB

3

1

Q5

2N7002

Page 14

1

)

y

(R)

(

)

y

]

]

]

]

]

]

A A

13 ,18,29

13,18

VCC

13 ,18,29

R258

B B

12, 18,21,29,33

SA[19:0

10k

VCC

R53

8.2K

C C

VCC

1 8

2 7

3 6

4 5

KBCLK#24

KB DAT#24

MSCLK#24

MSDAT#24

XD[7:0

21,33

XOE#13

D D

XD IR#13

1

DRQ[7:0

DACK#[3:0

IRQ[7:0

IRQ913,18,29

IRQ1013,18,29

IRQ1113,18,29

IRQ1213,18,29

IRQ1413,18,19,29

IRQ1513,18,19,29

RP1

4.7K

2

12,18,29

TC13,18

Stuff for 93XFR

2

OSC35

IOR#1 2 ,18,29,33

IOW#12,18,29,33

RSTDRV12,26

IOCHRDY12,18,29

SD[15:0

3

AEN12,18

SD0

SD1

SD2

SD3

SD4

SD5

SD6

SD7

DRQ0

DRQ1

DRQ2 TP090

DRQ3

DACK#0

DACK#1

DACK#2

DACK#3

IRQ1

IRQ3

IRQ4

IRQ5

IRQ6

IRQ7

IRQ9

IRQ10

IRQ11

IRQ12

IRQ14

IRQ15

SA0

SA1

SA2

SA3

SA4

SA5

SA6

SA7

SA8

SA9

SA10

SA11

SA12

SA13

SA14

SA15

SIO _PU2

1

VCC

R288

0

TP11

TP12

TP13

TP15

TP17

TP18

TP20

TP22

TP080

1

TP081

1

TP082 TP092

1

TP083 TP091

1

TP084

1

TP079 TP073

1

TP078 TP072

1

TP085 TP087

XD0

XD1

XD2

XD3

XD4

XD5

XD6

XD7

Stuff for 93XFR

3

R289

0

4

U6

121

VBAT

122

XTAL1

124

XTAL2

22

14C LOCKI

68

IOR#

69

IOW#

70

AEN

80

RSTDRV

90

IOCHRDY

72

SD0

73

SD1

74

SD2

75

SD3

76

SD4

77

SD5

78

SD6

79

SD7

89

TC

82

DRQ0

84

DRQ1

86

DRQ2

88

DRQ3

81

DACK0

83

DACK1

85

DACK2

87

DACK3

67

IRQ1

66

IRQ3

65

IRQ4

64

IRQ5

63

IRQ6

62

IRQ7

61

IRQ8#

59

IRQ9

58

IRQ10

57

IRQ11

56

IRQ12

55

IRQ14

54

IRQ15

41

SA0

42

SA1

43

SA2

44

SA3

45

SA4

46

SA5

47

SA6

48

SA7

49

SA8

50

SA9

51

SA10

52

SA11

53

SA1 2/CS

27

SA13/HDCS2#

28

SA14/HDCS3#

29

SA15/IDE2_IRQ

26

IDE1_IRQ

23

IDE1_OE#

24

HDCS0#

25

HDCS1#

30

IOROP#

31

IOWOP#

34

IDE_A0

33

IDE_A1

32

IDE_A2

92

KCLK

91

KDAT

94

MSCLK

93

MSDAT

111

RD0

112

RD1

113

RD2

114

RD3

115

RD4

116

RD5

117

RD6

118

RD7

119

ROMCS#

120

RO M DIR#

FDC37C932FR_1.3

4

101

125

139

VCC21VCC60VCC

VCC

FDC37C932FR

160 PIN QFP

1

ULTRA I/O

5

VCC

DSKCHG#

DRVSEL0#

DRVSEL1#

DRVDEN0

DRVDEN1

GP10/IRQIN

GP11/IRQIN

GP12/IRRX

GP13/IRTX

GP15/WS

GP16/JOYRS

GP17/JSWS

GP20/IDE2_OE

GP21/EEDIN

GP22/EDOUT

GP23/EECLK

GP24/EEEN

GP25/8042_P21

VSS

VSS95VSS71VSS40VSS8VSS

130

123