5

D D

4

3

2

1

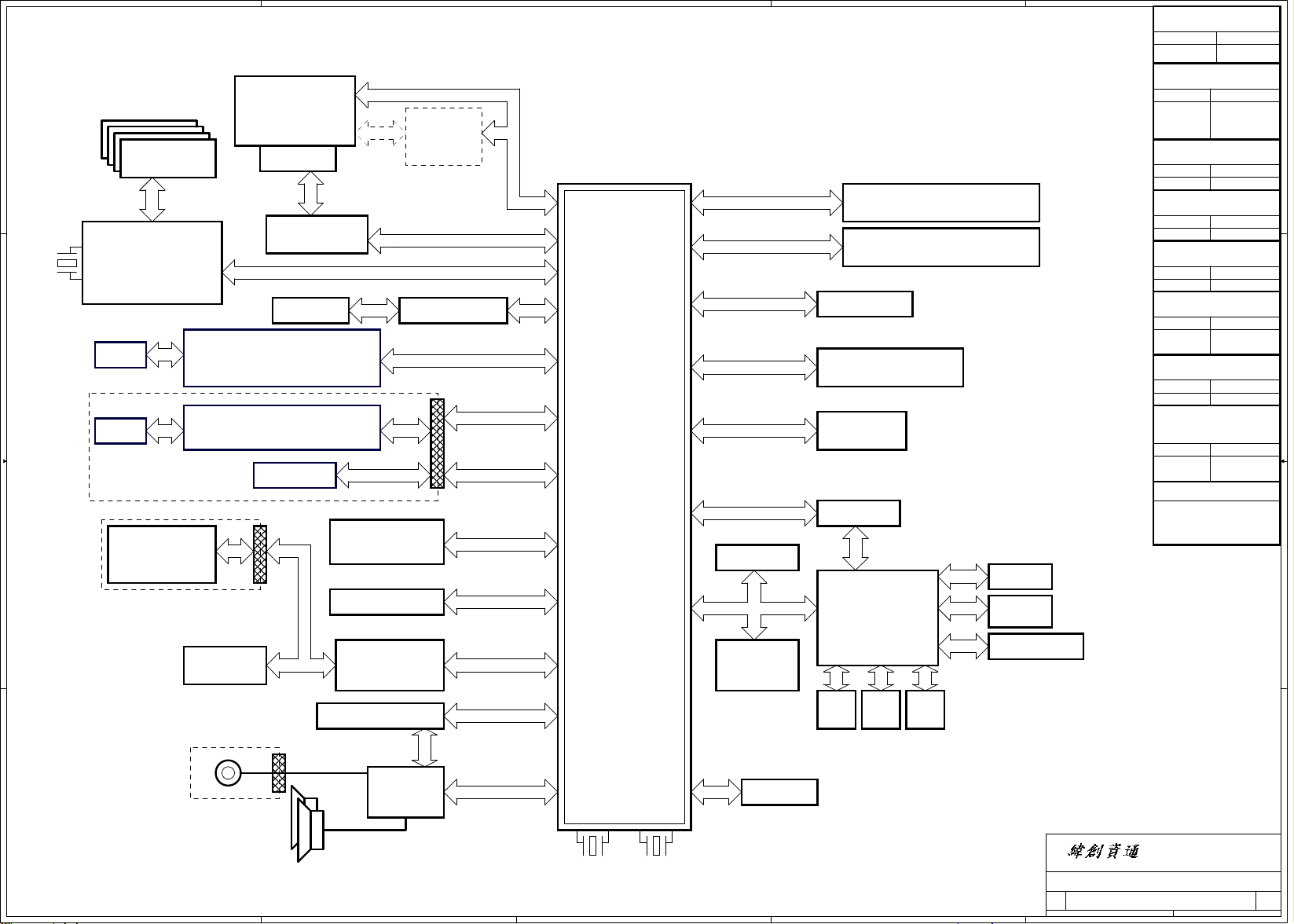

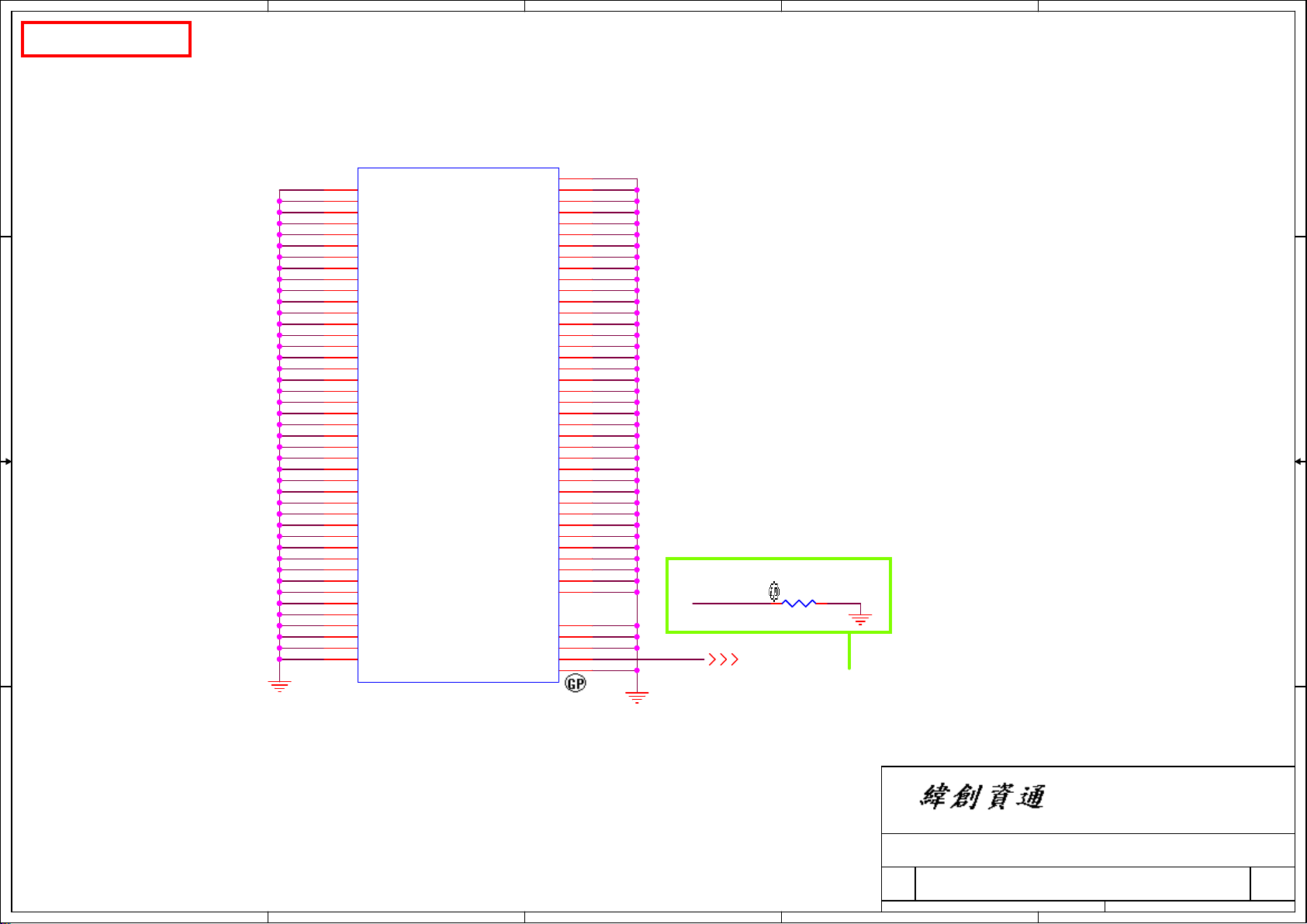

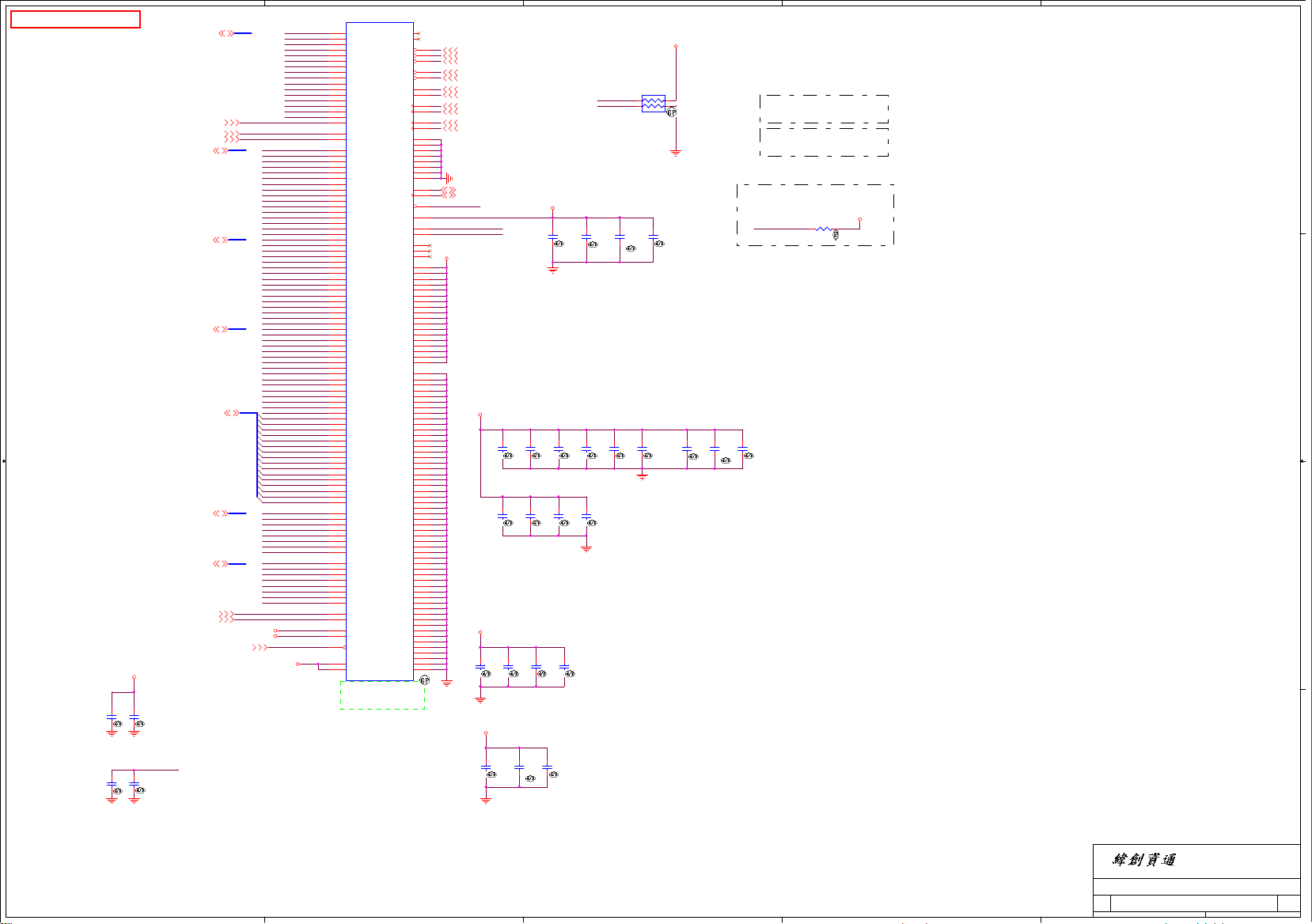

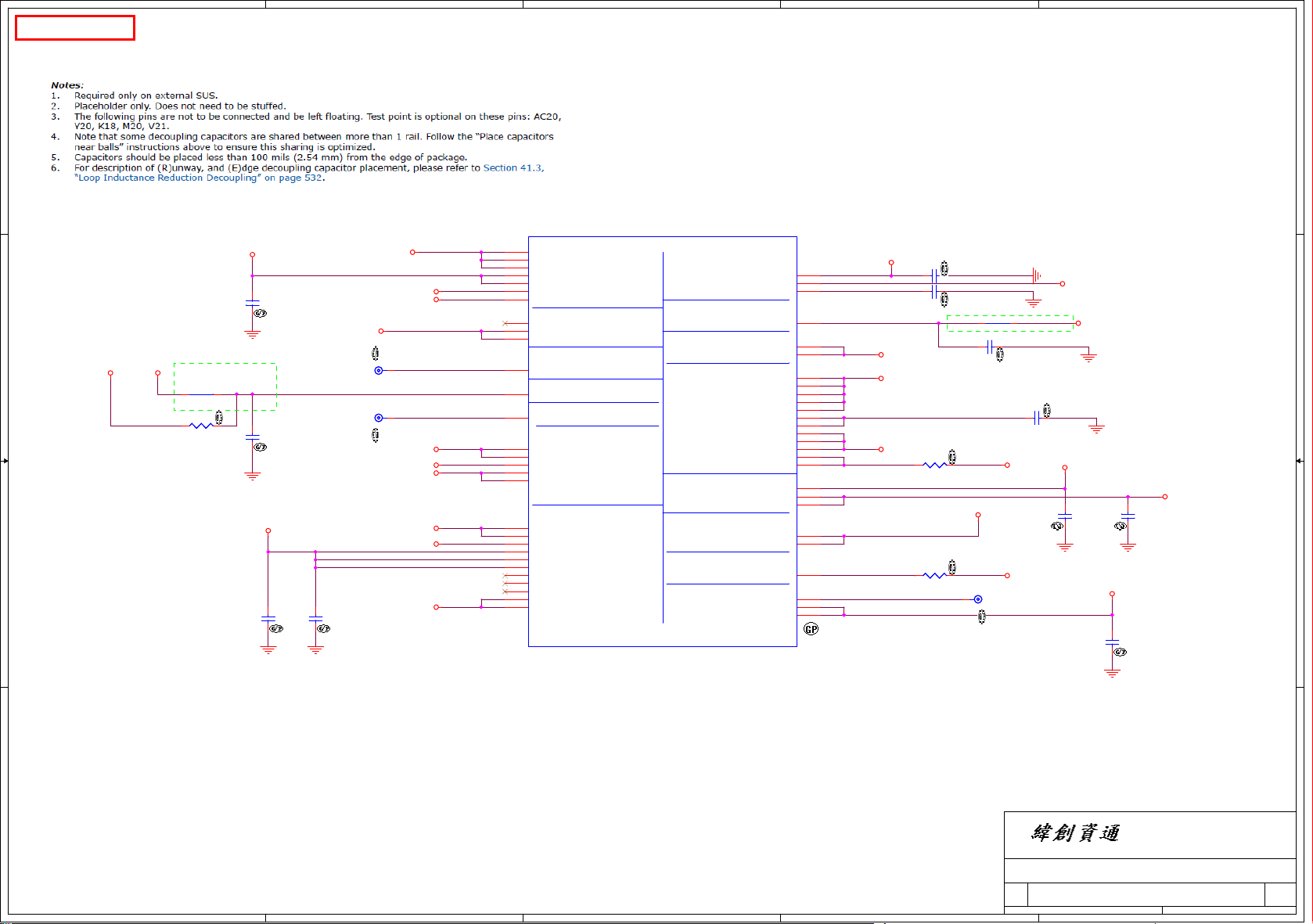

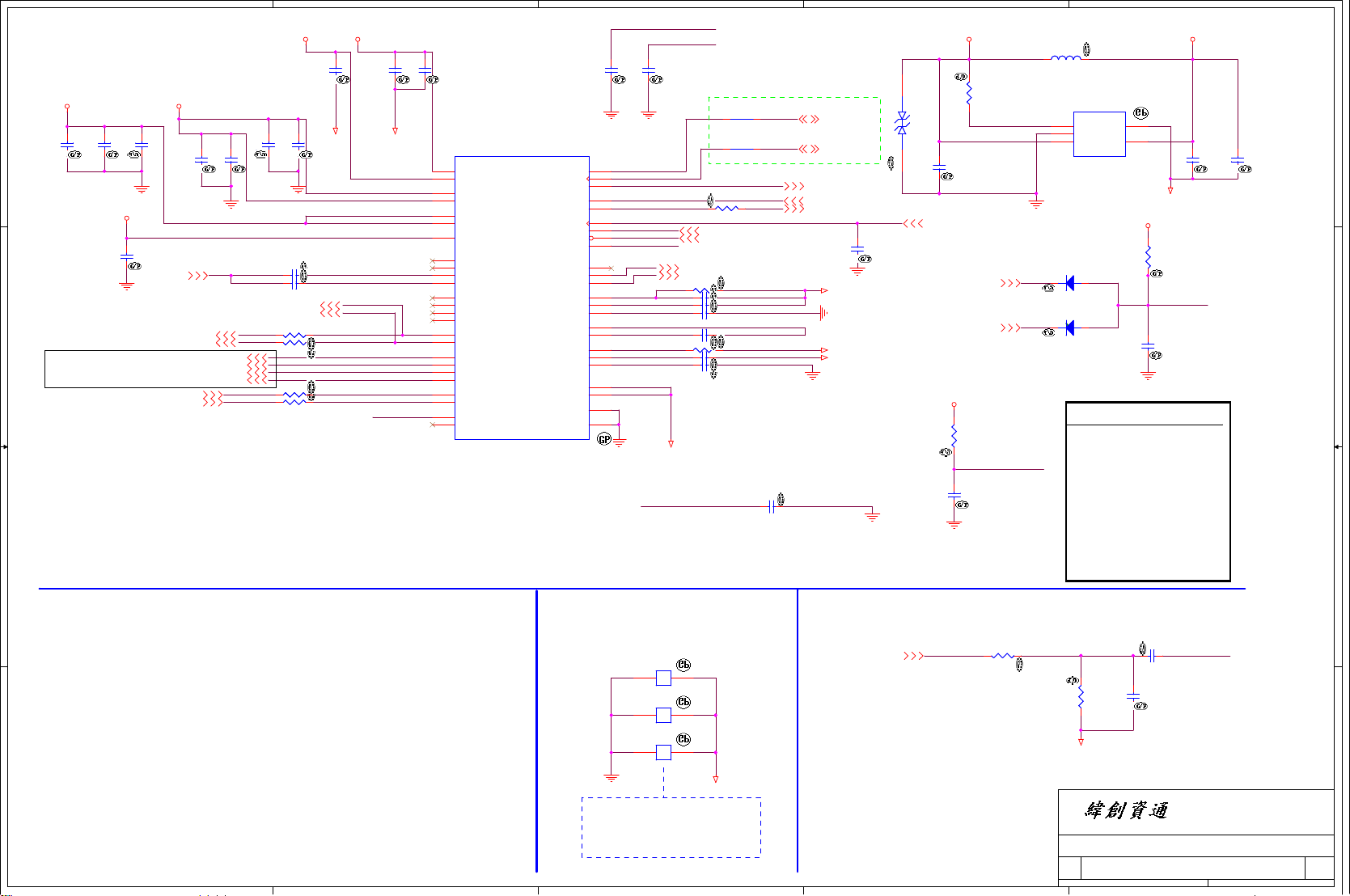

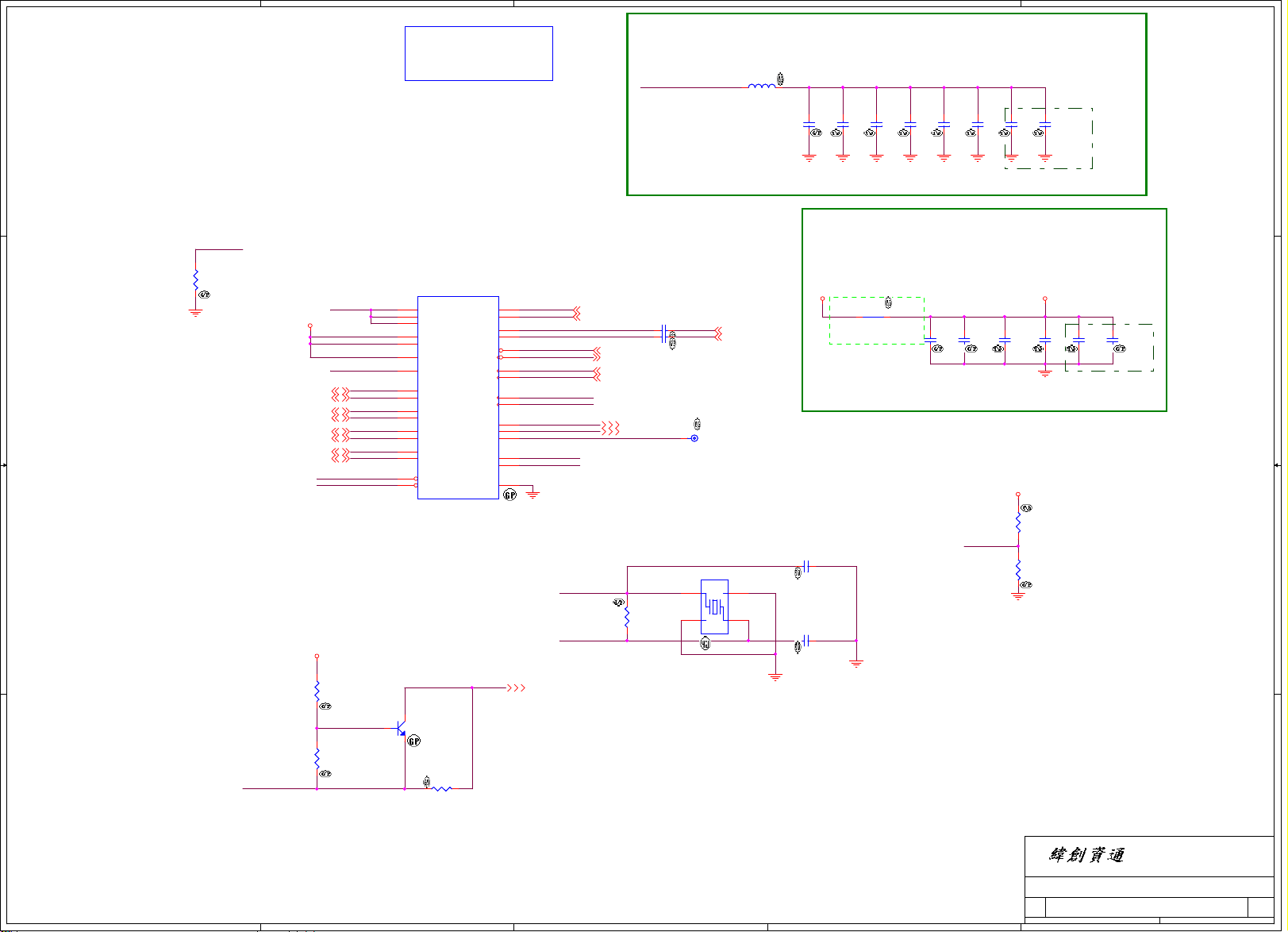

Laduree 15.6" Intel Crescent Bay

UMA/DIS Co-lay Schematic

C C

Broadwell-U 15W TDP

nVidia N16S-GM 16W

REV:1

B B

2015-02-13

Wistron Confidential document, Anyone can not

Duplicate, Modify, Forward or any other purpose

application without get Wistron permission

UMA

UMA

UMA

Wistron Corporation

Wistron Corporation

A A

Title

Title

Title

Cover Page

Cover Page

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A4

A4

A4

Friday, February 13, 2015

Friday, February 13, 2015

Friday, February 13, 2015

Date: Sheet of

Date: Sheet of

5

4

3

Date: Sheet of

2

Cover Page

Laduree-BDW 15.6"

Laduree-BDW 15.6"

Laduree-BDW 15.6"

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

1

1

1 102

1 102

1 102

1

1

5

Vinafix.com

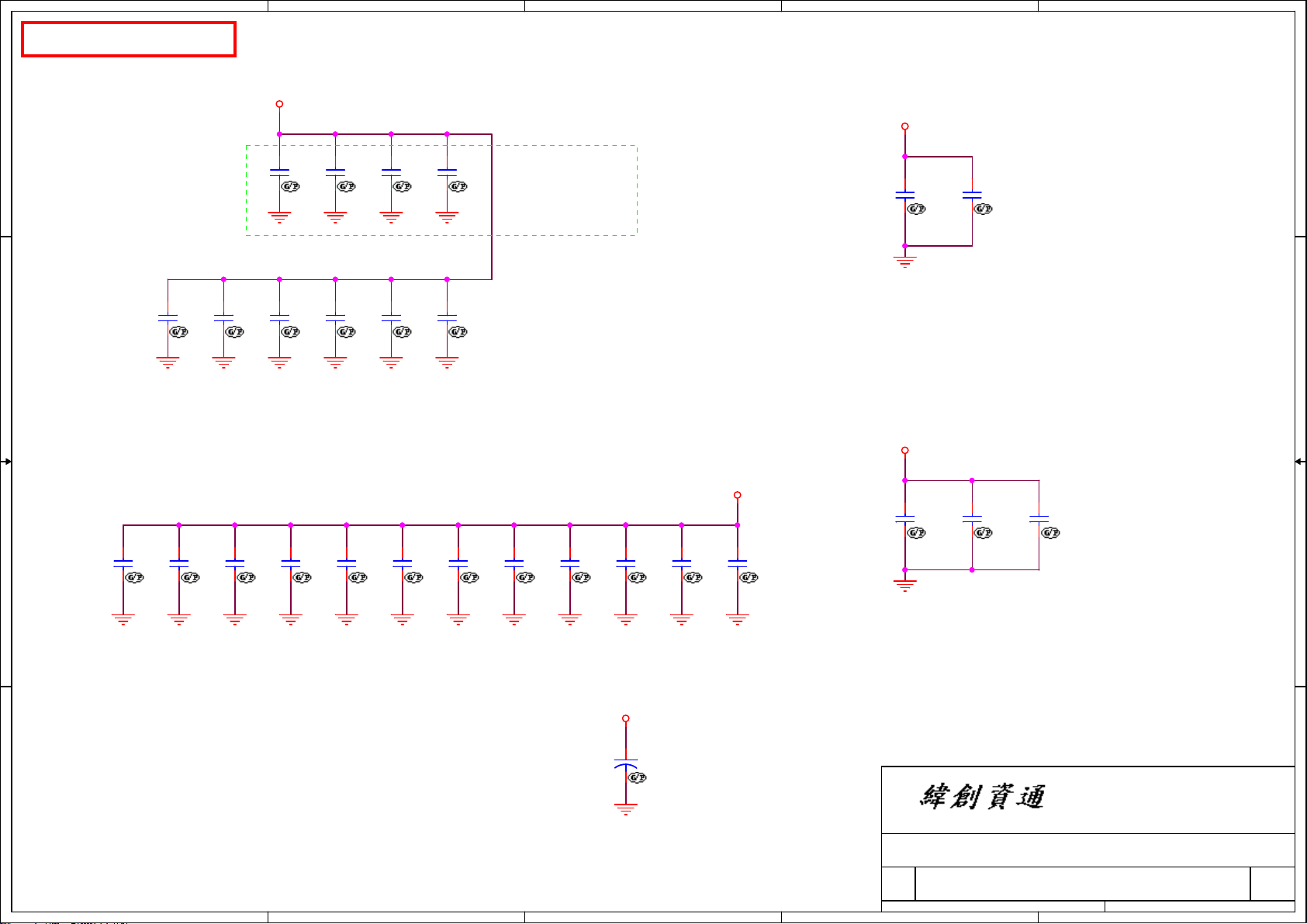

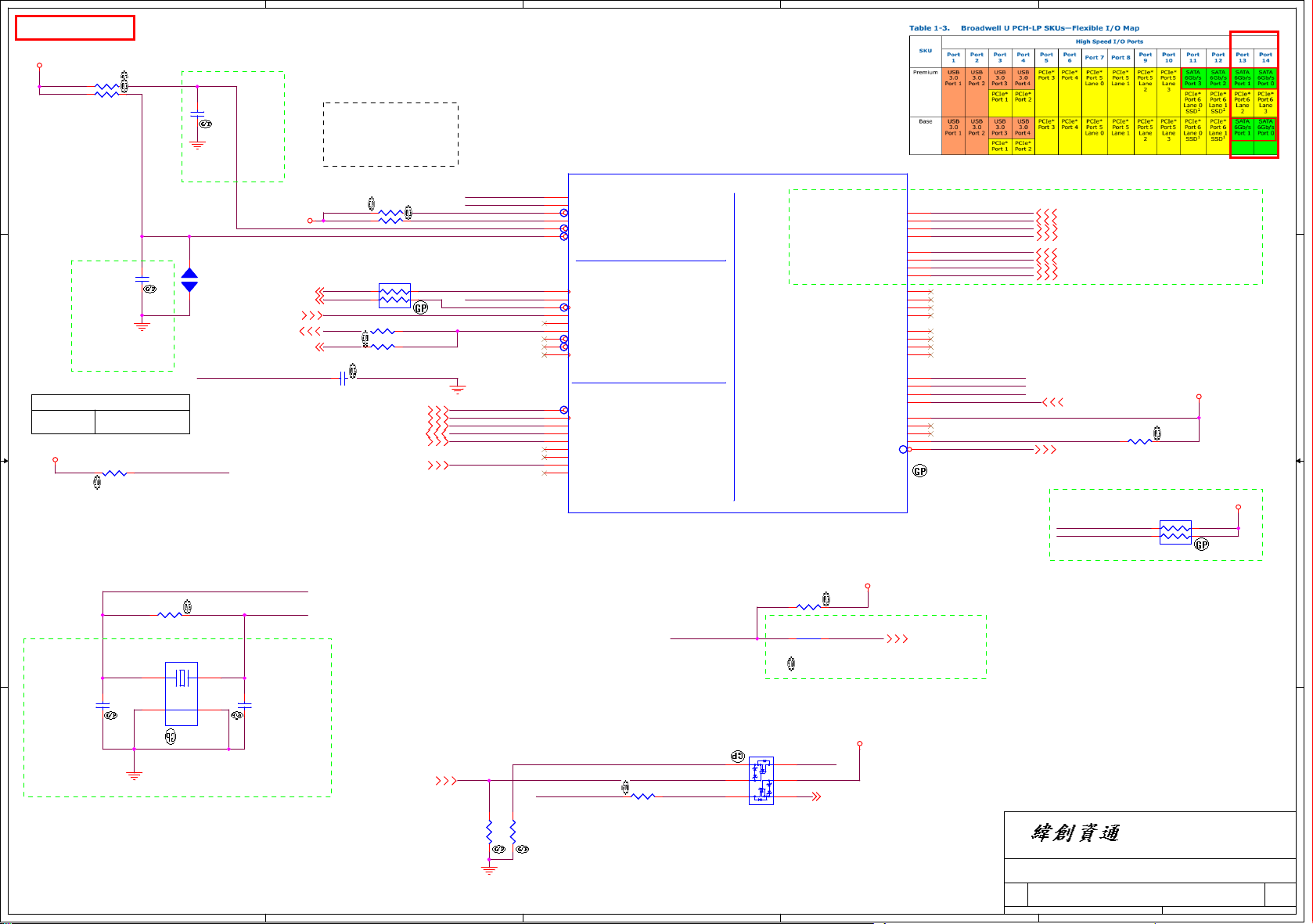

Laduree 15.6" Block Diagram

LCD

1366x768(LVDS HD)

D D

VRAM*4

128M*16/256M*16

78,79,80,81

DDR3L/1.35V

900MHz

nVidia

27MHz

N16S-GM-S 930M

(15.6" DIS only)

23x23mm

C C

RJ45

CONN

16W

73,74,75,76,77

Lan Controller

31

Realtek

RTL8111HSH-CG (10/100/1000)

IO Board

SD Card

Slot

33

CardReader

Realtek

RTS5237S-GR

Sensor Board (On LCD side)

Touch Control Board

Accelerometer+

e-Compass+

B B

Gyro

HP9DS1

Accelerometer

ST

IO Board

1920x1080(eDP FHD)

4

PCIE x 4 lanes

USB2.0 CONN

67

HP3DC2

Touch CONN.

Touch Control Board

Synaptics

S7501

HDMI 1.4a

54

USB3.0 Ext.Port0

w/ USB Charger

TPS2546

52

USB3.0 Ext.Port1

I2C

Camera module + DMIC

63

4

eDPx1/2/4

eDP to LVDS

LVDS

52

52

HDMI

Parade

PS8625QFN

HDMI Redriver

Parade

30

PCIe

32

USB2.0 USB2.0

34

35

Sensor Hub

ST

STM32F102CBT6

66

52

I2C

PCIe (15" only)

PS8407A

PCIe

63

DMIC

55

54

PCIe

USB2.0 & USB3.0

USB2.0 & USB3.0

USB2.0

USB2.0

DP

Intel CPU

Broadwell-U

BGA1168

15W

8 USB 2.0/1.1 ports

6 USB 3.0 ports

High Definition Audio

4 SATA ports

8 PCIE ports

LPC I/F

ACPI 4.0a

3,4,5,6,7,8,9,10

11,15,16,17,18,19,20

3

DDR3L 1333/1600 Channel A

DDR3L / 1.35V

DDR3L 1333/1600 Channel B

PCIe / USB2.0

SATA/ PCIe

DDR3L-1600

SO-DIMM1

DDR3L-1600

SO-DIMM2

NGFF

WLAN + BT

NGFF

SSD

2

Project code : 4PD048010001

PCB P/N : 14257

Revision : SA

12

13

58

60

1

CHARGER

HPA02224RGRR

OUTPUTSINPUTS

AD+

BT+ DCBATOUT

SYSTEM DC/DC

TPS51225RUKR-GP

INPUTS OUTPUTS

DCBATOUT

5V_AUX_S5

3D3V_AUX_S5

5V_S5

3D3V_S5

CPU DC/DC

TPS51624RSMR

INPUTS

DCBATOUT

OUTPUTS

CPU_CORE

SYSTEM DC/DC

RT8068AZQWID

DCBATOUT 1D5V_S0

OUTPUTSINPUTS

SYSTEM DC/DC

SY8208DQNC

INPUTS

DCBATOUT

OUTPUTS

1D05V_LAN

SYSTEM DC/DC

TPS51716RUKR

INPUTS

DCBATOUT

OUTPUTS

1D35V_PWR

VGA

RT8179CGQW

DCBATOUT

OUTPUTSINPUTS

VGA_CORE

44

45

46,47

51

48

49

80,81

VGA

SATA

2.5" HDD/ SSHD

56

RT8068AZQWID

SY8208DQNC

INPUTS OUTPUTS

3D3V_S5

DCBATOUT 0D95V

1D8V

82

PCB LAYER

SPI

LPC debug port

LPC BUS

TPM 2.0

Infineon

SLB9665TT2.0

SPI Flash

8MB

25

65

88

SPI

KBC

ene

KB9028Q

Touch

PAD

62 62

Int.

KB

24

Int.

BATT

Fan Control

PWM

SMBus

I2C

43

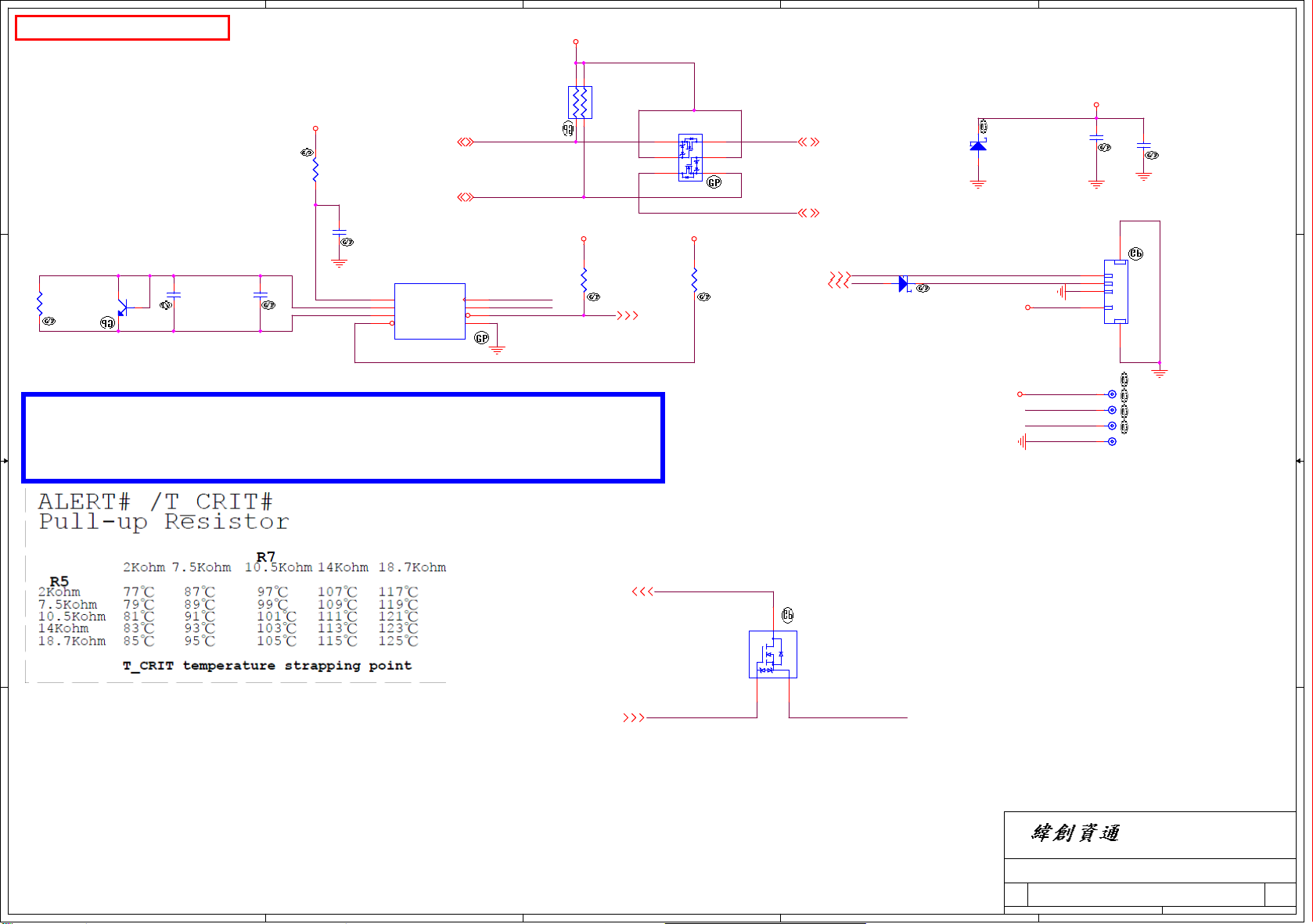

Thermal

NCT7718W

Accelerometer

HP3DC2

ST

26

26

67

L1:

L2:

L3:

L4:

TOP

GND

Signal

Signal

L5:

L6:

GND/PWR

BOTTOM

A A

Combo Jack

Realtek

ALC3227-CG

27

Speaker

29

Audio Codec

5

4

HDA BUS

32.768KHz 24MHz

3

CPU_XDP

96

2

Wistron Confidential document, Anyone can not

Duplicate, Modify, Forward or any other purpose

application without get Wistron permission

UMA

UMA

UMA

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Friday, January 30, 2015

Friday, January 30, 2015

Friday, January 30, 2015

Date: Sheet of

Date: Sheet of

Date: Sheet of

Taipei Hsien 221, Taiwan, R.O.C.

Block Diagram

Block Diagram

Block Diagram

Laduree-BDW 15.6"

Laduree-BDW 15.6"

Laduree-BDW 15.6"

1

2 102

2 102

2 102

1

1

1

D

C

B

A

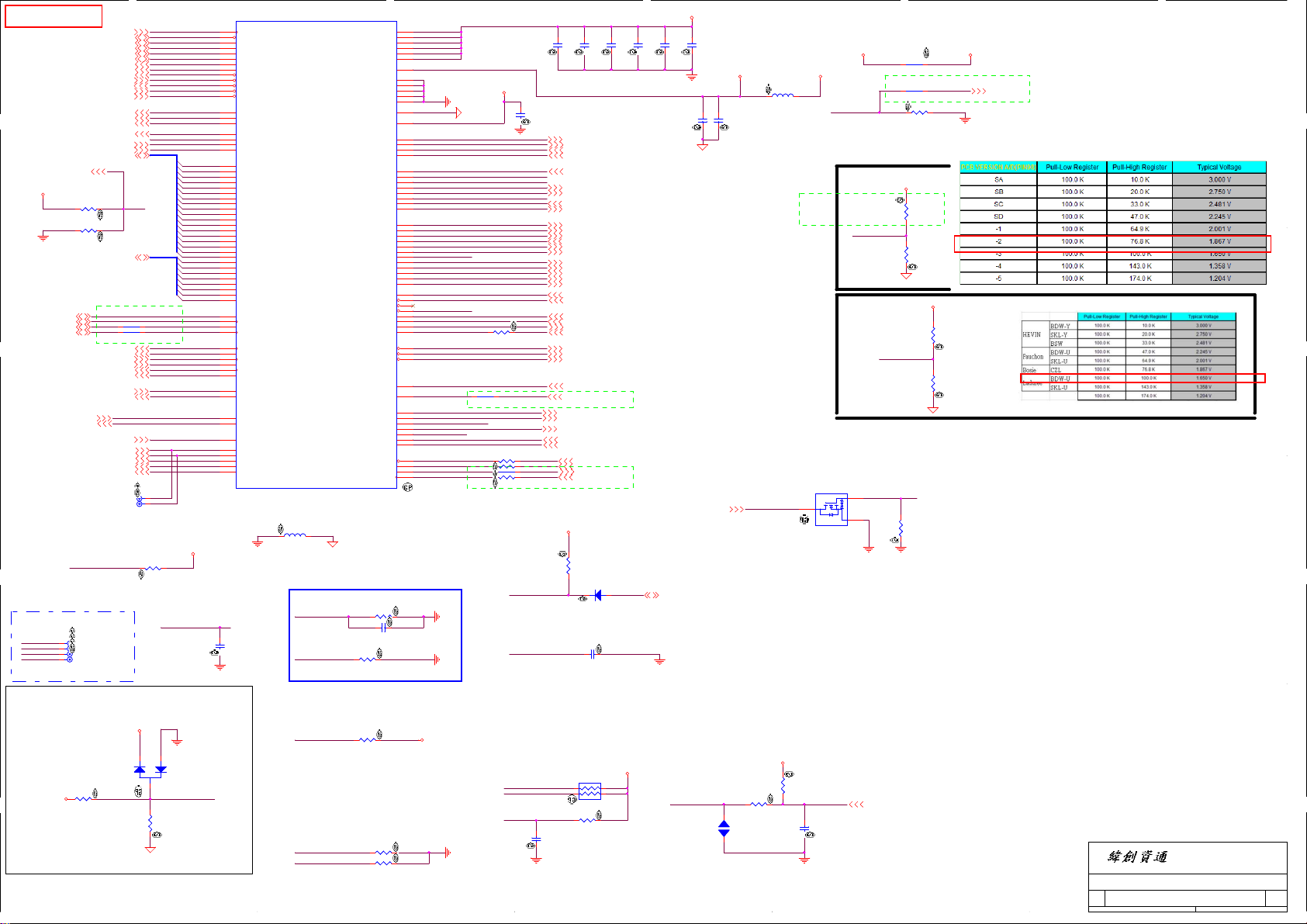

SSID = CPU

D

C

5

4

3

2

1

B

Wistron Confidential document, Anyone can not

Duplicate, Modify, Forward or any other purpose

application without get Wistron permission

UMA

UMA

UMA

Wistron Corporation

Wistron Corporation

A

Title

Title

Title

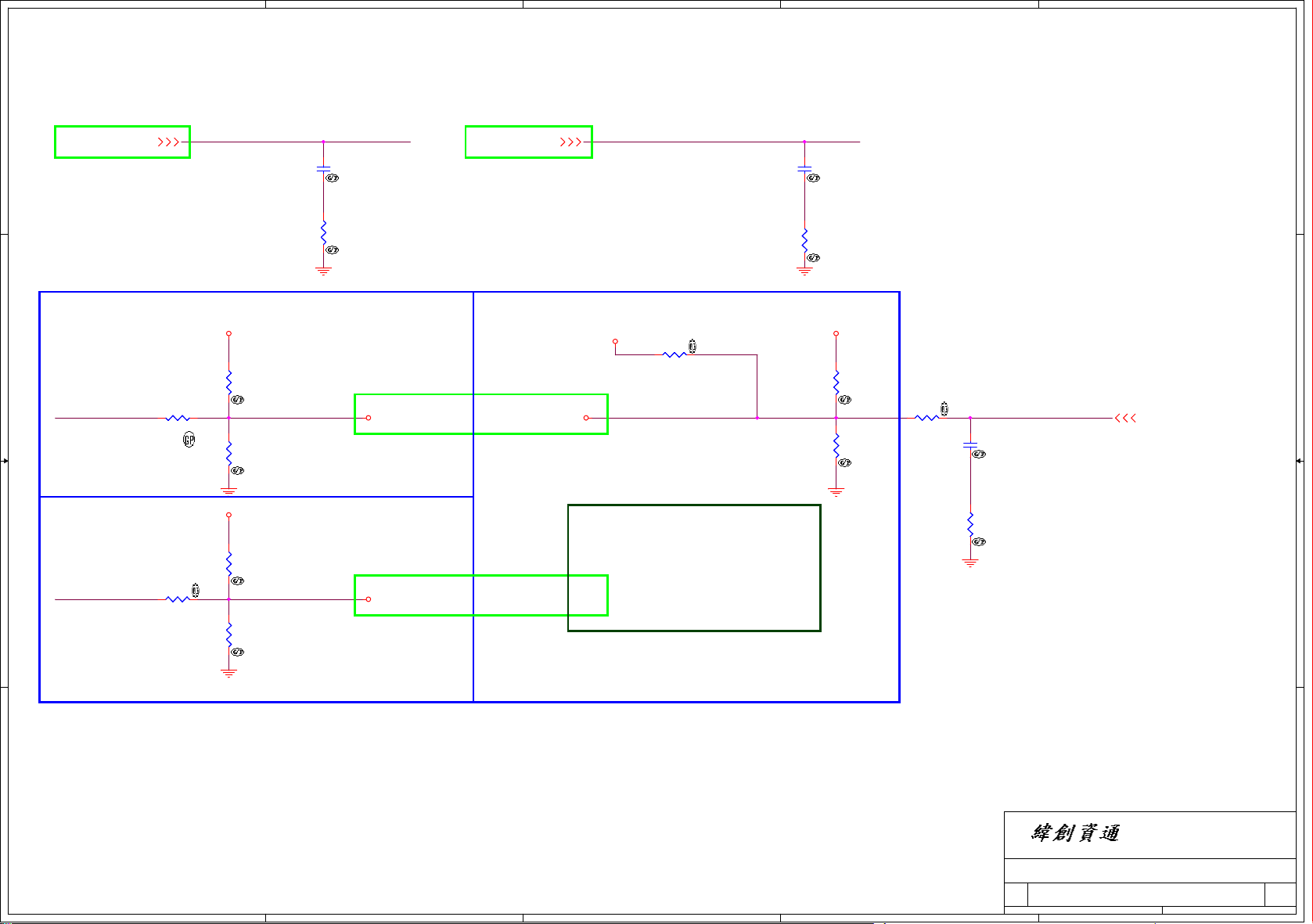

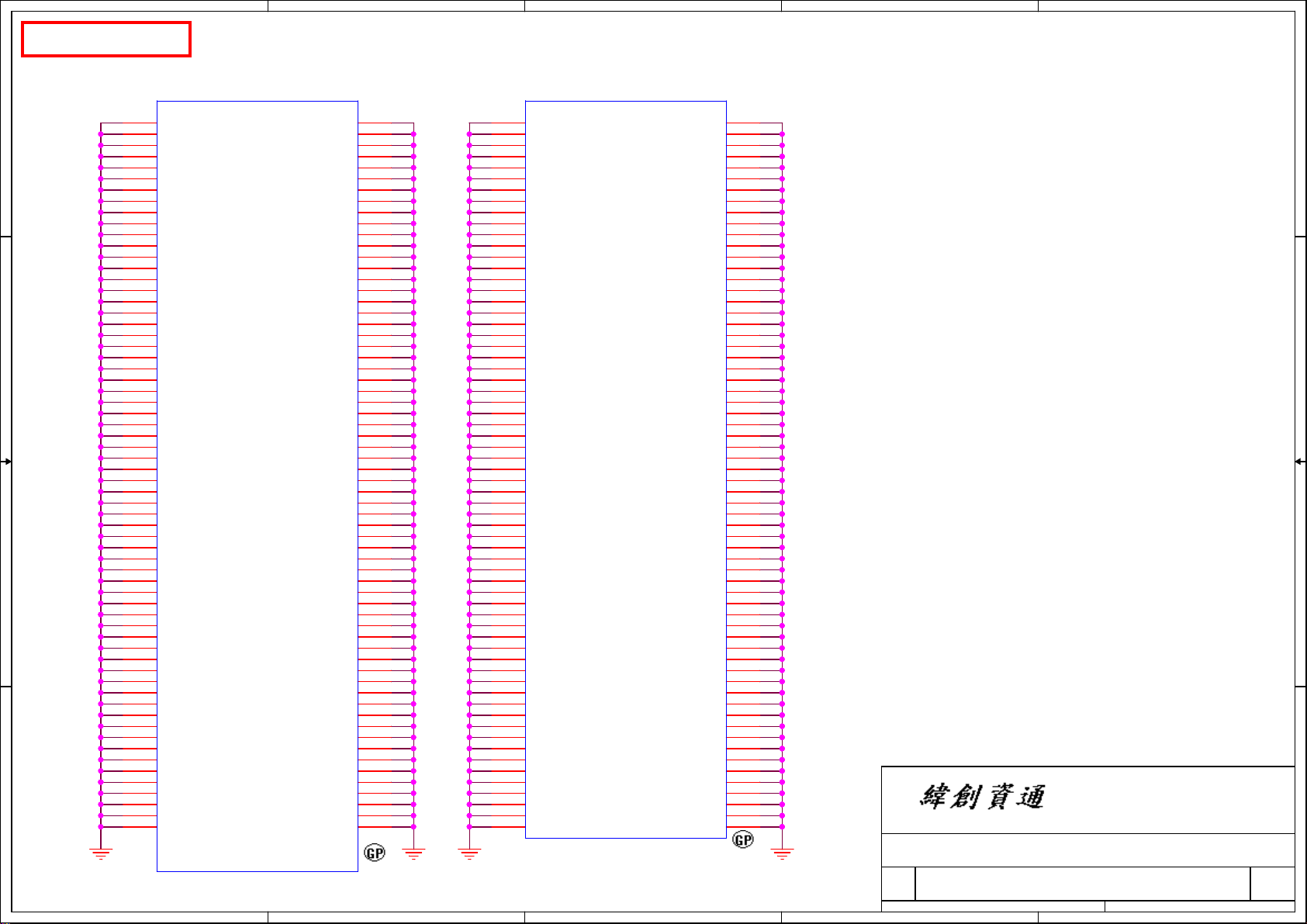

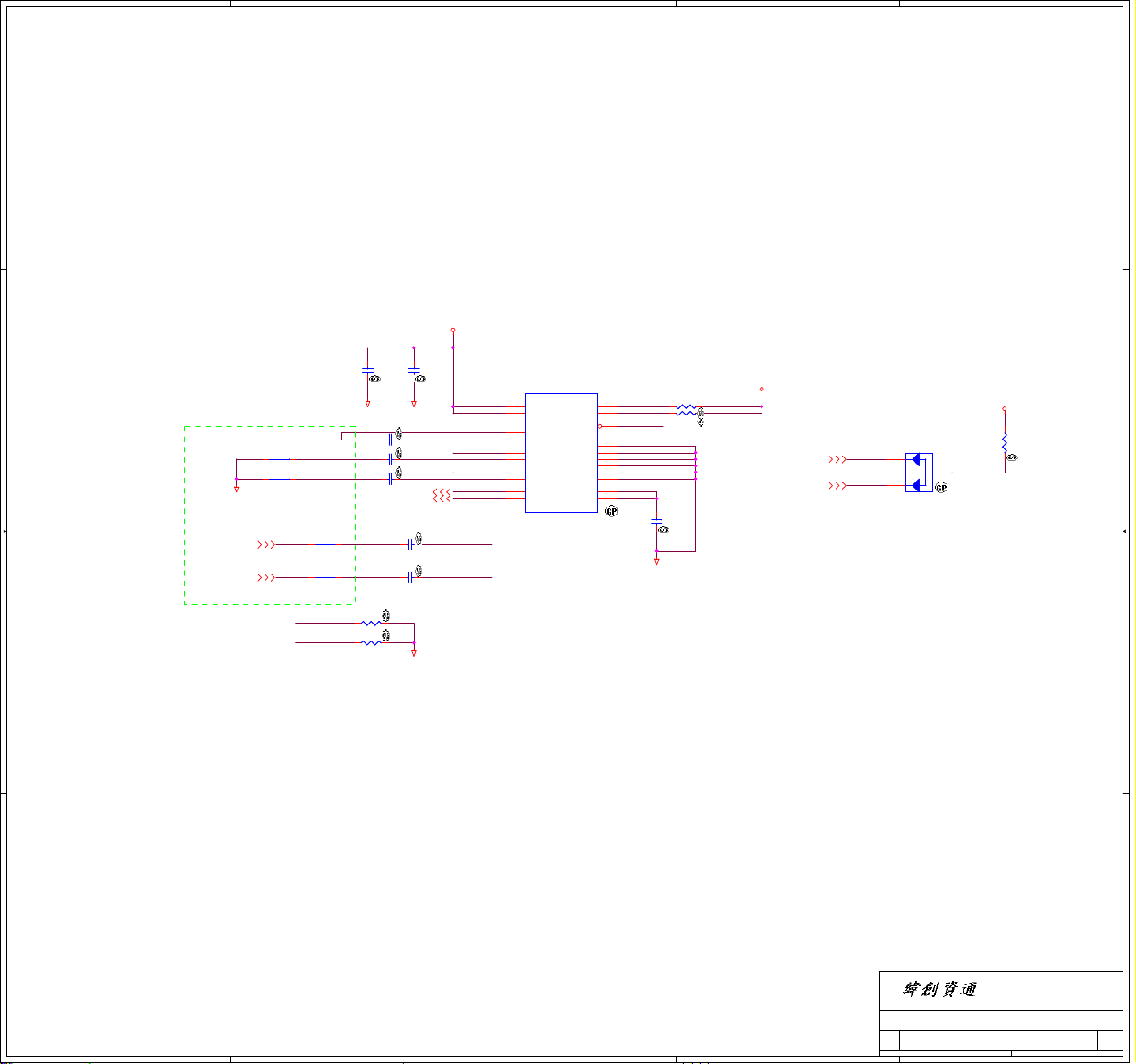

CPU (Reserved)

CPU (Reserved)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A4

A4

A4

Friday, January 30, 2015

Friday, January 30, 2015

Friday, January 30, 2015

Date: Sheet of

Date: Sheet of

Date: Sheet of

CPU (Reserved)

Laduree-BDW 15.6"

Laduree-BDW 15.6"

Laduree-BDW 15.6"

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

1

1

3 102

3 102

3 102

1

5

D

C

B

A

SSID = CPU

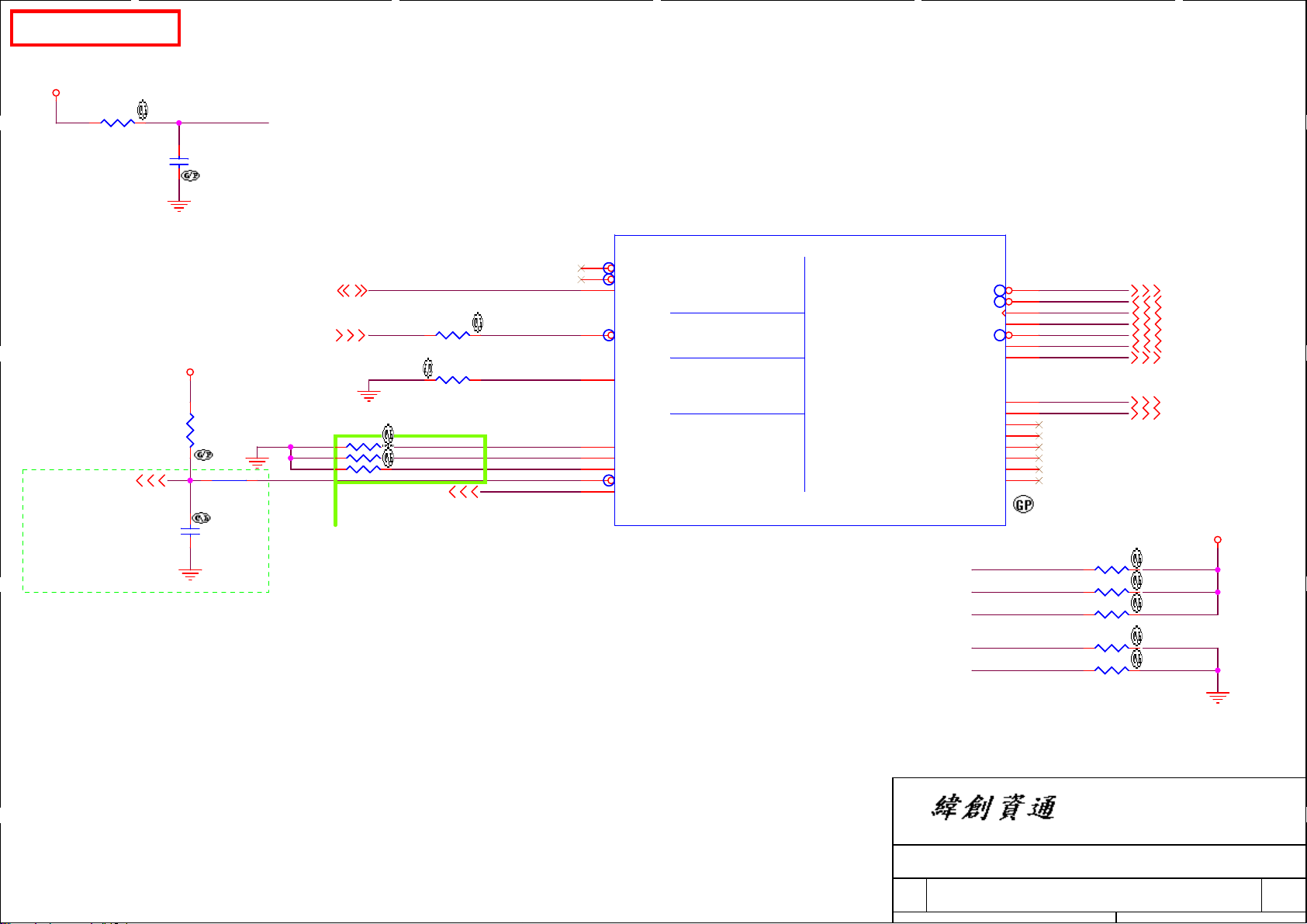

1D05V_VCCST

4

3

2

1

D

1 2

R401

R401

62R2J-GP

62R2J-GP

C

DDR3_DRAMRST#12,13

SC100P50V2JN-L-GP

SC100P50V2JN-L-GP

20150205 MV-1 Ita

B

R420

R420

470R2F-GP

470R2F-GP

C403

C403

H_PROCHOT#

12

C402

C402

SC47P50V2JN-L1-GP

SC47P50V2JN-L1-GP

1D35V_S3

12

1 2

DY

DY

1 2

H_PECI24

H_PROCHOT#24,46

R406 200R2F-L1-GPR406 200R2F-L1-GP

1 2

R407 120R2F-GPR407 120R2F-GP

1 2

R408 100R2F-L1-GP-UR408 100R2F-L1-GP-U

1 2

R402

R402

0R0402-PAD

0R0402-PAD

DDR_PG_CTRL12

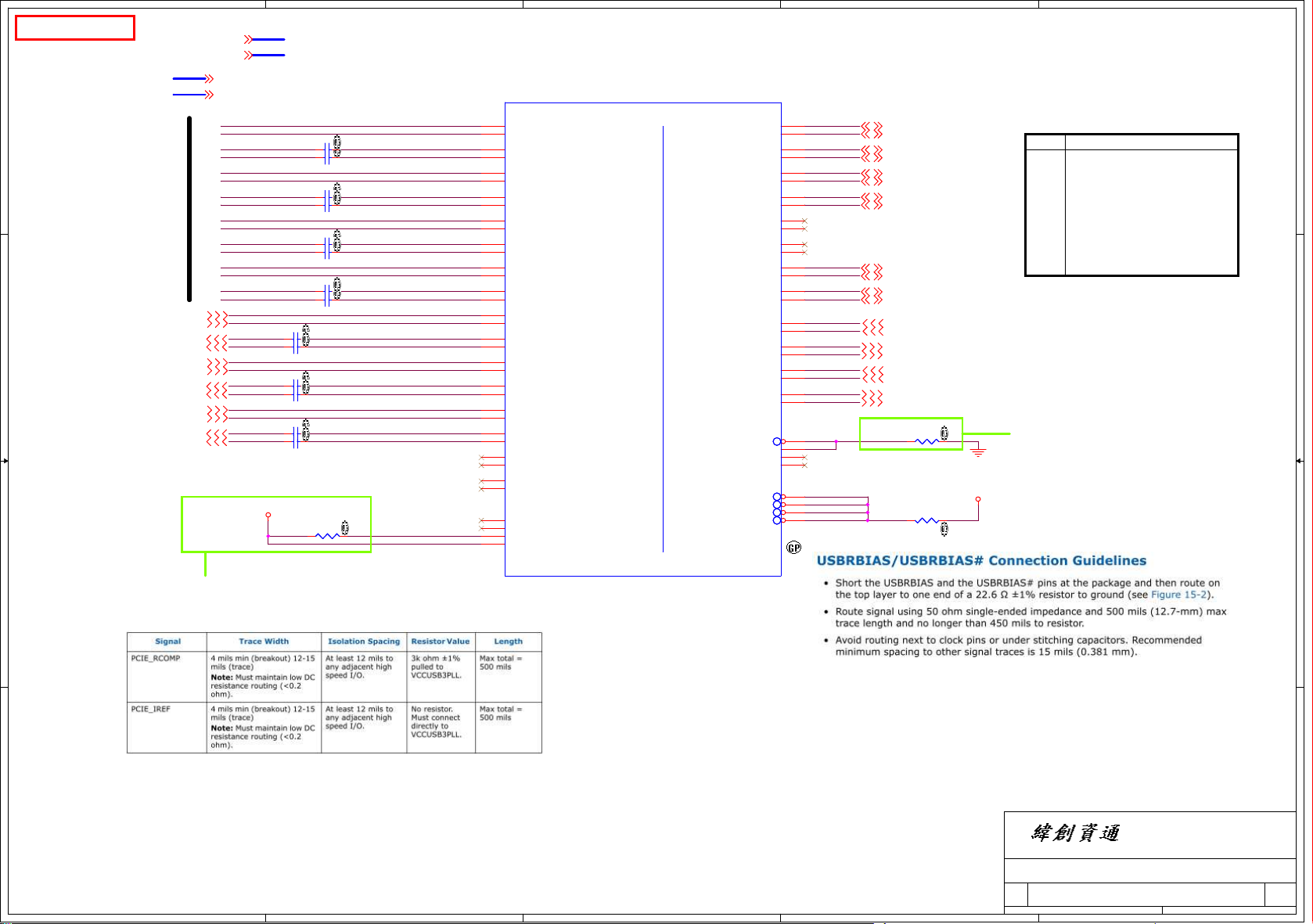

Layout Note:

1. SM_RCOMP trace width=12~15mil

2. Isolation Spacing: 20mil

3. Total trace length<500mil

1 2

R413

R413

56R2J-L1-GP

56R2J-L1-GP

R403

R403

10KR2J-L-GP

10KR2J-L-GP

H_PROCHOT#_R

H_CPUPWRGD

12

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

SM_DRAMRST#

CPU1B

CPU1B

D61

PROC_DETECT#

K61

CATERR#

N62

PECI

K63

PROCHOT#

C61

PROCPWRGD

AU60

SM_RCOMP0

AV60

SM_RCOMP1

AU61

SM_RCOMP2

AV15

SM_DRAMRST#

AV61

SM_PG_CNTL1

BROADWELL-1-GP

BROADWELL-1-GP

MISC

MISC

THERMAL

THERMAL

PWR

PWR

DDR3L

DDR3L

BROADWELL

BROADWELL

JTAG

JTAG

2 OF 19

2 OF 19

PRDY#

PREQ#

PROC_TCK

PROC_TMS

PROC_TRST#

PROC_TDI

PROC_TDO

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

BPM#6

BPM#7

XDP_TMS

XDP_TDI

XDP_TDO

J62

K62

E60

E61

E59

F63

F62

J60

H60

H61

H62

K59

H63

K60

J61

R404 51R2J-2-GP

R404 51R2J-2-GP

1 2

DY

DY

R405 51R2J-2-GP

R405 51R2J-2-GP

1 2

DY

DY

R409 51R2J-2-GPR409 51R2J-2-GP

1 2

XDP_PRDY# 96

XDP_PREQ# 96

XDP_TCK 96

XDP_TMS 96

XDP_TRST# 19,96

XDP_TDI 96

XDP_TDO 96

XDP_BPM0 96

XDP_BPM1 96

1D05V_VCCST

XDP_TCK

XDP_TRST#

Wistron Confidential document, Anyone can not

Duplicate, Modify, Forward or any other purpose

application without get Wistron permission

UMA

UMA

UMA

A

Title

Title

Title

CPU (THERMAL/CLOCK/PM)

CPU (THERMAL/CLOCK/PM)

CPU (THERMAL/CLOCK/PM)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A4

A4

A4

Thursday, February 12, 2015

Thursday, February 12, 2015

Thursday, February 12, 2015

Date: Sheet of

Date: Sheet of

Date: Sheet of

R410 51R2J-2-GPR410 51R2J-2-GP

1 2

R411 51R2J-2-GP

R411 51R2J-2-GP

1 2

DY

DY

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Laduree-BDW 15.6"

Laduree-BDW 15.6"

Laduree-BDW 15.6"

4 102

4 102

4 102

1

1

1

5

4

3

2

1

SSID = CPU

4 OF 19

3 OF 19

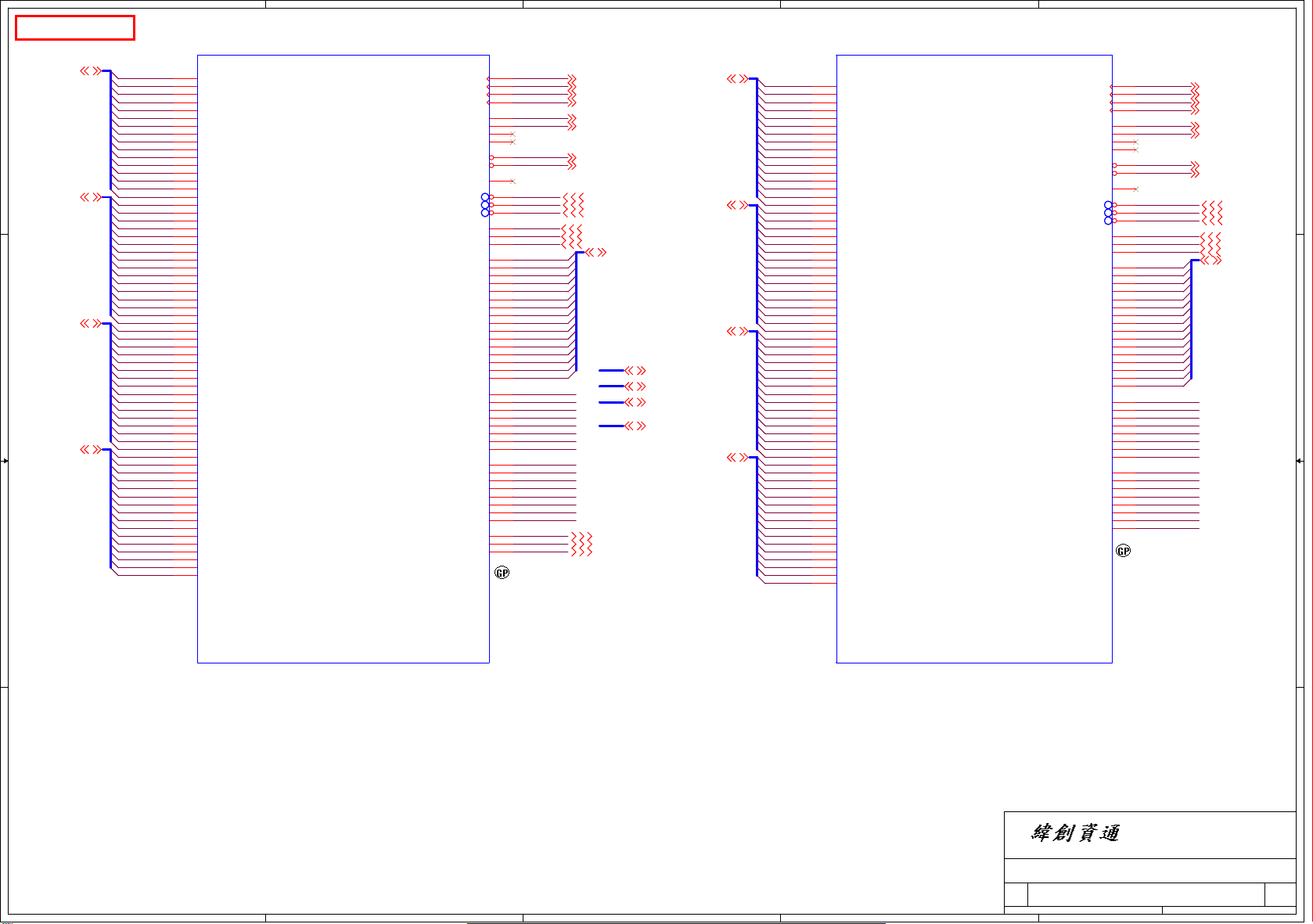

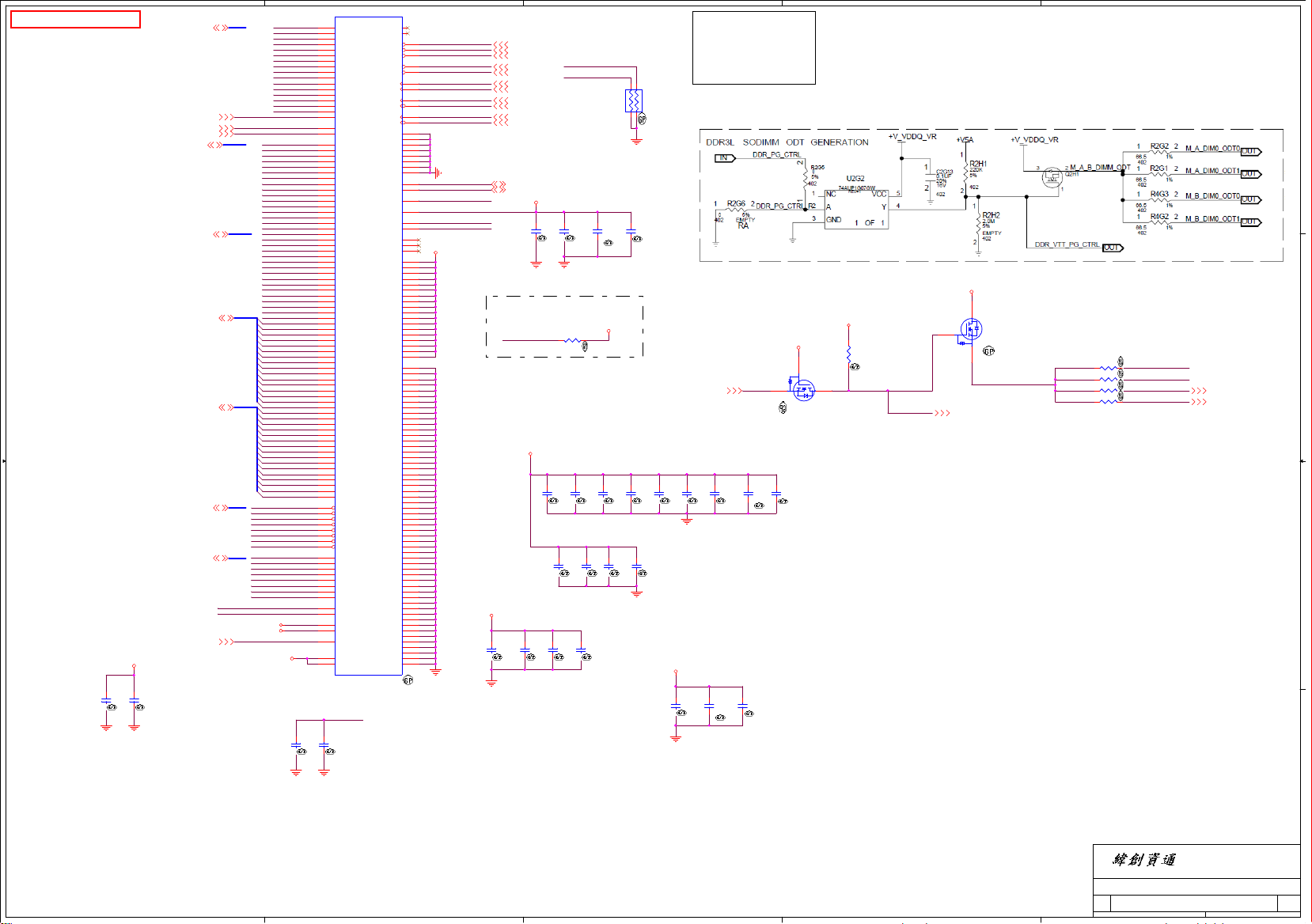

CPU1C

CPU1C

M_A_DQ[15:0]12

D D

M_B_DQ[15:0]13

M_A_DQ[31:16]12

C C

M_B_DQ[31:16]13

B B

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

AH63

AH62

AK63

AK62

AH61

AH60

AK61

AK60

AM63

AM62

AP63

AP62

AM61

AM60

AP61

AP60

AP58

AR58

AM57

AK57

AL58

AK58

AR57

AN57

AP55

AR55

AM54

AK54

AL55

AK55

AR54

AN54

AY58

AW58

AY56

AW56

AV58

AU58

AV56

AU56

AY54

AW54

AY52

AW52

AV54

AU54

AV52

AU52

AK40

AK42

AM43

AM45

AK45

AK43

AM40

AM42

AM46

AK46

AM49

AK49

AM48

AK48

AM51

AK51

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

BROADWELL

BROADWELL

DDR CHANNEL A

DDR CHANNEL A

3 OF 19

SA_CLK#0

SA_CLK0

SA_CLK#1

SA_CLK1

SA_CKE0

SA_CKE1

SA_CKE2

SA_CKE3

SA_CS#0

SA_CS#1

SA_ODT0

SA_RAS#

SA_WE#

SA_CAS#

SA_BA0

SA_BA1

SA_BA2

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_MA15

SA_DQSN0

SA_DQSN1

SA_DQSN2

SA_DQSN3

SA_DQSN4

SA_DQSN5

SA_DQSN6

SA_DQSN7

SA_DQSP0

SA_DQSP1

SA_DQSP2

SA_DQSP3

SA_DQSP4

SA_DQSP5

SA_DQSP6

SA_DQSP7

SM_VREF_CA

SM_VREF_DQ0

SM_VREF_DQ1

AU37

AV37

AW36

AY36

AU43

AW43

AY42

AY43

AP33

AR32

AP32

AY34

AW34

AU34

AU35

AV35

AY41

AU36

AY37

AR38

AP36

AU39

AR36

AV40

AW39

AY39

AU40

AP35

AW41

AU41

AR35

AV42

AU42

AJ61

AN62

AM58

AM55

AV57

AV53

AL43

AL48

AJ62

AN61

AN58

AN55

AW57

AW53

AL42

AL49

AP49

AR51

AP51

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_DQS_DN0

M_A_DQS_DN1

M_B_DQS_DN0

M_B_DQS_DN1

M_A_DQS_DN2

M_A_DQS_DN3

M_B_DQS_DN2

M_B_DQS_DN3

M_A_DQS_DP0

M_A_DQS_DP1

M_B_DQS_DP0

M_B_DQS_DP1

M_A_DQS_DP2

M_A_DQS_DP3

M_B_DQS_DP2

M_B_DQS_DP3

M_A_CLK#0 12

M_A_CLK0 12

M_A_CLK#1 12

M_A_CLK1 12

M_A_CKE0 12

M_A_CKE1 12

M_A_CS#0 12

M_A_CS#1 12

M_A_RAS# 12

M_A_WE# 12

M_A_CAS# 12

M_A_BS0 12

M_A_BS1 12

M_A_BS2 12

M_A_A[15:0] 12

+V_SM_VREF_CNT 14

DDR_WR_VREF01 14

DDR_WR_VREF02 14

M_A_DQ[47:32]12

M_B_DQ[47:32]13

M_A_DQ[63:48]12

M_A_DQS_DN[7:0] 12

M_A_DQS_DP[7:0] 12

M_B_DQS_DN[7:0] 13

M_B_DQS_DP[7:0] 13

M_B_DQ[63:48]13

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

AY31

AW31

AY29

AW29

AV31

AU31

AV29

AU29

AY27

AW27

AY25

AW25

AV27

AU27

AV25

AU25

AM29

AK29

AL28

AK28

AR29

AN29

AR28

AP28

AN26

AR26

AR25

AP25

AK26

AM26

AK25

AL25

AY23

AW23

AY21

AW21

AV23

AU23

AV21

AU21

AY19

AW19

AY17

AW17

AV19

AU19

AV17

AU17

AR21

AR22

AL21

AM22

AN22

AP21

AK21

AK22

AN20

AR20

AK18

AL18

AK20

AM20

AR18

AP18

CPU1D

CPU1D

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

BROADWELL

BROADWELL

DDR CHANNEL B

DDR CHANNEL B

4 OF 19

SB_CK#0

SB_CK0

SB_CK#1

SB_CK1

SB_CKE0

SB_CKE1

SB_CKE2

SB_CKE3

SB_CS#0

SB_CS#1

SB_ODT0

SB_RAS#

SB_WE#

SB_CAS#

SB_BA0

SB_BA1

SB_BA2

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_MA14

SB_MA15

SB_DQSN0

SB_DQSN1

SB_DQSN2

SB_DQSN3

SB_DQSN4

SB_DQSN5

SB_DQSN6

SB_DQSN7

SB_DQSP0

SB_DQSP1

SB_DQSP2

SB_DQSP3

SB_DQSP4

SB_DQSP5

SB_DQSP6

SB_DQSP7

AM38

AN38

AK38

AL38

AY49

AU50

AW49

AV50

AM32

AK32

AL32

AM35

AK35

AM33

AL35

AM36

AU49

AP40

AR40

AP42

AR42

AR45

AP45

AW46

AY46

AY47

AU46

AK36

AV47

AU47

AK33

AR46

AP46

AW30

AV26

AN28

AN25

AW22

AV18

AN21

AN18

AV30

AW26

AM28

AM25

AV22

AW18

AM21

AM18

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_A_DQS_DN4

M_A_DQS_DN5

M_B_DQS_DN4

M_B_DQS_DN5

M_A_DQS_DN6

M_A_DQS_DN7

M_B_DQS_DN6

M_B_DQS_DN7

M_A_DQS_DP4

M_A_DQS_DP5

M_B_DQS_DP4

M_B_DQS_DP5

M_A_DQS_DP6

M_A_DQS_DP7

M_B_DQS_DP6

M_B_DQS_DP7

M_B_CLK#0 13

M_B_CLK0 13

M_B_CLK#1 13

M_B_CLK1 13

M_B_CKE0 13

M_B_CKE1 13

M_B_CS#0 13

M_B_CS#1 13

M_B_RAS# 13

M_B_WE# 13

M_B_CAS# 13

M_B_BS0 13

M_B_BS1 13

M_B_BS2 13

M_B_A[15:0] 13

BROADW ELL-1-GP

BROADW ELL-1-GP

BROADW ELL-1-GP

A A

5

4

3

BROADW ELL-1-GP

Wistron Confidential document, Anyone can not

Duplicate, Modify, Forward or any other purpose

application without get Wistron permission

UMA

UMA

UMA

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

CPU (DDR)

CPU (DDR)

CPU (DDR)

Laduree-BDW 15.6"

Laduree-BDW 15.6"

Thursday, February 12, 2015

Thursday, February 12, 2015

Thursday, February 12, 2015

Laduree-BDW 15.6"

Taipei Hsien 221, Taiwan, R.O.C.

5 102

5 102

5 102

1

1

1

1

5

4

3

2

1

SSID = CPU

19 OF 19

CPU1S

AC60

AC62

AC63

AA63

AA60

Y62

Y61

Y60

V62

V61

V60

U60

AA62

U63

AA61

U62

V63

H18

B12

T63

T62

T61

T60

A5

E1

D1

J20

CPU1S

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG18

CFG17

CFG19

CFG_RCOMP

RSVD#A5

RSVD#E1

RSVD#D1

RSVD#J20

RSVD#H18

TD_IREF

BROADWELL

BROADWELL

RESERVED

RESERVED

PROC_OPI_RCOMP

CFG[19:0]96

D D

R607

C C

R607

49D9R2F-GP

49D9R2F-GP

1 2

R606

R606

8K2R2F-1-GP

8K2R2F-1-GP

12

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG18

CFG17

CFG19

CFG_RCOMP

TD_IREF

19 OF 19

RSVD_TP#AV63

RSVD_TP#AU63

RSVD_TP#C63

RSVD_TP#C62

RSVD#B43

RSVD_TP#A51

RSVD_TP#B51

RSVD_TP#L60

RSVD#N60

RSVD#W23

RSVD#Y22

RSVD#AV62

RSVD#D58

VSS

VSS

RSVD#P20

RSVD#R20

AV63

AU63

C63

C62

B43

A51

B51

L60

N60

W23

Y22

AY15

AV62

D58

P22

N21

P20

R20

RSVDAV63

RSVDAU63

RSVDA51

RSVDB51

OPI_COMP1

TP601 TPAD14-OP-GPTP601 TPAD14-OP-GP

1

TP602 TPAD14-OP-GPTP602 TPAD14-OP-GP

1

20141126 SE - Ita

TP604 TPAD14-OP-GPTP604 TPAD14-OP-GP

1

TP605 TPAD14-OP-GPTP605 TPAD14-OP-GP

1

12

R610

R610

49D9R2F-GP

49D9R2F-GP

CFG9

CFG0

B B

1

TP606

TP606

TPAD14-OP-GP

TPAD14-OP-GP

12

DY

DY

R605

R605

1KR2J-1-GP

1KR2J-1-GP

NO SVID PROTOCOL CAPABLE VR CONNECTED

0:NO VR SUPPORTING SVID IS PRESENT. THE CHIP

WILL NOTGENERATE (OR RESPOND TO) SVID ACTIVITY

1:VRS SUPPORTING SVID PROTOCOL ARE PRESENT

PHYSICAL_DEBUG_ENABLED (DFX PRIVACY)

CFG3

1

TP607

TP607

TPAD14-OP-GP

TPAD14-OP-GP

CFG[3]

0 : ENABLED

SET DFX ENABLED BIT IN DEBUG INTERFACE MSR

1 : DISABLED

CFG4

12

R603

R603

1KR2J-L2-GP

1KR2J-L2-GP

A A

5

DISPLAY PORT PRESENCE STRAP

0 : ENABLED

CFG[4]

AN EXTERNAL DISPLAY PORT DEVICE IS CONNECTED TO THE EMBEDDED DISPLAY PORT

1 : DISABLED

NO PHYSICAL DISPLAY PORT ATTACHED TO EMBEDDED DISPLAY PORT

4

Wistron Confidential document, Anyone can not

Duplicate, Modify, Forward or any other purpose

application without get Wistron permission

UMA

UMA

UMA

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet of

CPU (CFG)

CPU (CFG)

CPU (CFG)

Laduree-BDW 15.6"

Laduree-BDW 15.6"

Thursday, February 12, 2015

Thursday, February 12, 2015

Thursday, February 12, 2015

Laduree-BDW 15.6"

Taipei Hsien 221, Taiwan, R.O.C.

6 102

6 102

6 102

1

1

1

1

SSID = CPU

5

4

3

2

1

C36

C40

C44

C48

C52

C56

E23

E25

E27

E29

E31

E33

E35

E37

E39

E41

E43

E45

E47

E49

E51

E53

E55

E57

F24

F28

F32

F36

F40

F44

F48

F52

F56

G23

G25

G27

G29

G31

G33

G35

G37

G39

G41

G43

G45

G47

G49

G51

G53

G55

G57

H23

J23

K23

K57

L22

M23

M57

P57

U57

W57

CPU_CORE

12 OF 19

CPU1L

CPU1L

L59

J58

AH26

AJ31

AJ33

AJ37

AN33

AP43

AR48

AY35

AY40

AY44

AY50

F59

N58

AC58

E63

AB23

A59

E20

AD23

AA23

AE59

L62

N63

L63

B59

F60

C59

D63

H59

P62

P60

P61

N59

N61

T59

AD60

AD59

AA59

AE60

AC59

AG58

U59

V59

AC22

AE22

AE23

AB57

AD57

AG57

C24

C28

C32

BROADW ELL-1-GP

BROADW ELL-1-GP

RSVD#L59

RSVD#J58

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VCC

RSVD#N58

RSVD#AC58

VCC_SENSE

RSVD#AB23

VCCIO_OUT

VCOMP_OUT

RSVD#AD23

RSVD#AA23

RSVD#AE59

VIDALERT#

VIDSCLK

VIDSOUT

VCCST_PWRGD

VR_EN

VR_READY

VSS

PWR_DEBUG#

VSS

RSVD_TP#P60

RSVD_TP#P61

IVR_ERROR

IST_TRIGGER

RSVD#T59

RSVD#AD60

RSVD#AD59

RSVD#AA59

RSVD#AE60

RSVD#AC59

RSVD#AG58

RSVD#U59

RSVD#V59

VCCST

VCCST

VCCST

VCC

VCC

VCC

VCC

VCC

VCC

BROADWELL

BROADWELL

HSW ULT POWER

HSW ULT POWER

DY

DY

CPU_CORE

1D35V_S3

12

VCC_SENSE

VCCIO_OUT_R

CPU_SVIDALRT#

VR_READY

D D

1D05V_VCCST

130R2F-1-GP

130R2F-1-GP

R703

R703

1 2

75R2F-2-GP

75R2F-2-GP

R704

R704

1 2

150R2F-4-L-GP

150R2F-4-L-GP

R706

R706

1 2

CPU_CORE

C C

1D05V_VCCST

B B

R701 close to CPU

R701

R701

100R2F-L1-GP-U

100R2F-L1-GP-U

12

C703

C703

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

Close to CPU

H_CPU_SVIDDAT

VR_SVID_ALERT#

PWR_DEBUG

Follow Intel CRB

12

VCC_SENSE 46

C703,C715 close to CPU

PIN AC22 AE22 AE23

DY

DY

12

C715

C715

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

VR_SVID_ALERT#46

H_CPU_SVIDCLK46

H_CPU_SVIDDAT46

VCCST_PWRGD96

PWR_DEBUG96

1D05V_S0

20150205 MV-1 Ita

1D05V_VCCST

FC701

FC701

SC10U25V5KX-GP

SC10U25V5KX-GP

1V_VCOMP_OUT

H_VR_EN46

1 2

R711

R711

0R0402-PAD

0R0402-PAD

SC4D7U6D3V3KX-L-GP

SC4D7U6D3V3KX-L-GP

12

DY

DY

DY

DY

1D05V_VCCST

43R2J-GP

43R2J-GP

1D05V_VCCST

C716

C716

12

FC702

FC702

SC10U25V5KX-GP

SC10U25V5KX-GP

CPU_CORE

0R2J-L-GP

0R2J-L-GP

R707

R707

1 2

R705

R705

12

12 OF 19

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

RN702

RN702

1

8

2

7

3

6

1D05V_S0_PWRGD36,48,51

A A

5

4 5

SRN10KJ-6-GP

SRN10KJ-6-GP

VCCST_PWRGD

IMVP_PWRGD36,46

4

3

RN703

RN703

1

2

3

4 5

SRN10KJ-6-GP

SRN10KJ-6-GP

8

7

6

VR_READY

Wistron Confidential document, Anyone can not

Duplicate, Modify, Forward or any other purpose

application without get Wistron permission

UMA

UMA

UMA

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

CPU (VCC_CORE)

CPU (VCC_CORE)

CPU (VCC_CORE)

Laduree-BDW 15.6"

Laduree-BDW 15.6"

Thursday, February 12, 2015

Thursday, February 12, 2015

Thursday, February 12, 2015

Laduree-BDW 15.6"

Taipei Hsien 221, Taiwan, R.O.C.

7 102

7 102

7 102

1

1

1

1

5

4

3

2

1

SSID = CPU

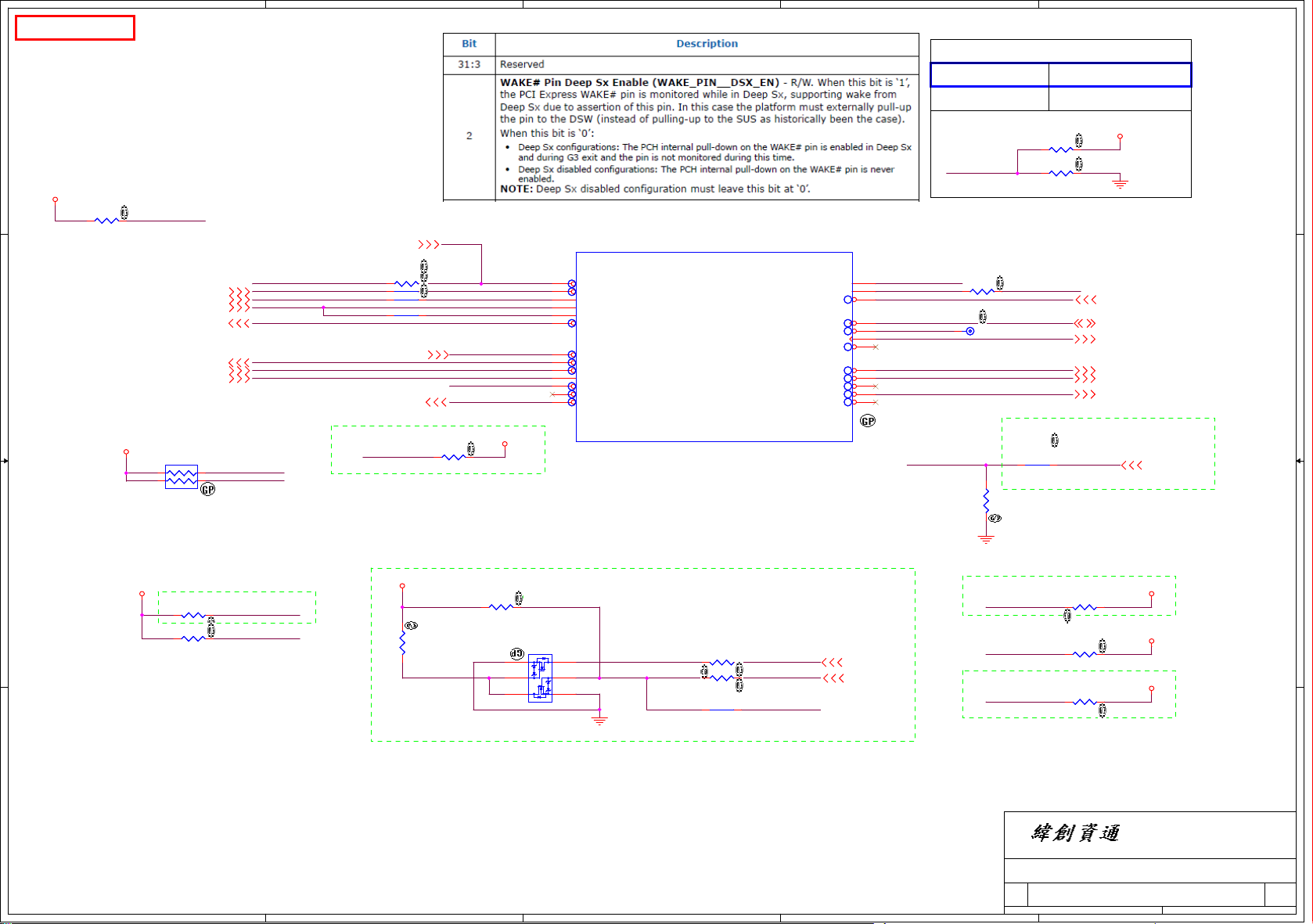

D D

1 OF 19

CPU1A

CPU1A

BROADWELL

BROADWELL

1 OF 19

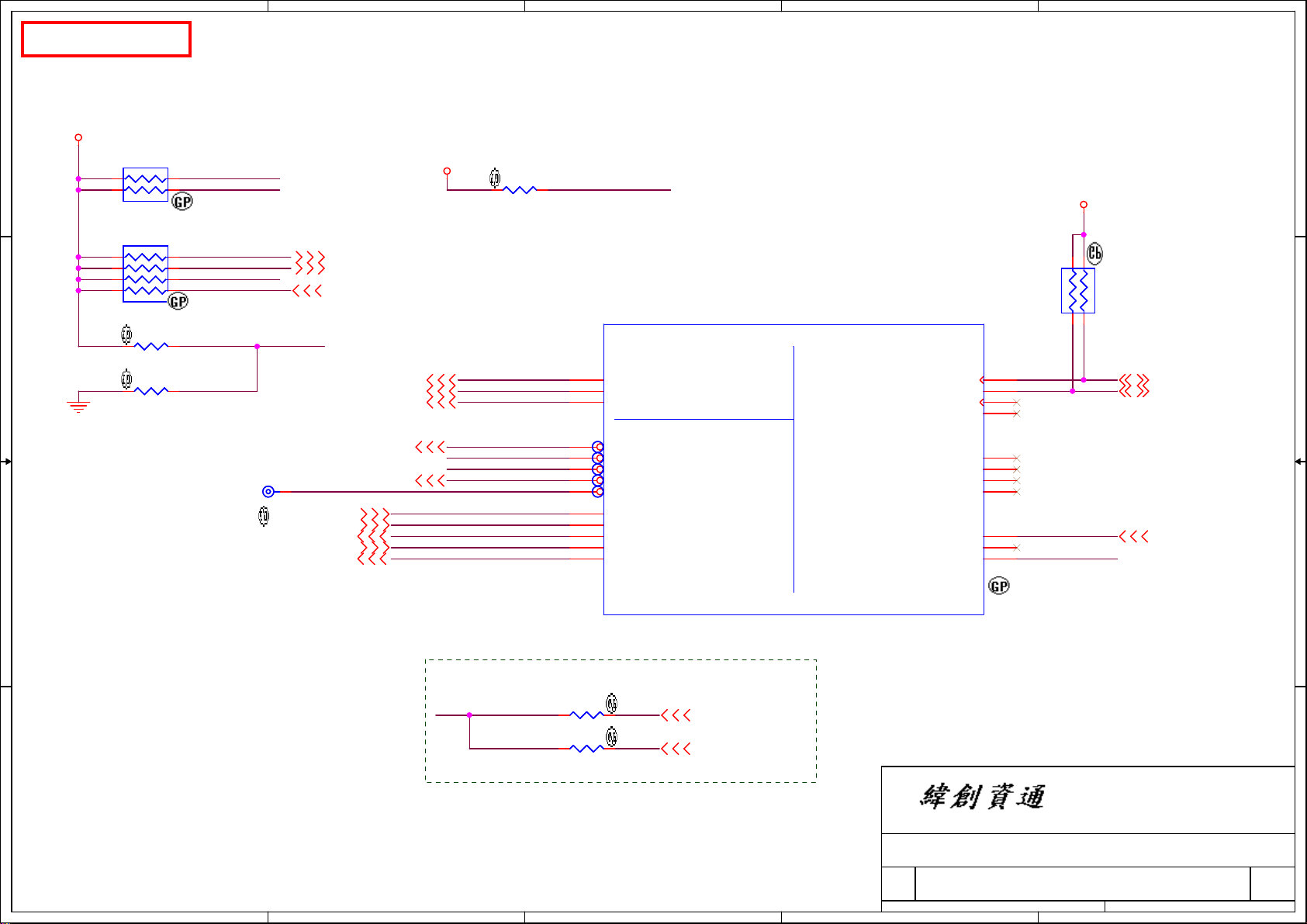

HDMI_DATA_CPU_N254

HDMI_DATA_CPU_P254

HDMI_DATA_CPU_N154

HDMI

C C

HDMI_DATA_CPU_P154

HDMI_DATA_CPU_N054

HDMI_DATA_CPU_P054

HDMI_DATA_CPU_N354

HDMI_DATA_CPU_P354

C54

C55

B58

C58

B55

A55

A57

B57

C51

C50

C53

B54

C49

B50

A53

B53

DDI1_TXN0

DDI1_TXP0

DDI1_TXN1

DDI1_TXP1

DDI1_TXN2

DDI1_TXP2

DDI1_TXN3

DDI1_TXP3

DDI2_TXN0

DDI2_TXP0

DDI2_TXN1

DDI2_TXP1

DDI2_TXN2

DDI2_TXP2

DDI2_TXN3

DDI2_TXP3

EDP_TXN0

EDP_TXP0

EDP_TXN1

EDP_TXP1

EDP_TXN2

EDP_TXP2

EDPDDI

EDPDDI

EDP_TXN3

EDP_TXP3

EDP_AUXN

EDP_AUXP

EDP_RCOMP

EDP_DISP_UTIL

C45

B46

A47

B47

C47

C46

A49

B49

A45

B45

D20

A43

EDP_RCOMP

eDP_TX_CPU_N0 55

eDP_TX_CPU_P0 55

eDP_TX_CPU_N1 55

eDP_TX_CPU_P1 55

eDP_TX_CPU_N2 52

eDP_TX_CPU_P2 52

eDP_TX_CPU_N3 52

eDP_TX_CPU_P3 52

eDP_AUX_CPU_N 55

eDP_AUX_CPU_P 55

eDP

R80124D9R2F-L-GP R80124D9R2F-L-GP

12

1V_VCOMP_OUT

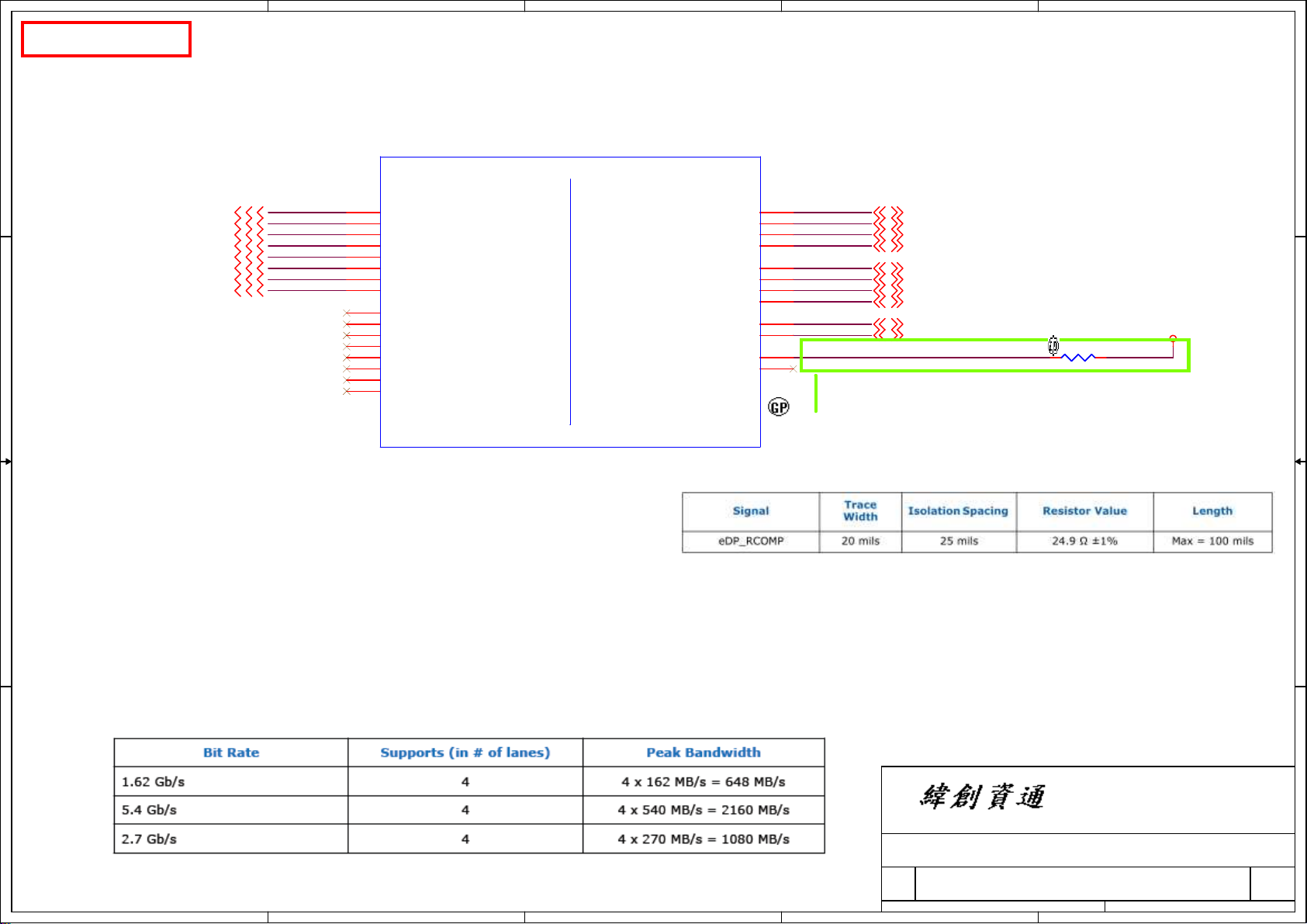

Layout Note:

BROADWELL-1-GP

BROADWELL-1-GP

B B

Design Guideline:

EDP_COMP keep routing length max 100 mils.

Trace Width:20 mils.

Wistron Confidential document, Anyone can not

Duplicate, Modify, Forward or any other purpose

application without get Wistron permission

UMA

UMA

UMA

Wistron Corporation

Wistron Corporation

A A

Title

Title

Title

CPU (DDI/EDP)

CPU (DDI/EDP)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A4

A4

A4

Date: Sheet of

Date: Sheet of

5

4

3

Date: Sheet of

CPU (DDI/EDP)

Laduree-BDW 15.6"

Laduree-BDW 15.6"

Thursday, February 12, 2015

Thursday, February 12, 2015

Thursday, February 12, 2015

2

Laduree-BDW 15.6"

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

1

1

8 102

8 102

8 102

1

1

5

4

3

2

1

SSID = CPU

D D

16 OF 19

CPU1P

CPU1P

BROADWELL

D33

VSS

D34

VSS

D35

VSS

D37

VSS

D38

VSS

D39

VSS

D41

VSS

D42

VSS

D43

VSS

D45

VSS

D46

VSS

D47

VSS

D49

VSS

D5

VSS

D50

C C

B B

VSS

D51

VSS

D53

VSS

D54

VSS

D55

VSS

D57

VSS

D59

VSS

D62

VSS

D8

VSS

E11

VSS

E17

VSS

F20

VSS

F26

VSS

F30

VSS

F34

VSS

F38

VSS

F42

VSS

F46

VSS

F50

VSS

F54

VSS

F58

VSS

F61

VSS

G18

VSS

G22

VSS

G3

VSS

G5

VSS

G6

VSS

G8

VSS

H13

VSS

BROADWELL-1-GP

BROADWELL-1-GP

BROADWELL

16 OF 19

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS_SENSE

VSS

H17

H57

J10

J22

J59

J63

K1

K12

L13

L15

L17

L18

L20

L58

L61

L7

M22

N10

N3

P59

P63

R10

R22

R8

T1

T58

U20

U22

U61

U9

V10

V3

V7

W20

W22

Y10

Y59

Y63

V58

AH46

V23

E62

AH16

R901 close to CPU

VSS_SENSE

R901

R901

100R2F-L1-GP-U

100R2F-L1-GP-U

VSS_SENSE 46

12

Layout Note:

Wistron Confidential document, Anyone can not

Duplicate, Modify, Forward or any other purpose

application without get Wistron permission

UMA

UMA

UMA

Wistron Corporation

Wistron Corporation

A A

Title

Title

Title

CPU (VSS)

CPU (VSS)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A4

A4

A4

Date: Sheet of

Date: Sheet of

5

4

3

Date: Sheet of

CPU (VSS)

Laduree-BDW 15.6"

Laduree-BDW 15.6"

Thursday, February 12, 2015

Thursday, February 12, 2015

Thursday, February 12, 2015

2

Laduree-BDW 15.6"

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

1

1

9 102

9 102

9 102

1

1

5

4

3

2

1

SSID = MCP

1D35V_S3

1D35V_S3

D D

2.2uF x 4

10uF x 6

MAX: 9.76A

1D35V_S3

12

C1034

C1034

SC2D2U10V3KX-L-GP

SC2D2U10V3KX-L-GP

12

C1033

C1033

SC2D2U10V3KX-L-GP

SC2D2U10V3KX-L-GP

12

C1032

C1032

SC2D2U10V3KX-L-GP

SC2D2U10V3KX-L-GP

12

C1031

C1031

SC2D2U10V3KX-L-GP

SC2D2U10V3KX-L-GP

12

EC1001

EC1001

12

EC1002

SCD1U25V2KX-L-GP

SCD1U25V2KX-L-GP

EC1002

SCD1U25V2KX-L-GP

SCD1U25V2KX-L-GP

20141203 SE - Ita

12

C C

C1040

C1040

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

12

C1039

C1039

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

12

C1038

C1038

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

12

C1037

C1037

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

12

C1036

C1036

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

12

C1035

C1035

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

CPU_CORE

CPU_CORE

22uF x 10

DUMMY 22UF*2

C1009

C1010

C1011

C1012

C1012

12

DY

B B

DY

C1011

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

12

DY

DY

C1010

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

12

C1009

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

12

C1008

C1008

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

12

C1007

C1007

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

12

C1006

C1006

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

12

C1005

C1005

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

12

C1004

C1004

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

12

C1003

C1003

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

12

12

C1002

C1002

CPU_CORE

C1001

C1001

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

12

12

EC1003

EC1003

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

12

EC1004

SCD1U25V2KX-L-GP

SCD1U25V2KX-L-GP

EC1004

12

EC1005

SCD1U25V2KX-L-GP

SCD1U25V2KX-L-GP

EC1005

SCD1U25V2KX-L-GP

SCD1U25V2KX-L-GP

20141204 SE - Ita change back

CPU_CORE

Wistron Confidential document, Anyone can not

12

TC1001

TC1001

ST220U2VDM-5-GP

ST220U2VDM-5-GP

79.22719.2BL

79.22719.2BL

A A

5

4

3

Duplicate, Modify, Forward or any other purpose

application without get Wistron permission

UMA

UMA

UMA

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

CPU (Power CAP1)

CPU (Power CAP1)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A4

A4

A4

Date: Sheet of

Date: Sheet of

Date: Sheet of

CPU (Power CAP1)

Laduree-BDW 15.6"

Laduree-BDW 15.6"

Friday, January 30, 2015

Friday, January 30, 2015

Friday, January 30, 2015

2

Laduree-BDW 15.6"

10 102

10 102

10 102

1

1

1

1

5

4

3

2

1

1D05V_S0 1D05V_MODPHY 1D05V_MODPHY

D D

C1102;C1103

pin K9 L10

12

C1102

C1102

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

12

C1103

C1103

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

Page 21

20141022 SC - Terry 20141022 SC - Terry

0.041A 0.042A

1 2

L1101

L1101

IND-2D2UH-196-GP

IND-2D2UH-196-GP

2nd = 68.2R21G.10Q

2nd = 68.2R21G.10Q

C1108 ;C1109

pin B18

12

C1108

C1108

12

C1109

C1109

SC4D7U6D3V3KX-L-GP

SC4D7U6D3V3KX-L-GP

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

C1104 ;C1106

1 2

L1102

L1102

IND-2D2UH-196-GP

IND-2D2UH-196-GP

2nd = 68.2R21G.10Q

2nd = 68.2R21G.10Q

pin B11

12

C1104

C1104

SC4D7U6D3V3KX-L-GP

SC4D7U6D3V3KX-L-GP

MAX: 1.92A

12

C1106

C1106

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

3D3V_RTC_AUX1D05V_VCCUSB3PLL_S0 1D05V_VCCSATA3PLL_S0

12

12

C1135

C1135

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

20141203 SE - Ita

C1135;C1136

pin AG10

C1136

C1136

SCD1U50V3KX-L-GP

SCD1U50V3KX-L-GP

3D3V_SUS

12

C1116

C1116

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

20141204 SE - Ita change back

C1116 pin AC9, AA9

MAX: 3.51A

12

C1111

C1111

1D05V_VCCCLK_S01D05V_VCCACLKPLL_S01D05V_S0 1D05V_S0

12

C1115

C1115

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

SC4D7U6D3V3KX-L-GP

SC4D7U6D3V3KX-L-GP

3D3V_S0

MAX: 0.285A

12

C C

C1101 pin V8

C1119 pin K14

12

C1119

C1119

SCD1U16V2KX-L-GP

SCD1U16V2KX-L-GP

C1101

C1101

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

C1118;C1120

1 2

L1104

L1104

IND-2D2UH-196-GP

IND-2D2UH-196-GP

2nd = 68.2R21G.10Q

2nd = 68.2R21G.10Q

pin A20

12

C1118

C1118

12

C1120

C1120

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

SC4D7U6D3V3KX-L-GP

SC4D7U6D3V3KX-L-GP

C1111;C1115

1 2

L1103

L1103

IND-2D2UH-196-GP

IND-2D2UH-196-GP

2nd = 68.2R21G.10Q

2nd = 68.2R21G.10Q

pin J18, K19

20141204 SE - Ita change back

1D05V_S0 1D05V_S0 1D05V_S0

12

C1144

C1144

pin AE9

B B

A A

5

C1144

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

C1110 pin J11

C1134 C1141 pin J11, AE8

4

12

C1134

C1134

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

12

12

C1141

C1141

C1110

C1110

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

3

C1122;C1123

pin AA21

12

C1122

C1122

12

C1123

C1123

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

SC4D7U6D3V3KX-L-GP

SC4D7U6D3V3KX-L-GP

Wistron Confidential document, Anyone can not

Duplicate, Modify, Forward or any other purpose

application without get Wistron permission

UMA

UMA

UMA

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

CPU (Power CAP2)

CPU (Power CAP2)

CPU (Power CAP2)

Laduree-BDW 15.6"

Laduree-BDW 15.6"

Friday, January 30, 2015

Friday, January 30, 2015

Friday, January 30, 2015

Laduree-BDW 15.6"

Taipei Hsien 221, Taiwan, R.O.C.

11 102

11 102

11 102

1

1

1

1

5

SSID = MEMORY

D D

C C

B B

M_VREF_CA_D IMM0

12

C1226

C1226

SCD1U16V2KX- L-GP

SCD1U16V2KX- L-GP

12

C1225

C1225

SC2D2U10V3KX- L-GP

SC2D2U10V3KX- L-GP

DY

DY

M_A_A[15:0]5

M_A_BS25

M_A_BS05

M_A_BS15

M_A_DQ[15:0]5

M_A_DQ[31:16]5

M_A_DQ[47:32]5

M_A_DQ[63:48]5

M_A_DQS_DN[7: 0]5

M_A_DQS_DP[7:0]5

M_VREF_CA_D IMM0

DDR3_DR AMRST#4,13

M_VREF_DQ_D IMM0

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

M_A_DQS_DN0

M_A_DQS_DN1

M_A_DQS_DN2

M_A_DQS_DN3

M_A_DQS_DN4

M_A_DQS_DN5

M_A_DQS_DN6

M_A_DQS_DN7

M_A_DQS_DP0

M_A_DQS_DP1

M_A_DQS_DP2

M_A_DQS_DP3

M_A_DQS_DP4

M_A_DQS_DP5

M_A_DQS_DP6

M_A_DQS_DP7

M_A_DIM0_ODT0

M_A_DIM0_ODT1

0D675V_VREF_S0

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

H = 4mm

Close DIMM1 VREF_CA pin

98

97

96

95

92

91

90

86

89

85

107

84

83

119

80

78

79

109

108

5

7

15

17

4

6

16

18

21

23

33

35

22

24

34

36

39

41

51

53

40

42

50

52

57

59

67

69

56

58

68

70

129

131

141

143

130

132

140

142

147

149

157

159

146

148

158

160

163

165

175

177

164

166

174

176

181

183

191

193

180

182

192

194

10

27

45

62

135

152

169

186

12

29

47

64

137

154

171

188

116

120

126

1

30

203

204

M_VREF_DQ_D IMM0

12

12

C1205

C1205

SCD1U16V2KX-L-GP

SCD1U16V2KX-L-GP

DY

DY

DIMM1

DIMM1

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12

A13

A14

A15

A16/BA2

BA0

BA1

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

DQS0#

DQS1#

DQS2#

DQS3#

DQS4#

DQS5#

DQS6#

DQS7#

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

ODT0

ODT1

VREF_CA

VREF_DQ

RESET#

VTT1

VTT2

DDR3-204P- 306-GP

DDR3-204P- 306-GP

062.10011.0461

062.10011.0461

C1211

C1211

SC2D2U10V3ZY- 1GP

SC2D2U10V3ZY- 1GP

RAS#

CAS#

CS0#

CS1#

CKE0

CKE1

CK0#

CK1#

EVENT#

VDDSPD

NC#1

NC#2

NC#/TEST

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

4

NP1

NP1

NP2

NP2

110

113

WE#

115

114

121

73

74

101

CK0

103

102

CK1

104

11

DM0

28

DM1

46

DM2

63

DM3

136

DM4

153

DM5

170

DM6

187

DM7

200

SDA

202

SCL

SA0

SA1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

TS#_DIMM0_1

198

199

SA0_DIM0

197

SA1_DIM0

201

77

122

1D35V_S3

125

75

76

81

82

87

88

93

94

99

100

105

106

111

112

117

118

123

124

2

3

8

9

13

14

19

20

25

26

31

32

37

38

43

44

48

49

54

55

60

61

65

66

71

72

127

128

133

134

138

139

144

145

150

151

155

156

161

162

167

168

172

173

178

179

184

185

189

190

195

196

205

206

0D675V_VREF_S0

12

C1214

C1214

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

M_A_RAS# 5

M_A_WE# 5

M_A_CAS# 5

M_A_CS#0 5

M_A_CS#1 5

M_A_CKE0 5

M_A_CKE1 5

M_A_CLK0 5

M_A_CLK#0 5

M_A_CLK1 5

M_A_CLK#1 5

SMB_DATA 13,18,62,96

SMB_CLK 13,18,62,96

3D3V_S0

SA0_DIM0

SA1_DIM0

12

12

FC1201

FC1201

C1203

C1203

SCD1U25V2KX-L-GP

SCD1U25V2KX-L-GP

SCD1U16V2KX-L-GP

SCD1U16V2KX-L-GP

Thermal EVENT

R1204

1D35V_S3

12

C1215

C1215

R1204

10KR2J-L-GP

10KR2J-L-GP

1 2

12

C1206

C1206

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

12

C1223

C1223

12

C1219

C1219

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

Layout Note:

Place these Caps near

SO-DIMMA.

SODIMM A DECOUPLING

12

C1207

C1207

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

12

TS#_DIMM0_1

12

C1222

C1222

C1216

C1216

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

12

FC1207

FC1207

3D3V_S0

12

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

SC10U25V5KX-GP

SC10U25V5KX-GP

3

1

23

RN1202

RN1202

SRN10KJ-5-G P

SRN10KJ-5-G P

4

12

FC1208

FC1208

SC100P50V2JN-3GP

SC100P50V2JN-3GP

RF

RF

RF

RF

12

C1208

C1208

C1209

C1209

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

12

12

C1220

C1220

C1221

C1221

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

Place these caps

close to VTT1 and

VTT2.

0D675V_VREF_S0

Note:

If SA0 DIM0 = 0, SA1_DIM0 = 0

SO-DIMMA SPD Address is 0xA0

SO-DIMMA TS Address is 0x30

If SA0 DIM0 = 1, SA1_DIM0 = 0

SO-DIMMA SPD Address is 0xA2

SO-DIMMA TS Address is 0x32

DDR_PG_CT RL4

12

12

C1210

C1210

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

DY

DY

12

FC1202

FC1202

SCD1U25V2KX-L-GP

SCD1U25V2KX-L-GP

DY

DY

12

12

FC1204

FC1204

FC1210

FC1210

SCD1U25V2KX-L-GP

SCD1U25V2KX-L-GP

RF

RF

FC1203

FC1203

SCD1U25V2KX-L-GP

SCD1U25V2KX-L-GP

DY

DY

SC10U25V5KX-GP

SC10U25V5KX-GP

Q1202

Q1202

DMN5L06K-7-G P

DMN5L06K-7-G P

84.05067.031

84.05067.031

12

FC1205

FC1205

SC10U25V5KX-GP

SC10U25V5KX-GP

RF

RF

12

FC1209

FC1209

SC100P50V2JN-3GP

SC100P50V2JN-3GP

RF

RF

Q1202 Q1203

Vth1V

1D35V_S3

G

DS

12

FC1206

FC1206

SC100P50V2JN-3GP

SC100P50V2JN-3GP

RF

RF

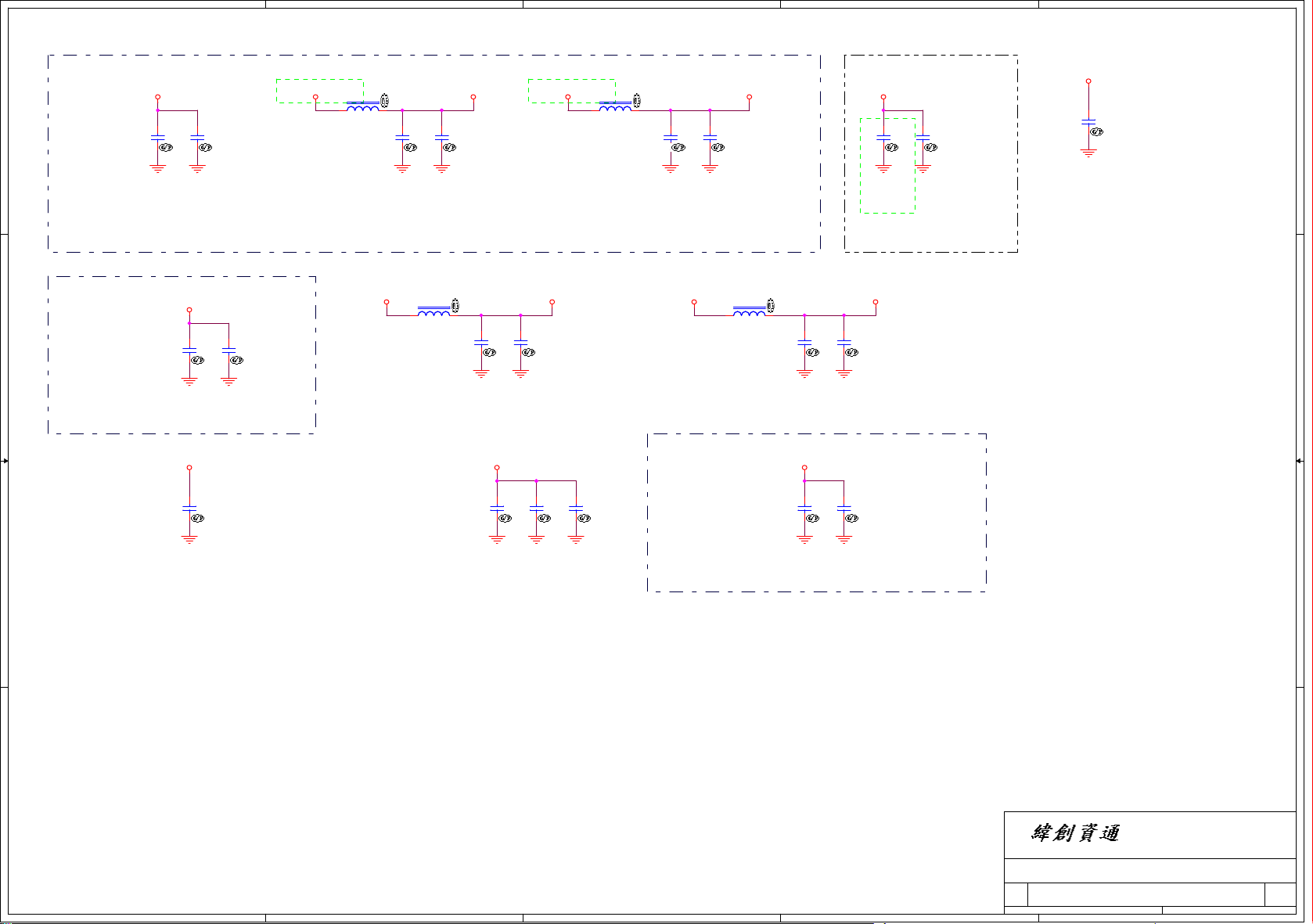

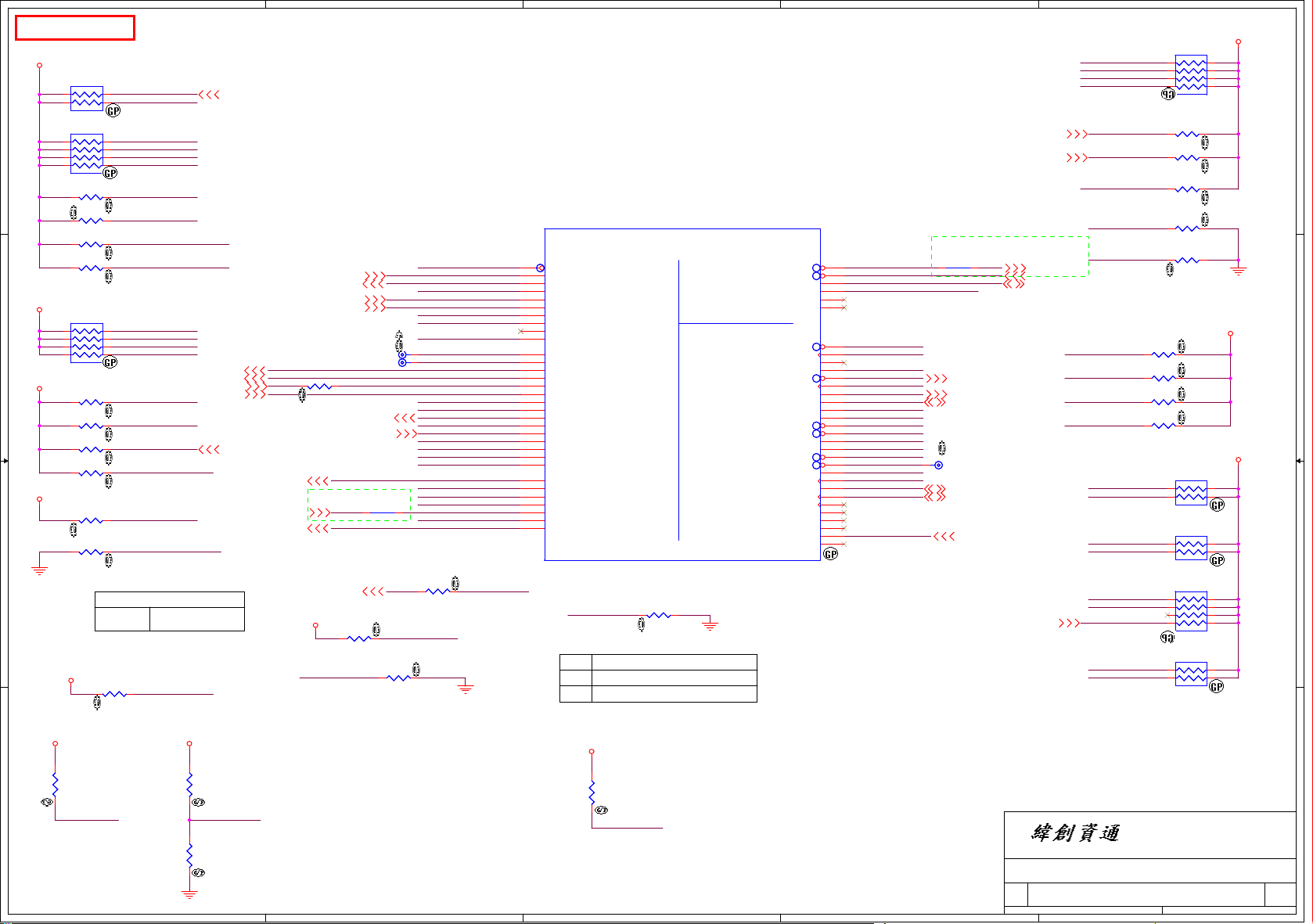

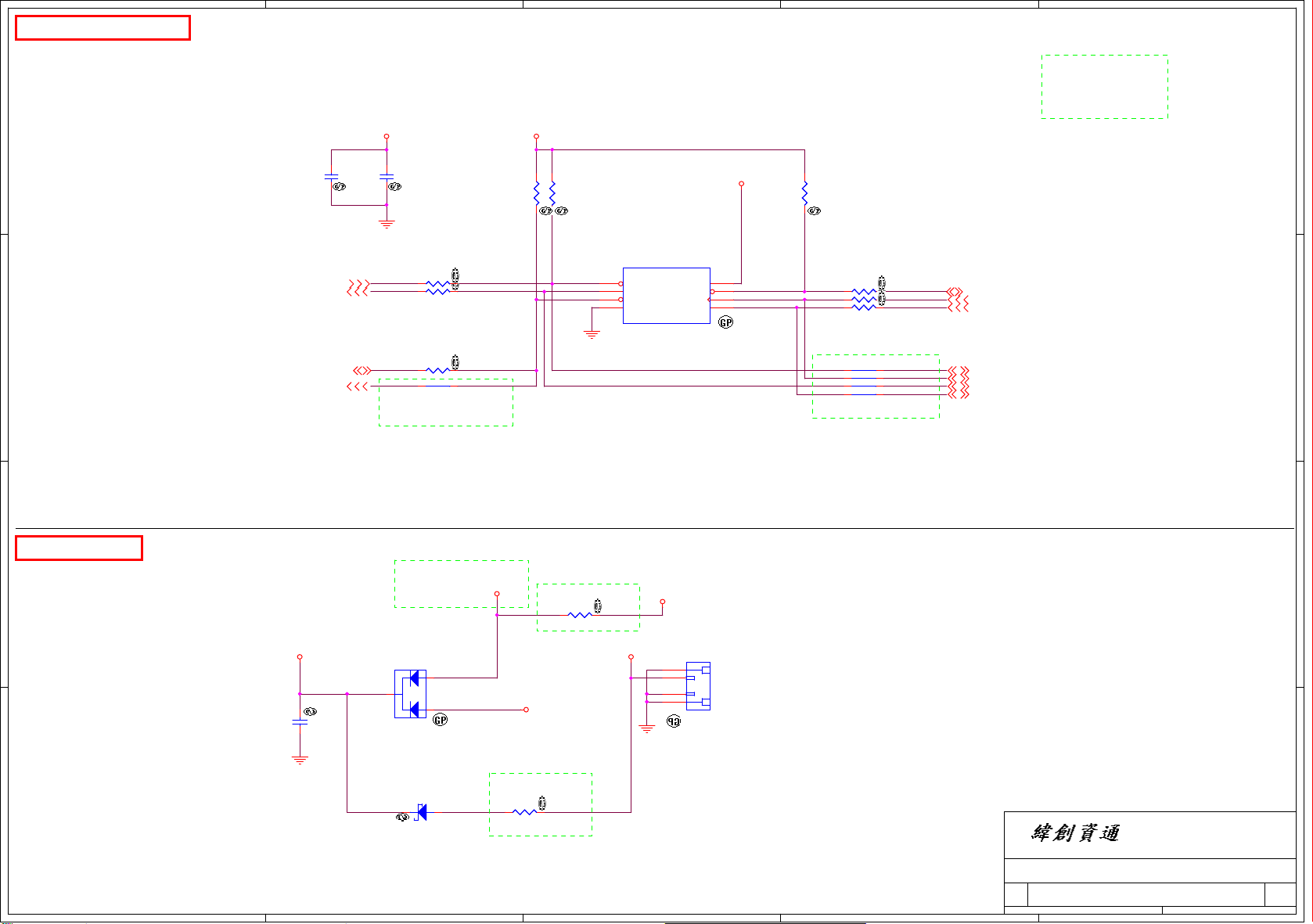

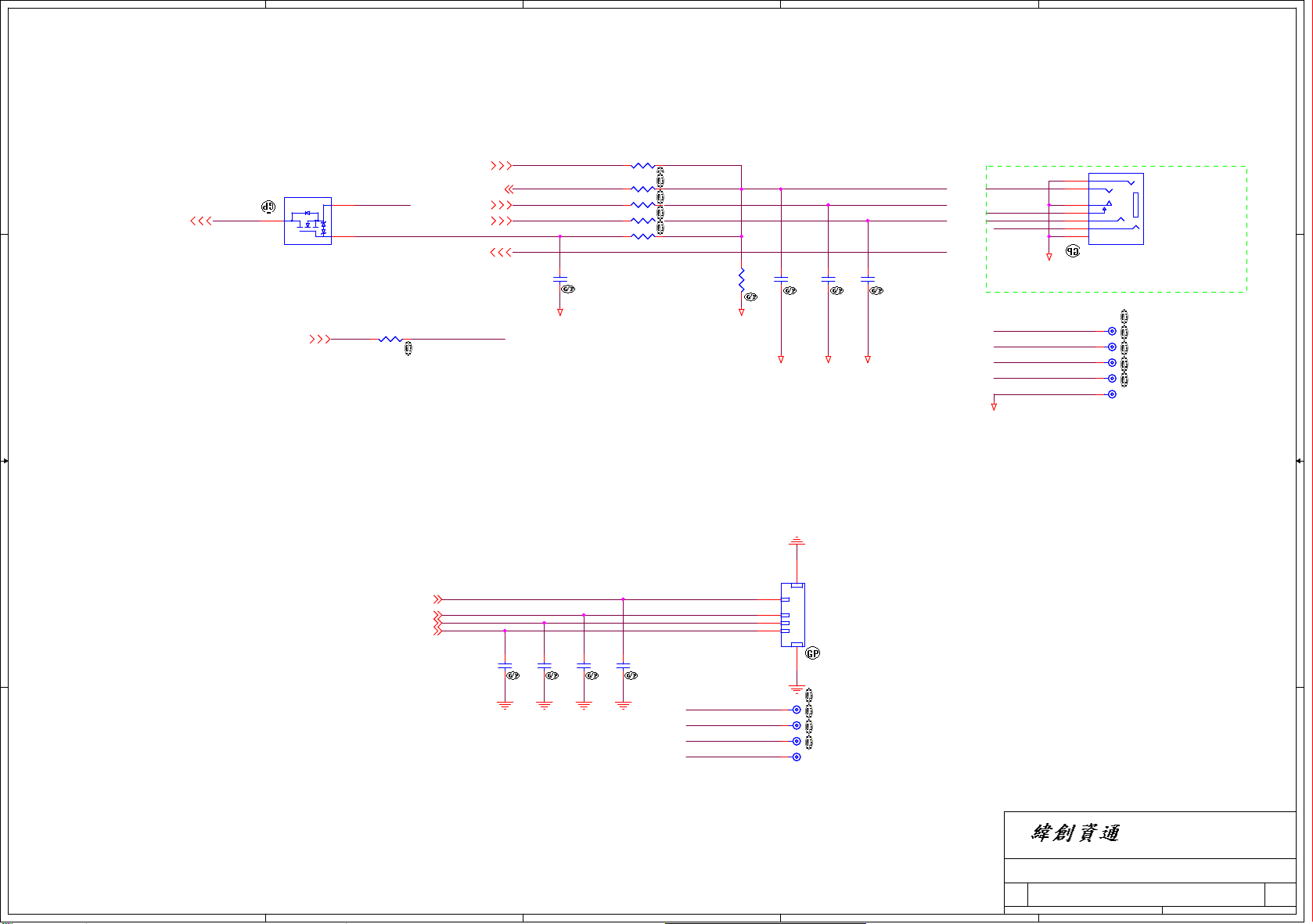

SODIMM Memory Connectivity and Topology

ODT Signal Connectivity and Support

For DDR3L SODIMM designs, Intel recommends ODT signals not to be routed between

CPU and DIMM on platform, leave ODT at CPU as no-connect (open), and tie DIMM

ODT to VDDQ through FET and resistor. The reason for this additional ODT-control

circuitry on the platform is to save power dissipation by turning off VDDQ to VTT path

during low power states, as ODT signal is terminated to VTT through RTT on SODIMM.

The ODT value for DDR3L SODIMM 1-DPC platform will be encoded in the write

command and use RTT_NOM = Off and RTT_WR = (60,120) Ohm.

CPU ODT output would be NOCON

SODIMM ODT input should be tied to VDDQ through a FET and a resistor to

support low power states.

84.05067.031

3D3V_S0

12

R1212

R1212

220KR2J-L2-GP

220KR2J-L2-GP

2

1D35V_S3

DS

Q1203

Q1203

DMN5L06K-7-G P

DMN5L06K-7-G P

G

84.05067.031

84.05067.031

ODT resistor must be 66.5 ohm

1 2

R1208 66D5R2F-GPR1208 66D5R2F-GP

M_A_B_DIM_ODT

DDR_PG_OU T 49

1 2

R1209 66D5R2F-GPR1209 66D5R2F-GP

1 2

R1210 66D5R2F-GPR1210 66D5R2F-GP

1 2

R1211 66D5R2F-GPR1211 66D5R2F-GP

M_A_DIM0_ODT0

M_A_DIM0_ODT1

1

M_B_DIM0_ODT0 13

M_B_DIM0_ODT1 13

A A

Wistron Confidential document, Anyone can not

Duplicate, Modify, Forward or any other purpose

application without get Wistron permission

UMA

UMA

UMA

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin T ai Wu Rd., H sichih,

21F, 88, Sec.1, Hsin T ai Wu Rd., H sichih,

21F, 88, Sec.1, Hsin T ai Wu Rd., H sichih,

Taipei Hsie n 221, Taiwan, R.O.C.

Taipei Hsie n 221, Taiwan, R.O.C.

Title

Title

Title

DDR3-SODIMM1

DDR3-SODIMM1

DDR3-SODIMM1

Size Document Num ber Rev

Size Document Num ber Rev

Size Document Num ber Rev

Custom

Custom

Custom

Thursday, Feb ruary 12, 2015

Thursday, Feb ruary 12, 2015

Thursday, Feb ruary 12, 2015

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Taipei Hsie n 221, Taiwan, R.O.C.

Laduree-BDW 15.6"

Laduree-BDW 15.6"

Laduree-BDW 15.6"

1

12 102

12 102

12 102

1

1

1

5

DIMM2

SSID = MEMORY

D D

C C

B B

M_VREF_CA_D IMM0

12

12

C1330

C1330

SCD1U16V2KX- L-GP

SCD1U16V2KX- L-GP

M_B_DQ[15:0]5

M_B_DQ[31:16]5

M_B_DQ[47:32]5

M_B_DQS_DN[7: 0]5

M_B_DQS_DP[7:0]5

M_B_DIM0_ODT012

M_B_DIM0_ODT112

C1329

C1329

SC2D2U10V3KX- L-GP

SC2D2U10V3KX- L-GP

DY

DY

M_B_A[15:0]5

M_B_BS25

M_B_BS05

M_B_BS15

M_B_DQ[63:48]5

M_VREF_CA_D IMM0

M_VREF_DQ_D IMM1

DDR3_DR AMRST#4,12

M_B_DQ23

M_B_DQ17

M_B_DQ20

M_B_DQ19

M_B_DQ22

M_B_DQ16

M_B_DQ21

M_B_DQ18

M_B_DQ5

M_B_DQ4

M_B_DQ7

M_B_DQ6

M_B_DQ3

M_B_DQ2

M_B_DQ0

M_B_DQ1

M_B_DQ9

M_B_DQ14

M_B_DQ11

M_B_DQ13

M_B_DQ12

M_B_DQ8

M_B_DQ15

M_B_DQ10

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ31

M_B_DQ29

M_B_DQ30

M_B_DQ28

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ38

M_B_DQ32

M_B_DQ33

M_B_DQ37

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQS_DN2

M_B_DQS_DN0

M_B_DQS_DN1

M_B_DQS_DN3

M_B_DQS_DN4

M_B_DQS_DN5

M_B_DQS_DN6

M_B_DQS_DN7

M_B_DQS_DP2

M_B_DQS_DP0

M_B_DQS_DP1

M_B_DQS_DP3

M_B_DQS_DP4

M_B_DQS_DP5

M_B_DQS_DP6

M_B_DQS_DP7

0D675V_VREF_S0

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

H=4mm

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

DIMM2

98

97

96

95

92

91

90

86

89

85

107

84

83

119

80

78

79

109

108

5

7

15

17

4

6

16

18

21

23

33

35

22

24

34

36

39

41

51

53

40

42

50

52

57

59

67

69

56

58

68

70

129

131

141

143

130

132

140

142

147

149

157

159

146

148

158

160

163

165

175

177

164

166

174

176

181

183

191

193

180

182

192

194

10

27

45

62

135

152

169

186

12

29

47

64

137

154

171

188

116

120

126

1

30

203

204

DDR3-204P- 327-GP

DDR3-204P- 327-GP

062.10011.0841

062.10011.0841

20141202 SE - Ita

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12

A13

A14

A15

A16/BA2

BA0

BA1

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

DQS0#

DQS1#

DQS2#

DQS3#

DQS4#

DQS5#

DQS6#

DQS7#

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

ODT0

ODT1

VREF_CA

VREF_DQ

RESET#

VTT1

VTT2

SKT_DDR 204P SMD

SKT_DDR 204P SMD

4

RAS#

CAS#

CS0#

CS1#

CKE0

CKE1

CK0#

CK1#

EVENT#

VDDSPD

NC#1

NC#2

NC#/TEST

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

3

NP1

NP1

NP2

NP2

110

M_B_RAS# 5

113

115

114

121

73

74

101

103

102

104

11

28

46

63

136

153

170

187

200

202

198

199

197

201

77

122

125

75

76

81

82

87

88

93

94

99

100

105

106

111

112

117

118

123

124

2

3

8

9

13

14

19

20

25

26

31

32

37

38

43

44

48

49

54

55

60

61

65

66

71

72

127

128

133

134

138

139

144

145

150

151

155

156

161

162

167

168

172

173

178

179

184

185

189

190

195

196

205

206

M_B_WE# 5

M_B_CAS# 5

M_B_CS#0 5

M_B_CS#1 5

M_B_CKE0 5

M_B_CKE1 5

M_B_CLK0 5

M_B_CLK#0 5

M_B_CLK1 5

M_B_CLK#1 5

SMB_DATA 12,18,62,96

SMB_CLK 12,18,62,96

TS#_DIMM1_1

SB0_DIM0

SB1_DIM0

1D35V_S3

0D675V_VREF_S0

1D35V_S3

12

C1314

C1314

0D675V_VREF_S0

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

3D3V_S0

12

C1303

C1303

SCD1U16V2KX-L-GP

SCD1U16V2KX-L-GP

Layout Note:

Place these Caps near

SO-DIMMB.

SODIMM B DECOUPLING

12

12

C1320

C1320

EC1305

EC1305

12

C1315

C1315

12

12

C1307

C1307

EC1306

EC1306

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

SCD1U16V2KX-L-GP

SCD1U16V2KX-L-GP

SCD1U16V2KX-L-GP

SCD1U16V2KX-L-GP

12

12

C1318

C1318

C1321

C1321

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

12

C1316

C1316

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

12

C1317

C1317

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

SB1_DIM0

SB0_DIM0

12

FC1301

FC1301

SC100P50V2JN-3GP

SC100P50V2JN-3GP

RF

RF

12

12

C1308

C1308

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

12

C1319

C1319

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

Place these caps

close to VTT1 and

VTT2.

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

WE#

CK0

CK1

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

SDA

SCL

SA0

SA1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

SRN10KJ-5-G P

SRN10KJ-5-G P

12

FC1302

FC1302

SC10U25V5KX-GP

SC10U25V5KX-GP

C1309

C1309

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

RN1302

RN1302

1

2 3

12

RF

RF

12

C1310

C1310

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

FC1303

FC1303

SCD1U16V2KX-L-GP

SCD1U16V2KX-L-GP

3D3V_S0

4

DY

DY

Note:

SO-DIMMB SPD Address is 0xA4

SO-DIMMB TS Address is 0x34

SO-DIMMB is placed farther from

the Processor than SO-DIMMA

Thermal EVENT

TS#_DIMM1_1

12

12

FC1310

FC1310

RF

RF

12

FC1311

FC1311

FC1304

FC1304

SC10U25V5KX-GP

SC10U25V5KX-GP

SC100P50V2JN-3GP

SC100P50V2JN-3GP

SCD1U16V2KX-L-GP

SCD1U16V2KX-L-GP

RF

RF

DY

DY

R1302

R1302

10KR2J-L-GP

10KR2J-L-GP

1 2

3D3V_S0

2

1

Close DIMM2 VREF_CA pin

12

FC1320

FC1320

SCD1U25V2KX-L-GP

M_VREF_DQ_D IMM1

12

12

C1327

C1327

SCD1U16V2KX-L-GP

SCD1U16V2KX-L-GP

DY

DY

C1328

C1328

SC2D2U10V3ZY- 1GP

A A

SC2D2U10V3ZY- 1GP

5

4

SCD1U25V2KX-L-GP

DY

DY

12

12

FC1322

FC1322

FC1321

FC1321

SC100P50V2JN-3GP

SC100P50V2JN-3GP

SC10U25V5KX-GP

SC10U25V5KX-GP

RF

RF

RF

RF

Wistron Confidential document, Anyone can not

Duplicate, Modify, Forward or any other purpose

application without get Wistron permission

UMA

UMA

UMA

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin T ai Wu Rd., H sichih,

21F, 88, Sec.1, Hsin T ai Wu Rd., H sichih,

21F, 88, Sec.1, Hsin T ai Wu Rd., H sichih,

Taipei Hsie n 221, Taiwan, R.O.C.

Taipei Hsie n 221, Taiwan, R.O.C.

Title

Title

Title

DDR3-SODIMM2

DDR3-SODIMM2

DDR3-SODIMM2

Size Document Num ber Rev

Size Document Num ber Rev

Size Document Num ber Rev

A2

A2

A2

Thursday, Feb ruary 12, 2015

Thursday, Feb ruary 12, 2015

Thursday, Feb ruary 12, 2015

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet of

Taipei Hsie n 221, Taiwan, R.O.C.

Laduree-BDW 15.6"

Laduree-BDW 15.6"

Laduree-BDW 15.6"

1

13 102

13 102

13 102

1

1

1

5

4

3

VREF circuit -M1 (Voltage Driver Network) & M3 (Driven by Processor) Implementation

2

1

D D

C C

B B

Driven by process (PIN#AR51) Driven by process (PIN#AP51)

DDR_WR_VREF015 DDR_WR_VREF025

SA_DIMM_VREFDQ SB_DIMM_VREFDQ

DDR_WR_VREF01

12

C1401

C1401

SCD022U16V2KX-3GP

SCD022U16V2KX-3GP

+V_VREF_PATH1

12

R1403

R1403

24D9R2F-L-GP

24D9R2F-L-GP

Close to DIMM

1D35V_S3

12

R1406

R1406

1K8R2F-GP

DDR_WR_VREF01

DDR_WR_VREF02

R1408

R1408

1 2

2R2F-GP

2R2F-GP

R1416

R1416

1 2

4D99R2F-GP

4D99R2F-GP

12

1D35V_S3

12

12

1K8R2F-GP

R1412

R1412

1K8R2F-GP

1K8R2F-GP

R1415

R1415

1K8R2F-GP

1K8R2F-GP

R1419

R1419

1K8R2F-GP

1K8R2F-GP

M_VREF_DQ_DIMM0 M_VREF_CA_DIMM0

Close to DM

M_VREF_DQ_DIMM1

SODIMM1

SODIMM2

DDR_WR_VREF02

Close to DIMM

DDR_VREF_S3

1 2

DY

DY

R1405

R1405

0R2J-2-GP

0R2J-2-GP

12

C1402

C1402

SCD022U16V2KX-3GP

SCD022U16V2KX-3GP

+V_VREF_PATH2

12

R1404

R1404

24D9R2F-L-GP

24D9R2F-L-GP

1D35V_S3

12

R1407

R1407

1K8R2F-GP

1K8R2F-GP

12

R1413

R1413

1K8R2F-GP

1K8R2F-GP

0820-Anthony

R1422

R1422

1 2

2D7R2F-1-GP

2D7R2F-1-GP

+V_SM_VREF_CNT

12

C1403

C1403

SCD022U16V2KX-3GP

SCD022U16V2KX-3GP

+V_VREF_PATH3

12

R1414

R1414

24D9R2F-L-GP

24D9R2F-L-GP

+V_SM_VREF_CNT 5

Wistron Confidential document, Anyone can not

Duplicate, Modify, Forward or any other purpose

A A

5

4

3

2

application without get Wistron permission

UMA

UMA

UMA

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

M1 & M3 Implementation

M1 & M3 Implementation

M1 & M3 Implementation

Laduree-BDW 15.6"

Laduree-BDW 15.6"

Thursday, February 12, 2015

Thursday, February 12, 2015

Thursday, February 12, 2015

Laduree-BDW 15.6"

Taipei Hsien 221, Taiwan, R.O.C.

14 102

14 102

14 102

1

1

1

1

5

SSID = CPU

4

3

2

1

D D

C C

B B

3D3V_S0

RN1503

RN1503

SRN10KJ-L-GP

SRN10KJ-L-GP

1

2 3

RN1504

RN1504

SRN10KJ-6-GP

SRN10KJ-6-GP

1

2

3

4 5

R1523

R1523

10KR2J-L-GP

10KR2J-L-GP

R1524

R1524

10KR2J-L-GP

10KR2J-L-GP

4

8

7

6

12

12

DY

DY

INT_PIRQC#

ACCEL_INT

WIFI_RST#

DGPU_PWR_EN#

TP608TPAD14-OP-GP TP608TPAD14-OP-GP

3D3V_S0

INT_PIRQB#

R1525

R1525

10KR2J-L-GP

10KR2J-L-GP

MCP_GPIO90 20

INT_SERIRQ 20,24,88

SATA_LED# 19,63

eDP_BLCTRL_CPU52,55

eDP_BLEN_CPU52

eDP_VDDEN_CPU52

WIFI_RST#58

1

ACCEL_INT67

DGPU_PWR_EN#83

DGPU_PWROK24,73,82,83

GPU_EVENT#76

INT_PIRQD#20

EC_SCI#20,24

INT_PIRQB#

INT_PIRQC#

INT_PIRQD#

PCH_PME#

12

9 OF 19

9 OF 19

DDPB_AUXN

DDPC_AUXN

DDPB_AUXP

DDPC_AUXP

DDPB_HPD

DDPC_HPD

EDP_HPD

B9

C9

D9

D11

C5

B6

B5

A6

C8

A8

D6

C6

U6

N4

N2

AD4

U7

R5

CPU1I

CPU1I

B8

A9

P4

L1

L3

L4

EDP_BKLCTL

EDP_BKLEN

EDP_VDDEN

PIRQA#/GPIO77

PIRQB#/GPIO78

PIRQC#/GPIO79

PIRQD#/GPIO80

PME#

GPIO55

GPIO52

GPIO54

GPIO51

GPIO53

eDP SIDEBAND

eDP SIDEBAND

PCIE

PCIE

BROADWELL

BROADWELL

DISPLAY

DISPLAY

DDPB_CTRLCLK

DDPB_CTRLDATA

DDPC_CTRLCLK

DDPC_CTRLDATA

3D3V_S0

4

1

2 3

eDP_HPD_CPU

RN1506

RN1506

SRN2K2J-5-GP

SRN2K2J-5-GP

HDMI_CLK_CPU 54

HDMI_DATA_CPU 54

HDMI_DET_CPU 54

BROADWELL-1-GP

BROADWELL-1-GP

DY_LVDS

DY_LVDS

R1521

eDP_HPD_CPU

For Colay

A A

5

4

R1521

0R2J-2-GP

0R2J-2-GP

1 2

1 2

eDP

eDP

R1522 0R2J-2-GP

R1522 0R2J-2-GP

eDP_HPD_CPU_T 55

eDP_HPD_CPU_C 52

3

Wistron Confidential document, Anyone can not

Duplicate, Modify, Forward or any other purpose

application without get Wistron permission

UMA

UMA

UMA

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

CPU(EDP SIDEBAND/GPIO/DDI)

CPU(EDP SIDEBAND/GPIO/DDI)

CPU(EDP SIDEBAND/GPIO/DDI)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A4

A4

A4

Thursday, February 12, 2015

Thursday, February 12, 2015

Thursday, February 12, 2015

Date: Sheet of

Date: Sheet of

Date: Sheet of

2

Laduree-BDW 15.6"

Laduree-BDW 15.6"

Laduree-BDW 15.6"

15 102

15 102

15 102

1

1

1

1

5

4

3

2

1

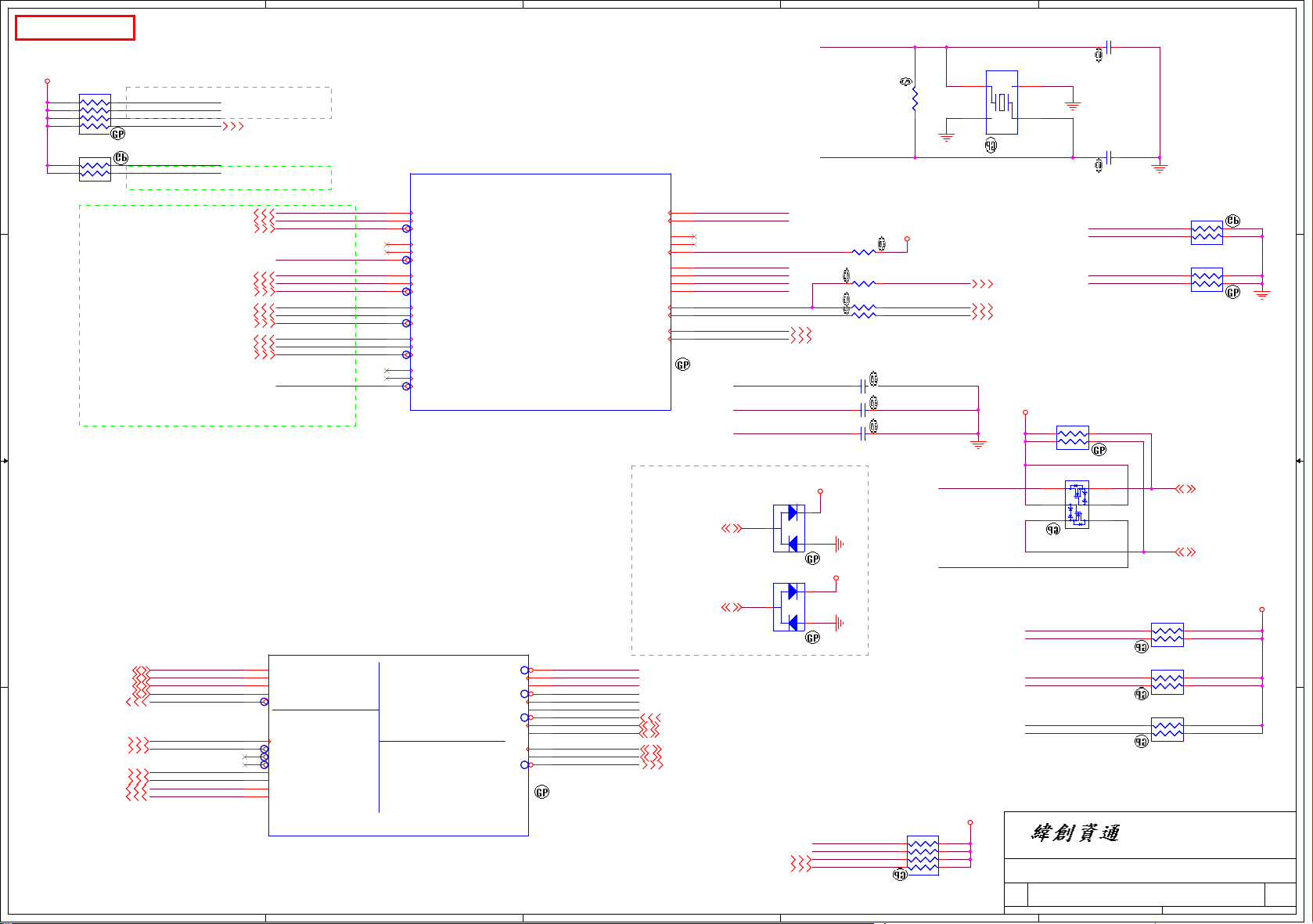

SSID = PCH

D D

LAN

C C

WLAN

Cardreader

PCIE_TX_LAN_N330

PCIE_TX_LAN_P330

PCIE_TX_W LAN_N458

PCIE_TX_W LAN_P458

PCIE_TX_CARD_N163

PCIE_TX_CARD_P163

dGPU

PCIE_RX_CPU_N330

PCIE_RX_CPU_P330

PCIE_RX_CPU_N458

PCIE_RX_CPU_P458

PCIE_RX_CPU_N163

PCIE_RX_CPU_P163

PCIE_RXN[5..8]73

PCIE_RXP[5..8]73

PCIE_TXP[5..8] 73

PCIE_TXN[5..8] 73

PCIE_RXN5

PCIE_RXP5

PCIE_TXN5

PCIE_TXP5 PCIE_TXP5_C

PCIE_RXN6

PCIE_RXP6

PCIE_TXN6

PCIE_TXP6 PCIE_TXP6_C

PCIE_RXN7

PCIE_RXP7

PCIE_TXN7

PCIE_TXP7 PCIE_TXP7_C

PCIE_RXN8

PCIE_RXP8

PCIE_TXN8

PCIE_TXP8 PCIE_TXP8_C

1D05V_VCCUSB3PLL_S0

C1605 SCD22U10V2KX-L1-GP

C1605 SCD22U10V2KX-L1-GP

1 2

PX

PX

C1606 SCD22U10V2KX-L1-GP

C1606 SCD22U10V2KX-L1-GP