Up to 6 GHz Medium Power

Silicon Bipolar Transistor Chip

Technical Data

AT-42000

Features

• High Output Power:

21.0 dBm Typical P

20.5 dBm Typical P

• High Gain at 1 dB

Compression:

15.0 dB Typical G

10.0 dB Typical G

• Low Noise Figure: 1.9 dB

Typical NFO at 2.0 GHz

• High Gain-Bandwidth

Product: 9.0 GHz Typical f

at 2.0␣ GHz

1 dB

at 4.0␣ GHz

1 dB

at 2.0␣ GHz

1 dB

at 4.0␣ GHz

1 dB

T

Description

Hewlett-Packard’s AT-42000 is a

general purpose NPN bipolar

transistor chip that offers excellent high frequency performance.

The 4 micron emitter-to-emitter

pitch enables this transistor to be

used in many different functions.

The 20 emitter finger interdigitated

geometry yields a medium sized

transistor with impedances that

are easy to match for low noise

and medium power applications.

This device is designed for use in

low noise, wideband amplifier,

mixer and oscillator applications

in the VHF, UHF, and microwave

frequencies. An optimum noise

match near 50 Ω up to 1 GHz ,

makes this device easy to use as a

low noise amplifier.

The AT-42000 bipolar transistor is

fabricated using Hewlett-Packard’s

10 GHz f

(SAT) process. The die is nitride

passivated for surface protection.

Excellent device uniformity,

performance and reliability are

produced by the use of ionimplantation, self-alignment

techniques, and gold metalization

in the fabrication of this device.

The recommended assembly

procedure is gold-eutectic die

attach at 400oC and either wedge

or ball bonding using 0.7 mil gold

wire. See APPLICATIONS section,

“Chip Use”.

Self-Aligned-Transistor

T

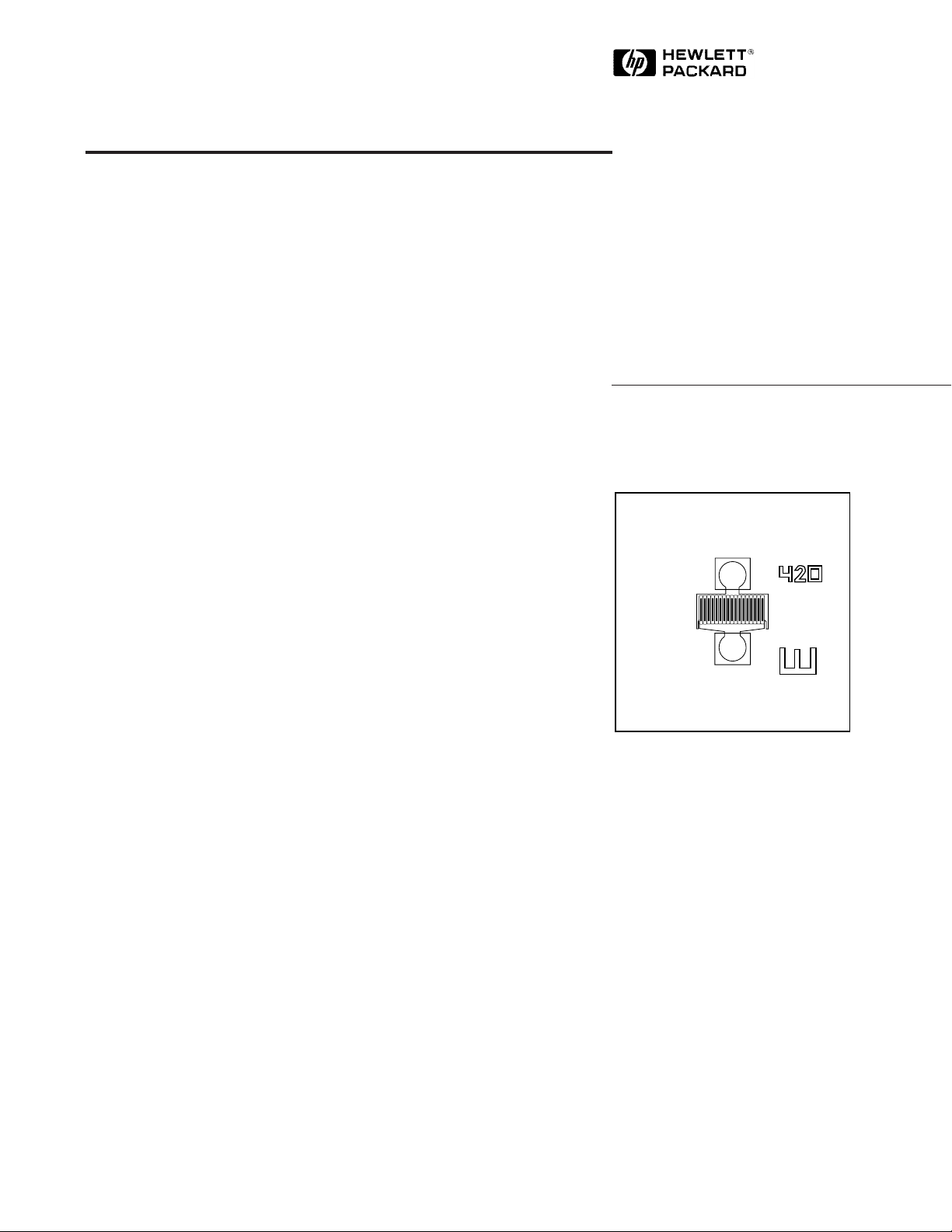

Chip Outline

4-149

5965-8909E

AT-42000 Absolute Maximum Ratings

Absolute

Symbol Parameter Units Maximum

V

V

V

T

EBO

CBO

CEO

I

C

P

T

STG

T

j

Emitter-Base Voltage V 1.5

Collector-Base Voltage V 20

Collector-Emitter Voltage V 12

Collector Current mA 80

Power Dissipation

[2,3]

m W 600

Junction Temperature °C 200

Storage Temperature °C -65 to 200

Part Number Ordering Information

Part Number Devices Per Tray

AT-42000-GP4 100

[1]

Thermal Resistance

[2,4]

θjc = 70°C/W

Notes:

1. Permanent damage may occur if

any of these limits are exceeded.

2. T

Mounting Surface

3. Derate at 14.3 mW/° C for

T

Mounting Surface

4. The small spot size of this technique results in a higher, though

more accurate determination of θ

than do alternate methods. See

MEASUREMENTS section

“Thermal Resistance” for more

information.

= 25°C.

> 158° C.

:

jc

Electrical Specifications, T

Symbol Parameters and Test Conditions

|S

|2Insertion Power Gain; VCE = 8 V, IC = 35 mA f = 2.0 GHz dB 11.5

21E

= 25° C

A

[1]

Units Min. Typ. Max.

f = 4.0 GHz 5.5

P

1 dB

Power Output @ 1 dB Gain Compression f = 2.0 GHz dBm 21.0

VCE = 8 V, IC = 35 mA f= 4.0 GHz 20.5

G

1 dB

1 dB Compressed Gain; VCE = 8 V, IC = 35 mA f = 2.0 GHz dB 15.0

f = 4.0 GHz 10.0

NF

Optimum Noise Figure: VCE = 8 V, IC = 10 mA f = 2.0 GHz dB 1.9

O

f = 4.0 GHz 3.0

G

A

Gain @ NFO; VCE = 8 V, IC = 10 mA f = 2.0 GHz dB 14.0

f = 4.0 GHz 10.5

f

T

h

FE

I

CBO

I

EBO

C

CB

Notes:

1.

RF performance is determined by packaging and testing 10 devices per wafer

2. For this test, the emitter is grounded.

Gain Bandwidth Product: VCE = 8 V, IC = 35 mA GHz 9.0

Forward Current Transfer Ratio; VCE = 8 V, IC = 35 mA — 30 150 270

Collector Cutoff Current; V

Emitter Cutoff Current; V

Collector Base Capacitance

= 8 V µA 0.2

CB

= 1 V µA 2.0

EB

[2]

: VCB = 8 V , f = 1 MH z pF 0.23

.

4-150

Loading...

Loading...