Fairchild Semiconductor 100395QCX, 100395QC, 100395CW Datasheet

© 1999 Fairchild Semiconductor Corporation DS010651 www.fairchildsemi.com

February 1990

Revised November 1999

100395 Low Power 9-Bit ECL-to-TTL Translator with Registers

100395

Low Power 9-Bit ECL-to-TTL Translator with Registers

General Description

The 100395 is a 9-b it tra nslator for con verti ng F1 00K l ogic

levels to TTL logic levels. A HIGH on the output enable

(OE

) holds the TTL outputs in a high impedance state. Two

separate clock inputs are available for multiplexing and

system level testing.

The 100395 is desi gned with TTL 64 mA o utputs for bus

driving capability. All in puts have 50 kΩ pu ll do wn r es is t or s.

When the inputs are either un connected or at the same

potential, the outputs will go LOW.

Features

■ 64 mA IOL drive capability

■ 2000V ESD protection

■ −4.2V to −5.7V operating range

■ Registered outputs

■ TTL outputs

Ordering Code:

Devices also availab le in Tape and Reel. Specify by appending th e s uffix let t er “X” to the ordering code.

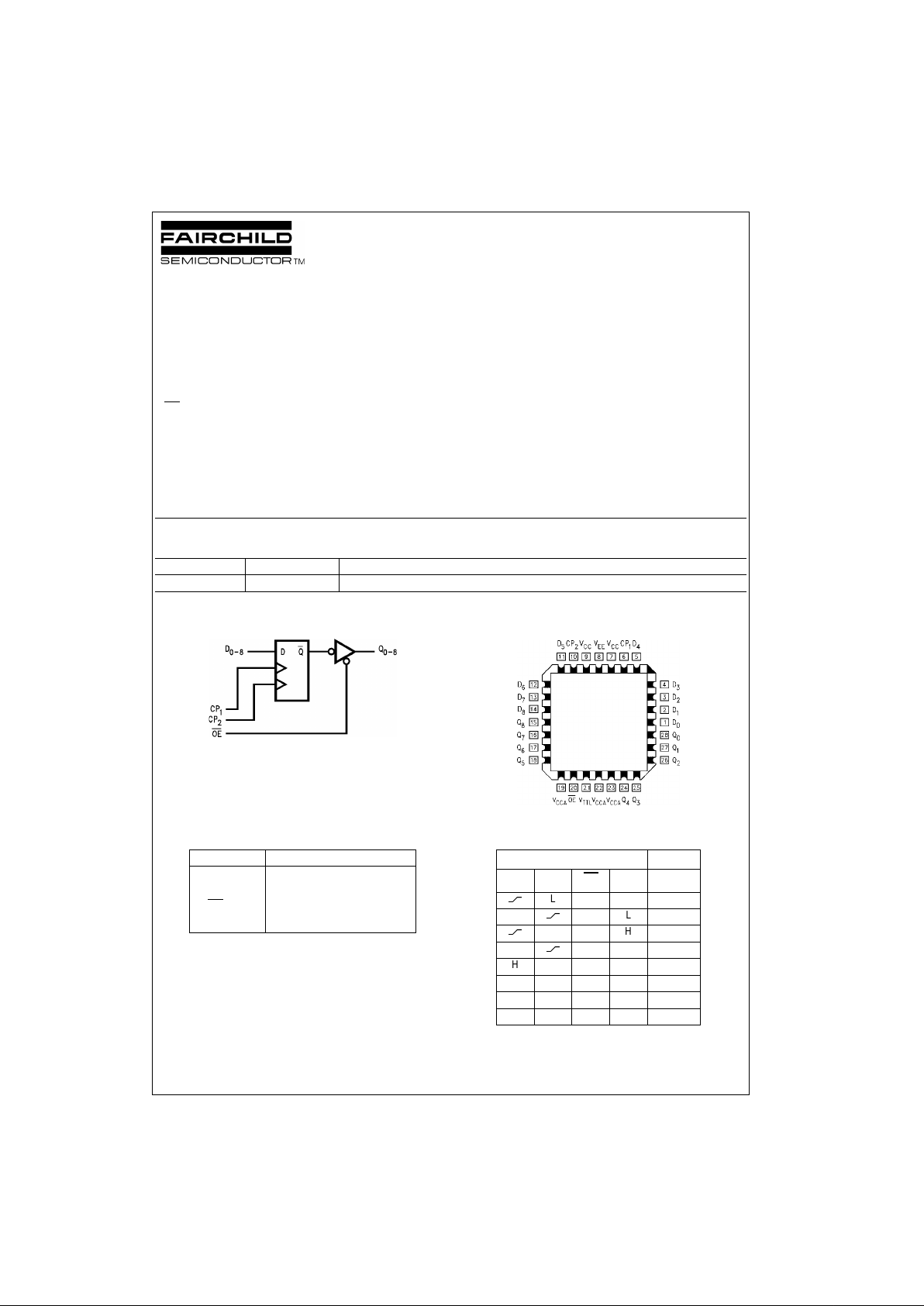

Logic Symbol

Pin Descriptions

Connection Diagram

Truth Ta ble

H = HIGH Voltage Level Z = High Impedance

L = LOW Voltage Level NC = No Change

X = Don't Care

Order Number Package Number Package Description

100395QC V28A 28-Lead Plastic Lead Chip Carrier (PLCC), JEDEC MO-047, 0.450 Square

Pin Names Description

D

0–D8

Data Inputs (ECL)

Q

0–Q8

Data Outputs (TTL)

OE

Output Enable (ECL)

CP

1

, CP2Clock Inputs (ECL)

Inputs Outputs

CP

1

CP2OE D

N

Q

N

LLL L

L

LL L

LLH H

L

LH H

HXXX NC

XHXX NC

LLXXNC

XXHX Z

www.fairchildsemi.com 2

100395

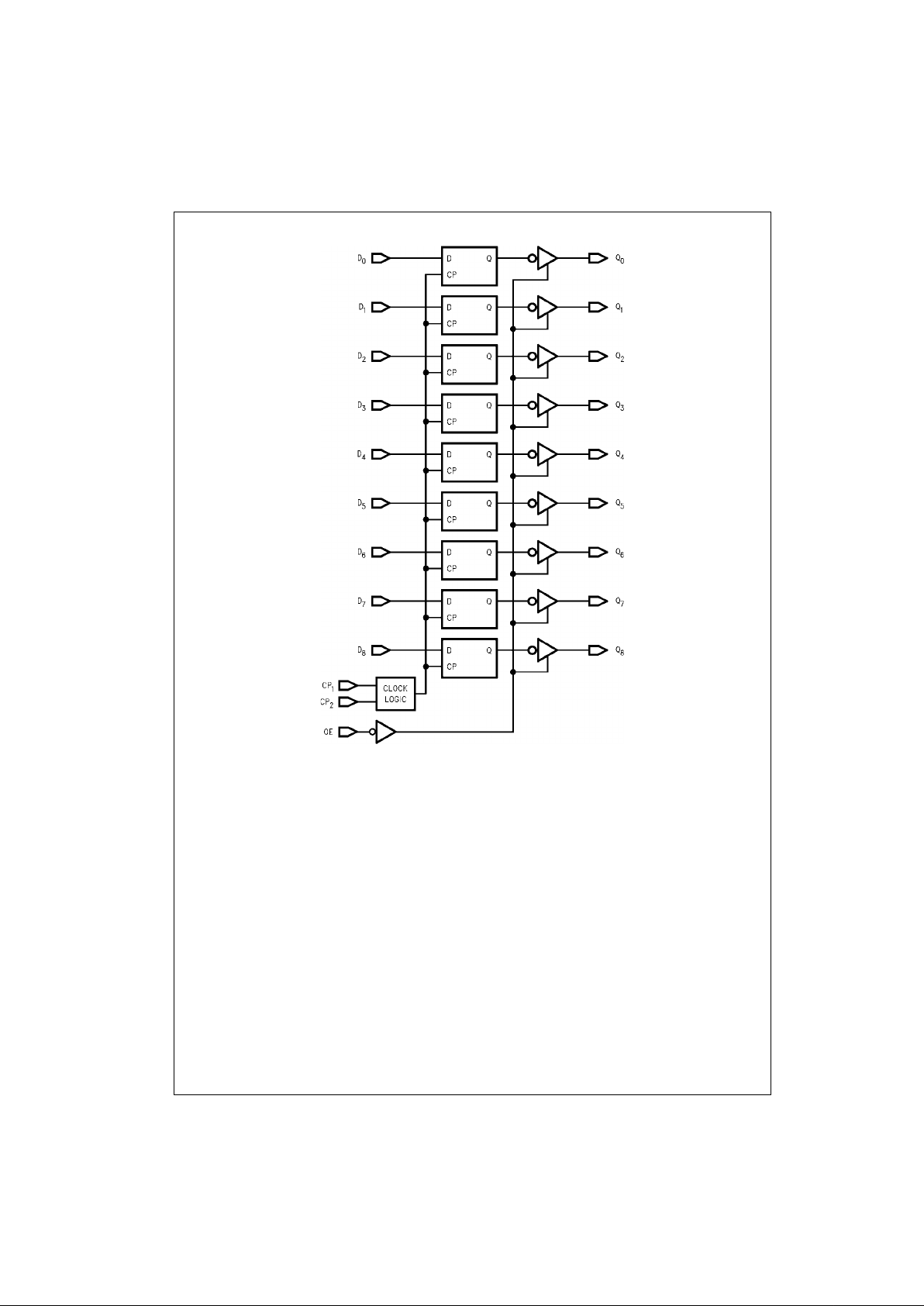

Logic Diagram

Loading...

Loading...