Page 1

Elenberg LVD-1902 SERVICE MANUAL

CONTENT

PART 1:

Brief Introduction Of The LVD-1902

◆ Schematic Diagram

◆ Printed Circuit

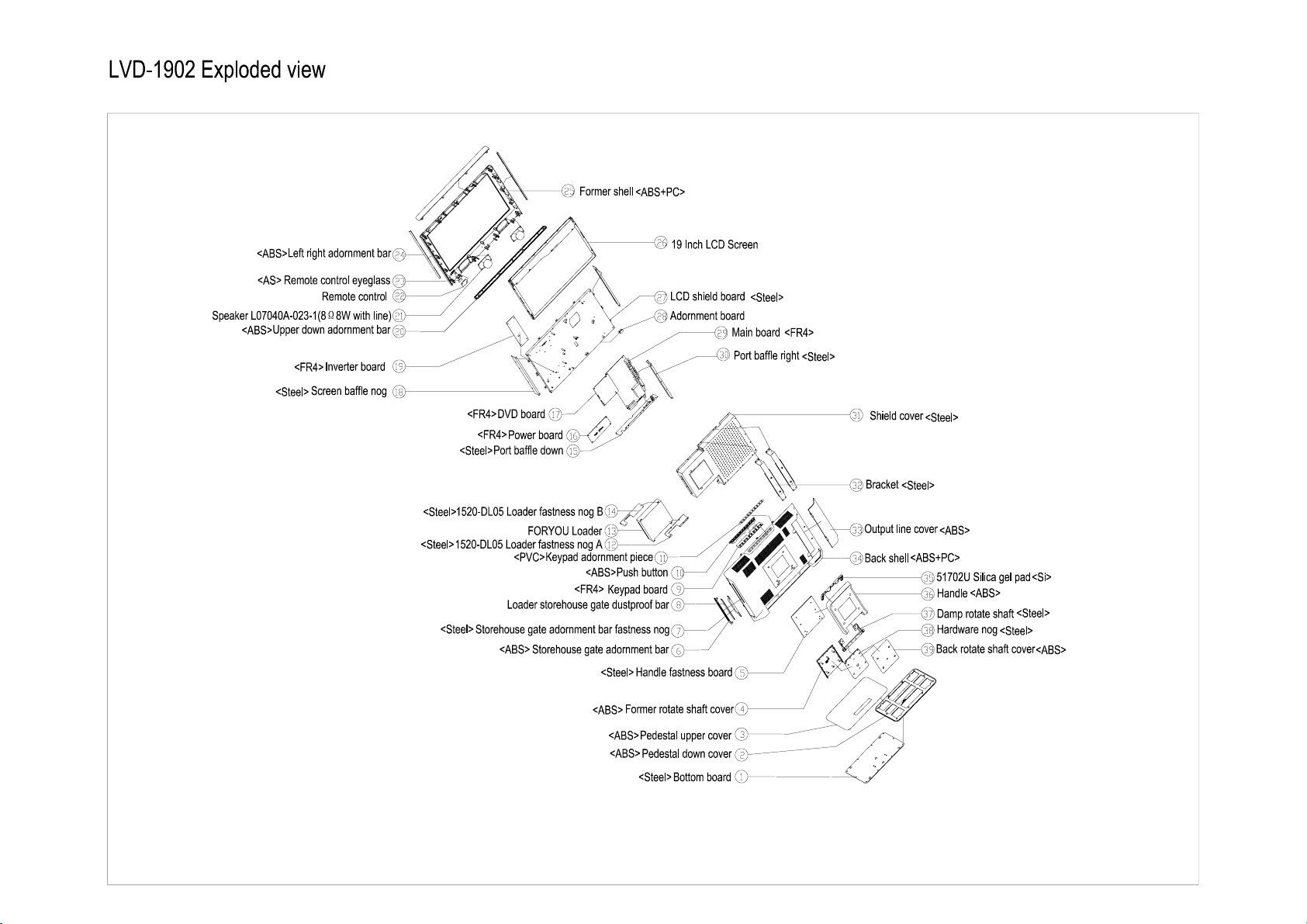

PART 2: Exploded View

PART 3:Key Ics And Assemblies

PART 4:

◆

◆

◆

Detailed Circuit

Main Board

DVD Board

HI-voltage Board

PART 5: Parts List

PART6:

Debug Procedure

Page 2

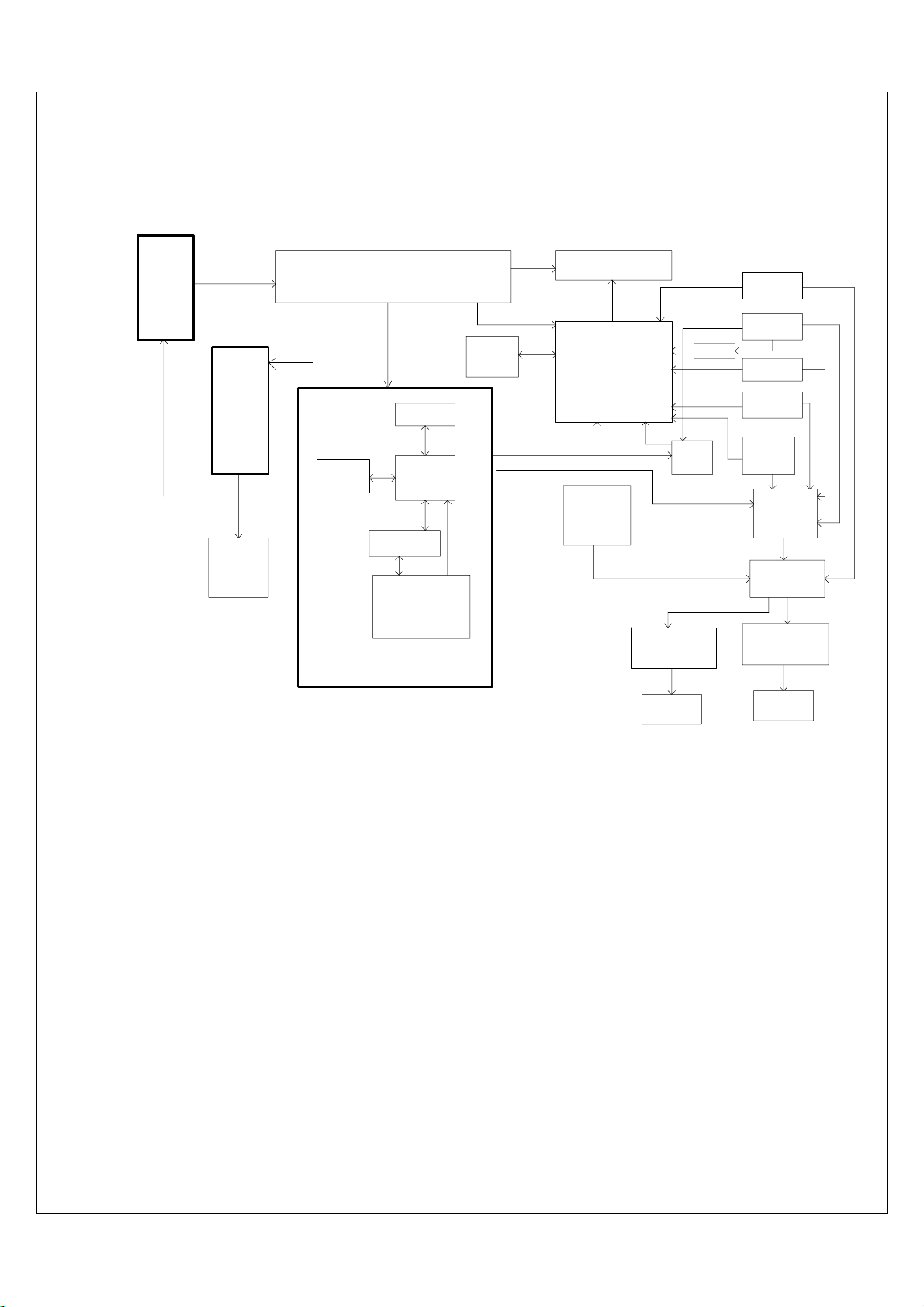

Part 1 Brief Introduction Of TheLVD-1902

Schematic Diagram

DIANYUAN

POWER SOURCE 100---240V AC 47HZ--63HZ 1.5A MAX

16V

IN

INVERTER

4 CCFL

BACKLIGHT

POWER

SUPPLY:16V

16V

K4S641632H

SD-RAM

DVD

、5V、

16V 5V

MOTOR DRIVER

3.3V、1.8V

MX29LV160

FLASH

MTK1389DE

DECODER

BA5954

LOADER

AT49F040A

FLASH

3.3V

YPBPR

L R

5V

1.8V

PANEL

LVDS

FLI8125

DECODER

AND

SCALER

CVBS

TUNER

RGB/YUV

SIF

BH3547

AMPLIFIER

PHONE

RGB/CVBS

CVBS

FSAV330

VEDIO

SWITCH

R G B

74LVC125

Y C

YPBPR

SCART

PC IN

HSI VSI

AV IN

SVHS IN

YPBPR

L\R

IN

AUDIO SWITCH

L R

VHC4052

L R

MPS3415

TPA3008

AMPLIFIER

SPEAKER

L R

L R

L R

Page 3

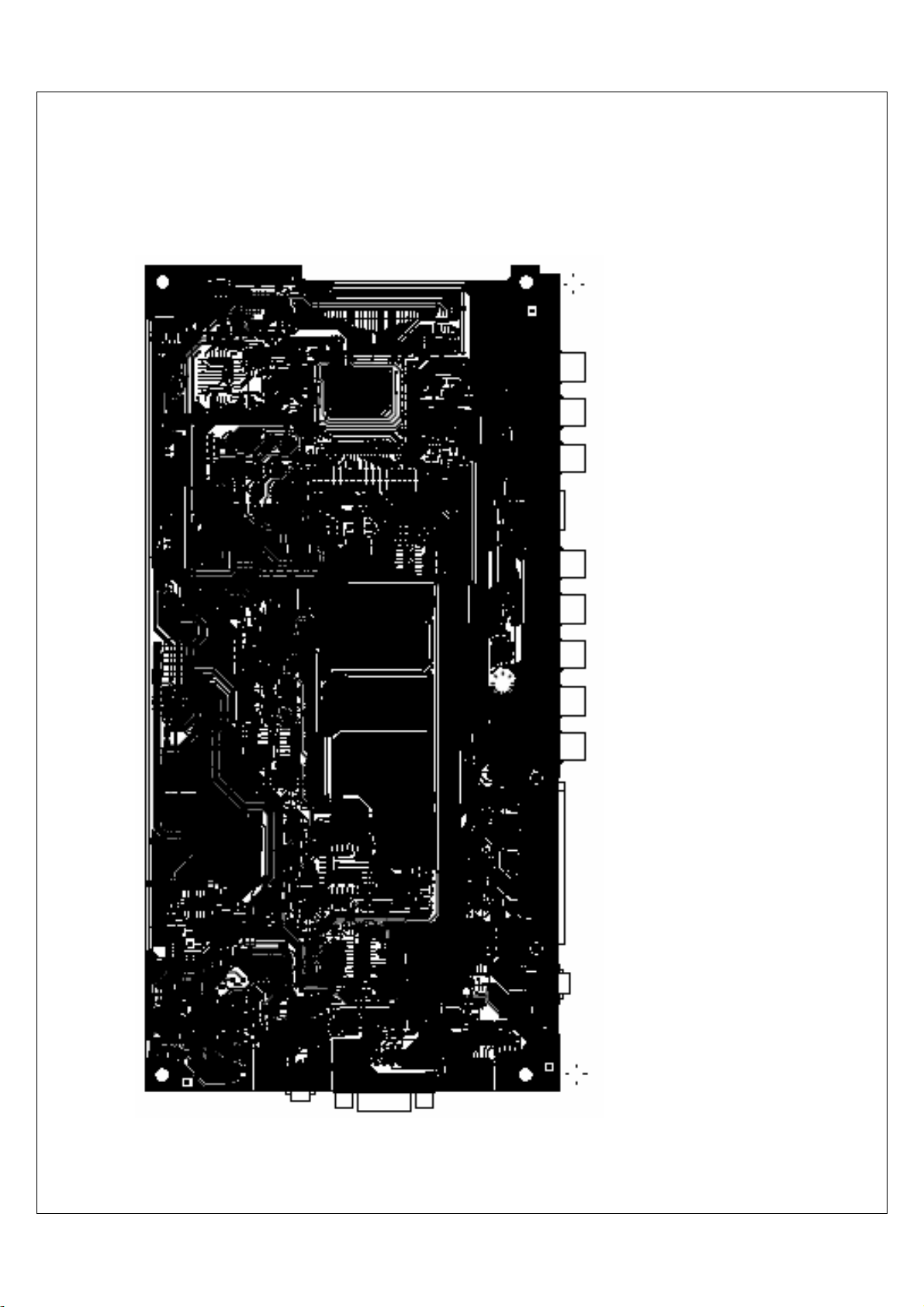

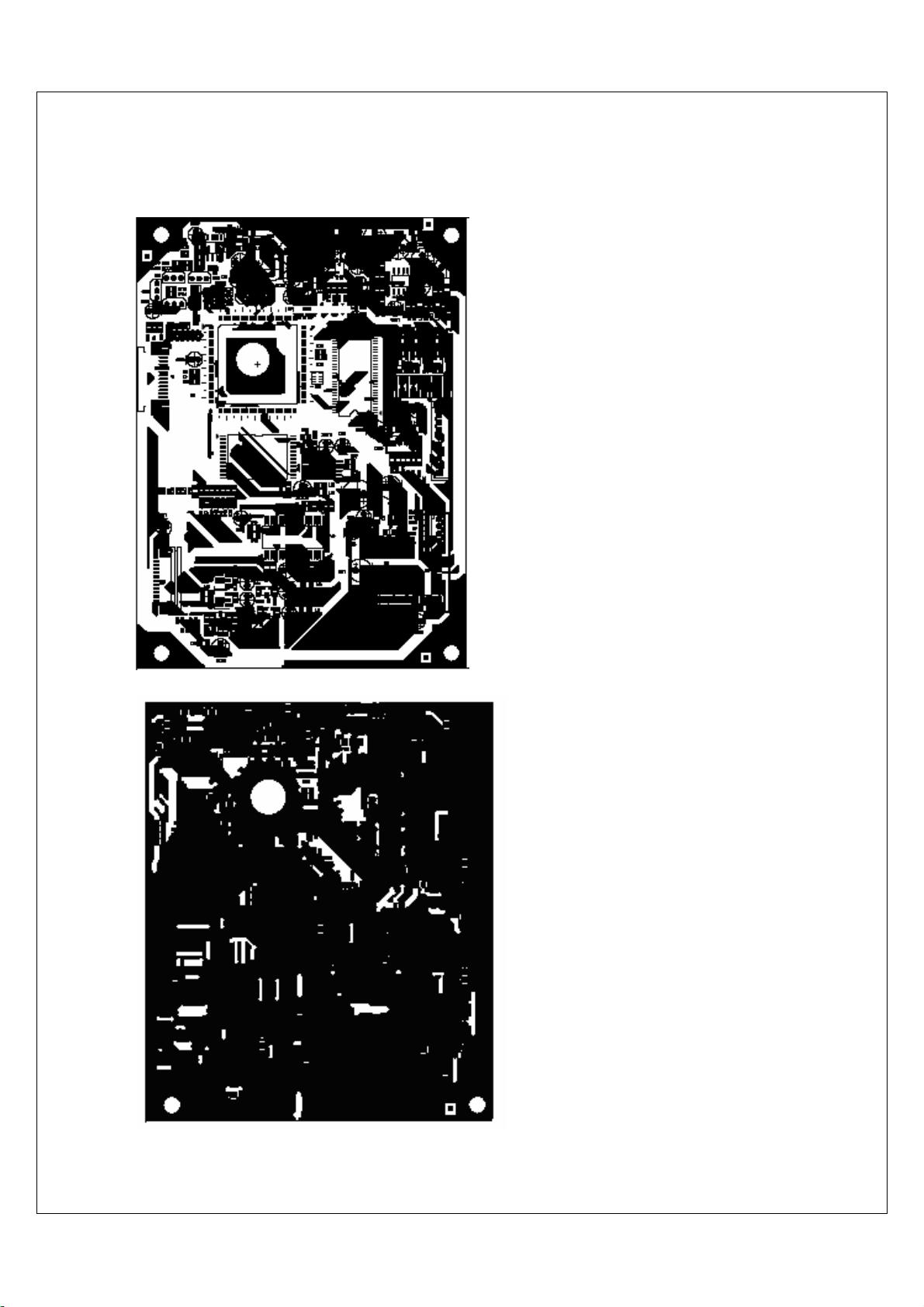

1. Main board

A: TOP LAYER

Printed Circuit

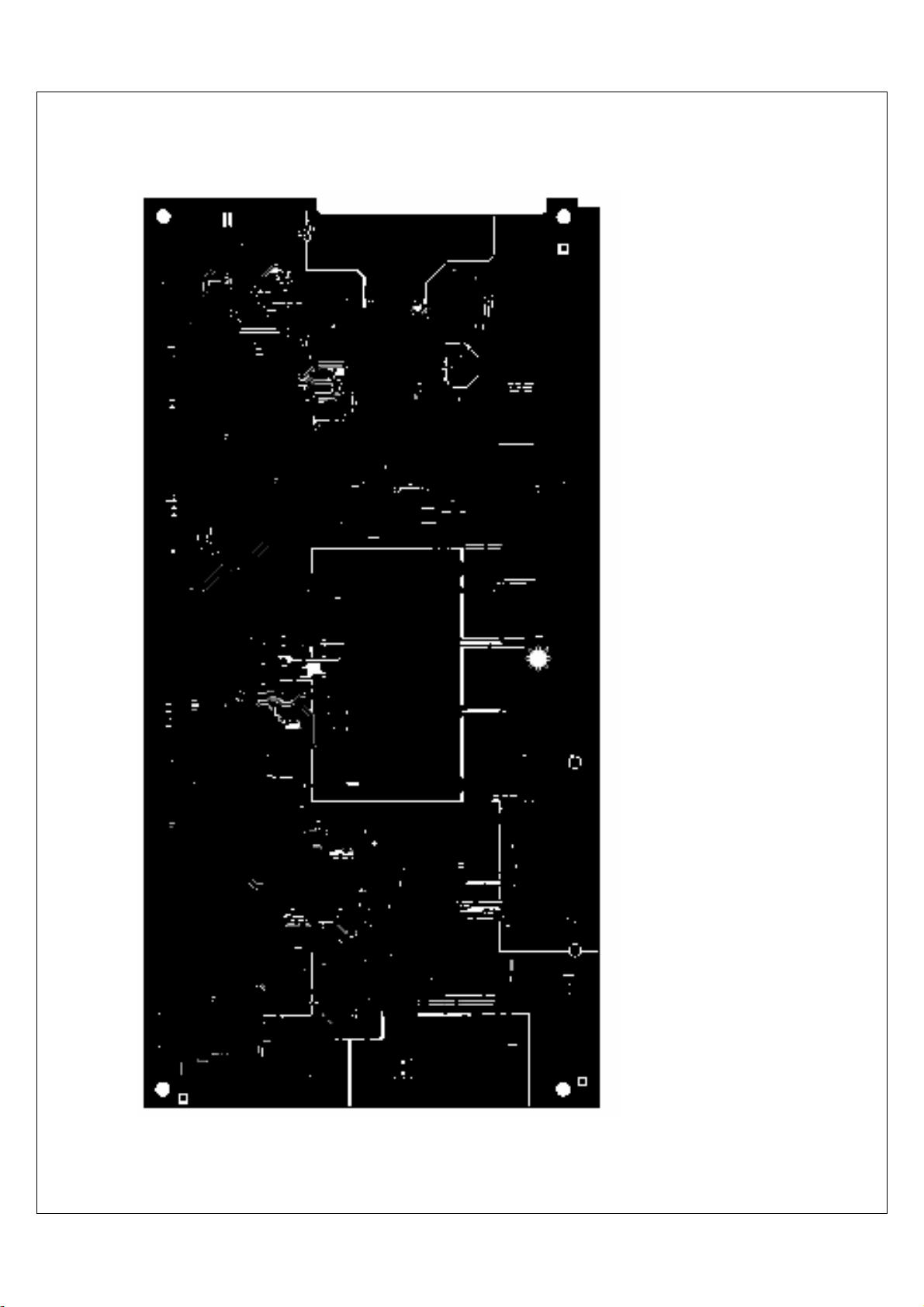

Page 4

B: BOTTOM LAYER

Page 5

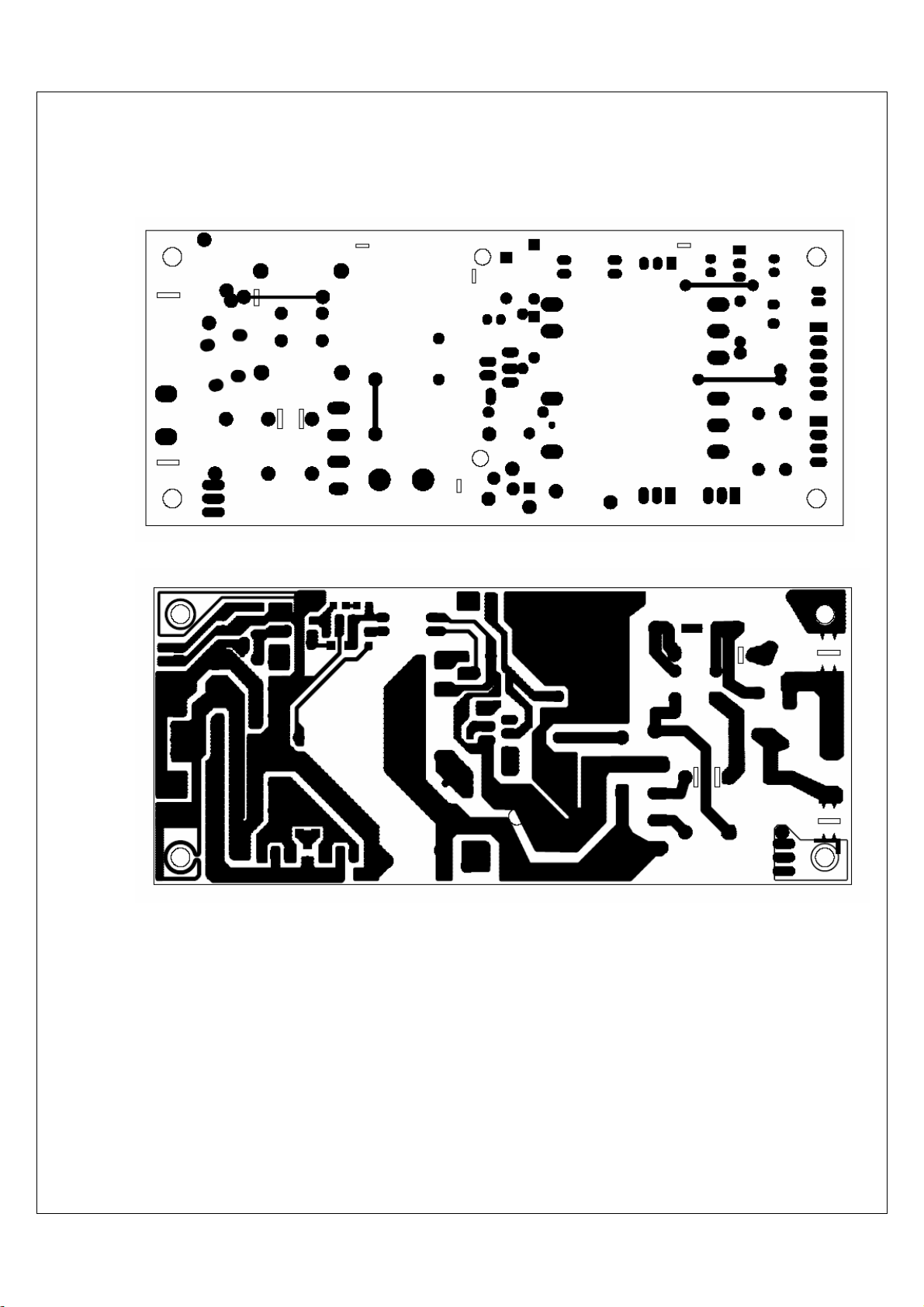

2. DVD board

A: TOP LAYER

B: BOTTOM LAYER

Page 6

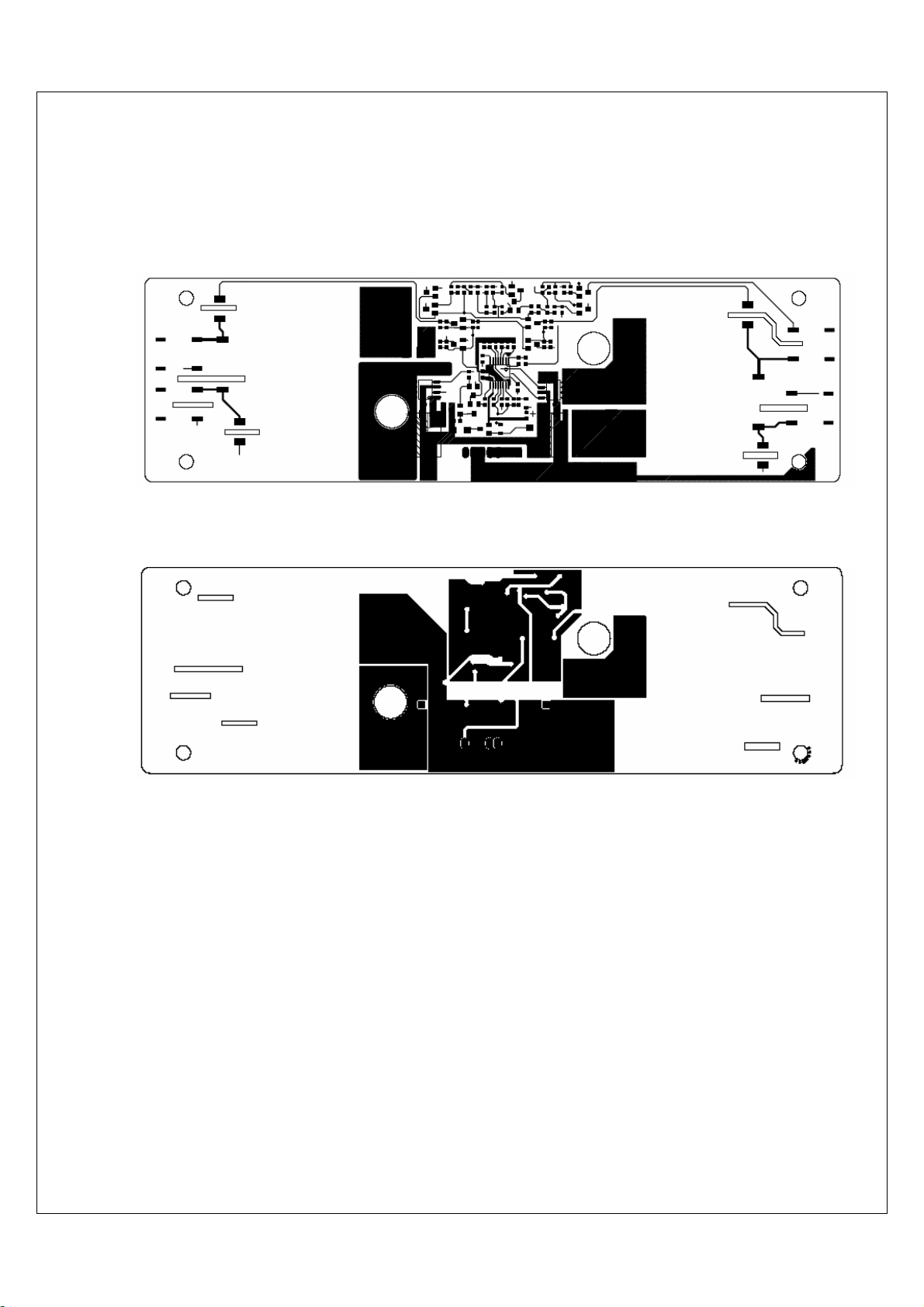

3. Power board

A: TOP LAYER

B: BOTTOM LAYER

Page 7

4. Inverter board

A: TOP LAYER

B: BOTTOM LAYER

Page 8

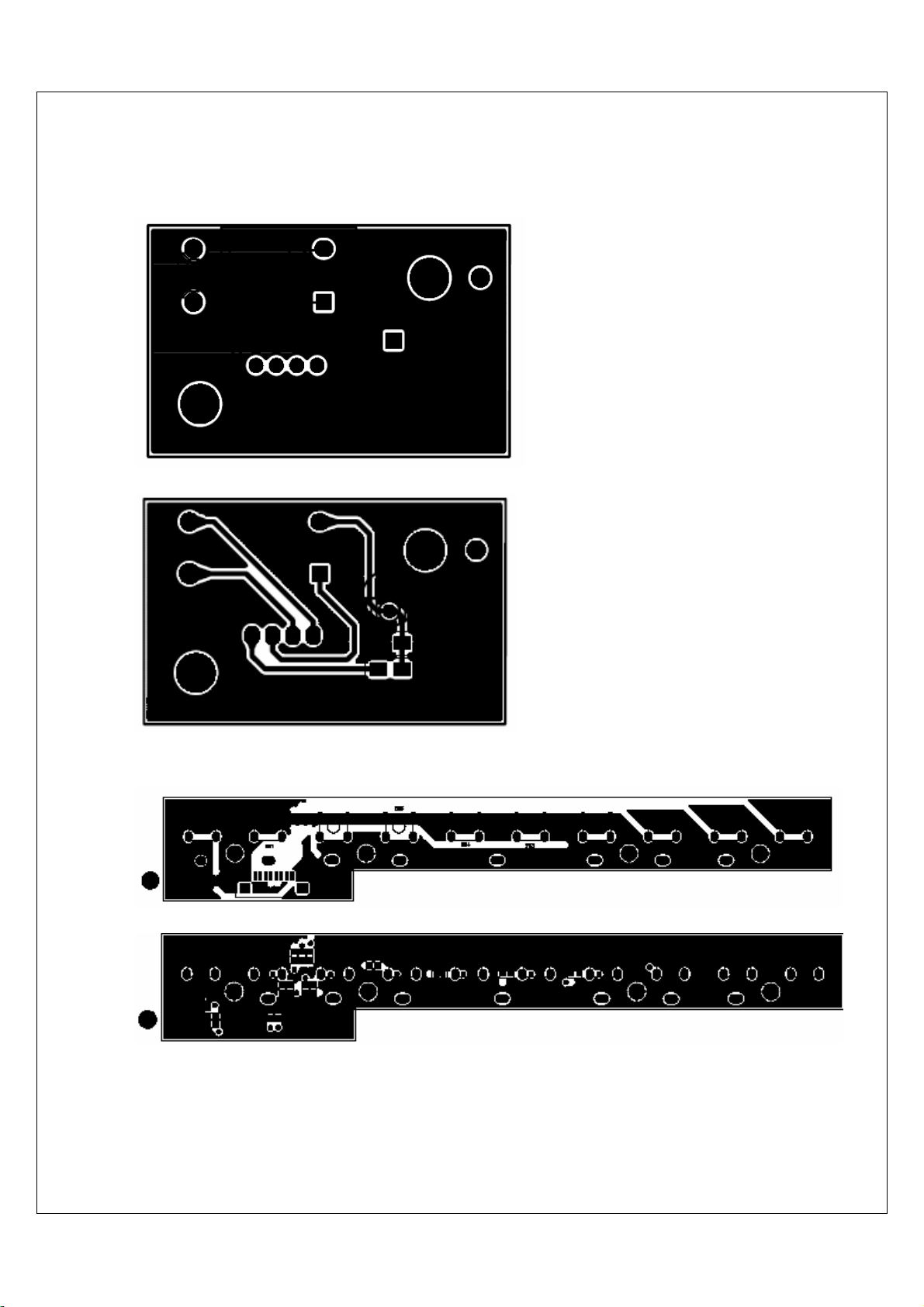

5. Remote Control Board

A: TOP LAYER

B: BOTTOM LAYER

6. Key board

A: TOP LAYER

B: BOTTOM LAYER

Page 9

Exploded vi ew

Part 2 Exploded view

Page 10

Page 11

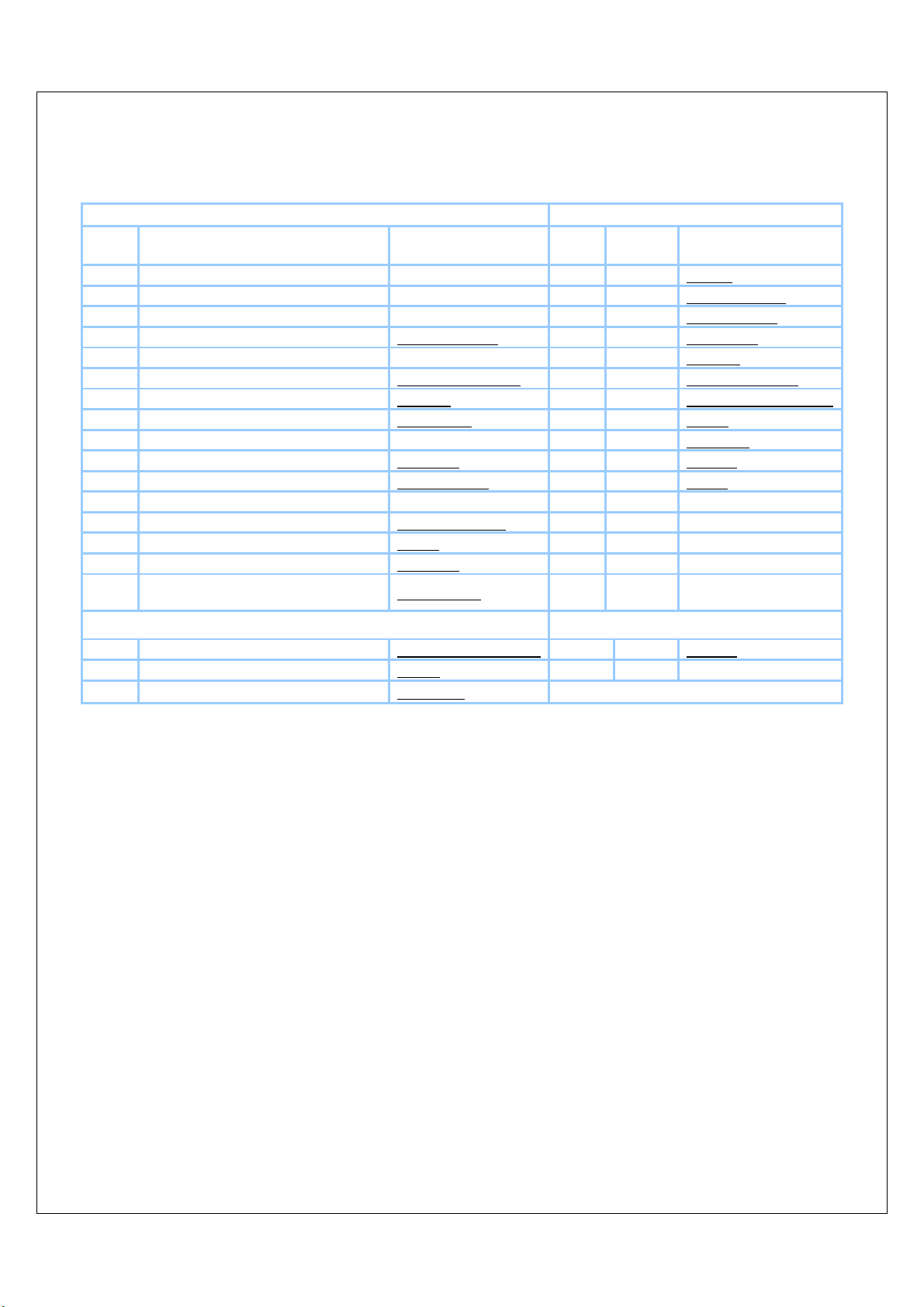

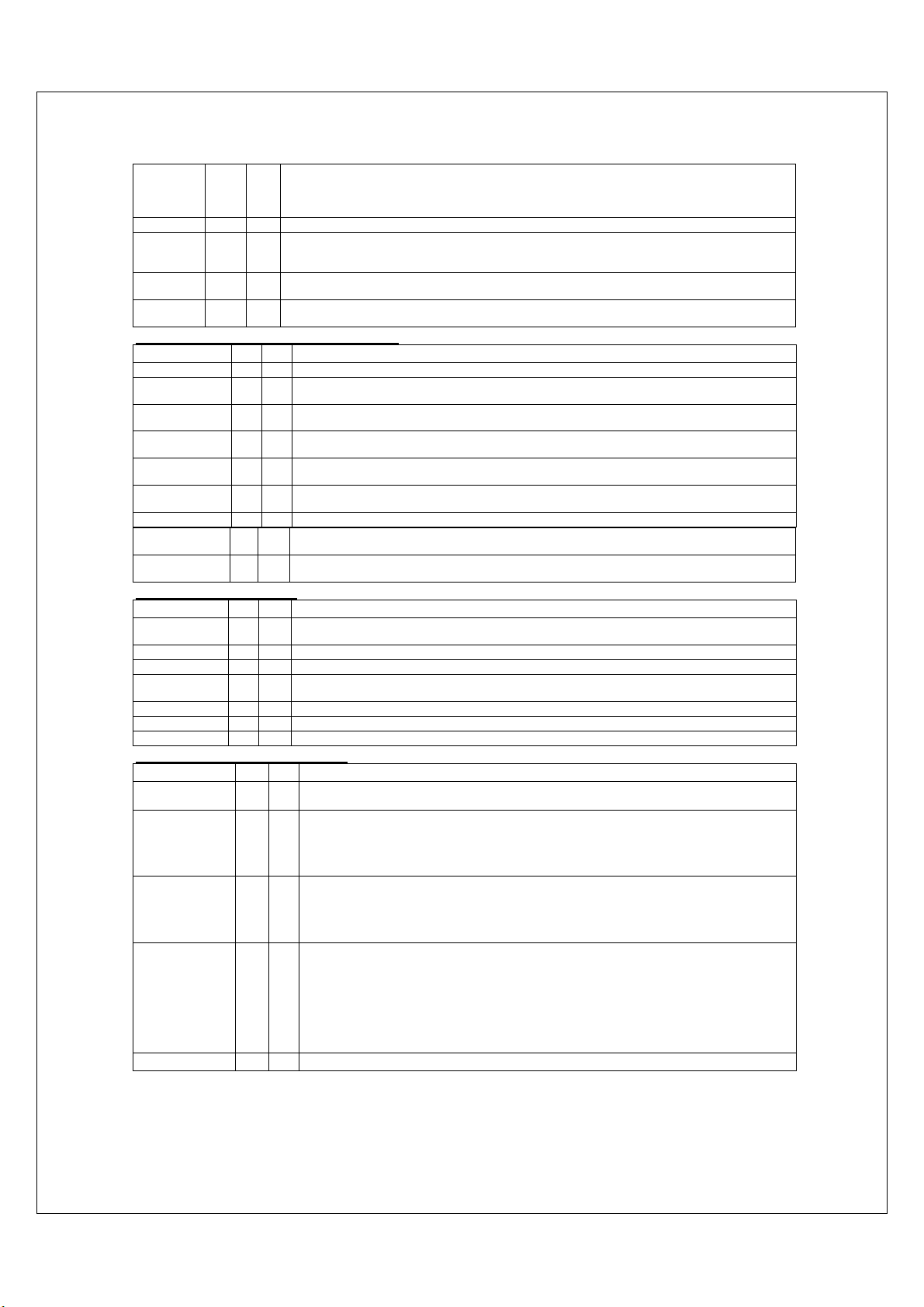

Part 3 Key ICs And Assemblies

On Main Board On DVD board

Serial

No

Position Type

1 3U7 78L09 1 U2 BA033

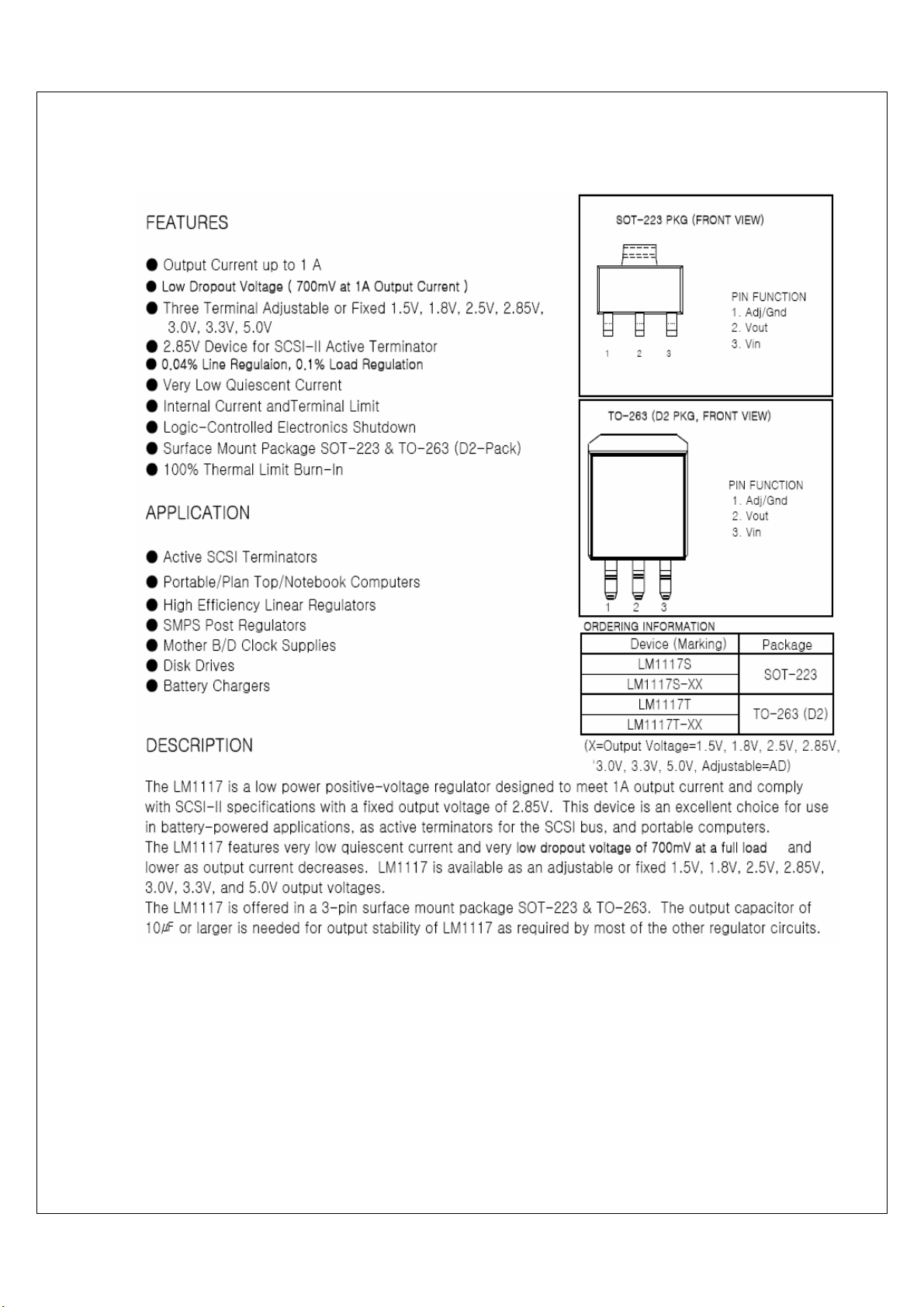

2 4U5 LM1117MPX-3.3V 2 U3 AZ1117H-1.8V

3 2U3 4U6 FDS9435 3 U6 MT1389DE/E

4 4U2 AIC1084(3.3V) 4 U4 BA5954FP

5 4U1 TL494C 5 U5 BA6287

6 4U3 LM1117DTX-1.8V 6 U8 IS42S16400B-7T

7 3U4 CD4052 7 U9 MX29LV160BBTC-70

8 3U1 MSP3415G 8 U7 24C16

9 1U4 AT24C32AN 9 U11 NJM4558

10 1U1 FSAV330 10 U10 CS4344

11 2U1 AT49BV040B 11 U1 78L05

12 2U5 FLI8125-LF

13 3U6 TPA3008D2PHP

14 1U3 24C02

15 3U9 BH3547F

16

1U7 1U6 1U8 1U9 1U11 1U12 1U13

1U15

PESD5V0L5

On Power Board On Inverter Board

1 U5 FSCM0765RGWDTU 1 1C1 Bit3193

2 U2 PC817

3 U3 KA431AZ

Serial

no

Position Type

Page 12

ICS ON MAIN BOARD

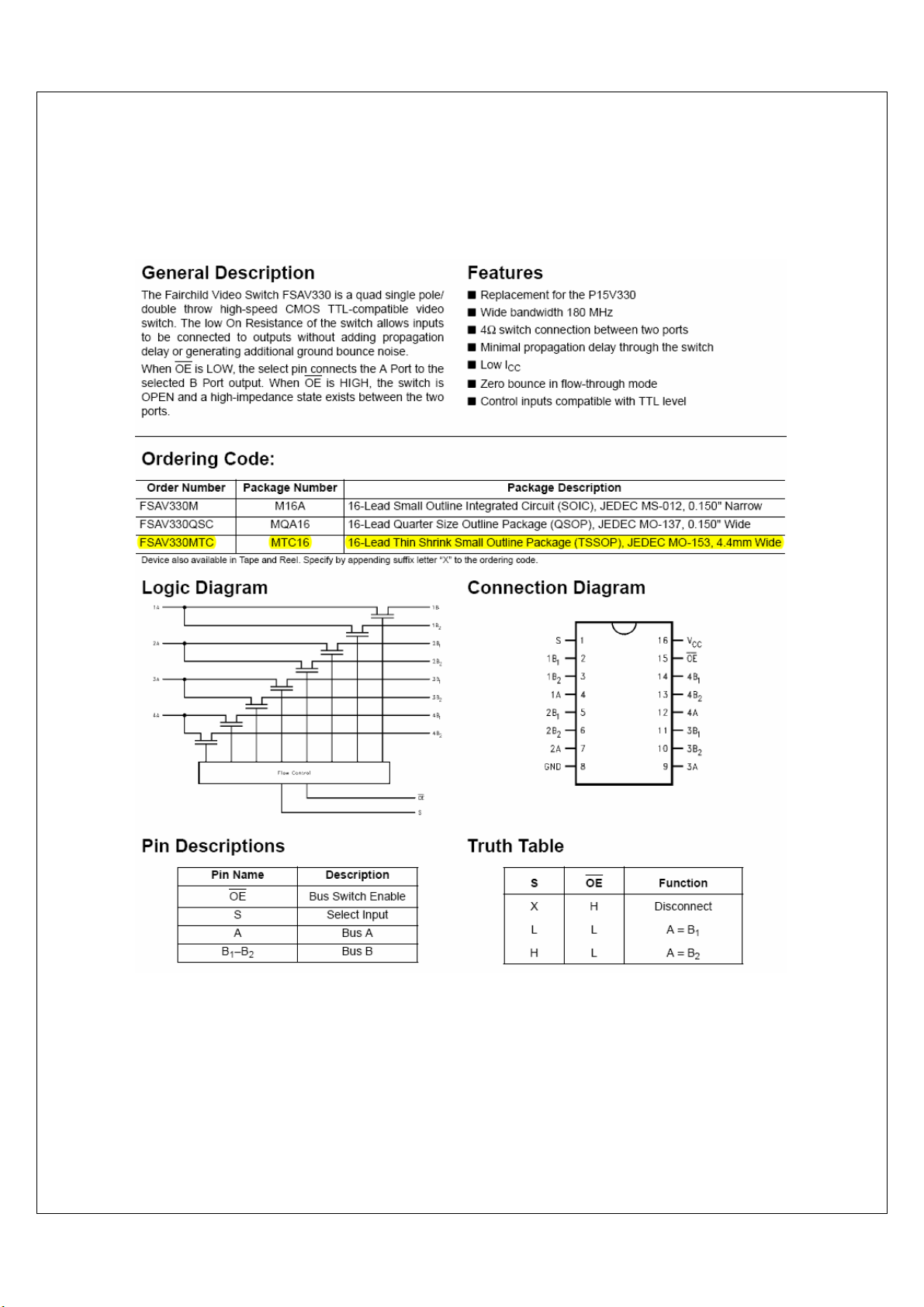

1. FSAV330

Low On Resistance Quad SPDT Wide Bandwidth Video Switch

Page 13

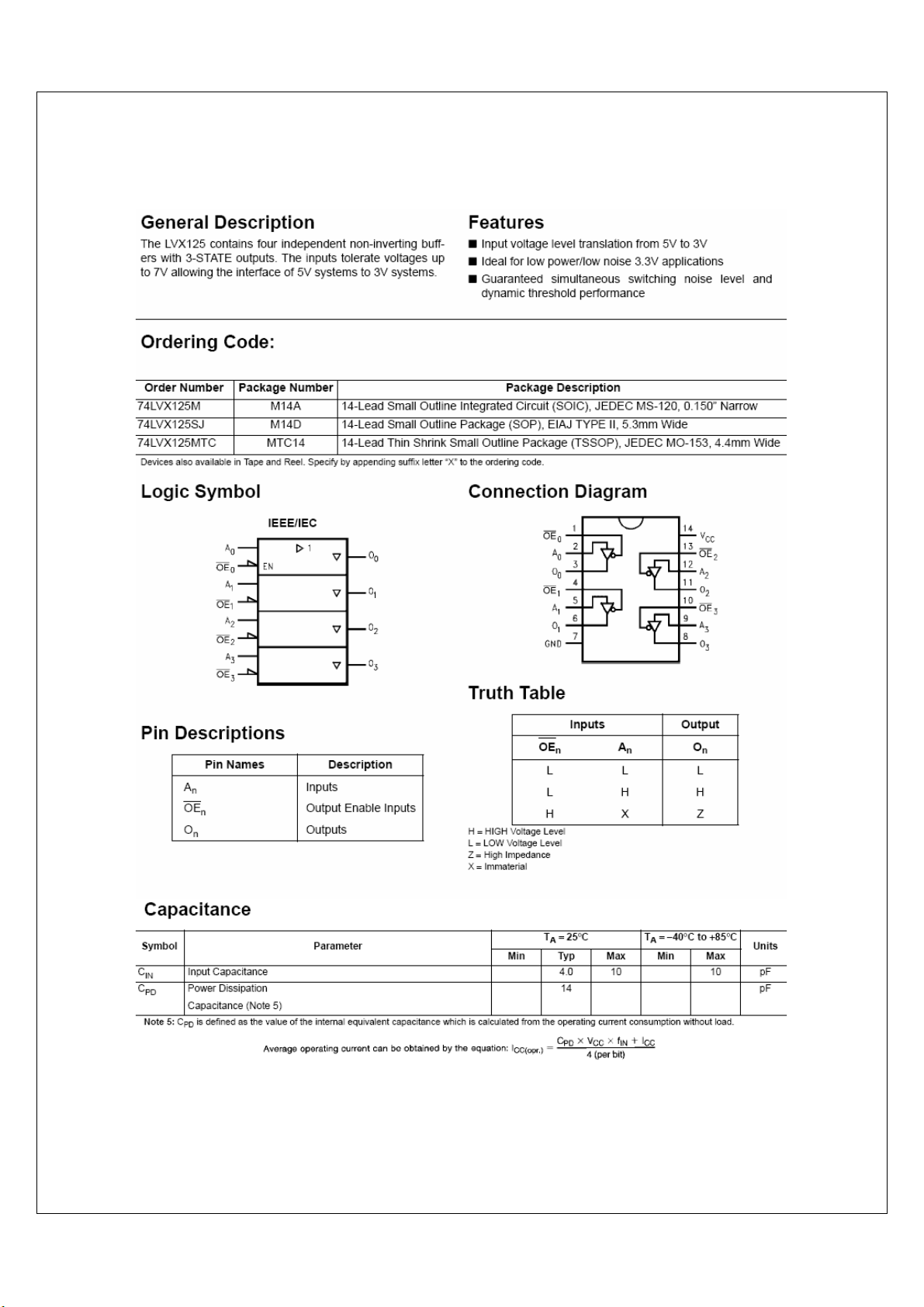

2. 74LVX125

Low Voltage Quad Buffer with 3-STATE Outputs.

Page 14

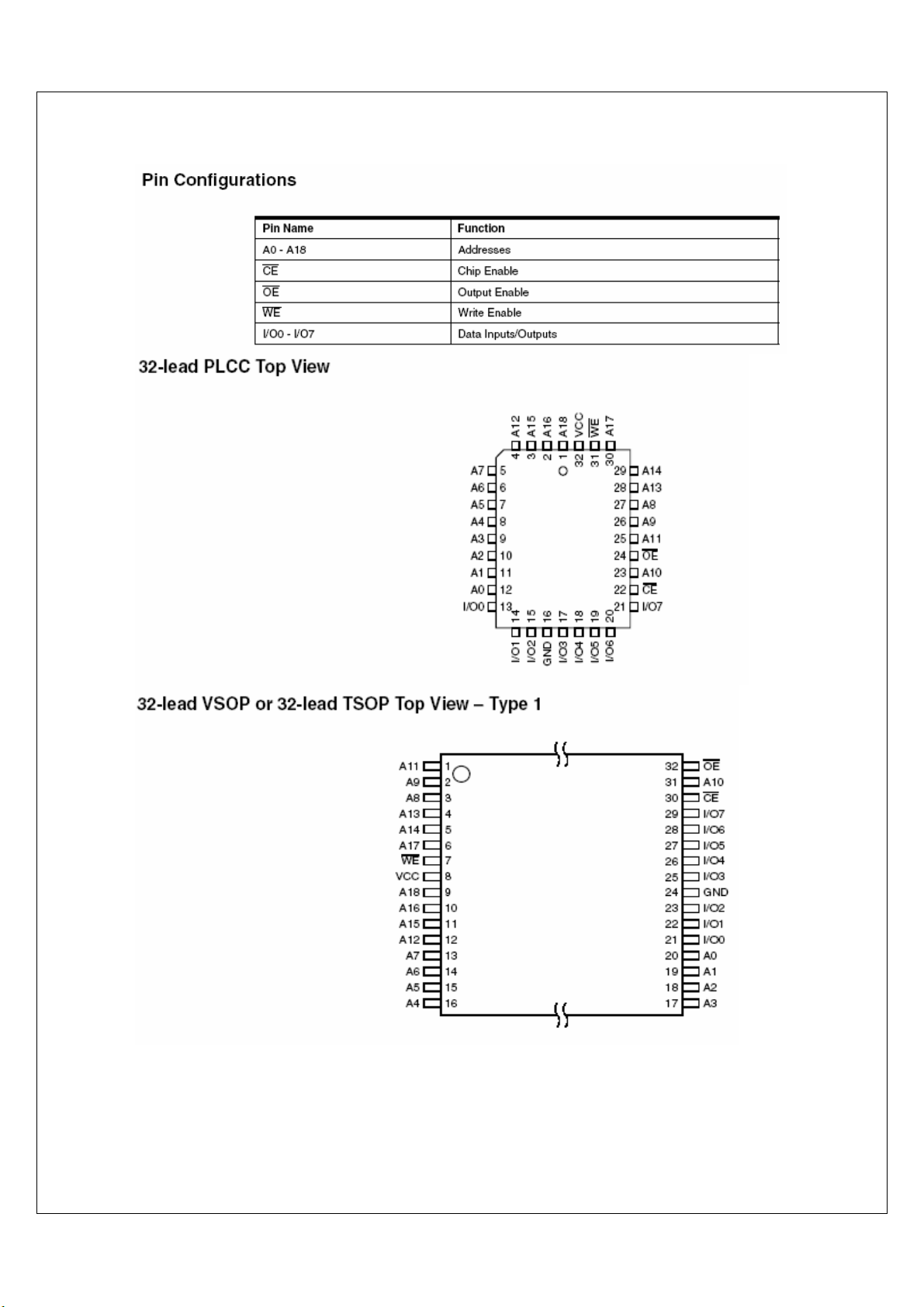

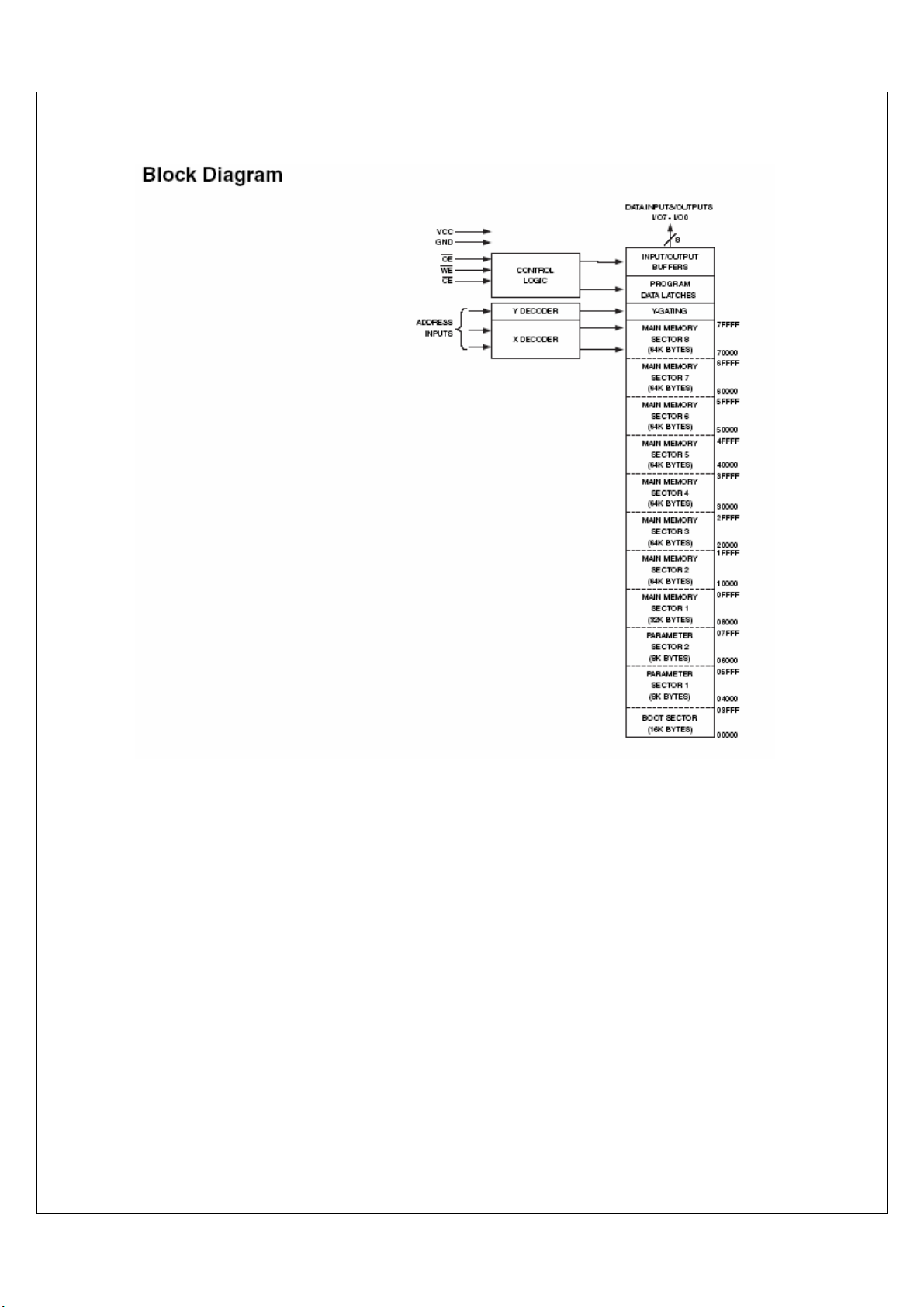

3. A T49BVO40B

Page 15

Page 16

Page 17

4. LM1117

Page 18

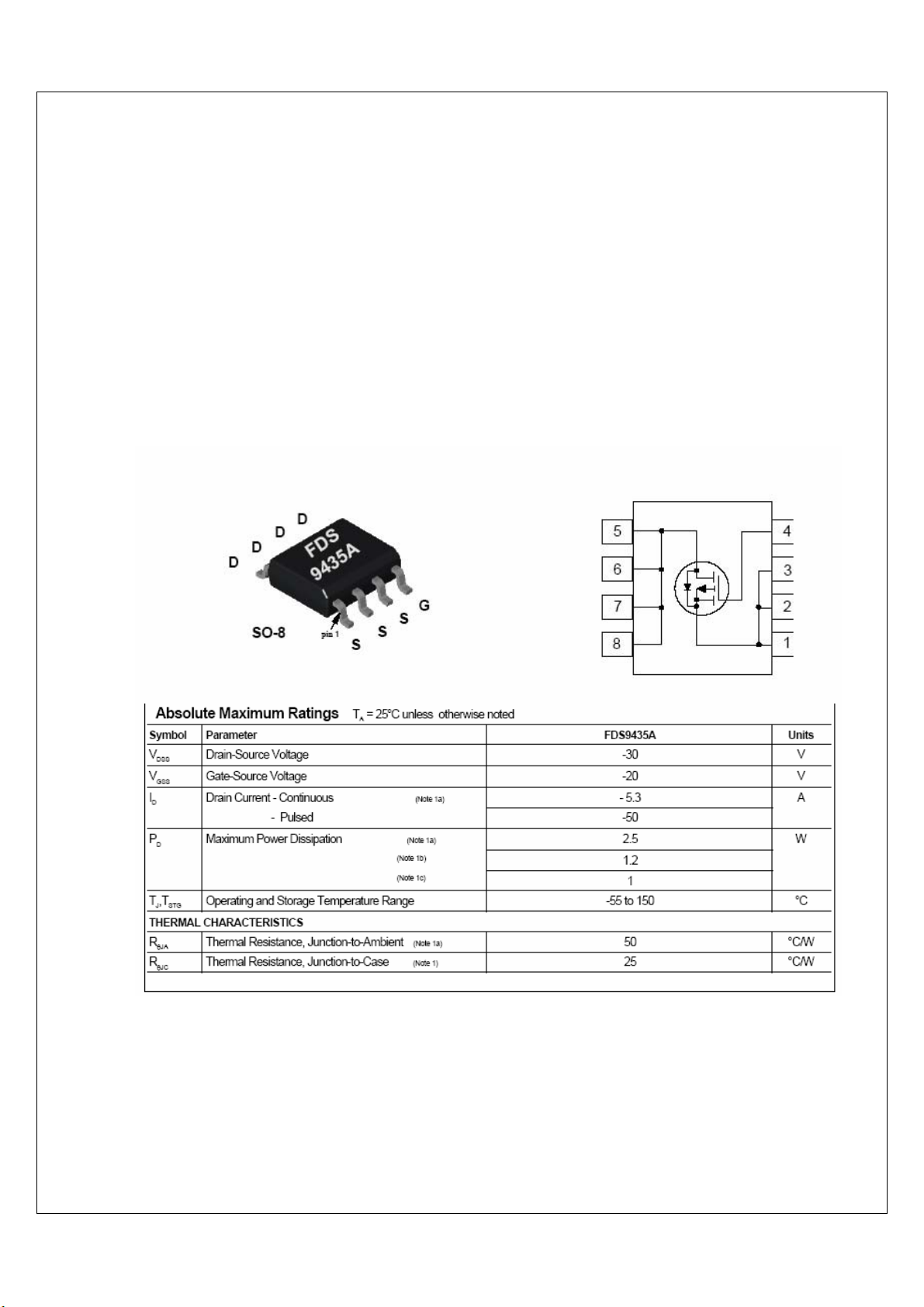

5. FDS9435A

Single P-Channel Enhancement Mode Field Effect Transistor

SO-8 P-Channel enhancement mode power field effect transistors are produced using

Fairchild's proprietary, high cell density, DMOS technology. This very high density process is

especially tailored to minimize on-state resistance and provide superior switching

performance. These devices are particularly suited for low voltage applications such as

notebook computer power management and other battery powered circuits where fast

switching, low in-line power loss, and resistance to transients are needed.

·Features

-5.3 A, -30 V, R

R

High density cell design for extremely low RDS(ON).

High power and current handling capability in a widely used surface mount package.

= 0.045 Ω @ VGS = -10 V,

DS(ON)

= 0.075 Ω @ VGS = - 4.5 V.

DS(ON)

Page 19

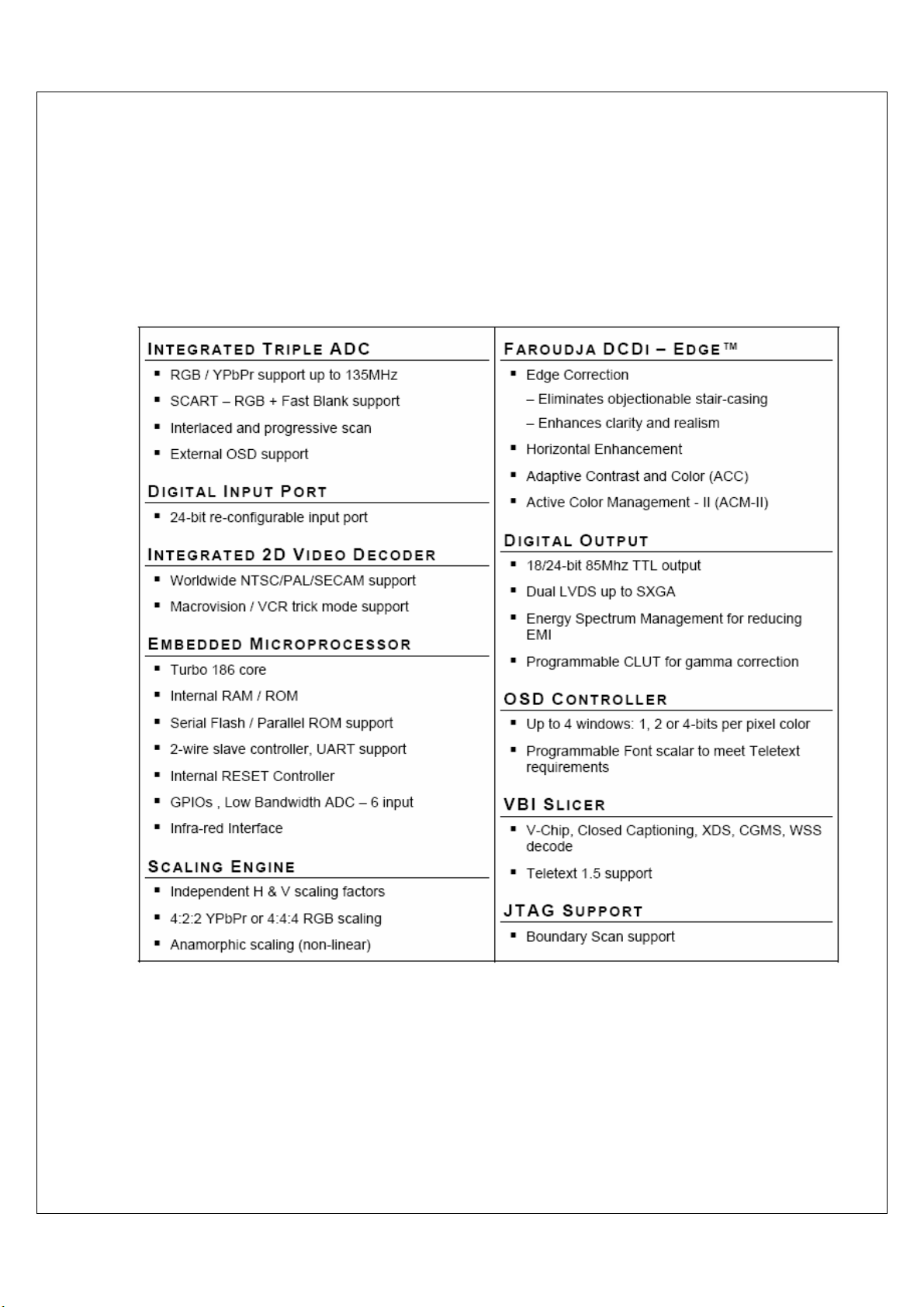

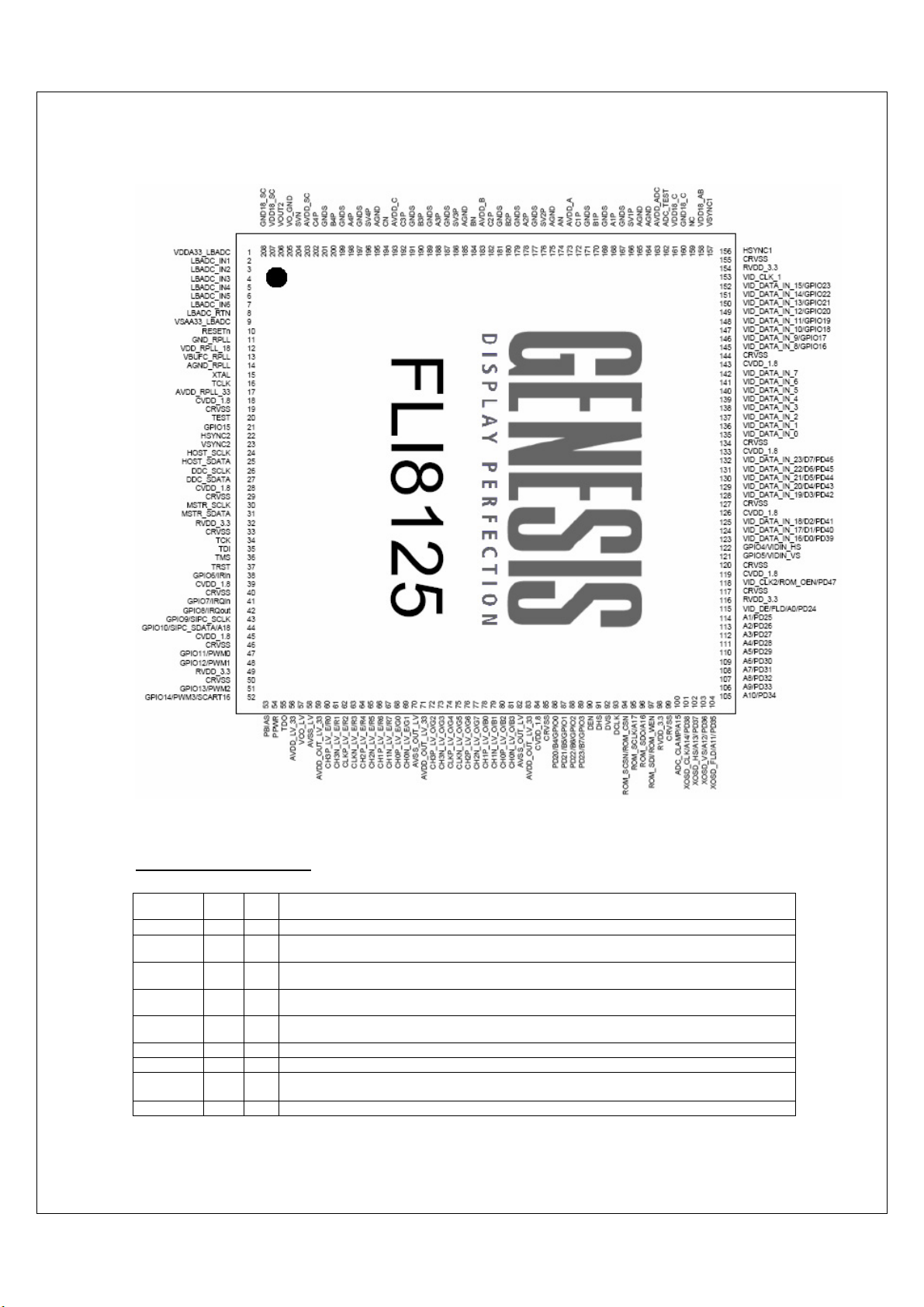

6.FLI8125

The FLI8125 is a cost-effective, highly-integrated, mixed signal solution for TV and Digit al

Video applications. It incorporates a multi-standard video decoder, high-speed triple 8 -bit

Analog-to-Digital Converter(ADC),and front end switching. An integrated VBI Slicer adds

Closed Captioning(CC) and Teletext service support, and the built-in microprocessor enables

full system control without external devices.

Features

Page 20

·PInput

·Pin List

I/O Legend: A = Analog, I = Input, O = Output, P = Power, G= Ground

Table 1: Analog Input Port

Pin Name No. I/O Description

VDD18_A

B

NC 159 No Connection. Leave this pin open for normal operation.

GND18_C 160 AG Analog Ground (1.8V Return) for C channel. Must be directly connected to the analog system ground plane

VDD18_C 16 1 AP Analog Power (1.8V) for C Channel. Must be bypassed with 0.1uF capacitor to the analog system ground

ADC_TES

T

AVDD_AD

C

AGND 164 AG Analog Ground. Must be directly connected to the analog system ground plane on board.

AGND 165 AG Analog Ground. Must be directly connected to the analog system ground plane on board.

SV1P 166 AI Positive analog sync input for channel 1.

GNDS 167 AG Analog Ground. Must be directly connected to the analog system ground plane on board.

158 AP Analog Power (1.8V) for A & B Channels. Must be bypassed with 0.1uF capacitor to the analog system

162 O Analog Front End Test O/P. Leave this Pin open. Used for factory testing purpose only.

163 AP Analog Power (3.3V) for ADC. Must be bypassed with 0.1uF capacitor to the analog system ground plane.

ground plane.

on board.

plane.

The input has to be AC coupled using a series 20 Ohm resistor and 0.1uF Capacitor network.

Page 21

A1P 168 AI Positive analog input ‘A’ for channel 1.

GNDS 169 AG Analog Ground. Must be directly connected to the analog system ground plane on board.

B1P 170 AI Positive analog input ‘B’ for channel 1.

GNDS 171 AG Analog Ground. Must be directly connected to the analog system ground plane on board.

C1P 172 AI Positive analog input ‘C’ for channel 1.

AVDD_A 173 AP Analog Power (3.3V) for ADC of Channel-A. Must be bypassed with 0.1uF capacitor to the analog system

AN 174 AI Nega t ive analog input ‘A’ for channels 1 through 4.

AGND 175 AG Analog Ground. Must be directly connected to the analog system ground plane on board.

SV2P 176 AI Positive analog sync input for channel 2.

GNDS 177 AG Analog Ground. Must be directly connected to the analog system ground plane on board.

A2P 178 AI Positive analog input ‘A’ for channel 2.

GNDS 179 AG Analog Ground. Must be directly connected to the analog system ground plane on board.

B2P 180 AI Positive analog input ‘B’ for channel 2.

GNDS 181 AG Analog Ground. Must be directly connected to the analog system ground plane on board.

C2P 182 AI Positive analog input ‘C’ for channel 2.

AVDD_B 183 AP Analog Power (3.3V) for ADC of Channel-B. Must be bypassed with 0.1uF capacitor to the analog system

BN 184 AI Nega t ive analog input ‘B’ for channels 1 through 4.

AGND 185 AG Analog Ground. Must be directly connected to the analog system ground plane on board.

SV3P 186 AI Positive analog sync input for channel 3.

VDD18_AB 158 AP Analog Power (1.8V) for A & B Channels. Must be bypassed with 0.1uF capacitor to the analog system

GNDS 187 AG Analog Ground. Must be directly connected to the analog system ground plane on board.

A3P 188 AI Positive analog input ‘A’ for channel 3.

GNDS 189 AG Analog Ground. Must be directly connected to the analog system ground plane on board.

B3P 190 AI Positive analog input ‘B’ for channel 3.

GNDS 191 AG Analog Ground. Must be directly connected to the analog system ground plane on board.

C3P 192 AI Positive an alog input ‘C’ for channel 3.

AVDD_C 193 AP Analog Power (3.3V) for ADC of Channel-C. Must be bypassed with 0.1uF capacitor to the analog system

CN 194 AI Negative analog input ‘C’ for channels 1 through 4.

The input has to be AC coupled using a series 20 Ohm resistor and 0.1uF Capacitor network.

The input has to be AC coupled using a series 20 Ohm resistor and 0.1uF Capacitor network.

The input has to be AC coupled using a series 20 Ohm resistor and 0.1uF Capacitor network.

ground plane.

This acts as the return Path for the Sources connected to Channel-A Inputs. This has to be AC coupled

using a series 20 Ohm resistor and 0.1uF Capacitor network to Analog Ground Plane on board.

The input has to be AC coupled using a series 20 Ohm resistor and 0.1uF Capacitor network.

The input has to be AC coupled using a series 20 Ohm resistor and 0.1uF Capacitor network.

The input has to be AC coupled using a series 20 Ohm resistor and 0.1uF Capacitor network.

The input has to be AC coupled using a series 20 Ohm resistor and 0.1uF Capacitor network.

ground plane.

This acts as the return Path for the Sources connected to Channel-B Inputs. This has to be AC coupled

using a series 20 Ohm resistor and 0.1uF Capacitor network to Analog Ground Plane on board.

The input has to be AC coupled using a series 20 Ohm resistor and 0.1uF Capacitor network.

ground plane.

The input has to be AC coupled using a series 20 Ohm resistor and 0.1uF Capacitor network.

The input has to be AC coupled using a series 20 Ohm resistor and 0.1uF Capacitor network.

The input has to be AC coupled using a series 20 Ohm resistor and 0.1uF Capacitor network.

ground plane.

This acts as the return Path for the Sources connected to Channel-C Inputs. This has to be AC coupled

using a series 20 Ohm resistor and 0.1uF Capacitor network to Analog Ground Plane on board.

AGND 195 AG Analog Ground. Must be directly connected to the analog system ground plane on board.

SV4P 196 AI Positive analog sync input for channel 4.

GNDS 197 AG Analog Ground. Must be directly connected to the analog system ground plane on board.

A4P 198 AI Positive analog input ‘A’ for channel 4.

GNDS 199 AG Analog Ground. Must be directly connected to the analog system ground plane on board.

B4P 200 AI Positive analog input ‘B’ for channel 4.

GNDS 201 AG Analog Ground. Must be directly connected to the analog system ground plane on board.

C4P 202 AI Positive an alog input ‘C’ for channel 4.

AVDD_SC 203 AP Analog Power (3.3V) for ADC of SYNC Channel. Must be bypassed with 0.1uF capacitor to the analog

The input has to be AC coupled using a series 20 Ohm resistor and 0.1uF Capacitor network.

The input has to be AC coupled using a series 20 Ohm resistor and 0.1uF Capacitor network.

The input has to be AC coupled using a series 20 Ohm resistor and 0.1uF Capacitor network.

The input has to be AC coupled using a series 20 Ohm resistor and 0.1uF Capacitor network.

system ground plane.

Page 22

SVN 204 AI Negative analog sync input for channels 1 through 4.

VO_GND 205 AG Analog Ground. Must be directly connected to the analog system ground plane on board.

VOUT2 206 AO Analog VOUT signal

VDD18_SC 207 AP Analog Power (1.8V) for SYNC Channel. Must be bypassed with 0.1uF capacitor to the analog system

GND18_SC 208 AG Analog Ground (1.8V Return) for SYNC channel. Must be directly connected to the analog system ground

This acts as the return Path for the Sources connected to SV Channel Inputs. This has to be AC coupled

using a series 20 Ohm resistor and 0.1uF Capacitor network to Analog Ground Plane on board.

This is the Analog Video Output from the Decoder in the Composite Video format. This can be amplified

and be fed to any video display device.

ground plane.

plane on board.

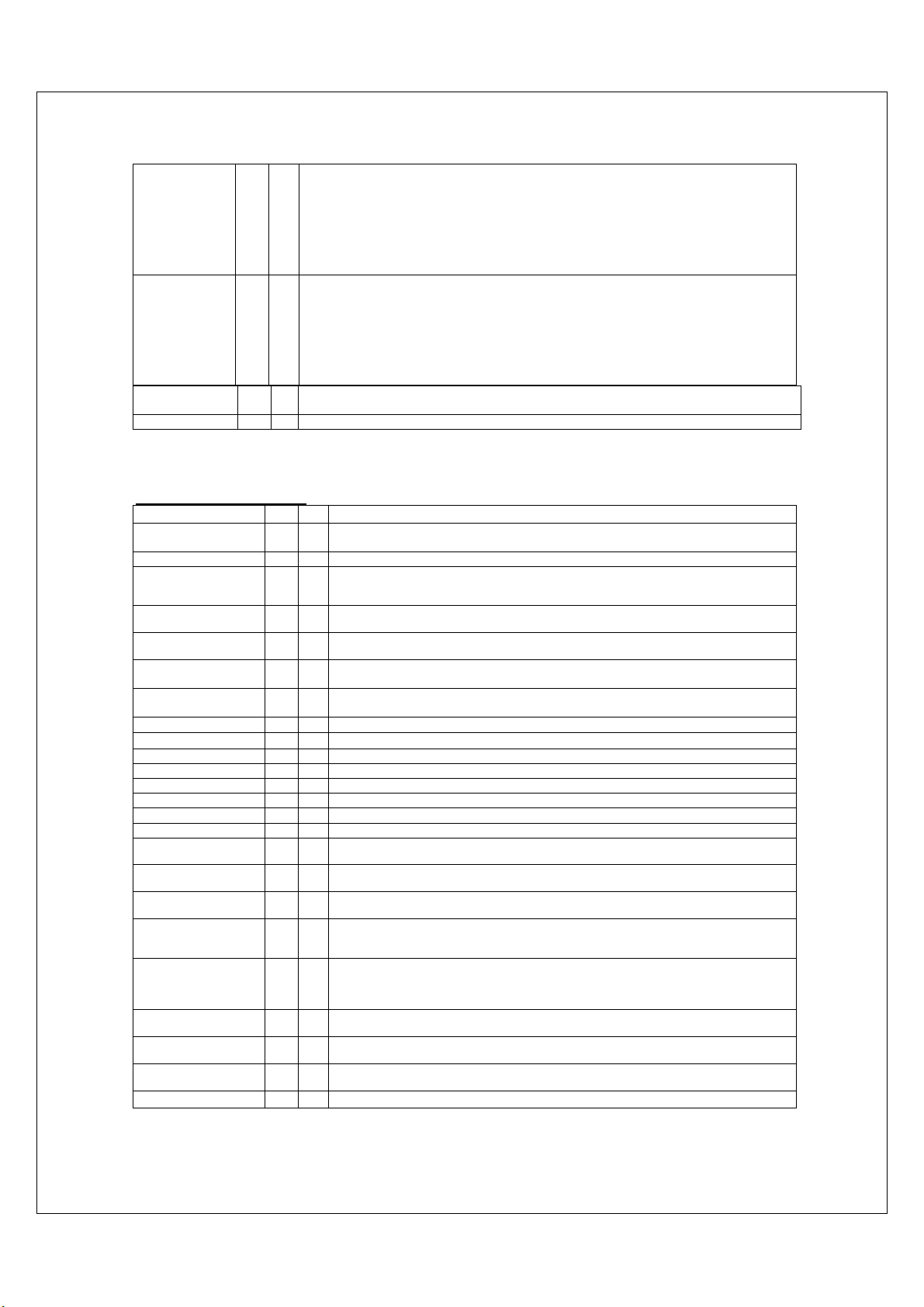

Table 2: Low Bandwidth ADC Input Port

Pin Name No I/O Description

VDDA33_LBADC 1 AP Analog Power (3.3V) for Low Bandwidth ADC Block. Must be bypassed with 0.1uF capacitor.

LBADC_IN1 2 AI Low Bandwidth Analog Input-1. The Input signal connected to this Pin, must be bypassed with a 0.1uF

LBADC_IN2 3 AI Low Bandwidth Analog Input-2. The Input signal connected to this Pin, must be bypassed with a 0.1uF

LBADC_IN3 4 AI Low Bandwidth Analog Input-3. The Input signal connected to this Pin, must be bypassed with a 0.1uF

LBADC_IN4 5 AI Low Bandwidth Analog Input-4. The Input signal connected to this Pin, must be bypassed with a 0.1uF

LBADC_IN5 6 AI Low Bandwidth Analog Input-5. The Input signal connected to this Pin, must be bypassed with a 0.1uF

LBADC_IN6 7 AI Low Bandwidth Analog Input-6. The Input signal connected to this Pin, must be bypassed with

LBADC_RTN 8 AG This Pin provides the Return Path for LBADC inputs. Must be directly connected to the analog system

VSSA33_LBADC 9 AG Analog Ground for Low Bandwidth ADC Block. Must be directly connected to the analog system ground

capacitor and could be in the range of 0V to 3.3V (peak to peak).

capacitor and could be in the range of 0V to 3.3V (peak to peak).

capacitor and could be in the range of 0V to 3.3V (peak to peak).

capacitor and could be in the range of 0V to 3.3V (peak to peak).

capacitor and could be in the range of 0V to 3.3V (peak to peak).

ground plane on board.

plane on board.

Table 3: RCLK PLL Pins

Pin Name No I/O Description

GND_RPLL 11 DG Digital GND for ADC clocking circuit. Must be directly connected to the digital system ground plane.

VDD_RPLL_18 12 DP Digital power (1.8V) for ADC digital logic. Must be bypassed with capacitor to Ground Plane.

VBUFC_RPLL 13 O Test Output. Leave this Pin Open. This is reserved for Factory Testing Purpose.

AGND_RPLL 14 AG Analog ground for the Reference DDS PLL. Must be directly connected to the analog system ground

XTAL 15 AO Crystal oscillator output.

TCLK 16 AI Reference clock (TCLK) from the 14.3MHz crystal oscillator.

AVDD_RPLL_33 17 AP Analog Power (3.3V) for RCLK PLL. Must be bypassed with 0.1uF capacitor.

plane.

Table 4: Digital Video Input Port

Pin Name No I/O Description

VID_CLK_1 153 I Video port data clock input meant for Video Input – 1. Up to 75Mhz

VIDIN_HS 122 I When Video Input – 1 is in BT656 Mode, this Pin acts as Horizontal Sync Input for Video Input – 2.

VIDIN_VS 121 I When Video Input – 1 is in BT656 Mode, this Pin acts as Vertical Sync Input for Video Input – 2.

VID_DATA_IN_0

VID_DATA_IN_1

VID_DATA_IN_2

VID_DATA_IN_3

VID_DATA_IN_4

VID_DATA_IN_5

VID_DATA_IN_6

VID_DATA_IN_7

Pin Name No I/O Description

135

136

137

138

139

140

141

142

[Input, 5V-tolerant]

OR when Video Input – 1 is in 16 Bit Mode this Pin acts as Horizontal Sync Input for Video Input – 1.

OR this Pin acts as Horizontal Sync Input for 24 Bit Video Input

OR when Video Input – 1 is in 16 Bit Mode this Pin acts as Vertical Sync Input for Video Input – 1.

OR this Pin acts as Vertical Sync Input for 24 Bit Video Input

IO Input YUV data in 8-bit BT656 of Video Input – 1

[Bi-Directional, 5V-tolerant]

OR Input Y Data in case of 16 Bit Video Input (CCIR601) of Video Input – 1

OR Input Red Data in case of 24 Bit Video Input

Page 23

VID_DATA_IN_8

VID_DATA_IN_9

VID_DATA_IN_10

VID_DATA_IN_11

VID_DATA_IN_12

VID_DATA_IN_13

VID_DATA_IN_14

VID_DATA_IN_15

VID_DATA_IN_16

VID_DATA_IN_17

VID_DATA_IN_18

VID_DATA_IN_19

VID_DATA_IN_20

VID_DATA_IN_21

VID_DATA_IN_22

VID_DATA_IN_23

VID_CLK2 118 I Video port data clock input meant for Video Input – 2. Up to 75Mhz

VID_DE/FLD 115 I Video Active Signal Input or the Field Signal Input from external Digital Video Source.

145

IO Input Pr / Pb Data in case of 16 Bit Video Input (CCIR601) of Video Input – 1

146

147

148

149

150

151

152

123

124

125

128

129

130

131

132

OR Input Green Data in case of 24 Bit Video Input

IO Input Blue Data in case of 24 Bit Video Input

OR Video Input – 2 in 8-bit with Embedded Sync / Separate Sync Sync in which case

VID_DATA_IN_16 acts as the LSB of the 8-bit Video input and VID_DATA_IN_23 acts as the MSB of

the 8-bit Video input.

[Input, 5V-tolerant]

Note: In case of Multiple Digital Video Input Sources, only one source could be in 8-Bit with

embedded Sync (BT656 mode) format.

Table 5: System Interface

Pin Name No I/O Description

RESETn 10 I Hardware Reset (active low) [Schmitt trigger, 5v-tolerant]

TEST 20 I For normal mode of operation connect this Pin to Ground.

GPIO15 21 IO This pin is available as a general-purpose input/output port. Also it is optionally programmable to

Connect to ground with 0.01uF (or larger) capacitor.

give out the external chip select signal meant for external SRAM. Refer to note below.

HSYNC2 22 I Horizontal Sync signal Input-2. Used when Analog RGB component signal carries separate

VSYNC2 23 I Vertical Sync signal Input-2. Used when Analog RGB component signal carries separate VSYNC

HOST_SCLK 24 IO Host input clock or 186 UART Data In or JTAG clock signal.

HOST_SDATA 25 IO Host input data or 186 UART Data Out or JTAG mode signal.

DDC_SCLK 26 IO

DDC_SDATA 27 IO

MSTR_SCLK 30 O Clock signal from Master Serial 2 Wire Interface Controller

MSTR_SDATA 31 IO Data signal meant for Master Serial 2 Wire interface Controller

TCK 34 IO This Pin accepts the Input Clock signal in case of Boundary Scan Mode.

TDI 35 IO This Pin accepts the Input Data signal in case of Boundary Scan Mode.

TMS 36 IO This Pin accepts the Input Test Mode Select signal in case of Boundary Scan Mode.

TRST 37 IO This Pin accepts the Boundary Scan Reset signal in case of Boundary Scan Mode.

GPIO6/IRin 38 IO Input from Infra Red Decoder can be connected to this Pin. When not used, this pin is available

GPIO7/IRQin 41 IO Input Interrupt Request signal can be connected to this Pin. When not used, this pin is available

GPIO8/IRQout 42 IO This Pin will give out the Interrupt Signal to interrupt external Micro. When not used, this pin is

GPIO9/SIPC_SCLK 43 IO This Pin accepts the Clock signal from External Serial 2 Wire interface Bus if FLI8125 is

GPIO10/SIPC_SDATA/

A18

GPIO11/PWM0 47 IO This Pin can be programmed to give out Pulse Width Modulated Output Pulses for external use.

GPIO12/PWM1 48 IO This Pin can be programmed to give out Pulse Width Modulated Output Pulses for external use.

GPIO13/PWM2 51 IO This Pin can be programmed to give out Pulse Width Modulated Output Pulses for external use.

Pin Name No I/O Description

44 IO This Pin acts as the Data I/O signal when used with External Serial 2 Wire interface Bus if

HSYNC signal.

signal.

[Input, Schmitt trigger, 5V-tolerant]

[Bi-directional, Schmitt trigger, slew rate limited, 5V-tolerant]

DDC2Bi clock for VGA Port [internal 10KΩ pull-up resistor]

DDC2Bi data for VGA Port [internal 10KΩ pull-up resistor]

as General Purpose Input/output Port.

as General Purpose Input/output Port.

available as General Purpose Input/output Port.

programmed to be in Slave mode. When not used, this pin is available as General Purpose

Input/output Port.

FLI8125 is programmed to be in Slave mode. Or this Pin is programmable to give out Address #

18 from the Internal Micro when used with 512K External Memory. When not used, this pin is

available as General Purpose Input/output Port.

When not used, this pin is available as General Purpose Input/output Port.

When not used, this pin is available as General Purpose Input/output Port.

When not used, this pin is available as General Purpose Input/output Port.

Page 24

GPIO14/PWM3/

SCART16

TDO 55 O This Pin provides the Output Data in case of Boundary Scan Mode.

HSYNC1 156 I Horizontal Sync signal Input-1. Used when Analog RGB component signal carries separate

VSYNC1 157 I Vertical Sync signal Input-1. Used when Analog RGB component signal carries separate VSYNC

101 O Clock Output meant for External OSD Controller

102 O Horizontal Sync Output meant for External OSD Controller

XOSD_CLK 103 O Vertical Sync Output meant for External OSD Controller

XOSD_HS 104 O Field Signal Output meant for External OSD Controller

PD20/B4/GPIO0

PD21/B5/GPIO1

PD22/B6/GPIO2

PD23/B7/GPIO3

52 IO This Pin can be programmed to give out Pulse Width Modulated Output Pulses for external use.

86

87

88

89

Or it can be programmed to sense the Fast Blank Input signal from a SCART I/P source. When

not used, this pin is available as General Purpose Input/output Port.

HSYNC signal.

signal.

IO T hese Pins provide the Panel Data as shown in the TTL Display Interface Table below. These are

available as General Purpose Input / Output Pins when not used as Panel Data.

Table 6: LVDS Display Interface

Pin Name No I/O Description

PBIAS 53 O Panel Bias Control (backlight enable) [Tri-state output, 5V- tolerant]

PPWR 54 O Panel Power Control [Tri-state output, 5V- tolerant]

AVDD_LV_33

VCO_LV

AVSS_LV

AVDD_OUT_LV_33

CH3P_LV_E

CH3N_LV_E

CLKP_LV_E

CLKN_LV_E

CH2P_LV_E

CH2N_LV_E

CH1P_LV_E

CH1N_LV_E

CH0P_LV_E

CH0N_LV_E

AVSS_OUT_LV

AVDD_OUT_LV_33

CH3P_LV_O

CH3N_LV_O

CLKP_LV_O

CLKN_LV_O

CH2P_LV_O

CH2N_LV_O

CH1P_LV_O

CH1N_LV_O

CH0P_LV_O

CH0N_LV_O

AVSS_OUT_LV

AVDD_OUT_LV_33

56 DP Digital Power for LVDS Block. Connect to digital 3.3V supply.

57 O Reserved. Output for Testing Purpose only at Factory.

58 G Ground for LVDS outputs.

59 DP Digital Power for LVDS outputs. Connect to digital 3.3V supply.

60 O

61 O

62 O

63 O

64 O

65 O

66 O

67 O

68 O

69 O

70 G Ground for LVDS outputs.

71 DP Digital Power for LVDS outputs. Connect to digital 3.3V supply.

72 O

73 O

74 O

75 O

76 O

77 O

78 O

79 O

80 O

81 O

82 G Ground for LVDS outputs.

83 DP Digital Power for LVDS outputs. Connect to digital 3.3V supply.

These form the Differential Data Output for Channel – 3 (Even).

These form the Differential Clock Output Even Channel.

These form the Differential Data Output for Channel – 2 (Even).

These form the Differential Data Output for Channel – 1 (Even).

These form the Differential Data Output for Channel – 0 (Even).

These form the Differential Data Output for Channel – 3 (Odd).

These form the Differential Clock Output Odd Channel.

These form the Differential Data Output for Channel – 2 (Odd).

These form the Differential Data Output for Channel – 1 (Odd).

These form the Differential Data Output for Channel – 0 (Odd).

Page 25

Table 7: TTL Display Interface

Pin Name No I/O Description

PBIAS 53 O Panel Bias Control (backlight enable) [Tri-state output, 5V- tolerant]

PPWR 54 O Panel Power Control [Tri-state output, 5V- tolerant]

AVDD_LV_33

VCO_LV

AVSS_LV

AVDD_OUT_LV_33

R0

R1

R2

R3

R4

R5

R6

R7

G0

G1

AVSS_OUT_LV

AVDD_OUT_LV_33

G2

G3

G4

G5

G6

G7

B0

B1

B2

B3

AVSS_OUT_LV

AVDD_OUT_LV_33

PD20/B4 86 O Blue channel bit 4 (Even) Blue channel bit 2 (Even)

PD21/B5 87 O Blue channel bit 5 (Even) Blue channel bit 3 (Even)

PD22/B6 88 O Blue channel bit 6 (Even) Blue channel bit 4 (Even)

PD23/B7 89 O Blue channel bit 7 (Even) Blue channel bit 5 (Even)

DEN 90 O Display Data Enable

DHS 91 O Display Horizontal Sync.

DVS 92 O Display Vertical Sync.

DCLK 93 O Display Pixel Clock

PD24

Pin Name No I/O Description

PD25

PD26

PD27

PD28

PD29

PD30

PD31

PD32

PD33

PD34

PD35

PD36

PD37

PD38

PD39

PD40

PD41

PD42

PD43

PD44

PD45

56 DP Digital Power for TTL Block. Connect to digital 3.3V supply.

57 O Reserved. Output for Testing Purpose only at Factory.

58 G Ground for TTL outputs.

59 DP Digital Power for TTL outputs. Connect to digital 3.3V supply.

60 O Red channel bit 0 (Even) Not used.

61 O Red channel bit 1 (Even) Not used.

62 O Red channel bit 2 (Even) Red channel bit 0 (Even)

63 O Red channel bit 3 (Even) Red channel bit 1 (Even)

64 O Red channel bit 4 (Even) Red channel bit 2 (Even)

65 O Red channel bit 5 (Even) Red channel bit 3 (Even)

66 O Red channel bit 6 (Even) Red channel bit 4 (Even)

67 O Red channel bit 7 (Even) Red channel bit 5 (Even)

68 O Green channel bit 0 (Even) Not used.

69 O Green channel bit 1 (Even) Not used.

70 G Ground for TTL outputs.

71 DP Digital Power for TTL outputs. Connect to digital 3.3V supply.

72 O Green channel bit 2 (Even) Green channel bit 0 (Even)

73 O Green channel bit 3 (Even) Green channel bit 1 (Even)

74 O Green channel bit 4 (Even) Green channel bit 2 (Even)

75 O Green channel bit 5 (Even) Green channel bit 3 (Even)

76 O Green channel bit 6 (Even) Green channel bit 4 (Even)

77 O Green channel bit 7 (Even) Green channel bit 5 (Even)

78 O Blue channel bit 0 (Even) Not used.

79 O Blue channel bit 1 (Even) Not used.

80 O Blue channel bit 2 (Even) Blue channel bit 0 (Even)

81 O Blue channel bit 3 (Even) Blue channel bit 1 (Even)

82 G Ground for TTL outputs.

83 DP Digital Power for TTL outputs. Connect to digital 3.3V supply.

115 O Red channel bit 0 (Odd) Not used.

114 O Red channel bit 1 (Odd) Not used.

113 O Red channel bit 2 (Odd) Red channel bit 0 (Odd)

112 O Red channel bit 3 (Odd) Red channel bit 1 (Odd)

111 O Red channel bit 4 (Odd) Red channel bit 2 (Odd)

110 O Red channel bit 5 (Odd) Red channel bit 3 (Odd)

109 O Red channel bit 6 (Odd) Red channel bit 4 (Odd)

108 O Red channel bit 7 (Odd) Red channel bit 5 (Odd)

107 O Green channel bit 0 (Odd) Not used.

106 O Green channel bit 1 (Odd) Not used.

105 O Green channel bit 2 (Odd) Green channel bit 0 (Odd)

104 O Green channel bit 3 (Odd) Green channel bit 1 (Odd)

103 O Green channel bit 4 (Odd) Green channel bit 2 (Odd)

102 O Green channel bit 5 (Odd) Green channel bit 3 (Odd)

101 O Green channel bit 6 (Odd) Green channel bit 4 (Odd)

123 O Green channel bit 7 (Odd) Green channel bit 5 (Odd)

124 O Blue channel bit 0 (Odd) Not used.

125 O Blue channel bit 1 (Odd) Not used.

128 O Blue channel bit 2 (Odd) Blue channel bit 0 (Odd)

129 O Blue channel bit 3 (Odd) Blue channel bit 1 (Odd)

130 O Blue channel bit 4 (Odd) Blue channel bit 2 (Odd)

131 O Blue channel bit 5 (Odd) Blue channel bit 3 (Odd)

For 8-bit panels For 6-bit panels

For 8-bit panels For 6-bit panels

24

Page 26

PD46

PD47

132 O Blue channel bit 6 (Odd) Blue channel bit 4 (Odd)

118 O Blue channel bit 7 (Odd) Blue channel bit 5 (Odd)

Note: In case of 24 Bit TTL Panels the RGB Odd Channel Outputs will not be used. In that case they can be

made available for other purposes as Address & Data from On-Chip Micro or Digital Video Input Data.

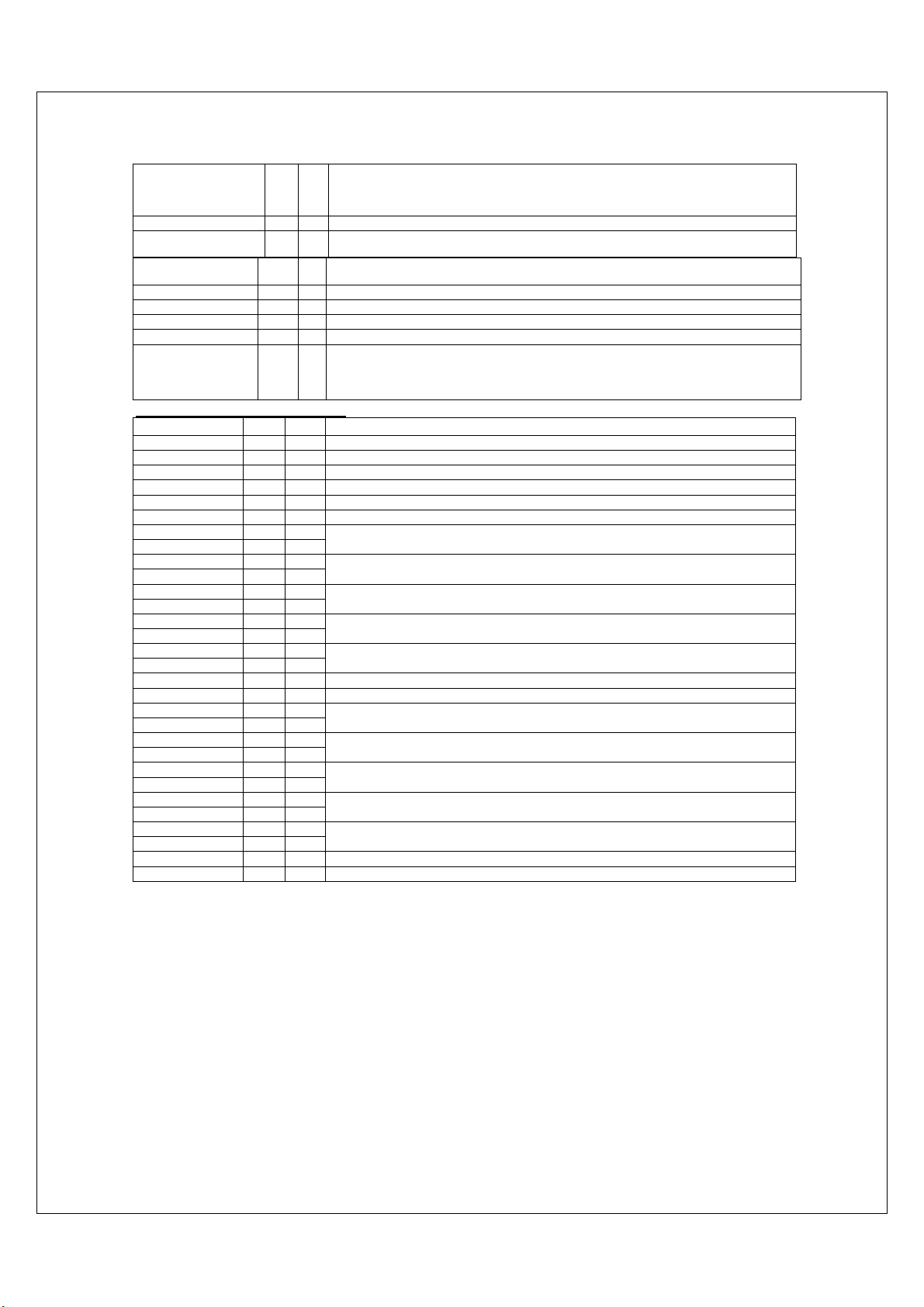

Table 8: Parallel/Serial ROM Interface

Pin Name No I/O Description

A17

A16

A15

A14

A13

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

D7

D6

D5

D4

D3

D2

D1

D0

ROM_OEN 118 O External PROM data Output Enable.

ROM_SDI/

ROM_WEN

ROM_SCSN/

ROM_CSN

Table 9: Digital Power and Ground

Pin Name No I/O Description

RVDD_3.3 32 49 98 116 154 P Ring VDD. Connect to digital 3.3V.

95

O 256K x8 PROM Address. These pins also have bootstrap functionality.

96

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

132

131

130

129

128

125

124

123

97 O External PROM data Write Enable (for In-System-Programming of FLASH) or Serial Data Input

94 O External PROM data Chip Select or Serial PROM Chip Select (ROM_SCSN) for SPI ROM

For serial SPI ROM interface:

- ROM_ADDR17 will be Serial Clock (ROM_SCLK)

- ROM_ADDR16 will be Serial Data Output (ROM_SDO)

For 512K X 8 PROM, Address Signal A18 is available thru Pin # 44 which is GPIO10.

IO External PROM data input.

(SDI) for SPI ROM interface.

interface.

CVDD_1.8 18 28 39 45 84 119 126 133 143 P Core VDD. Connect to digital 1.8V.

CRVSS 19 29 33 40 46 50 85 99 117 120

127 134 144 155

G Chip ground for core and ring.

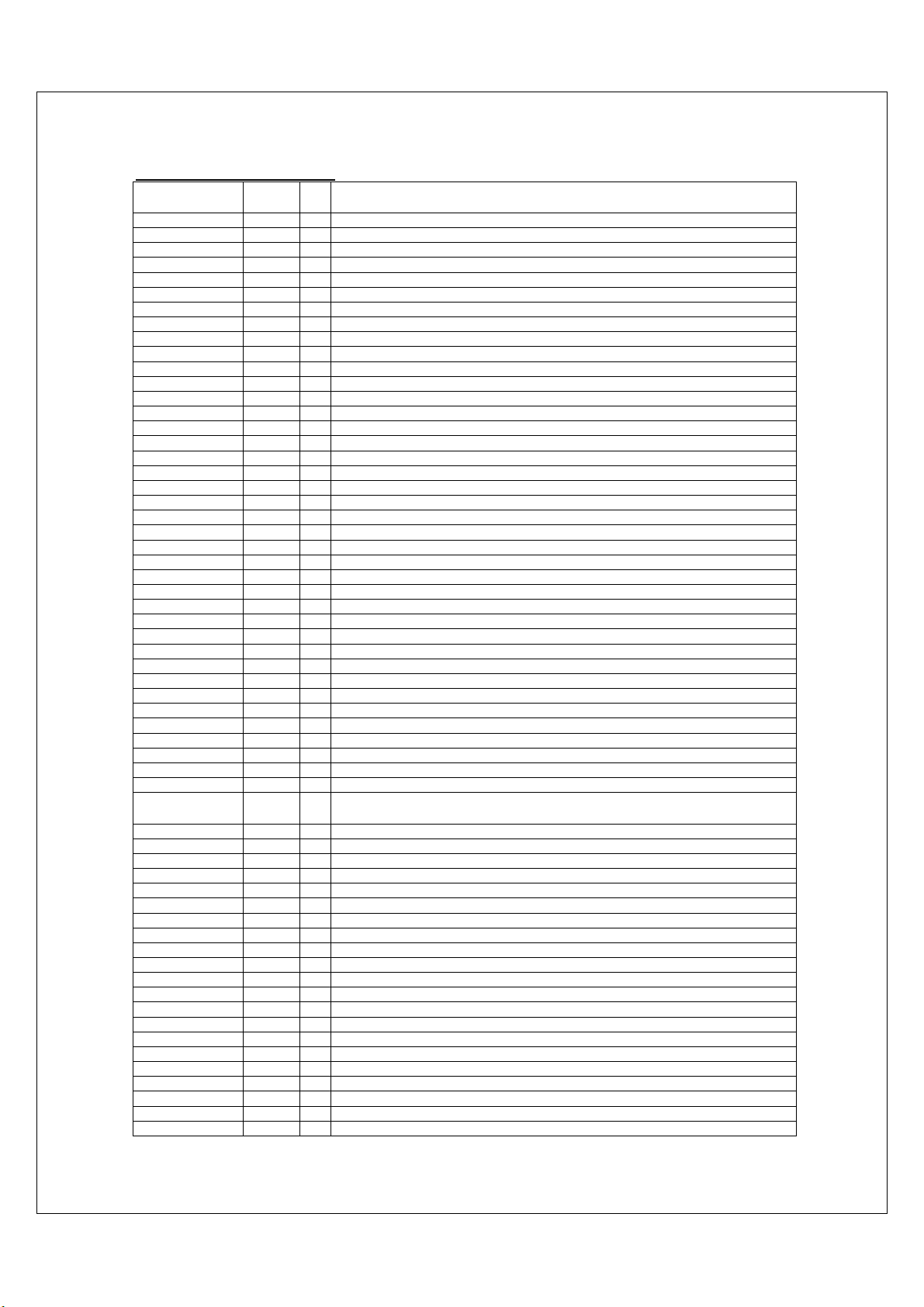

Table 10: JTAG Boundary Scan

Pin Name No I/O Description

TCK 34 I JTAG Boundary Scan TCK signal

TDO 55 O JTAG Boundary Scan TDO signal

TDI 35 I JTAG Boundary Scan TDI signal. Pad has internal 50K pull-up resistor.

TMS 36 I JTAG Boundary Scan RST signal. Pad has internal 50K pull-up resistor.

TRST 37 I JTAG Boundary Scan TMS signal. Pad has internal 50K pull-up resistor.

25

Page 27

7. CD4052B

The CD4052B is a differential 4-Channel multiplexer having two binary control inputs, A

and B, and an inhibit input. The two binary signals selec t 1 of 4 pairs of channels to be turned

on and connect the analog inputs to the outputs.

·PInputs

.

26

Page 28

8. A T24C32AN

2-Wire Serial EEPROM 32K (4096 x 8)

27

Page 29

28

Page 30

9. TPA3008D2

10-W STEREO CLASS-D AUDIO POWER AMPLIFIER.

29

Page 31

·Pin Description

30

Page 32

10. TL494

PULSE-WIDTH-MODULATION CONTROL CIRCUITS

31

Page 33

1. BA5954

ICS ON DVD BOARD

32

Page 34

33

Page 35

2. MT1389HD

Abbr. :

SR : Slew Rate

PU : Pull Up

PD : Pull Down

SMT : Schmitt Trigger

2MA~16MA : Output buffer driving strength.

Pin Main Alt. Type Description

231 RFGND18

232 RFVDD18

252 OSP

253 OSN

254 RFGC

Ground Analog ground

Analog output RF Offset cancellation capacitor connecting

Analog output RF Offset cancellation capacitor connecting

Analog output RF AGC loop capacitor connecting for DVD-ROM

255 IREF

Analog Input RF path. Connect an external 15K resistor to this pin and

Ground Analog ground

Analog Input AC coupled input path A

Analog Input AC coupled input path B

Analog Input AC coupled input path C

Analog Input AC coupled input path D

Analog Input AC coupled DVD RF signal input RFIP

Analog Input AC coupled DVD RF signal input RFIN

Analog Input DC coupled main-beam RF signal input A

Analog Input DC coupled main-beam RF signal input B

Analog Input DC coupled main-beam RF signal input C

Analog Input DC coupled main-beam RF signal input D

Analog Input DC coupled sub-beam RF signal input A

Analog Input DC coupled sub-beam RF signal input B

Analog Input DC coupled sub-beam RF signal input C

Analog Input DC coupled sub-beam RF signal input D

Analog Input CD focusing error negative input

Analog Input CD focusing error positive input

Analog Input 3 beam satellite PD signal negative input

Analog Input 3 beam satellite PD signal positive input

256 AVDD3

1 AGND

2 DVDA

3 DVDB

4 DVDC

5 DVDD

6 DVDRFIP

7 DVDRFIN

8 MA

9 MB

10 MC

11 MD

12 SA

13 SB

14 SC

15 SD

16 CDFON

17 CDFOP

18 TNI

19 TPI

RF Interface ( 26 )

Power Analog power 1.8V

Current reference input. It generates reference current for

AVSS.

Power Analog power 3.3V

ALPC ( 4 )

Pin Main Alt. Type Description

20 MDI1

21 MDI2

22 LDO2

23 LDO1

Analog Input Laser power monitor input

Analog Input Laser power monitor input

Analog Output Laser driver output

Analog Output Laser driver output

34

Page 36

ADC Power ( 2 )

244 ADCVDD3

245 ADCVSS

43 VPLLVSS

44 CAPPAD

45 VPLLVDD3

28 V2REFO

29 V20

30 VREFO

24 SVDD3

25 CSO RFOP Analog output

26 RFLVL RFON Analog output

27 SGND

31 FEO

32 TEO

33 TEZISLV

Power Analog 3.3V Power for ADC

Ground Analog ground for ADC

VPLL (3)

Ground Analog ground for VPLL

Analog Input VPLL External Capacitance connection

Power Analog 3.3V Power for VPLL

Reference Voltage ( 3 )

Analog output Reference voltage 2.8V

Analog output Reference voltage 2.0V

Analog output Reference voltage 1.4V

Analog Monitor Output ( 7 )

Power Analog power 3.3V

Ground Analog ground

Analog output Focus error monitor output

Analog output Tracking error monitor output

Analog output TE Slicing Level

1)

Central servo Positive main beam summing output

2)

1)

RFRP low pass, or Negative main beam summing

2)

output

246 RFVDD3

247 RFRPDC

248 RFRPAC

249 HRFZC

250 CRTPLP

251 RFGND

Analog Servo Interface ( 6 )

Power Analog Power

Analog output RF ripple detect output

Analog Input RF ripple detect input(through AC-coupling)

Analog Input High frequency RF ripple zero crossing

Analog output Defect level filter capacitor connecting

Ground Analog Power

35

Page 37

RF Data PLL Interface ( 9 )

Pin Main Alt. Type Description

235 JITFO

236 JITFN

237 PLLVSS

238 IDACEXLP

239 PLLVDD3

240 LPFON

241 LPFIP

242 LPFIN

243 LPFOP

Analog output The output terminal of RF jitter meter.

Analog Input The input terminal of RF jitter meter.

Ground Ground pin for data PLL and related analog circuitry.

Analog output Data PLL DAC Low-pass filter

Power Power pin for data PLL and related analog circuitry.

Analog Output The negative output of loop filter amplifier

Analog Input The positive input terminal of loop filter amplifier.

Analog Input The negative input terminal of loop filter amplifier.

Analog Output The positive output of loop filter amplifier

Motor and Actuator Driver Interface ( 10 )

34 OP_OUT

35 OP_INN

36 OP_INP

37 DMO

38 FMO

39

40

41 TRO

42 FOO

50

55,93,

142,160,

174, 213

81,178 DVSS

65,96,11

8,

131,145,

156,

170, 208

90, 148 DVSS

TROPENP

W M

PWMOUT

FG (Digital

pin)

DVDD18

DVDD3

1

V_ADIN9 Analog Output

V_ADIN8

Analog output Op amp output.

Analog input Op amp negative input

Analog input Op amp positive input

Analog Output Disk motor control output. PWM output.

Analog Output Feed motor control. PWM output.

Analog Output Tray PWM output / Tray open output.

Analog Output

Analog Output

LVTTL 3.3V Input,

Schmitt Input, pull

up , with analog

input path for

V_ADIN8

General Power/Ground ( 18 )

Power 1.8V power pin for internal digital circuitry

Ground 1.8V Ground pin for internal digital circuitry

Power 3.3V power pin for internal digital circuitry

Ground 3.3V Ground pin for internal digital circuitry

1)

2)

Tracking servo output. PDM output of tracking servo

compensator.

Focus servo output. PDM output of focus servo

compensator

1)

2)

1st General PWM output, or

Version AD input 9

Motor Hall sensor input, or

Version AD input 8

Micro Controller and Flash Interface (48)

Pin Main Alt. Type Description

36

Page 38

62 HIGHA0

Input

2~16MA, SR

PU

Microcontroller address 8

74 HIGHA1

73 HIGHA2

72 HIGHA3

71 HIGHA4

70 HIGHA5

69 HIGHA6

68 HIGHA7

Input

2~16MA, SR

PU

Input

2~16MA, SR

PU

Input

2~16MA, SR

PU

Input

2~16MA, SR

PU

Input

2~16MA, SR

PU

Input

2~16MA, SR

PU

Input

2~16MA, SR

PU

Microcontroller address 9

Microcontroller address 10

Microcontroller address 11

Microcontroller address 12

Microcontroller address 13

Microcontroller address 14

Microcontroller address 15

89 AD7

86 AD6

85 AD5

84 AD4

83 AD3

82 AD2

80 AD1

79 AD0

92 IOA0

Input 2~16MA, SR

Input 2~16MA, SR

Input 2~16MA, SR

Input 2~16MA, SR

Input 2~16MA, SR

Input 2~16MA, SR

Input 2~16MA, SR

Input 2~16MA, SR

Input

2~16MA, SR

PU

Microcontroller address/data 7

Microcontroller address/data 6

Microcontroller address/data 5

Microcontroller address/data 4

Microcontroller address/data 3

Microcontroller address/data 2

Microcontroller address/data 1

Microcontroller address/data 0

Microcontroller address 0 / IO

37

Page 39

Pin Main Alt. Type Description

77

IOA1

Input

2~16MA, SR

PU

Microcontroller address 1 / IO

56 IOA2

57 IOA3

58 IOA4

59 IOA5

60 IOA6

61 IOA7

Input

2~16MA, SR

PU

Microcontroller address 2 / IO

Input

2~16MA, SR

PU

Microcontroller address 3 / IO

Input

2~16MA, SR

PU

Microcontroller address 4 / IO

Input

2~16MA, SR

PU

Microcontroller address 5 / IO

Input

2~16MA, SR

PU

Microcontroller address 6 / IO

Input

2~16MA, SR

PU

Microcontroller address 7 / IO

67 A16

91 A17

63 IOA18

64 IOA19

75 IOA20

87 IOA21

Output 2~16MA,

SR

Output 2~16MA,

SR

Flash address 16

Flash address 17

Input

2~16MA, SR

SMT

Flash address 18 / IO

Input

2~16MA, SR

SMT

Flash address 19 / IO

Input

2~16MA, SR

SMT

Flash address 20 / IO

Input

2~16MA, SR

SMT

1) Flash address 21 / IO

2) While External FLASH size <= 2MB:

I) GPIO

38

Page 40

88 ALE

2~16MA, SR

PU, SMT

Microcontroller address latch enable

Input

Pin Main Alt. Type Description

78 IOOE#

Input

2~16MA, SR

SMT

Flash output enable, active low / IO

66 IOWR#

76 IOCS#

94 UWR#

95 URD#

97 UP1_2

98 UP1_3

99 UP1_4

100 UP1_5

Input

2~16MA, SR

SMT

Input

2~16MA, SR

PU, SMT

Input

2~16MA, SR

PU, SMT

Input

2~16MA, SR

PU, SMT

Input

4MA, SR

PU, SMT

Input

4MA, SR

PU, SMT

Input

4MA, SR

PU, SMT

Input

4MA, SR

PU, SMT

Flash write enable, active low / IO

Flash chip select, active low / IO

Microcontroller write strobe, active low

Microcontroller read strobe, active low

Microcontroller port 1-2

Microcontroller port 1-3

Microcontroller port 1-4

Microcontroller port 1-5

101 UP1_6 SCL

102 UP1_7 SDA

103 UP3_0 RXD

104 UP3_1 TXD

Input

4MA, SR

PU, SMT

Input

4MA, SR

PU, SMT

Input

4MA, SR

PU, SMT

Input

4MA, SR

PU, SMT

1) Microcontroller port 1-6

2

2) I

C clock pin

1) Microcontroller port 1-7

2) I2C data pin

1) Microcontroller port 3-0

2) 8032 RS232 RXD

1) Microcontroller port 3-1

2) 8032 RS232 TXD

39

Page 41

105 UP3_4 RXD SCL

Input

4MA, SR

PU, SMT

1) Microcontroller port 3-4

2) Hardwired RD232 RXD

2

3) I

C clock pin

1) Microcontroller port 3-5

2) Hardwired RD232 TXD

2

3) I

C data pin

106 UP3_5 TXD SDA

Input

4MA, SR

PU, SMT

109 IR

110 INTO#

Input

SMT

Input

4MA, SR

PU, SMT

IR control signal input

Microcontroller external interrupt 0, active low

Audio interface ( 28 )

Pin Main Alt. Type Description

1)

2)

1)

2)

204 SPMCLK SCLK0

205 SPDATA SDIN0

Input

Non-pull

Input

Non-pull

Audio DAC master clock of SPDIF input

While SPDIF input is not used:

I) Serial interface port 0 clock pin

II) GPIO

Audio data of SPDIF input

While SPDIF input is not used:

I) Serial interface port 0 data-in

II) GPIO

206 SPLRCK SDO0

207 SPBCK

SDCS0

ASDATA5

209 ALRCK

210 ABCK Fs64

211 ACLK

1)

Audio left/right channel clock of SPDIF input

2)

While SPDIF input is not used:

Input

Non-pull

Input

Non-pull

Input 4MA, PD,

SMT

Output

4MA

Non-pull

Input

4MA Audio DAC master clock

I) Serial interface port 0 data-out

II) GPIO

1)

Audio bit clock of SPDIF input

2)

While SPDIF input is not used:

I) Serial interface port 0 chip select

II) Audio serial data 5 part I : DSD data sub-woofer

channel or Microphone output

III) GPIO

1)

Audio left/right channel clock Trap value in power-on

2)

reset: I) 1 : use external 373 II) 0: use internal 373

1)

Audio bit clock

2)

Phase de-modulation

40

Page 42

197 ASDATA0

202 ASDATA1

203 ASDATA2

212 ASDATA3

Non-pull

Input

4MA

PD SMT

Input

4MA

PD SMT

Input 4MA PD

SMT

Input

4MA

PD SMT

Audio serial data 0 (Front-Left/Front-Right)

1)

DSD data left channel

2)

Trap value in power-on reset :

3)

I) 1 : manufactory test mode

II) 0 : normal operation

While using external channels:

4)

I) GPO_2

Audio serial data 1 (Left-Surround/Right-Surround)

1)

DSD data right channel

2)

Trap value in power-on reset :

3)

I) 1 : manufactory test mode

II) 0 : normal operation

While using external channels:

4)

I) GPO_1

Audio serial data 2 (Center/LFE) DSD data left surround

1)

channel Trap value in power-on reset : I) 1 : manufactory

2)

test mode II) 0 : normal operation While using external

3)

channels: I) GPO_0

4)

Audio serial data 3 (Center-back/

1)

Center-left-back/Center-right-back, in 6.1 or 7.1 mode)

DSD data right surround channel

2)

Trap value in power-on reset :

3)

I) 1 : manufactory test mode

II) 0 : normal operation

While only 2 channels output:

4)

I) GPO_0

214 ASDATA4 INT1#

215 MC_DATA INT2#

216 SPDIF

217 APLLVDD3

218 APLLCAP

Audio serial data 4 (Down-mixed Left/Right)

1)

DSD data center channel

2)

Trap value in power-on reset :

Input

4MA

PD SMT

Input

PD SMT

Output

2~16MA,

SR : ON/OFF

Non-pull

Power 3.3V Power pin for audio clock circuitry

Analog Input APLL External Capacitance connection

3)

I) 1 : manufactory test mode

II) 0 : normal operation

While only 2 channels output:

4)

I) Microcontroller external interrupt 1

II) GPO_0

1)

Microphone serial input

2)

While not support Microphone:

I) Microcontroller external interrupt 2

II) GPO_0

SPDIF output

41

Page 43

219 APLLVSS

220 ADACVSS2

221 ADACVSS1

222 ARF GPIO Output

Ground Ground pin for audio clock circuitry

Ground Ground pin for AUDIO DAC circuitry

Ground Ground pin for AUDIO DAC circuitry

1)

AUDIO DAC Sub-woofer channel output While internal

2)

AUDIO DAC not used: GPIO

223 ARS GPIO Output

224 AR GPIO Output

225 AVCM

Analog AUDIO DAC reference voltage

226 AL GPIO Output

227 ALS GPIO Output

228 ALF GPIO Output

229 ADACVDD1 Power 3.3V power pin for AUDIO DAC circuitry

230 ADACVDD2 Power 3.3V power pin for AUDIO DAC circuitry

1) AUDIO DAC Right Surround channel output

2) While internal AUDIO DAC not used:

a. SDATA3

b. GPIO

1) AUDIO DAC Right channel output

2) While internal AUDIO DAC not used:

a. SDATA1

b. GPIO

1) AUDIO DAC Left Surround channel output

2) While internal AUDIO DAC not used:

a. SDATA2

b. GPIO

1) AUDIO DAC Left Surround channel output

2) While internal AUDIO DAC not used:

a. SDATA0

b. GPIO

1) AUDIO DAC Center channel output

2) While internal AUDIO DAC not used:GPIO

Video Interface ( 18 )

196 DACVDDC

195 VREF

194 FS

193 YUV0 CIN

Power 3.3V power pin for VIDEO DAC circuitry

Analog Bandgap reference voltage

Analog Full scale adjustment

Output 4MA,

SR

1)

Video data output bit 0

2)

Compensation capacitor

192 DACVSSC

191 YUV1 Y

190 DACVDDB

189 YUV2 C

188 DACVSSB

187 YUV3 CVBS

186 DACVDDA

185 YUV4 Y/G

184 DACVSSA

183 YUV5 B/Cb/Pb

Ground Ground pin for VIDEO DAC circuitry

Output 4MA,

SR

Power 3.3V power pin for VIDEO DAC circuitry

Output 4MA,

SR

Ground Ground pin for VIDEO DAC circuitry

Output 4MA,

SR

Power 3.3V power pin for VIDEO DAC circuitry

Output

4MA, SR

Ground Ground pin for VIDEO DAC circuitry

Output

4MA, SR

1)

Video data output bit 1

2)

Analog Y output

1)

Video data output bit 2

2)

Analog chroma output

1)

Video data output bit 3

2)

Analog composite output

1)

Video data output bit 4

2)

Green or Y

1)

Video data output bit 5

2)

Blue or CB

42

Page 44

182 YUV6 R/Cr/Pr

181 VSYN V_ADIN1

180 YUV7

179 HSYN

46 USB_VSS

47 USBP

48 USBM

49 USB_VDD3

108 PRST#

107 ICE

233 XTALO

234 XTALI

201 GPIO_3

200 GPIO_4

199 RCLKB GPIO_5

198 RVREF GPIO_6

INT3#

ASDATA5

INT4#

V_ADIN2

Output

4MA, SR

Input

4MA, SR

SMT

Non-pull

Input

4MA, SR

SMT

Non-pull

Input

4MA, SR

SMT

Non-pull

USB Ground USB ground pin

Analog Input USB port DPLUS analog pin

Analog Input USB port DMINUS analog pin

USB Power USB Power pin 3.3V

Input

PU, SMT

Input

PD, SMT

Output 27M crystal out

Input

Input

Pull-Down

Input

Pull-Down

Input

Pull-Up

Input

Pull-Up

Dram Interface ( 58 ) ( Sorted by position )

1)

Video data output bit 6

2)

Red or CR

1)

Vertical sync input/output

2)

While no External TV-encoder:

I) Vertical sync for video-input

II) Version AD input port 1

III) GPIO

1)

Video data output bit 7

2)

While no External TV-encoder:

I) Microcontroller external interrupt 3

II) Audio serial data 5 part II : DSD data sub-woofer

channel or Microphone output

III) GPIO

1)

Horizontal sync input/output

2)

While no External TV-encoder:

I) Horizontal sync for video-input

II) Microcontroller external interrupt 4

III) Version AD input port 2

IV) GPIO

MISC ( 12 )

Power on reset input, active low

Microcontroller ICE mode enable

27M crystal in

GPIO

GPIO

GPIO

GPIO

176 C_0

175 C_1

173 C_2

172 C_3

171 C_4

IO_0

(RD16)

IO_1

(RD17)

IO_2

(RD18)

IO_3

(RD19)

IO_4

(RD20)

Input

Non-pull

Input

Non-pull

Input

Non-pull

Input

Non-pull

Input

Non-pull

1)

Digital Video output C bit 0

2)

GPIO

1)

Digital Video output C bit 1

2)

GPIO

1)

Digital Video output C bit 2

2)

GPIO

1)

Digital Video output C bit 3

2)

GPIO

1)

Digital Video output C bit 4

2)

GPIO

43

Page 45

169 C_5

168 C_6

167 C_7

IO_5

(RD21)

IO_6

(RD22)

IO_7

(RD23)

177 IO_17 (DQM2)

Input

Non-pull

Input

Non-pull

Input

Non-pull

Input

Non-pull

1)

Digital Video output C bit 5

2)

GPIO

1)

Digital Video output C bit 6

2)

GPIO

1)

Digital Video output C bit 7

2)

GPIO

GPIO

166 YUVCLK

165 Y_0

164 Y_1

163 Y_2

162 Y_3

161 Y_4

159 Y_5

158 Y_6

157 Y_7

155 RA4

154 RA5

153 RA6

152 RA7

151 RA8

150 RA9

149 RA11

IO_8

(DQM3)

IO_9

(RD24)

IO_10

(RD25)

IO_11

(RD26)

IO_12

(RD27)

IO_13

(RD28)

IO_14

(RD29)

IO_15

(RD30)

IO_16

(RD31)

Input

Non-pull

Input

Non-pull

Input

Non-pull

Input

Non-pull

Input

Non-pull

Input

Non-pull

Input

Non-pull

Input

Non-pull

Input

Non-pull

Input

Input

Input

Input

Input DRAM address 8

Input

Input

Pull-Down

1)

Digital Video output Clock

2)

GPIO

1)

Digital Video output Y bit 0

2)

GPIO

1)

Digital Video output Y bit 1

2)

GPIO

1)

Digital Video output Y bit 2

2)

GPIO

1)

Digital Video output Y bit 3

2)

GPIO

1)

Digital Video output Y bit 4

2)

GPIO

1)

Digital Video output Y bit 5

2)

GPIO

1)

Digital Video output Y bit 6

2)

GPIO

1)

Digital Video output Y bit 7

2)

GPIO

DRAM address 4

DRAM address 5

DRAM address 6

DRAM address 7

DRAM address 9

DRAM address bit 11

147 CKE

146 RCLK

144 RA3

143 RA2

141 RA1

140 RA0

139 RA10

138 BA1

137 BA0

136 RCS#

135 RAS#

output DRAM clock enable

Input Dram clock

Input

Input

Input

Input

Input

Input

Input

output DRAM chip select, active low

output DRAM row address strobe, active low

DRAM address 3

DRAM address 2

DRAM address 1

DRAM address 0

DRAM address 10

DRAM bank address 1

DRAM bank address 0

44

Page 46

134 CAS#

133 RWE#

132 DQM1

130 IO_18 (DQS1)

129 RD8

128 RD9

127 RD10

126 RD11

125 RD12

124 RD13

123 RD14

122 RD15

121 RD0

120 RD1

119 RD2

117 RD3

116 RD4

115 RD5

114 RD6

113 RD7

112 IO_19 (DQS0)

111 DQM0

output DRAM column address strobe, active low

output DRAM Write enable, active low

Input

Input Non-pull

Input

Input DRAM data 9

Input

Input

Input

Input

Input

Input

Input

Input

Input

Input

Input

Input

Input

Input

Input

Non-pull

Input

Data mask 1

GPIO

DRAM data 8

DRAM data 10

DRAM data 11

DRAM data 12

DRAM data 13

DRAM data 14

DRAM data 15

DRAM data 0

DRAM data 1

DRAM data 2

DRAM data 3

DRAM data 4

DRAM data 5

DRAM data 6

DRAM data 7

GPIO

Data mask 0

JTAG Interface( 4 )

Serial interface port 3 data-out

1)

51 TDI V_ADIN4 Input Non-pull

52 TMS V_ADIN5 Input Non-pull

53 TCK V_ADIN6 Input Non-pull

54 TDO V_ADIN7 Input Non-pull

Version AD input port 4

2)

GPIO

3)

Serial interface port 3 data-in

1)

Version AD input port 5

2)

GPIO

3)

1)

Serial interface port 3 clock pin

2)

Version AD input port 6

3)

GPIO

1)

Serial interface port 3 chip-select

2)

Version AD input port 7

3)

GPO

Note:

1. The Main column is the main function, Alt. Means alternative function.

2. The multi-function GPIO pins are set to green characters.

3. The video input port and external TV encoder mode can not both use CCIR-601 mode, at

least one of them should be in CCIR-656 mode.

4. Following is a summary of modified pins.

(a) Pin 48, 49, 50, 51 are no longer for JTAG functions.

(b) V_ADIN0 and V_ADIN3 is not available.

45

Page 47

3.24C16

2-Wire Serial CMOS E2PROM 16k ( 2048 x 8 )

The AT24C16 provides 16384 bits of serial electrically erasable and program mable read

only memory (EEPROM) organized as 2048 words of 8 bits each. The device is optimized f or

use in many industrial and commercial applications where low power and low voltage

operation are essential. The AT24C16 is available in space saving 8-pin PDIP, 8-pin and

14-pin SOIC packages and is accessed via a 2-wire serial interface. In addition, the entire

family is available in 5.0V(4.5V to 5.5V), 2.7V(2.7V to 5.5V) and 1.8V(1.8V to 5.5V) versions.

46

Page 48

47

Page 49

48

Page 50

4. NJM4558

DUAL OPERATIONAL AMPLIFIER

49

Page 51

5. BA033

Low saturation voltage type 3-pin regulator

50

Page 52

ICS ON HI-VOLTAGE BOARD

1. BIT3193

High Performance PWM Controller

BIT3193 integrated circuit provides the essential features for general purpose PWM

controller in a small low cost 16-pin package. BIT3193 has built-in a low frequency PWM

generator for any specified application. BIT3193 includes latched off protection feature may

make the system more reliable while compare to other similar products.

·Features

·4.5V ~ 8V operation

·Fixed High Frequency, Voltage Mode PWM Control

·Latched Off Protection

·Build-In Low Frequency PWM Generator

·Build-in UVLO

·Low Power CMOS Process

·Totem Pole Output

·16 Pin Package

·Applications

·DC/DC Converters

·LCD TV

·LCD Monitor

·Notebook Computer

·Tablet PC

·Personal Digital Assistants

·Navigation Phone/ Door Phone

·Portable consumer product

·Recommended Operating Condition:

Supply Voltage 4.5~8V

Operating Ambient Temperature 0~70 °C

Operating Frequency 50K~400K Hz

·Pin Layout:

1 16

INN MODSEL

CMP ISEN

LOAD CLAMP

CTOSC PWMDC

TIMER CTPWM

ONOFF PWMOUT

GND VDD

NOUT2 NOUT1

8 9

51

Page 53

·Pin Description

Pin

No.

1 INN I/O The i nve rting input of the error amplifier.

2 CMP O Output of the error amplifier.

3 LOAD I/O A switch that connected to the high frequency triangle wave generator.

4 CTOSC I/O An external capacitor connected here can set the frequency of high

5 TIMER I/O With internal reference current and an external capacitor connected here

6 ONOFF I The control pin of turning on or off the IC.1V threshold with an internal 80K

7 GND I/O The ground pin of the device.

8 NOUT2 O The number 2 output driver for driving the NMOSFET switch.

9 NOUT1 O The number 1 output driver for driving the NMOSFET switch.

10 VDD I The power supplies pin of the device.

11 PWMOUT O The output pin of low frequency PWM generator. A 2.5V or floating two

12 CTPWM I/O With the internal reference current and an external capacitor connected

13 PWMDC I Low frequency PWM controlling input. A PWM output comes out by

14 CLAMP I

15 ISEN I Load current detection pin, the open load situation is detected if a less than

16 MODSEL O To set the output polarity of the low frequency PWM controller.

Symbol I/O Descriptions

This switch is op en while ISEN pin <1.3V. An e xternal resistor conne cted

here may change the operation frequency of CTOSC in open load situation.

frequency PWM controller.

can set the required period of starting and the timing of initialization. The

controller is forced to reset mode while TIMER<0.3V. During reset mode,

a~60uA current will flow into the INN pin to reduce the output level of the

error amplifier CMP to turn off the controller. The latched off protection

function will be enable after this node is charged to>2.5V. System is latched

off if any abnormal operation is detected if pin TIMER>2.5V.

The output current of this pin is 20uA when TIMER<0.3V.

The output current becomes to 1uA when TIMER>0.3V.

±15% ohm pull-low resistor.

state output is provided through this pin.

The internal circuit limits the max. Duty-cycle to ~92%.

here can set the operation frequency of low frequency PWM generator with

1.0V~2.5V triangle wave output.

comparing this DC input and the 1.0~2.5V triangle wave that is generated

by CTPWM.

Over voltage clamping. If a>2.0V voltage is detected. A~60uA current will

flow into the INN pin to reduce the output of the error amplifier pin CMP to

regulate the output voltage.

1.3V input is sensed.

52

Page 54

1. Analog front end

1CON1

1

2

3

4

5

6

7

8

9

10

11

12

13

CON1402H

1

2

3

4

5

6

7

8

9

10

11

12

13

15

14

13

12

11

7

8

2

4

6

DVD-IR

GND

DVD-L

GND

DVD-R

DVD-16V

GND

GND

CON\VGA15S

1CN1

RCA JACK

1

3

5

1CN2

DSWK-4

2 4

1

2R39 100R

2R18 100R

2R16 100R

5V

5V

1CN4

10

5

9

4

8

3

7

2

6

1

1U12

PESD5V0L5

AV-S/VIDEO-L-IN

AV-S/VIDEO-R-IN

13456

1U9

PESD5V0L5

34

3

12

3FB1

FB0410

CON1002H

1CON4

DDC/SCL

VGA/HS

VGA/VS

DDC/5V

VGA/B

VGA/G

VGA/R

1U8

PESD5V0L5

1

3

4

5

6

2

PB

10

9

8

7

6

5

4

3

2

1

PLAY

STOP

EJECT

D-LOCK

DVD-IR

DVD-PW

AV-S/VIDEO-L-IN

AV-S/VIDEO-R-IN

DDC/SDA

1

VGA/VS

3

VGA/HS

4

5

6

2

VGA/R

VGA/G

VGA/B

12

GND

10

PLAY

9

8

STOP

7

EJECT

GND

6

5

DVD-B

GND

4

3

DVD-G

GND

2

DVD-R

1

DDC/SDA

DDC/SCL

CHECK

D-LOCK

2

SVIDOI-Y

SVIDOI-C

DTB

13456

1U13

PESD5V0L5

VCC16

PLAY [2]

STOP [2]

EJECT [2]

D-LOCK [2]

DVD-IR 2 [2]

DVD-PW 2 [2]

AV-S/VIDEO-L-IN 3 [3]

DAV-S/VIDEO-R-IN 3 [3]

VGA/R

VGA/G

VGA/B

VGA/VS

VGA/HS

DDC/SCL

DDC/SDA

DDC/5V

YPBPR-R-IN

YPBPR-L-IN

3C87

2

DVD-R

DVD-G

DVD-B

1 2

1FB5 PB1 2

1FB6 PB1 2

1FB7 PB1 2

1FB10 PB/01 2

1FB11 PB/01 2

1N4148/NC

1D14

1D15

1N4148/NC

1FB13 PB

L0603

DDC/SCL

1D22

PACDN042

3

2 1

DDC/SDA

0.1uF

1L17 PB

1 2

1L19 PB

L0603

21

21

1EC10

10uF/16V

12

L0603

1R54

1R55

2.2K

RCA JACK

7

8

2

4

6

2.2K

1C58

22pF

VCC5

1R6

75R/1%

1CN3

1

3

5

1U11

PESD5V0L5

1L12 PB

1 2

1R25

75R/1%

1L14 PB

1 2

1R26

75R/1%

1L16 PB

1 2

L0603

1R27

75R/1%

1R32

2.2K

1R35

2.2K

1C53

22pF

1FB1

1 2

1FB9 PB/01 2

1C59

22pF

1EC8

10uF

VCC5V

GND

13456

L0603

L0603

1C39

5pF/NC

1C43

5pF/NC

1C54

22pF

PB/0

DDC-VCLK

1C60

100nF

1C70

0.1uF

2

1C34

22pF/NC

1C36

22pF/NC

1C38

22pF/NC

1R31

100

1R33

100

1C55

22pF

1C57

5pF

1R57 100R

1R58 100R

1R63 100/NC

Part 4 Detailed Circuit

MAIN BOARD

2CON8

21

SHIELD

SCART-CVBS1

20

V/YIN

CVBS_OUT

19

VOUT

18

BLKGND

17

VGND

SCART-FB

16

BLK

SCART-R

15

R

14

DGND

13

RGND

12

DATA

SCART-G

11

G

10

CLK

9

GGND

SCART-CHECK

8

SW

AIL

BGND

AGND

AOL

AIR

AOR

CON\SCART21

1U15

PESD5V0L5

1

3

4

5

6

2

+

1EC7

16

100uF/16V

VCC

12

4A

9

3A

7

2A

4

1A

15

OE

1C47

GND

22pF/NC

8

14

3

1R45 100

1Y

VCC

1R46 100

6

2Y

8

1R48 100

3Y

1R49 100

11

4Y

GND

1R51

10K

7

1

1R56

100

1Q4

2N3904

2 3

1Q5

2N3904

7

B

6

5

4

3

2

1

SCART-B

SCART-G

SCART-R

SCART-CVBS1

SCART-FB

1 2

1C40

100nF

1C48

22pF/NC

1R52

10K

FAIRCHILD 74VHC125 &

74LVX125 can be used

1L18 PB

L0603

SCART-B

SCART-A-L-IN

SCART-A-R-IN

1C49

22pF/NC

1C52

100nF

1R74

75R/1%/NC

SCART-B

ADC-VS

ADC-HS

1R75

75R/1%/NC

SCART-A-OUTR [3]

1R67

75R

VCC5V

1R76

75R/1%/NC

1R72

75R

1R73

75R

20R/1%

1R34

20R/1%

1R36

20R/1%

1R37

SCART-A-OUTL [3]

1R77

75R

1R82

75R

the RGB ter m i n al

network clo se to

A/D

1C41 104

1C44

1C46 104

DVD-VSI

DVD-HSI

1R50 100R

1R53 100R

1C56

5pF

DDC-SCL

DDC-SDA

1R65

0R

GND

1R3

75R/1%

1R13

75R/1%

YPBPR-Y-IN

1R1575R/1%

YPbPr-Pb-IN

1R24

75R/1%

YPBPR-PR-IN

1R19

75R/1%

7

6

5

AUX1-CVBS

1R5

1C6

0.1uF

20R/1%

SVH-Y

1C1

1R2

0.1uF

20R/1%

SVH-C

1R66

1C12

20R/1%

0.1uF

1R14

20R/1%

1R18

20R/1%

1R21

20R/1%

DVD-RIN

DVD-GIN

DVD-BIN

VGA-RI

1R40

75R/1%

VGA-GI

1R43

75R/1%

VGA-BI

1R47

75R/1%

VGA-VSI

VGA-HSI

D-PW[2]

1U3

AT24C21/NC

SOP08

84

1

NC

VCLK

2

NC

VCCGND

3

NC

SCL

SDA

YPbPr-Y

1C20

104

YPbPr-Pb

1C25

104

YPbPr-Pr

1C31

104

VGA-RI

14

4B1

11

VGA-GI

3B1

VGA-BI

5

2B1

2

1B1

13

DVD-RIN

4B2

10

DVD-GIN

3B2

6

DVD-BIN

2B2

3

1C66

22pF

VGA-HSI

DVD-HSI

VGA-VSI

DVD-VSI

1C68

22pF

DVD-PW

1B2

1C65

1C45

1

S

22pF

22pF

1U1

FSAV330

TSSOP16

1U2

74LVS125

SO14

1

1C

2

1A

4

2C

5

2A

10

3C

9

3A

13

4C

12

4A

1C69

22pF

1R60

100

1=PC

DVD=0

1

1R59

1k

2 3

1U6

PESD5V0L5

SCART-G [2]

SCART-R [2]

SCART-CVBS1

SCART-FB [ 2]

1O4

SCART-A-OUTR

1

SCART-A-R-IN

3

SCART-A-OUTL

4

5

6

2

SCART-CHECK

SCART-B [2]

ADC-R

ADC-G

ADC-B

VCC9V

1R84

1R86

47K

1R83

47K

10K

TUNER_AUDIO_MONO

1C16

TV-5V

0.1uF

TUNCVBSA

SIF_AUDIO

1R28 OR EUROPE

1R28 1K FOR USA AND JAPAN

1R28 OR

SDA

1R29 0 R

SCL

1R30 0 R

+5V-TV

1R9

75R/1%/NC

1C37

20PF

SVH-Y

AUX1-CVBS

SVH-C

YPbPr-Y

YPbPr-Pb

YPbPr-Pr

ADC-HS

ADC-VS

YPbPr-Pr

+5V-TV

GND

CHECK

47K

1R87

47K

20PF

SCART-A-R [3]

SCART-A-L [3]

SCEL

TUNER5V

1C15

1FB27F B0410

1FB28F B0410

1R41

20R/1%

ADC-G 2 [ 2]

AUX1-CVBS 2 [2]

SVH-C 2 [2]

YPbPr-Y 2 [2]

YPbPr-Pb 2 [2]

YPbPr-Pr 2 [2]

ADC-HS 2

ADC-VS 2 [2]

YPbPr-Pr 2 [2]

+5V-TV 4 [4]

GND [2,3,4]

CHECK 2 [2]

SCART-CVBS1

SCART-CVBS1 [2]

CVBS_OUT

CVBS_OUT 2 [2]

SCART-FB

SCART-FB [2]

SCART-R

SCART-R [2]

SCART-G

SCART-G [2]

SCART-B

SCART-B [2]

SCART-SW

SCART-SW [2]

SCART-A-OUTL

SCART-A-OUTL [3]

SCART-A-OUTR

SCART-A-OUTR [3]

SCART-A-L

SCART-A-L [3]

SCART-A-R

SCART-A-R [3]

YPBPR-R-IN

YPBPR-R-IN 3[3]

YPBPR-L-IN

YPBPR-L-IN 3[3]

MPE05-1-E

1TU1

1

AGMONO

2

IFSUP

3

VCVBS

4

IF-VIDIO

5

NC

6

NC1

7

NA

8

NA1

9

18

SCEL

TH1

10

11

12

13

14

TV-5V

12

TUNER5V

12

VCC5V

VCC9V

MONO-1

TV-CVBS

DDC-SCL

DDC-SDA

SIF_AUDIO

ADC-G

ADC-B

ADC-R

DVD-L

DVD-R

D-LOCK

DTB

SDA

SCL

1EC2

220uF/10V

220uF/16V

SDA

SCL

TV5V

TVMONO

AFOUT

17

TH2

16

TH3

15

TH4

1C42

0.01uF

1C35

1EC3

0.1uF

TV-CVBS

1C51

0.1uF

VCC5V 2 [2,3,4]

VCC9V 3 [2, 3]

MONO 3 [3]

TV-CVBS 2 [2]

DDC-SCL 2 [2]

DDC-SDA 2 [2]

SIF_AUDIO 3 [3]

ADC-G 3 [2]

ADC-B 3 [2]

ADC-R 3 [2]

DVD-L 2 [3]

DVD-R 2 [3]

D-LOCK [2]

DTB 2 [2]

SDA 2 [2,3]

SCL 2 [2,3]

3EC52 2 2uF/10V

1R78

47K

3EC62 2 2uF/10V

1R79

47K

1C32

0.1uF

SCART-SW

1R80

33K

1R81

MONO-1

GND

1R44

75R/1%

53

Page 55

2. Hudson

ADC-R

CON-1.25

2CON3

1

2

3

4

5

6

7

8

1C67

0.1uF

1C67 1C71 1C72 1C73 1C74 1C75 ESD--AVL 14K03300

CVBS_OUT

2L21 PB06031 2

2L23 PB06031 2

2L24 PB06031 2

2L25 PB06031 2

2L26 PB06031 2

2L27 PB06031 2

2L28 PB06031 2

2L29 PB06031 2

1C73

1C75

1C72

1C74

1C71

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

2R1

DVD-IR

100

IR-IN

IR-VCC

1

2R9 100R

2

2R10 1.2K

3

2R11 2K

4

5

2CON2

CON-1.25

TO IR LED BOARD

+3.3V_ADC

2L7

PB0805

1 2

2L8

PB0805

1 2

2L9

PB0805

1 2

2L10

PB0805

1 2

2L11

PB0805

1 2

2R17

2R31

470

470/NC

2EC21

1R88

470uF/10V

75

2Q7

3906

2

2Q6

1

3906

3

V3.3V

2R24

2R25

2R23

10K

10K

2C67

0.1uF

23

1

2N3906

2Q3

2C13

100nF

SCART-CVBS1

SCART-G

SCART-R

SCART-B

+1.8VCC

1 2

Supply Current:60mA

2EC16

+

100uF/16V

Supply Current:250mA

2EC17

+

100uF/16V

RING3.3V

2C68

0.1uF

DVD=1

2R8

10K

2R22

10K

SCART-FB

2L12

PB0805

2C36

100nF

2C39

100nF

Supply Current:250mA

2C48

0.1uF

Supply Current:250mA

2C53

0.1uF

10K

2C69

0.1uF

TO KEY BOARD

IR-SW

LED-G

LED-R

ADC-VS

ADC-VS

2C14

20PF

SVH-C

YPbPr-Pb

YPbPr-Y

YPbPr-Pr

1R68

22R/1%

1R70

22R/1%

1R69

22R/1%

1R71

22R/1%

TV-CVBS

AUX1-CVBS

Supply Current:60mA

+

2EC13

100uF/16V

+3.3VCC

1 2

+1.8VCC

1 2

2C40

2C41

100nF

100nF

2C49

0.1uF

2C55

2C54

0.1uF

0.1uF

22PF

2L13

PB0805

2L14

PB0805

2C58

100nF

CODER1.8V

D[0..7]

D3

D6

D1

D0

D2

D4

D5

D7

DTB

ROM_OEN

A10

A7

A4

A8

A9

A1

A2

A3

A0

A6

TV-PW

RESET-3415

VOL-MUTE

AUDIO-SEL0

AUDIO-SEL1

CHECK

SRS-MONO

SRS-STER

151

152

153

154

155

156

150

149

148

147

146

145

144

143

142

141

140

139

138

137

136

135

134

133

132

131

130

129

128

CVDD_18

VID_D7/VID1_D7

VID_D6/VID1_D6

VID_D5/VID1_D5

VID_D4/VID1_D4

VID_D3/VID1_D3

VID_D2/VID1_D2

VID_D1/VID1_D1

VID_D0/VID1_D0

2U5

GENESIS-FLI8125

+1.8V_CORE

AGND_RPLL

XTAL

TCLK

STI_TM2

GPIO15/STI_T M1/EXT_CS

SYNC2

RVSS

CVDD_18

AVDD_RPLL_33

19

17

GND

CSRAM

TEST

TCLK

XTAL

2R47

0R

VCC5V

SDA

SCL

127

RVSS

CVDD_18

VID_DIN23/D7/PD46/VID2_7

VID_DIN22/D6/PD45/VID2_6

VID_DIN21/D5/PD44/VID2_5

VID_DIN20/D4/PD43/VID2_4

VID_DIN19/D3/PD42/VID2_3

VSYNC2

HOST_SCL/UART_DI/JTAG_CLK

HOST_SDA/UART_DO/JTAG_MODE

DDC_SCL

DDC_SDA

RVSS

CVDD_18

29

281832

3031343536373841424344474851524650

M-SCL

MCU-TXD

DDC-SCL

MCU-RXD

DDC-SDA

2R52

2.7K

2R53

2.7K

123

4

2CON6

CON402H

2R20

2.7K

3R70OR

3R71OR

RVSS

RVSS

HSYNC1

RVDD_33

VID_CLK_1/VI D1_CLK

VID_D14/VID 1_14/GP22

VID_D15/VID 1_15/GP23

VID_D13/VID 1_13/GP21

VID_D12/VID 1_12/GP20

GND_RVSS

VDDA33_LBADC

2345678

1

KEY_ADC_IN1

0.1uF

2C37

22pF

LBADC_IN1

LBADC_IN2

LBADC_IN3

LBADC_IN4

LBADC_IN5

ADC_IN4

KEY_ADC_IN3

SCART-SW

KEY_ADC_IN2

2C32

19.6608MHz

2Y1

VID_D11/VID 1_11/GP19

VID_D8/JTRST/VID1_D8/GP16

VID_D10/JT AG_TDI/VID 1_10/GP18

VID_D9/JTAG_TDO/VID1_D9/GP17

VSSA33_LBADC

RESETn

GND_RPLL

VBUFC_RPLL

LBADC_IN6

LBADC_RTN

VDD_RPLL_18

91011131415162021222324252627

12

GND

2C33

0.1uF

2C38

22pF

2C15

SVH-Y

ADC-R

ADC-G

1C61

104

2C28

100nF

2C42

100nF

2C50

0.1uF

+3.3VCCL

2C59

0.1uF

157

VSYNC1

158

VDD18_AB

159

NC

160

GND18_C

161

VDD18_C

162

ADC_TEST

163

AVDD_ADC

164

AGND

165

AGND

166

SV1P

167

GNDS

168

A1P

169

GNDS

170

B1P

171

GNDS

ADC-B

172

C1P

173

AVDD_A

2C21

2R38

174

AN

175

0.1uF

20R/1%

2R41

20R/1%

1C62

104

1C63

104

1C64

104

2R44

20R/1%

1R10

20R/1%

2R45

0R

2R46

20R/1%

2C29

100nF

2C43

100nF

2C51

0.1uF

AGND

176

SV2P

177

GNDS

178

A2P

179

GNDS

180

B2P

181

GNDS

182

C2P

183

AVDD_B

2C23

184

BN

185

0.1uF

AGND

186

SV3P

187

GNDS

188

A3P

189

GNDS

190

B3P

191

GNDS

192

C3P

193

AVDD_C

2C25

194

CN

0.1uF

195

AGND

1C30

196

SV4P

0.1uF

197

GNDS

198

A4P

199

GNDS

200

B4P

201

GNDS

202

C4P

203

AVDD_SC

2C27

204

SVN

205

0.1uF

VO_GND

206

VOUT

207

VDD18_SC

208

GND18_SC

2C62

2C30

100nF

100nF

GND

+3.3_LBADC

2EC14

2C31

2C56

+

100uF/16V

100nF

100nF

Supply Current:60mA

+1.8_RPLL

2EC15

100uF/16V

+

2C57

2C34

100nF

100nF

2R14

10K

2C46

2C47

2C45

2C44

100nF

2C60

0.1uF

2C63

100nF

100nF

100nF

100nF

2C61

2C52

0.1uF

0.1uF

A5

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

RVSS

RVSS

RVSS

RVDD_33

CVDD_18

CVDD_18

VID_DIN16/D0/PD39/VID2_0

VID_DIN17/D1/PD40/VID2_1

VID_DIN18/D2/PD41/VID2_2

RVSS

RVDD_33

I2CM_SCL

I2CM_SDA

GPIO0/LED1/T CK

33

M-SDA

VCC5V

2EC19

100uF/16V

2R21

2.7K

VBI_D6/A9/PD 33/BT1

VBI_D5/A8/PD 32/BT0

VBI_D7/A10/PD34/BT2

VBI_D4/A7/GPIO23/PD31