Page 1

A

1 1

2 2

B

C

D

E

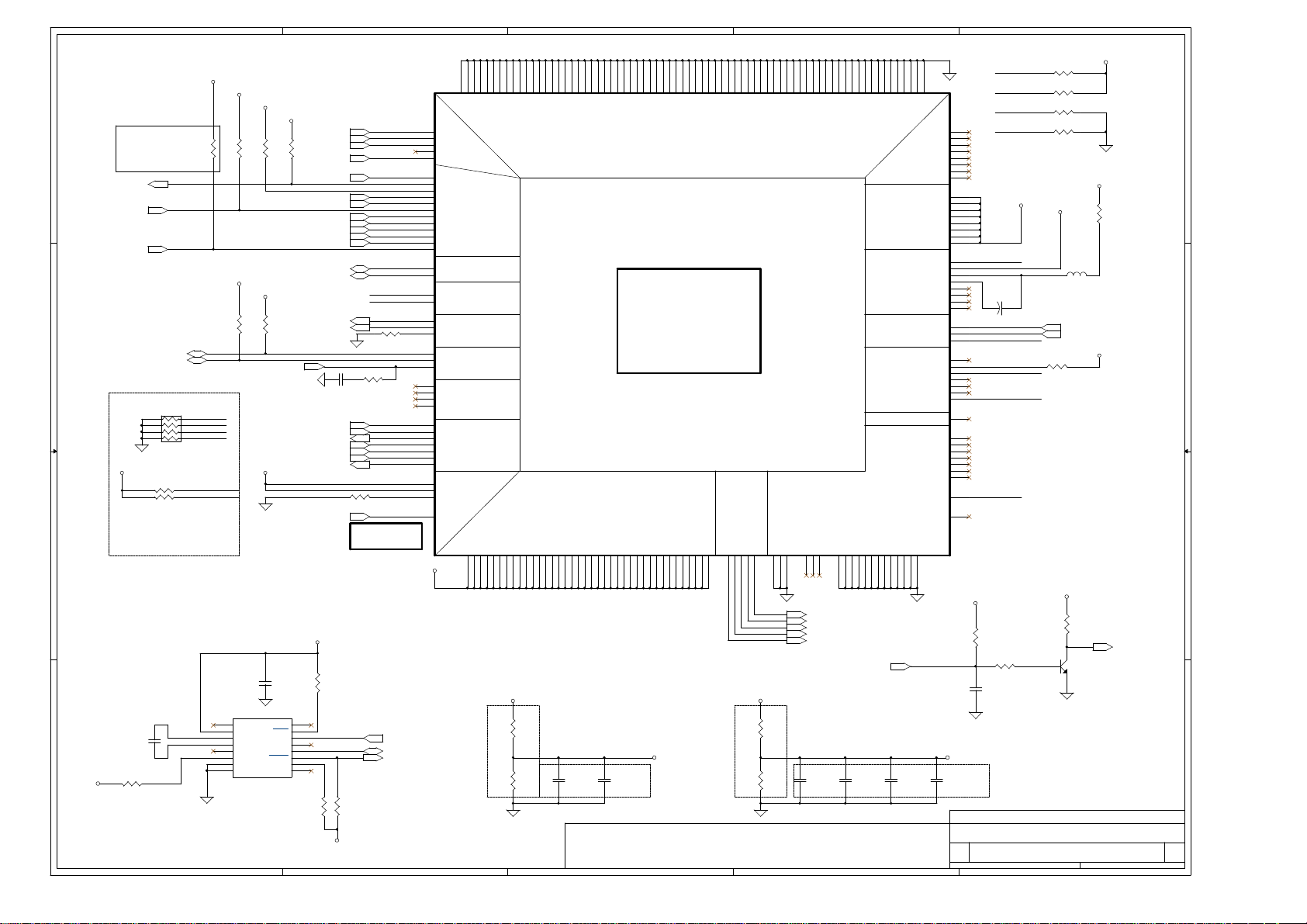

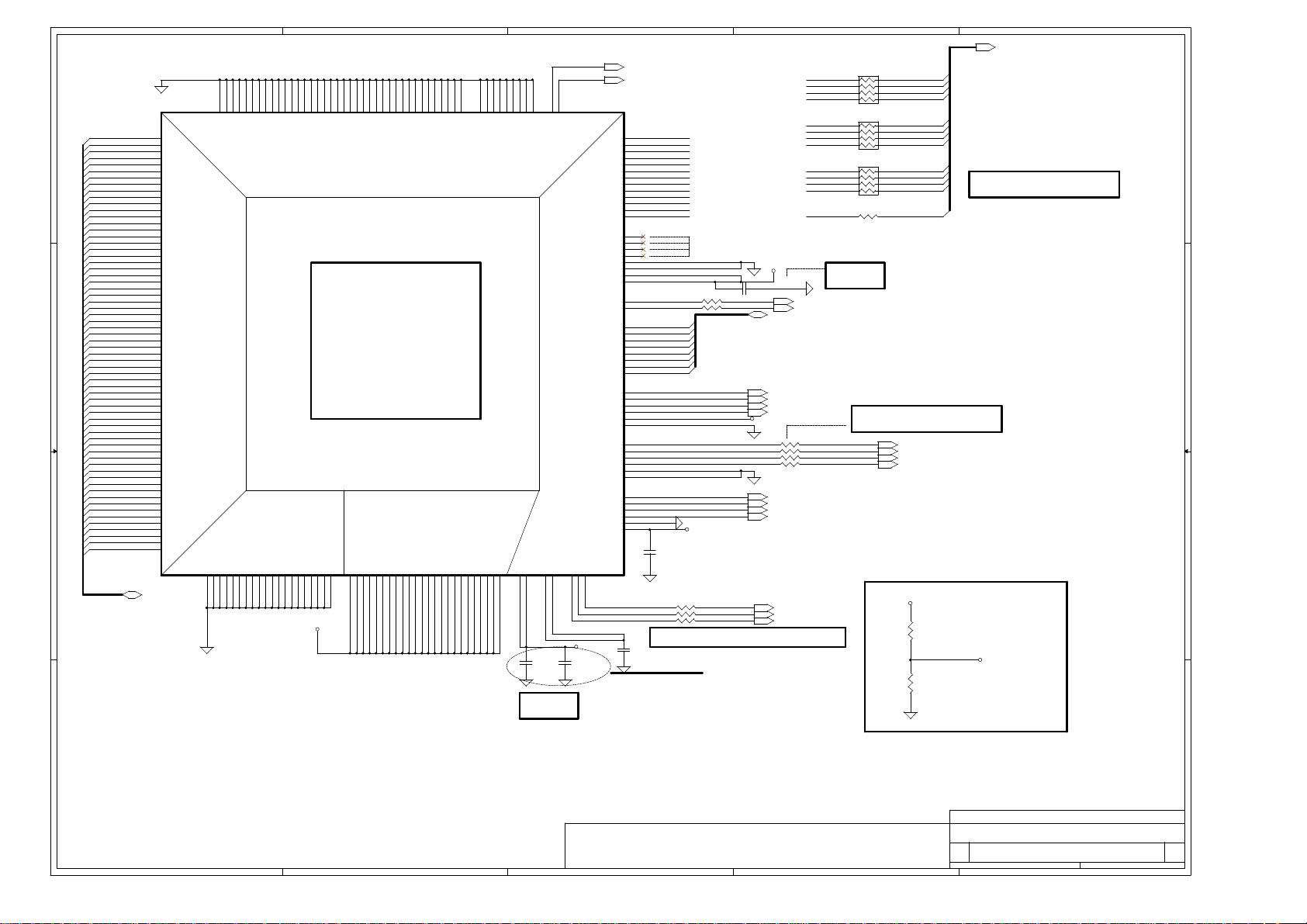

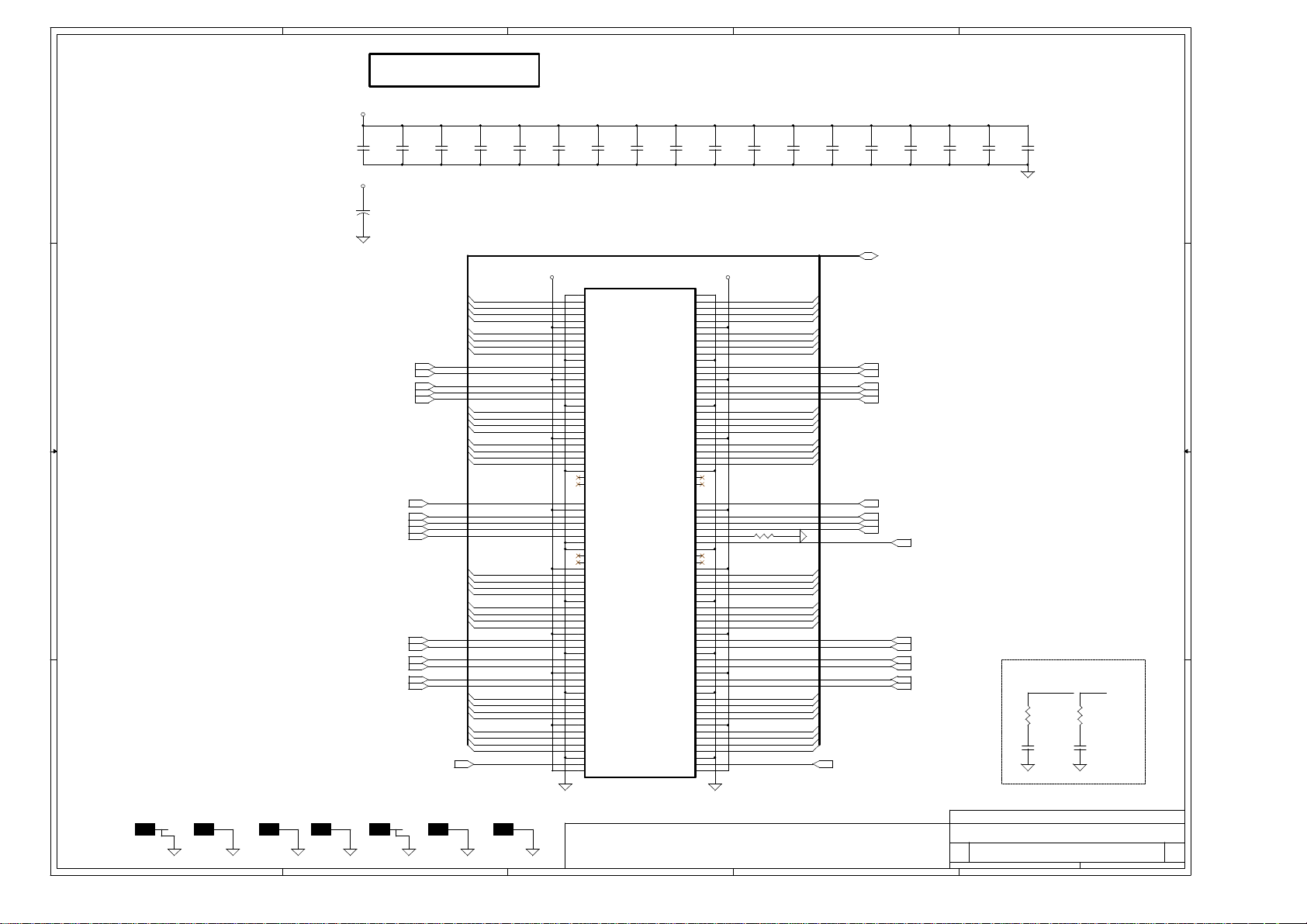

Tang/TangBTO Schematics Document

uFCBGA/uFCPGA Coppermine-T or Tualatin

2001-11-16

3 3

REV: 2.0

4 4

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

A

B

C

D

Title

Size Document Number Rev

Date: Sheet of

Compal Electronics, Inc.

ADY11 LA-1181

Cover Sheet

E

1 41Friday, November 16, 2001

2

Page 2

A

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,I

NC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF

THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE

INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF

COMPAL ELECTRONICS,INC.

Compal confidential

B

C

D

E

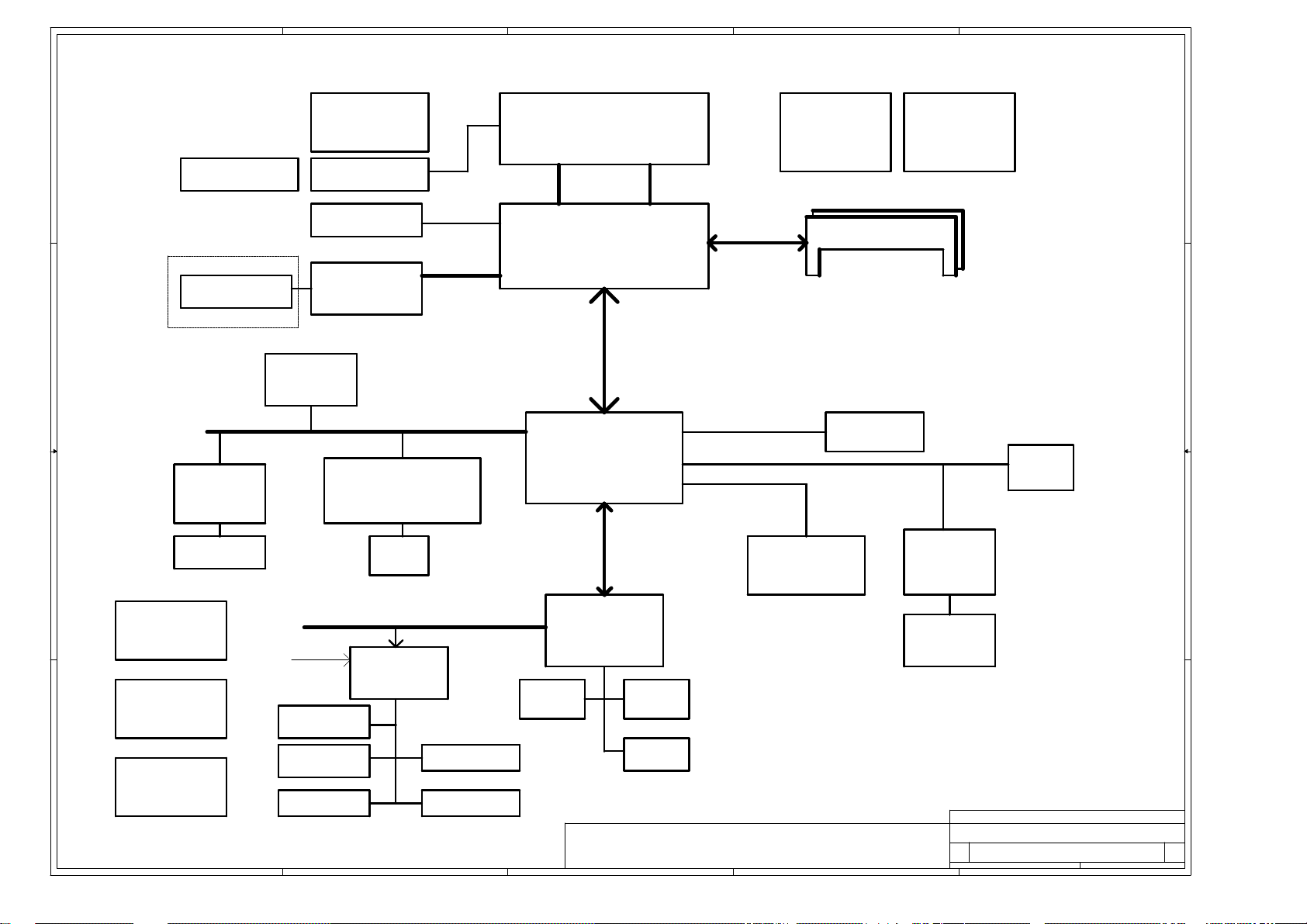

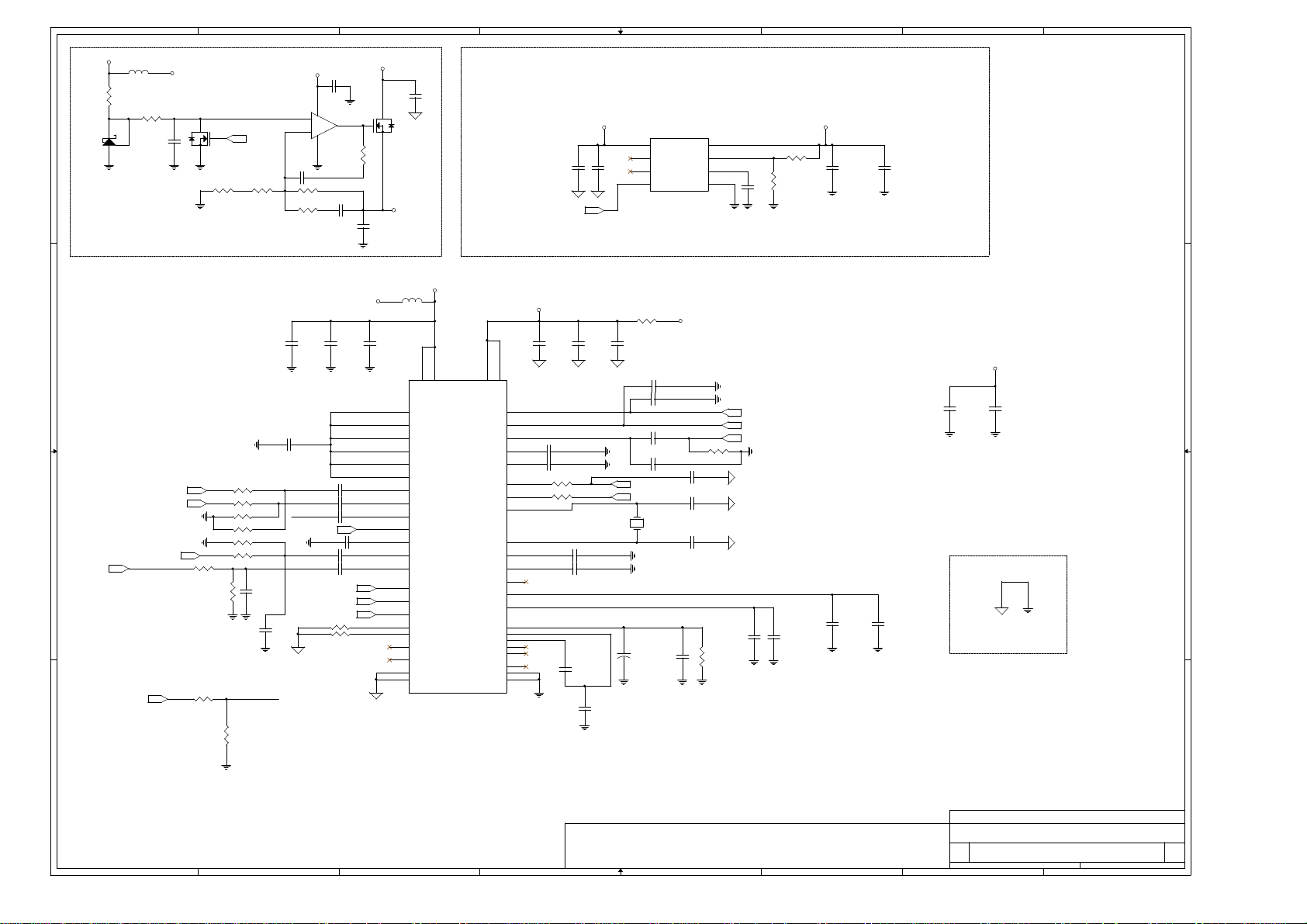

Block Diagram

Model Name :ADY11(Tang)

File Name : LA-1181

CPU Bypass

1 1

Fan Control

page 7

& CPUVID

page 6

ITP Connector

page 7

Coppermine-T or

Tualatin

uFCBGA/uFCPGA CPU

page 4,5

PSB

133MHz

HD#(0..63)HA#(3..31)

Thermal Sensor

Clock Generator

MAX6654 W320-04

page 5

page 14

CRT Connector

page 15

DVO Link

VCH

Board

2 2

VCH Conn

PCI debug

port

page 27

page 15

PCI BUS

IDSEL:AD17

(PIRQA#,GNT# 3,REQ#3)

LAN

3COM -3C920

page 20

A

RJ45

page 30

page 31

page 20

3 3

Power On/Off

Reset & RTC

DC/DC Interface

Suspend

4 4

Power Circuit

DC/DC

page

32,33,34,35,36,37

IDSEL:AD20

(PIRQA/B#,GN T#2,REQ#2)

CardBus Controller

OZ 6912

Slot 0

page 22

14M_5V

Touch Pad

EC I/O Buffer

BIOS

EC 87570

page 27

page 29

page 29 page 27

B

page 21

page 28

3.3V 33MHz

X BUS

Int.KBD

PS/2 conn

page 29

Almador-M

GMCH-M

625 BGA

page 8,9,10

HUB Link

1.8V 66MHz

ICH3-M

421 BGA

page 16,17

LPC BUS

3.3V 33MHz

NS PC87393

LPC to X-BUS

& Super I/O

page 26

SIOPIO

page 27 page 27

FDD

page 19

C

Memory BUS

3.3V 133MHz

3.3V 48MHz

3.3V 24.576MHz

3.3V ATA100

IDE Connector

(HDD/CR-ROM)

SO-DIMM X2

BANK 0, 1, 2, 3

USB conn

page 19

D

page 12,13

page 30

AMP& Phone

Jack

AC-LINK

AC97

Codec

STAC9700

page 23

page 24

Title

Size Document Number Rev

ADY11 LA-1181

Date: Sheet of

MDC

page 25

Compal Electronics, Inc.

Block Diagram

E

2 41Friday, November 16, 2001

2

Page 3

Note:"@" means all model depop

"#" means Tang depop

5

4

3

2

1

Model

Function

TangM2P3

SST-Build

D D

FDD

PS/2

Series port

Parallel port

RJ45

3Com Lan

chipset(3C920)

Note:"@" means all model depop

"&" means M2P3 depop

C C

"#" means Tang depop

YES

YES

NO

YES

YES

NO

YES

NO

YES

NO

NOYES

SST2-Build

PT-Build

ST-Build

FW82830MG FW82801CAM

QB63QB88

QC34 QB62

QC34

QB62 Lot:M28010

QC34 QC42

3C920-ST06CHIPS Rev CHIPS Rev

Lot:M28010

DC:C0117

Lot:M28010

DC:C0117

DC:C0117

Lot:M28010

DC:C0117

B B

A A

Compal Electronics, Inc.

Title

Note & Revision

Size Document Number Rev

5

4

3

2

Date: Sheet of

ADY11 LA-1181

3 41Friday, November 16, 2001

1

2

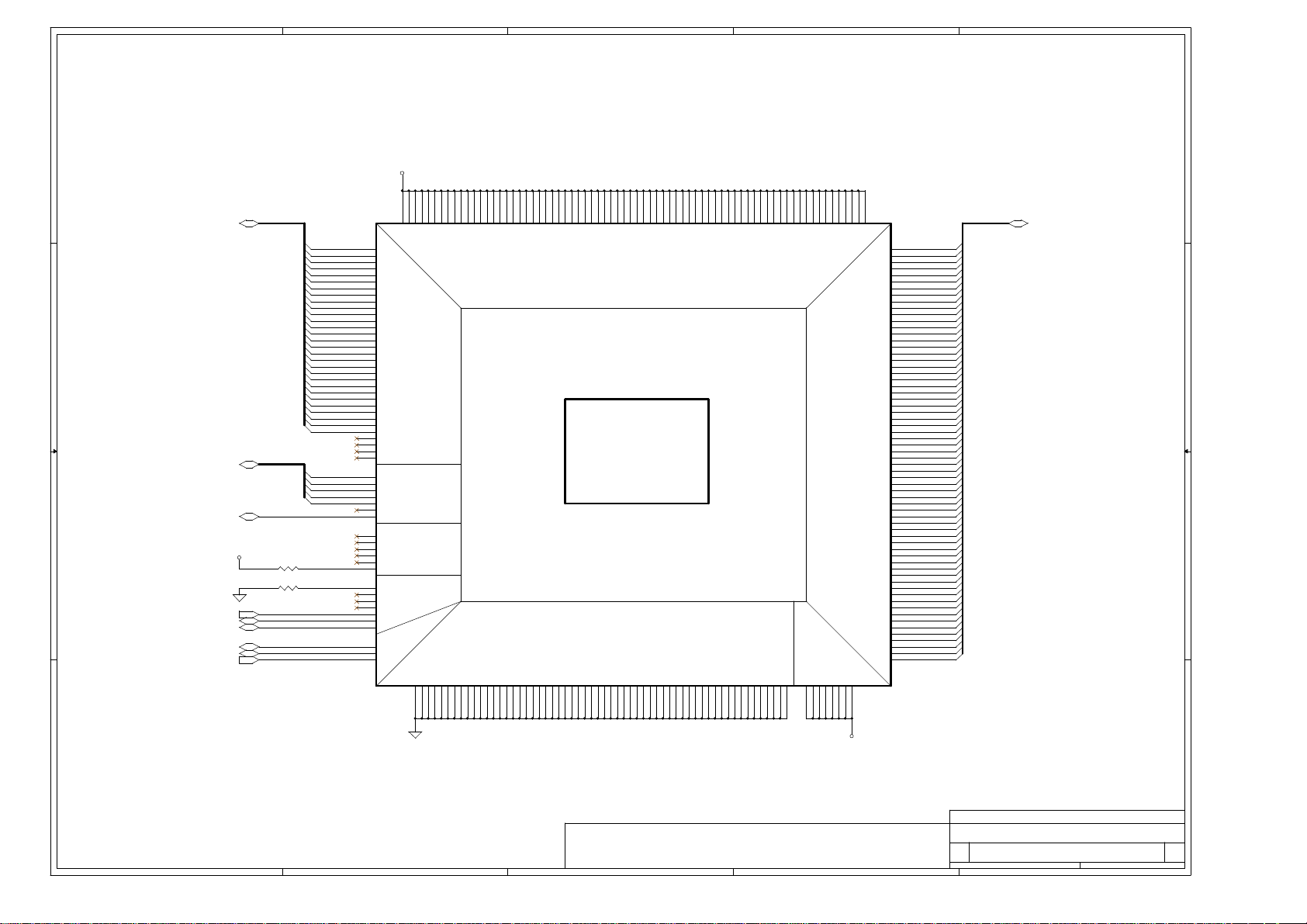

Page 4

A

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,I

NC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF

THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE

INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF

COMPAL ELECTRONICS,INC.

1 1

+1.5VS

HA#[3..31]

HREQ#[0..4]

R108 1.5K

1 2

R121 10_0402

1 2

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HA#[3..31]<8>

2 2

HREQ#[0..4]<8>

HADS#<8>

3 3

HBPRI#<8>

HBNR#<8>

HLOCK#<8>

HIT#<8>

HITM#<8>

HDEFER#<8>

AF23

AD23

K1

G2

K3

H3

G1

A3

H1

D3

F3

G3

C2

B5

B11

C6

B9

B7

C8

A8

A10

B3

A13

A9

C3

C12

C10

A6

A15

A14

B13

A12

R1

L3

T1

U1

L1

T4

AA3

W2

AB3

P3

C14

AF4

A7

C4

C22

R2

L2

V3

AA2

U2

T3

J1

J2

J3

B

+CPU_CORE

U5A

A#3

A#4

A#5

A#6

A#7

A#8

A#9

A#10

A#11

A#12

A#13

A#14

A#15

A#16

A#17

A#18

A#19

A#20

A#21

A#22

A#23

A#24

A#25

A#26

A#27

A#28

A#29

A#30

A#31

A#32

A#33

A#34

A#35

REQ#0

REQ#1

REQ#2

REQ#3

REQ#4

RP#

ADS#

AERR#

AP#0

AP#1

BERR#

BINIT#

IERR#

BREQ0#

NC

NC

NC

BPRI#

BNR#

LOCK#

HIT#

HITM#

DEFER#

TUALATIN

D22

F22

E21

H22

VCC_0

VCC_1

VCC_2

Address

Lines

Request

Signals

Error

Interface

Arbitration

Signals

Snoop

Signals

VSS_0

E16R4E25

G21

VCC_3

VCC_4

VSS_1

VSS_2

K22

VCC_5

VSS_3

G25

J21

VCC_6

VSS_4

J25

M22

VCC_7

VSS_5

L25

L21

VCC_8

VSS_6

N25

P22

VCC_9

VSS_7

R25

N21

T22

VCC_10

VSS_8

U25

W25

R21

V22

VCC_11

VCC_12

VSS_9

VSS_10

AA25

AC25

U21

Y22

VCC_13

VCC_14

VSS_11

VSS_12

AF25

AE26

W21

AB22

VCC_15

VCC_16

VSS_13

VSS_14

C23

F23

AA21

AC21

VCC_17

VCC_18

VSS_15

VSS_16

H23

K23

D20

VCC_19

VCC_20

VSS_17

VSS_18

M23

F20

E19

VCC_21

VSS_19

P23

T23

AB20

VCC_22

VCC_23

VSS_20

VSS_21

V23

AA19

AC19

VCC_24

VSS_22

Y23

AB23

D18

F18

VCC_25

VCC_26

VSS_23

VSS_24

AE23

B22

E17

VCC_27

VCC_28

VSS_25

VSS_26

D21

C

AB18

AA17

AC17

D16

F16

E15

AB16

AA15

AC15

D14

F14

E13

AB14

AA13

AC13

D12

F12

E11

AB12

AA11

AC11

D10

VCC_29

VCC_30

VCC_31

VCC_32

VCC_33

VCC_34

VCC_35

VCC_36

VCC_37

VCC_38

VCC_39

VCC_40

VCC_41

VCC_42

VCC_43

VCC_44

VCC_45

VCC_46

VCC_47

VCC_48

VCC_49

VCC_50

VCC

Mobile

Tualatin

VSS VCC

VSS_27

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

VSS_40

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

F21

E22

H21

G22

K21

J22

M21

L22

P21

N22

T21

R22

V21

U22

Y21

VSS_48

W22

AB21

AA22

AC22

AE21

B20

D19

F10E9AB10

VCC_51

VCC_52

VSS_49

VSS_50

AB19

AA20

AC20

AA9

AC9D8F8E7AB8

VCC_53

VCC_54

VCC_55

VSS_51

VSS_52

VSS_53

AE19

B18

VCC_56

VSS_54

D17

F17

VCC_57

VCC_58

VSS_55

VSS_56

E18

AB17

AA7

VCC_59

VSS_57

D

AC7D6F6E5H6G5K6J5N5T6V6

VCC_61

VCC_62

VCC_63

VCC_64

VCC_65

VCC_66

VCC_67

VCC_68

VCC_69

Data

Signals

VCC_74

VCC_75

VCC_76

VCC_77

VCC_78

VCC_79

VCC_80

U5Y6W5

AB6

AA5

AC5M6P6

VCC_70

VCC_71

VCC_73

VCC_72

D#0

D#1

D#2

D#3

D#4

D#5

D#6

D#7

D#8

D#9

D#10

D#11

D#12

D#13

D#14

D#15

D#16

D#17

D#18

D#19

D#20

D#21

D#22

D#23

D#24

D#25

D#26

D#27

D#28

D#29

D#30

D#31

D#32

D#33

D#34

D#35

D#36

D#37

D#38

D#39

D#40

D#41

D#42

D#43

D#44

D#45

D#46

D#47

D#48

D#49

D#50

D#51

D#52

D#53

D#54

D#55

D#56

D#57

D#58

D#59

D#60

D#61

D#62

D#63

A16

B17

A17

D23

B19

C20

C16

A20

A22

A19

A23

A24

C18

D24

B24

A18

E23

B21

B23

E26

C24

F24

D25

E24

B25

G24

H24

F26

L24

H25

C26

K24

G26

K25

J24

K26

F25

N26

J26

M24

U26

P25

L26

R24

R26

M25

V25

T24

M26

P24

AA26

T26

U24

Y25

W26

V26

AB25

T25

Y24

W24

Y26

AB24

AA24

V24

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

HD#[0..63]

E

HD#[0..63] <8>

4 4

A

+CPU_CORE

Title

Size Document Number Rev

B

C

D

Date: Sheet of

Compal Electronics, Inc.

Mobile Tualatin uFCPGA

ADY11 LA-1181

4 41Friday, November 16, 2001

E

2

Page 5

A

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,I

NC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF

THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE

INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF

COMPAL ELECTRONICS,INC.

+VTT

+1.8VS

+1.5VS

+1.5VS

PICD0<16>

PICD1<16>

1 8

2 7

3 6

4 5

12

12

R_K

R28

56.2_1%

1 1

2 2

Place

R_K<0.1"

from CPU

H_FERR#<16>

H_PWRGD<16>

H_RESET#<8>

RP6 8P4R_1.5K

+VTT

R136 1.5K

R38 56.2_1%

12

ITP_TDI

ITP_TMS

ITP_TRST#

ITP_TCK

ITP_PREQ#

ITP_PRDY#

R18

1.5K

+1.5VS

R36

150

12

12

+VS_CMOSREF

R19

3K

+1.5VS

R37

150

12

12

R24

1.5K

12

CLK_CPU_APIC<14>

PM_CPUPERF#<16>

H_RS#0<8>

H_RS#1<8>

H_RS#2<8>

H_TRDY#<8>

H_A20M#<16>

H_IGNNE#<16>

H_SMI#<16>

H_STPCLK#<16>

H_DPSLP#<16,32>

H_INTR<16>

H_NMI<16>

H_INIT#<16>

H_DBSY#<8>

H_DRDY#<8>

H_BSEL0<14>

H_BSEL1<14>

@10PF_0402

ITP_TCK<7>

ITP_TDI<7>

ITP_TDO<7>

ITP_TMS<7>

ITP_TRST#<7>

ITP_PREQ#<7>

ITP_PRDY#<7>

C38

1 2

R30 56.2_1%

If used ITP port mu st depop

3 3

C35

.1UF_0402

1 2

STBY

SMBCLK

ALERT

ADD0

NC

NC

1K_0402

+5VALW

R26

10K_0402

1 2

16

15

14

13

12

11

10

R23

1 2

+5VALW

R27

1 2

W=15mil

Thermal Sensor

MAX6654MEE

U6

1

NC

12

H_THERMDA

H_THERMDC

C34

2200PF

4 4

+5VALW

R29 1K_0402

12

2

VCC

3

DXP

4

DXN

5

NC

SMBDATA

6

ADD1

7

GND

8 9

GND NC

MAX6654MEE

Address :1001_110X

A

H_A20M#

H_IGNNE#

H_INTR

H_NMI

H_THERMDA

H_THERMDC

1 2

R34 110_1%

R35

1 2

@33_0402

ITP_TCK

ITP_TDI

ITP_TDO

ITP_TMS

ITP_TRST#

ITP_PREQ#

ITP_PRDY#

Note :

GHI# Pull-Up internally

SMB_EC_CK1 <15,28,29,33>

SMB_EC_DA1 <15,28,29,33>

THRM# <29>

10K_0402

B

AA18

AC18

AE17

B16

D15

F15

AB15

AA16

AC16

AE15

B14

D13

F13

E14

AB13

AA14

AC14

U5B

VSS_58

VSS_59

VSS_60

VSS_61

VSS_62

VSS_63

VSS_64

VSS_65

VSS_66

APIC

Debug

Break

Point

Test

Access

PORT

( ITP )

VCCT_2

VCCT_3

J23

L23

VCCT_4

VCCT_5

N23

R23

+1.5VS

R_E

R_F

VCCT_6

VCCT_7

U23

W23

12

12

VSS_67

VCCT_8

VCCT_9

AA23

R20

499_1%

R22

1K_1%

Y3

RS#0

V1

RS#1

U3

RS#2

M5

Request

RSP#

W1

Signals GND

TRDY#

AC3

A20M#

AF6

FERR#

AF5

FLUSH#

AD9

IGNNE#

AD3

SMI#

AB4

PWRGOOD

AE4

STPCLK#

AF8

AD15

AE14

AE6

B15

AF13

AF14

AE12

AF10

AF16

AD19

AD17

AF20

AF22

AE20

AD22

AD21

AD10

AD7

AD11

AF7

AF15

AF19

AE22

AF12

AD5

AE16

B

W3

Y1

L5

DPSLP#

INTR/LINT0

NMI/LINT1

INIT#

RESET#

DBSY#

DRDY#

THERMDA

THERMDC

SELFSB0

SELFSB1

EDGECTRLP

PICD0

PICD1

PICCLK

RP2#

RP3#

BPM0#

BPM1#

TCK

TDI

TDO

TMS

TRST#

PREQ#

PRDY#

CMOSREF_1

CMOSREF_0

RTTIMPDEP

GHI#

+VTT

Compatibility

VCCT_1

A26

G23

AE13

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_74

VCCT_10

VCCT_11

VCCT_12

VCCT_13

VCCT_14

VCCT_15

VCCT_16

C21

C19

AD20

C17

AD18

C15

C13

AD14

CMOS Reference Voltage

Layout note :

1. Place R_E1 and R_F near CPU.

2. Place decoupling caps near CPU.

12

C33

.1UF_0402

C

B12

D11

F11

E12

AB11

AA12

AC12

AE11

B10D9F9

E10

AB9

AA10

AC10

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

Mobile

Tualatin

VCCT VID

VCCT_17

VCCT_18

VCCT_19

VCCT_20

VCCT_21

VCCT_22

VCCT_23

VCCT_24

VCCT_25

VCCT_26

VCCT_27

VCCT_28

VCCT_29

VCCT_30

VCCT_31

C11

AD12C9C7

AD8C5AD6

12

C31

.1UF_0402

AC23

C

AA4E4G4J4L4

VCCT_32

AC4V4AE3

+VS_CMOSREF

AE9B8D7F7E8

VSS_91

VSS_92

VSS_93

VCCT_33

VCCT_34

VCCT_35

AF2

AF1

AE18D5E6

AB7

AA8

AC8

AE7B6F5H5G6K5J6N6L6T5R6V5U6Y5W6

VSS_94

VSS_95

VSS_96

VSS_97

VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VCCT_36

VCCT_37

VCCT_38

VID0

VID1

VID2

VID3

AB1

AC2

AE2

AF3R3B26M4AF26C1AF17

+VTT

R_A

R_B

D

AB5

AA6

AC6

AE5B4D4F4H4K4M3U4W4B2D2F2H2

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VID4

VSS

VSS

VSSNCNC

GTL Reference Voltage

12

R31

Layout note :

1K_1%

1. Place R_A and R_B between and GMCH and CPU.

2. Place decoupling caps near CPU.(Within 500mils)

12

R21

2K_1%

NC

N4

CPU_VR_VID4 <6>

CPU_VR_VID3 <6>

CPU_VR_VID2 <6>

CPU_VR_VID1 <6>

CPU_VR_VID0 <6>

12

C26

.1UF_0402

VSS_142

E20

F19

12

D

AE1

A25

C25

VTT_PWRGD<32>

C36

.1UF_0402

AD2

VSS_123

VSS_124

VSS_125

Data

Signals

VTT Ref

Analog

VSS_133

VSS_134

VSS_135

12

C41

.1UF_0402

R25 1K_0402

TESTHI1

R10 1K_0402

TESTHI2

R7 1K_0402

VSS_126

VSS_127

VSS_128

VSS_129

AE24

DEP#0

AD25

DEP#1

AE25

DEP#2

AC24

DEP#3

AF24

DEP#4

AD26

DEP#5

AC26

DEP#6

AD24

DEP#7

AF21

VREF_1

AB26

VREF_2

H26

VREF_3

A21

VREF_4

AF9

VREF_5

A4

VREF_6

N1

VREF_7

AA1

VREF_8

Y4

TESTLO

R5

VCC

N3

PLL1

N2

PLL2

P1

NC

P5

NC

E1

NC

F1

NC

AC1

CLK0

AD1

CLK0#

M1

TESTLO

AF18

NC

AD16

NCHCTRLP

AF11

TESTHI

AE8

NC

N24

NC

AE10

NC

E2

TESTHI

P4

NC

AD4

NC_1

A5

NC_2

D1

NC_3

AD13

NC_4

B1

NC_5

P26

NC_6

A11

NC_7

VTTPWRGOOD

VSS_132

E3

D26

NC

VSS_130

VSS_131

TUALATIN

K2M2P2T2V2Y2AB2

R11

1K_0402

VTT_PWRGD

+V_AGTLREF

12

C30

.1UF_0402

Title

Size Document Number Rev

Date: Sheet of

TESTLO1

R9 1K_0402

TESTLO2

+V_AGTLREF

+CPU_CORE

TESTLO1

+VTT_C

CLK_HCLK

CLK_HCLK#

TESTLO2

TESTHI1

TESTHI2

VTT_PWRGD

+VTT

12

12

C25

.1UF_0402

+VTT_PLL

+

R14

1 2

19.6K

C22

33UF_D2_16V

R134 14_1%

1 2

+3VS

2

1 2

L22 FLM-201209-4R7K

CLK_HCLK <14>

CLK_HCLK# <14>

12

Compal Electronics, Inc.

Mobile Tualatin uFCPGA & Thermal sensor

ADY11 LA-1181

E

12

12

12

12

R6

10K_0402

1

Q2

3904

3

E

+VTT

+VTT

12

R15

0_0402

+VTT_PLLIN

+VTT

VTT_PWRGD# <14,28>

5 41Friday, November 16, 2001

2

Page 6

A

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,I

NC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF

THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE

INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF

COMPAL ELECTRONICS,INC.

B

C

D

E

Layout note :

Place close to CPU, Use 2~3 vias per PAD.

Place .22uF caps underneath balls on solder side.

Place 10uF caps on the peripheral near balls.

Use 2~3 vias per PAD.

1 1

+CPU_CORE

12

12

C205

C144

.22UF_X7R

.22UF_X7R

+CPU_CORE

12

12

C194

C145

.22UF_X7R

.22UF_X7R

+CPU_CORE

2 2

3 3

12

+CPU_CORE

12

+CPU_CORE

12

+

+CPU_CORE

12

+

C200

10UF_10V_1206

C183

10UF_10V_1206

C29

220UF_D2_4V

C293

@220UF_D2_4V

Pls used X7R(uFCPGA EMTS Rev0.7)

12

C164

.22UF_X7R

12

C233

.22UF_X7R

12

C142

.22UF_X7R

Pls used X7R(uFCPGA EMTS Rev0.7)

12

12

C141

.22UF_X7R

12

C174

.22UF_X7R

C143

.22UF_X7R

Pls used X7R(uFCPGA EMTS Rev0.7)

12

C202

10UF_10V_1206

12

C28

10UF_10V_1206

12

C201

10UF_10V_1206

Pls used X7R(uFCPGA EMTS Rev0.7)

12

C151

10UF_10V_1206

12

C126

+

@220UF_D2_4V

12

C119

+

220UF_D2_4V

12

C191

10UF_10V_1206

12

C292

+

220UF_D2_4V

12

C210

+

@220UF_D2_4V

12

C24

10UF_10V_1206

12

C260

+

220UF_D2_4V

12

C153

+

220UF_D2_4V

12

C196

.22UF_X7R

12

C192

.22UF_X7R

12

C234

.22UF_X7R

12

C212

.22UF_X7R

12

C182

10UF_10V_1206

12

C184

10UF_10V_1206

12

C230

.22UF_X7R

12

C235

.22UF_X7R

12

C216

.22UF_X7R

12

C231

.22UF_X7R

12

C229

.22UF_X7R

12

C228

.22UF_X7R

12

12

C146

C173

.22UF_X7R

.22UF_X7R

12

12

C188

C165

.22UF_X7R

.22UF_X7R

R257

1K_0402

+3VS

182736

45

12

RP7

8P4R_1K

4 5

8 9

14 15

18 19

22 23

1

CPU Voltage ID

CPU_VR_VID0<5> CPU_VID0 <32>

CPU_VR_VID1<5>

CPU_VR_VID2<5>

CPU_VR_VID3<5>

CPU_VR_VID4<5>

AC_VID0<17>

AC_VID1<17>

AC_VID2<17>

AC_VID3<17>

AC_VID4<17>

PM_GMUXSEL = 0 : for low Voltage A-C

1 : for high Voltage B-C

PM_GMUXSEL<16,32>

+VTT

12

+

+VTT

12

U24

B0 D0

B1 D1

B2 D2

B3 D3

B4 D4

BE#

SN74CBT3383

Layout note :

Place close to CPU,

Use 2 vias per PAD.

C37

220UF_D2_4V

C222

1UF

VCC

GNDBX

12

+

12

C123

1UF

CPU_VID0

23

C0A0

CPU_VID1

67

C1A1

CPU_VID2

1011

C2A2

CPU_VID3

1617

C3A3

CPU_VID4

2021

C4A4

24

1213

C118

@220UF_D2_4V

12

12

C152

1UF

+5VS

12

C455

.01UF_0402

12

C130

1UF

CPU_VID1 <32>

CPU_VID2 <32>

CPU_VID3 <32>

CPU_VID4 <32>

C135

1UF

12

C249

1UF

12

12

C248

C199

1UF

1UF

12

12

C129

C227

1UF

1UF

+CPU_CORE

12

C32

+

220UF_D2_4V

4 4

EMI Clip PAD for CPU

PAD2

1

PAD-2.5X3

PAD6

PAD-2.5X3

A

12

C289

+

220UF_D2_4V

12

C283

+

220UF_D2_4V

PAD7

1

1

PAD-2.5X3

PAD8

PAD-2.5X3

Tualatin Coppermine-T

D4 D3 D2 D1 D0 CPU_Core(V) ES(before MP)

-------------------------------------------------------

0 0 1 0 1 1.50V

-------------------------------------------------------

1.15V0 1 1 0 0

D4 D3 D2 D1 D0 CPU_Core(V) QS ( MP)

-------------------------------------------------------

0 1 1.40V

-------------------------------------------------------

1

B

1.15V0 1 1 0 0

C

D4 D3 D2 D1 D0 CPU_Core(V) ES(before MP)

------------------------------------------------------ -

0 0 0 0 1 1.70V

------------------------------------------------------ -

1.35V0 1 0 0 0

D4 D3 D2 D1 D0 CPU_Core(V) QS ( MP)

------------------------------------------------------ -

0

10

1 000000

------------------------------------------------------ -

D

1.70V0 1 1

1.35V

Title

Size Document Number Rev

Date: Sheet of

Compal Electronics, Inc.

CPU Bypass & CPU VID

ADY11 LA-1181

6 41Friday, November 16, 2001

E

2

Page 7

5

4

3

2

1

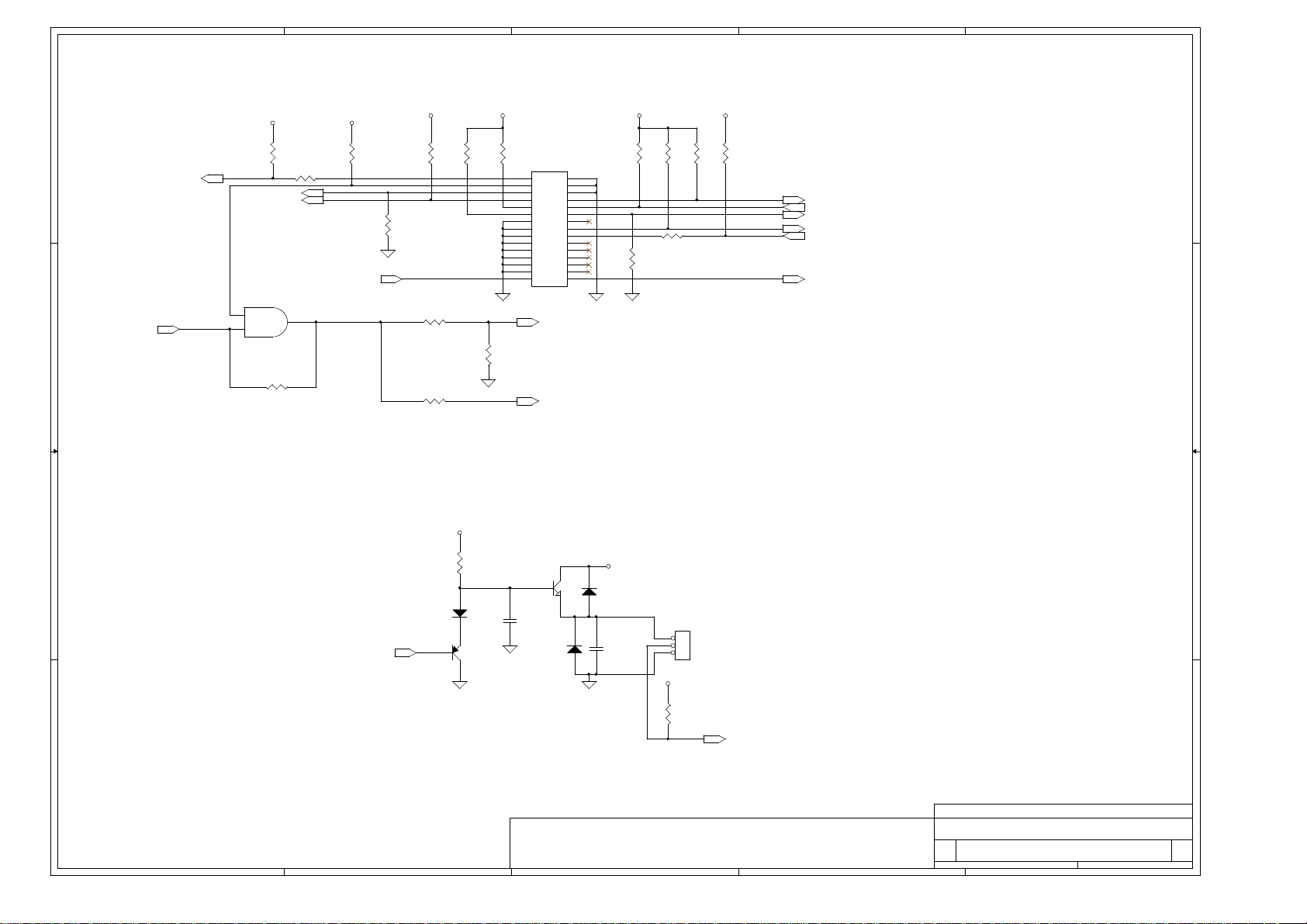

ITP PORT

+VTT +3VS

D D

H_RESETX#<8>

ITP_PWROK<16,30>

C C

9

10

+5VS POWER

U26C

74HCT08

R96

@56_1%

R95 @240

ITP_TCK<5>

ITP_TMS<5>

8

ITP_TCK

ITP_TMS

R94

240

R91

@39

R93

@39

1 2

R415 5.6K_0402

+VTT +VTT+1.5VS +1.5VS

R87

R89

@1.5K

@10K_0402

12

R245

10K_0402

JP18

2

2

4

4

6

6

8

8

10

10

12

12

14

14

16

16

18

18

20

20

22

22

24

24

26

26

28

28

30

30

@AMP104078-4

PM_PWROK <16>

1

1

3

3

5

5

7

7

9

9

11

11

13

13

15

15

17

17

19

19

21

21

23

23

25

25

27

27

29

29

R90

@150

R84 @240

R88

@510

R86

@200

R92

@200

R85

@56.2_1%

ITP_TDI

ITP_TDO

ITP_TRST#

ITP_PREQ#

ITP_PRDY#

ITP_TDI <5>

ITP_TDO <5>

ITP_TRST# <5>

ITP_PREQ# <5>

ITP_PRDY# <5>

CLK_ITPP# <14>CLK_ITPP<14>

R249 @0_0402

B B

EN_DFAN<28>

A A

5

1 2

R416 100_0402

R235

3.48K_1%

2

4

+12VALW

1 2

21

3

1

EC_HPOWON <28>

Fan Control circuit

2 1

+5VALW

D2

1SS355

2 1

C99

@1000PF_0402

+5VFAN

3

+3V

JP17

1

2

3

53398-0310

12

R375

10K_0402

FAN1_TACH <28>

Q4

FMMT619

D8

1N4148

2.2UF_16V_0805

1 2

Q10

2SA1036K

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

C420

1

2

3

D1

1N4148

COMPAL Electronics,Inc

Title

ITP PORT & Fan control

Size Document Number Rev

ADY11 LA-1181

2

Date: Sheet of

7 41Friday, November 16, 2001

1

2

Page 8

A

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,I

NC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF

THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE

INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF

COMPAL ELECTRONICS,INC.

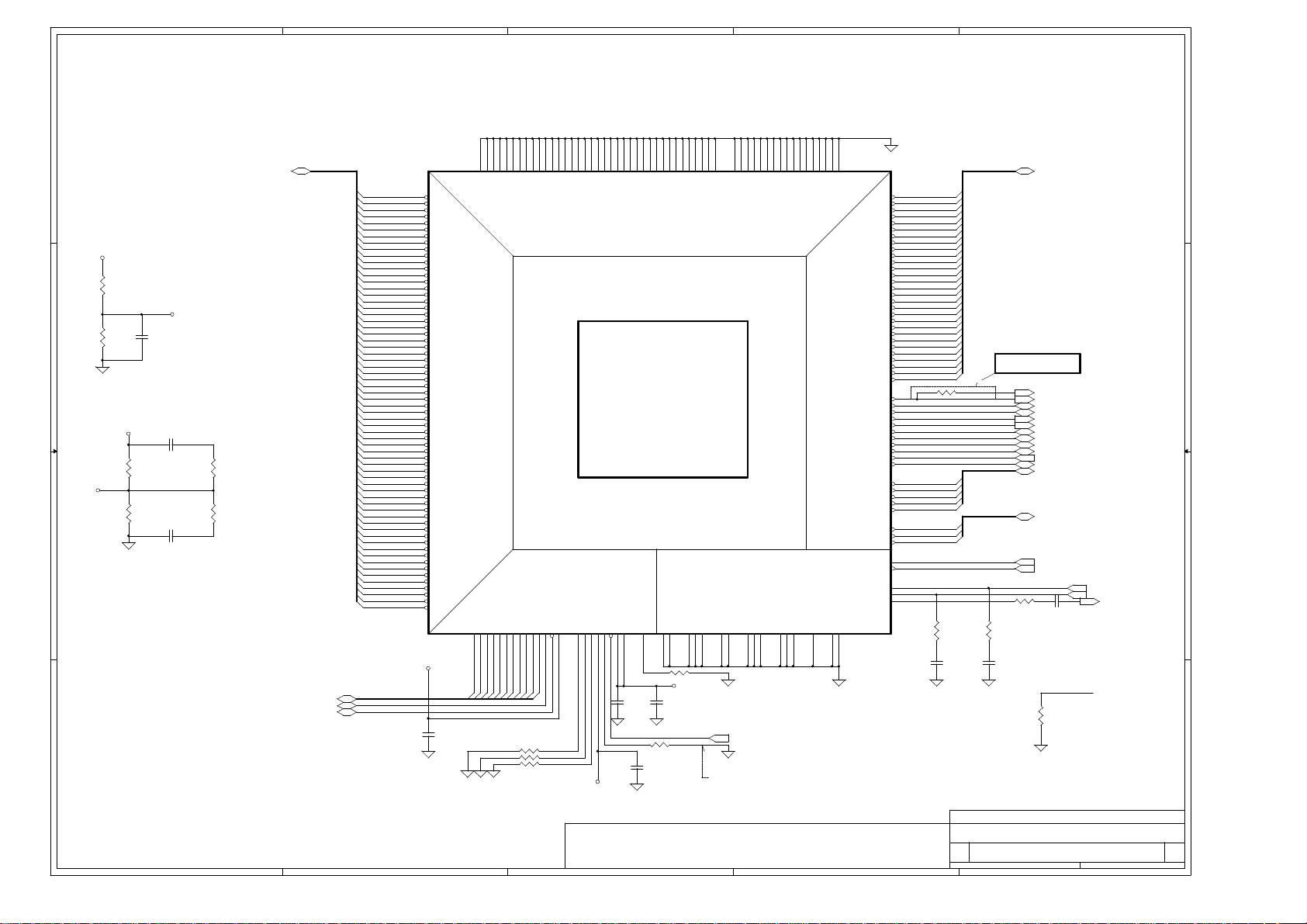

1 1

+1.8VS

HUB Interface Reference

12

R125

301_1%

Layout note :

1. Place R_C and R_D in middle of Bus.

R_C

2. Place capacitors near GMCH.

12

R124

301_1%

R_D

2 2

Place Reference Circuit near GMCH

+1.5VS

12

VGAREF

3 3

4 4

12

+VS_HUBREF

12

C176

.1UF_0402

C261 470PF

1 2

R142

1K_1%

R141

1K_1%

C270 470PF

1 2

A

12

12

R143

82.5_1%

R147

82.5_1%

HUB_PD[0..10]<16>

HUB_PSTRB<16>

HUB_PSTRB#<16>

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

B

B

U7A

U4

H_D#0

P1

H_D#1

W6

H_D#2

U2

H_D#3

U6

H_D#4

R1

H_D#5

N3

H_D#6

W5

H_D#7

V4

H_D#8

P3

H_D#9

R3

H_D#10

U1

H_D#11

V6

H_D#12

W4

H_D#13

T3

H_D#14

P2

H_D#15

V3

H_D#16

R2

H_D#17

T1

H_D#18

W3

H_D#19

U3

H_D#20

Y4

H_D#21

AA3

H_D#22

W1

H_D#23

V1

H_D#24

Y1

H_D#25

Y6

H_D#26

AD3

H_D#27

AB4

H_D#28

AB5

H_D#29

V2

H_D#30

Y3

H_D#31

Y2

H_D#32

AA4

H_D#33

AA1

H_D#34

AA6

H_D#35

AB1

H_D#36

AC4

H_D#37

AA2

H_D#38

AB3

H_D#39

AD2

H_D#40

AD1

H_D#41

AC2

H_D#42

AB6

H_D#43

AC6

H_D#44

AC1

H_D#45

AF3

H_D#46

AD4

H_D#47

AD6

H_D#48

AC3

H_D#49

AH3

H_D#50

AE5

H_D#51

AE3

H_D#52

AG2

H_D#53

AF4

H_D#54

AF2

H_D#55

AJ3

H_D#56

AE4

H_D#57

AG1

H_D#58

AE1

H_D#59

AG4

H_D#60

AH4

H_D#61

AG3

H_D#62

AF1

H_D#63

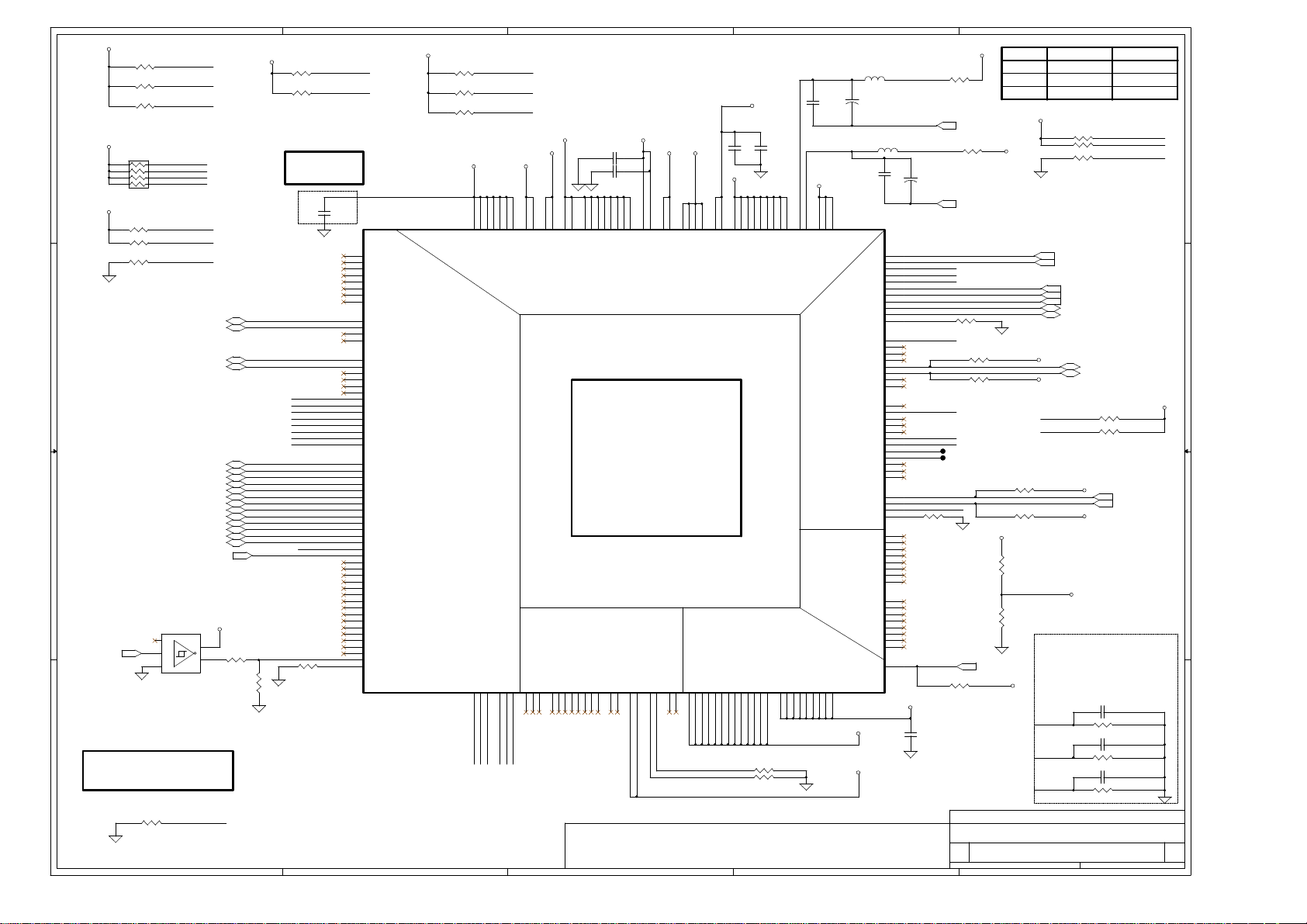

ALMADOR-M

+VS_HUBREF

12

C178

.01UF_0402

M12

M13

M17

M18

N12

VSS0

VSS1

VSS2

VSS3

VSS4

Host

Interface

HUB_PD0

HUB_PD1

HUB_PD2

HUB_PD3

HUB_PD4

HUB_PD5

G26

H28

H29

H27

F29

F27

HUB_PD0

HUB_PD1

HUB_PD2

HUB_PD3

HUB_PD4

HUB_PD5

R138 54.9_1%

R126 27.4_1%

R127 54.9_1%

N13

N14

N15

N16

VSS5

VSS6

VSS7

HUB_PD6

HUB_PD7

HUB_PD8

E29

E28

G25

G27

HUB_PD7

HUB_PD6

HUB_PD8

HUB_PD9

1 2

1 2

1 2

N17

N18

VSS8

VSS9

VSS10

HUB_PD9

HUB_PD10

HUB_PSTRB

H26

G29

HUB_PD10

P13

P14

P15

P16

VSS11

VSS12

VSS13

VSS14

HUB_REF

HUB_PSTRB#

H24

F28

C

P17

R13

R14

R15

R16

R17

T13

T14

T15

T16

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

Almador-M

GMCH

DVO_RCOMP

SM_RCOMP

HUB_RCOMP

AGP_REF

AGP_RCOMP/DVOBC_RCOMP

RESET#

H_GTLREF1

VGAREF

J25

K24

AB24

H_GTLREF0

AA7J7C2

12

C263

.1UF_0402

12

C

AC22F6J23

T17

U12

U13

U14

U15

U16

U17

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS

H_GTLRCOMP

VSS

VSS

AB23

AC23

1 2

R116 80.6_1%

+V_AGTLREF

12

C185

.1UF_0402

12

R128 54.9_1%

C190

.1UF_0402

U18

V12

V13

V17

V18

AJ5D2AC5Y5U5P5L5H5AH2

VSS32

VSS33

VSS34

VSS35

VSS36

VSS_H0

VSS_H1

VSS_H2

VSS_H3

VSSPCMOS_LM0

VSSPCMOS_LM1

VSSPCMOS_LM2

VSSP_HUB0

VSSP_HUB1

VSSP_IO0

AH19

AH20

AF5

VSSP_IO1

G28

H25

AC26

AD22

AE28

PCIRST# <15,16,20,21,26,27,28>

10 mils wide,length <=500 mils.

VSS_H4

VSS_H5

VSS_H6

VSSP_IO2

AE2

AB2W2T2N2K2G2AC7

VSS_H7

VSS_H8

VSS_H9

VSSP_DVO0

VSSP_DVO1

VSSP_DVO2

AH24

AF25

AF27

VSS_H10

VSS_H11

VSS_H12

VSSA_DAC

AH26G8AD7

VSS_H13

VSS_H14

VSS_H15

Host

Interface

VSSA_CPLL

D

VSS_H16

H_CPURST#

H_DBSY#

H_DEFER#

H_DRDY#

H_LOCK#

H_TRDY#

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

CLK_HT#

CLK_DREF

CLK_GBIN

CLK_GBOUT

VSSA_HPLL

D

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_ADS#

H_BNR#

H_BPRI#

H_HIT#

H_HITM#

H_RS#0

H_RS#1

H_RS#2

CLK_HT

H2

E3

G3

N4

M6

F1

F2

J3

F3

P6

G1

N5

H1

P4

T4

M2

J2

L2

R4

K1

L3

L1

J1

N1

T5

H3

M3

M1

K3

R6

C1

E1

L4

G5

J4

F4

D3

D1

J6

G4

K6

M4

K5

K4

L6

H6

H4

G6

AJ4

AH5

AC19

AG26

AD24

33_0402

5PF_0402

C297

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

H_RS#0

H_RS#1

H_RS#2

R168

E

HA#[3..31]HD#[0..63]

HA#[3..31] <4>HD#[0..63]<4>

Close to Ball R6.

1 2

R133 @0_0402

HREQ#[0..4]

H_RS#[0..2]

CLKGBOUT

1 2

Title

Size Document Number Rev

ADY11 LA-1181

Date: Sheet of

H_RESETX# <7>

H_RESET# <5>

HADS# <4>

HBNR# <4>

HBPRI# <4>

H_DBSY# <5>

HDEFER# <4>

H_DRDY# <5>

HIT# <4>

HITM# <4>

HLOCK# <4>

H_TRDY# <5>

HREQ#[0..4] <4>

H_RS#[0..2] <5>

CLK_GHT <14>

CLK_GHT# <14>

1 2

1 2

R156 47_0402

R151

@33_0402

1 2

C259

@10PF_0402

C277 .01UF_0402

CLK_GBIN

12

R167

@240K

Compal Electronics, Inc.

Almador-M GMCH(1/3)

CLK_DREF <14>

CLK_GBIN <14>

E

CLK_GBOUT <14>

8 41Friday, November 16, 2001

2

Page 9

A

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,I

NC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF

THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE

INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF

COMPAL ELECTRONICS,INC.

AD8

AD9

AD10

AJ21

AE8

AE9

AE10

AE11

AE12

AE13

AE17

AE19

AH21

AF8

AF9

AF10

AF11

AF12

AF13

U7B

SM_DQ0

D29

1 1

2 2

3 3

SM_DQ1

SM_DQ2

SM_DQ3

SM_DQ4

SM_DQ5

SM_DQ6

SM_DQ7

SM_DQ8

SM_DQ9

SM_DQ10

SM_DQ11

SM_DQ12

SM_DQ13

SM_DQ14

SM_DQ15

SM_DQ16

SM_DQ17

SM_DQ18

SM_DQ19

SM_DQ20

SM_DQ21

SM_DQ22

SM_DQ23

SM_DQ24

SM_DQ25

SM_DQ26

SM_DQ27

SM_DQ28

SM_DQ29

SM_DQ30

SM_DQ31

SM_DQ32

SM_DQ33

SM_DQ34

SM_DQ35

SM_DQ36

SM_DQ37

SM_DQ38

SM_DQ39

SM_DQ40

SM_DQ41

SM_DQ42

SM_DQ43

SM_DQ44

SM_DQ45

SM_DQ46

SM_DQ47

SM_DQ48

SM_DQ49

SM_DQ50

SM_DQ51

SM_DQ52

SM_DQ53

SM_DQ54

SM_DQ55

SM_DQ56

SM_DQ57

SM_DQ58

SM_DQ59

SM_DQ60

SM_DQ61

SM_DQ62

SM_DQ63

SM_DQ[0..63]

SM_DQ0

C29

SM_DQ1

D27

SM_DQ2

C27

SM_DQ3

A27

SM_DQ4

B26

SM_DQ5

E24

SM_DQ6

C25

SM_DQ7

E23

SM_DQ8

B25

SM_DQ9

C23

SM_DQ10

F22

SM_DQ11

B23

SM_DQ12

C22

SM_DQ13

E21

SM_DQ14

B22

SM_DQ15

C12

SM_DQ16

D10

SM_DQ17

C11

SM_DQ18

A10

SM_DQ19

C10

SM_DQ20

C8

SM_DQ21

A7

SM_DQ22

E9

SM_DQ23

C7

SM_DQ24

E8

SM_DQ25

A5

SM_DQ26

F8

SM_DQ27

C5

SM_DQ28

D6

SM_DQ29

B4

SM_DQ30

C4

SM_DQ31

E27

SM_DQ32

C28

SM_DQ33

B28

SM_DQ34

E26

SM_DQ35

C26

SM_DQ36

D25

SM_DQ37

A26

SM_DQ38

D24

SM_DQ39

F23

SM_DQ40

A25

SM_DQ41

G22

SM_DQ42

D22

SM_DQ43

A23

SM_DQ44

F21

SM_DQ45

D21

SM_DQ46

A22

SM_DQ47

F11

SM_DQ48

A11

SM_DQ49

B11

SM_DQ50

F10

SM_DQ51

B10

SM_DQ52

B8

SM_DQ53

D9

SM_DQ54

B7

SM_DQ55

F9

SM_DQ56

A6

SM_DQ57

C6

SM_DQ58

D7

SM_DQ59

B5

SM_DQ60

E6

SM_DQ61

A4

SM_DQ62

D4

SM_DQ63

ALMADOR-M

SM_DQ[0..63] <12,13>

VSS_LM

SDRAM

System

Memory

VSSP_SM0

VSSP_SM1

VSSP_SM2

B3B6B9

VSS_LM

VSS_LM

VSSP_SM3

VSSP_SM4

B12

B15

B18

VSS_LM

VSS_LM

VSS_LM

VSS_LM

VSSP_SM5

VSSP_SM6

VSSP_SM7

VSSP_SM8

B21

B24

B27E7E10

VSS_LM

VSS_LM

VSS_LM

VSS

VSSP_SM9

VSSP_SM10

VSSP_SM11

E13

E16

VSS_LM

VSS_LM

VSSP_SM12

VSSP_SM13

E19

AF14

VSS_LM

VSS_LM

VSS_LM

VSS_LM

VSS_LM

VSS_LM

VSS_LM

VSS_LM

Almador-M

GMCH

VSSP_SM14

VSSP_SM15

VSSP_SM16

VSSP_SM17

VSSP_SM18

VSSP_SM19

E22

E25G9G21E4D28

+VTT

B

AF15

AF16

AF17

AF18

AF19

AF20

AG7

AG15

VSS_LM

VSS_LM

VSS_LM

VSS_LM

VSS_LM

VSS_LM

VSS_LM

VSS

VCC

VCC

VCC

VCC

VCC

VCC

VCC

H7

H23K7K23L7N6T6W7Y7AB7

AG16

AG21

VSS_LM

VSS_LM

VCC

VCC

AH6

AH8

VSS_LM

VSS_LM

Power

VCC

VCC

M24

P24

AH9

AH11

VSS_LM

VSS_LM

VCC

VCC

T24

V24

AH12

AH14

VSS_LM

VSS_LM

VCC

VCC

Y23

M14

AH17

AH18

VSS_LM

VSS_LM

VCC

VCC

M15

M16

VSS_LM

VCC

VCC

P12

R12

K28

N28

VSSP_AGP0

VSSP_AGP1

VCC

VCC

VCC

T12

P18

T28

W28

AB28

L25

VSSP_AGP2

VSSP_AGP3

VSSP_AGP4

VCC

VCC

R18

T18

P25

U25

Y25

VSSP_AGP5

VSSP_AGP6

VSSP_AGP7

VSSP_AGP8

SM_VREF0

SM_VREF1

E5

F24

12

C160

.1UF_0402

AE20

G24

VSSA_DPLL0

VSSA_DPLL1

SDRAM

System

Memory

SM_OCLK

SM_RCLK

A24

C24

SM_OCLK_RCLK

12

SM_RAS#

SM_CAS#

SM_WE#

C20

D19

A21

+V_SMREF

C157

.1UF_0402

SM_MA0

SM_MA1

SM_MA2

SM_MA3

SM_MA4

SM_MA5

SM_MA6

SM_MA7

SM_MA8

SM_MA9

SM_MA10

SM_MA11

SM_MA12

VCC_SM

VCC_SM

SM_BA0

SM_BA1

SM_DQM0

SM_DQM1

SM_DQM2

SM_DQM3

SM_DQM4

SM_DQM5

SM_DQM6

SM_DQM7

SM_CS#0

SM_CS#1

SM_CS#2

SM_CS#3

VCCQ_SM

SM_CLK0

SM_CLK1

SM_CLK2

SM_CLK3

SM_CKE0

SM_CKE1

SM_CKE2

SM_CKE3

VCC_SM

C

VSSA_DPLL0 <10>

VSSA_DPLL1 <10>

A20

B20

B19

C19

A18

A19

C17

C18

B17

A17

A16

C15

C14

F20

NC

E20

NC

F12

NC

E11

NC

C21

VSS

F19

VSS

E12

A12

SM_D_BA0

B16

SM_D_BA1

C16

F18

D18

D13

D12

E18

F17

F14

F13

E17

F16

D16

D15

E15

E14

VSS

A15

B2

B14

A3

A14

VSS

C3

VSS

A13

C9

C13

A9

B13

VSS

A8

SM_D_RAS#

SM_D_CAS#

SM_D_WE#

12

C134

@22PF_0402

Close to Ball E5 and F24

MMA0

MMA1

MMA2

MMA3

MMA4

SM_BA0 <12,13>

SM_BA1 <12,13>

1 2

1 2

1 2

1 2

SM_RAS# <12,13>

SM_CAS# <12,13>

SM_WE# <12,13>

MMA5

MMA6

MMA7

MMA8

MMA9

MMA10

MMA11

MMA12

Cap

near pin A12

MMA0

MMA1

MMA2

MMA3

MMA4

MMA5

MMA6

MMA7

MMA8

MMA9

MMA10

MMA11

MMA12

XOR

Layout Note:

F20,E20,F12,E11

ADD Testpoint

for Factory

C132 .1UF_0402

R114 10_0402

1 2

R115 10_0402

1 2

SM_DQM0

SM_DQM1

SM_DQM2

SM_DQM3

SM_DQM4

SM_DQM5

SM_DQM6

SM_DQM7

SM_CS#0

SM_CS#1

SM_CS#2

SM_CS#3

SM_D_CLK0

SM_D_CLK1

SM_D_CLK2

SM_D_CLK3

SM_CKE0

SM_CKE1

SM_CKE2

SM_CKE3

+3V

12

C131

Layout note

Cap near pin A8

.1UF_0402

R118 10_0402

1 2

R120 10_0402

1 2

R111 10_0402

1 2

Layout note

SM_OCLK_RCLK trace length 150mil +-50mil

+3V

1 2

SM_DQM[0..7] <12,13>

SM_CS#0 <12>

SM_CS#1 <12>

SM_CS#2 <13>

SM_CS#3 <13>

+3V

R110 10_0402

R113 10_0402

R119 10_0402

R109 10_0402

SM_CKE0 <12>

SM_CKE1 <12>

SM_CKE2 <13>

SM_CKE3 <13>

D

RP5

8P4R_10

RP4

8P4R_10

RP3

8P4R_10

SM_MA0

SM_MA1

SM_MA2

SM_MA3

SM_MA4

SM_MA5

SM_MA6

SM_MA7

SM_MA8

SM_MA9

SM_MA10

SM_MA11

SM_MA12

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 2

R112 10_0402

Layout note :

Place resistors near GMCH

SMD_CLK0 <12>

SMD_CLK1 <12>

SMD_CLK2 <13>

SMD_CLK3 <13>

+3V

12

R122

249_1%

12

R123

49.9_1%

E

SM_MA[0..12] <12,13>

Layout note :

Place resistors near GMCH

System Memory Reference

+V_SMREF

Layout note :

near pin A24

4 4

A

Title

Size Document Number Rev

B

C

D

Date: Sheet of

Compal Electronics, Inc.

Almador-M GMCH(2/3)

ADY11 LA-1181

9 41Friday, November 16, 2001

E

2

Page 10

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,I

NC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF

THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE

INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF

COMPAL ELECTRONICS,INC.

1 2

1 2

1 2

RP9

@8P4R_8.2K

1

2

3

1 2

R132 330

A

AGP_FRAME#

AGP_TRDY#

AGP_STOP#

AGP_REQ#

AGP_GNT#

AGP_PIPE#

AGP_WBF#

AGP_RBF#

DVO_INT#

DVO_STALL

U47

NC

A

GND

TC7SH14

A

VCC

DVO_HSYNC<15>

DVO_VSYNC<15>

DVO_D7<15>

DVO_BL#<15>

DVO_CLK<15>

DVO_CLK#<15>

DVO_D1<15>

DVO_D0<15>

DVO_D3<15>

DVO_D2<15>

DVO_D5<15>

DVO_D4<15>

DVO_D6<15>

DVO_D9<15>

DVO_D8<15>

DVO_D11<15>

DVO_D10<15>

DVO_STALL<15>

Y

AGP_PAR

5

4

+3VS

R421

+1.5VS

1.5V level clock

12

732_1%

R422

604_1%

1 2

AGP_DEVSEL#

1 2

R137 8.2K_0402

AGP_IRDY#

1 2

R417 8.2K_0402

Layout note :

Place close to AE16,

AE15 of GMCH

12

AGP_FRAME#

AGP_IRDY#

AGP_TRDY#

AGP_STOP#

AGP_DEVSEL#

AGP_REQ#

AGP_GNT#

AGP_PAR

DVO_INT#

DVO_STALL

DPMS_CLK

1 2

R145 10K_0402

C278

68PF

AA29

AA24

AA25

AA27

AA28

AC27

AD29

W24

M29

M28

M27

M25

W29

W26

W25

W27

+1.5VS

R430 8.2K_0402

R431 8.2K_0402

R432 @8.2K_0402

1 1

+1.5VS

1 8

2 7

3 6

4 5

+1.5VS

R150 @8.2K_0402

1 2

1 2

R131 100K_0402

1 2

R129 @100K_0402

2 2

3 3

RTCCLK<16>

AGP_PAR : Strapping option for SW detection of

4 4

AGP or DVO device.

0 -> DVO B/C device

1 -> AGP device

B

AGP_SBA0/ZV_D8

AGP_SBA1/ZV_D7

AGP_SBA2/ZV_D6

Y24

AGP_SBA3/ZV_D5

Y27

AGP_SBA4/ZV_D2

Y26

AGP_SBA5/ZV_D1

AGP_SBA6/ZV_D0

Y28

AGP_SBA7/ZV_HREF

L27

AGP_CBE#0/DVOB_D7

P29

AGP_CBE#1/DVOB_BLANK#

R27

AGP_CBE#2/ZV_VSYNC

T25

AGP_CBE#3/DVOC_D5

L29

AGP_ADSTB0/DVOB_CLK

L28

AGP_ADSTB#0/DVOB_CLK#

U29

AGP_ADSTB1/DVOC_CLK

U28

AGP_ADSTB#1/DVOC_CLK#

AGP_SBSTB/ZV_D4

AGP_SBSTB#/ZV_D3

R29

AGP_FRAME#/M_DDC2_DATA

P26

AGP_IRDY#/M_I2C_CLK

P27

AGP_TRDY#/M_DDC2_CLK

N25

AGP_STOP#

R28

AGP_DEVSEL#/M_I2C_DATA

AGP_REQ#/ZV_CLK

AGP_GNT#/ZV_D15

P28

AGP_PAR

J29

AGP_AD0/DVOB_HSYNC

J28

AGP_AD1/DVOB_VSYNC

K26

AGP_AD2/DVOB_D1

K25

AGP_AD3/DVOB_D0

L26

AGP_AD4/DVOB_D3

J27

AGP_AD5/DVOB_D2

K29

AGP_AD6/DVOB_D5

K27

AGP_AD7/DVOB_D4

AGP_AD8/DVOB_D6

AGP_AD9/DVOB_D9

L24

AGP_AD10/DVOB_D8

AGP_AD11/DVOB_D11

N29

AGP_AD12/DVOB_D10

AGP_AD13/DVOBC_CLKINT#

N26

AGP_AD14/DVOB_FLD/STL

N27

AGP_AD15

R25

AGP_AD16/DVOC_VSYNC

R24

AGP_AD17/DVOC_HSYNC

T29

AGP_AD18/DVOC_BLANK#

T27

AGP_AD19/DVOC_D0

T26

AGP_AD20/DVOC_D1

U27

AGP_AD21/DVOC_D2

V27

AGP_AD22/DVOC_D3

V28

AGP_AD23/DVOC_D4

U26

AGP_AD24/DVOC_D7

V29

AGP_AD25/DVOC_D6

AGP_AD26/DVOC_D9

V25

AGP_AD27/DVOC_D8

AGP_AD28/DVOC_D11

AGP_AD29/DVOC_D10

AGP_AD30/DVOC_INT#/DPMS_CLK

Y29

AGP_AD31/DVOC_FLD/STL

B

+1.5VS

R155 @8.2K_0402

1 2

R163 @8.2K_0402

1 2

R149 @8.2K_0402

1 2

+VTT

V14

AGP

Interface

V15

VDD_LM

U7C

(DVOB/DVOC & ZV port)

ALMADOR-M

AGP_PIPE#/ZV_D10

AB26

AB29

AGP_WBF#

AGP_PIPE#

AGP_ST0

AGP_ST1

AGP_ST2

+3V

V16

AE16

AE15

AD15

AD16

VDD_LM

VDD_LM

VDD_LM

VDD_LM

VDD_LM

VDD_LM

AGP_WBF#/ZV_D9

AGP_RBF#/ZV_D11

AGP_ST0/ZV_D14

AGP_ST1/ZV_D13

AGP_ST2/ZV_D12

AB25

AC28

AC29

AB27

AGP_RBF#

AGP_ST0

AGP_ST1

AGP_ST2

AE25

AD23

VCCP_IO

VCCP_IO

LM_CMD

LM_SCK

AH7

AF7

+1.8VS

J24

LM_SIO

AJ7

+1.5VS

F26

N24

VCCP_HUB

VCCP_HUB

LM_RQ0

LM_RQ1

AG11

AJ12

AG12

C

C281 .1UF_0402

12

12

C170

.1UF_0402

W23

J26

M26

R26

V26

AA26

L23

AA23

VCCP_AGP

VCCP_AGP

VCCP_AGP

VCCP_AGP

VCCP_AGP

VCCP_AGP

VCCQ_AGP

VCCQ_AGP

VCCP_AGP

Almador-M

GMCH

Local Memory

Interface

LM_RQ2

LM_RQ3

LM_RQ4

LM_RQ5

LM_RQ6

LM_RQ7

LM_RCLK

AG13

AJ13

AG14

AJ14

AJ6

LM_GCLK

AG6

C

AH13

+VTT

U24

AE6G7G10

VCCP_AGP

VCCA_HPLL

VCCA_CPLL

Power

Interface

LM_RAMREF0

LM_RAMREF1

LM_CTM

AD14

AE14

AH15

+3V

G20

VCCQ_SM

LM_CTM#

AJ15

AJ16

+1.8VS

AF6

AE7

VCCQ_SM

VCCPCMOS_LM

VCCPCMOS_LM

LM_CFM

LM_CFM#

VCCP_SM

AH16

D5D8D11

.01UF_0402

AC9

AC8

AF26

AG27F5J5M5R5V5AA5

VCCA_DAC

VCCA_DAC

VCCPCMOS_LM

VCCPCMOS_LM

VCCP_SM

VCCP_SM

VCCP_SM

VCCP_SM

VCCP_SM

D14

D17

D20

12

C632

+VTT

VCC_H

VCCP_SM

VCCP_SM

D23

D26F7F15

R170

R169

+1.8VS

12

.1UF_0402

VCC_H

VCC_H

VCC_H

VCCP_SM

VCCP_SM

VCCP_SM

G11

G19

10K_0402

1 2

1 2

10K_0402

C290

AD5

VCC_H

VCC_H

VCC_H

VCCP_SM

VCCP_SM

G23

AG5

E2

VCC_H

VCC_LM

AC10

AC11

VCC_H

VCC_LM

AD11

12

C294

.1UF_0402

+1.5VS

VCCA_DPLL

VCCADPLL

AC20

F25

AC21

AF21

VCCP_DVO

VCCA_DPLL0

VCCA_DPLL1

Display

Interface

(DVOA port)

Local Memory

Interface

VCC_LM

VCC_LM

VCC_LM

VCC_LM

VCC_LM

AD12

AD13

AE18

AD17

AD18

D

AF24

DAC_VSYNC

DAC_HSYNC

VCCP_DVO

VCCP_DVO

DAC_RED#

DAC_GREEN#

DAC_BLUE#

DAC_GREEN

IO_DDC1CLK

IO_DDC1DATA

DAC_REFSET

DVO_CLKIN

DVO_BLANK#

DVO_VSYNC

DVO_HSYNC

IO_I2CDATA

IO_DDC2DATA

IO_DDC2CLK

DVO_INTR#

DVO_FIELD

AGP_BUSY#

VCC_LM

VCC_LM

AD19

+VS_RIMMREF

D

L49

FBM-11-201209-601T

1 2

12

C302

+

100UF_D2_6.3V

L45

FBM-11-201209-601T

1 2

12

C167

.1UF_0402

DAC_RED

DAC_BLUE

IO_I2CCLK

DVO_CLK#

DVO_CLK

DVO_D0

DVO_D1

DVO_D2

DVO_D3

DVO_D4

DVO_D5

DVO_D6

DVO_D7

DVO_D8

DVO_D9

DVO_D10

DVO_D11

LM_DQA0

LM_DQA1

LM_DQA2

LM_DQA3

LM_DQA4

LM_DQA5

LM_DQA6

LM_DQA7

LM_DQB0

LM_DQB1

LM_DQB2

LM_DQB3

LM_DQB4

LM_DQB5

LM_DQB6

LM_DQB7

+3V

VCCA_DPLL0

VCCA_DPLL1

12

C180

+

100UF_D2_6.3V

AE29

AD28

CRT_R#

AF28

CRT_G#

AG28

CRT_B#

AH27

AF29

AG29

AH28

AE27

AD27

R172 255_1%

AJ27

DVOA_CLKIN

AD20

AD21

AF23

AF22

AD25

AC25

AG24

AJ24

AJ22

DVOA_D1

AH22

AG22

AJ23

AH23

DVOA_D5

AG23

DVOA_D6

AE23

AE24

1

AJ25

1

AH25

AG25

AJ26

AD26

AE26

DVOA_INTR#

AE21

1 2

AE22

R166

10K_0402

AG17

AJ17

AG18

AJ18

AG19

AJ19

AG20

AJ20

AJ11

AH10

AJ10

AG10

AJ9

AG9

AJ8

AG8

AC24

R152 10K_0402

+1.8VS

12

C266

68PF

E

+VTT

Strap Name Low High

R176 0_0402

1 2

DVOA_D1 IOQD=1 IOQD=8

DVOA_D5 Desktop Mobile

DVOA_D6 Dual Ended Term Single Ended Term

VSSA_DPLL0 <9>

R117 0_0402

1 2

VSSA_DPLL1 <9>

1 2

R162

1 2

R153

1 2

T52

T53

XOR

Layout Note:

AE24,AJ25

ADD Testpoint

for Factory

R159

576_1%

R_I

R154

2K_1%

+1.5VS

R146 @2.2K

R144 2.2K

+VTT

R173 @2.2K

CRT_VSYNC <15>

CRT_HSYNC <15>

10K_0402

+3VS

10K_0402

+3VS

DVOA_CLKIN

DVOA_INTR#

1 2

R161 10K_0402

R160 10K_0402

1 2

+1.8VS

12

1. Place R_I and R_J near GMCH.

12

1 2

1 2

1 2

CRT_R <15>

CRT_G <15>

CRT_B <15>

3VDDCCL <15>

3VDDCDA <15>

GMBSCL <15>

GMBSDA <15>

R157

1 2

R164

1 2

+3VS

+3VS

+VS_RIMMREF

DVOA_D6

DVOA_D5

DVOA_D1

100K_0402

100K_0402

LTVDA <15>

LTVCK <15>

R_J

AGP_BUSY# <16>

1 2

Title

Size Document Number Rev

ADY11 LA-1181

Date: Sheet of

37.4_1% resistors and cap

must be placed after RGB

pi filter near CRT

+3VS

connector.

C627

CRT_R#

CRT_G#

CRT_B#

1 2

1 2

R418 37.4_1%

C628

1 2

1 2

R419 37.4_1%

C629

1 2

1 2

R420 37.4_1%

Compal Electronics, Inc.

Almador-M GMCH(3/3)

E

@.1UF_0402

@.1UF_0402

@.1UF_0402

10 41Friday, November 16, 2001

+1.5VS

2

Page 11

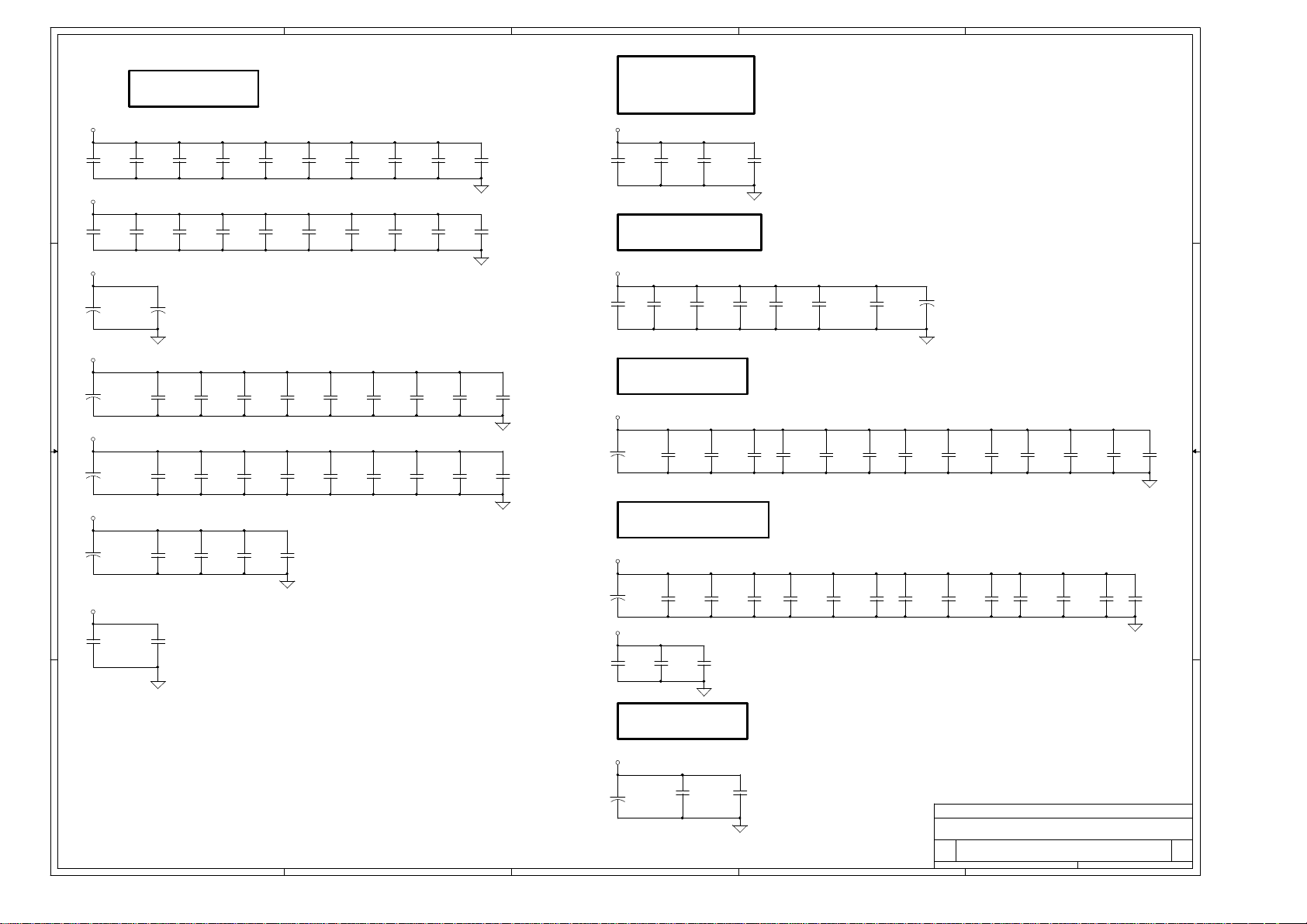

5

4

3

2

1

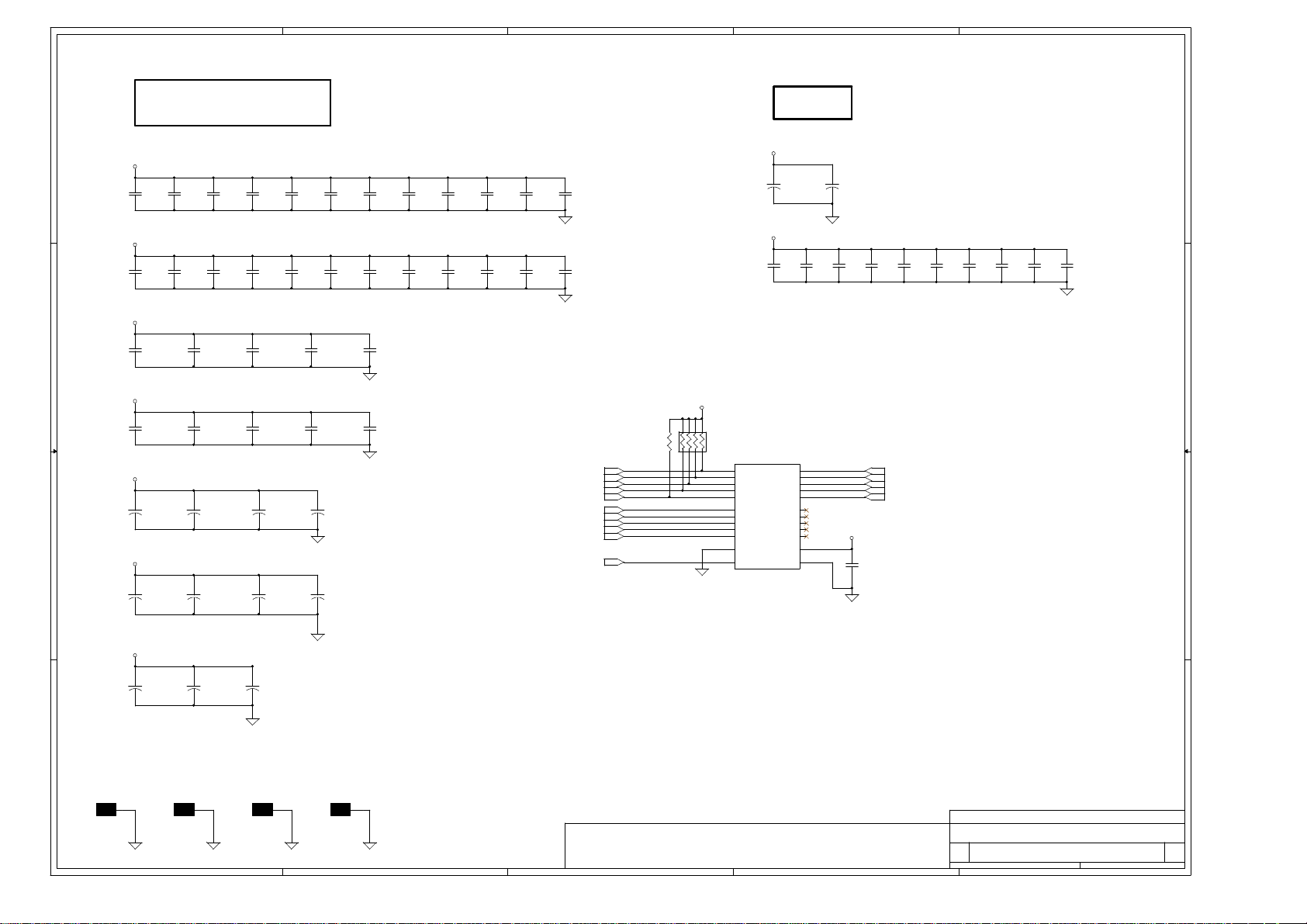

Layout note :

Distribute as close as possible

to GMCH Processor Quadrant .

+VTT

D D

+VTT

+VTT

+

C C

+VTT

+

+VTT

+

+VTT

+

B B

+VTT

12

C169

.1UF_0402

12

C158

.1UF_0402

12

C27

220UF_D2_4V

12

C303

220UF_D2_4V

12

C122

@220UF_D2_4V

12

C127

@220UF_D2_4V

12

C306

10UF_10V_1206

12

C177

.1UF_0402

12

C203

.1UF_0402

12

C23

+

220UF_D2_4V

12

C163

.1UF_0402

12

C221

.1UF_0402

12

C267

.1UF_0402

12

C300

10UF_10V_1206

12

C193

.1UF_0402

12

C219

.1UF_0402

12

C187

.1UF_0402

12

C244

.1UF_0402

12

C264

.1UF_0402

12

C198

.1UF_0402

12

C237

.1UF_0402

12

C204

.1UF_0402

12

C243

.1UF_0402

12

C181

.1UF_0402

12

C208

.1UF_0402

12

C247

.1UF_0402

12

C213

.1UF_0402

12

C245

.1UF_0402

12

C197

.1UF_0402

12

C207

.1UF_0402

12

C291

.1UF_0402

12

C223

.1UF_0402

12

C257

.1UF_0402

12

C206

.1UF_0402

12

C286

.1UF_0402

12

C236

.1UF_0402

12

C265

.1UF_0402

12

C220

.1UF_0402

12

C256

.1UF_0402

12

C246

.1UF_0402

12

C295

.1UF_0402

12

C224

.1UF_0402

12

C225

.1UF_0402

12

C274

.1UF_0402

12

C276

.1UF_0402

12

C238

.1UF_0402

12

C239

.1UF_0402

12

C271

.1UF_0402

12

C251

.1UF_0402

Layout note :

Distribute as close as possible

to VCCPCMOS_LM. (GMCH pin

AF6, AE7, AC9, AC8)

+1.8VS

12

12

C288

@.1UF_0402

12

C282

.1UF_0402

Layout note :

Distribute as close as possible

to GMCH Local Memory Quadrant .

+1.8VS

12

12

12

C252

82PF

C279

.1UF_0402

C156

.1UF_0402

Layout note :

Distribute as close as possible

to GMCH AGP/DVO Quadrant .

+1.5VS

12

+

22UF_10V_1206

C273

12

C214

.1UF_0402

Layout note :

Distribute as close as possible

to GMCH System Memory Quadrant .

+3V

12

+

22UF_10V_1206

+3V

12

C133

C149

.1UF_0402

12

12

C138

.1UF_0402

C159

.1UF_0402

12

C269

@.01UF_0402

12

C255

.1UF_0402

12

C140

.1UF_0402

C280

.1UF_0402

12

C268

.01UF_0402

12

C240

.1UF_0402

12

+

C304

22UF_10V_1206

12

C262

.1UF_0402

12

C209

.1UF_0402

12

C232

.1UF_0402

12

C272

82PF

12

12

C242

C285

.1UF_0402

82PF

12

C258

82PF

12

C296

82PF

12

C275

.1UF_0402

12

C287

.1UF_0402

12

C254

.1UF_0402

12

C250

.1UF_0402

12

C186

.01UF_0402

12

C299

82PF

.1UF Cap Used X7R

12

12

12

C171

82PF

C162

.1UF_0402

C168

.1UF_0402

12

12

12

C154

C284

.1UF_0402

82PF

C139

.1UF_0402

12

C179

82PF

12

C147

.1UF_0402

12

C150

.1UF_0402

12

12

C166

C148

82PF

.1UF_0402

Layout note :

Distribute as close as possible

to IO Quadrant .

A A

5

4

+3V

12

C125

+

22UF_10V_1206

3

12

C155

.1UF_0402

12

C137

.1UF_0402

Title

Size Document Number Rev

2

Date: Sheet of

Compal Electronics, Inc.

GMCH-M Decoupling

ADY11 LA-1181

1

11 41Friday, November 16, 2001

2

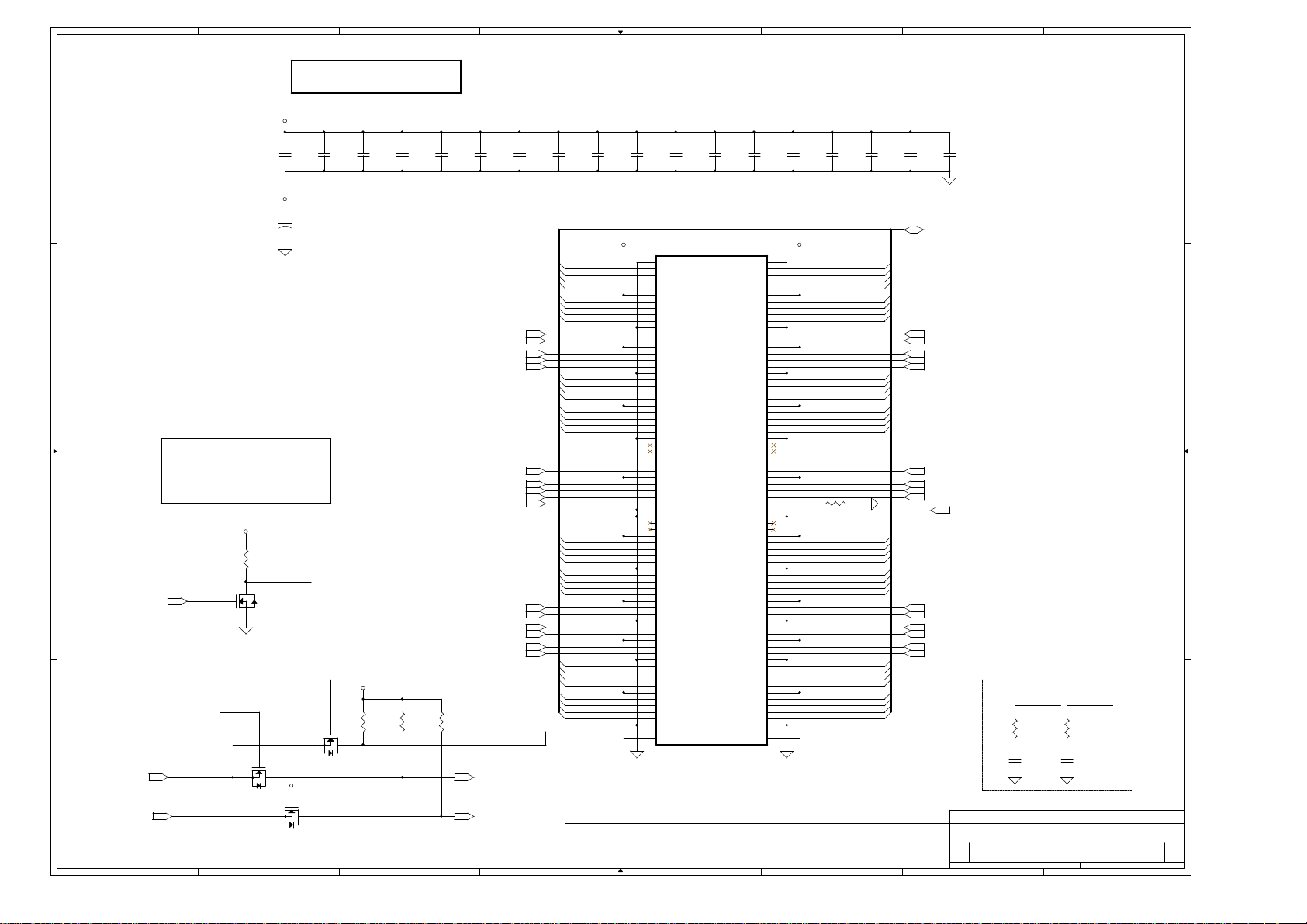

Page 12

A

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,I

NC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF

THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE

INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF

COMPAL ELECTRONICS,INC.

B

C

D

E

F

G

H

Layout note :

One .1uF cap per power pin .

Place each cap close to SODIMM(DIMM 0) pin .

+3V

1 1

2 2

12

C330

.1UF_0402

+3V

12

C316

+

22UF_10V_1206

System S MBus Select

SM_SEL#

0=SODIMM0 ;

1=SODIMM1

+3VS

12

2

G

SM_SEL#

R268

10K_0402

13

D

S

S

2N7002

G

Q17

2

SM_SEL

2N7002

Q19

13

D

B

SM_SEL

+5VS

G

2

Q18

13

D

S

2N7002

3 3

SM_SEL#<16>

4 4

SMB_DATA<14,16,18> SODIMM1_SMDAT1 <13>

A

SM_SEL#

12

S

C72

.1UF_0402

G

2

13

D

2N7002

+3V

Q16

12

C329

.1UF_0402

12

R183

10K_0402

SODIMM_SMCLK

12

C335

.1UF_0402

12

R184

10K_0402

C

12

C331

.1UF_0402

12

R48

10K_0402

12

SODIMM_SMCLK <13>SMB_CLK<14,16,18>

C68

.1UF_0402

SM_DQM4<9,13>

SM_DQM5<9,13>

SM_MA0<9,13>

SM_MA1<9,13>

SM_MA2<9,13>

SMD_CLK0<9>

SM_RAS#<9,13>

SM_WE#<9,13>

SM_CS#0<9>

SM_CS#1<9>

SM_MA6<9,13>

SM_MA8<9,13>

SM_MA9<9,13>

SM_MA10<9,13>

SM_DQM6<9,13>

SM_DQM7<9,13>

12

C71

.1UF_0402

12

C328

.1UF_0402

SM_DQ32

SM_DQ33

SM_DQ34

SM_DQ35

SM_DQ36

SM_DQ37

SM_DQ38

SM_DQ39

SM_DQM4

SM_DQM5

SM_MA0

SM_MA1

SM_MA2

SM_DQ40

SM_DQ41

SM_DQ42

SM_DQ43

SM_DQ44

SM_DQ45

SM_DQ46

SM_DQ47

SMD_CLK0

SM_RAS#

SM_WE#

SM_CS#0

SM_CS#1

SM_DQ48

SM_DQ49

SM_DQ50

SM_DQ51

SM_DQ52

SM_DQ53

SM_DQ54

SM_DQ55

SM_MA6

SM_MA8

SM_MA9

SM_MA10

SM_DQM6

SM_DQM7

SM_DQ56

SM_DQ57

SM_DQ58

SM_DQ59

SM_DQ60

SM_DQ61

SM_DQ62

SM_DQ63

SODIMM0_SMDAT0

D

12

C334

.1UF_0402

JP21

1

VSS

3

DQ0

5

DQ1

7

DQ2

9

DQ3

11

VCC

13

DQ4

15

DQ5

17

DQ6

19

DQ7

21

VSS

23

CKE0#DQMB0

25

CKE1#/DQMB1

27

VCC

29

A0

31

A1

33

A2

35

VSS

37

DQ8

39

DQ9

41

DQ10

43

DQ11

45

VCC

47

DQ12

49

DQ13

51

DQ14

53

DQ15

55

VSS

57

RFU/DQ64

59

RFU/DQ65

61

RFU/CLK0

63

VCC

65

RFU/RAS#

67

WE#

69

RE0#/S0#

71

RE1#/S1#

73

RFU/EDO_OE#

75

VSS

77

RFU/DQ66

79

RFU/DQ67

81

VCC

83

DQ16

85

DQ17

87

DQ18

89

DQ19

91

VSS

93

DQ20

95

DQ21

97

DQ22

99

DQ23

101

VCC

103

A6

105

A8

107

VSS

109

A9

111

A10

113

VCC

115

CE2#/DQMB2

117

CE3#/DQMB3

119

VSS

121

DQ24

123

DQ25

125

DQ26

127

DQ27

129

VCC

131

DQ28

133

DQ29

135

DQ30

137

DQ31

139

VSS

141

SDA

143

VCC

SO-DIMM144-Reverse

12

C347

.1UF_0402

12

C327

.1UF_0402

DQMB4/CE4#

DQMB5/CE5#

DQMB6/CE6#

DQMB7/CE7#

DQ32

DQ33

DQ34

DQ35

VCC

DQ36

DQ37

DQ38

DQ39

VCC

DQ40

DQ41

DQ42

DQ43

VCC

DQ44

DQ45

DQ46

DQ47

DQ68/RFU

DQ69/RFU

CKE0/RFU

VCC

CAS#/RFU

CKE1/RFU

A12/RFU

A13/RFU

CLK1/RFU

DQ70/RFU

DQ71/RFU

VCC

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

VCC

VCC

DQ56

DQ57

DQ58

DQ59

VCC

DQ60

DQ61

DQ62

DQ63

VCC

12

C69

.1UF_0402

+3V +3V

DIMM0

E

12

VSS

VSS

A3

A4

A5

VSS

VSS

VSS

VSS

A7

BA0

VSS

BA1

A11

VSS

VSS

SCL

C65

.1UF_0402

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

12

C332

.1UF_0402

SM_DQ0

SM_DQ1

SM_DQ2

SM_DQ3

SM_DQ4

SM_DQ5

SM_DQ6

SM_DQ7

SM_DQM0

SM_DQM1

SM_MA3

SM_MA4

SM_MA5

SM_DQ8

SM_DQ9

SM_DQ10

SM_DQ11

SM_DQ12

SM_DQ13

SM_DQ14

SM_DQ15

SM_CKE0

SM_CAS#

SM_CKE1

SM_MA12

1 2

R50 0_0402

SM_DQ16

SM_DQ17

SM_DQ18

SM_DQ19

SM_DQ20

SM_DQ21

SM_DQ22

SM_DQ23

SM_MA7

SM_BA0

SM_BA1

SM_MA11

SM_DQM2

SM_DQM3

SM_DQ24

SM_DQ25

SM_DQ26

SM_DQ27

SM_DQ28

SM_DQ29

SM_DQ30

SM_DQ31

SODIMM_SMCLK

12

C67

.1UF_0402

F

12

C333

.1UF_0402

12

SMD_CLK1

C70

.1UF_0402

12

C66

.1UF_0402

SM_DQ[0..63] <9,13>

SM_DQM0 <9,13>

SM_DQM1 <9,13>

SM_MA3 <9,13>

SM_MA4 <9,13>

SM_MA5 <9,13>

SM_CKE0 <9>

SM_CAS# <9,13>

SM_CKE1 <9>

SM_MA12 <9,13>

SMD_CLK1 <9>

SM_MA7 <9,13>

SM_BA0 <9,13>

SM_BA1 <9,13>

SM_MA11 <9,13>

SM_DQM2 <9,13>

SM_DQM3 <9,13>

Place closely to DIMM0

12

R185

@10

12

C326

@15PF

Title

Size Document Number Rev

Date: Sheet of

Compal Electronics, Inc.

SO-DIMM SLOT0 /Decoupling & DIMM Select

ADY11 LA-1181

G

12

12

SMD_CLK1SMD_CLK0

R49

@10

C73

@15PF

12 41Friday, November 16, 2001

H

2

Page 13

A

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,I

NC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF

THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE

INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF

COMPAL ELECTRONICS,INC.

B

C

D

E

Layout note :

One .1uF cap per power pin .

Place each cap close to SODIMM(DIMM 1) pin .

+3V

12

C55

.1UF_0402

SM_DQ32

SM_DQ33

SM_DQ34

SM_DQ35

SM_DQ36

SM_DQ37

SM_DQ38

SM_DQ39

SM_DQM4

SM_DQM5

SM_MA3

SM_MA4

SM_MA5

SM_DQ40

SM_DQ41

SM_DQ42

SM_DQ43

SM_DQ44

SM_DQ45

SM_DQ46

SM_DQ47

SM_CKE2

SM_CAS#

SM_CKE3

SM_MA12

1 2

SM_DQ48

SM_DQ49

SM_DQ50

SM_DQ51

SM_DQ52

SM_DQ53

SM_DQ54

SM_DQ55

SM_MA7

SM_BA0

SM_BA1

SM_MA11

SM_DQM6

SM_DQM7

SM_DQ56

SM_DQ57

SM_DQ58

SM_DQ59

SM_DQ60

SM_DQ61

SM_DQ62

SM_DQ63

SODIMM_SMCLK

12

C54

.1UF_0402

12

C48

.1UF_0402

SMD_CLK3

D

12

12

C56

.1UF_0402

SM_DQ[0..63] <9,12>

SM_DQM4 <9,12>

SM_DQM5 <9,12>

SM_MA3 <9,12>

SM_MA4 <9,12>

SM_MA5 <9,12>

SM_CKE2 <9>

SM_CAS# <9,12>

SM_CKE3 <9>

SM_MA12 <9,12>

12

12

C63

C57

.1UF_0402

.1UF_0402

SMD_CLK3 <9>

SM_MA7 <9,12>

SM_BA0 <9,12>

SM_BA1 <9,12>

SM_MA11 <9,12>

SM_DQM6 <9,12>

SM_DQM7 <9,12>

Title

Size Document Number Rev

ADY11 LA-1181

Date: Sheet of

12

C52

C51

.1UF_0402

.1UF_0402

Place closely to DIMM1

SMD_CLK2 SMD_CLK3

12

12

R47

@10

C64

@15PF

12

12

Compal Electronics, Inc.

SO-DIMM SLOT1 & Decoupling

E

R44

@10

C45

@15PF

2

13 41Friday, November 16, 2001

1

12

C59

.1UF_0402

+3V

12

C44

+

22UF_10V_1206

SMD_CLK2<9>

PAD14

PAD-2.5X3

SM_DQM0<9,12>

SM_DQM1<9,12>

SM_MA0<9,12>

SM_MA1<9,12>

SM_MA2<9,12>

SM_RAS#<9,12>

SM_WE#<9,12>

SM_CS#2<9>

SM_CS#3<9>

SM_MA6<9,12>

SM_MA8<9,12>

SM_MA9<9,12>

SM_MA10<9,12>

SM_DQM2<9,12>

SM_DQM3<9,12>

B

1 1

2 2

3 3

4 4

EMI Clip PAD for Memory Door

PAD10

PAD-2.5X3

PAD11

1

PAD-2.5X3

A

PAD12

1

PAD-2.5X3

PAD19

1

PAD-2.5X3

12

12

C60

.1UF_0402

SODIMM1_SMDAT1<12> SODIMM_SMCLK <12>

PAD16

1

PAD-2.5X3

C61

.1UF_0402

1

12

C58

.1UF_0402

SM_DQ0

SM_DQ1

SM_DQ2

SM_DQ3

SM_DQ4

SM_DQ5

SM_DQ6

SM_DQ7

SM_DQM0

SM_DQM1

SM_MA0

SM_MA1

SM_MA2

SM_DQ8

SM_DQ9

SM_DQ10

SM_DQ11

SM_DQ12

SM_DQ13

SM_DQ14

SM_DQ15

SMD_CLK2

SM_RAS#

SM_WE#

SM_CS#2

SM_CS#3

SM_DQ16

SM_DQ17

SM_DQ18

SM_DQ19

SM_DQ20

SM_DQ21

SM_DQ22

SM_DQ23

SM_MA6

SM_MA8

SM_MA9

SM_MA10

SM_DQM2

SM_DQM3

SM_DQ24

SM_DQ25

SM_DQ26

SM_DQ27

SM_DQ28

SM_DQ29

SM_DQ30

SM_DQ31

SODIMM1_SMDAT1

PAD18

PAD-2.5X3

12

12

C62

C53

.1UF_0402

.1UF_0402

+3V +3V

JP13

1

VSS

3

DQ0

5

DQ1

7

DQ2

9

DQ3

11

VCC

13

DQ4

15

DQ5

17

DQ6

19

DQ7

21

VSS

23

CKE0#DQMB0

25

CKE1#/DQMB1

27