Dell 13-7370, 13-7570, 13-7373, 13-7573 Schematic

5

D D

4

3

2

1

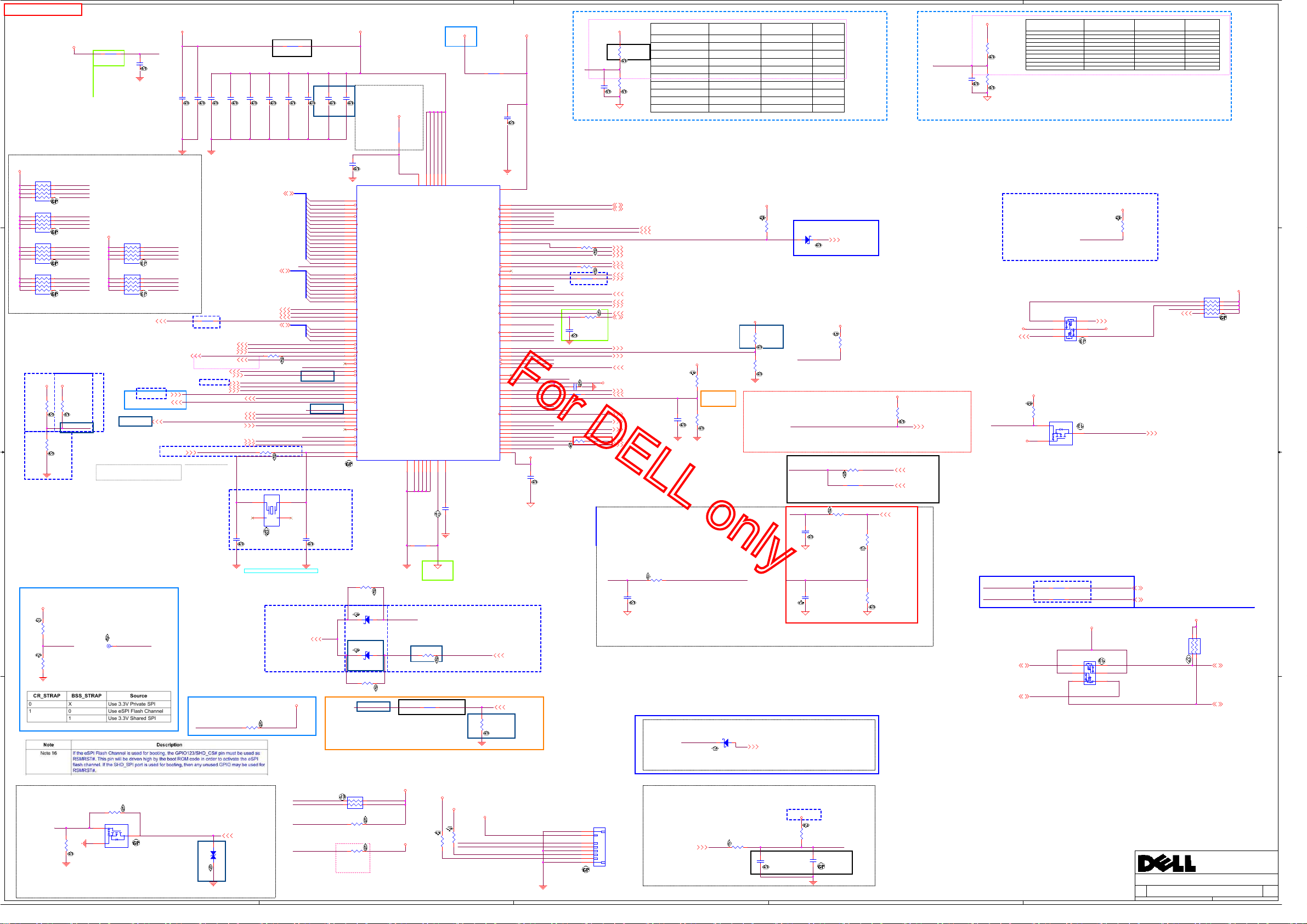

KyloRen 13" Schematics

KabyLake-R

C C

2017-06-29

REV : -1

B B

A A

DY : None Installed

UMA: UMA only installed

OPS: DISCRTE OPTIMUS installed

5

4

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Cover Page

Cover Page

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Thursday, June 29, 2017

Thursday, June 29, 2017

Thursday, June 29, 2017

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet of

Cover Page

KyloRen 13"

KyloRen 13"

KyloRen 13"

1 106

1 106

1 106

1

A00

A00

A00

5

4

3

2

1

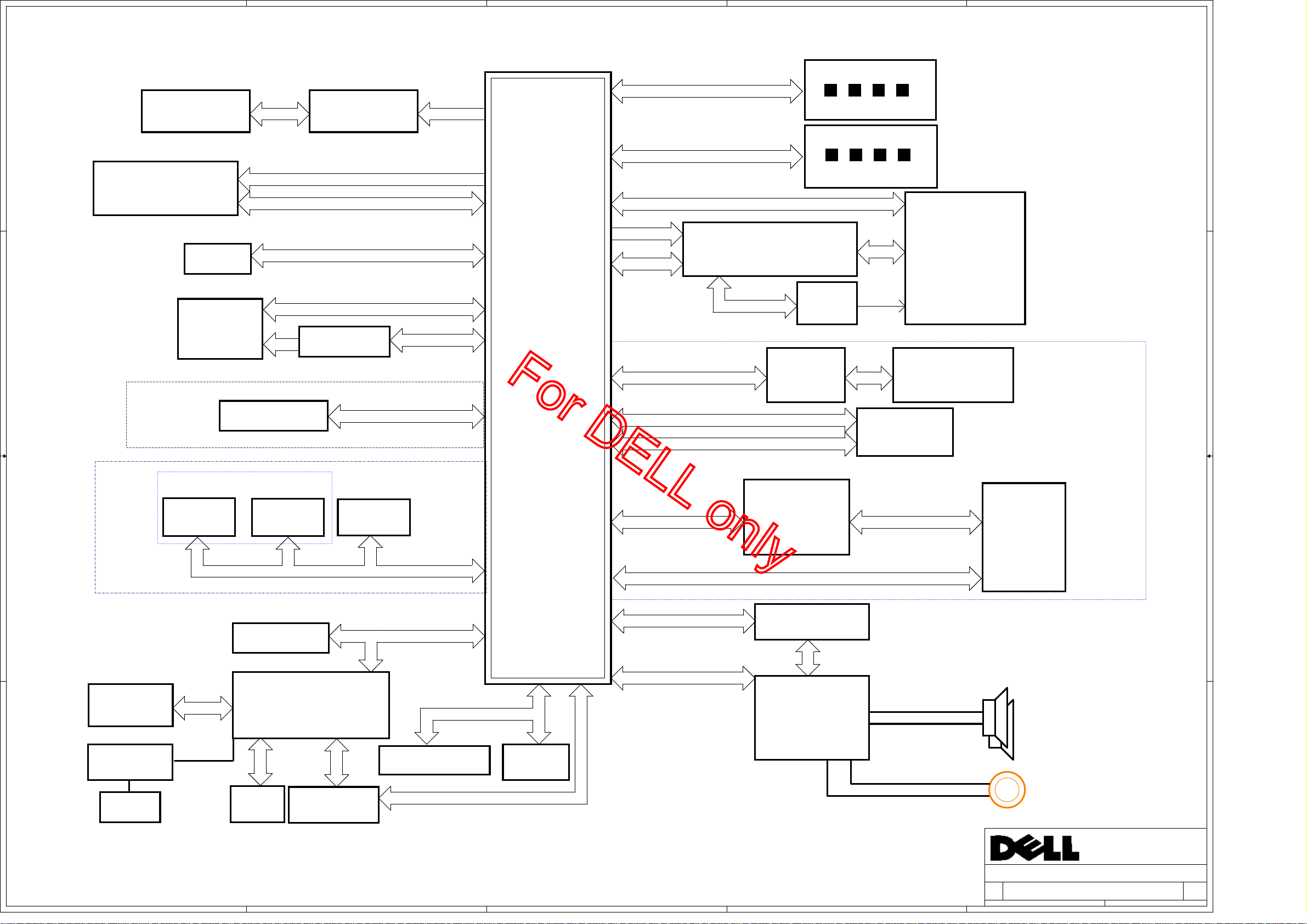

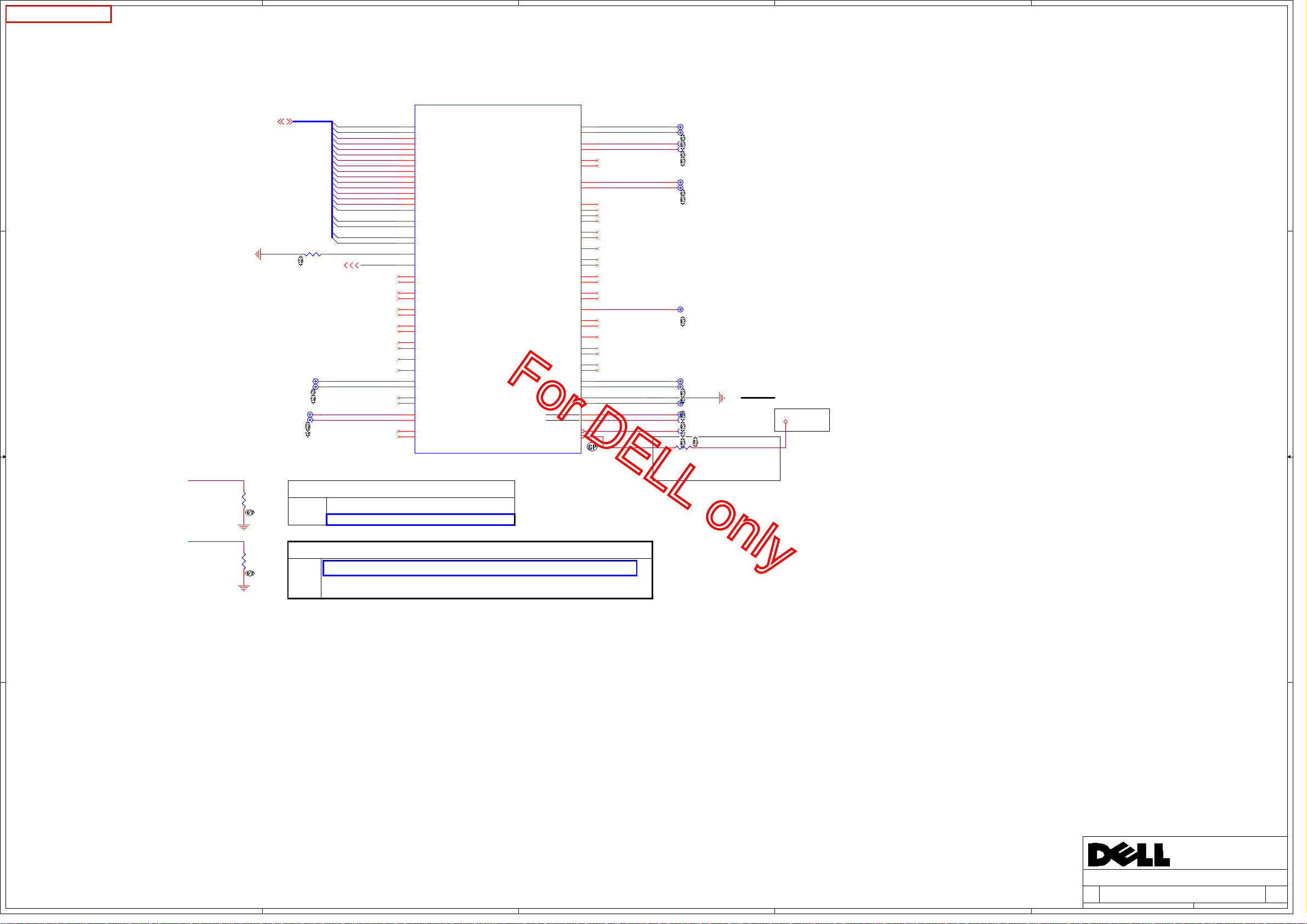

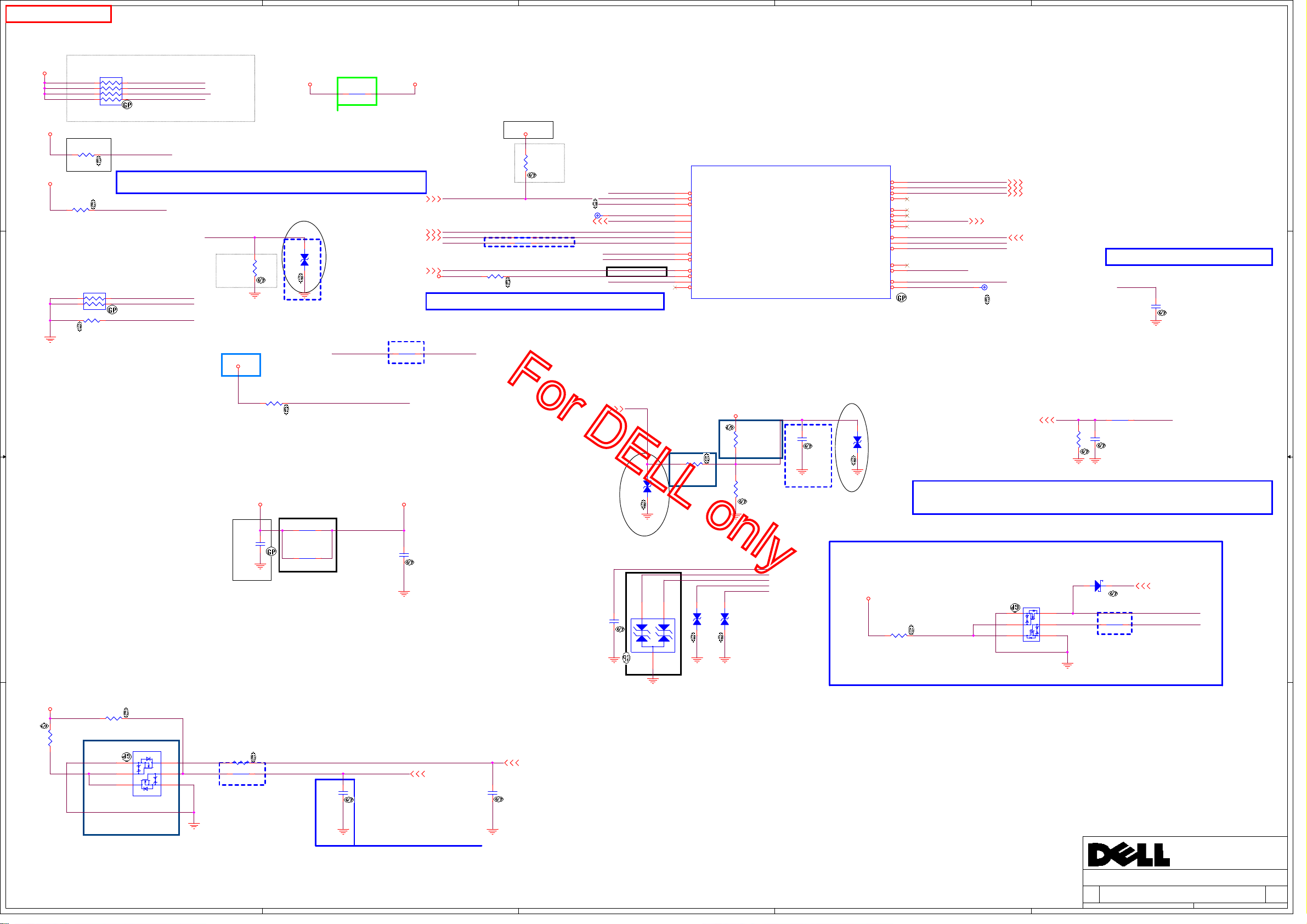

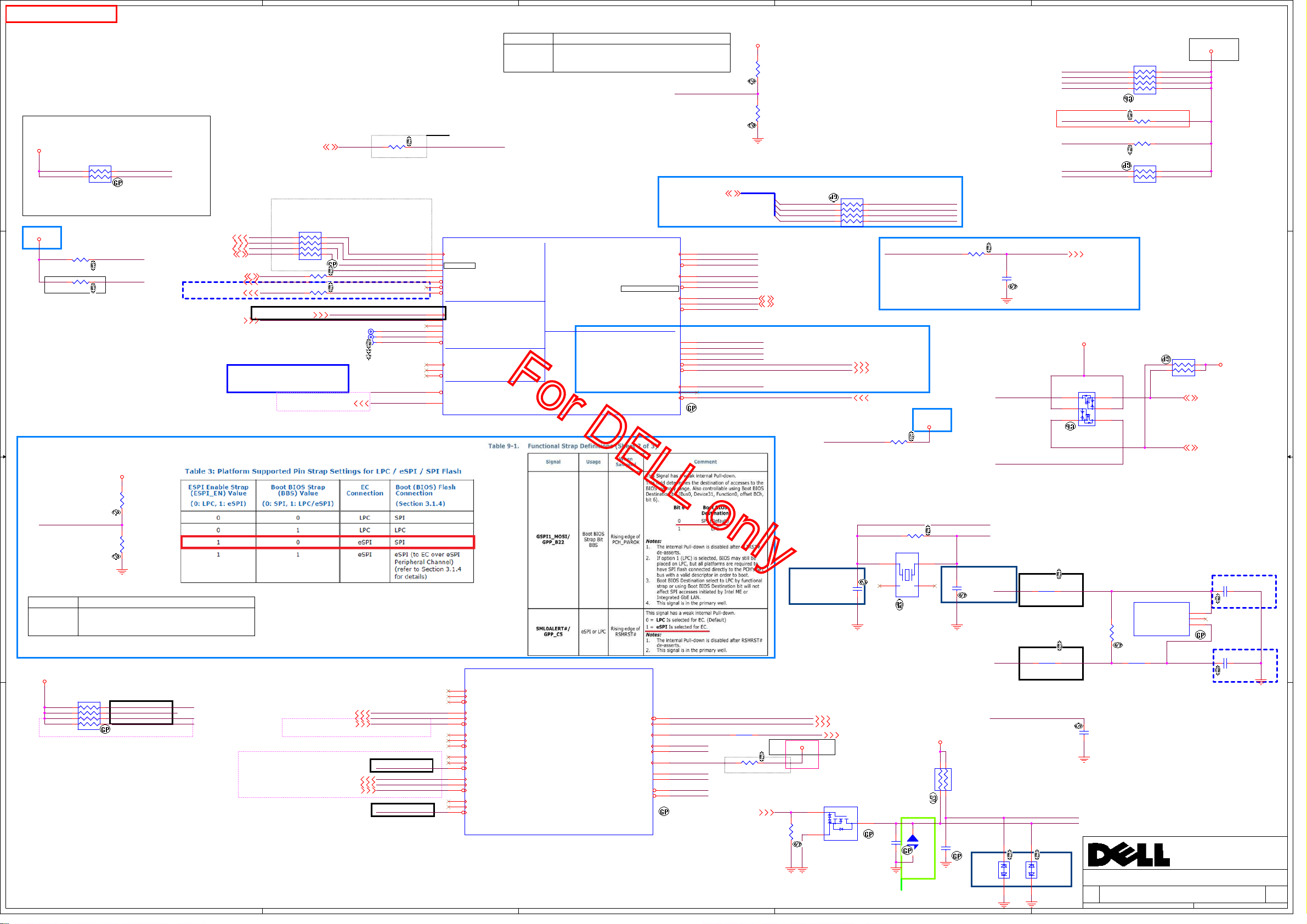

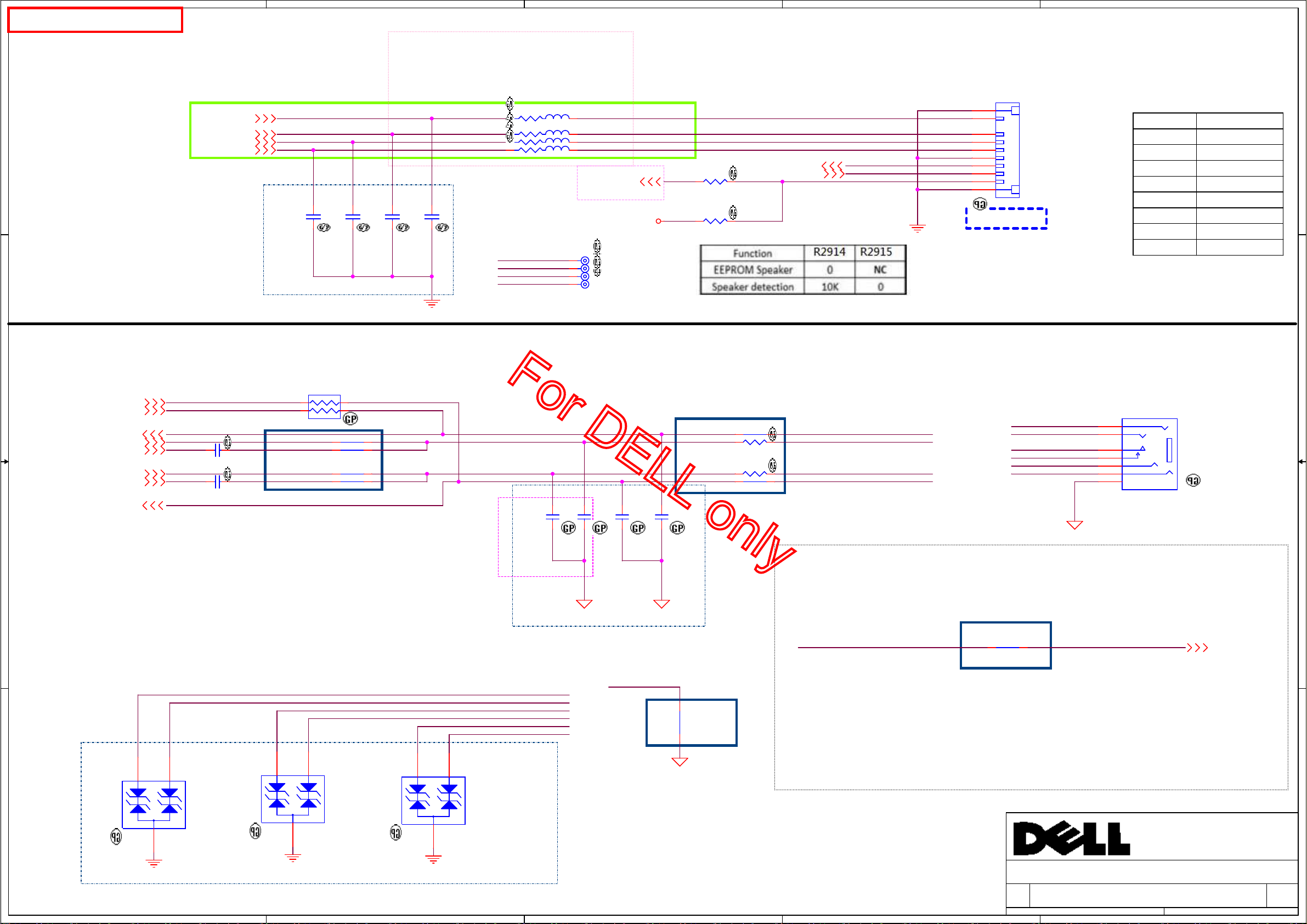

KBL-U(R) 13" CPU 15W Block Diagram

Project code: 4PD0B5010001

PCB P/N: 16839

Revision: -1

Channel A

D D

HDMI V2.0

HDMI 2.0

57

HDMI Converter

Parade

PS175

57

DP1.2

Intel CPU

Kaby Lake U

Channel B

13.3"

eDP

Kaby Lake R

15W (UMA)

(HD/FHD)

Touch panel

M.2 SSD

55

63

SATA/PCIex2/PCIEx4(Optane)

USB3.0 Port2

USB PowerShare

C C

Power share

36

TI

TPS2544RTER

USB3.0

34

I2C

USB3.0 LANE1

USB2.0

USB2.0 LANE1

KBL PCH-LP

10 USB 2.0/1.1 ports

6 USB 3.0 ports

High Definition Audio

3 SATA ports

6 PCIE ports

LPC I/F

ACPI 5.0

USB2.0

DP

USB3.0

USB3.0 LANE4

USB2.0 LANE8

USB2.0 LANE4

1Rx16

1Rx16

MUX and Redriver

TI

TUSB546

USB2.0 x 1

I2C

DDR4

DDR4 13X16 Memory Down

CC

Cypress

CCG4

CardReader

SD 3.0

Realtak

RTS5176E

X16 Memory Down

DP/USB 3.0

38

CC1/CC2

12

USB3.0 type c

Port1

3837

SD Card Slot

Clamshell

Finger Printer

92

USB2.0 LANE9

USB2.0 x 1

PCIE LANE5

USB2.0 LANE6

PCIe

USB2.0

NGFF WLAN

IO Board

Sensor BD on

Panel side

USB 3.0

re-driver

TI

HPA02232ARGER

USB2.0

Camera (HD/IR)

D-MIC

SMBUS

HDA

CODEC

Realtek

ALC3254

USB2.0 LANE3

55

27

MIC_IN/GND

USB3.0

USB3.0 LANE3

2CH SPEAKER

(2CH 2W/4ohm)

USB3.0 Port3

I2C

68

Free fall

Gsensor

ST

LNG2DMTR

70

eSPI

USB3.0

USB2.0 x 1

USB2.0 LANE5

USB3.0 LANE3

Accelerometer

E-compass

ST

2 in 1

B B

LIS3MDL

Gyro+G

ST

LSM6DS3

eSPI debug port

HDA

Thermal

NUVOTON

NCT7718W

Fan Control

PWM

26

SMBUS

FAN DETECT

KB SCAN

INTERFACE

KBC

MICROCHIP

MEC1416

PS2

24

TPM

NUVOTON NPCT650

SPI

Flash ROM

91

16MB

Quad Read

2526

A A

FAN

5

Int.

KB

Touch PAD

Image sensor

4

I2C

HP_R/L

Universal Jack

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet of

Block Diagram

Block Diagram

Block Diagram

KyloRen 13"

KyloRen 13"

KyloRen 13"

1

A00

A00

2 106Thursday, June 29, 2017

2 106Thursday, June 29, 2017

2 106Thursday, June 29, 2017

A00

5

D D

4

3

2

1

C C

(Blanking)

B B

A A

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

C

C

C

(Reserved)

(Reserved)

(Reserved)

KyloRen 13"

KyloRen 13"

KyloRen 13"

A00

A00

3 106Thursday, June 29, 2017

3 106Thursday, June 29, 2017

1

3 106Thursday, June 29, 2017

A00

5

4

3

2

1

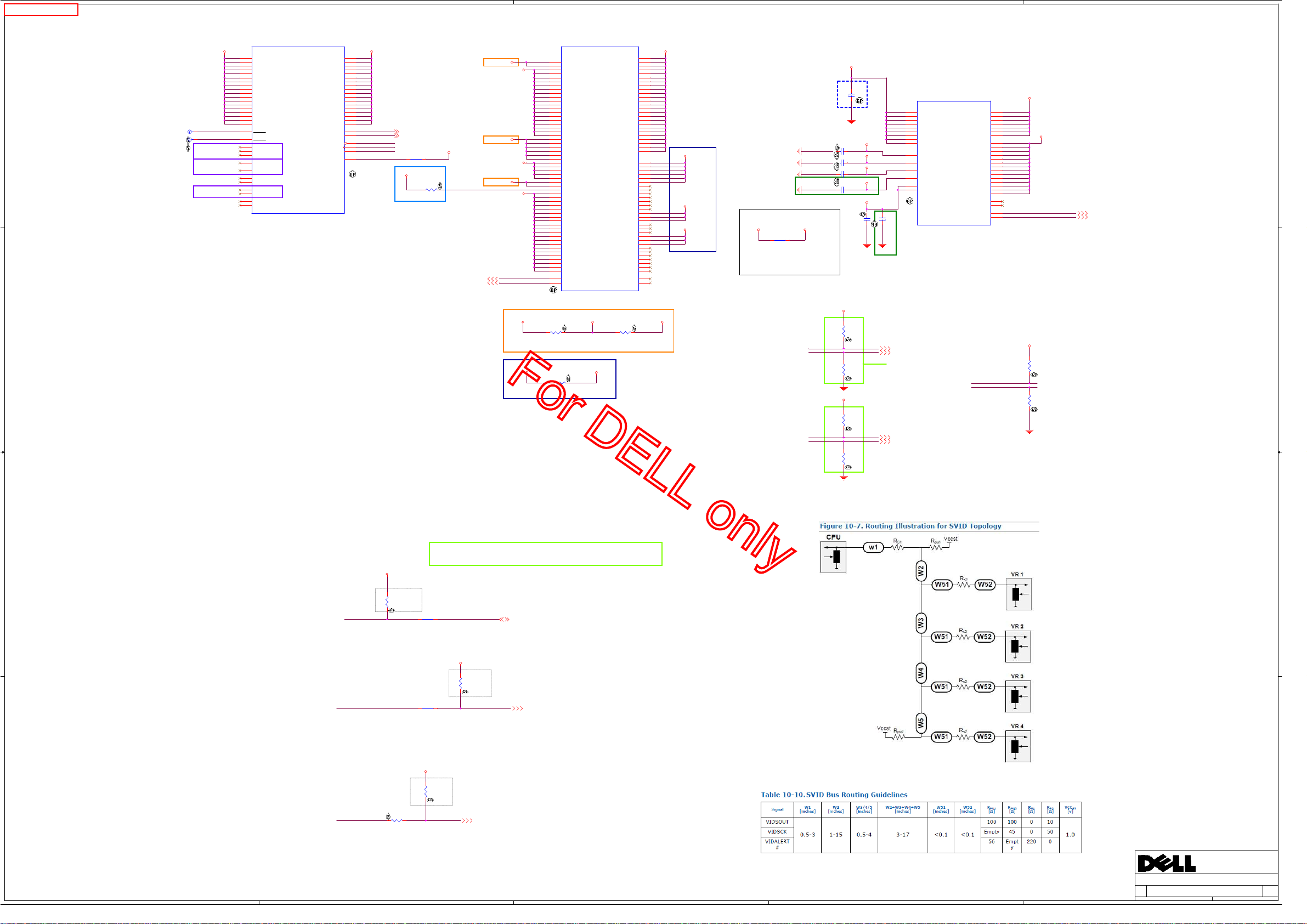

SSID = CPU

+VCCST_CPU

12

R419

1KR2J-1-GP

+VCCSTG

D D

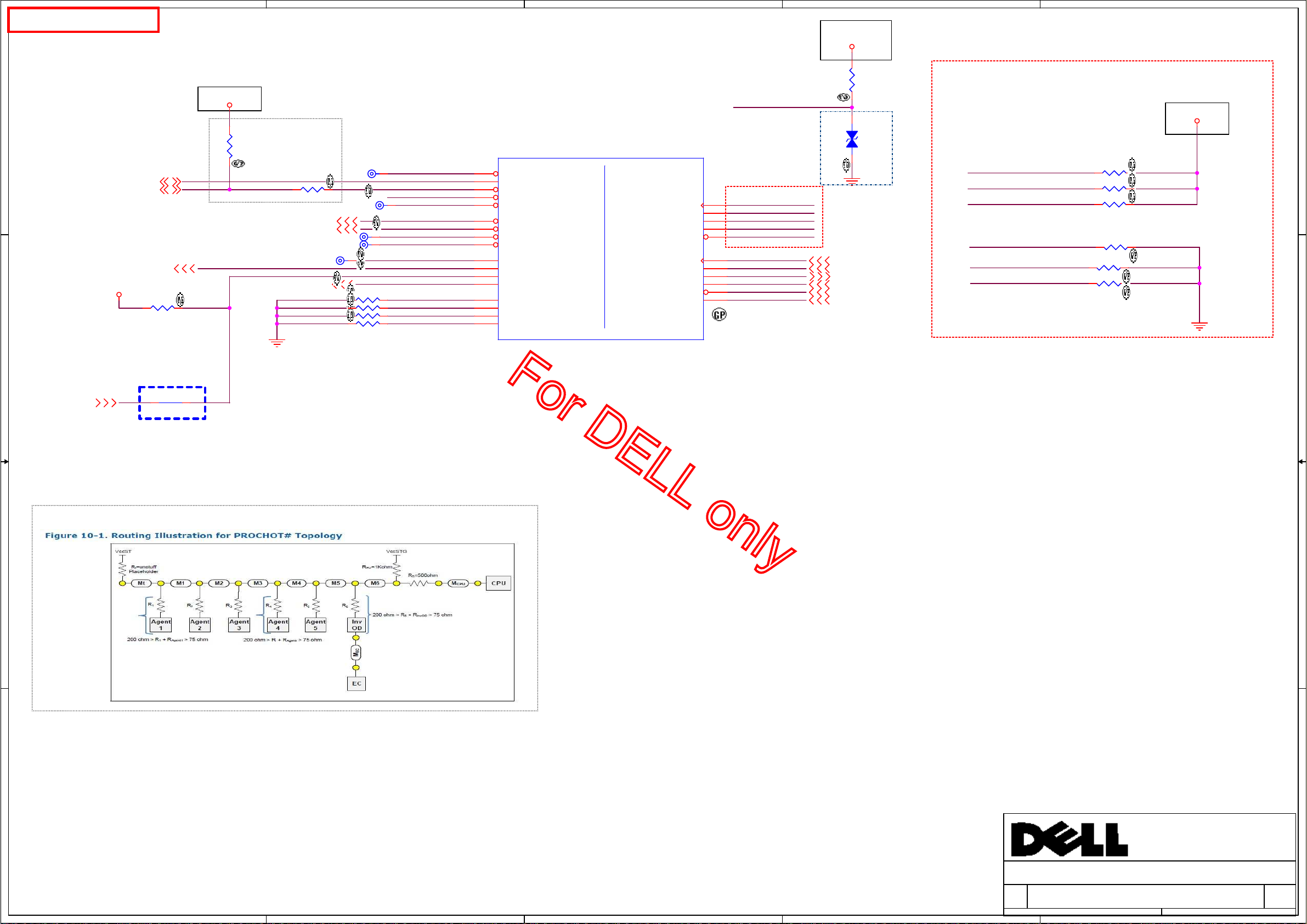

[PECI] and [PROCHOT#]

Impedance control: 50 ohm

PECI24

H_PROCHOT#24,44,46

TOUCH_PANEL_INTR#55

3D3V_S5_PCH

C C

R404

1 2

DY

100KR2J-1-GP

12

Rb

+VCCSTG = 1.0 V +VCCSTG = 1.0 V

PCH_THERMTRIP#

12

R401

1KR2J-1-GP

TPAD14-OP-GP

TPAD14-OP-GP

TPAD14-OP-GP

TOUCH_PANEL_PD#55

1 2

R403499R2F-2-GP

Ra

TPAD14-OP-GP

XDP_BPM099

XDP_BPM199

TP403

TOUCH_PAD_INTR#

TP401

TPAD14-OP-GP

TP402

TP407

TP408

1

R41249D9R2F-GP

R41349D9R2F-GP

R41449D9R2F-GP

R41549D9R2F-GP

H_CATERR#

1

H_PROCHOT#_R

PCH_THERMTRIP#

1

SKTOCC#

XDP_BPM2

1

XDP_BPM3

1

GPP_E3/CPU_GP0

CPU_POPIRCOMP

12

PCH_POPIRCOMP

12

EDRAM_OPIO_RCOMP

12

EOPIO_RCOMP

12

CPU1D

D63

CATERR#

A54

PECI

C65

PROCHOT#

C63

THERMTRIP#

A65

SKTOCC#

C55

BPM#[0]

D55

BPM#[1]

B54

BPM#[2]

C56

BPM#[3]

A6

GPP_E3/CPU_GP0

A7

GPP_E7/CPU_GP1

BA5

GPP_B3/CPU_GP2

AY5

GPP_B4/CPU_GP3

AT16

PROC_POPIRCOMP

AU16

PCH_OPIRCOMP

H66

OPCE_RCOMP

H65

OPC_RCOMP

SKYLAKE-U-GP

SKYLAKE_ULT

CPU MISC

4 OF 20

JTAG

PROC_TCK

PROC_TDI

PROC_TDO

PROC_TMS

PROC_TRST#

PCH_JTAG_TCK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_TRST#

JTAGX

B61

D60

A61

C60

B59

B56

D59

A56

C59

C61

A59

XDP_TCK_JTAGX

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

XDP_TRST#

EC401

DY

AZ5725-01FDR7G-GP

20160812 EMI

PCH_JTAG_TCK 99

PCH_JTAG_TDI 99

PCH_JTAG_TDO 99

PCH_JTAG_TMS 99

XDP_TRST# 99

XDP_TCK_JTAGX 99

#544669 CRB Rev0.52

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

XDP_TCK_JTAGX

XDP_TRST#

PCH_JTAG_TCK

1 2

XDP

1 2

100R2F-L1-GP-U

R417 51R2J-2-GP

R402 51R2J-2-GP

R407 51R2J-2-GP

XDP

1 2

XDP

1 2

XDP

1 2

DY

1 2

DY

+VCCSTG

R40851R2J-2-GP

R409

R41651R2J-2-GP

071.SKYLA.000U

R410

TP_WAKE_KBC#24,65

1 2

0R0402-PAD

2016/12/28

(#543016) PROCHOT# Routing Guidelines

B B

M1,2,3,4,5: <3 inches

M6: 1-11 inches

MCPU: 0.3-1.5 inches

Mt <0.3 mils

Main route(M1+M2+M3+M4+M5+M6+MCPU): 1-12 inches

A A

5

4

3

2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

CPU_(JTAG/CPU SIDE BAND)

CPU_(JTAG/CPU SIDE BAND)

CPU_(JTAG/CPU SIDE BAND)

KyloRen 13"

KyloRen 13"

KyloRen 13"

4 106Thursday, June 29, 2017

4 106Thursday, June 29, 2017

4 106Thursday, June 29, 2017

1

A00

A00

A00

SSID = CPU

5

4

3

2

1

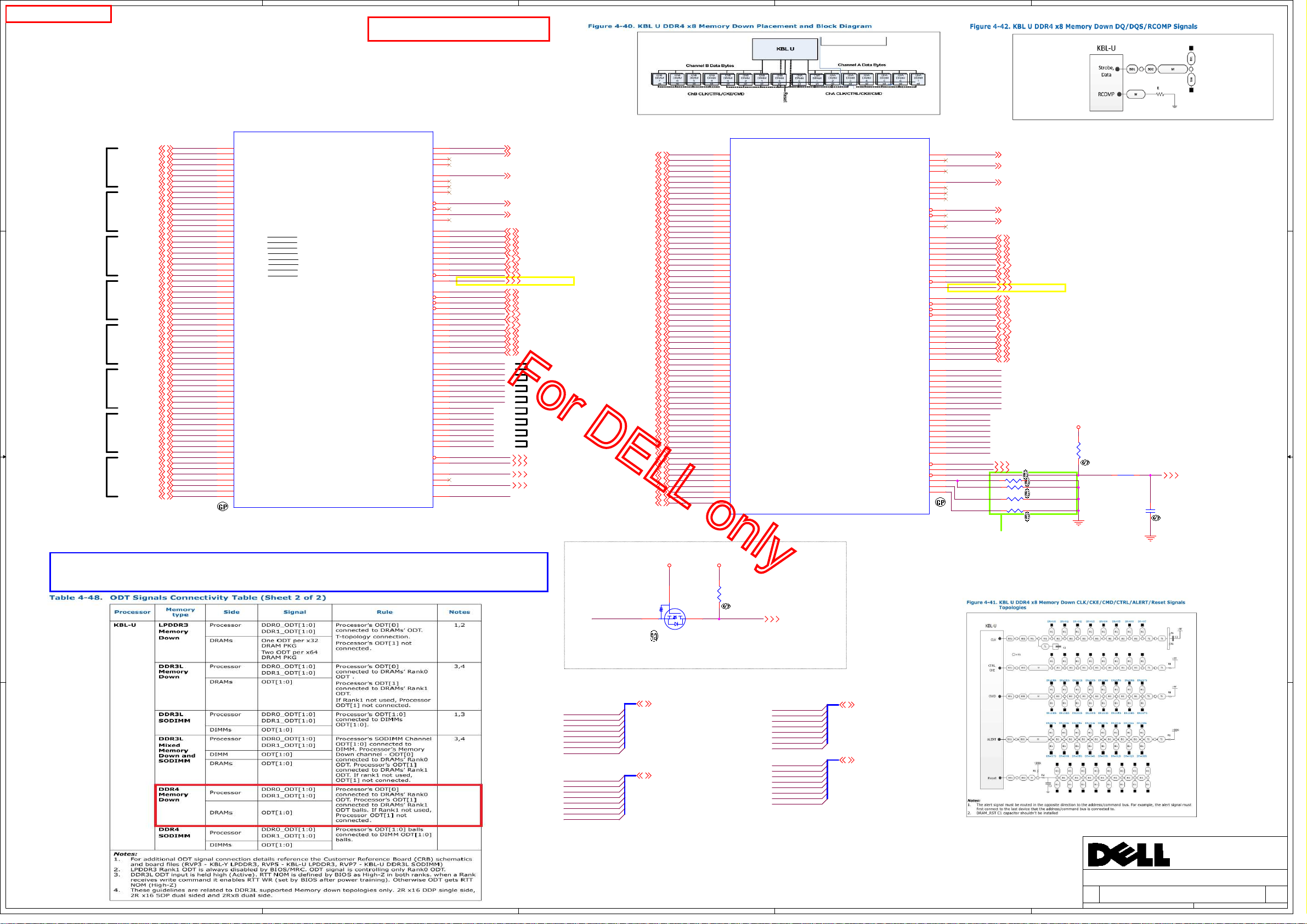

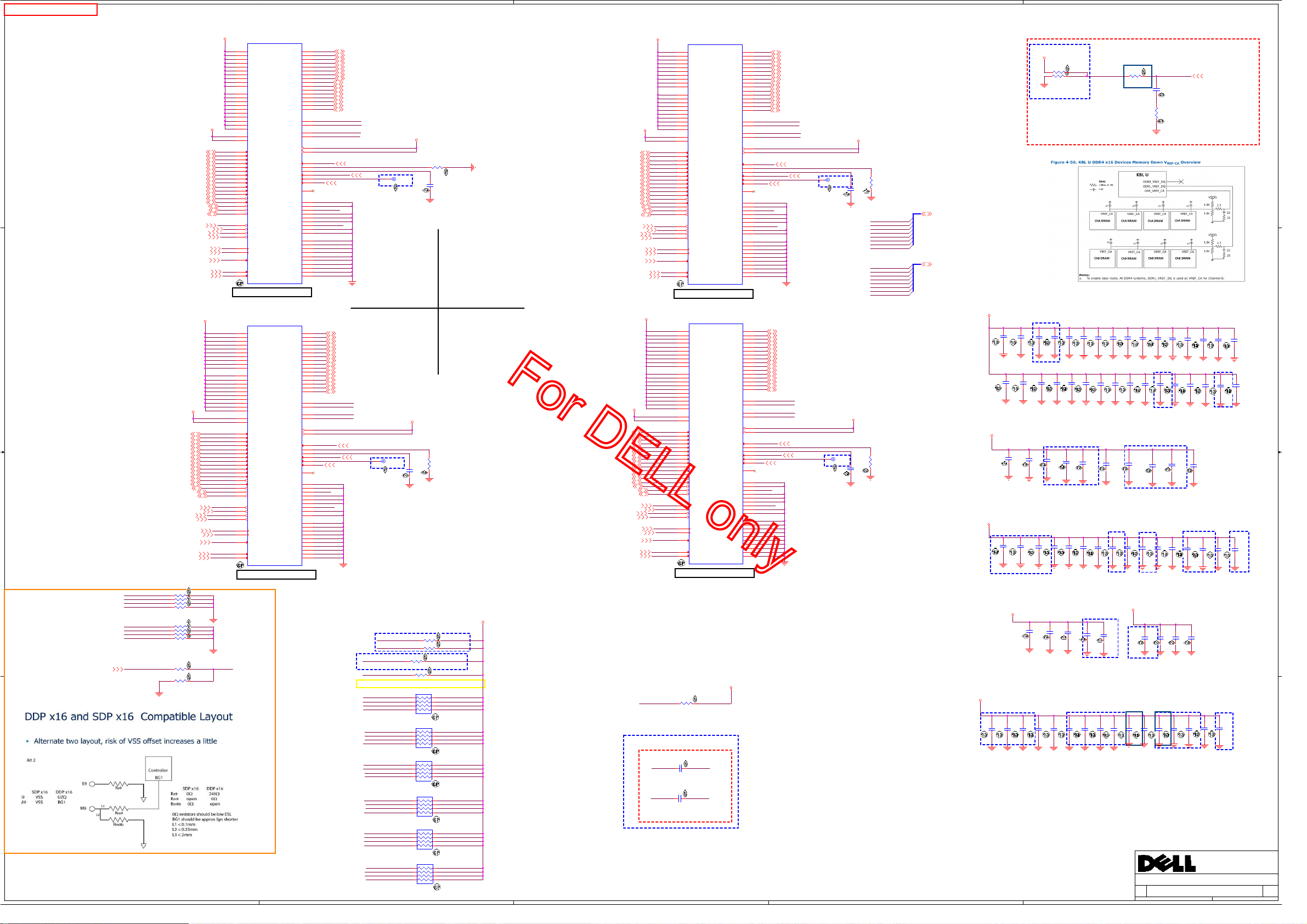

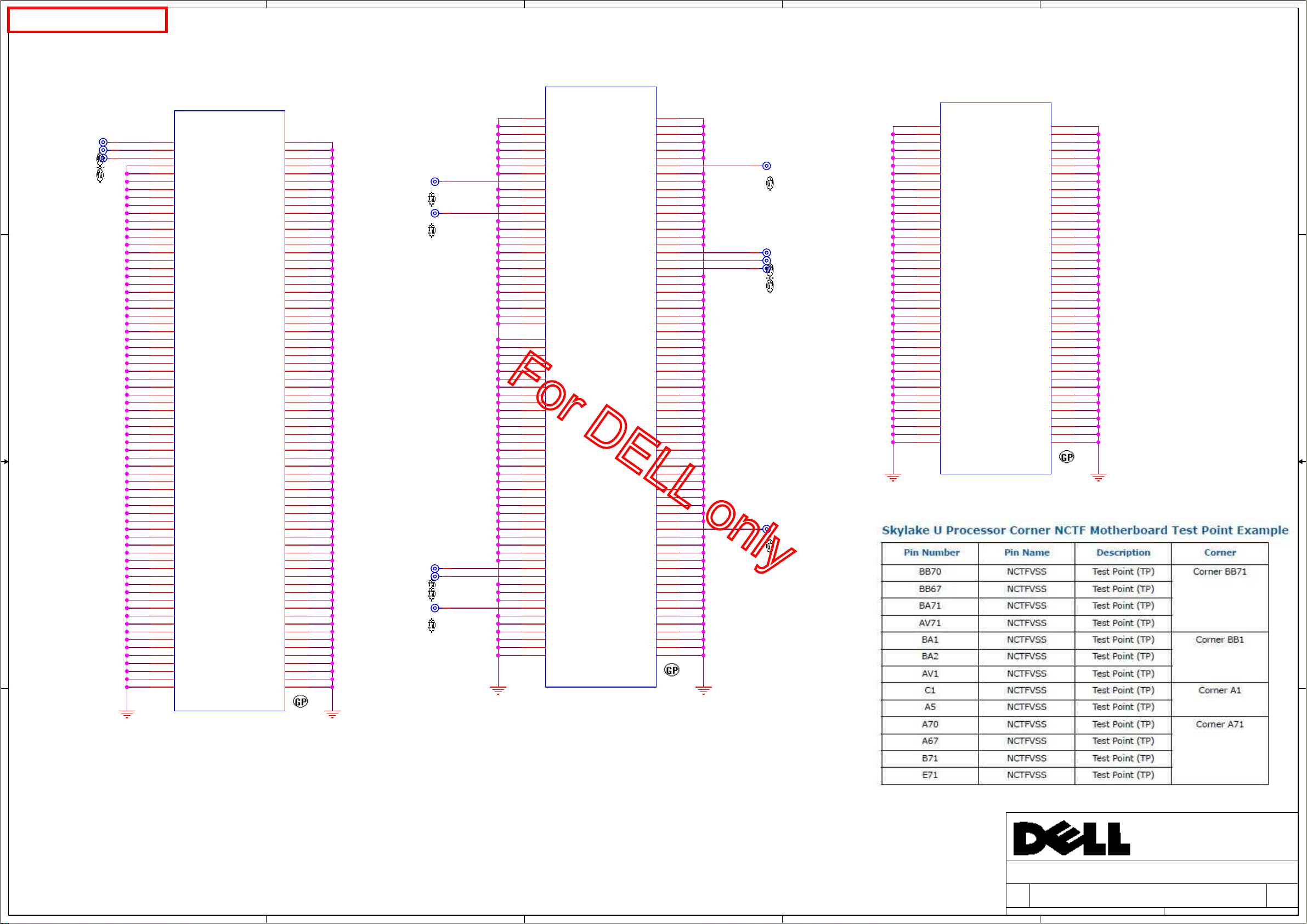

DDR4 ball type: Non-Interleaved Type

D D

M_A_DQ012

M_A_DQ112

M_A_DQ212

M_A_DQ[0:7]

M_A_DQ[8:15]

M_A_DQ[16:23]

M_A_DQ[24:31]

C C

M_A_DQ[32:39]

M_A_DQ[40:47]

M_A_DQ[48:55]

M_A_DQ[56:63]

DQ Bit Swapping is allowed within the same byte, and Byte Swapping is allowed within the same channel.

B B

Clock (CLK and CLK#) and Strobe (DQS and DQS#) differential signal swapping within a pair is not allowed. Also differential

clock pair to clock pair swapping within a channel is not allowed.

M_A_DQ312

M_A_DQ412

M_A_DQ512

M_A_DQ612

M_A_DQ712

M_A_DQ812

M_A_DQ912

M_A_DQ1012

M_A_DQ1112

M_A_DQ1212

M_A_DQ1312

M_A_DQ1412

M_A_DQ1512

M_A_DQ1612

M_A_DQ1712

M_A_DQ1812

M_A_DQ1912

M_A_DQ2012

M_A_DQ2112

M_A_DQ2212

M_A_DQ2312

M_A_DQ2412

M_A_DQ2512

M_A_DQ2612

M_A_DQ2712

M_A_DQ2812

M_A_DQ2912

M_A_DQ3012

M_A_DQ3112

M_A_DQ3212

M_A_DQ3312

M_A_DQ3412

M_A_DQ3512

M_A_DQ3612

M_A_DQ3712

M_A_DQ3812

M_A_DQ3912

M_A_DQ4012

M_A_DQ4112

M_A_DQ4212

M_A_DQ4312

M_A_DQ4412

M_A_DQ4512

M_A_DQ4612

M_A_DQ4712

M_A_DQ4812

M_A_DQ4912

M_A_DQ5012

M_A_DQ5112

M_A_DQ5212

M_A_DQ5312

M_A_DQ5412

M_A_DQ5512

M_A_DQ5612

M_A_DQ5712

M_A_DQ5812

M_A_DQ5912

M_A_DQ6012

M_A_DQ6112

M_A_DQ6212

M_A_DQ6312

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

CPU1B

AL71

DDR0_DQ[0]

AL68

DDR0_DQ[1]

AN68

DDR0_DQ[2]

AN69

DDR0_DQ[3]

AL70

DDR0_DQ[4]

AL69

DDR0_DQ[5]

AN70

DDR0_DQ[6]

AN71

DDR0_DQ[7]

AR70

DDR0_DQ[8]

AR68

DDR0_DQ[9]

AU71

DDR0_DQ[10]

AU68

DDR0_DQ[11]

AR71

DDR0_DQ[12]

AR69

DDR0_DQ[13]

AU70

DDR0_DQ[14]

AU69

DDR0_DQ[15]

AF65

DDR1_DQ[0]/DDR0_DQ[8]

AF64

DDR1_DQ[1]/DDR0_DQ[9]

AK65

DDR1_DQ[2]/DDR0_DQ[10]

AK64

DDR1_DQ[3]/DDR0_DQ[11]

AF66

DDR1_DQ[4]/DDR0_DQ[12]

AF67

DDR1_DQ[5]/DDR0_DQ[13]

AK67

DDR1_DQ[6]/DDR0_DQ[14]

AK66

DDR1_DQ[7]/DDR0_DQ[15]

AF70

DDR1_DQ[8]/DDR0_DQ[24]

AF68

DDR1_DQ[9]/DDR0_DQ[25]

AH71

DDR1_DQ[10]/DDR0_DQ[26]

AH68

DDR1_DQ[11]/DDR0_DQ[27]

AF71

DDR1_DQ[12]/DDR0_DQ[28]

AF69

DDR1_DQ[13]/DDR0_DQ[29]

AH70

DDR1_DQ[14]/DDR0_DQ[30]

AH69

DDR1_DQ[15]/DDR0_DQ[31]

BB65

DDR0_DQ[16]/DDR0_DQ[32]

AW65

DDR0_DQ[17]/DDR0_DQ[33]

AW63

DDR0_DQ[18]/DDR0_DQ[34]

AY63

DDR0_DQ[19]/DDR0_DQ[35]

BA65

DDR0_DQ[20]/DDR0_DQ[36]

AY65

DDR0_DQ[21]/DDR0_DQ[37]

BA63

DDR0_DQ[22]/DDR0_DQ[38]

BB63

DDR0_DQ[23]/DDR0_DQ[39]

BA61

DDR0_DQ[24]/DDR0_DQ[40]

AW61

DDR0_DQ[25]/DDR0_DQ[41]

BB59

DDR0_DQ[26]/DDR0_DQ[42]

AW59

DDR0_DQ[27]/DDR0_DQ[43]

BB61

DDR0_DQ[28]/DDR0_DQ[44]

AY61

DDR0_DQ[29]/DDR0_DQ[45]

BA59

DDR0_DQ[30]/DDR0_DQ[46]

AY59

DDR0_DQ[31]/DDR0_DQ[47]

AT66

DDR1_DQ[16]/DDR0_DQ[48]

AU66

DDR1_DQ[17]/DDR0_DQ[49]

AP65

DDR1_DQ[18]/DDR0_DQ[50]

AN65

DDR1_DQ[19]/DDR0_DQ[51]

AN66

DDR1_DQ[20]/DDR0_DQ[52]

AP66

DDR1_DQ[21]/DDR0_DQ[53]

AT65

DDR1_DQ[22]/DDR0_DQ[54]

AU65

DDR1_DQ[23]/DDR0_DQ[55]

AT61

DDR1_DQ[24]/DDR0_DQ[56]

AU61

DDR1_DQ[25]/DDR0_DQ[57]

AP60

DDR1_DQ[26]/DDR0_DQ[58]

AN60

DDR1_DQ[27]/DDR0_DQ[59]

AN61

DDR1_DQ[28]/DDR0_DQ[60]

AP61

DDR1_DQ[29]/DDR0_DQ[61]

AT60

DDR1_DQ[30]/DDR0_DQ[62]

AU60

DDR1_DQ[31]/DDR0_DQ[63]

SKYLAKE-U-GP

SKYLAKE_ULT

DDR0_DQ[16]

DDR0_DQ[17]

DDR0_DQ[18]

DDR0_DQ[19]

DDR0_DQ[20]

DDR0_DQ[21]

DDR0_DQ[22]

DDR0_DQ[23]

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

DDR CH - A

071.SKYLA.000U

2 OF 20

DDR0_CKN[0]

DDR0_CKP[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_ODT[0]

DDR0_ODT[1]

DDR0_MA[3]

DDR0_MA[4]

DDR0_DQSN[0]

DDR0_DQSP[0]

DDR0_DQSN[1]

DDR0_DQSP[1]

DDR1_DQSN[0]/DDR0_DQ[2]

DDR1_DQSP[0]/DDR0_DQ[2]

DDR1_DQSN[1]/DDR0_DQ[3]

DDR1_DQSP[1]/DDR0_DQ[3]

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR0_ALERT#

DDR0_PAR

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

DDR_VTT_CNTL

AU53

AT53

AU55

AT55

BA56

BB56

AW56

AY56

AU45

AU43

AT45

AT43

BA51

BB54

BA52

AY52

AW52

AY55

AW54

BA54

BA55

AY54

AU46

AU48

AT46

AU50

AU52

AY51

AT48

AT50

BB50

AY50

BA50

BB52

AM70

AM69

AT69

AT70

AH66

AH65

AG69

AG70

BA64

AY64

AY60

BA60

AR66

AR65

AR61

AR60

AW50

AT52

AY67

AY68

BA67

AW67

M_A_A5

M_A_A9

M_A_A6

M_A_A8

M_A_A7

M_A_A12

M_A_A11

M_A_A13

M_A_A15

M_A_A14

M_A_A16

M_A_A2

M_A_A10

M_A_A1

M_A_A0

M_A_A3

M_A_A4

M_A_DQS_DN0

M_A_DQS_DP0

M_A_DQS_DN1

M_A_DQS_DP1

M_A_DQS_DN2

M_A_DQS_DP2

M_A_DQS_DN3

M_A_DQS_DP3

M_A_DQS_DN4

M_A_DQS_DP4

M_A_DQS_DN5

M_A_DQS_DP5

M_A_DQS_DN6

M_A_DQS_DP6

M_A_DQS_DN7

M_A_DQS_DP7

SM_PGCNTL

M_A_CLK#0 12

M_A_CLK0 12

M_A_CKE0 12

M_A_CS#0 12

M_A_DIMA_ODT0 12

M_A_A5 12

M_A_A9 12

M_A_A6 12

M_A_A8 12

M_A_A7 12

M_A_BG0 12

M_A_A12 12

M_A_A11 12

M_A_ACT_N 12

M_A_BG1 12

M_A_A13 12

M_A_A15 12

M_A_A14 12

M_A_A16 12

M_A_BA0 12

M_A_A2 12

M_A_BA1 12

M_A_A10 12

M_A_A1 12

M_A_A0 12

M_A_A3 12

M_A_A4 12

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_ALERT_N 12

M_A_PARITY 12

V_SM_VREF_CNTA 12

V_SM_VREF_CNTB 13

CPU1C

M_B_DQ013

M_B_DQ113

M_B_DQ213

M_B_DQ313

M_B_DQ413

M_B_DQ513

M_B_DQ613

M_B_DQ713

M_B_DQ813

M_B_DQ913

M_B_DQ1013

M_B_DQ1113

M_B_DQ1213

M_B_DQ1313

M_B_DQ1413

M_B_DQ1513

M_B_DQ1613

M_B_DQ1713

M_B_DQ1813

M_B_DQ1913

M_B_DQ2013

M_B_DQ2113

M_B_DQ2213

M_B_DQ2313

M_B_DQ2413

M_B_DQ2513

M_B_DQ2613

M_B_DQ2713

M_B_DQ2813

M_B_DQ2913

M_B_DQ3013

M_B_DQ3113

M_B_DQ3213

M_B_DQ3313

M_B_DQ3413

M_B_DQ3513

M_B_DQ3613

M_B_DQ3713

M_B_DQ3813

M_B_DQ3913

M_B_DQ4013

M_B_DQ4113

M_B_DQ4213

M_B_DQ4313

M_B_DQ4413

M_B_DQ4513

M_B_DQ4613

M_B_DQ4713

M_B_DQ4813

M_B_DQ4913

M_B_DQ5013

M_B_DQ5113

M_B_DQ5213

M_B_DQ5313

M_B_DQ5413

M_B_DQ5513

M_B_DQ5613

M_B_DQ5713

M_B_DQ5813

M_B_DQ5913

M_B_DQ6013

M_B_DQ6113

M_B_DQ6213

M_B_DQ6313

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

AY39

DDR0_DQ[32]/DDR1_DQ[0]

AW39

DDR0_DQ[33]/DDR1_DQ[1]

AY37

DDR0_DQ[34]/DDR1_DQ[2]

AW37

DDR0_DQ[35]/DDR1_DQ[3]

BB39

DDR0_DQ[36]/DDR1_DQ[4]

BA39

DDR0_DQ[37]/DDR1_DQ[5]

BA37

DDR0_DQ[38]/DDR1_DQ[6]

BB37

DDR0_DQ[39]/DDR1_DQ[7]

AY35

DDR0_DQ[40]/DDR1_DQ[8]

AW35

DDR0_DQ[41]/DDR1_DQ[9]

AY33

DDR0_DQ[42]/DDR1_DQ[10]

AW33

DDR0_DQ[43]/DDR1_DQ[11]

BB35

DDR0_DQ[44]/DDR1_DQ[12]

BA35

DDR0_DQ[45]/DDR1_DQ[13]

BA33

DDR0_DQ[46]/DDR1_DQ[14]

BB33

DDR0_DQ[47]/DDR1_DQ[15]

AU40

DDR1_DQ[32]/DDR1_DQ[16]

AT40

DDR1_DQ[33]/DDR1_DQ[17]

AT37

DDR1_DQ[34]/DDR1_DQ[18]

AU37

DDR1_DQ[35]/DDR1_DQ[19]

AR40

DDR1_DQ[36]/DDR1_DQ[20]

AP40

DDR1_DQ[37]/DDR1_DQ[21]

AP37

DDR1_DQ[38]/DDR1_DQ[22]

AR37

DDR1_DQ[39]/DDR1_DQ[23]

AT33

DDR1_DQ[40]/DDR1_DQ[24]

AU33

DDR1_DQ[41]/DDR1_DQ[25]

AU30

DDR1_DQ[42]/DDR1_DQ[26]

AT30

DDR1_DQ[43]/DDR1_DQ[27]

AR33

DDR1_DQ[44]/DDR1_DQ[28]

AP33

DDR1_DQ[45]/DDR1_DQ[29]

AR30

DDR1_DQ[46]/DDR1_DQ[30]

AP30

DDR1_DQ[47]/DDR1_DQ[31]

AY31

DDR0_DQ[48]/DDR1_DQ[32]

AW31

DDR0_DQ[49]/DDR1_DQ[33]

AY29

DDR0_DQ[50]/DDR1_DQ[34]

AW29

DDR0_DQ[51]/DDR1_DQ[35]

BB31

DDR0_DQ[52]/DDR1_DQ[36]

BA31

DDR0_DQ[53]/DDR1_DQ[37]

BA29

DDR0_DQ[54]/DDR1_DQ[38]

BB29

DDR0_DQ[55]/DDR1_DQ[39]

AY27

DDR0_DQ[56]/DDR1_DQ[40]

AW27

DDR0_DQ[57]/DDR1_DQ[41]

AY25

DDR0_DQ[58]/DDR1_DQ[42]

AW25

DDR0_DQ[59]/DDR1_DQ[43]

BB27

DDR0_DQ[60]/DDR1_DQ[44]

BA27

DDR0_DQ[61]/DDR1_DQ[45]

BA25

DDR0_DQ[62]/DDR1_DQ[46]

BB25

DDR0_DQ[63]/DDR1_DQ[47]

AU27

DDR1_DQ[48]

AT27

DDR1_DQ[49]

AT25

DDR1_DQ[50]

AU25

DDR1_DQ[51]

AP27

DDR1_DQ[52]

AN27

DDR1_DQ[53]

AN25

DDR1_DQ[54]

AP25

DDR1_DQ[55]

AT22

DDR1_DQ[56]

AU22

DDR1_DQ[57]

AU21

DDR1_DQ[58]

AT21

DDR1_DQ[59]

AN22

DDR1_DQ[60]

AP22

DDR1_DQ[61]

AP21

DDR1_DQ[62]

AN21

DDR1_DQ[63]

SKYLAKE-U-GP

SKYLAKE_ULT

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT#

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1_DQSP[5]/DDR1_DQSP[3]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

DDR0_DQSP[7]/DDR1_DQSP[5]

DDR CH - B

071.SKYLA.000U

Design Guideline:

1D2V_S3 3D3V_S0

12

G

R506

220KR2F-GP

SM_RCOMP keep routing length less than 500 mils.

3 OF 20

DDR1_CKN[0]

DDR1_CKN[1]

DDR1_CKP[0]

DDR1_CKP[1]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_ODT[0]

DDR1_ODT[1]

DDR1_MA[3]

DDR1_MA[4]

DDR1_DQSN[6]

DDR1_DQSP[6]

DDR1_DQSN[7]

DDR1_DQSP[7]

DDR1_ALERT#

DDR1_PAR

DRAM_RESET#

DDR_RCOMP[0]

DDR_RCOMP[1]

DDR_RCOMP[2]

AN45

AN46

AP45

AP46

AN56

AP55

AN55

AP53

BB42

AY42

BA42

AW42

AY48

AP50

BA48

BB48

AP48

AP52

AN50

AN48

AN53

AN52

BA43

AY43

AY44

AW44

BB44

AY47

BA44

AW46

AY46

BA46

BB46

BA47

BA38

AY38

AY34

BA34

AT38

AR38

AT32

AR32

BA30

AY30

AY26

BA26

AR25

AR27

AR22

AR21

AN43

AP43

AT13

AR18

AT18

AU18

M_B_A5

M_B_A9

M_B_A6

M_B_A8

M_B_A7

M_B_A12

M_B_A11

M_B_ACT_N

M_B_A13

M_B_A15

M_B_A14

M_B_A16

M_B_A2

M_B_A10

M_B_A1

M_B_A0

M_B_A3

M_B_A4

M_B_DQS_DN0

M_B_DQS_DP0

M_B_DQS_DN1

M_B_DQS_DP1

M_B_DQS_DN2

M_B_DQS_DP2

M_B_DQS_DN3

M_B_DQS_DP3

M_B_DQS_DN4

M_B_DQS_DP4

M_B_DQS_DN5

M_B_DQS_DP5

M_B_DQS_DN6

M_B_DQS_DP6

M_B_DQS_DN7

M_B_DQS_DP7

SM_DRAMRST#

SM_RCOMP_0

SM_RCOMP_0

SM_RCOMP_1

#543016

SM_RCOMP_2

M_B_CLK#0 13

M_B_CLK0 13

M_B_CKE0 13

M_B_CS#0 13

M_B_DIMB_ODT0 13

M_B_A5 13

M_B_A9 13

M_B_A6 13

M_B_A8 13

M_B_A7 13

M_B_BG0 13

M_B_A12 13

M_B_A11 13

M_B_ACT_N 13

M_B_BG1 13

M_B_A13 13

M_B_A15 13

M_B_A14 13

M_B_A16 13

M_B_BA0 13

M_B_A2 13

M_B_BA1 13

M_B_A10 13

M_B_A1 13

M_B_A0 13

M_B_A3 13

M_B_A4 13

M_B_ALERT_N 13

M_B_PARITY 13

R501

1 2

1 2

1 2

1 2

121R2F-GP

DDP

200R2F-L-GP

R507

SDP

R502 80D6R2F-L-GP

R503 100R2F-L1-GP-U

DDP R501:121

SDP R507:200

2016/11/28

Layout Note:

1D2V_S3

12

R505

470R2F-GP

1 2

R504

0R0402-PAD

DDR4_DRAMRST# 12,13

12

C501

SCD1U25V2KX-1-DL-GP

SM_PGCNTL

Q501

DMN5L06K-7-GP

DS

SM_PGCNTL_R 51

2015/11/18 Modify

M_A_DQS_DN0

M_A_DQS_DN1

M_A_DQS_DN2

M_A_DQS_DN3

M_A_DQS_DN4

M_A_DQS_DN5

M_A_DQS_DN6

M_A_DQS_DN7

M_A_DQS_DP0

M_A_DQS_DP1

M_A_DQS_DP2

A A

5

4

M_A_DQS_DP3

M_A_DQS_DP4

M_A_DQS_DP5

M_A_DQS_DP6

M_A_DQS_DP7

M_A_DQS_DN[7:0] 12

M_A_DQS_DP[7:0] 12

3

M_B_DQS_DN0

M_B_DQS_DN1

M_B_DQS_DN2

M_B_DQS_DN3

M_B_DQS_DN4

M_B_DQS_DN5

M_B_DQS_DN6

M_B_DQS_DN7

M_B_DQS_DP0

M_B_DQS_DP1

M_B_DQS_DP2

M_B_DQS_DP3

M_B_DQS_DP4

M_B_DQS_DP5

M_B_DQS_DP6

M_B_DQS_DP7

M_B_DQS_DN[7:0] 13

M_B_DQS_DP[7:0] 13

2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

CPU_(DDR)

CPU_(DDR)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A2

A2

A2

Date: Sheet of

Date: Sheet of

Date: Sheet of

CPU_(DDR)

KyloRen 13"

KyloRen 13"

KyloRen 13"

1

5 106Thursday, June 29, 2017

5 106Thursday, June 29, 2017

5 106Thursday, June 29, 2017

A00

A00

A00

SSID = CPU

5

4

3

2

1

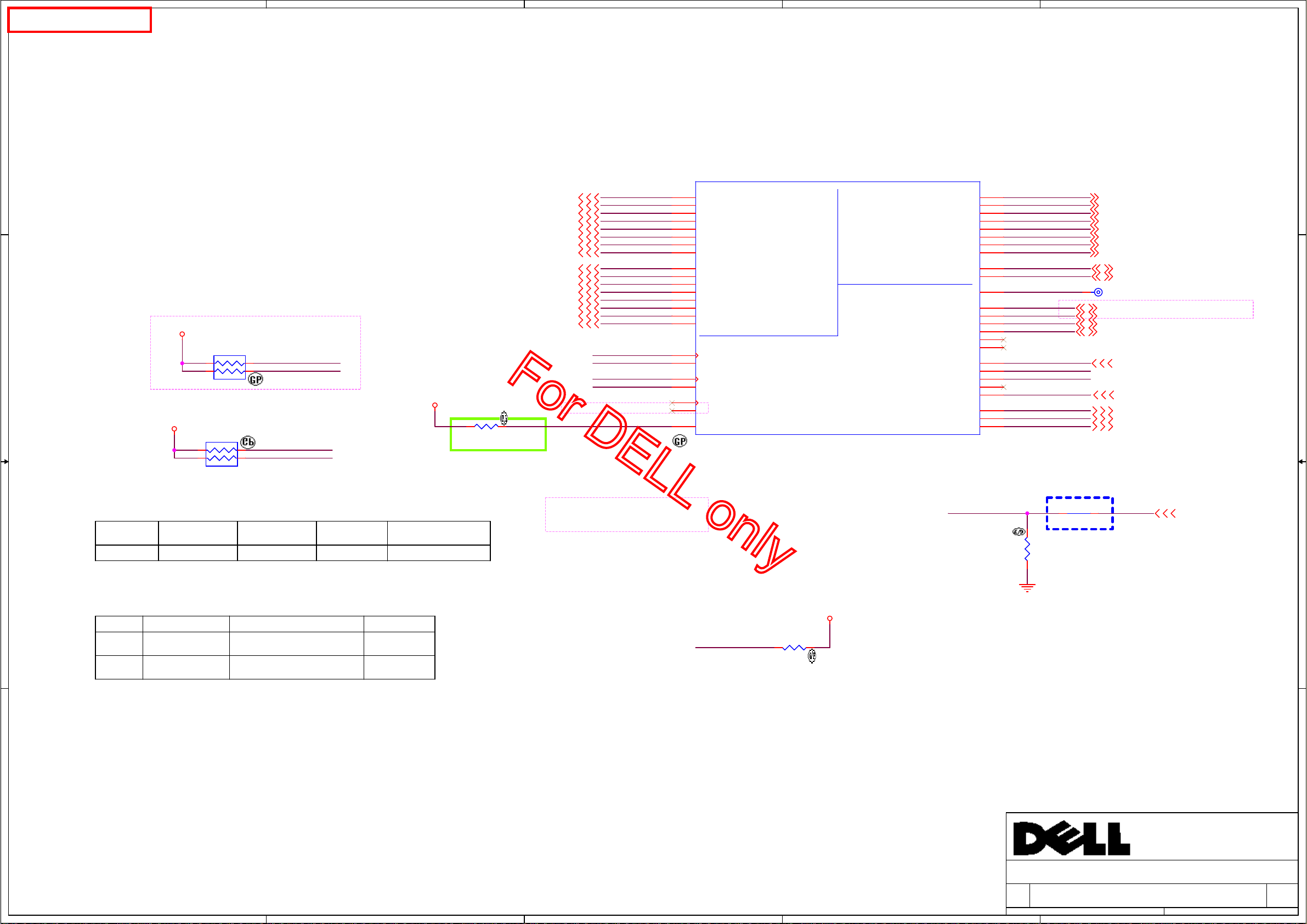

CPU1S

D D

C C

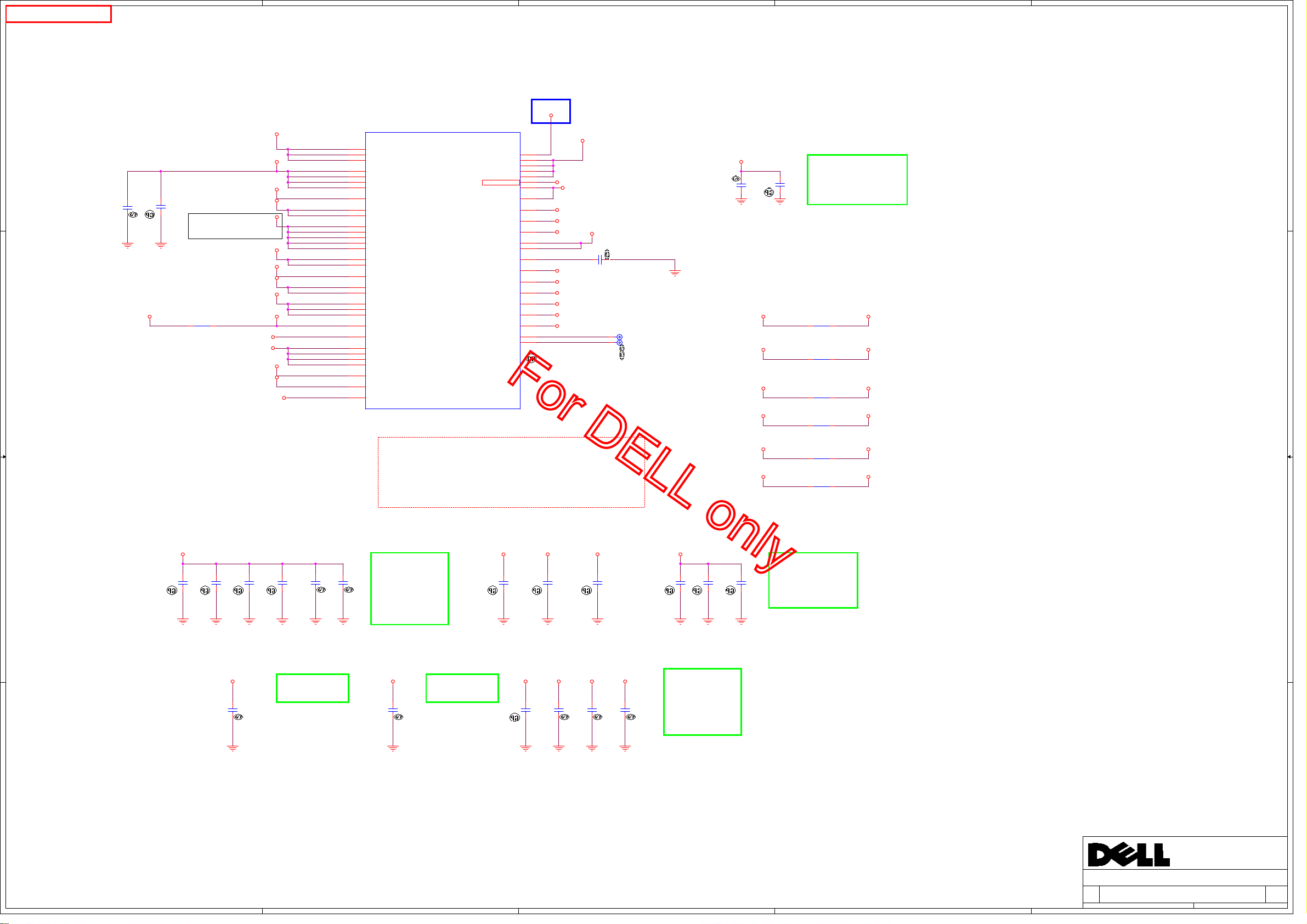

PCH strap pin:

CFG3

DY

CFG[19:0]99

12

R604

1KR2J-1-GP

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

CFG_RCOMP

12

R60149D9R2F-GP

ITP_PMODE99

RSVD_TP_BA70

1

1

TP601TPAD14-OP-GP

TP602TPAD14-OP-GP

RSVD_F65

1

RSVD_G65

1

TP612TPAD14-OP-GP

TP613TPAD14-OP-GP

E68

B67

D65

D67

E70

C68

D68

C67

F71

G69

F70

G68

H70

G71

H69

G70

E63

F63

E66

F66

E60

AY2

AY1

K46

K45

AL25

AL27

C71

B70

F60

A52

BA70

BA68

F65

G65

F61

E61

E8

D1

D3

J71

J68

CFG[0]

CFG[1]

CFG[2]

CFG[3]

CFG[4]

CFG[5]

CFG[6]

CFG[7]

CFG[8]

CFG[9]

CFG[10]

CFG[11]

CFG[12]

CFG[13]

CFG[14]

CFG[15]

CFG[16]

CFG[17]

CFG[18]

CFG[19]

CFG_RCOMP

ITP_PMODE

RSVD_AY2

RSVD_AY1

RSVD_D1

RSVD_D3

RSVD_K46

RSVD_K45

RSVD_AL25

RSVD_AL27

RSVD_C71

RSVD_B70

RSVD_F60

RSVD_A52

RSVD_TP_BA70

RSVD_TP_BA68

RSVD_J71

RSVD_J68

VSS_F65

VSS_G65

RSVD_F61

RSVD_E61

SKYLAKE-U-GP

071.SKYLA.000U

[BDW Only]PHYSICAL_DEBUG_ENABLED (DFX PRIVACY)

CFG[3]

0 : ENABLED

SET DFX ENABLED BIT IN DEBUG INTERFACE MSR

RESERVED SIGNALS-1

SKYLAKE_ULT

RSVD_TP_AW71

RSVD_TP_AW70

19 OF 20

RSVD_TP_BB68

RSVD_TP_BB69

RSVD_TP_AK13

RSVD_TP_AK12

RSVD_BB2

RSVD_BA3

TP5

TP6

RSVD_D5

RSVD_D4

RSVD_B2

RSVD_C2

RSVD_B3

RSVD_A3

RSVD_AW1

RSVD_E1

RSVD_E2

RSVD_BA4

RSVD_BB4

RSVD_A4

RSVD_C4

TP4

RSVD_A69

RSVD_B69

RSVD_AY3

RSVD_D71

RSVD_C70

RSVD_C54

RSVD_D54

TP1

TP2

VSS_AY71

ZVM#

RSVD_AW71

RSVD_AW70

MSM#

PROC_SELECT#

BB68

BB69

AK13

AK12

BB2

BA3

AU5

AT5

D5

D4

B2

C2

B3

A3

AW1

E1

E2

BA4

BB4

A4

C4

BB5

A69

B69

AY3

D71

C70

C54

D54

AY4

BB3

AY71

AR56

AW71

AW70

AP56

C64

RSVD_TP_BB68

RSVD_TP_BB69

RSVD_TP_AK13

RSVD_TP_AK12

TP5_AU5

TP6_AT5

TP4_BB5

TP1_AY4

TP2_BB3RSVD_TP_BA68

VSS_AY71

ZVM#

RSVD_TP_AW71

RSVD_TP_AW70

MSM#

PROC_SELECT#

1

1

1

1

1

1

1

1

1

1 2

R602 0R0402-PAD

1

1

1

1

1 2

R603

100KR2J-1-GP

2016/01/11 modify

TP603 TPAD14-OP-GP

TP604 TPAD14-OP-GP

TP605 TPAD14-OP-GP

TP606 TPAD14-OP-GP

TP607 TPAD14-OP-GP

TP608 TPAD14-OP-GP

TP609 TPAD14-OP-GP

TP610 TPAD14-OP-GP

TP611 TPAD14-OP-GP

TP618

TPAD14-OP-GP

TP614 TPAD14-OP-GP

TP615 TPAD14-OP-GP

TP617 TPAD14-OP-GP

DY

#54469 CRB.

+VCCST_CPU

1 : DISABLED

CFG4

B B

12

R605

1KR2J-1-GP

(#543016)

DISPLAY PORT PRESENCE STRAP

CFG[4]

0 : ENABLED

An external Display Port device is connected to the Embedded Display Port.

1 : DISABLED (Default)

No Physical Display Port attached to Embedded DisplayPort*. No connect for disable.

SKL(#543016):

Processor strap CFG[4] should be pulled low to enable embedded DisplayPort*

A A

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

CPU_(RESERVED)

CPU_(RESERVED)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A2

A2

A2

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

CPU_(RESERVED)

KyloRen 13"

KyloRen 13"

KyloRen 13"

1

6 106Thursday, June 29, 2017

6 106Thursday, June 29, 2017

6 106Thursday, June 29, 2017

A00

A00

A00

SSID = CPU

5

4

3

2

1

A48

A53

A58

A62

A66

AA63

AA64

AA66

AA67

AA69

AA70

AA71

AC64

AC65

AC66

AC67

AC68

AC69

AC70

AC71

J43

J45

J46

J48

J50

J52

J53

J55

J56

J58

J60

K48

K50

K52

K53

K55

K56

K58

K60

L62

L63

L64

L65

L66

L67

L68

L69

L70

L71

M62

N63

N64

N66

N67

N69

J70

J69

U42

R736

1 2

D0002R5J-GP- U

U42

R743

1 2

D0002R5J-GP- U

CPU1M

CPU POWER 2 OF 4

VCCGT

SKYLAKE_ULT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT_SENSE

VSSGT_SENSE

SKYLAKE-U-GP

071.SKYLA.000U

13 OF 20

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGTX_AK42

VCCGTX_AK43

VCCGTX_AK45

VCCGTX_AK46

VCCGTX_AK48

VCCGTX_AK50

VCCGTX_AK52

VCCGTX_AK53

VCCGTX_AK55

VCCGTX_AK56

VCCGTX_AK58

VCCGTX_AK60

VCCGTX_AK70

VCCGTX_AL43

VCCGTX_AL46

VCCGTX_AL50

VCCGTX_AL53

VCCGTX_AL56

VCCGTX_AL60

VCCGTX_AM48

VCCGTX_AM50

VCCGTX_AM52

VCCGTX_AM53

VCCGTX_AM56

VCCGTX_AM58

VCCGTX_AU58

VCCGTX_AU63

VCCGTX_BB57

VCCGTX_BB66

VCCGTX_SENSE

VSSGTX_SENSE

U22

R742

1 2

D0002R5J-GP- U

+VCCGT

N70

N71

R63

R64

R65

R66

R67

R68

R69

R70

R71

T62

U65

U68

U71

W63

W64

W65

W66

W67

W68

W69

W70

W71

Y62

AK42

AK43

AK45

AK46

AK48

AK50

AK52

AK53

AK55

AK56

AK58

AK60

AK70

AL43

AL46

AL50

AL53

AL56

AL60

AM48

AM50

AM52

AM53

AM56

AM58

AU58

For U42 only

AU63

BB57

BB66

AK62

AL61

GTX_CORE

GTX_CORE

GTX_CORE

SC10U6D3V3MX- DL-GP

#544669 CRB.

+VDDQ_CPU _CLK1D2V_S3

R705

1 2

0R0805-PAD

2016/02/16 modify

2017/01/18

DY

2017/06/28

VCC_CORE

+VCCGT

1D2V_S3

DY

12

12

12

12

12

12

12

12

12

C719

SC1U10V2KX-1D LGP

+VDDQ_CPU _CLK

C715

+VCCST_CP U

C716SC1U10V2KX-1D LGP

+VCCSTG

C717SC1U10V2KX-1D LGP

1D2V_S3

C718SC1U10V2KX-1D LGP

+VCCSFR

C720

SCD1U25V2KX-1-DL-GP

1 2

R719

100R2F-L1-GP- U

R720

100R2F-L1-GP- U

R721

100R2F-L1-GP- U

R722

100R2F-L1-GP- U

CPU1N

CPU POWER 3 OF 4

AU23

VDDQ_AU23

AU28

VDDQ_AU28

AU35

VDDQ_AU35

AU42

VDDQ_AU42

BB23

VDDQ_BB23

BB32

VDDQ_BB32

BB41

VDDQ_BB41

BB47

VDDQ_BB47

BB51

VDDQ_BB51

AM40

VDDQC

A18

0.04 A

VCCST

A22

VCCSTG_A22

AL23

VCCPLL_OC

K20

VCCPLL_K20

K21

VCCPLL_K21

0.12 A

12

C721

SC1U10V2KX-1DLGP

SKYLAKE-U-GP

071.SKYLA.000U

VCC_SENSE 7,46

VSS_SENSE 7,46

Layout Note:

1. Place close to CPU

2. VCC_SENSE/ VSS_SENSE

impedance=50 ohm

3. Length match<25mil

VCCGT_SEN SE 7,46

VSSGT_SENSE 7,46

SKYLAKE_ULT

14 OF 20

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCIO_SENSE

VSSIO_SENSE

VSSSA_SENSE

VCCSA_SENSE

AK28

AK30

AL30

AL42

AM28

AM30

AM42

AK23

AK25

G23

G25

G27

G28

J22

J23

J27

K23

K25

K27

K28

K30

AM23

AM22

H21

H20

VCCSA_SENS E

VSSSA_SENSE

+VCCIO

+VCCIO(ICCMAX.=2.73A

+VCCSA

+VCCSA

12

R735

100R2F-L1-GP- U

12

R734

100R2F-L1-GP- U

VSSSA_SENSE 46

VCCSA_SENS E 46

AM32

AM33

AM35

AM37

AM38

AK33

AK35

AK37

AK38

AK40

AL33

AL37

AL40

AK32

AB62

AC63

AE63

AE62

AG62

AL63

AJ62

A30

A34

A39

A44

G30

K32

P62

V62

H63

G61

CPU1L

VCC_A30

VCC_A34

VCC_A39

VCC_A44

VCC_AK33

VCC_AK35

VCC_AK37

VCC_AK38

VCC_AK40

VCC_AL33

VCC_AL37

VCC_AL40

VCC_AM32

VCC_AM33

VCC_AM35

VCC_AM37

VCC_AM38

VCC_G30

RSVD_K32

VCCG0

RSVD_AK32

VCCG1

VCCOPC_AB62

VCCOPC_P62

VCCOPC_V62

VCC_OPC_1P8_H63

VCC_OPC_1P8_G61

VCCOPC_SENSE

VSSOPC_SENSE

VCCEOPIO

VCCEOPIO

VCCEOPIO_SENSE

VSSEOPIO_SENSE

SKYLAKE-U-GP

CPU POWER 1 OF 4

SKYLAKE_ULT

VCC_CORE VCC_CORE

D D

1

+VCCCOR EG0

TP701TPAD14-OP-GP

1

+VCCCOR EG1

TP707TPAD14-OP-GP

3A

+V_EDRAM_VR

140mA

+V1.8S_EDRAM

SEN_EDRAM

3A

+V_EOPIO_VR

SEN_EOPIO

12 OF 20

VCC_G32

VCC_G33

VCC_G35

VCC_G37

VCC_G38

VCC_G40

VCC_G42

VCC_J30

VCC_J33

VCC_J37

VCC_J40

VCC_K33

VCC_K35

VCC_K37

VCC_K38

VCC_K40

VCC_K42

VCC_K43

VCC_SENSE

VSS_SENSE

VIDALERT#

VIDSCK

VIDSOUT

VCCSTG_G20

G32

G33

G35

G37

G38

G40

G42

J30

J33

J37

J40

K33

K35

K37

K38

K40

K42

K43

E32

E33

B63

A63

D64

G20

H_CPU_SVIDALR T#

H_CPU_SVIDC LK

H_CPU_SVIDD AT

+VCCFUSE PRG

VCC_SENSE 7,46

VSS_SENSE 7,46

1 2

R703

0R0603-PAD

+VCCGT

1 2

R738

DY

0R2J-2-GP

+VCCSTG

U22_POWER _K52

For U22 & U42

GT_CORE

+VCCGT

GT_CORE

+VCCGT

GT_CORE

+VCCGT

071.SKYLA.000U

VCCGT_SEN SE7,46

VSSGT_SENSE7,46

VCC_CORE GT_CORE +VCCGT

C C

VCC_CORE GTX_CORE

Layout Note:

SVID_543016:

B B

CLOSE TO CPU

H_CPU_SVIDD AT

+VCCST_CP U

12

R726

100R2F-L1-GP- U

SVID CLOCK

H_CPU_SVIDC LK

A A

SVID DATA

H_CPU_SVIDALR T#

5

R728

220R2J-L2-GP

4

The total Length of Data and Clock (from CPU to each VR) must be equal (±0.1 inch).

Route the Alert signal between the Clock and the Data signals.

#544669

1 2

12

R709

0R0402-PAD

1 2

R732

0R0402-PAD

+VCCST_CP U

12

R727

56R2J-4-GP

+VCCST_CP U

12

DY

#544669

CLOSE TO CPU

R723

54D9R2F-L1-G P

VR_SVID_ALERT# 46

VR_SVID_DATA 46

#544669

CLOSE TO VR

VR_SVID_CLK 46

<Core Desig n>

<Core Desig n>

<Core Desig n>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin T ai Wu Rd ., Hsichih,

21F, 88, Sec.1, Hsin T ai Wu Rd ., Hsichih,

21F, 88, Sec.1, Hsin T ai Wu Rd ., Hsichih,

Taipei Hsie n 221, Taiwan, R.O. C.

Taipei Hsie n 221, Taiwan, R.O. C.

Title

Title

Title

Size Document Num ber Rev

Size Document Num ber Rev

Size Document Num ber Rev

A1

A1

A1

Thursday, June 29, 2017

Thursday, June 29, 2017

Thursday, June 29, 2017

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet of

1

Taipei Hsie n 221, Taiwan, R.O. C.

CPU(VCC_CORE)

CPU(VCC_CORE)

CPU(VCC_CORE)

KyloRen 13"

KyloRen 13"

KyloRen 13"

7 106

7 106

7 106

A00

A00

A00

5

4

3

2

1

SSID = CPU

D D

CPU1A

DP_DATA0_N57

DP_DATA0_P57

DP_DATA1_N57

DP_DATA1_P57

DP to HDMI2.0

DP for Type-C Mux

2016/11/01modify

3D3V_S0

C C

3D3V_S0

SRN2K2J-1-GP

1

2 3

RN801

RN803

2 3

1

SRN2K2J-1-GP

CPU_DP1_CTRL_DATA

4

CPU_DP1_CTRL_CLK

CPU_DP2_CTRL_DATA

CPU_DP2_CTRL_CLK

4

DP to HDMI2.0 DP to HDMI2.0

+VCCIO

R801

1 2

24D9R2F-L-GP

DP_DATA2_N57

DP_DATA2_P57

DP_DATA3_N57

DP_DATA3_P57

PCH_DPC_N038

PCH_DPC_P038

PCH_DPC_N138

PCH_DPC_P138

PCH_DPC_N238

PCH_DPC_P238

PCH_DPC_N338

PCH_DPC_P338

CPU_DP1_CTRL_CLK

CPU_DP1_CTRL_DATA

CPU_DP2_CTRL_CLK SIO_EXT_SMI#

CPU_DP2_CTRL_DATA

2016/11/07

EDP_COMP

E55

DDI1_TXN[0]

F55

DDI1_TXP[0]

E58

DDI1_TXN[1]

F58

DDI1_TXP[1]

F53

DDI1_TXN[2]

G53

DDI1_TXP[2]

F56

DDI1_TXN[3]

G56

DDI1_TXP[3]

C50

DDI2_TXN[0]

D50

DDI2_TXP[0]

C52

DDI2_TXN[1]

D52

DDI2_TXP[1]

A50

DDI2_TXN[2]

B50

DDI2_TXP[2]

D51

DDI2_TXN[3]

C51

DDI2_TXP[3]

L13

GPP_E18/DDPB_CTRLCLK

L12

GPP_E19/DDPB_CTRLDATA

N7

GPP_E20/DDPC_CTRLCLK

N8

GPP_E21/DDPC_CTRLDATA

N11

GPP_E22/DDPD_CTRLCLK

N12

GPP_E23/DDPD_CTRLDATA

E52

EDP_RCOMP

SKYLAKE-U-GP

071.SKYLA.000U

(#543016) The Skylake U/Y processor supports only two DDI ports - Port 1 and Port 2.

SKYLAKE_ULT

DDI

DISPLAY SIDEBANDS

EDP

GPP_E13/DDPB_HPD0

GPP_E14/DDPC_HPD1

GPP_E15/DDPD_HPD2

GPP_E16/DDPE_HPD3

GPP_E17/EDP_HPD

1 OF 20

EDP_TXN[0]

EDP_TXP[0]

EDP_TXN[1]

EDP_TXP[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXN

EDP_AUXP

EDP_DISP_UTIL

DDI1_AUXN

DDI1_AUXP

DDI2_AUXN

DDI2_AUXP

DDI3_AUXN

DDI3_AUXP

EDP_BKLTEN

EDP_BKLTCTL

EDP_VDDEN

C47

C46

D46

C45

A45

B45

A47

B47

E45

F45

B52

G50

F50

E48

F48

G46

F46

L9

L7

L6

N9

L10

R12

R11

U13

EDP_DISP_UTIL

CPU_DP2_HPD

EDP_TX0_DN 55

EDP_TX0_DP 55

EDP_TX1_DN 55

EDP_TX1_DP 55

EDP_TX2_DN 55

EDP_TX2_DP 55

EDP_TX3_DN 55

EDP_TX3_DP 55

EDP_AUX_DN 55

EDP_AUX_DP 55

1

TP801 TPAD14-OP-GP

HDMI_AUXN 57

HDMI_AUXP 57

DPB_AUXN 38

DPB_AUXP 38

CPU_DP1_HPD 57

EDP_HPD 55

L_BKLT_CTRL 55

EDP_VDD_EN 55

2016/11/01modify

for HDMI2.0

for Type-C Mux

L_BKLT_EN 24

2016/11/07

(#543016) eDP_RCOMP Guideline

Signal Trace

Width

eDP_RCOMP 20 mils 25 mils 24.9 Ω ±1%

B B

Isolation

Spacing

Resistor

Value

Length

Max = 100 mils

(#543016) DDI Disabling and Termination Guidelines

Touch_panel _Resert Remove

3D3V_S0

CPU_DP2_HPD

TypeC

1 2

R804

1 2

0R0402-PAD

2016/12/28

R803

100KR2J-1-GP

CPU_DP_HPD_R 37,38

DP for Type-C Mux

Port Strap Enable Port Disable Port

Port 1

Port 2

A A

DDPB_CTRLDATA

DDPC_CTRLDATA

PU to 3.3 V with 2.2-k

±5% resistor

PU to 3.3 V with 2.2-k

±5% resistor

NC

NC

SIO_EXT_SMI#

1 2

R802 10KR2J-3-GP

<Core Design>

<Core Design>

<Core Design>

Design Guideline:

Skylake processor signal eDP_RCOMP should be connected to the VCCIO rail via a single 24.9 ±1% Ω resistor.

5

4

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

CPU_(DISPLAY)

CPU_(DISPLAY)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet of

CPU_(DISPLAY)

KyloRen 13"

KyloRen 13"

KyloRen 13"

8 106Thursday, June 29, 2017

8 106Thursday, June 29, 2017

8 106Thursday, June 29, 2017

1

A00

A00

A00

5

D D

4

3

2

1

C C

(Blanking)

B B

A A

5

4

3

2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

(Reserved)

(Reserved)

(Reserved)

KyloRen 13"

KyloRen 13"

KyloRen 13"

9 106Thursday, June 29, 2017

9 106Thursday, June 29, 2017

9 106Thursday, June 29, 2017

1

A00

A00

A00

A00

A00

A00

10 106Thursday, June 29, 2017

10 106Thursday, June 29, 2017

10 106Thursday, June 29, 2017

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

1

<Core Design>

<Core Design>

<Core Design>

2

Title

Title

Title

1

KyloRen 13"

KyloRen 13"

KyloRen 13"

CPU_(Power CAP1)

CPU_(Power CAP1)

CPU_(Power CAP1)

A2

A2

A2

Size Document Number Rev

Date: Sheet of

Size Document Number Rev

Date: Sheet of

Size Document Number Rev

Date: Sheet of

2

SC10U6D3V2MX-2-GP

PC1083

12

3

U42

SC10U6D3V2MX-2-GP

PC1082

12

U42

SC10U6D3V2MX-2-GP

PC1081

12

U42

SC10U6D3V2MX-2-GP

PC1080

12

U42

SC10U6D3V2MX-2-GP

PC1035

12

U42

SC10U6D3V2MX-2-GP

PC1079

12

U42

SC10U6D3V2MX-2-GP

PC1033

12

U42

SC10U6D3V2MX-2-GP

PC1093

12

U42

SC10U6D3V2MX-2-GP

PC1092

12

U42

SC10U6D3V2MX-2-GP

PC1091

12

U42

SC10U6D3V2MX-2-GP

PC1090

12

U42

SC10U6D3V2MX-2-GP

PC1086

12

U42

SC10U6D3V2MX-2-GP

PC1085

12

U42

SC10U6D3V2MX-2-GP

PC1084

12

U42

3

2016/11/7modify

VCC_CORE

SC10U6D3V2MX-2-GP

PC1087

12

4

2017/01/182017/01/18

2017/04/26

5

22U 0603 x 30

U-line 22 15W

IccMax current-10ms max = 31 A

VCC_CORE

10U 0402 x 2 (2DY)

DY

SC10U6D3V2MX-2-GP

PC1032

12

DY

SC10U6D3V3MX-DL-GP

PC1020

12

DY

SC10U6D3V3MX-DL-GP

PC1017

12

DY

SC22U6D3V3MX-1-DL-GP

PC1011

12

SC22U6D3V3MX-1-DL-GP

PC1010

12

SC22U6D3V3MX-1-DL-GP

PC1009

12

SC22U6D3V3MX-1-DL-GP

PC1008

12

SC22U6D3V3MX-1-DL-GP

PC1007

12

SC22U6D3V3MX-1-DL-GP

PC1006

DY

12

SC22U6D3V3MX-1-DL-GP

PC1005

12

SC22U6D3V3MX-1-DL-GP

PC1004

12

SC22U6D3V3MX-1-DL-GP

PC1003

12

SC22U6D3V3MX-1-DL-GP

PC1002

12

DY

2017/04/26

SC22U6D3V3MX-1-DL-GP

PC1023

12

SC22U6D3V3MX-1-DL-GP

PC1022

12

SC22U6D3V3MX-1-DL-GP

PC1021

12

SC22U6D3V3MX-1-DL-GP

PC1019

12

SC22U6D3V3MX-1-DL-GP

PC1018

12

SC22U6D3V3MX-1-DL-GP

PC1016

12

SC22U6D3V3MX-1-DL-GP

PC1015

12

SC22U6D3V3MX-1-DL-GP

PC1014

2017/04/26

12

SC22U6D3V3MX-1-DL-GP

PC1013

12

SC22U6D3V3MX-1-DL-GP

PC1012

12

4

SC22U6D3V3MX-1-DL-GP

PC1001

SC22U6D3V3MX-1-DL-GP

PC1070

12

U42

SC22U6D3V3MX-1-DL-GP

PC1069

12

2017/04/26

SC22U6D3V3MX-1-DL-GP

PC1036

DY

DY

DY

12

SC22U6D3V3MX-1-DL-GP

PC1034

DY

12

SC22U6D3V3MX-1-DL-GP

PC1031

12

SC22U6D3V3MX-1-DL-GP

PC1030

12

SC22U6D3V3MX-1-DL-GP

PC1029

12

DY

SC22U6D3V3MX-1-DL-GP

PC1028

12

SC22U6D3V3MX-1-DL-GP

PC1027

12

SC22U6D3V3MX-1-DL-GP

PC1026

DY

12

SC22U6D3V3MX-1-DL-GP

PC1025

12

SC22U6D3V3MX-1-DL-GP

PC1024

12

VCCGT

22U 0603 x 30 (3 DY)

U-line 22 15W

IccMax current-10ms max[A] = 64 A

U42

SC22U6D3V3MX-1-DL-GP

PC1046

12

SC22U6D3V3MX-1-DL-GP

PC1045

12

SC22U6D3V3MX-1-DL-GP

PC1044

12

SC22U6D3V3MX-1-DL-GP

PC1043

12

SC22U6D3V3MX-1-DL-GP

PC1042

12

SC22U6D3V3MX-1-DL-GP

PC1041

12

SC22U6D3V3MX-1-DL-GP

PC1040

12

SC22U6D3V3MX-1-DL-GP

PC1039

12

SC22U6D3V3MX-1-DL-GP

PC1038

12

SC22U6D3V3MX-1-DL-GP

PC1037

12

SC22U6D3V3MX-1-DL-GP

PC1056

12

SC22U6D3V3MX-1-DL-GP

PC1055

12

SC22U6D3V3MX-1-DL-GP

PC1054

12

SC22U6D3V3MX-1-DL-GP

PC1053

12

SC22U6D3V3MX-1-DL-GP

PC1052

12

SC22U6D3V3MX-1-DL-GP

PC1051

12

SC22U6D3V3MX-1-DL-GP

PC1050

12

SC22U6D3V3MX-1-DL-GP

PC1049

12

SC22U6D3V3MX-1-DL-GP

PC1048

12

SC22U6D3V3MX-1-DL-GP

PC1047

12

12

DY

SC22U6D3V3MX-1-DL-GP

PC1068

12

DY

SC22U6D3V3MX-1-DL-GP

PC1067

12

DY

SC22U6D3V3MX-1-DL-GP

PC1066

12

SC22U6D3V3MX-1-DL-GP

PC1065

12

SC22U6D3V3MX-1-DL-GP

PC1064

12

SC22U6D3V3MX-1-DL-GP

PC1063

12

SC22U6D3V3MX-1-DL-GP

PC1062

12

SC22U6D3V3MX-1-DL-GP

PC1061

12

SC22U6D3V3MX-1-DL-GP

PC1060

12

SC22U6D3V3MX-1-DL-GP

PC1059

12

SC22U6D3V3MX-1-DL-GP

PC1058

12

SC22U6D3V3MX-1-DL-GP

PC1057

12

VCCSA

SC22U6D3V3MX-1-DL-GP

PC1078

12

DY

SC22U6D3V3MX-1-DL-GP

PC1077

12

SC22U6D3V3MX-1-DL-GP

PC1076

12

SC22U6D3V3MX-1-DL-GP

PC1075

12

DY

SC22U6D3V3MX-1-DL-GP

PC1074

12

DY

SC22U6D3V3MX-1-DL-GP

PC1073

12

SC22U6D3V3MX-1-DL-GP

PC1072

12

SC22U6D3V3MX-1-DL-GP

PC1071

12

5

22U 0603 x 5 (3DY)

SSID = CPU

VCC_CORE

D D

C C

+VCCGT

B B

+VCCSA

A A

SSID = CPU

5

4

3

2

1

PCH DERIVED RAILS

1D0V_S5

D D

2017/05/08

UNSLICED GT

+VCCGT

VCCIO

+VCCIO

+VCCIO(ICCMAX.=2.73A)

1 2

R1101

0R1206-PAD

1 2

R1102

0R0603-PAD

+VCCPRIM_CORE

+V1.00A_SIP

C1112

SC22U6D3V3MX-1-GP

12

12

12

C1103

C1102

DY

DY

SC1U10V2KX-1DLGP

SC1U10V2KX-1DLGP

Dummy : 20150123 Dummy : 20150123

12

C1104

DY

SC1U10V2KX-1DLGP

12

C1105

SC1U10V2KX-1DLGP

12

C1106

DY

SC1U10V2KX-1DLGP

12

C1107

1U 0402 x 6

SC1U10V2KX-1DLGP

DY

12

C1108

SC1U10V2KX-1DLGP

12

C1109

SC1U10V2KX-1DLGP

12

C1110

SC1U10V2KX-1DLGP

12

C1111

SC1U10V2KX-1DLGP

DY

3D3V_S5_PCH +V3.3A_SIP

1 2

C C

R1103

0R0603-PAD

C1113

SC22U6D3V3MX-1-GP

12

+VCCMPHYGTAON_1P0(ICCMAX.=2.12A)

DY

Layout Note:

+V1.8A +V1.8A_SIP

R1104

12

0R0603-PAD

12

DY

+VCCMPHYGTAON_1P0_LS_SIP +VCCMPHYGTAON_1P0_LS_SIP+VCCMPHYGTAON_1P0_LS_SIP+VCCMPHYGTAON_1P0_LS_SIP

C1117

C1115

DY

SC22U6D3V3MX-1-GP

12

C1116

SC1U10V2KX-1DLGP

12

C1114

SC1U10V2KX-1DLGP

12

C1122

SC22U6D3V3MX-1-GP

SC1U10V2KX-1DLGP

12

C1118

12

DY

C1119

SC22U6D3V3MX-1-GP

SC1U10V2KX-1DLGP

12

SC10U6D3V3MX-DL-GP

C1120

12

C1121

SC1U10V2KX-1DLGP

12

DY

1uF:

C1174 near N15

C1180 near K15

C1173 near AF20

C1172 near N18

C1175 near AB19

22uF :

C1182 C1184 near N15

10uF:

C1176 near N15

+VCCIO

+VCCPRIM_CORE

+VCCIO(ICCMAX.=2.73A)

C1134

C1133

12

SC22U6D3V3MX-1-DL-GP

B B

12

C1135

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

12

C1128

12

C1129

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

12

1D2V_S3

DY

12

C1130

12

12

12

C1139SCD1U25V2KX-1-DL-GP

C1140SCD1U25V2KX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

EC1102

SC2D2U6D3V2MX-DL-GP

12

12

12

DY

C1141SCD1U25V2KX-1-DL-GP

EC1103

SC2D2U6D3V2MX-DL-GP

C1142SCD1U25V2KX-1-DL-GP

12

DY

VCC_CORE

2017/01/17

1U 0402 x 5

+V3.3A_SIP

SC10U6D3V3MX-DL-GP

C1123

12

C1132

12

12

C1137

C1138

SC10U6D3V3MX-DL-GP

SC10U6D3V3MX-DL-GP

C1131

SC22U6D3V3MX-1-DL-GP

SC22U6D3V3MX-1-DL-GP

12

DY

C1136

SC10U6D3V3MX-DL-GP

DY

12

DY

A A

U-line 23e 28W

IccMax current-10ms max = 34 A

DY

12

C1124

SC1U10V2KX-1DLGP

DY

5

12

C1125

SC1U10V2KX-1DLGP

DY

12

C1126

SC1U10V2KX-1DLGP

DY

12

C1101

DY

SC1U10V2KX-1DLGP

12

C1127

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

SC1U10V2KX-1DLGP

RF request 2016/01/12 modify

Title

Title

Title

CPU_(Power CAP2)

CPU_(Power CAP2)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

4

3

2

CPU_(Power CAP2)

KyloRen 13"

KyloRen 13"

KyloRen 13"

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

11 106Thursday, June 29, 2017

11 106Thursday, June 29, 2017

11 106Thursday, June 29, 2017

1

A00

A00

A00

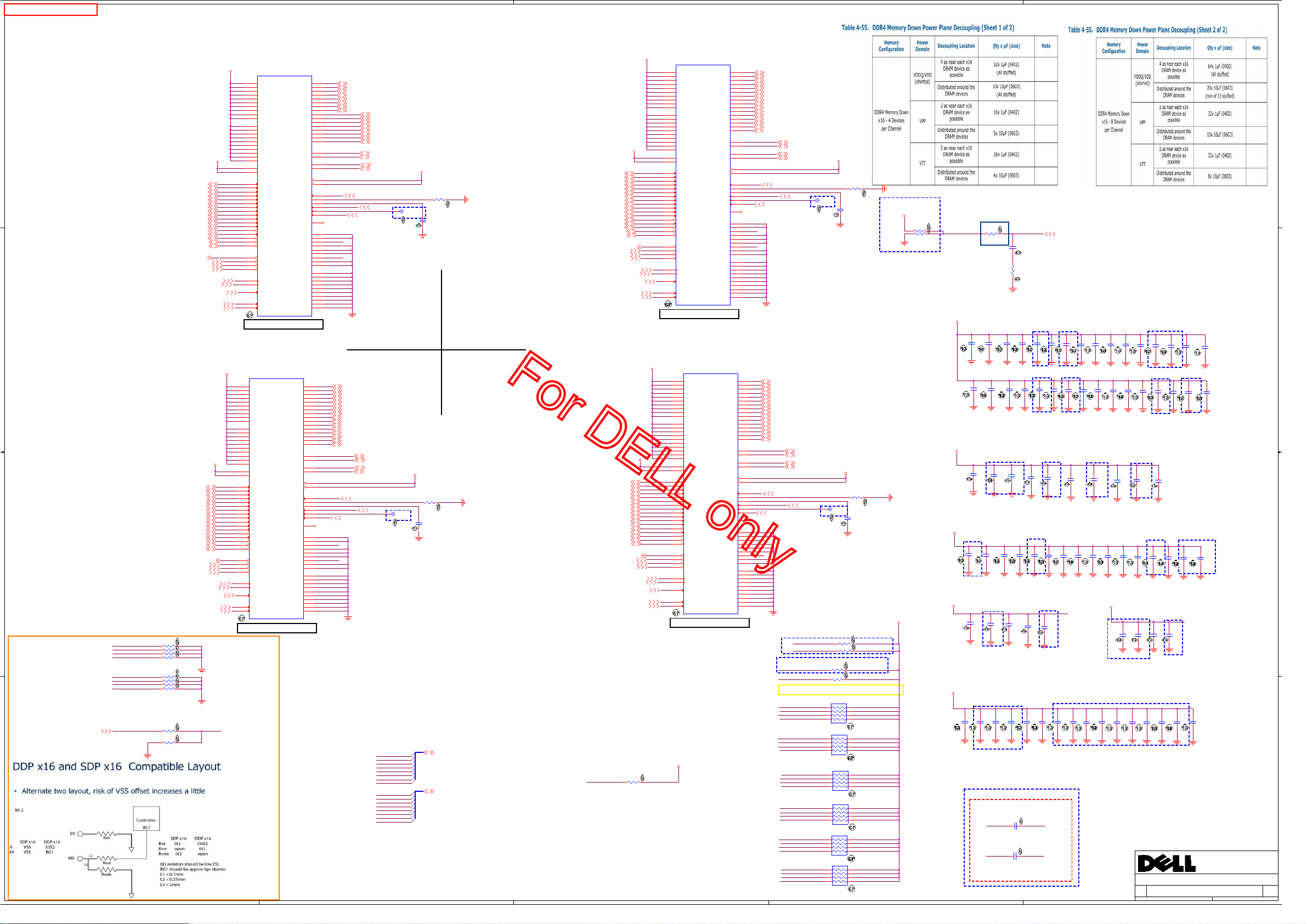

SSID = MEMORY

5

4

3

2

1

1D2V_S3

U1204

B3

VDD

B9

VDD

D1

VDD

G7

VDD

J1

VDD

J9

VDD

L1

VDD

L9

VDD

R1

VDD

T9

VDD

A1

VDDQ

A9

VDDQ

C1

VDDQ

D9

VDDQ

F2

VDDQ

F8

VDDQ

D D

2D5V_S3

M_A_A05,12

M_A_A15,12

M_A_A25,12

M_A_A35,12

M_A_A45,12

M_A_A55,12

M_A_A65,12

M_A_A75,12

M_A_A85,12

M_A_A95,12

M_A_A105,12

M_A_A115,12

M_A_A125,12

M_A_A135,12

M_A_A145,12

M_A_A155,12

M_A_A165,12

M_A_CS#05,12

DDR4_DR AMRST#5,12,13

M_A_ACT_N5,12

M_A_ALERT_N5,12

M_A_CLK05,12

M_A_CLK#05,12

M_A_CKE05,12

M_A_BA05,12

M_A_BA15,12

G1

VDDQ

G9

VDDQ

J2

VDDQ

J8

VDDQ

B1

VPP

R9

VPP

NF#E2/UDM#/UDBI#

P3

A0

NF#E7/LDM#/LDBI#

P7

A1

R3

A2

N7

A3

N3

A4

P8

A5

P2

A6

R8

A7

R2

A8

R7

A9

M3

A10/AP

T2

A11

M7

A12/BC#

T8

A13

L2

WE#/A14

M8

CAS#/A15

L8

RAS#/A16

L7

CS#

P1

RESET#

L3

ACT#

P9

ALERT#

K7

CK_T

K8

CK_C

K2

CKE

N2

BA0

N8

BA1

MT40A256M16GE-083E- B-COLAY1-GP

ZZ.00PAD.0Q2

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

UDQS_T

UDQS_C

LDQS_T

LDQS_C

VREFCA

NC#T7

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

G2

DQ0

F7

DQ1

H3

DQ2

H7

DQ3

H2

DQ4

H8

DQ5

J3

DQ6

J7

DQ7

A3

DQ8

B8

DQ9

C3

C7

C2

C8

D3

D7

B7

A7

G3

M_A_DQS_DN1

F3

E2

E7

K3

ODT

F9

ZQ

M1

M2

BG0

N9

TEN

T3

PAR

T7

B2

VSS

E1

VSS

M_A_BG1_E9_1

E9

VSS

G8

VSS

K1

VSS

K9

VSS

M_A_BG1_M9_R

M9

VSS

N1

VSS

T1

VSS

A2

A8

C9

D2

D8

E3

E8

F1

H1

H9

M_A_DQS_DP0

M_A_DQS_DN0

M_A_DQS_DP1

TEST_MODE_1

M_A_DQ8 5

M_A_DQ9 5

M_A_DQ10 5

M_A_DQ11 5

M_A_DQ12 5

M_A_DQ13 5

M_A_DQ14 5

M_A_DQ15 5

M_A_DQ0 5

M_A_DQ1 5

M_A_DQ2 5

M_A_DQ3 5

M_A_DQ4 5

M_A_DQ5 5

M_A_DQ6 5

M_A_DQ7 5

M_A_DIMA_ODT0 5,12

M_A_BG0 5,12

M_A_PARITY 5,12

A_ZQ_RAM4

M_VREF_CA_D IMMA

1

TP1201

TPAD14-OP-G P

2016/11/29

1D2V_S3

240R2D-GP

C1201

SCD047U25V2KX-4-GP

R1201

1 2

12

M_A_A05,12

M_A_A15,12

M_A_A25,12

M_A_A35,12

M_A_A45,12

M_A_A55,12

M_A_A65,12

M_A_A75,12

M_A_A85,12

M_A_A95,12

M_A_A105,12

M_A_A115,12

M_A_A125,12

M_A_A135,12

DDR4_DR AMRST#5,12,13

M_A_ACT_N5,12

M_A_ALERT_N5,12

2017/05/10

1D2V_S3

C C

2D5V_S3

M_A_A05,12

M_A_A15,12

M_A_A25,12

M_A_A35,12

M_A_A45,12

M_A_A55,12

M_A_A65,12

M_A_A75,12

M_A_A85,12

M_A_A95,12

M_A_A105,12

M_A_A115,12

M_A_A125,12

M_A_A135,12

M_A_A145,12

M_A_A155,12

M_A_A165,12

M_A_CS#05,12

DDR4_DR AMRST#5,12,13

M_A_ACT_N5,12

M_A_ALERT_N5,12

M_A_CLK05,12

M_A_CLK#05,12

M_A_CKE05,12

M_A_BA05,12

B B

M_A_BA15,12

SDP & DDP SETTING

M_A_BG1_E9_1

M_A_BG1_E9_2

M_A_BG1_E9_3

M_A_BG1_E9_4

M_A_BG1_E9_1

M_A_BG1_E9_2

M_A_BG1_E9_3

M_A_BG1_E9_4

M_A_BG15

A A

5

1 2

R1212 240R2F-1-GP

DDP

1 2

R1213 240R2F-1-GP

DDP

1 2

R1214 240R2F-1-GP

DDP

1 2

R1215 240R2F-1-GP

DDP

1 2

R1216 0R2J-2-GP

SDP

1 2

R1217 0R2J-2-GP

SDP

1 2

R1218 0R2J-2-GP

SDP

1 2

R1219 0R2J-2-GP

SDP

DDP

1 2

R1220 0R2J-2-GP

1 2

R1221 0R2J-2-GP

SDP

M_A_BG1_M9_R

U1201

B3

VDD

B9

VDD

D1

VDD

G7

VDD

J1

VDD

J9

VDD

L1

VDD

L9

VDD

R1

VDD

T9

VDD

A1

VDDQ

A9

VDDQ

C1

VDDQ

D9

VDDQ

F2

VDDQ

F8

VDDQ

G1

VDDQ

G9

VDDQ

J2

VDDQ

J8

VDDQ

B1

VPP

R9

VPP

NF#E2/UDM#/UDBI#

P3

A0

NF#E7/LDM#/LDBI#

P7

A1

R3

A2

N7

A3

N3

A4

P8

A5

P2

A6

R8

A7

R2

A8

R7

A9

M3

A10/AP

T2

A11

M7

A12/BC#

T8

A13

L2

WE#/A14

M8

CAS#/A15

L8

RAS#/A16

L7

CS#

P1

RESET#

L3

ACT#

P9

ALERT#

K7

CK_T

K8

CK_C

K2

CKE

N2

BA0

N8

BA1

MT40A256M16GE-083E- B-COLAY1-GP

ZZ.00PAD.0Q2

2017/05/10

G2

DQ0

F7

DQ1

H3

DQ2

H7

DQ3

H2

DQ4

H8

DQ5

J3

DQ6

J7

DQ7

A3

DQ8

B8

DQ9

C3

DQ10

C7

DQ11

C2

DQ12

C8

DQ13

D3

DQ14

D7

DQ15

B7

UDQS_T

A7

UDQS_C

G3

LDQS_T

F3

LDQS_C

E2

E7

K3

ODT

F9

ZQ

M1

VREFCA

M2

BG0

N9

TEN

T3

PAR

T7

NC#T7

B2

VSS

E1

VSS

E9

VSS

G8

VSS

K1

VSS

K9

VSS

M9

VSS

N1

VSS

T1

VSS

A2

VSSQ

A8

VSSQ

C9

VSSQ

D2

VSSQ

D8

VSSQ

E3

VSSQ

E8

VSSQ

F1

VSSQ

H1

VSSQ

H9

VSSQ

CTRL/CKE/CMD

M_A_DQS_DP7

M_A_DQS_DN7

M_A_DQS_DP6

M_A_DQS_DN6

TEST_MODE_2

M_A_BG1_E9_3

M_A_BG1_M9_R

CLK

M_A_DQ53 5

M_A_DQ51 5

M_A_DQ55 5

M_A_DQ50 5

M_A_DQ48 5

M_A_DQ52 5

M_A_DQ54 5

M_A_DQ49 5

M_A_DQ61 5

M_A_DQ57 5

M_A_DQ58 5

M_A_DQ63 5

M_A_DQ60 5

M_A_DQ56 5

M_A_DQ59 5

M_A_DQ62 5

M_A_DIMA_ODT0 5,12

M_A_BG0 5,12

M_A_PARITY 5,12

2016/11/29

A_ZQ_RAM1

1

TP1202

TPAD14-OP-G P

2016/11/29

M_A_CLK#0

M_A_CLK0

M_A_BG1_M9_R

2016/11/25

M_A_CKE0

M_A_A12

M_A_A3

M_A_ACT_N

M_A_BG0

M_A_A5

M_A_A2

M_A_BA1

M_A_A6

M_A_A7

M_A_A0

M_A_A13

M_A_A11

M_A_A9

M_A_A8

M_A_PARITY

M_A_A1

M_A_BA0

M_A_A4

M_A_A14

M_A_A10

M_A_A16

M_A_A15

M_A_DIMA_ODT0

M_A_CS#0

1D2V_S3

M_VREF_CA_D IMMA

SCD047U25V2KX-4-GP

12

C1236

R1226 36R2F-1-GP

R1225 36R2F-1-GP

1 2

R1224 36R2F-1-GP

R1211 36R2F-1-GP

1 2

1

2

3

4 5

1

2

3

4 5

1

2

3

4 5

4

240R2D-GP

R1205

1 2

1 2

DDP

RN1202

SRN36J-GP

RN1203

SRN36J-GP

RN1204

SRN36J-GP

RN1205

1

2

3

4 5

SRN36J-GP

RN1206

1

2

3

4 5

SRN36J-GP

RN1207

1

2

3

4 5

SRN36J-GP

M_A_A05,12

M_A_A15,12

M_A_A25,12

M_A_A35,12

M_A_A45,12

12

0D6V_S0

8

7

6

8

7

6

8

7

6

8

7

6

8

7

6

8

7

6

M_A_A55,12

M_A_A65,12

M_A_A75,12

M_A_A85,12

M_A_A95,12

M_A_A105,12

M_A_A115,12

M_A_A125,12

M_A_A135,12

M_A_A145,12

DDR4_DR AMRST#5,12,13

M_A_ACT_N5,12

M_A_ALERT_N5,12

ALERT

M_A_A155,12

M_A_A165,12

2D5V_S3

M_A_A145,12

M_A_A155,12

M_A_A165,12

M_A_CS#05,12

M_A_CLK05,12

M_A_CLK#05,12

M_A_CKE05,12

M_A_BA05,12

M_A_BA15,12

1D2V_S3

2D5V_S3

M_A_CS#05,12

M_A_CLK05,12

M_A_CLK#05,12

M_A_CKE05,12

M_A_BA05,12

M_A_BA15,12

M_A_ALERT_N

2016/11/25 DY

3

1D2V_S3

U1203

B3

VDD

B9

VDD

D1

VDD

G7

VDD

J1

VDD

J9

VDD

L1

VDD

L9

VDD

R1

VDD

T9

VDD

A1

VDDQ

A9

VDDQ

C1

VDDQ

D9

VDDQ

F2

VDDQ

F8

VDDQ

G1

VDDQ

G9

VDDQ

J2

VDDQ

J8

VDDQ

B1

VPP

R9

VPP

P3

A0

P7

A1

R3

A2

N7

A3

N3

A4

P8

A5

P2

A6

R8

A7

R2

A8

R7

A9

M3

A10/AP

T2

A11

M7

A12/BC#

T8

A13

L2

WE#/A14

M8

CAS#/A15

L8

RAS#/A16

L7

CS#

P1

RESET#

L3

ACT#

P9

ALERT#

K7

CK_T

K8

CK_C

K2

CKE

N2

BA0

N8

BA1

MT40A256M16GE-083E- B-COLAY1-GP

ZZ.00PAD.0Q2

2017/05/10

U1202

B3

VDD

B9

VDD

D1

VDD

G7

VDD

J1

VDD

J9

VDD

L1

VDD

L9

VDD

R1

VDD

T9

VDD

A1

VDDQ

A9

VDDQ

C1

VDDQ

D9

VDDQ

F2

VDDQ

F8

VDDQ

G1

VDDQ

G9

VDDQ

J2

VDDQ

J8

VDDQ

B1

VPP

R9

VPP

P3

A0

P7

A1

R3

A2

N7

A3

N3

A4

P8

A5

P2

A6

R8

A7

R2

A8

R7

A9

M3

A10/AP

T2

A11

M7

A12/BC#

T8

A13

L2

WE#/A14

M8

CAS#/A15

L8

RAS#/A16

L7

CS#

P1

RESET#

L3

ACT#

P9

ALERT#

K7

CK_T

K8

CK_C

K2

CKE

N2

BA0

N8

BA1

MT40A256M16GE-083E- B-COLAY1-GP

ZZ.00PAD.0Q2

2017/05/10

R1208

1 2

49D9R2F-GP

close to cpu

C1285

M_A_CLK0 M_A_CLK0

1 2

SC3300P50V2KX-1D LGP

DY

C1287

M_A_CLK#0 M_A_CLK#0

1 2

SC3300P50V2KX-1D LGP

DY

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

UDQS_T

UDQS_C

LDQS_T

LDQS_C

NF#E2/UDM#/UDBI#

NF#E7/LDM#/LDBI#

VREFCA

NC#T7

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

UDQS_T

UDQS_C

LDQS_T

LDQS_C

NF#E2/UDM#/UDBI#

NF#E7/LDM#/LDBI#

VREFCA

NC#T7

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

1D2V_S3

G2

DQ0

F7

DQ1

H3

DQ2

H7

DQ3

H2

DQ4

H8

DQ5

J3

DQ6

J7

DQ7

A3

DQ8

B8

DQ9

C3

C7

C2

C8

D3

D7

B7

A7

G3

F3

E2

E7

K3

ODT

F9

ZQ

M1

M2

BG0

N9

TEN

T3

PAR

T7

B2

VSS

E1

VSS

E9

VSS

G8

VSS

K1

VSS

K9

VSS

M9

VSS

N1

VSS

T1

VSS

A2

A8

C9

D2

D8

E3

E8

F1

H1

H9

G2

DQ0

F7

DQ1

H3

DQ2

H7

DQ3

H2

DQ4

H8

DQ5

J3

DQ6

J7

DQ7

A3

DQ8

B8

DQ9

C3

C7

C2

C8

D3

D7

B7

A7

G3

F3

E2

E7

K3

ODT

F9

ZQ

M1

M2

BG0

N9

TEN

T3

PAR

T7

B2

VSS

E1

VSS

E9

VSS

G8

VSS

K1

VSS

K9

VSS

M9

VSS

N1

VSS

T1

VSS

A2

A8

C9

D2

D8

E3

E8

F1

H1

H9

M_A_DQS_DP2

M_A_DQS_DN2

M_A_DQS_DP3

M_A_DQS_DN3

TEST_MODE_3

M_A_BG1_E9_2

M_A_BG1_M9_R

M_A_DQS_DP4

M_A_DQS_DN4

M_A_DQS_DP5

M_A_DQS_DN5

TEST_MODE_4

M_A_BG1_E9_4

M_A_BG1_M9_R

M_A_DQ24 5

M_A_DQ25 5

M_A_DQ26 5

M_A_DQ27 5

M_A_DQ28 5

M_A_DQ29 5

M_A_DQ30 5

M_A_DQ31 5

M_A_DQ16 5

M_A_DQ17 5

M_A_DQ18 5

M_A_DQ19 5

M_A_DQ20 5

M_A_DQ21 5

M_A_DQ22 5

M_A_DQ23 5

M_A_DIMA_ODT0 5,12

M_A_BG0 5,12

M_A_PARITY 5,12

2016/11/29

M_A_DQ40 5

M_A_DQ41 5

M_A_DQ47 5

M_A_DQ42 5

M_A_DQ44 5

M_A_DQ45 5

M_A_DQ43 5

M_A_DQ46 5

M_A_DQ33 5

M_A_DQ37 5

M_A_DQ34 5

M_A_DQ35 5

M_A_DQ36 5

M_A_DQ32 5

M_A_DQ38 5

M_A_DQ39 5

M_A_DIMA_ODT0 5,12

M_A_BG0 5,12

M_A_PARITY 5,12

2016/11/29

A_ZQ_RAM3

M_VREF_CA_D IMMA

1

TP1203

TPAD14-OP-G P

A_ZQ_RAM2

M_VREF_CA_D IMMA

1

TP1204

TPAD14-OP-G P

1D2V_S3

1K8R2F-GP

R1222

1 2

1 2

R1223

1K8R2F-GP

2016/11/25

1D2V_S3

240R2D-GP

12

R1204

12

SCD047U25V2KX-4-GP

C1203

M_A_DQS_DN0

M_A_DQS_DN1

M_A_DQS_DN2

M_A_DQS_DN3

M_A_DQS_DN4

M_A_DQS_DN5

M_A_DQS_DN6

M_A_DQS_DN7

M_A_DQS_DP0

M_A_DQS_DP1

M_A_DQS_DP2

M_A_DQS_DP3

M_A_DQS_DP4

M_A_DQS_DP5

M_A_DQS_DP6

M_A_DQS_DP7

1D2V_S3

240R2D-GP

12

R1234

12

SCD047U25V2KX-4-GP

C1286

M_A_DQS_DN[7: 0] 5

M_A_DQS_DP[7:0] 5

1D2V_S3

VDDQ/VDD 1uF x32

12

12

C1204

SC1U10V2KX-1DLGP

12

C1220

SC1U10V2KX-1DLGP

1D2V_S3

VDDQ/VDD 10uF x10

12

C1237

SC10U6D3V3MX-DL-GP

VPP 1uF x16

2D5V_S3

2017/01/17

C1205

DY

SC1U10V2KX-1DLGP

12

C1221

SC1U10V2KX-1DLGP

12

C1238

SC10U6D3V3MX-DL-GP

12

C1206

SC1U10V2KX-1DLGP

12

C1222

12

12

C1207

DY

SC1U10V2KX-1DLGP

12

C1223

SC1U10V2KX-1DLGP

SC1U10V2KX-1DLGP

2017/01/17

DY

C1239

SC10U6D3V3MX-DL-GP

12

12

C1208

C1209

SC1U10V2KX-1DLGP

12

12

C1224

C1225

SC1U10V2KX-1DLGP

DY

DY

C1240

12

12

C1241

SC10U6D3V3MX-DL-GP

2017/01/17

12

12

12

12

12

C1260

C1259

SC1U10V2KX-1DLGP

2D5V_S3

DY

C1268

SC1U10V2KX-1DLGP

SC1U10V2KX-1DLGP

DY

VPP 10uF x5

12

C1279

12

SC10U6D3V3MX-DL-GP

DY

C1261

C1275

12

C1269

C1262

SC1U10V2KX-1DLGP

SC1U10V2KX-1DLGP

12

C1276

12

SC10U6D3V3MX-DL-GP

SC10U6D3V3MX-DL-GP

M_VREF_CA_D IMMA

12

C1210

SC1U10V2KX-1DLGP

SC1U10V2KX-1DLGP

12

C1226

SC1U10V2KX-1DLGP

SC1U10V2KX-1DLGP

12

SC10U6D3V3MX-DL-GP

12

C1270

SC1U10V2KX-1DLGP

SC1U10V2KX-1DLGP

DY

DY

C1277

12

C1278

SC10U6D3V3MX-DL-GP

2017/03/07

1 2

12

C1211

SC1U10V2KX-1DLGP

12

C1227