Page 1

iVPX7225

Installation and Use

P/N: 6806800S11C

April 2015

Page 2

©

Copyright 2015 Artesyn Embedded Technologies, Inc.

All rights reserved.

Trademarks

Artesyn Embedded Technologies, Artesyn and the Artesyn Embedded Technologies logo are trademarks and service marks of

Artesyn Embedded Technologies, Inc.© 2015 Artesyn Embedded Technologies, Inc. All other product or service names are the

property of their respective owners.

Intel® is a trademark or registered trademark of Intel Corporation or its subsidiaries in the United States and other countries.

Java™ and all other Java-based marks are trademarks or registered trademarks of Oracle America, Inc. in the U.S. and other countries.

Microsoft®, Windows® and Windows Me® are registered trademarks of Microsoft Corporation; and Windows XP™ is a trademark of

Microsoft Corporation.

PICMG®, CompactPCI®, AdvancedTCA™ and the PICMG, CompactPCI and AdvancedTCA logos are registered trademarks of the PCI

Industrial Computer Manufacturers Group.

UNIX® is a registered trademark of The Open Group in the United States and other countries.

Notice

While reasonable efforts have been made to assure the accuracy of this document, Artesyn assumes no liability resulting from any

omissions in this document, or from the use of the information obtained therein. Artesyn reserves the right to revise this document

and to make changes from time to time in the content hereof without obligation of Artesyn to notify any person of such revision or

changes.

Electronic versions of this material may be read online, downloaded for personal use, or referenced in another document as a URL to

an Artesyn website. The text itself may not be published commercially in print or electronic form, edited, translated, or otherwise

altered without the permission of Artesyn.

It is possible that this publication may contain reference to or information about Artesyn products (machines and programs),

programming, or services that are not available in your country. Such references or information must not be construed to mean that

Artesyn intends to announce such Artesyn products, programming, or services in your country.

Limited and Restricted Rights Legend

If the documentation contained herein is supplied, directly or indirectly, to the U.S. Government, the following notice shall apply

unless otherwise agreed to in writing by Artesyn.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (b)(3) of the Rights in

Technical Data clause at DFARS 252.227-7013 (Nov. 1995) and of the Rights in Noncommercial Computer Software and

Documentation clause at DFARS 252.227-7014 (Jun. 1995).

Contact Address

Artesyn Embedded Technologies Artesyn Embedded Technologies

Marketing Communications

2900 S. Diablo Way, Suite 190

Tempe, Arizona 85282

Lilienthalstr. 17-19

85579 Neubiberg/Munich

Germany

Page 3

Contents

Contents

About this Manual . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Safety Notes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Sicherheitshinweise . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

1.2 Standard Compliances . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

1.3 Mechanical Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

1.3.1 Air Cooled. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

1.3.2 Conduction Cooled. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

1.4 Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

1.4.1 Supported Board Models. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

1.5 Product Identification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

2 Hardware Preparation and Installation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

2.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

2.2 Unpacking and Inspecting the Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

2.3 Environmental and Power Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

2.3.1 Environmental Requirements. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

2.3.2 Power Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

2.4 Installing the Accessories . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

2.4.1 Installing the XMC on Air Cooled Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

2.4.2 Installing the XMC on Conduction Cooled Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

2.4.3 Rear Transition Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

2.5 Installing and Removing the Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

2.5.1 Installing Air Cooled iVPX7225. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

2.5.2 Installing Conduction Cooled iVPX7225. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

3 Controls, LEDs and Connectors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

3.1 Board Layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

3.2 Planar LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

iVPX7225 Installation and Use (6806800S11C)

3

Page 4

Contents

Contents

Contents

3.2.1 Debug LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

3.2.2 POST Code LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

3.3 Front Panel Connectors and LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

3.4 Backplane Connectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

3.4.1 P0 Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

3.4.2 P1 Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

3.4.3 P2 Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

3.5 XMC Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

3.6 Switches . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

4.1 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

4.2 Processor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

4.3 Chipset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

4.4 System Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

4.5 Ethernet Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

4.6 PCI Express . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

4.7 SATA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

4.8 USB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

4.9 Serial COM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

4.10 Video . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

4.10.1 Rear DisplayPort . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

4.10.2 VGA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

4.11 GPIO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

4.12 SMBus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

4.13 Boot Flash . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

4.14 NAND Flash . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

4.15 FRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

4.16 Trusted Platform Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

4.17 Real Time Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

4.18 Watchdog Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

4.19 XMC Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

4.20 Boot Firmware . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

4.21 Operating System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

4

iVPX7225 Installation and Use (6806800S11C)

Page 5

Contents

5 BIOS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

5.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

5.2 Processor Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

5.3 Memory Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

5.3.1 Serial Presence Detect (SPD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

5.3.2 Memory Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

5.3.3 ECC Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

5.3.4 DDR3 Refresh Rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

5.4 Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

5.5 PCIe Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

5.6 I/O Device Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

5.7 Boot Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

5.8 I/O Redirection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

5.9 BIOS Setup Layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

5.9.1 Main Menu . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

5.9.2 Boot Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

5.9.3 Advanced Menu . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

5.9.4 Processor Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

5.9.5 Processor Power Management. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

5.9.6 HDD Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

5.9.7 Memory Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

5.9.8 System Agent (SA) Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

5.9.9 Graphics Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

5.9.10 IGD Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

5.9.11 PEG Port Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

5.9.12 South Bridge Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

5.9.13 SB USB Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

5.9.14 SB Security Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

5.9.15 Network Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

5.9.16 SIO Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

5.9.17 ME Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

5.9.18 Thermal Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

5.9.19 Platform Thermal Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

5.9.20 Intel® Rapid Start Technology . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

5.9.21 iVPX7225 Menu. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

iVPX7225 Installation and Use (6806800S11C)

5

Page 6

Contents

Contents

Contents

5.9.22 Security Menu . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

5.9.23 TPM Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

5.9.24 Boot Menu . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

5.9.25 Exit Menu . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

5.10 BIOS POST Codes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

5.11 Memory POST Codes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

6 Maps and Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

6.1 Flash Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

6.2 BIOS Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

7 FPGA Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

7.1 FPGA Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .100

7.1.1 Blade Revision Register - 0x00 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .100

7.1.2 FPGA Major Revision Register - 0x01. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

7.1.3 FPGA Minor Revision Register - 0x02. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

7.1.4 FPGA Date Code Register - 0x04 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

7.1.5 FPGA Month Code Register - 0x05. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

7.1.6 FPGA Year Code Register 0x06. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

7.1.7 FPGA Reset Cause Register - 0x08 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

7.1.8 Watchdog Control Register - 0x09 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

7.1.9 Watchdog Re-trigger Register - 0x0A . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

7.1.10 Memory Write Protect Register - 0x0B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

7.1.11 Power Good Status 1 Register - 0x0C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .107

7.1.12 Power Good Status 2 Register - 0x0D . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .108

7.1.13 System Status Register - 0x0E. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

7.1.14 Misc 1 Control and Status Register - 0x10 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .109

7.1.15 Misc 2 Control and Status Register - 0x11 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .110

7.1.16 DIP Switch Status Register - 0x14 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .111

7.1.17 Misc 3 Control and Status Register - 0x15 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .112

7.1.18 Boot Control and Status 1 Register - 0x16 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .113

7.1.19 Boot Control and Status 2 Register - 0x17 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .114

7.1.20 PCIE Switch Control and Status 1 Register - 0x18 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

7.1.21 PCIE Switch Control and Status 2 Register - 0x19 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

6

iVPX7225 Installation and Use (6806800S11C)

Page 7

Contents

7.1.22 CPU Package Temperature Reading Register - 0x1C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

7.1.23 IPMC Inlet Temperature Sensor Status Register - 0x1D. . . . . . . . . . . . . . . . . . . . . . . . . . . 117

7.1.24 IPMC Outlet Temperature Sensor Status Register - 0x1E . . . . . . . . . . . . . . . . . . . . . . . . . 118

7.1.25 FRAM Page Access Register - 0x20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

7.1.26 VPX System Register - 0x24 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

7.1.27 POST Code Latch Register - 0x28 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .120

7.1.28 BIOS Boot Status Register - 0x2C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

7.2 FPGA SIO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .120

7.2.1 Super IO Configuration Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

7.2.1.1 Entering the Configuration State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

7.2.1.2 Exiting the Configuration State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .121

7.2.1.3 Configuration Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

7.2.1.4 Super IO Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

7.2.1.5 Global Control Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

7.2.1.6 Logical Device Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

7.3 UART Register Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

7.3.1 UART Registers DLAB=0. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .128

7.3.1.1 Received Buffer Register (RBR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

7.3.1.2 Transmitter Holding Register (THR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

7.3.1.3 Interrupt Enable Register (IER) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

7.3.1.4 Interrupt Identification Register (IIR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

7.3.1.5 FIFO Control Register (FCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

7.3.1.6 Line Control Register (LCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

7.3.1.7 Modem Control Register (MCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

7.3.1.8 Line Status Register (LSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .137

7.3.1.9 Modem Status Register (MSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

7.3.1.10 Scratch Register (SCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

7.3.1.11 Programmable Baud Rate Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

A Related Documentation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .146

A.1 Artesyn Embedded Technologies - Embedded Computing Documentation . . . . . . . . . . . . . . . 146

A.2 Related Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

iVPX7225 Installation and Use (6806800S11C)

7

Page 8

Contents

Contents

Contents

8

iVPX7225 Installation and Use (6806800S11C)

Page 9

List of Tables

Table 1-1 Key Features of the iVPX7225 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Table 1-2 Standard Compliances . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Table 1-3 Mechanical Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Table 1-4 Available Board Variants . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Table 1-5 Accessories . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Table 2-1 Environmental Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Table 2-2 Power Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Table 3-1 Planar LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Table 3-2 POST Code LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Table 3-3 Face Plate LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Table 3-4 P0 Connector Pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Table 3-5 P1 Connector Pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Table 3-6 P2 Connector Pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Table 3-7 XJ15 Connector Pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Table 3-8 XJ16 Connector Pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Table 3-9 S1 Switch Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Table 6-1 Flash Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Table 6-2 BIOS Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Table 7-1 Blade Revision Register - 0x00 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .100

Table 7-2 FPGA Major Revision Register - 0x01 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

Table 7-3 FPGA Minor Revision Register - 0x02 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

Table 7-4 FPGA Date Code Register - 0x04 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

Table 7-5 FPGA Month Code Register - 0x05 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

Table 7-6 FPGA Year Code Register - 0x06 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .102

Table 7-7 FPGA Reset Cause Register - 0x08 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

Table 7-8 Watchdog Control Register - 0x09 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .104

Table 7-9 Watchdog Re-trigger Register - 0x0A . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

Table 7-10 Memory Write Protect Register - 0x0B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .105

Table 7-11 Power Good Status 1 Register - 0x0C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .107

Table 7-12 Power Good Status 2 Register - 0x0D . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .108

Table 7-13 System Status Register - 0x0E . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

Table 7-14 Misc 1 Control and Status Register - 0x10 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .109

Table 7-15 Misc 2 Control and Status Register - 0x11 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .110

Table 7-16 DIP Switch Status Register - 0x14 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

Table 7-17 Misc 3 Control and Status Register - 0x15 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .112

Table 7-18 Boot Control and Status 1 Register - 0x16 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .113

iVPX7225 Installation and Use (6806800S11C)

9

Page 10

List of Tables

Table 7-19 Boot Control and Status 2 Register - 0x17 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .114

Table 7-20 PCIE Switch Control and Status 1 Register - 0x18 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .115

Table 7-21 PCIE Switch Control and Status 2 Register - 0x19 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .116

Table 7-22 CPU Package Temperature Reading Register - 0x1C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .117

Table 7-23 IPMC Inlet Temperature Sensor Status Register - 0x1D . . . . . . . . . . . . . . . . . . . . . . . . . . . . .117

Table 7-24 IPMC Outlet Temperature Sensor Status Register - 0x1E . . . . . . . . . . . . . . . . . . . . . . . . . . . .118

Table 7-25 FRAM Page Access Register - 0x20 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .118

Table 7-26 VPX System Register - 0x24 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .119

Table 7-27 POST Code Latch Register - 0x28 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .120

Table 7-28 BIOS Boot Status Register - 0x2C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .120

Table 7-29 Super IO Configuration Index Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .121

Table 7-30 Super IO Configuration Data Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .121

Table 7-31 Global Configuration Register Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .122

Table 7-32 Super IO Logical Device Number Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .123

Table 7-33 Super IO Device Identification Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .123

Table 7-34 Super IO Device Revision Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .123

Table 7-35 Super IO LPC Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .124

Table 7-36 Global Super IO SERIRQ and Pre-divide Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . .124

Table 7-37 Logical Device Configuration Register Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .125

Table 7-38 Logical Device Enable Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .125

Table 7-41 Logical Device Common Decode Ranges . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .126

Table 7-39 Logical Device Base IO Address MSB Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .126

Table 7-40 Logical Device Base IO Address LSB Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .126

Table 7-42 Logical Device Primary Interrupt Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .127

Table 7-43 UART Register Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .128

Table 7-44 Receiver Buffer Register (RBR) if DLAB=0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .129

Table 7-45 Transmitter Holding Register (THR) if DLAB=0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .129

Table 7-46 Interrupt Enable Register (IER), if DLAB=0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .130

Table 7-47 UART Interrupt Priorities2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .131

Table 7-48 Interrupt Identification Register (IIR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .131

Table 7-49 Interrupt Identification Register Decode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .132

Table 7-50 FIFO Control Register (FCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .133

Table 7-51 Line Control Register (LCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .134

Table 7-52 Modem Control Register (MCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .136

Table 7-53 Line Status Register (LSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .138

Table 7-54 Modem Status Register (MSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .142

10

iVPX7225 Installation and Use (6806800S11C)

Page 11

List of Tables

Table 7-55 Scratch Register (LCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

Table 7-56 Divisor Latch LSB Register (DLL), if DLAB=1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

Table 7-57 Divisor Latch MSB Register (DLM), if DLAB=1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

Table 7-58 Logical Device 0x74 Reserved Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

Table 7-59 Logical Device 0x75 Reserved Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

Table 7-60 Logical Device 0xF0 Reserved Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

Table A-1 Artesyn Embedded Technologies - Embedded Computing Publications . . . . . . . . . . . . . . 146

Table A-2 Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

iVPX7225 Installation and Use (6806800S11C)

11

Page 12

List of Tables

12

iVPX7225 Installation and Use (6806800S11C)

Page 13

List of Figures

Figure 1-1 iVPX7225 Air Cooled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Figure 1-2 iVPX7225 Conduction Cooled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Figure 1-3 Serial Number Label Location . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Figure 3-1 Main Board Components (Top View) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Figure 3-2 Main Board Components (Bottom View) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Figure 3-3 Air Cooled Front Panel Connectors and LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Figure 3-4 Conduction Cooled Front Panel Connectors and LEDs . . . . . . . . . . . . . . . . . . . . . . . . 40

Figure 3-5 DIP Switch Location . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Figure 4-1 iVPX7225 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Figure 4-2 SLT3-PAY-2F2U-14.2.3 Slot Profile . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Figure 4-3 SLT3-PAY-1F1F2U-14.2.4 Slot Profile . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Figure 5-1 Main Menu . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Figure 5-2 Boot Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Figure 5-3 Advanced Menu . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Figure 5-4 Processor Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Figure 5-5 Processor Power Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Figure 5-6 HDD Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Figure 5-7 Memory Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

Figure 5-8 System Agent (SA) Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Figure 5-9 Graphics Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

Figure 5-10 IGD Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

Figure 5-11 PEG Port Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Figure 5-12 South Bridge Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Figure 5-13 SB USB Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

Figure 5-14 SB Security Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Figure 5-15 Network Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

Figure 5-16 SIO Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

Figure 5-17 ME Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Figure 5-18 Thermal Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

Figure 5-19 Platform Thermal Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Figure 5-20 Intel® Rapid Start Technology . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

Figure 5-21 iVPX7225 Menu . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

Figure 5-22 Security Menu . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

Figure 5-23 TPM Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

Figure 5-24 Boot Menu . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

Figure 5-25 Exit Menu . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

iVPX7225 Installation and Use (6806800S11C)

13

Page 14

List of Figures

14

iVPX7225 Installation and Use (6806800S11C)

Page 15

About this Manual

Overview of Contents

This manual is divided into the following chapters and appendices.

Safety Notes on page 23 summarizes the safety instructions in the manual.

Sicherheitshinweise on page 8 is a German translation of the Safety Notes chapter.

Chapter 1, Introduction gives an overview of the features of the product, standard

compliances, mechanical data, and ordering information.

Chapter 2, Hardware Preparation and Installation outlines the installation requirements,

hardware accessories, switch settings, and installation procedures.

Chapter 3, Controls, LEDs and Connectors describes external interfaces of the board. This

includes connectors and LEDs.

Chapter 4, Functional Description includes a block diagram and functional description of

major components of the product.

Chapter 5, BIOS provides information on the BIOS Setup Utility.

Chapter 6, Maps and Registers provides information on the product’s memory maps.

Chapter 7, FPGA Registers provides information about the FPGA registers.

Appendix A, Related Documentation provides a listing of related product documentation,

manufacturer’s documents, and industry standard specifications.

Abbreviations

This document uses the following abbreviations:

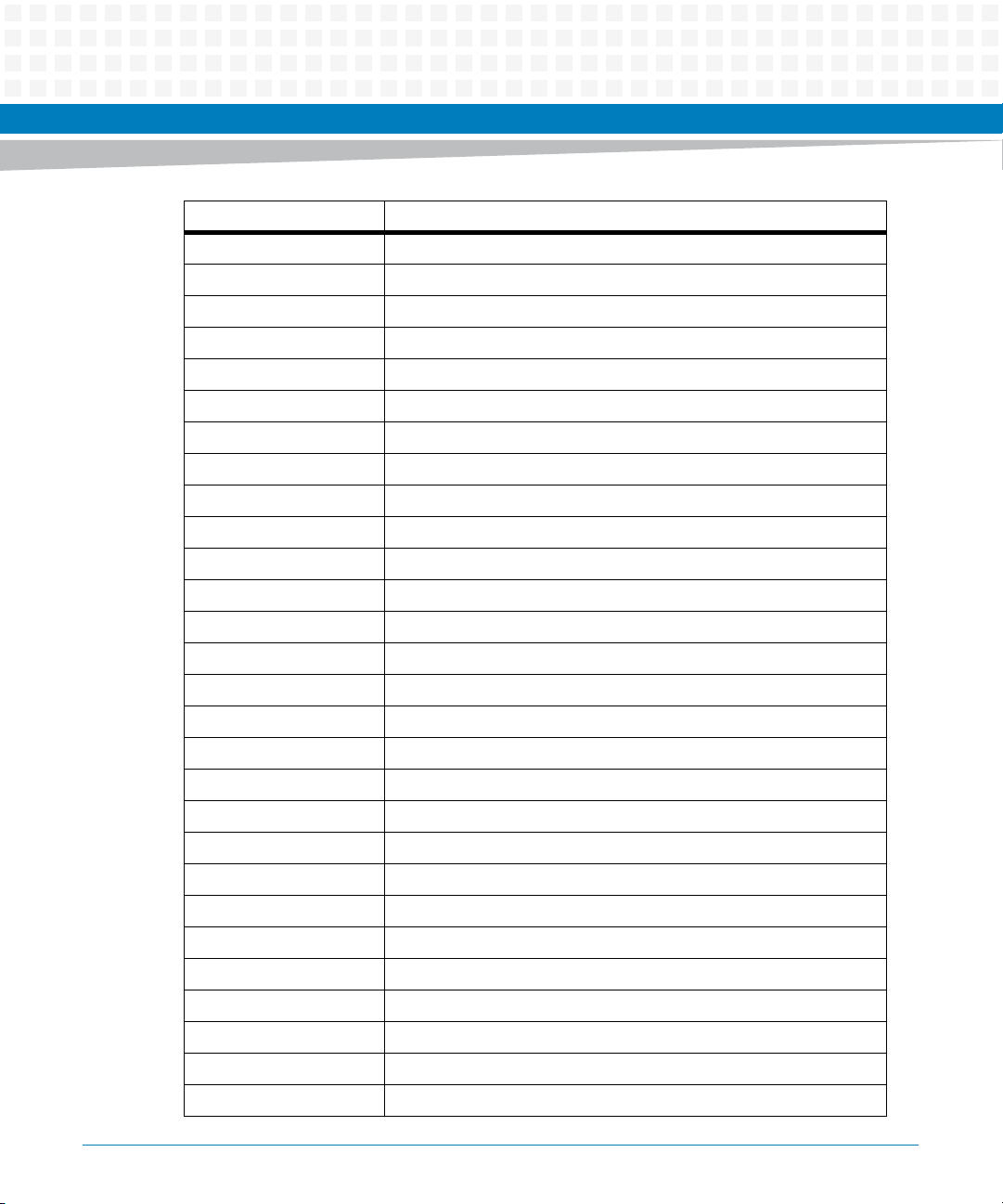

Abbreviation Description

# Indication for LOW active signals

2LM Two-Level Maintenance

BIOS Basic Input/Output System

BOM Bill of Material

CFM Cubic Feet per Minute

COM Serial V.24 / V.28 compliant interface

iVPX7225 Installation and Use (6806800S11C)

15

Page 16

About this Manual

Abbreviation Description

CRT Cathode Ray Tube

DDR Double Data Rate

DDR3 Double Data Rate 3 SDRAM is the name of the new DDR memory

DMI Direct Media Interface - Extension of the standard PCI Express

DP DisplayPort

DRAM Dynamic Random Access Memory

DVI Digital Visual Interface

ECC Error Correction Code

EMC Electro-magnetic Compatibility

EMI Electro-magnetic Interference

About this Manual

standard that is being developed as the successor to DDR2 SDRAM.

specification with special commands/features added to mimic the

legacy Hub Interface, DC coupled

ENP2 Artesyn's ENP2 Ruggedization Level

ENP4 Artesyn's ENP4 Ruggedization Level

ESD Electro-static Discharge

FPGA Field Programmable Gate Array

FSB Front-side Bus

FW Firmware

FWH Firmware Hub

Gb Gigabit(s)

GbE Gigabit Ethernet

Gb/s Gigabits per second

Gbps Gigabits per second

Gen1 PCI Express Generation 1 supporting 2.5 GT/s

Gen2 PCI Express Generation 2 supporting 5.0 GT/s

GHz Gigahertz

GPIO General Purpose Input/Output

GT/s Gigatransfers per second

16

iVPX7225 Installation and Use (6806800S11C)

Page 17

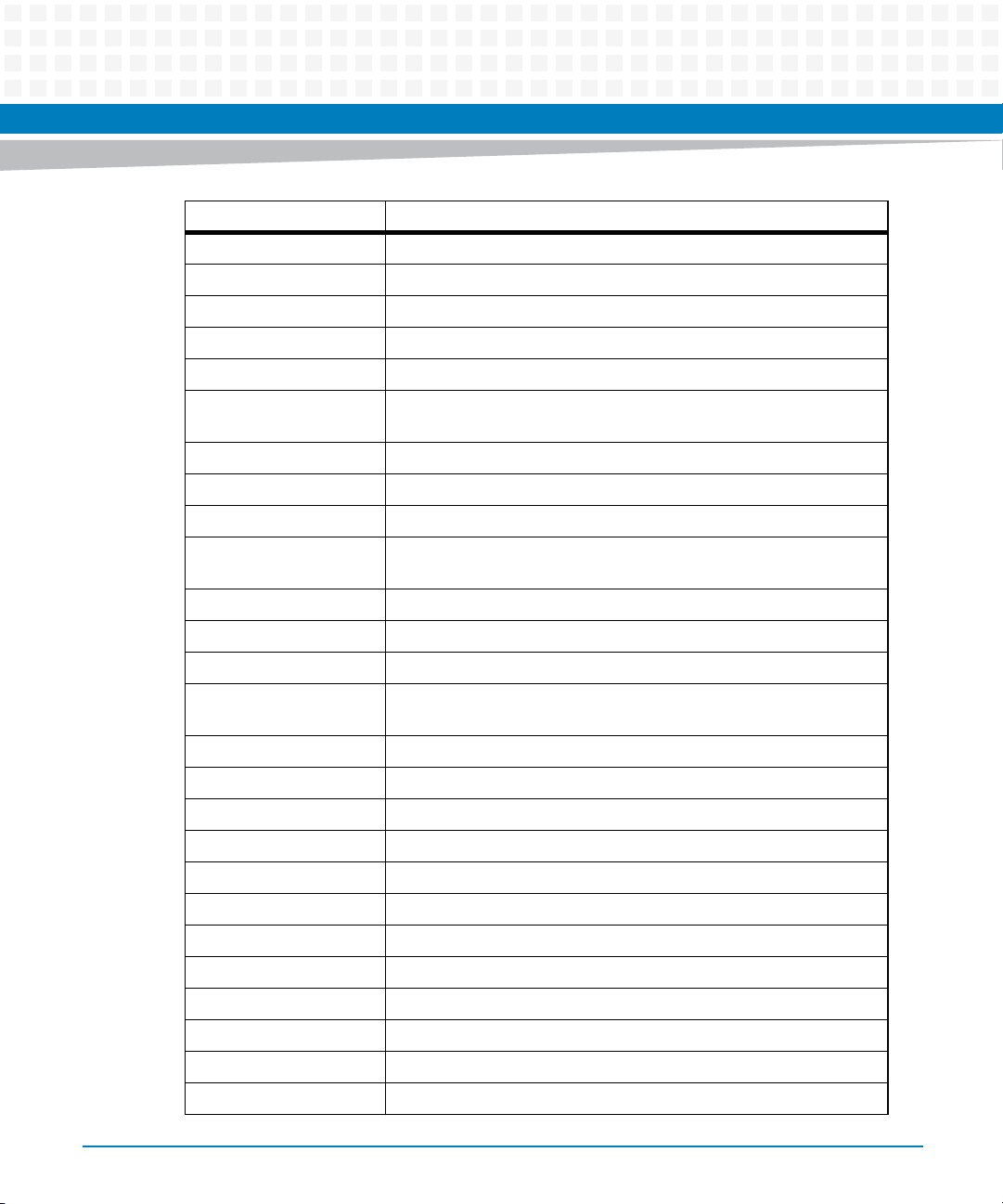

About this Manual

Abbreviation Description

HD High Definition

HDMI High-Definition Multimedia Interface

I2C Inter Integrated-Circuit Bus (2-wire serial bus and protocol)

ICT In-circuit Test

IF Interface

IPMC Intelligent Platform Management Controller

Kb Kilobits(s)

L2 Cache Level 2 Cache

L3 Cache Level 3 Cache

LAN Local Area Network

LFM Linear Feet per Minute

LPC Low Pin Count

LV Low Version

LVDS Low Voltage Differential Signaling

MAC Medium Access Controller

Mb Megabit(s)

Mbl Mobile Processor

MB Megabyte(s)

Mbps Megabits per second

ME Management Engine

MHz Megahertz

N/A Not Applicable

NAND Not AND

NEBS Network Equipment Building System

NMI Non-maskable Interrupt

NVRAM Non-volatile Random Access Memory

OEM Original Equipment Manufacturer

PCB Printed Circuit Board

iVPX7225 Installation and Use (6806800S11C)

17

Page 18

About this Manual

Abbreviation Description

PCH Platform Controller Hub

PCIE PCI-Express

PHY Physical layer device (e.g. for Ethernet)

RGB Red, Green, Blue

RoHS Restriction of Hazardous Substances

RS232 Recommended Standard 232C - interface standard for serial

RTC Real-Time Clock

Rx Receive line (of a duplex serial communication interface)

SAS Serial Attached SCSI

SATA Serial AT Attachment (high-speed serial interface standard for

About this Manual

communication

storage devices)

SDRAM Synchronous Dynamic Random Access Memory

SDVO Serial Digital Video Out

SerDes Serializer / Deserializer

SKU Stock Keeping Unit - A unique identifier for a distinct product variant

that can be ordered

SLC Single-level Cell

SMBus System Management Bus

SMI System Management Interrupt

SPD Serial Presence Detect

SPI Serial Peripheral Interface

TBD To be defined

TDP Thermal Design Power

TPM Trusted Platform Module

Tx Transmit line (of a duplex serial communication interface)

UART Universal Asynchronous Receiver-Transmitter

VID Voltage Identification (for Intel CPUs)

VPD Vendor Product Data

18

iVPX7225 Installation and Use (6806800S11C)

Page 19

Abbreviation Description

VT Intel® Virtualization Technology - A set of hardware enhancements

XCVR Transceiver

XDP Run-control Debug Port

XMC Switched Mezzanine Card

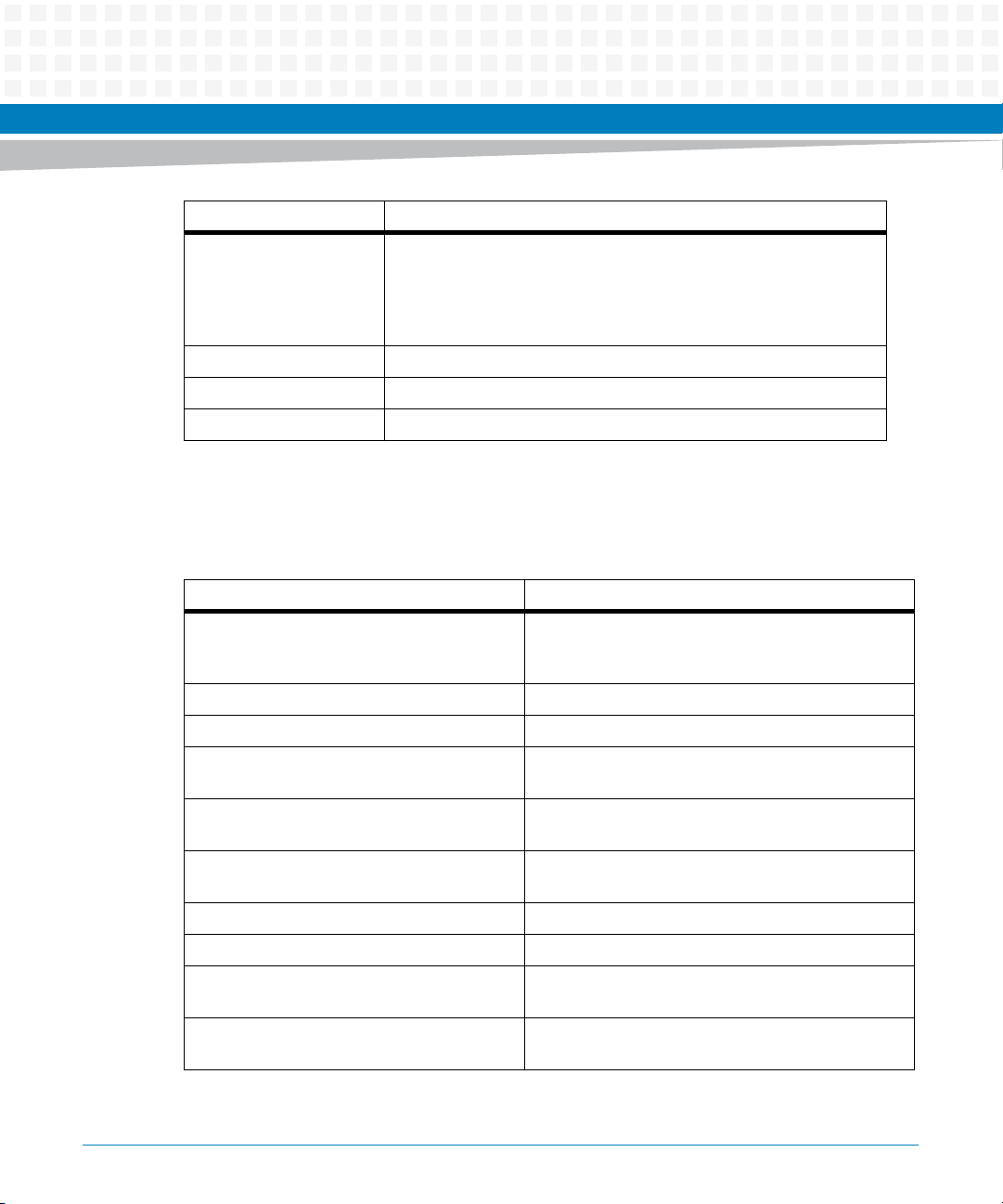

Conventions

The following table describes the conventions used throughout this manual.

About this Manual

to Intel server and client platforms that can improve virtualization

solutions. VT provides a foundation for widely-deployed

virtualization solutions and enables more robust hardware assisted

virtualization solution.

Notation Description

0x00000000 Typical notation for hexadecimal numbers (digits are

0 through F), for example used for addresses and

offsets

0b0000 Same for binary numbers (digits are 0 and 1)

bold Used to emphasize a word

Screen Used for on-screen output and code related elements

or commands in body text

Courier + Bold Used to characterize user input and to separate it

from system output

Reference Used for references and for table and figure

descriptions

File > Exit Notation for selecting a submenu

<text> Notation for variables and keys

[text] Notation for software buttons to click on the screen

and parameter description

... Repeated item for example node 1, node 2, ..., node

12

iVPX7225 Installation and Use (6806800S11C)

19

Page 20

About this Manual

Notation Description

About this Manual

.

.

.

.. Ranges, for example: 0..4 means one of the integers

| Logical OR

Omission of information from example/command

that is not necessary at the time being

0,1,2,3, and 4 (used in registers)

Indicates a hazardous situation which, if not avoided,

could result in death or serious injury

Indicates a hazardous situation which, if not avoided,

may result in minor or moderate injury

Indicates a property damage message

No danger encountered. Pay attention to important

information

20

iVPX7225 Installation and Use (6806800S11C)

Page 21

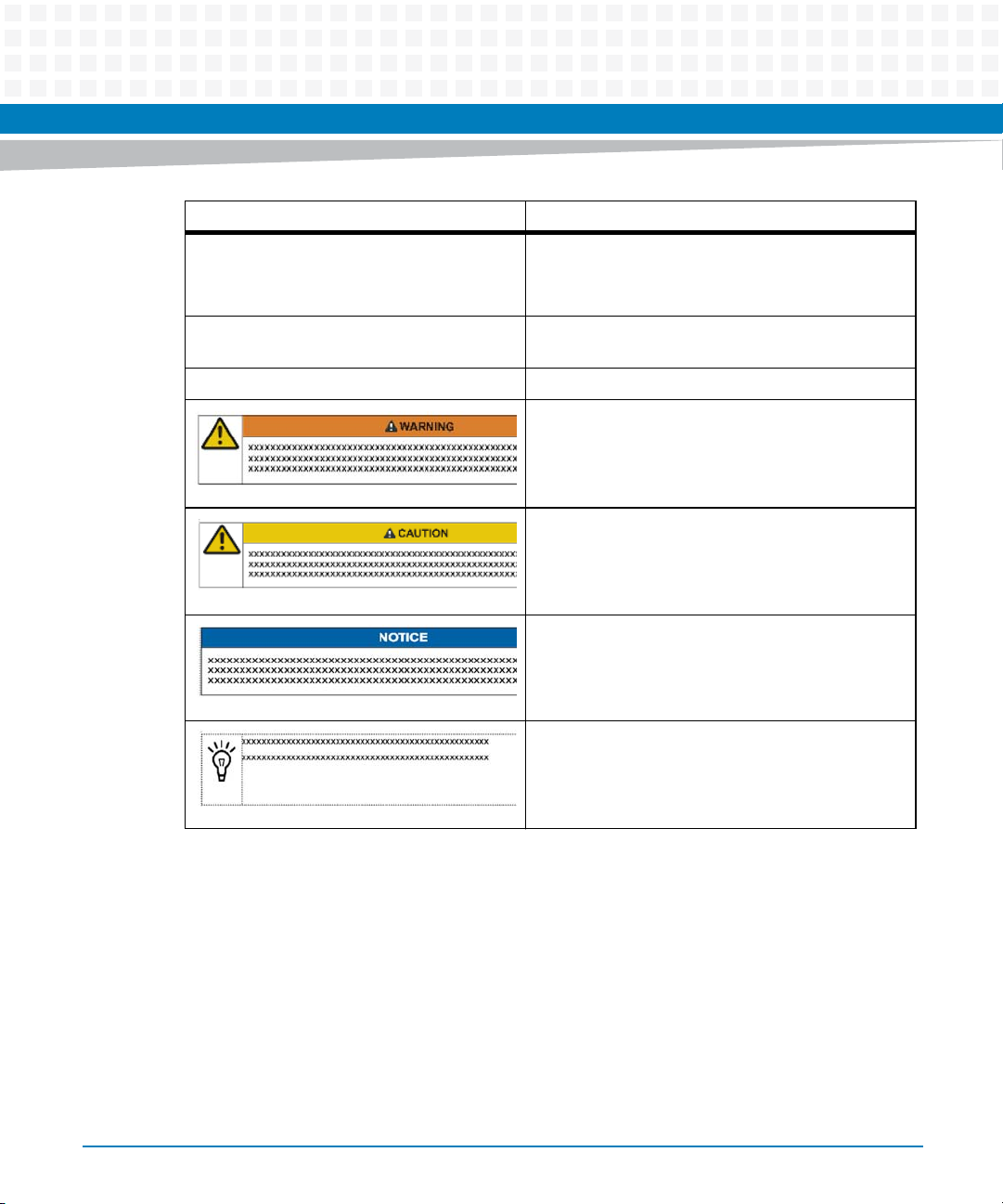

Summary of Changes

This manual has been revised and replaces all prior editions.

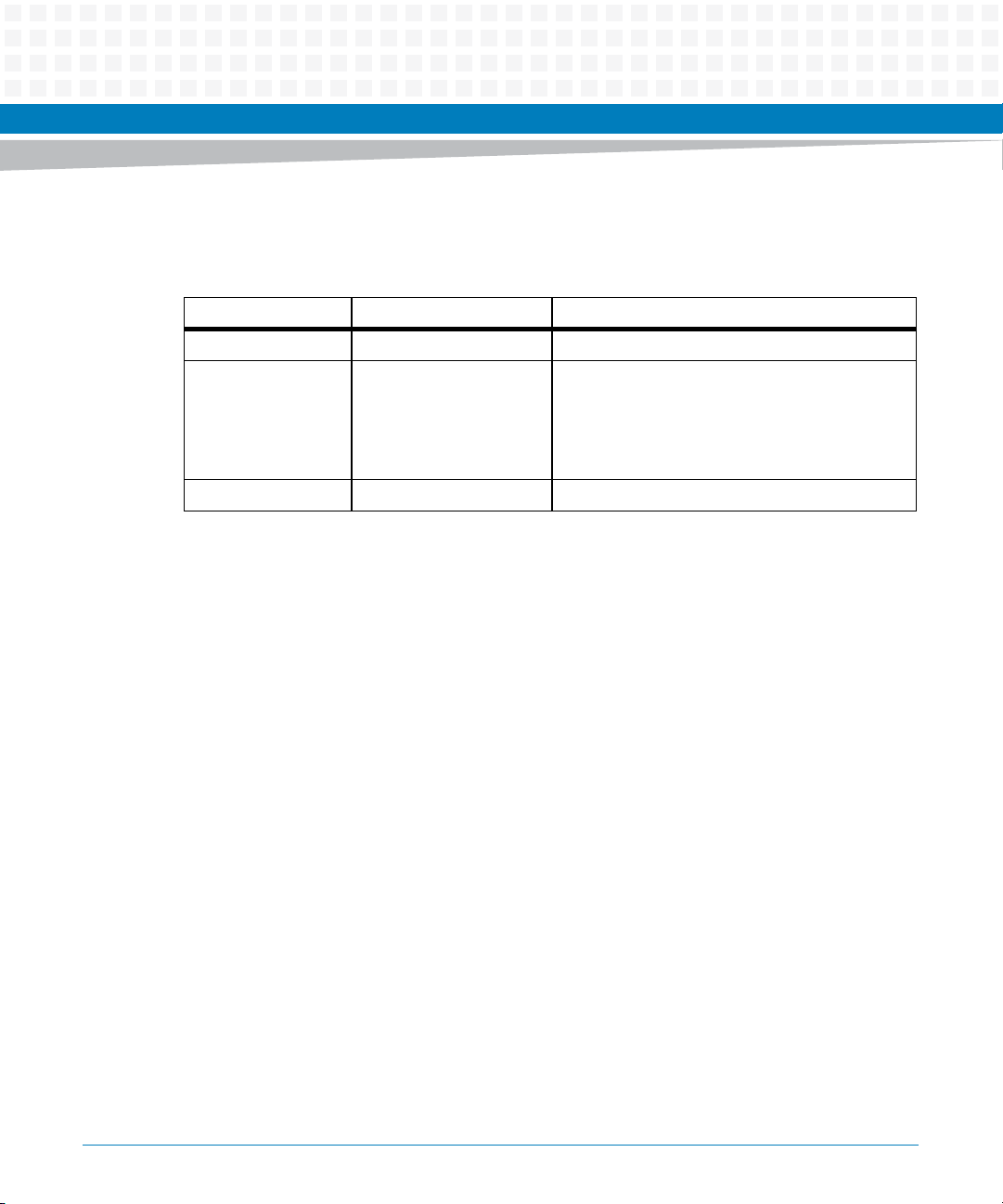

Part Number Publication Date Description

6806800S11A September 2013 Initial version

6806800S11B November 2013 Updated Table 3-4, Table 3-5, Table 3-6, Table

6806800S11C April 2015 Rebranded to Artesyn.

About this Manual

3-7, and Table 3-8 in Chapter 3, Controls, LEDs and

Connectors.

Updated Table 2-2 on page 23. Updated Figure

4-1 on page 50.

iVPX7225 Installation and Use (6806800S11C)

21

Page 22

About this Manual

About this Manual

22

iVPX7225 Installation and Use (6806800S11C)

Page 23

Safety Notes

This section provides warnings that precede potentially dangerous procedures throughout

this manual. Instructions contained in the warnings must be followed during all phases of

operation, service, and repair of this equipment. You should also employ all other safety

precautions necessary for the operation of the equipment in your operating environment.

Failure to comply with these precautions or with specific warnings elsewhere in this manual

could result in personal injury or damage to the equipment.

Artesyn Embedded Technologies intends to provide all necessary information to install and

handle the product in this manual. Because of the complexity of this product and its various

uses, we do not guarantee that the given information is complete. If you need additional

information, ask your Artesyn Embedded Technologies representative.

This product is a Safety Extra Low Voltage (SELV) device designed to meet the EN60950-1

requirements for Information Technology Equipment. The use of the product in any other

application may require safety evaluation specific to that application.

Only personnel trained by Artesyn Embedded Technologies or persons qualified in electronics

or electrical engineering are authorized to install, remove or maintain the product. The

information given in this manual is meant to complete the knowledge of a specialist and must

not be used as replacement for qualified personnel.

Keep away from live circuits inside the equipment. Operating personnel must not remove

equipment covers. Only factory authorized service personnel or other qualified service

personnel is allowed to remove equipment covers for internal subassembly or component

replacement or any internal adjustment.

Do not install substitute parts or perform any unauthorized modification of the equipment or

the warranty may be voided. Contact your local Artesyn representative for service and repair

to make sure that all safety features are maintained.

Artesyn and our suppliers take significant steps to make sure that there are no bent pins on the

backplane or connector damage to the boards prior to leaving the factory. Bent pins caused by

improper installation or by inserting boards with damaged connectors could void the Artesyn

warranty for the backplane or boards.

Use extreme caution when handling, testing, and adjusting this equipment and its

components around dangerous voltages that can cause injury or death.

iVPX7225 Installation and Use (6806800S11C)

23

Page 24

Safety Notes

System Installation

Damage of Circuits

Electrostatic discharge and incorrect installation and removal of the product can damage

circuits or shorten their life.

Before touching the product make sure that your are working in an ESD-safe environment or

wear an ESD wrist strap or ESD shoes. Hold the product by its edges and do not touch any

components or circuits.

Pin Damage

Forcing the module into the system may damage connector pins.

If the module hangs during insertion, pull it out and insert it again.

Damage of the Product and Additional Devices and Modules

Incorrect installation or removal of additional devices or modules damages the product or the

additional devices or modules.

Before installing or removing additional devices or modules, read the respective

documentation and use appropriate tools.

Operation

System Damage

During the course of handling, shipping, and assembly, pins, mounting screws, fans and other

items can become loose or damaged.

Do not operate a damaged shelf, this can cause damage to devices that interact with it.

System Overheating

Cooling Vents

Improper cooling can lead to blade and system damage and can void the manufacturer’s

warranty.

Always operate the blade in a configuration suitable for proper cooling. Do not obstruct the

ventilation of the system. Keep any fresh air intakes of the system enclosure completely clear.

Ensure that any fresh air supply is not mixed with hot exhaust from other devices. Ensure that

all system slots are populated with either blades, filler blades, or dummy blades.

24

iVPX7225 Installation and Use (6806800S11C)

Page 25

Product Damage

High humidity and condensation on surfaces cause short circuits.

Do not operate the product outside the specified environmental limits. Make sure the product

is completely dry and there is no moisture on any surface before applying power.

Expansion and FRU Replacement

Product Damage

Bent pins or loose components can cause damage to the product, the backplane, or other

system components.

Carefully inspect the product and the backplane for both pin and component integrity before

installation.

Personal Injury

During operation, hot surfaces may be present on the heat sinks and components of the

product.

To prevent injury from hot surfaces do not touch any of the exposed components or heat sinks

on the product when handling. Use the handle and face plate when removing the product

from the enclosure.

Safety Notes

External Battery or Super Capacitor

Data Loss

If the external battery (or super capacitor) does not provide enough power anymore, the RTC

is initialized and the data in the NVRAM is lost.

Data Loss

Exchanging the battery (or super capacitor) always results in data loss of the devices which use

the battery as power backup.

Back up affected data before exchanging the battery (or super capacitor).

iVPX7225 Installation and Use (6806800S11C)

25

Page 26

Safety Notes

Environment

Environmental Damage

Improperly disposing of used products may harm the environment.

Always dispose of used products according to your country’s legislation and manufacturer’s

instructions.

26

iVPX7225 Installation and Use (6806800S11C)

Page 27

Sicherheitshinweise

Dieses Kapitel enthält Hinweise, die potentiell gefährlichen Prozeduren innerhalb dieses

Handbuchs vorrangestellt sind. Beachten Sie unbedingt in allen Phasen des Betriebs, der

Wartung und der Reparatur des Systems die Anweisungen, die diesen Hinweisen enthalten

sind. Sie sollten außerdem alle anderen Vorsichtsmaßnahmen treffen, die für den Betrieb des

Systems innerhalb Ihrer Betriebsumgebung notwendig sind. Wenn Sie diese

Vorsichtsmaßnahmen oder Sicherheitshinweise, die an anderer Stelle diese Handbuchs

enthalten sind, nicht beachten, kann das Verletzungen oder Schäden am System zur Folge

haben.

Artesyn Embedded Technologies ist darauf bedacht, alle notwendigen Informationen zum

Einbau und zum Umgang mit dem System in diesem Handbuch bereit zu stellen. Da es sich

jedoch bei dem System um ein komplexes Produkt mit vielfältigen Einsatzmöglichkeiten

handelt, können wir die Vollständigkeit der im Handbuch enthaltenen Informationen nicht

garantieren. Falls Sie weitere Informationen benötigen sollten, wenden Sie sich bitte an die für

Sie zuständige Geschäftsstelle von Artesyn Embedded Technologies.

Das Produkt wurde entwickelt, um die Sicherheitsanforderungen für SELV Geräte nach der

Norm EN 60950-1 für informationstechnische Einrichtungen zu erfüllen. Die Verwendung des

Produkts in einer anderen Anwendung erfordert eine Sicherheitsüberprüfung für diese

spezifische Anwendung.

Einbau, Wartung und Betrieb dürfen nur von durch Artesyn Embedded Technologies

ausgebildetem oder im Bereich Elektronik oder Elektrotechnik qualifiziertem Personal

durchgeführt werden. Die in diesem Handbuch enthaltenen Informationen dienen

ausschließlich dazu, das Wissen von Fachpersonal zu ergänzen, können dieses jedoch nicht

ersetzen.

Halten Sie sich von stromführenden Leitungen innerhalb des Systems fern. Entfernen Sie auf

keinen Fall die Systemabdeckung. Nur werksseitig zugelassenes Wartungspersonal oder

anderweitig qualifiziertes Wartungspersonal darf die Systemabdeckung entfernen, um

Systemkomponenten zu ersetzen oder andere Anpassungen vorzunehmen.

Installieren Sie keine Ersatzteile oder führen Sie keine unerlaubten Veränderungen am System

durch, sonst verfällt die Garantie. Wenden Sie sich für Wartung oder Reparatur bitte an die für

Sie zuständige Geschäftsstelle von Artesyn Embedded Technologies. So stellen Sie sicher, dass

alle sicherheitsrelevanten Aspekte beachtet werden.

Gehen Sie mit äußerster Vorsicht vor, bei der Handhabung, Prüfung und Einstellung dieser

Anlagen und deren Komponenten bezueglich gefährliche Spannungen, die zu Verletzungen

oder zum Tod führen koennen.

iVPX7225 Installation and Use (6806800S11C)

8

Page 28

Sicherheitshinweise

System Installation

Beschädigung von Schaltkreisen

Elektrostatische Entladung und unsachgemäßer Ein- und Ausbau des Produktes kann

Schaltkreise beschädigen oder ihre Lebensdauer verkürzen.

Bevor Sie das Produkt oder elektronische Komponenten berühren, vergewissern Sie sich, daß

Sie in einem ESD-geschützten Bereich arbeiten.

Schäden an Steckern

Wenn Sie das Modul mit Gewalt installieren, können die Anschlussstifte in den Steckern

beschädigt werden.

Falls sich das Modul während der Installation verkantet, ziehen Sie es wieder heraus und führen

Sie sie erneut ein.

Beschädigung des Produktes und der Zusatzmodule

Fehlerhafter Ein- oder Ausbau von Zusatzmodulen führt zu Beschädigung des Produktes oder

der Zusatzmodule.

Lesen Sie deshalb vor dem Ein- oder Ausbau von Zusatzmodulen die Dokumentation und

benutzen Sie angemessenes Werkzeug.

Betrieb

Beschädigung des Systems

Während des Transportes, Zusammenbaus und dem Umgang mit dem System können sich

Schrauben, Lüfter oder andere Teile lösen oder beschädigt werden.

Nehmen Sie ein beschädigtes System nicht in Betrieb. Sonst können andere Einrichtungen, die

mit dem System kommunizieren, beschädigt werden.

Überhitzung des Systems

Lüftungsöffnungen

9

iVPX7225 Installation and Use (6806800S11C)

Page 29

Unzureichende Lüftung kann Schäden an Blades und am System verursachen und die

Herstellergarantie ungültig werden lassen.

Arbeiten mit dem Baord sollten immer in einer eigens gekuehlten und konfigurierten

Umgebung erfolgen. Behindern Sie nicht die Belüftung des Systems. Achten Sie darauf, dass

alle Luftzugaenge des Systems komplett frei sind. Stellen Sie sicher, dass die zufuehrende Luft

nicht mit heissen Gasen von andered Geraeten vermischt wird. Stellen Sie ausserdem sicher,

das alle Steckplaetze im System entweder mit Boards, Filler blades oder Dummy Boards belegt

sind.

Beschädigung des Systems

Hohe Luftfeuchtigkeit und Kondensat auf den Oberflächen der Produkte kann zu

Kurzschlüssen führen.

Betreiben Sie die Produkte nur innerhalb der angegebenen Grenzwerte für die relative

Luftfeuchtigkeit und Temperatur und stellen Sie vor dem Einschalten des Stroms sicher, dass

sich auf den Produkten kein Kondensat befindet.

Sicherheitshinweise

Erweiterung und FRU Austausch

Beschädigung des Produktes

Verbogene Stecker oder lose Teile können das Produkt, die Backplane oder andere

Systemkomponenten beschädigen.

Prüfen Sie das Produkt und die Backplane vor dem Einabau sorgfältig auf verbogene Stecker

und lose Teile.

Verletzungsgefahr

Während des Betriebs können Oberflächen an den Kühlkörpern oder anderen Komponenten

sehr heiß werden.

Um Verletzungen durch Verbrennung zu vermeiden, berühren Sie während der Arbeit keine

Komponenten oder Kühlkörper auf dem Produkt. Fassen Sie das Produkt an den Handles und

der Frontblende an, wenn Sie es aus dem System herausnehmen.

iVPX7225 Installation and Use (6806800S11C)

10

Page 30

Sicherheitshinweise

Externe Batterie or Super-Kondensator

Datenverlust

Wenn die externe Batterie (oder super Kondensator) nicht mehr genug Energie zur

Verfuegung stellen, wird der RTC initializierd und die Daten in der PCH Batterie-backed RAM

sind verloren. Das kommt auch vor, jedesmal wenn das Board aus dem System entfernd wird,

und/oder wenn das System kein VBAT zur Verfuegung stellt, und das RTM ist nicht installiert.

Datenverlust

Austausch der Batterie (oder super Kondensator) verursacht immer einen Datenverlust der

Komponente, die diese Batterie als Engergie Backup benutzen.

Daten sollten gesichert werden, bevor die Batterie (oder super Kondensator) ausgetauscht

wird.

Environment

Umweltverschmutzung

Falsche Entsorgung der Produkte schadet der Umwelt.

Entsorgen Sie alte Produkte gemäß der in Ihrem Land gültigen Gesetzgebung und den

Empfehlungen des Herstellers.

11

iVPX7225 Installation and Use (6806800S11C)

Page 31

Introduction

1.1 Features

The 3U iVPX7225 features the dual-core 3rd generation 2.5 GHz Intel Core I7-3555LE Mobile

Processor with integrated graphics and memory controller and the mobile Intel QM77 PCH

chipset with leading edge I/O functionality. This high compute density platform offers both

high speed fabric connectivity with PCI Express and Gigabit Ethernet control plane

connectivity with data transfer rates up to 5Gbps. On board memory includes 8GB DDR3L1600 memory, 4GB embedded USB flash, and 1MB non-volatile Ferroelectric Random Access

Memory (FRAM). Additional connectivity includes three USB 2.0 ports, two serial ports, three

SATA ports, eight GPIO, Display Port, VGA and one XMC site for maximum flexibility.

Table 1-1 Key Features of the iVPX7225

Features Description

Processor Dual-core 3rd generation Intel Core i7-3555LE, 2.50 GHz, 4MB

Chapter 1

Intel Smart Cache, 25 W (TDP)

Dual Channel DDR3/3L-1333/1600 memory controller

One x16 Gen2 PEG port (Bifurcated to support x8 capable

XMC Site and VPX PCIe data plane).

Chipset Intel QM77 PCH

iVPX7225 Installation and Use (6806800S11C)

Eight PCI Express root controllers and 8 lanes Gen2 PCIe (max.

5.0 GT/s; Utilization: 1x4 port routed to GigE controller)

Six SATA Controllers (Utilization: 3 routed to the backplane,

one routed to the XMC Site

14 USB 2.0 host controllers (Utilization: 3 rear USB, 1

embedded USB Flash Controller)

Three digital displays (DP/eDP/HDMI/DVI/

sDVO; Utilization: One (1) DP port (DDPD) routed to

backplane)

One analog display (CRT/VGA)

SPI interface (2 CS#)

LPC interface

SMBus

Programmable interrupt controller, watchdog timer,

real-time clock

Gigabit Ethernet Controller 10/100/1000BASE-T (unused)

12

Page 32

Introduction

Table 1-1 Key Features of the iVPX7225

Features Description

Memory Soldered down 8GB dual-channel DDR3L-1600 memory

(4GB/Channel) with ECC

User Flash/ NVRAM Memory

Boot Flash Memory Redundant UEFI BIOS in dual 8MB SPI flash devices

Backplane I/O Two 1000BASE-BX/KX Ethernet (Ultra Thin Pipe control plane)

Front Panel I/O Air cooled

4GB embedded USB flash

1 MB FRAM (NVRAM)

Two PCIe x4 Gen2 (Fat Pipe data plane)

– Either PCIe port may be configured to support Non-

Transparent bridging (one NT port max)

One DisplayPort

One VGA

Three USB 2.0

Three SATA (2x Gen3, 1x Gen2)

Two RS-232/RS-422/RS-485

Eight PCH GPIO

VITA 46.9 XMC IO Pattern X12d support

SMBus

IPMC I2C

Selective Non-Volatile Memory R/W Overrides

RTM control signals

– XMC Front I/O

– Reset switch

– Status LEDs

Conduction cooled

– Reset switch

– Status LEDs

13

Ethernet Controllers Intel 82580 Ethernet Controller (Ethernet control plane)

Optional Transition Modules

Mini DisplayPort, VGA, USB 2.0, Ethernet, Serial, I2C,

GPIO, SATA, XMC IO, write protect override switches

iVPX7225 Installation and Use (6806800S11C)

Page 33

Table 1-1 Key Features of the iVPX7225

Features Description

Other Features FPGA Watchdog Timer

Trusted Platform Module (TPM)

Intel vPro Technology capable (supports Intel TXT, VT, and

TPM)

VITA 46.11 system management IPMI V1.5 compliant

Multiple 32-bit timers

Temperature sensors

Status and user LEDs

Reset switch

Locking ejector handles

Configuration DIP switch

Reset switch

XMC site (Gen 2 PCIe support; also provisioned for SATA sup-

port)

Introduction

BIOS UEFI BIOS

IPMC Designed for Draft 0.8 of VITA 46.11 system management for VPX

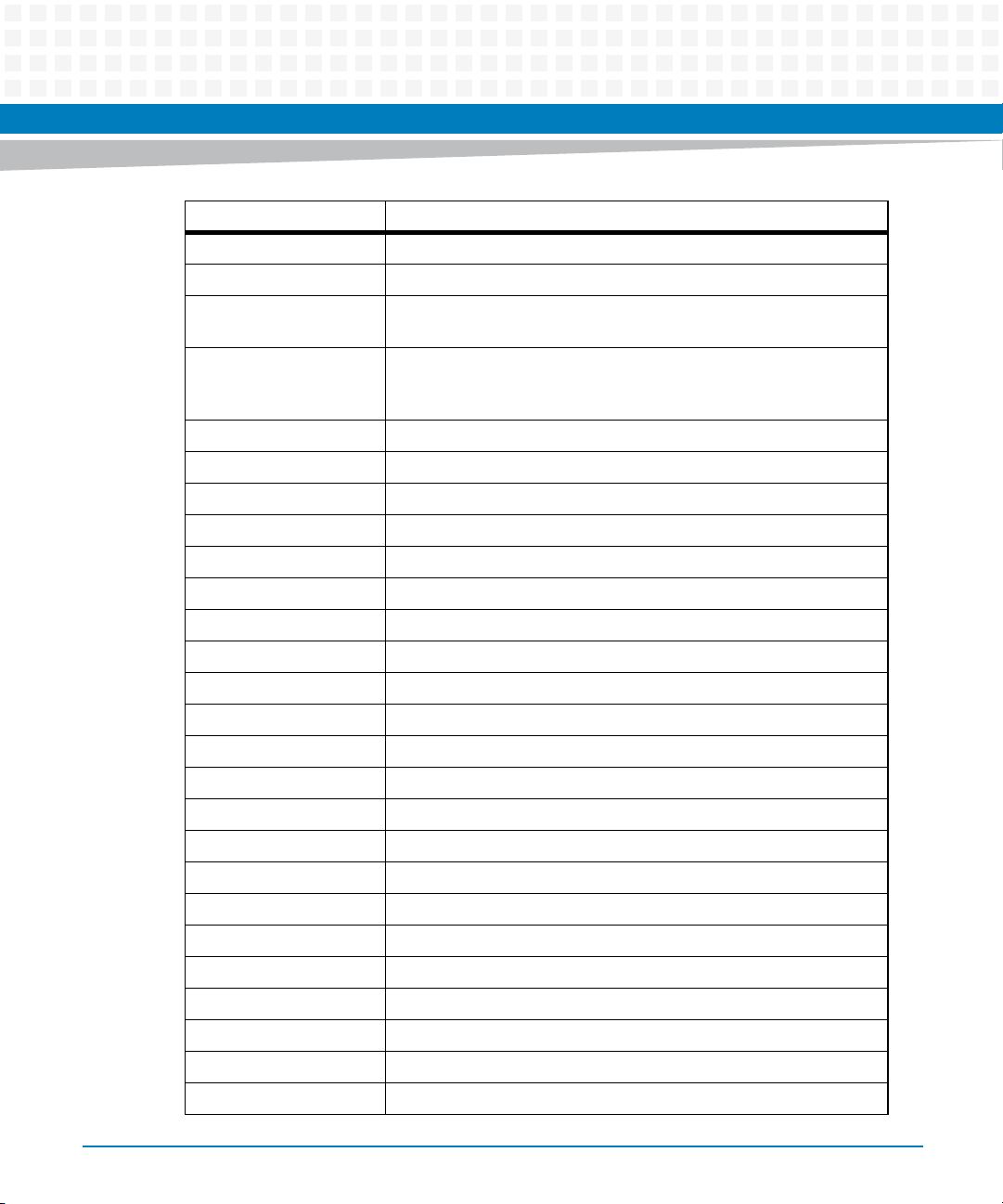

1.2 Standard Compliances

The following table details the Standard Compliance information.

Table 1-2 Standard Compliances

Standard Description

FCC 47 CFR Part 15, Subpart B (US), Class A EMC requirements

ICES-003, Class A (non-residential)

VCCI CLASS A (Japan)

EN55022 Class A

EN55024

AS/NZS CISPR 22, Class A

iVPX7225 Installation and Use (6806800S11C)

14

Page 34

Introduction

1.3 Mechanical Data

The following table provides details about the Form-factor and weight of both Air Cooled and

Conduction Cooled Assemblies:

Table 1-3 Mechanical Data

Feature Air Cooled Conduction Cooled

Form-factor Per VITA 48.1 Per VITA 48.2

Weight 0.33 kg (0.75 lb) 0.39 kg (0.86 lb)

1.3.1 Air Cooled

The following figure shows an Air Cooled type iVPX7225 board.

Figure 1-1 iVPX7225 Air Cooled

15

iVPX7225 Installation and Use (6806800S11C)

Page 35

1.3.2 Conduction Cooled

The following figure shows a Conduction Cooled type iVPX7225 board.

Figure 1-2 iVPX7225 Conduction Cooled

Introduction

1.4 Ordering Information

1.4.1 Supported Board Models

The following table lists the variants that are available upon release of this publication. As of the

printing date of this manual, this guide supports the board models listed below:

iVPX7225 Installation and Use (6806800S11C)

16

Page 36

Introduction

Consult your local Artesyn sales representative for the availability of other variants.

Table 1-4 Available Board Variants

Order Number Description

iVPX7225-02250822 3U VPX, AIR COOLED, DUAL-CORE 2.5GHZ 3555LE, 8GB DDR3, 1” FP,

iVPX7225-02250813L 3U VPX, CONDUCTION, DUAL-CORE 2.5GHZ 3555LE, 8GB DDR3,.85”

iVPX7225-02250802 3U VPX, AIR COOLED, DUAL-CORE 2.5GHZ 3555LE, 8GB DDR3,.8” FP,

iVPX7225-RTM 3U VPX, AIR, RTM FOR iVPX7225,.8” FACEPLATE

iVPX7225-RTM-1 3U VPX, AIR COOLED, RTM FOR iVPX7225, 1” FACEPLATE

Table 1-5 Accessories

ENP2

PITCH, ENP3

ENP2

Order Number Description

SERIAL-MINI-D (30-W2400E01A) Female-to-male micro-mini DB-9to DB9 adapter cable

(~12 inches)

17

iVPX7225 Installation and Use (6806800S11C)

Page 37

1.5 Product Identification

The following graphic shows the location of the serial number label of the iVPX7225 main

board.

Figure 1-3 Serial Number Label Location

Introduction

iVPX7225 Installation and Use (6806800S11C)

18

Page 38

Introduction

19

iVPX7225 Installation and Use (6806800S11C)

Page 39

Hardware Preparation and Installation

2.1 Overview

This chapter describes:

Instructions for inspecting the board

Requirements that have to be observed when using the board

Installation and removal instructions

2.2 Unpacking and Inspecting the Board

Read all notices and cautions prior to unpacking the product.

Chapter 2

Damage of Circuits

Before touching the board or electronic components, make sure that you are working

in an ESD-safe environment.

Shipment Inspection

To inspect the shipment, perform the following steps.

1. Verify that you have received all items of your shipment which includes the

following but are not limited to:

Printed Quick Start Guide and Safety Notes

iVPX7225 board

Any optional items ordered

iVPX7225 Installation and Use (6806800S11C)

20

Page 40

Hardware Preparation and Installation

2. Check for any damage. If there is some damage, report immediately to customer

service.

3. Remove the desiccant bag shipped together with the board and dispose properly.

The board is thoroughly inspected before shipment. If any damage occurred during transportation or any items are missing, please contact customer service immediately.

2.3 Environmental and Power Requirements

The following environmental and power requirements are applicable to the board.

2.3.1 Environmental Requirements

The environmental conditions must be tested and proven in the used system configuration.

These conditions refer to the surroundings of the board within the user environment.

Operating temperatures refer to the temperature of the air circulating around the board

(air-cooled) or the temperature of the card-edge (conduction-cooled), and not to the

component temperature.

To ensure that the operating conditions are met, adequate cooling is required within the

shelf environment.

The environmental values given in the table below only apply to the board without any

accessories. If installing accessories, their environmental requirements must also be

taken into account.

21

iVPX7225 Installation and Use (6806800S11C)

Page 41

Hardware Preparation and Installation

Product Damage

High humidity and condensation on the board surface causes short circuits.

Do not operate the board outside the specified environmental limits. Make sure the

board is completely dry and there is no moisture on any surface before applying power.

Table 2-1 Environmental Requirements

Environmental Parameter Air Cooled Conduction Cooled

Cooling Method Forced Air Conduction

Operating Temperature -40 °C to +71 °C

Storage Temperature -50 °C to +100 °C -50 °C to +100 °C

1

-40 °C to +71 °C 2(card edge)

Vibration Sine (10 min/Axis) 5G, 15 to 2000 HZ 10G, 15 to 2000 HZ

Vibration Random (1 Hr/Axis) 0.04g2/Hz, 15 to 2000 Hz

(8GRMS)

Shock 30g/11ms 40g/11ms

Humidity to 95% RH non-condensing to 95% RH non-condensing

1. Ambient temperature at sea-level without PMC/XMCs installed, while maintaining >= 80% CPU

performance (<=20% frequency down-step or duty-cycle throttling).

2. Measured at card edge, without PMC/XMCs installed, while maintaining >=80% CPU performance

(<=20% frequency down-step or duty-cycle throttling).

3. Flat 15-1000Hz, -6db/octave 1000Hz – 2000Hz [MIL-STD 810F Figure 514.5C-17]

4. +3db/octave 15-300Hz, Flat .1g2 300-1000Hz, -6db/octave 1000Hz – 2000Hz [MIL-STD 810F

Figure 514.5C-8]

3

0.1g2/Hz, 15 to 2000 Hz

(12GRMS)

4

iVPX7225 Installation and Use (6806800S11C)

22

Page 42

Hardware Preparation and Installation

2.3.2 Power Requirements

The following table contains the Power requirements:

Table 2-2 Power Requirements

Voltage Rail Minimum Power Typical Power Maximum Power

5V VPX PWR (VS3) 22W 32W 40W

3.3V Total 4W 5W 6W

Minimum Power: Representative of running Linux in a pure text mode (No X11/No GNOME), resting

idle the Linux login prompt.

Typical Power: Representative of running a mixture of CPU and I/O loads, including exercising

memory, local and backplane PCIe traffic, SATA, Gigabit Ethernet, FRAM and USB.

Maximum Power: Calculated worst-case power, based on device TDP and is not expected to be

reached under normal operation. A CPU-intensive workload could encroach upon this value.

All power requirements are specified with “no” XMC populated in the XMC site. The XMC site draws

power directly from the VPX backplane. No onboard regulation.

In the absence of an XMC, the iVPX7225 draws no power from the VPX 3.3V VS2 rail. However, the

“3.3V Total” power specified above includes a VS2 contribution due to the presence of an RTM in the

test configuration. The RTM draws 3.3V predominantly from VS2. One can therefore estimate the

iVPX7225 “3.3V AUX” power consumption by subtracting the iVPX7225 RTM 3.3V power

consumption from the total. The iVPX7225 “3.3V AUX” power consumption is fairly static at 2-3W.

Refer iVPX7225 RTM IU Manual for the RTM power consumption specifications.

2.4 Installing the Accessories

The following sections contains procedures on how to install the accessories on the iVPX7225

board.

Proper alignment of the XMC connector is essential to prevent damage to the XMC module

and/or to the mating XMC connector on the iVPX7225.

23

iVPX7225 Installation and Use (6806800S11C)

Page 43

Hardware Preparation and Installation

Damage of Circuits

Electrostatic discharge and incorrect installation and removal can damage circuits or

shorten their life.

Before touching the board or electronic components, make sure that you are working

in an ESD-safe environment.

Product Damage

Inserting or removing modules with power applied may result in damage to module

components.

Before installing or removing additional devices or modules, read the documentation

that came with the product.

iVPX7225 Installation and Use (6806800S11C)

24

Page 44

Hardware Preparation and Installation

2.4.1 Installing the XMC on Air Cooled Board