Page 1

VIETMOBILE.VN

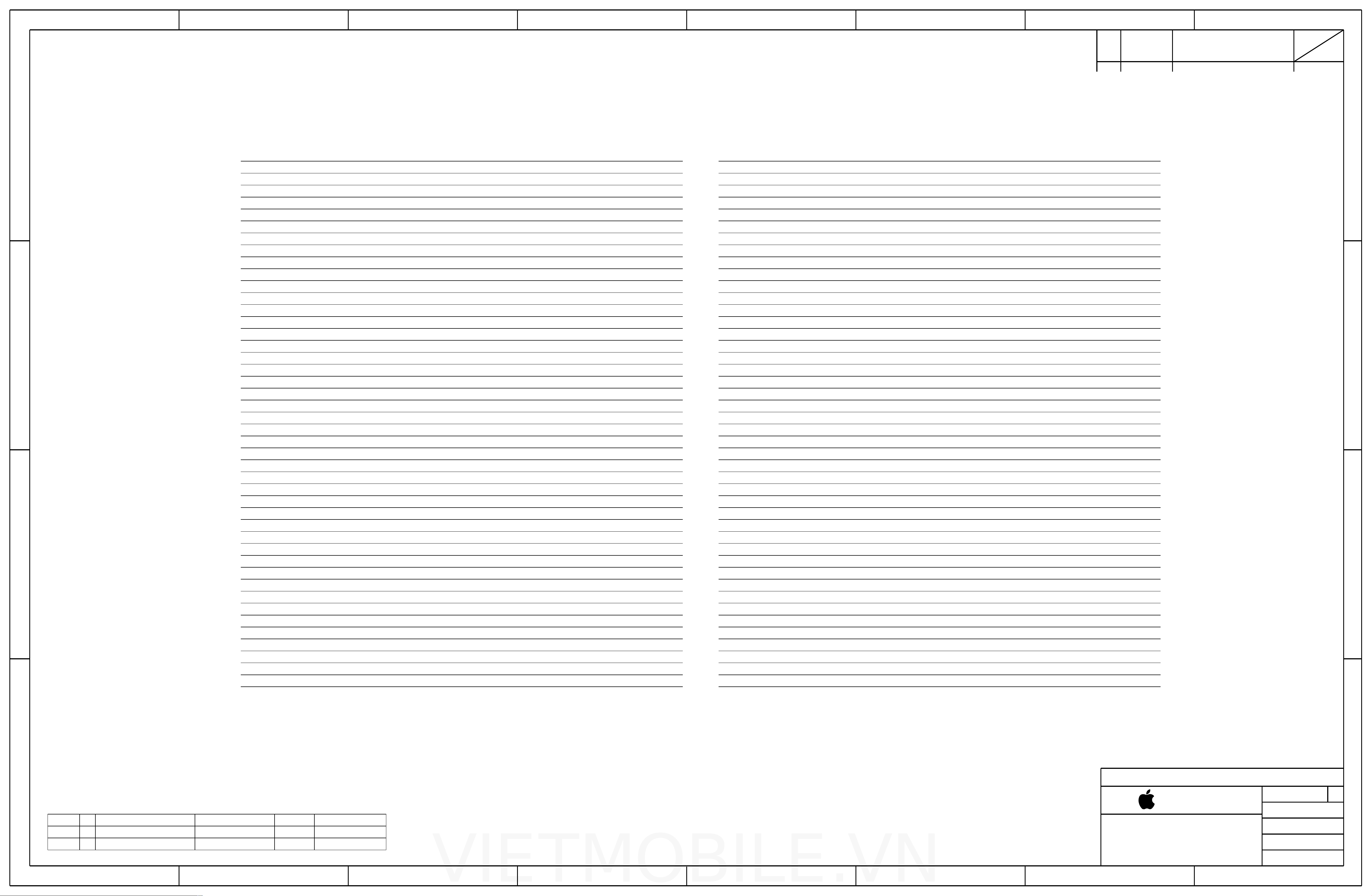

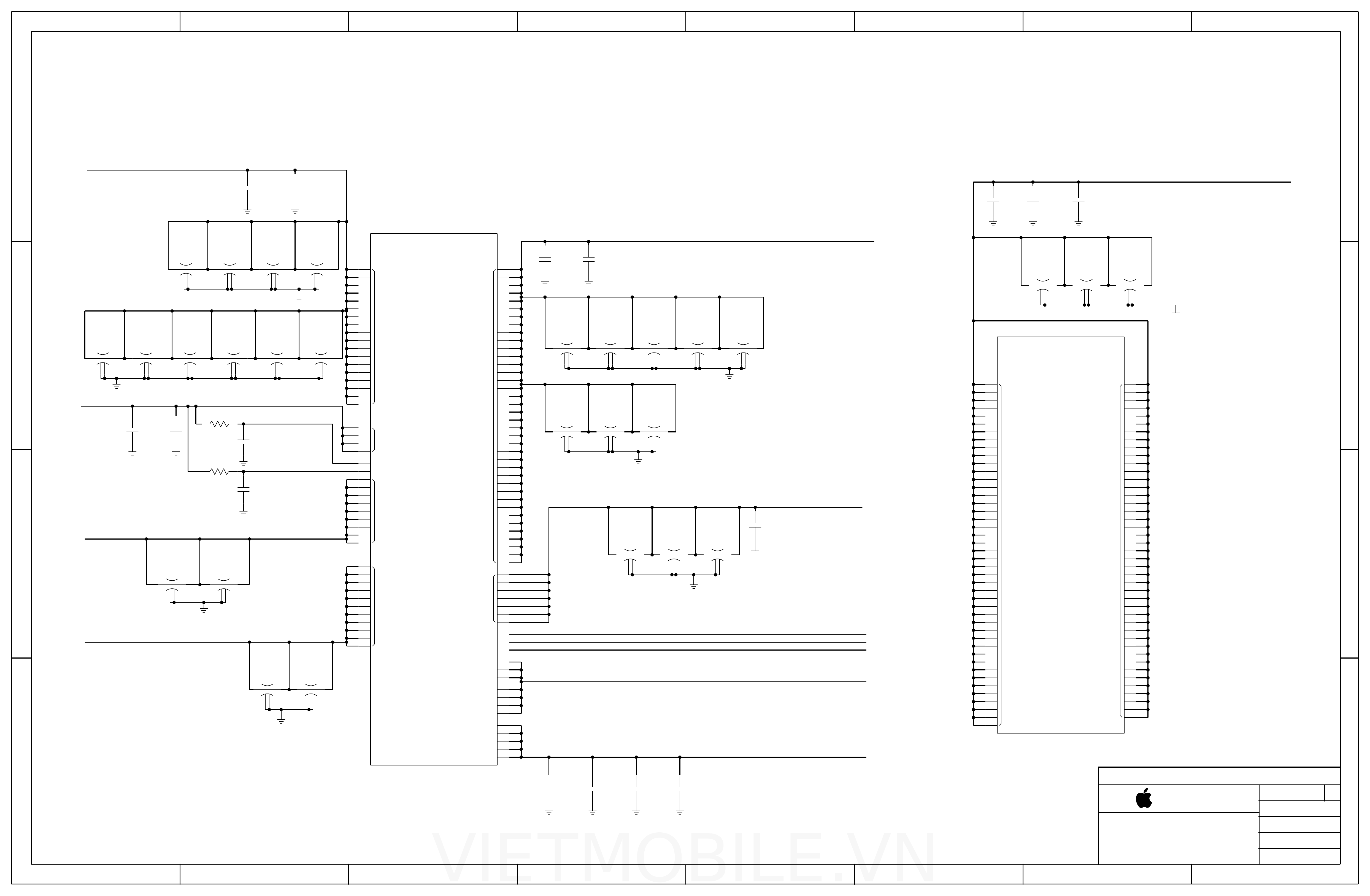

IPHONE XS MAX SCHEMATIC

Page 2

VIETMOBILE.VN

Page 3

VIETMOBILE.VN

Page 4

VIETMOBILE.VN

Page 5

VIETMOBILE.VN

Page 6

8

VIETMOBILE.VN

1. ALL RESISTANCE VALUES ARE IN OHMS, 0.1 WATT +/- 5%.

2. ALL CAPACITANCE VALUES ARE IN MICROFARADS.

3. ALL CRYSTALS & OSCILLATOR VALUES ARE IN HERTZ.

7

6543

D32/D33 Top MLB: EVT (D32 Build)

LAST_MODIFICATION=Wed Jan 31 16:37:18 2018

2 1

ECNREV DESCRIPTION OF REVISION

CK

APPD

DATE

2018-02-0500111753087 ENGINEERING RELEASED

D

1

2

3

4

5

6

7

8

10

11

12

1

2

3

4

5

6

10

11

129

13

14

15

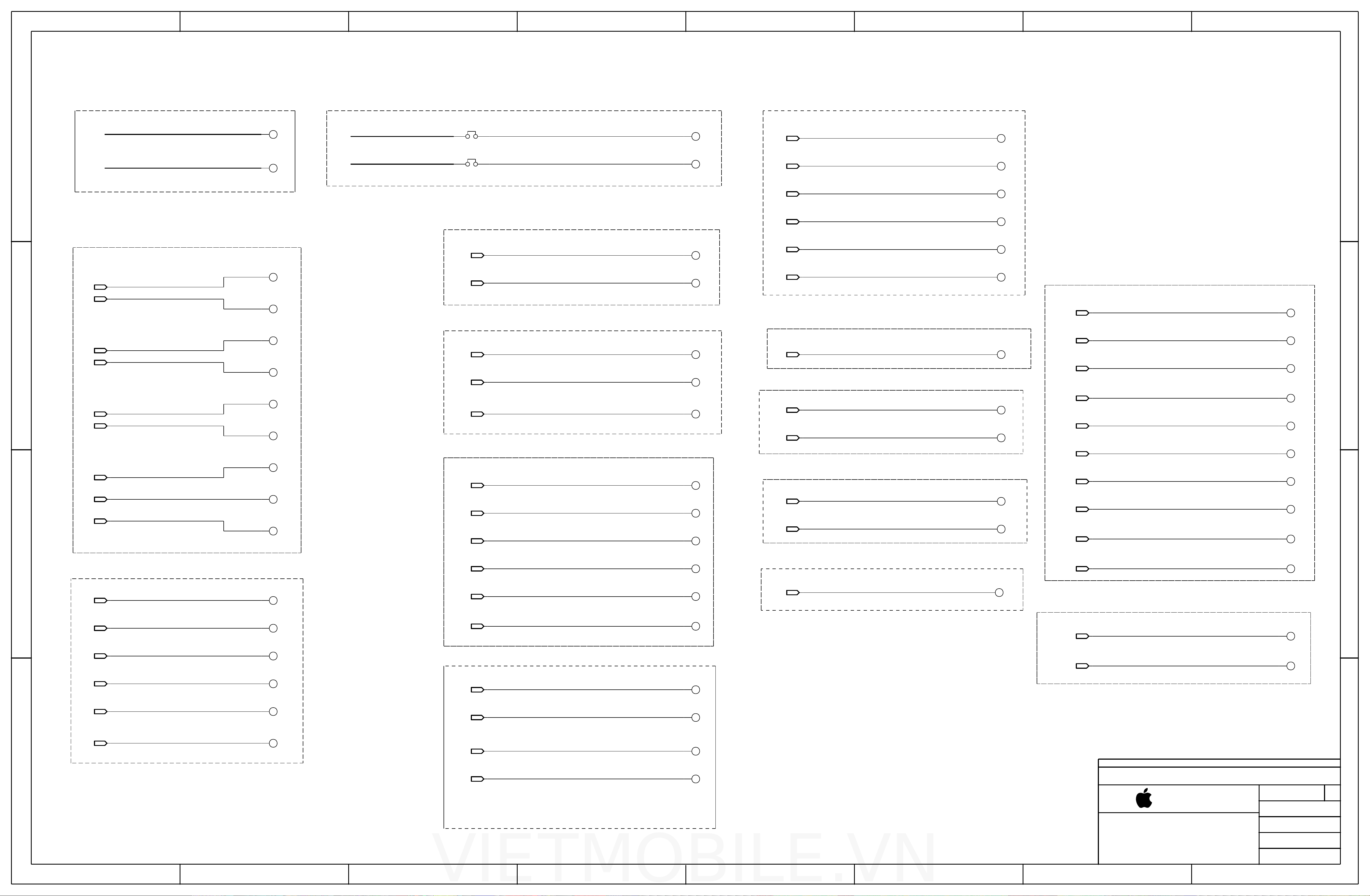

TABLE OF CONTENTS

SYSTEM:BOM Tables

SYSTEM:BOM Tables FF Specific

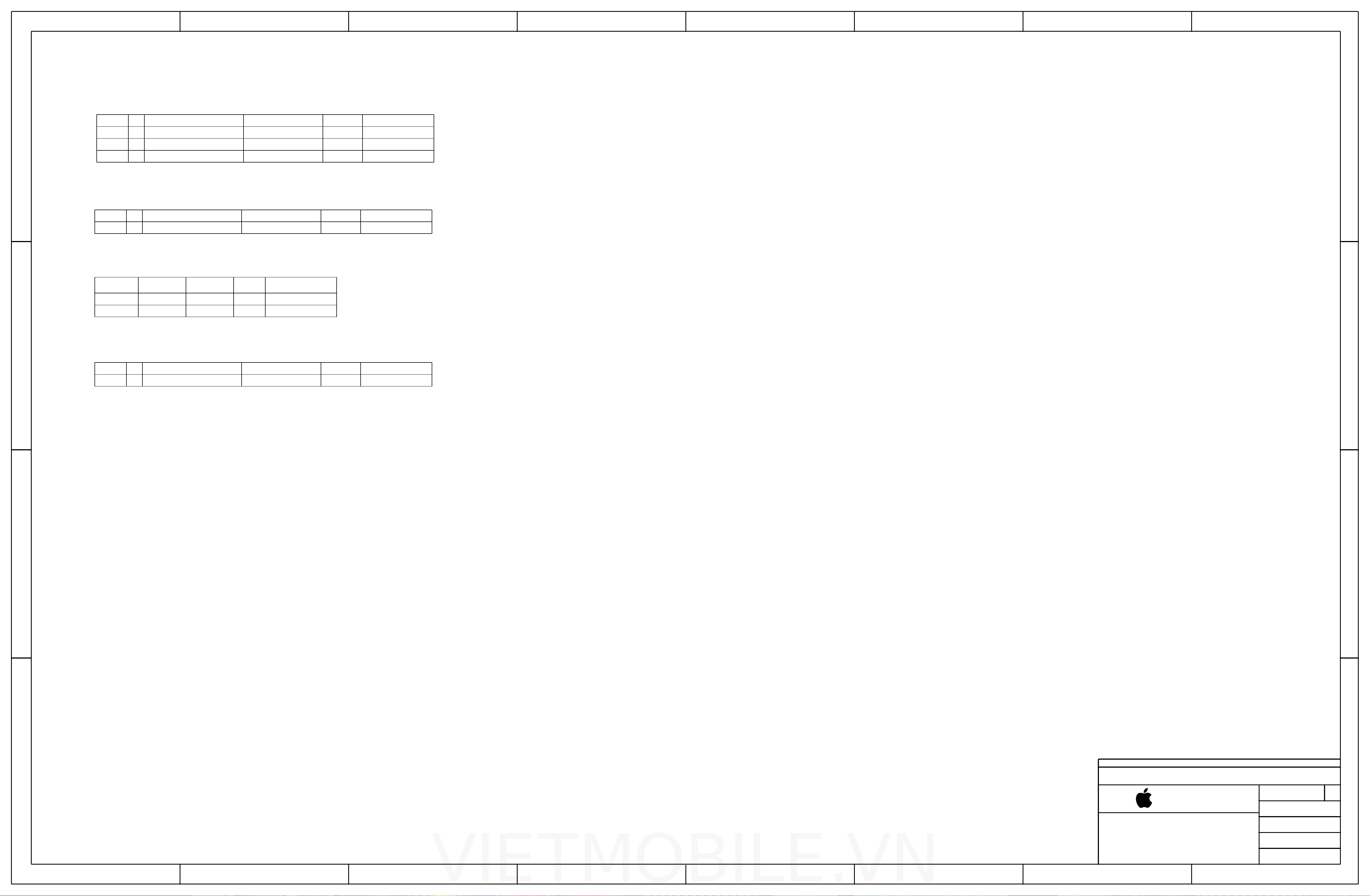

SYSTEM: Mechanical Components

SYSTEM: Testpoints (Top)

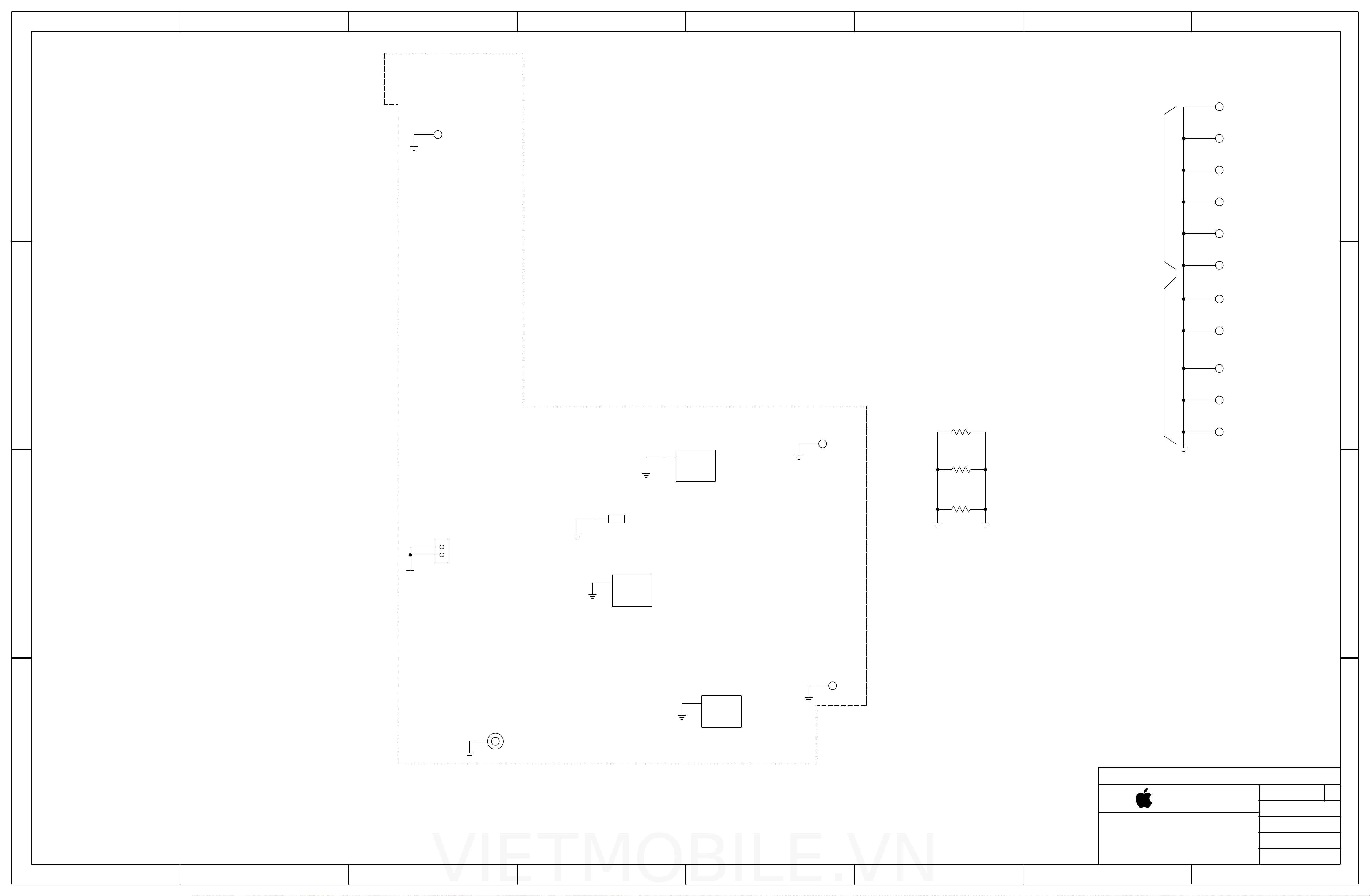

BOOTSTRAPPING

SOC: JTAG,USB,XTAL

SOC: PCIE

SOC: MIPI

SOC: LPDP

SOC: SERIAL

SOC: GPIO & UART

test_mlb

test_mlb

test_mlb

test_mlb

test_mlb

test_mlb

test_mlb

10/13/2016

08/09/2017

10/13/2016

10/13/2016

10/17/2016

04/07/2017

10/13/2016

04/05/2017

04/05/2017

46

47

48

49

50

51

52

53

54

55

56

57

60

61

62

63

64

65

66

67

68

70

71

81

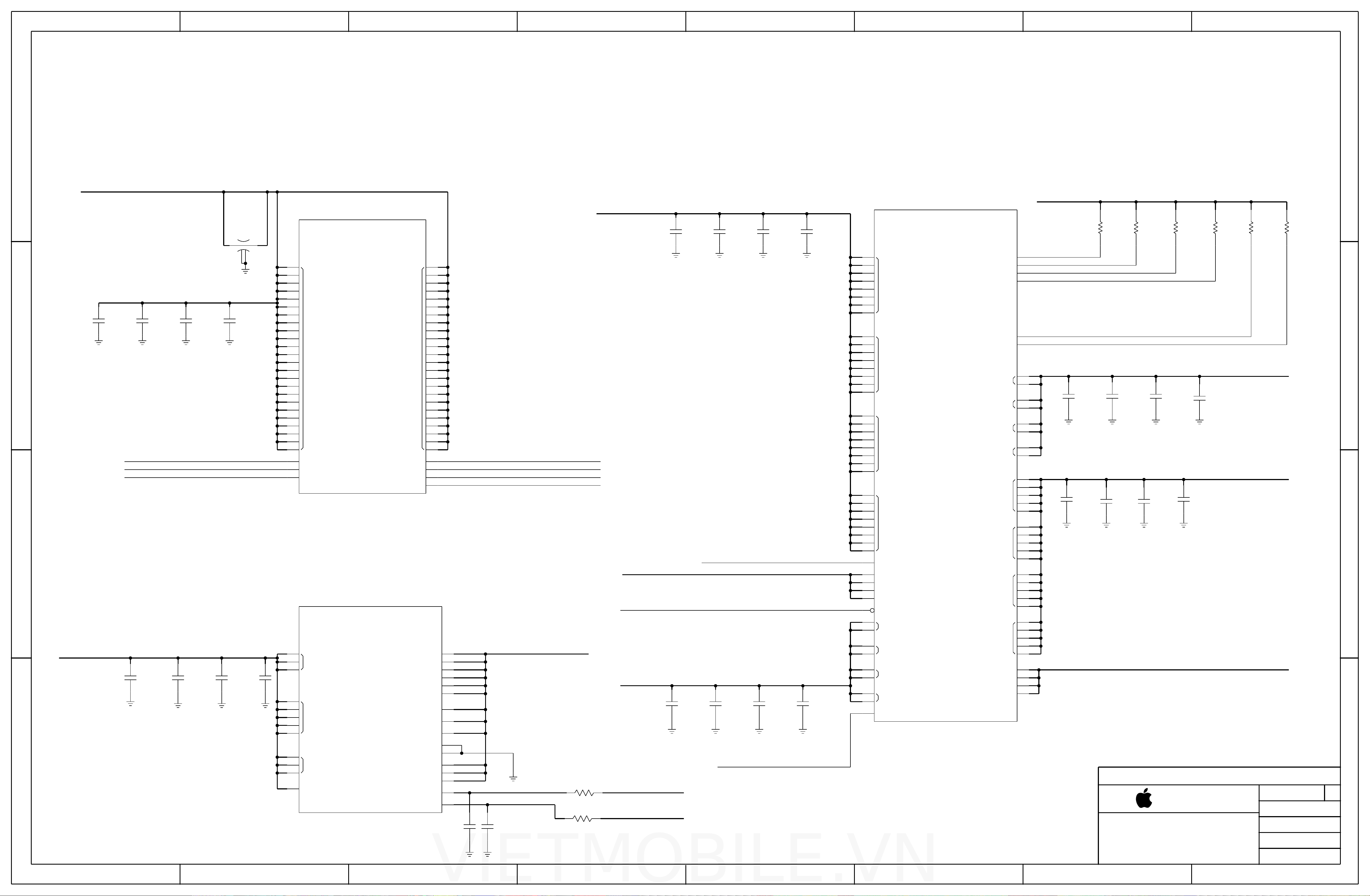

I/O: LDCM

I/O: Gecko

I/O: USB PD

I/O: Hydra

I/O: B2B Dock

B2B: Interposer Bot

SYSTEM: AP I2C

SYSTEM: ISP I2C

SYSTEM: AOP/SMC I2C

SYSTEM: SOC/PMU GPIOs

SYSTEM: AOP GPIOs

Interposer: Pins 1-144

test_mlb

test_mlb

test_mlb

test_mlb

test_mlb

D

DATESYNCCONTENTSCSAPAGEDATESYNCCONTENTSCSAPAGE

06/06/2017

10/17/2016

10/13/2016

10/13/2016

10/13/2016

08/30/2017

05/09/2017

05/09/2017

08/29/2017

C

13

14

15

16

17

18

19

20

21

22

23

24

25

26

16

17

18

19

21

26

27

29

30

31

32

33 SYSTEM POWER: Charger

SOC: AOP

SOC: POWER (1/3)

SOC: POWER (2/3)

SOC: POWER (3/3)

SOC: DEV BOARD ALIASES20

SOC: LPDP ALIASES

NAND

SYSTEM POWER: PMU Bucks (1/4)

SYSTEM POWER: PMU Bucks (2/4)28

SYSTEM POWER: PMU LDOs (3/4)

SYSTEM POWER: PMU (4/4)

SYSTEM POWER: Boost

SYSTEM POWER: B2B Battery

test_mlb

test_mlb

test_mlb

test_mlb

test_mlb

test_mlb

test_mlb

test_mlb

test_mlb

10/17/2016

04/17/2017

08/17/2017

03/22/2017

03/10/2017

06/01/2017

03/10/2017

03/10/2017

10/13/2016

10/13/2016

10/13/2016

58

59

60

82

83

85

Interposer: Pins 145-285

Interposer: Top Aliases

Interposer: Pins 286-359

08/30/2017

08/17/2017

08/30/2017

C

B

27 35

28

29

30

31

32

33 41

34

35

36

37

38

39

40

36

37

38

39 10/13/2016

40

42

43

44

46

47

48 AUDIO: CODEC (2/2)

SYSTEM POWER: B2B Cyclone + Button

SENSORS

CAMERA: PMU (1/2)

CAMERA: PMU (2/2)

CAMERA: B2B Wide (TX)

CAMERA: B2B Tele [MT]

CAMERA: Strobe Drivers

CAMERA: B2B Fcam

CAMERA: B2B Strobe + Hold Button

PEARL: Power

PEARL: B2B Romeo + Juliet

AUDIO: CODEC (1/2)

test_mlb

test_mlb

test_mlb

test_mlb

test_mlb

test_mlb

test_mlb

test_mlb

test_mlb

test_mlb45

test_mlb

test_mlb

test_mlb

10/13/2016

10/13/2016

10/13/2016

03/22/2017

10/13/2016

03/22/2017

10/13/2016

B

03/22/2017

10/13/2016

10/13/2016PEARL: B2B Rosaline + Sensor

10/13/2016

10/13/2016

A

41

42

43

44

45

49

50

51

57

59

AUDIO: SOUTH SPKAMP

AUDIO: NORTH SPKAMP

ARC: AMP

CG: B2B Display

I/O: Overvoltage Cut-Off Circuit

BOM:639-03991 (Ultimate)

BOM:639-03992 (Extreme)

BOM:639-03990 (Max)

MCO:056-05750

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

051-02545 SCHSCH,MLB_TOP,D32 CRITICAL ?1

PCBPCB,MLB_TOP,D32 ?CRITICAL820-00997 1

BOM OPTIONCRITICAL

TABLE_5_HEAD

TABLE_5_ITEM

TABLE_5_ITEM

test_mlb

04/05/2017

04/05/2017

04/05/2017

10/13/2016

TABLE OF CONTENTS

DRAWING TITLE

SCH,MLB,TOP,D32

Apple Inc.

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

051-02545

REVISION

7.0.0

BRANCH

PAGE

1 OF 85

SHEET

1 OF 60

A

SIZEDRAWING NUMBER

D

8

3

124567

Page 7

Display CMC's

VIETMOBILE.VN

PART NUMBER

155S00391155S00415 ALT_PARTS ALL

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

CMC,35OSM,7HGz,MUR

TABLE_ALT_HEAD

TABLE_ALT_ITEM

678

3 245

1

D

NAND

Ultimate

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

HYNIX, 3DV4. ULTIMATE CRITICAL ULTIMATEU26001335S00340

PART NUMBER

335S00359 335S00340 U2600ALT_PARTS TOSHIBA, BICS3, ULT

335S00286 U2600335S00340 ALT_PARTS SANDISK, BICS3, ULT

335S00340335S00288 SAMSUNG, 3DV4, ULTALT_PARTS U2600

Extreme

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

TABLE_ALT_HEAD

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

D

TABLE_5_HEAD

BOM OPTIONCRITICAL

TABLE_5_ITEM

Global R/C Alternates

TABLE_ALT_HEAD

PART NUMBER

138S0648 ALT_PARTS

138S0652 ALL

138S0706138S0739

ALT_PARTS

ALT_PARTS

ALL

ALL138S00049 138S0831

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

CAP,X5R,4.7UF,6.3V,0.65MM,0402,TAIYO

CAP,CER,X5R,0.22UF,20%,6.3V,20%

CAP,CER,X5R,2.2UF,20%,6.3V,0201

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

Yangtze Inductors

TABLE_ALT_HEAD

PART NUMBER

152S00918

152S00918

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

TABLE_ALT_ITEM

ALL152S00872 ALT_PARTS

ALT_PARTS ALL152S00847

IND,MLD,0.47UH,TDK

TABLE_ALT_ITEM

IND,MLD,0.47UH,CYN

CRITICAL PART# COMMENT

152S00918

TABLE_CRITICAL_HEAD

TABLE_CRITICAL_ITEM

IND,MLD,0.22UH,20%,5.8A,40MOHM,H=.65,1608

C

335S00342 EXTREMECRITICAL1 U2600HYNIX, 3DV4, Extreme

PART NUMBER

335S00276 ALT_PARTS335S00342

335S00358 U2600ALT_PARTS335S00342

Max

1 HYNIX, 3DV4, MAX CRITICAL MAX335S00343 U2600

PART NUMBER

335S00343

U2600335S00247 ALT_PARTS335S00342

U2600

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

U2600ALT_PARTS335S00339

TABLE_5_HEAD

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

TABLE_ALT_HEAD

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

TABLE_ALT_ITEM

SANDISK, BISC3, SUPREME

TABLE_ALT_ITEM

SAMSUNG, 3DV4, SUPREME

TABLE_ALT_ITEM

TOSHIBA, 3DV4, SUPREME

TABLE_ALT_HEAD

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

TABLE_ALT_ITEM

SAMSUNG, 3DV4, MAX

BOM OPTIONCRITICAL

TABLE_5_ITEM

Denali Inductors

TABLE_ALT_HEAD

PART NUMBER

ALT_PARTS152S00831 ALL152S00878

ALT_PARTS152S00818

152S00822152S00835

TABLE_5_HEAD

BOM OPTIONCRITICAL

TABLE_5_ITEM

ALT_PARTS ALL

ALT_PARTS152S00822

ALT_PARTS152S00877 152S00817 ALL

ALL152S00831

ALL152S00827

ALT_PARTS152S00829 152S00817 ALL

ALT_PARTS ALL152S00825 152S00823

ALT_PARTS152S00819 ALL152S00833

ALT_PARTS152S00819 ALL152S00824

152S00834

ALT_PARTS152S00820 ALL

ALT_PARTS152S00828 152S00820 ALL

ALT_PARTS152S00821 ALL152S00826

ALT_PARTS ALL152S00866 152S00821

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

TABLE_ALT_ITEM

IND,MLD,0.22UH,20%,5.9A,36MOHM,H=.65,1608

TABLE_ALT_ITEM

IND,MLD,0.22UH,20%,5.9A,36MOHM,H=.65,1608,CYN

TABLE_ALT_ITEM

IND,MLD,0.47UH,20%,4.5A,40MOHM,H=.80,2012

TABLE_ALT_ITEM

IND,MLD,0.47UH,20%,4.5A,50MOHM,H=.80,2012

TABLE_ALT_ITEM

IND,MLD,0.1UH,20%,9A,20MOHM,H=0.8,2012

TABLE_ALT_ITEM

IND,MLD,0.1UH,20%,9.0A,22MOHM,H=0.8,2012

TABLE_ALT_ITEM

IND,MLD,1UH,20%,3A,60MO,H=.65,2016

TABLE_ALT_ITEM

IND,MLD,1UH,20%,2.1A,62MO,H=.65,2012

TABLE_ALT_ITEM

IND,MLD,1UH,20%,2A,69MO,H=.65,2012

TABLE_ALT_ITEM

IND,MLD,0.47UH,20%,3.8A,270MO,H=.80,2012

TABLE_ALT_ITEM

IND,MLD,0.47UH,20%,3.2A,400MO,H=.80,2012

TABLE_ALT_ITEM

IND,MLD,1UH,20%,2.1A,52MO,H=.80,2012

TABLE_ALT_ITEM

IND,MLD,1UH,20%,2.1A,52MO,H=.80,2012

CRITICAL PART# COMMENT

152S00831

152S00822

152S00817

152S00823

152S00819

152S00820

152S00821

IND,MLD,0.22UH,20%,5.8A,40MOHM,H=.65,1608

IND,MLD,0.47UH,20%,4.5A,47MOHM,H=.8,2012

IND,MLD,0.1UH,20%,9.4A,22MOHM,H=0.65,1608

IND,MLD,1UH,20%,3.0A,60MO,H=.65,2016

IND,MLD,1UH,20%,1.7A,69MO,H=.65,2012

IND,MLD,0.47UH,20%,3.2A,42MO,H=.80,2012

IND,MLD,1UH,20%,2.2A,60MO,H=.80,2012

TABLE_CRITICAL_HEAD

TABLE_CRITICAL_ITEM

TABLE_CRITICAL_ITEM

TABLE_CRITICAL_ITEM

TABLE_CRITICAL_ITEM

TABLE_CRITICAL_ITEM

TABLE_CRITICAL_ITEM

TABLE_CRITICAL_ITEM

C

B

A

PART NUMBER

ALT_PARTS

ALT_PARTS

ALL138S00148 138S00149

ALL138S00150 138S00149

ALT_PARTS138S00151 ALL138S00149

PART NUMBER

138S00143 138S00144 ALT_PARTS

138S00163 ALT_PARTS138S00144

PART NUMBER

ALL

ALL

138S00139 ALL138S00138 ALT_PARTS

138S00139138S00164 ALLALT_PARTS

PART NUMBER

138S00221 ALT_PARTS138S00146 ALL

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

0402-3T,10.5uF@1V, Kyocera

0402-3T,10.5uF@1V, SEMCO

0402-3T,10.5uF@1V, TY

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

0402,16uF@1V, Kyocera

0402,16uF@1V, TY

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

0201,3uF@1V, Kyocera

0201,3uF@1V, TY

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

0402,5.1uF@3V, Kyocera

TABLE_ALT_HEAD

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_HEAD

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_HEAD

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_HEAD

TABLE_ALT_ITEM

CRITICAL PART# COMMENT

138S00149

CRITICAL PART# COMMENT

138S00144

CRITICAL PART# COMMENT

138S00139

CRITICAL PART# COMMENT

138S00146

0402-3T,10.5uF@1V

0402,16uF@1V

0201,3uF@1V

0402,5.1uF@3V

TABLE_CRITICAL_HEAD

TABLE_CRITICAL_ITEM

TABLE_CRITICAL_HEAD

TABLE_CRITICAL_ITEM

TABLE_CRITICAL_HEAD

TABLE_CRITICAL_ITEM

TABLE_CRITICAL_HEAD

TABLE_CRITICAL_ITEM

XTAL Alternate

PART NUMBER

197S00118 ALT_PARTS197S0612 Y1000

197S00120 ALT_PARTS Y1000

197S00118

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

XTAL, 24M, 1612

XTAL, 24M, 1612

NEON Alternate

PART NUMBER

152S00721 ALT_PARTS

152S00876

L4100, L4120 TY, IND

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

TABLE_ALT_HEAD

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_HEAD

TABLE_ALT_ITEM

SYNC_MASTER=test_mlb

PAGE TITLE

SYNC_DATE=10/13/2016

B

A

TABLE_ALT_HEAD

PART NUMBER

138S00141 ALT_PARTS ALL138S00140

138S00142

138S00166 ALT_PARTS

138S00141 ALLALT_PARTS

138S00141 ALL

8

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

TABLE_ALT_ITEM

0201,1.1uF@3V, Kyocera

TABLE_ALT_ITEM

0201,1.1uF@3V, SEMCO

TABLE_ALT_ITEM TABLE_ALT_ITEM

0201,1.1uF@3V, Taiyo

CRITICAL PART# COMMENT

138S00141

0201,1.1uF@3V

67

TABLE_CRITICAL_HEAD

TABLE_CRITICAL_ITEM

ANSEL Alternate

PART NUMBER

152S00875152S00716

ALT_PARTS

L3700

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

TY, IND

TABLE_ALT_HEAD

SYSTEM:BOM Tables

DRAWING NUMBER

051-02545

Apple Inc.

REVISION

7.0.0

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

35 4

2

BRANCH

PAGE

2 OF 85

SHEET

2 OF 60

1

SIZE

D

Page 8

D

VIETMOBILE.VN

EEEE Codes

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

EEEE FOR (MLB_TOP,639-03991,ULTIMATE)

EEEE FOR (MLB_TOP,639-03992,EXTREME)

EEEE FOR (MLB_TOP,639-03990,MAX)

678

TABLE_5_HEAD

BOM OPTIONCRITICAL

TABLE_5_ITEM

CRITICAL

EEEE_HWV01825-7691

ULTIMATEEEEE_HWV1825-7691 1

TABLE_5_ITEM

EXTREMEEEEE_HWV21825-7691 CRITICAL

TABLE_5_ITEM

MAXCRITICAL

3 245

1

D

C

Cyprus OMIT

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

339S00510 1 SOCU1000 CRITICALCYPRUS 4GB Micron

Cyprus ALTs

PART NUMBER

ALT_PARTS

ALT_PARTS U1000339S00510339S00512

U1000339S00510339S00511

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

CYPRUS 4GB Hynix

CYPRUS 4GB Samsung

Combo Stiffener

TABLE_5_HEAD

BOM OPTIONCRITICAL

TABLE_5_ITEM

TABLE_ALT_HEAD

TABLE_ALT_ITEM

TABLE_ALT_ITEM

C

TABLE_5_HEAD

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

ST04011604-19651 Combo Stiffener CRITICAL ALL

BOM OPTIONCRITICAL

TABLE_5_ITEM

B

B

A

8

67

SYNC_MASTER=

PAGE TITLE

SYNC_DATE=08/09/2017

A

SYSTEM:BOM Tables FF Specific

SIZE

D

Apple Inc.

DRAWING NUMBER

051-02545

REVISION

7.0.0

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

35 4

2

BRANCH

PAGE

3 OF 85

SHEET

3 OF 60

1

Page 9

678

VIETMOBILE.VN

3 245

1

FIDUCIALS

FD0401

0P5SQ-CROSS-NSP

FID

1

ROOM=ASSEMBLY

D

CL0400

2.10R1.60-NSP

1

Crosses

FD0402

FID

0P5SQ-CROSS-NSP

1

ROOM=ASSEMBLY

FD0403

FID

0P5SQ-CROSS-NSP

1

ROOM=ASSEMBLY

FD0404

FID

0P5SQ-CROSS-NSP

1

ROOM=ASSEMBLY

FD0407

FID

0P5SQ-CROSS-NSP

1

ROOM=ASSEMBLY

FD0406

FID

0P5SQ-CROSS-NSP

1

ROOM=ASSEMBLY

D

C

1

SH0403

SM

SHIELD-N-MLB-D32

CL0401

2.10R1.60-NSP

1

R0402

0.00

1/32W

01005

21

0%

MF

R0401

0.00

1/32W

01005

21

0%

MF

CKPLUS_WAIVE=TERMSHORTED

CKPLUS_WAIVE=TERMSHORTED

Squares

FD0405

0P5SQ-SMP3SQ-NSP

FID

1

ROOM=ASSEMBLY

FD0408

0P5SQ-SMP3SQ-NSP

FID

1

ROOM=ASSEMBLY

FD0410

0P5SQ-SMP3SQ-NSP

FID

1

ROOM=ASSEMBLY

FD0411

0P5SQ-SMP3SQ-NSP

FID

1

ROOM=ASSEMBLY

FD0412

0P5SQ-SMP3SQ-NSP

FID

1

ROOM=ASSEMBLY

C

B

CL0402

STDOFF-3.0OD1.6ID-H0.62-TH-D32

1

2

CKPLUS_WAIVE=TERMSHORTED

ST0401

WELD-AP-D3X

SM

1

OMIT_TABLE

1

SH0401

SM

SHIELD-W-MLB-D32

R0403

0.00

1/32W

01005

21

0%

MF

CKPLUS_WAIVE=TERMSHORTED

B

A

SB0401

STDOFF-2.9OD1.4ID-0.77H-SM1

1

1

SH0402

SM

SHIELD-S-MLB-D32

CL0403

2.10R1.60-NSP

1

PAGE TITLE

SYSTEM: Mechanical Components

Apple Inc.

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

DRAWING NUMBER

051-02545

REVISION

7.0.0

BRANCH

PAGE

4 OF 85

SHEET

4 OF 60

A

SIZE

D

8

67

35 4

2

1

Page 10

678

VIETMOBILE.VN

3 245

1

D

C

37 36

37 36

15

23 15

15

23 15

15

15

15

15

15

PEARL

PP_ROMEO_DENSE_ANODE

PP_ROMEO_CATHODE

BUMP SENSE

GPU_SENSE_NEG

IN

GPU_SENSE_POS

IN

CPU_PCORE_SENSE_NEG

IN

CPU_PCORE_SENSE_POS

IN

SOC_SENSE_NEG

IN

SOC_SENSE_POS

IN

DCS_SENSE_POS

IN

VDDQL_DCS_SENSE_NEG

IN

VDDQL_SENSE_POS

IN

PP0510

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0511

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0553

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0513

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0551

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0512

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0516

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0514

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0517

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0552

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0518

P2MM-NSM

SM

1

PP

ROOM=TEST

20 17

20 17

PP_GPU

PP_CPU_PCORE

LVCC

XW0510

SHORT-10L-0.05MM-SM

XW0511

SHORT-10L-0.05MM-SM

12

IN

12

IN

13

IN

23 13

IN

49 23 7

58 19 13

19 11 6

19 13

IN

IN

IN

IN

58

21

58

21

PAD_MTR_ANALOG_TEST_P

PAD_MTR_ANALOG_TEST_N

AOP_TO_DDR_SLEEP1_READY_PROBE

SPMI_PMU_BI_PMGR_SDATA

PMU_TO_AP_HYDRA_ACTIVE_READY

SWD_AP_BI_NAND_SWDIO

SWD_AOP_TO_MANY_SWCLK

SPI_S4E_TO_AP_MISO_BOOT_CONFIG2

PP_GPU_LVCC

PP_CPU_PCORE_LVCC

METROLOGY

PMU

NAND

PP0506

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0507

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0592

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0593

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0520

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0521

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0522

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0560

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0561

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0562

P2MM-NSM

SM

1

PP

ROOM=TEST

28 13

28 13

28 13

56 28

56 27

56 28

49 26

36 30

36 23 9

48 11

48 11

Sensors

SPI_AOP_TO_IMU_SCLK

IN

SPI_AOP_TO_IMU_MOSI

IN

SPI_IMU_TO_AOP_MISO

IN

IMU_TO_AOP_DATARDY

IN

COMPASS_TO_AOP_INT

IN

PHOSPHORUS_TO_AOP_INT

IN

Hydra VBUS

HYDRA_TO_YANGTZE_VBUS1_VALID_L

IN

Rigel

CAMPMU_TO_RIGEL_ENABLE

IN

RIGEL_TO_ISP_INT

IN

CCG SWD

AP_BI_CCG2_SWDIO

IN

AP_TO_CCG2_SWCLK

IN

PP0540

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0541

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0542

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0544

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0546

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0547

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0550

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0570

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0571

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0586

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0587

P2MM-NSM

SM

1

PP

ROOM=TEST

56 47

56 43 41

43 42 41

48 11

23 13

30 17

49 12

40 11

40 11

VALIDATION PP's

IN

IN

IN

IN

IN

IN

IN

IN

IN

GECKO_TO_AOP_IRQ_L

SPKAMP_BOT_ARC_TO_AOP_INT_L

SPKAMP_TO_OTHERS_SYNC

CCG2_TO_SMC_INT_L

PMU_TO_AOP_CLK32K

CAMPMU_TO_JULIET_DVDD_LDO_EN

UART_AP_DEBUG_RXD

SPI_CODEC_TO_AP_MISO

SPI_AP_TO_CODEC_MOSI

PP0590

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0591

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0566

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0567

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0594

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0595

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0596

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0597

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0598

P2MM-NSM

SM

1

PP

ROOM=TEST

D

C

B

A

23 7

12 6

23 12 7

9

9

12

SOC Debug

AP_TO_PMU_TEST_CLKOUT

IN

BOARD_ID0

IN

SOC_DEBUG2

IN

SOC_DEBUG3

IN

DFU_STATUS

IN

PMU_TO_AP_PRE_UVLO_L

IN

PP0500

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0501

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0502

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0503

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0504

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0505

P2MM-NSM

SM

1

PP

ROOM=TEST

19 7

19 8

19 8

17 8

17 8

19

19

NAND_ANI1_VREF

IN

NAND_ANI0_VREF

IN

AP_TO_NAND_RESET_L

IN

PCIE Refclk

90_PCIE_AP_TO_NAND_REFCLK_P

IN

90_PCIE_AP_TO_NAND_REFCLK_N

IN

90_PCIE_BB_TO_AP_RXD_C_P

IN

90_PCIE_BB_TO_AP_RXD_C_N

IN

PP0563

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0564

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0565

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0530

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0531

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0532

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0533

P2MM-NSM

SM

1

PP

ROOM=TEST

23

PP0599

PMU XTAL

42 41 40 13

50 43

PP0588

P2MM-NSM

SM

IN

XTAL_TO_PMU_CLK32K_2

1

PP

ROOM=TEST

57 43

57 43

IN

IN

IN

I2S_CODEC_ASP1_TO_AOP_AMPS_BCLK

WALLET MODE

NFC_TO_ARC_RESET_L

NFC_TO_ARC_TRIG

SYNC_MASTER=test_mlb SYNC_DATE=10/13/2016

PAGE TITLE

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0524

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0525

P2MM-NSM

SM

1

PP

ROOM=TEST

B

A

SYSTEM: Testpoints (Top)

SIZE

D

Apple Inc.

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

DRAWING NUMBER

051-02545

REVISION

7.0.0

BRANCH

PAGE

5 OF 85

SHEET

5 OF 60

8

67

35 4

2

1

Page 11

678

VIETMOBILE.VN

3 245

TOP BOARD ONLY CONFIGURATION IS D33 MLB MAV

BOTTOM BOARD SELECTS ICE/MAV and D32/D33

1

D

55

55

BOARD_REV3

OUT

BOARD_REV2

OUT

BOOTSTRAPPING:BOARD REV

BOARD ID

BOOT CONFIG

R0623

1.00K

1/32W

01005

ROOM=SOC

21

5%

MF

R0622

1.00K

1/32W

01005

ROOM=SOC

21

5%

MF

NOSTUFF

PP1V8_IO

53 52 44

D

37 36 34 32 31 30 29 20 19 17

SELECTED -->

C

55

55

12

BOARD_REV1

OUT

BOARD_REV0

OUT

BOARD_ID4

OUT

CKPLUS_WAIVE=SINGLE_NODENET

R0621

1.00K

1/32W

01005

ROOM=SOC

21

5%

MF

R0620

1.00K

1/32W

01005

ROOM=SOC

21

5%

MF

C

B

11

57 12

12

12 5

PP1V8_IO

OUT

BOARD_ID2

OUT

PP1V8_IO

OUT

BOARD_ID0

OUT

CKPLUS_WAIVE=SINGLE_NODENET

MAKE_BASE=TRUE

On mlb_bot

MAKE_BASE=TRUE

No connect

B

DEFAULT -->

No connect

R0601

4.7K

1/32W

01005

ROOM=SOC

21

1%

MF

A

19 11 5

19 11

SPI_S4E_TO_AP_MISO_BOOT_CONFIG2

OUT

SPI_AP_TO_S4E_MOSI_BOOT_CONFIG1

OUT

R0602

19 11

8

SPI_AP_TO_S4E_SCLK_BOOT_CONFIG0

OUT

4.7K

1%

1/32W

MF

01005

ROOM=SOC

NOSTUFF

21

<-------Removed at EVT

67

POR -->

SYNC_MASTER=test_mlb

PAGE TITLE

SYNC_DATE=10/13/2016

A

BOOTSTRAPPING

DRAWING NUMBER

051-02545

Apple Inc.

REVISION

7.0.0

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

35 4

2

BRANCH

PAGE

6 OF 85

SHEET

6 OF 60

1

SIZE

D

Page 12

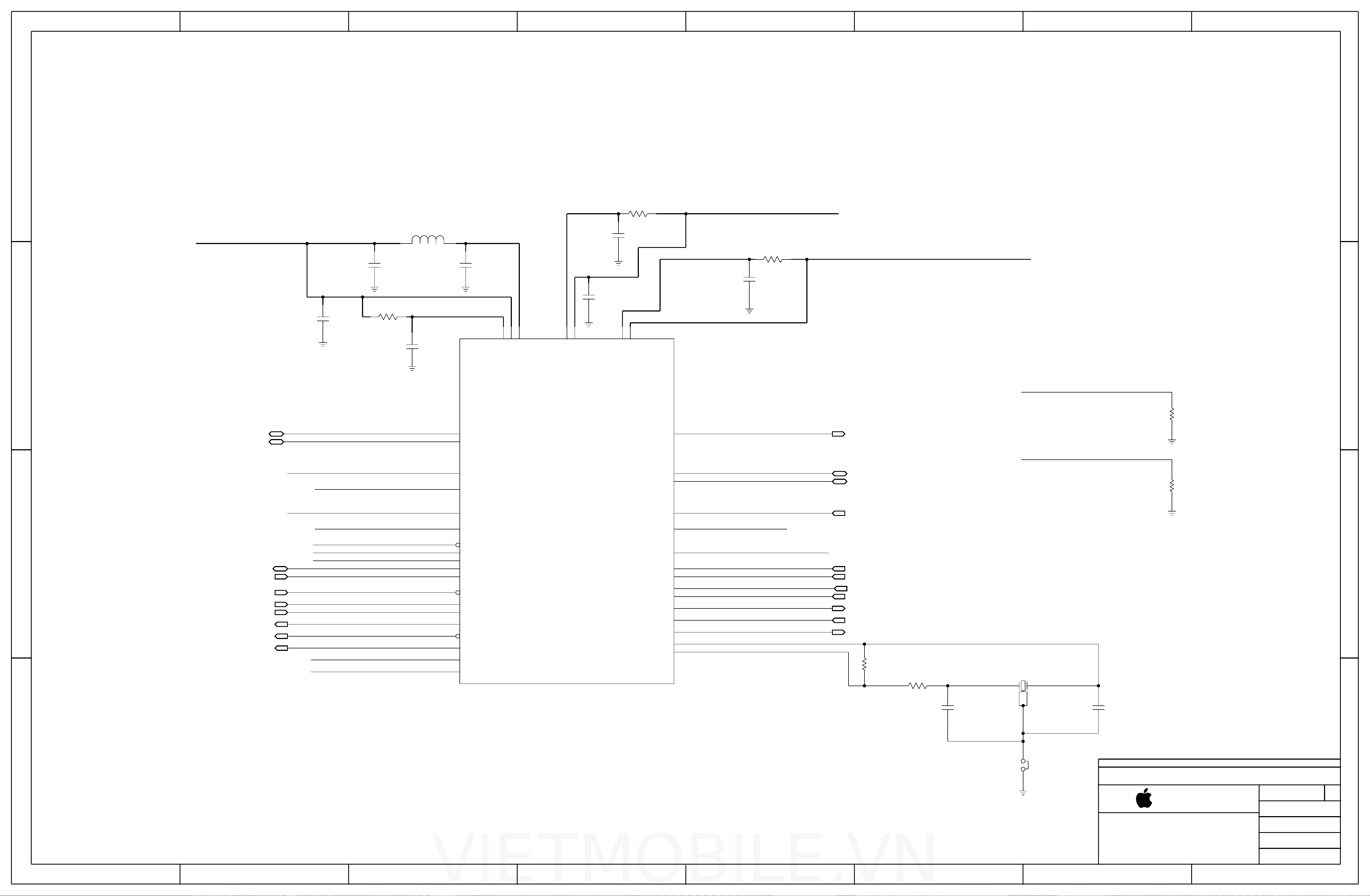

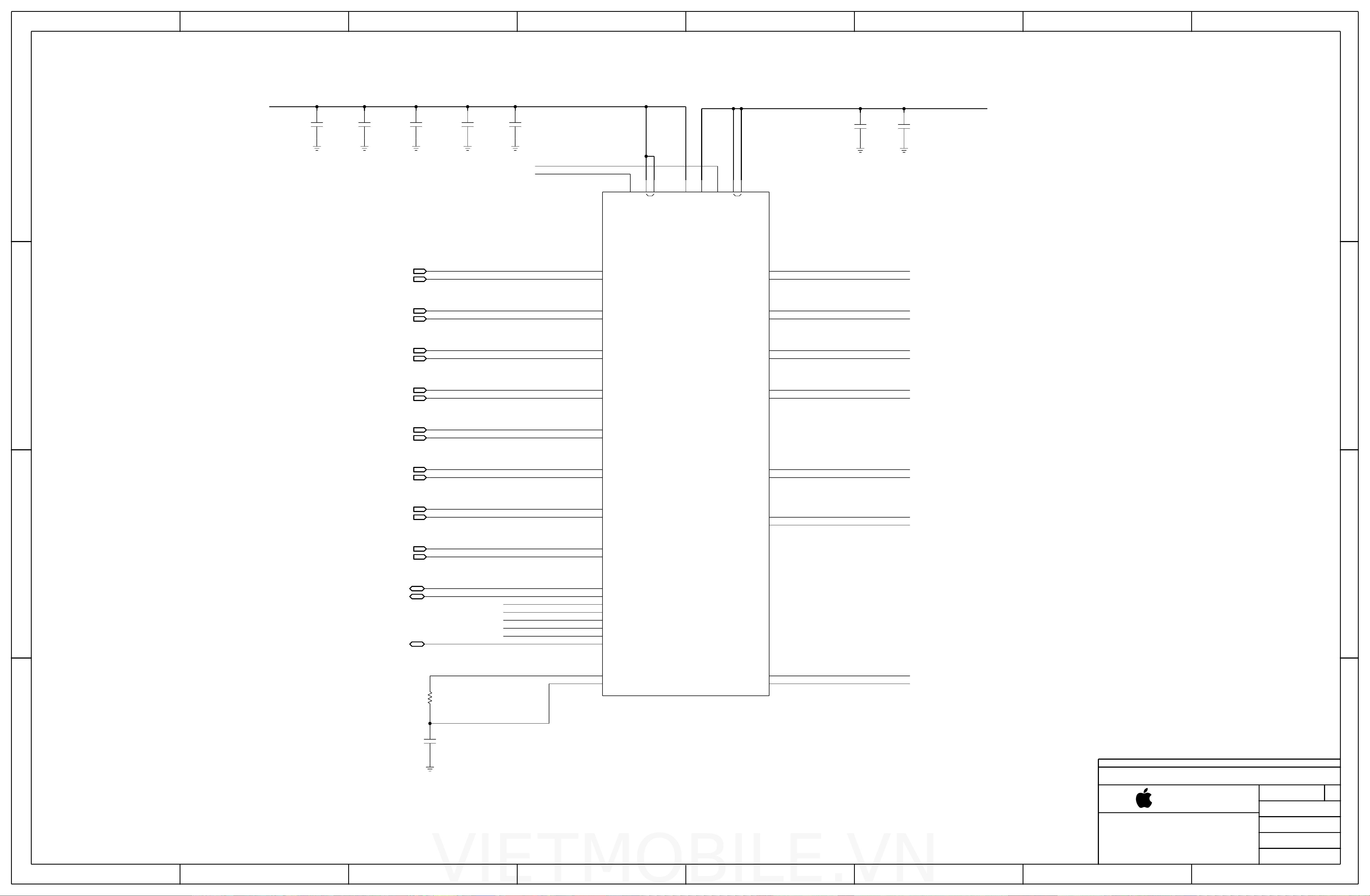

SOC - USB, JTAG, XTAL

VIETMOBILE.VN

678

3 245

1

D

C

VDD18_XTAL:1.06-1.17V @ 2mA MAX

VDD18_USB: 1.62V - 1.98V @ 20mA MAX

PP1V8_IO

15 17

1

C1097

0.1UF

20%

6.3V

2

X5R-CERM

01005

ROOM=SOC

FL1092

240OHM-25%-0.2A-0.9OHM

21

01005

1

C1093

4UF

20%

4V

2

X5R

0201

ROOM=SOC

ROOM=SOC

R1093

0.00

1/32W

01005

ROOM=SOC

0%

MF

21

1

C1090

0.1UF

20%

6.3V

2

X5R-CERM

01005

ROOM=SOC

PP1V8_USB_DEBUG

PP1V8_XTAL

1

C1092

0.1UF

20%

6.3V

2

X5R-CERM

01005

ROOM=SOC

AP27

AP13

AP15

VDD18_USB

VDD18_XTAL

7

PP3V3_USB_DEBUG

C1096

0.1UF

20%

6.3V

X5R-CERM

01005

ROOM=SOC

1

C1095

0.1UF

20%

6.3V

2

X5R-CERM

01005

ROOM=SOC

AP14

AR14

VDD33_USB

R1090

1

2

AM14

0.00

0%

1/32W

MF

01005

ROOM=SOC

AM15

D

VDD33_USB*: 3.14-3.46V @ 12mA MAX

21

R1091

PP0V8_USB_DEBUG

C1098

0.1UF

20%

6.3V

X5R-CERM

01005

ROOM=SOC

0.00

1

2

1/32W

01005

ROOM=SOC

21

0%

MF

PP3V3_USB

17

(Analog)

VDD_FIXED_USB*: 0.765V - 0.84V @ 5mA MAX

PP0V8_SOC_FIXED_S1

8 9 10 14 17

C

USB Reference

B

CONNECTED TO GND OFFPAGE ON MLB

CONNECTED TO GND OFFPAGE ON MLB

CONNECTED TO GND OFFPAGE ON MLB

49

49

49

49

57 23 15 7

49 23 5

57 23 15 7

23 5

19 5

19

BI

BI

90_USB_DBG_DATA_P

90_USB_DBG_DATA_N

PP3V3_USB_DEBUG

7

NC_DBG_USB_ID

DBG_USB_VBUS_REXT

7

GND

17

NC_JTAG_TRST_L

NC_JTAG_TDO

NC_JTAG_TDI

SWD_DOCK_BI_AP_SWDIO

BI

SWD_DOCK_TO_AP_SWCLK

IN

PMU_TO_SYSTEM_COLD_RESET_L

IN

PMU_TO_AP_HYDRA_ACTIVE_READY

IN

PMU_TO_SYSTEM_COLD_RESET_L

IN

AP_TO_PMU_TEST_CLKOUT

OUT

AP_TO_NAND_RESET_L

OUT

AP_TO_NAND_FW_STRAP

OUT

GND

17

GND

17

AY16

AW16

AU13

AT13

AT14

AP33

AP32

AR34

AP30

AP29

AR35

AP28

H2

AR33

G37

J4

J5

AE2

AE3

VDD18_USB_DEBUG

DBG_USB_DP

DBG_USB_DM

DBG_USB_VBUS

DBG_USB_ID

DBG_USB_REXT

JTAG_SEL

JTAG_TRST*

JTAG_TDO

JTAG_TDI

JTAG_TMS

JTAG_TCK

COLD_RESET*

CFSB

CFSB_AON

TST_CLKOUT

SSD_RESET*

SSD_BFH

HOLD_RESET

TESTMODE

ALT_FUNC

CTM_TRIGGER

VDD33_USB_DEBUG

U1000

CYP-4GB-M-TMJA47A0-C7

WLCSP

SYM 1 OF 16

ROOM=SOC

CRITICAL

OMIT_TABLE

VDD_FIXED_USB

VDD_FIXED_USB_DEBUG

XI0

AJ35

AW17

AY17

AT15

AU15

AU14

N3

N2

N5

N4

P4

P2

AP23

AY25

AW25

ANALOGMUX_OUT

USB_DP

USB_DM

USB_VBUS

USB_ID

USB_REXT

CPU_TRIGGER0

CPU_TRIGGER1

GPU_TRIGGER0

GPU_TRIGGER1

SOCHOT1

DROOP

WDOG

XO0

AP_TO_PMU_AMUX_OUT

90_USB_AP_DATA_P

90_USB_AP_DATA_N

USB_VBUS_DETECT

NC_AP_USB_ID

AP_USB_REXT

PMU_TO_AP_THROTTLE_PCORE_L

PMU_TO_AP_THROTTLE_ECORE_L

PMU_TO_AP_THROTTLE_GPU0_L

PMU_TO_AP_THROTTLE_GPU1_L

AP_TO_PMU_SOCHOT_L

PMU_TO_AP_PRE_UVLO_L

AP_TO_PMU_WDOG_RESET

XTAL_AP_24M_IN

XTAL_AP_24M_OUT

7

OUT

BI

BI

IN

IN

IN

IN

OUT

IN

OUT

AP_USB_REXT

7

1

R1000

200

1%

1/32W

MF

01005

2

23

26

49

49

DBG_USB_VBUS_REXT

7

ROOM=SOC

1

R1001

200

1%

1/32W

MF

01005

2

ROOM=SOC

B

23

23

23

IN

55

23

23 12 5

23

NOSTUFF

1

R1010

511K

1%

1/32W

MF

01005

2

ROOM=SOC

R1011

1.00K

5%

1/32W

MF

01005

ROOM=SOC

24MHZ-30PPM-9.5PF-60OHM

21

SOC_24M_O

1

C1010

12PF

5%

16V

2

CERM

01005

ROOM=SOC

CRITICAL

ROOM=SOC

Y1000

1.60X1.20MM-SM

NC GND

4312

XTAL_GND

1

C1011

12PF

5%

16V

2

CERM

01005

ROOM=SOC

A

8

67

OMIT

SHORT-20L-0.05MM-SM

XW1001

ROOM=SOC

2

SYNC_MASTER=test_mlb

PAGE TITLE

1

SOC: JTAG,USB,XTAL

DRAWING NUMBER

SYNC_DATE=10/17/2016

SIZE

051-02545

Apple Inc.

REVISION

A

D

7.0.0

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

35 4

2

BRANCH

PAGE

10 OF 85

SHEET

7 OF 60

1

Page 13

D

VIETMOBILE.VN

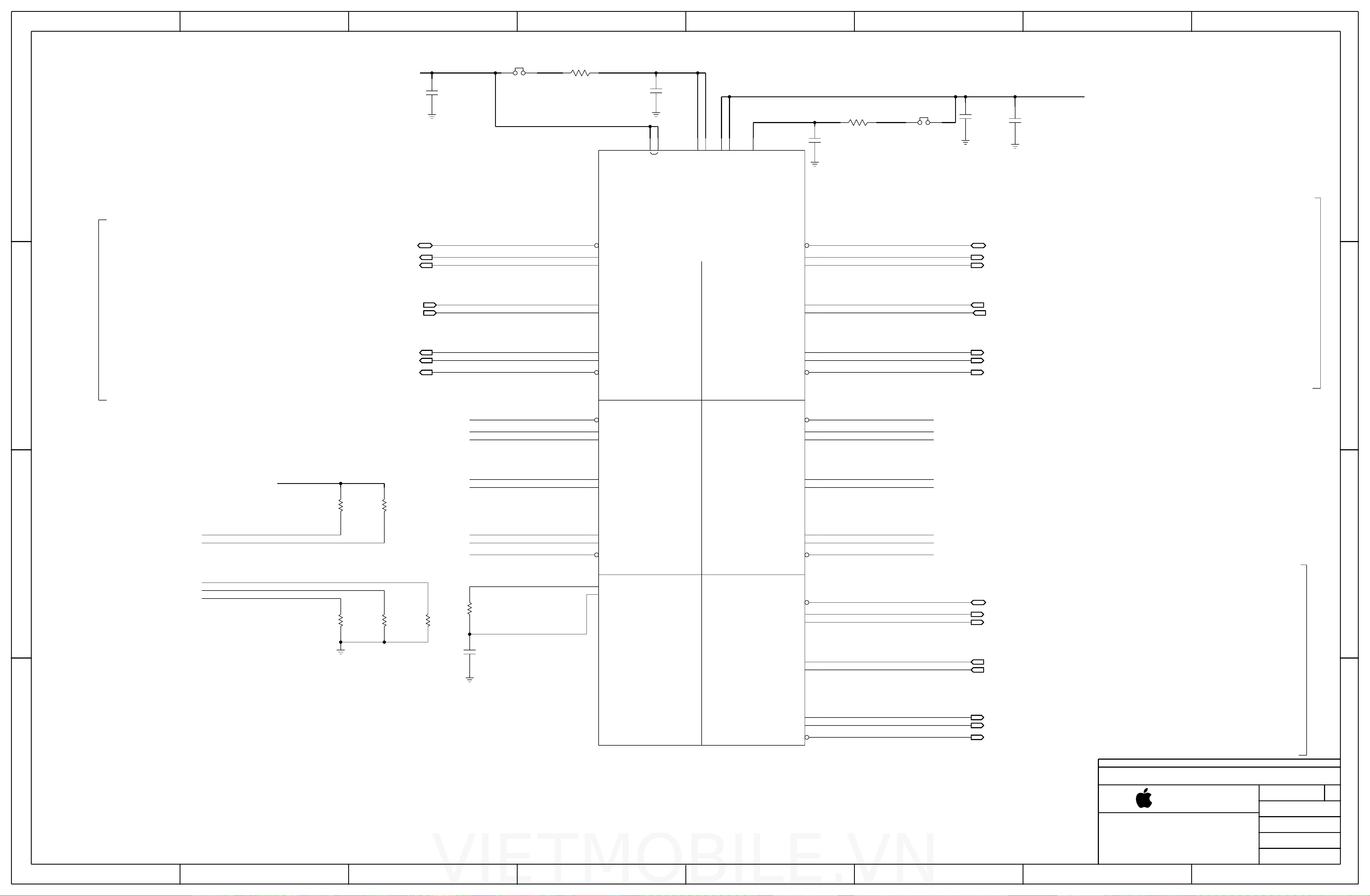

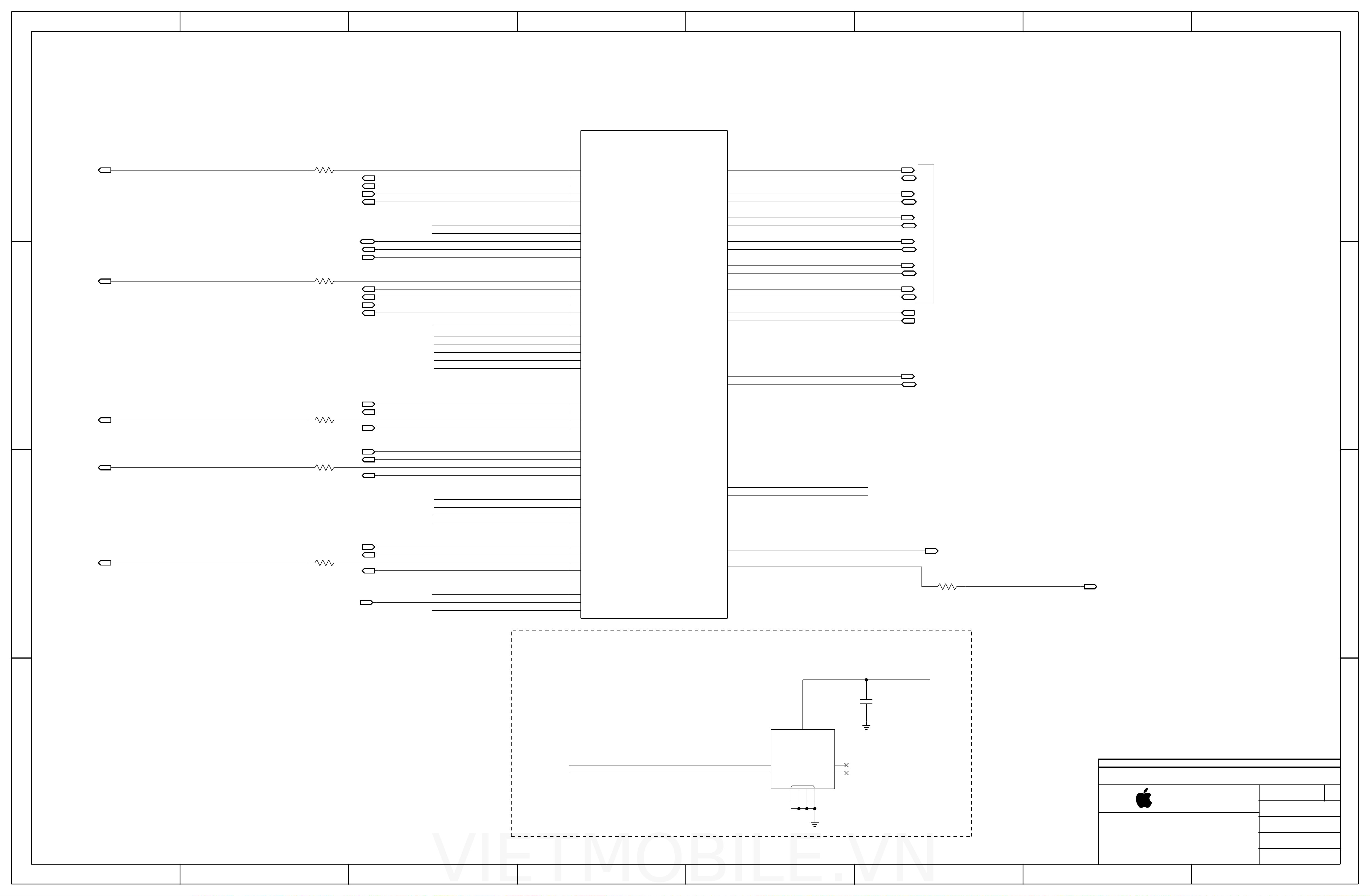

SOC - PCIE

PP1V2_SOC

10 17

C1199

2.2UF

20%

6.3V

X5R-CERM

0201

ROOM=SOC

678

VDD12_PCIE:1.14V - 1.26V @ 130mA MAX

VDD12_PCIE_REFBUF:1.14V - 1.26V @ 30mA MAX

OMIT

XW1101

SHORT-20L-0.05MM-SM

2 1

1

2

ROOM=SOC

PP1V2_SOC_PCIE_REFBUF_XW

R1195

0.00

0%

1/32W

MF

01005

ROOM=SOC

21

PP1V2_SOC_PCIE_REFBUF

1

C1198

0.1UF

20%

6.3V

2

X5R-CERM

01005

ROOM=SOC

AM31

AM29

AK27

AL26

AL30

AL28

PP0V8_SOC_FIXED_PCIE_REFBUF

AL27

1

C1194

0.1UF

20%

6.3V

2

X5R-CERM

01005

ROOM=SOC

VDD_FIXED_PCIE_REFBUF:0.769V - 0.85V @ 65mA MAX

R1194

0.00

1/32W

01005

21

0%

MF

ROOM=SOC

VDD_FIXED_PCIE:0.769V - 0.85V @ 105mA MAX

PP0V8_SOC_FIXED_PCIE_REFBUF_XW

3 245

OMIT

XW1100

SHORT-20L-0.05MM-SM

2 1

ROOM=SOC

1

C1193

0.1UF

20%

6.3V

2

X5R-CERM

01005

ROOM=SOC

PP0V8_SOC_FIXED_S1

1

C1191

2.2UF

20%

6.3V

2

X5R-CERM

0201

1

7 9 10 14 17

D

VDD12_PCIE

VDD_FIXED_PCIE0

VDD_FIXED_PCIE1

VDD12_PCIE_REFBUF

VDD12_PCIE_REFBUF

VDD_FIXED_PCIE_REFBUF

U1000

19 8

19 5

19 5

17 17

17

PCIE_NAND_BI_AP_CLKREQ_L

BI

90_PCIE_AP_TO_NAND_REFCLK_P

OUT

90_PCIE_AP_TO_NAND_REFCLK_N

OUT

90_PCIE_NAND_TO_AP_RXD_C_P

IN IN

90_PCIE_NAND_TO_AP_RXD_C_N

IN

U37

AW19

AY19

AY27

AW27

PCIE_CLKREQ0*

PCIE_REF_CLK0_P

PCIE_REF_CLK0_N

PCIE_RX0_P

PCIE_RX0_N

CYP-4GB-M-TMJA47A0-C7

WLCSP

SYM 2 OF 16

PCIE_CLKREQ3*

PCIE_REF_CLK3_P

PCIE_REF_CLK3_N

PCIE_RX3_P

PCIE_RX3_N

U34

AY22

AW22

AY33

AW33

PCIE_WLAN_BI_AP_CLKREQ_L

90_PCIE_AP_TO_WLAN_REFCLK_P

90_PCIE_AP_TO_WLAN_REFCLK_N

90_PCIE_WLAN_TO_AP_RXD_C_P

90_PCIE_WLAN_TO_AP_RXD_C_N

BI

OUT

OUT

58 8

58

58

17

IN

PCIE LINK 3

C

B

PCIE LINK 0

PCIe BB CLKREQ PU on BB domain

PCIe Clock Request Pull-Ups

PP1V8_IO

17

1

2

R1130

100K

1/32W

01005

ROOM=SOC

PCIE_NAND_BI_AP_CLKREQ_L

19 8

PCIE_WLAN_BI_AP_CLKREQ_L

58 8

R1100

100K

5%

1/32W

MF

01005

ROOM=SOC

PCIe Reset Pull-Downs

5%

MF

17

17

19 8

1

2

90_PCIE_AP_TO_NAND_TXD_C_P

OUT

90_PCIE_AP_TO_NAND_TXD_C_N

OUT

PCIE_AP_TO_NAND_PERST_L

OUT

NC_PCIE1_CLKREQ1_L

NC_PCIE1_REF_CLK_P

NC_PCIE1_REF_CLK_N

NC_PCIE1_RX1_P

NC_PCIE1_RX1_N

NC_PCIE1_TX1_P

NC_PCIE1_TX1_N

NC_PCIE1_PERST_L

AU26

AV26

T36

AW20

AY20

AY29

AW29

AU28

AV28

PCIE_TX0_P

PCIE_TX0_N

PCIE_CLKREQ1*

PCIE_REF_CLK1_P

PCIE_REF_CLK1_N

PCIE_RX1_P

PCIE_RX1_N

PCIE_TX1_P

PCIE_TX1_N

PCIE_PERST1*

Hardwired as Input

NAND LINK

PCIE_TX3_P

PCIE_TX3_N

PCIE_PERST3*PCIE_PERST0*

LINK3

PCIE_CLKREQ2*

PCIE_REF_CLK2_P

PCIE_REF_CLK2_N

PCIE_RX2_P

PCIE_RX2_N

PCIE_TX2_P

PCIE_TX2_N

PCIE_PERST2*

LINK1 LINK2

AU32

AV32

R37

U35U36

AW21

AY21

AY31

AW31

AU30

AV30

T34T35

90_PCIE_AP_TO_WLAN_TXD_C_P

90_PCIE_AP_TO_WLAN_TXD_C_N

PCIE_AP_TO_WLAN_PERST_L

NC_PCIE2_CLKREQ1_L

NC_PCIE2_REF_CLK_P

NC_PCIE2_REF_CLK_N

NC_PCIE2_RX1_P

NC_PCIE2_RX1_N

NC_PCIE2_TX1_P

NC_PCIE2_TX1_N

NC_PCIE2_PERST_L

OUT

OUT

OUT

17

17

57 8

C

B

PCIE_AP_TO_WLAN_PERST_L

57 8

PCIE_AP_TO_BB_PERST_L

57 8

PCIE_AP_TO_NAND_PERST_L

19 8

R1101

100K

5%

1/32W

MF

01005

ROOM=SOC

1

2

R1121

100K

5%

1/32W

MF

01005

ROOM=SOC

1

2

R1131

100K

5%

1/32W

MF

01005

ROOM=SOC

PCIE_RCAL_POS

1

R1140

1

2

200

1%

1/32W

MF

01005

2

ROOM=SOC

1

C1140

10PF

5%

16V

2

CERM

01005

ROOM=SOC

PCIE_RCAL_NEG

AT31

AR31

PCIE_RCAL_P

PCIE_RCAL_N

PCIE_CLKREQ4*

PCIE_REF_CLK4_P

PCIE_REF_CLK4_N

PCIE_RX4_P

PCIE_RX4_N

T37

AY23

AW23

AY35

AW35

PCIE_BB_BI_AP_CLKREQ_L

90_PCIE_AP_TO_BB_REFCLK_P

90_PCIE_AP_TO_BB_REFCLK_N

90_PCIE_BB_TO_AP_RXD_C_P

90_PCIE_BB_TO_AP_RXD_C_N

BI

OUT

OUT

IN

IN

57

57

57

17 5

17 5

PCIE LINK 4

LINK4

PCIE_TX4_P

PCIE_TX4_N

PCIE_PERST4*

AU34

AV34

R35

90_PCIE_AP_TO_BB_TXD_C_P

90_PCIE_AP_TO_BB_TXD_C_N

PCIE_AP_TO_BB_PERST_L

OUT

OUT

OUT

17

17

57 8

A

8

67

SYNC_DATE=04/07/2017

PAGE TITLE

A

SOC: PCIE

DRAWING NUMBER

051-02545

Apple Inc.

REVISION

7.0.0

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

35 4

2

BRANCH

PAGE

11 OF 85

SHEET

8 OF 60

1

SIZE

D

Page 14

SOC - MIPI

VIETMOBILE.VN

678

NEED MIPI LANE AND POLAIRTY SWAPPING MAP

3 245

1

D

(Analog)

VDD_FIXED_MIPID 0.769V - 0.85V @ TBDmA MAX

VDD_FIXED_MIPIC 0.769V - 0.85V @ TBDmA MAX

VDD_FIXED_MIPID_PLL 0.769V - 0.85V @ TBDmA MAX

PP0V8_SOC_FIXED_S1

7 8 10 14 17

20%

6.3V

1

2

F17

C1291

2.2UF

20%

6.3V

X5R-CERM

0201

ROOM=SOC

1

C1290

0.1UF

2

X5R-CERM

01005

ROOM=SOC

AM9

AP9

AL10

G18

VDD18_MIPIC

VDD18_MIPID

1

C1296

0.1UF

20%

6.3V

2

X5R-CERM

01005

ROOM=SOC

1

C1295

2.2UF

20%

6.3V

2

X5R-CERM

0201

ROOM=SOC

VDD18_MIPI*:1.62V - 1.98V @ TBDmA MAX

PP1V8_IO

D

17

C

MIPI lanes can all flip polarity for routing purposes

GNDed offpage on MLB

37

BI

37

BI

37

IN

37

IN

37

IN

37

IN

Juliet MIPI

17

IN

17

BI

17

BI

17

IN

17

IN

17

IN

17

IN

44

BI

44

BI

90_MIPI_JULIET_TO_AP_DATA0_P

90_MIPI_JULIET_TO_AP_DATA0_N

90_MIPI_JULIET_TO_AP_DATA1_P

90_MIPI_JULIET_TO_AP_DATA1_N

90_MIPI_JULIET_TO_AP_CLK_P

90_MIPI_JULIET_TO_AP_CLK_N

MIPI0C_REXT

9

GND

GND

GND

GND

GND

GND

GND

90_MIPI_AP_TO_DISPLAY_DATA0_P

90_MIPI_AP_TO_DISPLAY_DATA0_N

B9

A9

A11

B11

B10

A10

D11

D10

A8

B8

B6

A6

A7

B7

AY8

AW8

MIPI0C_DPDATA0

MIPI0C_DNDATA0

MIPI0C_DPDATA1

MIPI0C_DNDATA1

MIPI0C_DPCLK

MIPI0C_DNCLK

MIPI0C_REXT

MIPI1C_REXT

MIPI1C_DPDATA0

MIPI1C_DNDATA0

MIPI1C_DPDATA1

MIPI1C_DNDATA1

MIPI1C_DPCLK

MIPI1C_DNCLK

MIPID_DPDATA0

MIPID_DNDATA0

< CANT SWAP DUE TO BiDi

< CANT SWAP DUE TO BiDi

VDD_FIXED_MIPIC

VDD_FIXED_MIPID

VDD_FIXED_MIPID_PLL

U1000

CYP-4GB-M-TMJA47A0-C7

WLCSP

SYM 3 OF 16

ALT FUNC's

SIO_LEAP_MADI_IN and AOP_LEAP_MADI_IN

SIO_LEAP_MADI_OUT and AOP_LEAP_MADI_OUT

MTR_ADC_DOUT and

MTR_ADC_CLKOUT and SOC_DEBUG3

PLL_DIGOBS_IN_0 and

PLL_DIGOBS_IN_1 and

ISP_FCAM_SPMI_SDATA

ISP_FCAM_SPMI_SCLK

SOC_DEBUG2

SENSOR3_CLK

ISP_SPMI_SDATA

ISP_SPMI_SCLK

ISP_I2C0_SCL

ISP_I2C0_SDA

ISP_I2C1_SCL

ISP_I2C1_SDA

ISP_I2C2_SCL

ISP_I2C2_SDA

ISP_I2C3_SCL

ISP_I2C3_SDA

ISP_GPIO_0

ISP_GPIO_1

ISP_GPIO_2

ISP_GPIO_3

ISP_GPIO_4

ISP_GPIO_5

ISP_GPIO_6

ISP_GPIO_7

ISP_GPIO_8

ISP_GPIO_9

A16

C21

A17

B20

A18

C22

A19

A20

A23

A22

A21

B22

A15

B19

C20

A13

B13

D20

ISP_TO_WIDE_SHUTDOWN_L

ISP_TO_TELE_SHUTDOWN_L

NC_ISP_GPIO_3

ISP_TO_FCAM_SHUTDOWN_L

ISP_TO_JULIET_SHUTDOWN_L

NC_ISP_GPIO_7

ISP_TO_DISPLAY_FLASH_INT

I2C0_ISP_SCL

I2C0_ISP_SDA

I2C1_ISP_SCL

I2C1_ISP_SDA

I2C2_ISP_SCL

I2C2_ISP_SDA

I2C3_ISP_SCL

I2C3_ISP_SDA

SOC_DEBUG2

SOC_DEBUG3

RIGEL_TO_ISP_INT

OUT

BI

OUT

BI

OUT

BI

OUT

BI

OUT

OUT

OUT

OUT

OUT

OUT

OUT

53

53

53

53

53

53

53

53

31

32

5

5

34

37

44

IN

36 23 5

C

B

Display MIPI

44

44

44

44

44

44

44

44

57

44

90_MIPI_AP_TO_DISPLAY_DATA1_P

OUT

90_MIPI_AP_TO_DISPLAY_DATA1_N

OUT

90_MIPI_AP_TO_DISPLAY_DATA2_P

OUT

90_MIPI_AP_TO_DISPLAY_DATA2_N

OUT

90_MIPI_AP_TO_DISPLAY_DATA3_P

OUT

90_MIPI_AP_TO_DISPLAY_DATA3_N

OUT

90_MIPI_AP_TO_DISPLAY_CLK_P

BI

90_MIPI_AP_TO_DISPLAY_CLK_N

OUT

OUT

NC_DISP_BSYNC1

DISPLAY_TO_AP_BSYNC_WATCHDOG

IN

MIPID_REXT

9

NC_DISP_I2C_SCL

NC_DISP_I2C_SDA

AW7

AY7

AW5

AY5

AW4

AY4

AY6

AW6

AG4

AH3

AH4

AU9

AG3

AG2

MIPID_DPDATA1

MIPID_DNDATA1

MIPID_DPDATA2

MIPID_DNDATA2

MIPID_DPDATA3

MIPID_DNDATA3

MIPID_DPCLK

MIPID_DNCLK

DISP_TOUCH_BSYNC0

DISP_TOUCH_BSYNC1

DISP_TOUCH_EB

MIPID_REXT

ALT FUNC's

DISP_I2C_SCL

DISP_I2C_SDA

DISP_SPMI_SCLK

DISP_SPMI_SDATA

SENSOR0_CLK

SENSOR1_CLK

SENSOR2_CLK

A14

B14

B17

R1240

AP_TO_WIDE_CLK_R

AP_TO_TELE_CLK_R

AP_TO_FCAM_JULIET_RIGEL_CLK_RAP_TO_TOUCH_SCAN_CLK

33.2

1/32W

01005

ROOM=SOC

17

17

21

1%

MF

Series Terminations Offpage

AP_TO_WIDE_CLK

OUT

31

B

A

MIPI Reference

200

1%

1/32W

MF

01005

ROOM=SOC

1

2

R1250

200

1%

1/32W

MF

01005

ROOM=SOC

1

2

R1251

GNDed offpage on MLB

MIPI0C_REXT

MIPID_REXT

9

9

NC_DISP_POL

GND

17

AE5

AA2

DISP_POL

DISP_TE

PAGE TITLE

SOC: MIPI

Apple Inc.

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

DRAWING NUMBER

051-02545

REVISION

7.0.0

BRANCH

PAGE

12 OF 85

SHEET

9 OF 60

A

SIZE

D

8

67

35 4

2

1

Page 15

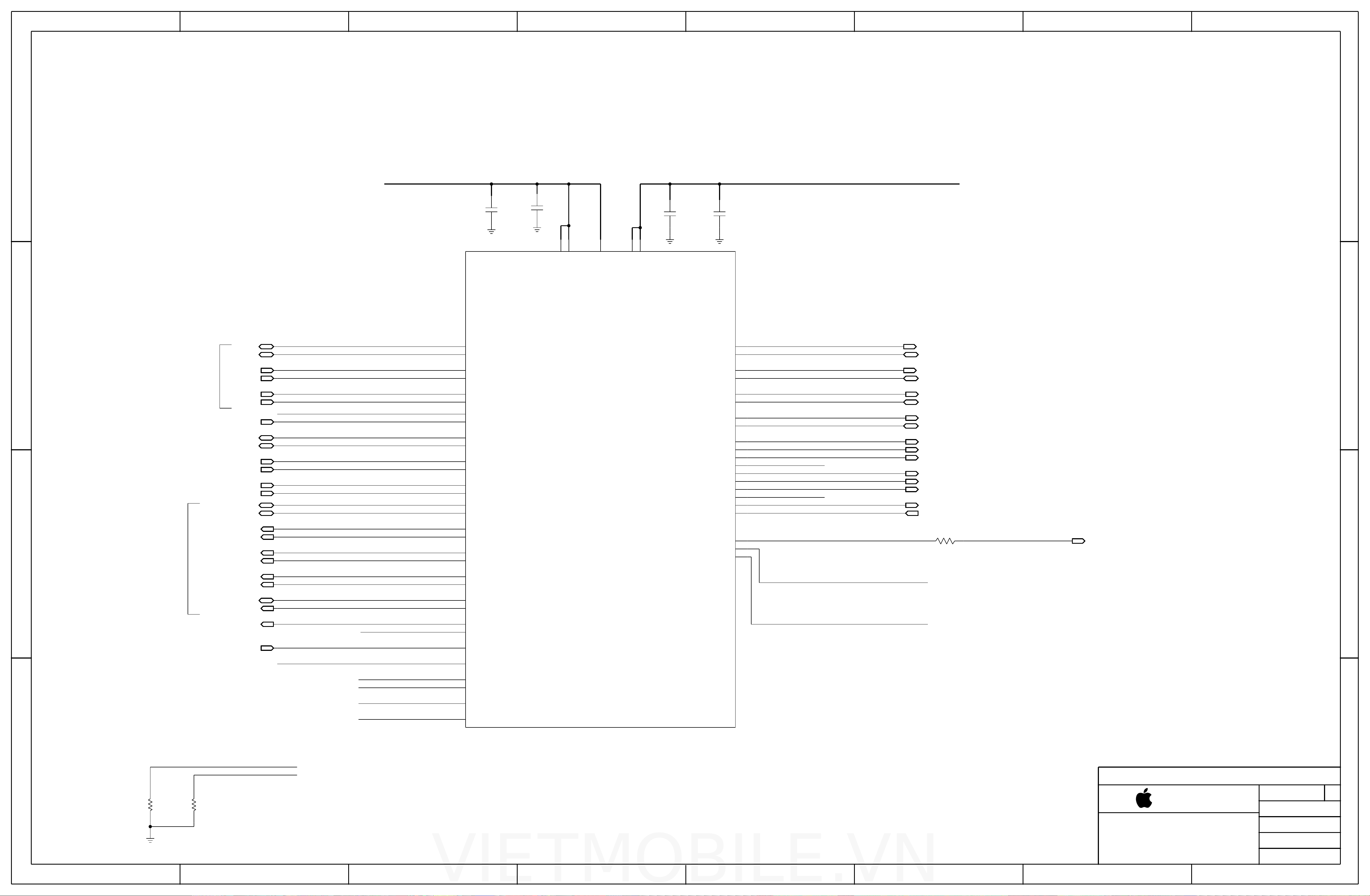

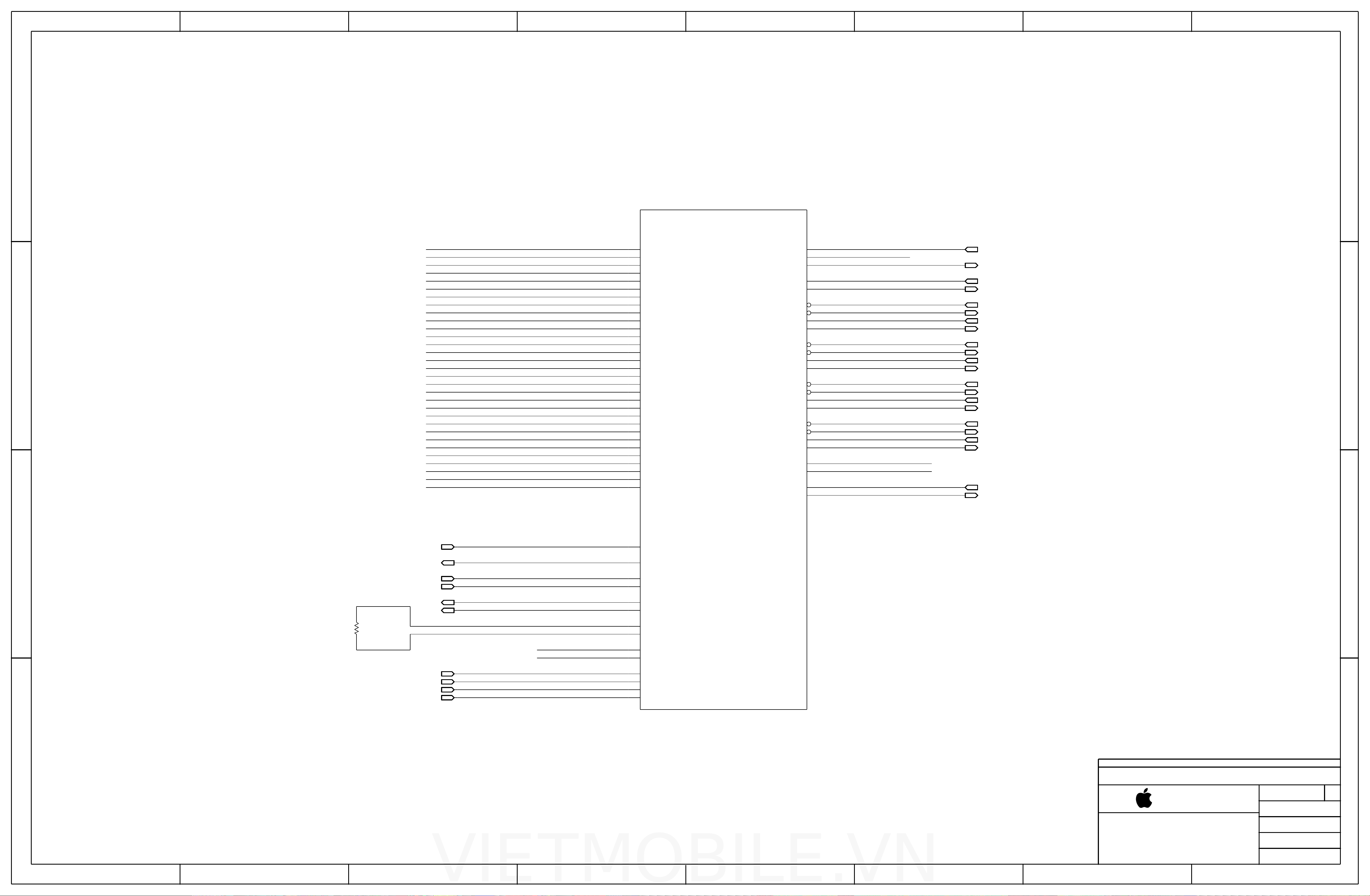

SOC - LPDP

VIETMOBILE.VN

678

3 245

1

D

VDD12_PLL_LPDP 1.14V - 1.26V @ 8mA MAX

VDD12_LPDP_RX 1.14V - 1.26V @ 60mA MAX

PP1V2_SOC

8 17

Dan LPDP Lane Assignment

1

C1390

2.2UF

20%

6.3V

2

X5R-CERM

0201

ROOM=SOC

1

C1391

2.2UF

20%

6.3V

2

X5R-CERM

0201

ROOM=SOC

1

C1392

0.1UF

20%

6.3V

2

X5R-CERM

01005

ROOM=SOC ROOM=SOC

1

2

GND'd offpage

GND'd offpage

C1393

0.01UF

10%

6.3V

X5R

01005

1

C1394

15PF

5%

16V

2

NP0-C0G-CERM

01005

ROOM=SOC

Desense for Wifi frequencies

GND

17

GND

17

AM10

VDD12_LPDP_TX

F29

F27

VDD12_LPDP_RX

AM11

AM12

AM13

VDD12_PLL_LPDP

VDD_FIXED_LPDP_TX

VDD_FIXED_PLL_LPDP

VDD_FIXED_PLL_LPDP 0.769V - 0.85V @ 4mA MAX

VDD_FIXED_LPDP_RX 0.769V - 0.85V @ 50mA MAX

G28

F31

VDD_FIXED_LPDP_RX

1

C1395

2.2UF

20%

6.3V

2

X5R-CERM

0201

ROOM=SOC

(Analog)

PP0V8_SOC_FIXED_S1

1

C1396

2.2UF

20%

6.3V

2

X5R-CERM

0201

ROOM=SOC

7 8 9 14 17

D

C

Wide: 0-2

Tele: 3-5

Fcam: 6-7

Justin LPDP Lane Assignment

Wide: 2-4

Tele: 5-7

Fcam: 0-1

LPD Assigned off page

18

18

18

18

18

18

18

18

18

18

90_LPDP_WIDE_TO_AP_D0_P

IN

90_LPDP_WIDE_TO_AP_D0_N

IN

90_LPDP_WIDE_TO_AP_D1_P

IN

90_LPDP_WIDE_TO_AP_D1_N

IN

90_LPDP_WIDE_TO_AP_D2_P

IN

90_LPDP_WIDE_TO_AP_D2_N

IN

90_LPDP_TELE_TO_AP_D0_P

IN

90_LPDP_TELE_TO_AP_D0_N

IN

90_LPDP_TELE_TO_AP_D1_P

IN

90_LPDP_TELE_TO_AP_D1_N

IN

A25

B25

B26

C26

A27

B27

B28

C28

B30

C30

LPDPRX_RX_D0_P

LPDPRX_RX_D0_N

CYP-4GB-M-TMJA47A0-C7

LPDPRX_RX_D1_P

LPDPRX_RX_D1_N

LPDPRX_RX_D2_P

LPDPRX_RX_D2_N

LPDPRX_RX_D3_P

LPDPRX_RX_D3_N

LPDPRX_RX_D4_P

LPDPRX_RX_D4_N

U1000

WLCSP

SYM 4 OF 16

LPDP_TX0P

LPDP_TX0N

LPDP_TX1P

LPDP_TX1N

LPDP_TX2P

LPDP_TX2N

LPDP_TX3P

LPDP_TX3N

AY14

AW14

AY13

AW13

AY12

AW12

AY11

AW11

NC_LPDP_TX0_P

NC_LPDP_TX0_N

NC_LPDP_TX1_P

NC_LPDP_TX1_N

NC_LPDP_TX2_P

NC_LPDP_TX2_N

NC_LPDP_TX3_P

NC_LPDP_TX3_N

C

B

31

32

34

18

18

18

18

18

18

90_LPDP_TELE_TO_AP_D2_P

IN

90_LPDP_TELE_TO_AP_D2_N

IN

90_LPDP_FCAM_TO_AP_D0_P

IN

90_LPDP_FCAM_TO_AP_D0_N

IN

90_LPDP_FCAM_TO_AP_D1_P

IN

90_LPDP_FCAM_TO_AP_D1_N

IN

LPDP_WIDE_BI_AP_AUX

BI

LPDP_TELE_BI_AP_AUX

BI

LPDP_FCAM_BI_AP_AUX

BI

NC_LPDP_D2_AUX

NC_LPDP_D3_AUX

NC_LPDP_D4_AUX

NC_LPDP_D5_AUX

NC_LPDP_D6_AUX

A31

B31

B32

C32

A33

B33

D23

D24

C24

D25

D27

D29

D31

D33

LPDPRX_RX_D5_P

LPDPRX_RX_D5_N

LPDPRX_RX_D6_P

LPDPRX_RX_D6_N

LPDPRX_RX_D7_P

LPDPRX_RX_D7_N

LPDPRX_AUX_D0_P

LPDPRX_AUX_D1_P

LPDPRX_AUX_D2_P

LPDPRX_AUX_D3_P

LPDPRX_AUX_D4_P

LPDPRX_AUX_D5_P

LPDPRX_AUX_D6_P

LPDPRX_AUX_D7_P

LPDP_AUX_P

LPDP_AUX_N

EDP_HPD

DP_WAKEUP

AY10

AW10

AF2

AF4

NC_LPDP_AUX_P

NC_LPDP_AUX_N

NC_EPD_HPD

NC_DP_WAKEUP

B

A

1

R1300

200

1%

1/32W

MF

01005

2

ROOM=SOC

1

C1301

10PF

5%

16V

2

CERM

01005

ROOM=SOC

LPDPRX_RCAL_POS

LPDPRX_RCAL_NEG

A29

B29

LPDPRX_RCAL_P

LPDPRX_RCAL_N

LPDP_RCAL_P

LPDP_RCAL_N

AU10

AT10

NC_LPDP_RCAL_P

NC_LPDP_RCAL_N

PAGE TITLE

SOC: LPDP

Apple Inc.

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

DRAWING NUMBER

051-02545

REVISION

7.0.0

BRANCH

PAGE

13 OF 85

SHEET

10 OF 60

SYNC_DATE=10/13/2016SYNC_MASTER=test_mlb

SIZE

D

A

8

67

35 4

2

1

Page 16

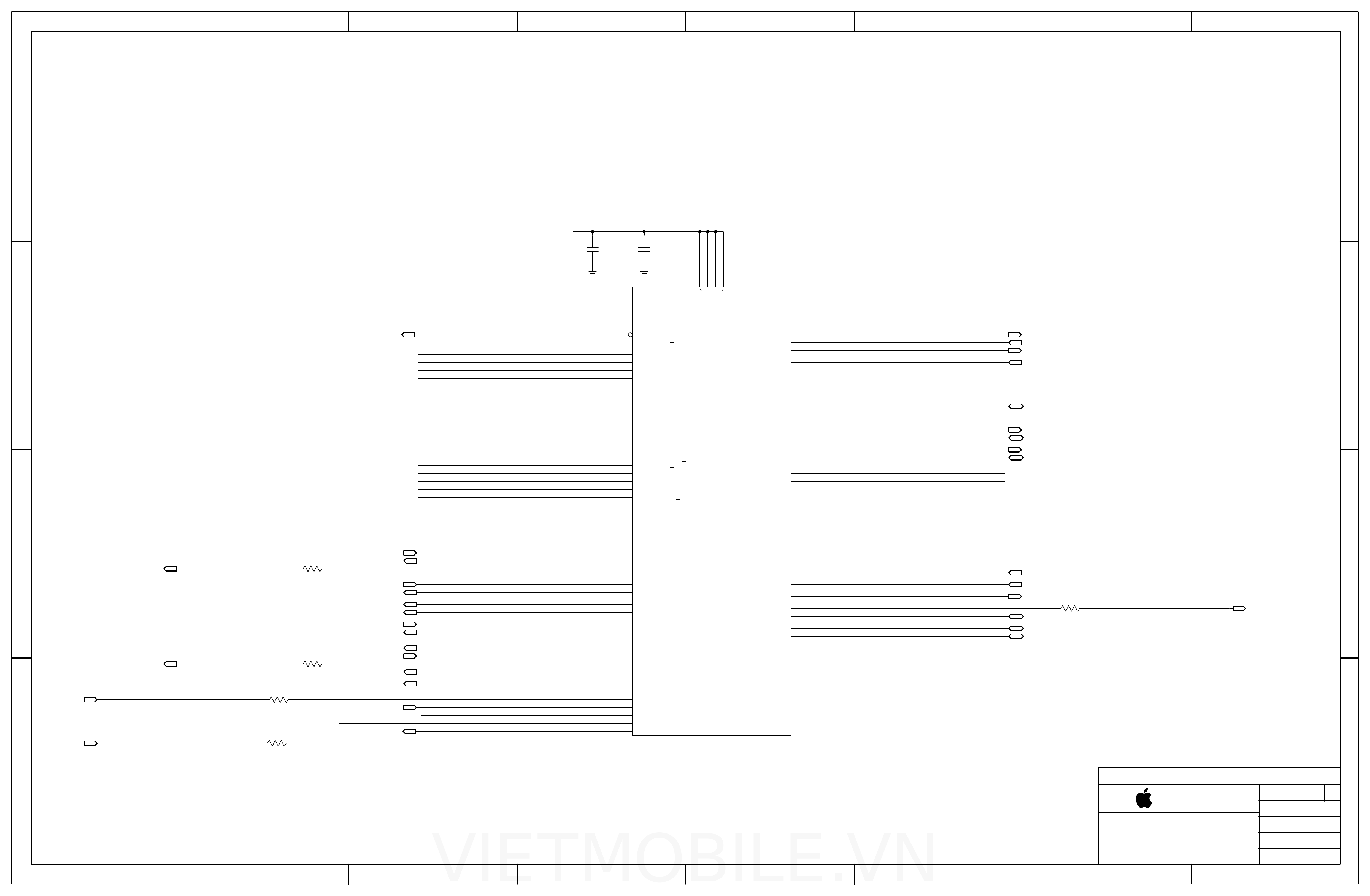

SOC - SERIAL INTERFACES

VIETMOBILE.VN

678

3 245

1

D

40

42

I2S_AP_TO_CODEC_MCLK1

OUT

I2S_AP_TO_SPKAMP_TOP_MCLK

OUT

R1460

33.2

1%

1/32W

MF

01005

ROOM=SOC

R1464

33.2

1%

1/32W

MF

01005

ROOM=SOC

U1000

D

CYP-4GB-M-TMJA47A0-C7

WLCSP

SYM 6 OF 16

21

40

40

40

40

I2S_AP_TO_CODEC_MCLK1_R

I2S_AP_TO_CODEC_ASP3_BCLK

OUT

I2S_AP_TO_CODEC_ASP3_LRCLK

OUT

I2S_CODEC_ASP3_TO_AP_DIN

IN

I2S_AP_TO_CODEC_ASP3_DOUT

OUT

NC_I2S1_MCLK

NC_I2S1_BCLK

48 5

48 5

40

21

57

57

57

57

AP_BI_CCG2_SWDIO

BI

AP_TO_CCG2_SWCLK

OUT

CODEC_TO_AP_INT_L

IN

I2S_AP_TO_SPKAMP_TOP_MCLK_R

I2S_BB_TO_AP_BCLK

OUT

I2S_BB_TO_AP_LRCLK

OUT

I2S_BB_TO_AP_DIN

IN

I2S_AP_TO_BB_DOUT

OUT

NC_AP_PDM_OUT0_DAT

AD35

AD37

AC34

AC35

AC36

AA35

Y37

Y34

Y35

Y36

AC37

AB34

AB35

AB36

AA37

AF36

I2S0_MCK

I2S0_BCLK

I2S0_LRCK

I2S0_DIN

I2S0_DOUT

I2S1_MCK

I2S1_BCLK

I2S1_LRCK

I2S1_DIN

I2S1_DOUT

I2S2_MCK

I2S2_BCLK

I2S2_LRCK

I2S2_DIN

I2S2_DOUT

AP_PDM_OUT0_DAT

GPIO SMC INT 8

GPIO SMC INT 9

I2C0_SCL

I2C0_SDA

I2C1_SCL

I2C1_SDA

I2C2_SCL

I2C2_SDA

I2C3_SCL

I2C3_SDA

SMC_I2CM0_SCL

SMC_I2CM0_SDA

SMC_I2CM1_SCL

SMC_I2CM1_SDA

ALT FUNC'S

SMC_UART0_RXD

SMC_UART0_TXD

C15

D17

L2

K5

K37

L34

M4

M5

AU24

AT24

AU20

AR24

AR23

AT20

CCG2_TO_SMC_INT_L

IKTARA_TO_SMC_INT

I2C0_AP_SCL

I2C0_AP_SDA

I2C1_AP_SCL

I2C1_AP_SDA

I2C2_AP_SCL

I2C2_AP_SDA

I2C3_AP_SCL

I2C3_AP_SDA

I2C0_SMC_SCL

I2C0_SMC_SDA

I2C1_SMC_SCL

I2C1_SMC_SDA

OUT

BI

OUT

BI

OUT

BI

OUT

BI

OUT

BI

OUT

BI

IN

IN

52

52

52

54

60

52

52

52

54

58 52

58 52

60 54

60 54

48 5

I2C bus descriptions on 66-68

C

19 6

58

SPI_AP_TO_S4E_SCLK_BOOT_CONFIG0

OUT

Hardwired as Board_ID3 -->

SPI_AP_TO_RACER_SCLK

OUT

R1465

0.00

0%

1/32W

MF

01005

ROOM=SOC

R1461

0.00

0%

1/32W

MF

01005

ROOM=SOC

21

21

19 6 5

19 6

58

58

58

NC_I2S3_MCK

NC_I2S3_BCLK

NC_I2S3_LRCLK

NC_I2S3_DIN

NC_I2S3_DOUT

SPI_S4E_TO_AP_MISO_BOOT_CONFIG2

IN

SPI_AP_TO_S4E_MOSI_BOOT_CONFIG1

OUT

SPI_AP_TO_S4E_SCLK_BOOT_CONFIG0_R

6

PP1V8_IO

IN

SPI_RACER_TO_AP_MISO

IN

SPI_AP_TO_RACER_MOSI

OUT

SPI_AP_TO_RACER_SCLK_R

SPI_AP_TO_RACER_CS_L

OUT

NC_SPI2_MISO

NC_SPI2_MOSI

NC_SPI2_SCLK

NC_SPI2_CS_L

AF37

AE34

AE35

AE37

AE36

AF34

AG37

AG35

AF35

AH36

AH35

AH34

AH37

V37

W35

W34

V35

I2S3_MCK

I2S3_BCLK

I2S3_LRCK

I2S3_DIN

I2S3_DOUT

SPI0_MISO

SPI0_MOSI

SPI0_SCLK

SPI0_SSIN

SPI1_MISO

SPI1_MOSI

SPI1_SCLK

SPI1_SSIN

SPI2_MISO

SPI2_MOSI

SPI2_SCLK

SPI2_SSIN

AP_PDM_OUT0_CLK

AP_PDM_IN2_CLK

AP_PDM_IN2_DAT

AP_PDM_IN1_DAT

AP_PDM_IN1_CLK

ALT FUNC'S

SPMI SCLK

SPMI SDATA

I2C4_SCL

I2C4_SDA

DWI_CLK

DWI_DO

G35

G34

J2

J3

I2C4_AP_SCL

I2C4_AP_SDA

NC_DWI_PMGR_TO_BACKLIGHT_CLK

NC_DWI_PMGR_TO_BACKLIGHT_DATA

17

17

OUT

BI

C

52

52

B

40

SPI_AP_TO_CODEC_SCLK

OUT

SPI: Route as Daisy-Chain. No T's Allowed

Place series terminations close to SoC Pins

R1462

0.00

0%

1/32W

MF

01005

ROOM=SOC

40 5

40 5

21

40

SPI_CODEC_TO_AP_MISO

IN

SPI_AP_TO_CODEC_MOSI

OUT

SPI_AP_TO_CODEC_SCLK_R

SPI_AP_TO_CODEC_CS_L

OUT

AD5

AD3

AD2

AD4

SPI3_MISO

SPI3_MOSI

SPI3_SCLK

SPI3_SSIN

CLK24M_OUT

NAND_SYS_CLK

AP21

W36

AP_TO_RACER_REF_CLK_R

AP_TO_NAND_SYS_CLK_R

OUT

17

Series Terminations Offpage

B

R1480

23

NC_SPI4_MISO

PMU_TO_AP_DOUBLE_CLICK_DET_L

IN

NC_SPI4_SCLK

E37

F35

F37

SPI4_MISO

SPI4_MOSI

SPI4_SCLK

0.00

1/32W

01005

ROOM=SOC

21

0%

MF

AP_TO_NAND_SYS_CLK

OUT

19

Lynx

A1

VCC

C1490

2.2UF

6.3V

X5R-CERM

0201

ROOM=SOC

PP1V8_IO

1

20%

2

17

A

8

67

I2C4_AP_SDA

52

I2C4_AP_SCL

52

At EVT, check if we can remove

U1401

STLNXA1L9YZ2

WLCSP

B1

SDA NC

A2 C1

SCL

CRITICAL

VSS

B3

B2

C2

C3

A3

NC

NC

NC

SYNC_MASTER=test_mlb

PAGE TITLE

SYNC_DATE=04/05/2017

A

SOC: SERIAL

DRAWING NUMBER

051-02545

Apple Inc.

REVISION

7.0.0

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

35 4

2

.

BRANCH

PAGE

14 OF 85

SHEET

11 OF 60

1

SIZE

D

Page 17

SOC - GPIO INTERFACES

VIETMOBILE.VN

678

3 245

1

D

C

GPIOs are wired on page 70

AP_TO_BT_DEVICE_WAKE

55

BOARD_REV0

55

BOARD_REV1

55

BOARD_REV2

55

AP_TO_PMU_AMUX_SYNC

55

BOARD_REV3

55

AP_CANARY1

55

PMU_TO_AP_BUTTON_VOL_UP_L

55

NC_AP_GPIO8

55

AP_TO_BBPMU_RADIO_ON_L

55

AP_TO_SPKRAMP_TOP_RESET_L

55

AP_TO_NFC_FW_DWLD_REQ

55

AP_TO_BB_PEAK_POWER_INDICATOR

55

AP_TO_NFC_DEV_WAKE

55

CAMPMU_TO_AP_IRQ_L

55

AP_TO_GNSS_TIME_MARK

55

SPKRAMP_TOP_TO_AP_INT_L

55

BB_TO_AP_COEX

55

BT_TO_AP_TIME_SYNC

55

AP_TO_BB_RESET_L

55

BB_TO_AP_PEAK_POWER_INDICATOR

55

BB_TO_AP_RESET_DETECT_L

55

AP_TO_BB_COREDUMP_TRIG

55

AP_TO_CAMPMU_RESET_L

55

AP_TO_BB_COEX

55

DISPLAY_TO_AP_PANEL_ID

55

AP_CANARY2

55

NC_AP_GPIO27

55

NC_AP_GPIO28

55

AP_TO_RACER_RESET_L

55

GNSS_TO_AP_LOW_PWR_IND

55

K3

T4

T3

T2

U4

U2

Y2

AA3

AA4

K2

H35

H34

L4

K36

K35

G36

K34

J37

AB3

D16

D13

C14

D14

J35

H37

AB4

AC2

AB5

AC4

K4

AA5

GPIO[0]

GPIO[1]

GPIO[2]

GPIO[3]

GPIO[4]

GPIO[5]

GPIO[6]

GPIO[7]

GPIO[8]

GPIO[9]

GPIO[10]

GPIO[11]

GPIO[12]

GPIO[13]

GPIO[14]

GPIO[15]

GPIO[16]

GPIO[17]

GPIO[18]

GPIO[19]

GPIO[20]

GPIO[21]

GPIO[22]

GPIO[23]

GPIO[24]

GPIO[25]

GPIO[26]

GPIO[27]

GPIO[28]

GPIO[29]

GPIO[30]

U1000

CYP-4GB-M-TMJA47A0-C7

WLCSP

SYM 5 OF 16

TMR32_PWM0

TMR32_PWM1

TMR32_PWM2

UART0_RXD

UART0_TXD

UART1_CTS*

UART1_RTS*

UART1_RXD

UART1_TXD

UART2_CTS*

UART2_RTS*

UART2_RXD

UART2_TXD

UART3_CTS*

UART3_RTS*

UART3_RXD

UART3_TXD

UART4_CTS*

UART4_RTS*

UART4_RXD

UART4_TXD

UART6_RXD

UART6_TXD

UART7_RXD

UART7_TXD

R5

R4

R3

P36

P37

V2

V3

V4

V5

N35

N36

P34

P35

L37

M35

M37

N34

Y4

W3

W4

W5

D19

C18

L35

L36

PMU_TO_AP_PRE_UVLO_L

NC_TMR32_PWM1

AP_TO_WLAN_TIME_SYNC

UART_AP_DEBUG_RXD

UART_AP_DEBUG_TXD

UART_BT_TO_AP_CTS_L

UART_AP_TO_BT_RTS_L

UART_BT_TO_AP_RXD

UART_AP_TO_BT_TXD

NC_UART_WLAN_TO_AP_CTS_L

NC_UART_AP_TO_WLAN_RTS_L

NC_UART_WLAN_TO_AP_RXD

NC_UART_AP_TO_WLAN_TXD

UART_NFC_TO_AP_CTS_L

UART_AP_TO_NFC_RTS_L

UART_NFC_TO_AP_RXD

UART_AP_TO_NFC_TXD

UART_GNSS_TO_AP_CTS_L

UART_AP_TO_GNSS_RTS_L

UART_GNSS_TO_AP_RXD

UART_AP_TO_GNSS_TXD

NC_UART6_RXD_L

NC_UART6_TXD_L

UART_ACCESSORY_TO_AP_RXD

UART_AP_TO_ACCESSORY_TXD

IN

OUT

IN

OUT

IN

OUT

IN

OUT

IN

OUT

IN

OUT

IN

OUT

IN

OUT

IN

OUT

IN

OUT

IN

OUT

57

49

58

58

58

58

17

17

17

17

57

57

57

57

57

57

57

57

49

49

D

23 7 5

49 5

C

B

1

R1501

39.2K

1%

1/32W

MF

01005

2

ROOM=SOC

57 49

23

23

6 5

57 6

HYDRA_TO_AP_FORCE_DFU

IN

5

5

5

DFU_STATUS

OUT

PMU_TO_AP_BUTTON_POWER_KEY_L

IN

PMU_TO_AP_BUTTON_VOL_DOWN_L

IN

PAD_MTR_ANALOG_TEST_P

OUT

PAD_MTR_ANALOG_TEST_N

OUT

MTR_RREF_P

MTR_RREF_N

NC_PAD_MTR_VREF_P

NC_PAD_MTR_VREF_N

BOARD_ID0

IN

6

6

PP1V8_IO

IN

BOARD_ID2

IN

BOARD_ID4

IN

C17

C16

M3

M2

AM37

AM36

AK37

AK36

AL35

AL34

C13

H36

R2

T5

FORCE_DFU

DFU_STATUS

REQUEST_DFU1

REQUEST_DFU2

PAD_MTR_ANALOG_TEST_P

PAD_MTR_ANALOG_TEST_N

PAD_MTR_RREF_P

PAD_MTR_RREF_N

PAD_MTR_VREF_P

PAD_MTR_VREF_N

ALT FUNC

BOARD_ID0

BOARD_ID1

BOARD_ID2

BOARD_ID4

SOC_DEBUG1

B

A

8

67

SYNC_MASTER=test_mlb

PAGE TITLE

SYNC_DATE=04/05/2017

A

SOC: GPIO & UART

DRAWING NUMBER

051-02545

Apple Inc.

REVISION

7.0.0

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

35 4

2

BRANCH

PAGE

15 OF 85

SHEET

12 OF 60

1

SIZE

D

Page 18

SOC - AOP

VIETMOBILE.VN

678

3 245

1

D

1.62V - 1.98V @ 10mA MAX

PP1V8_S2

15 17

1

C1690

2.2UF

20%

6.3V

2

X5R-CERM

0201

ROOM=SOC

1

C1691

0.1UF

20%

6.3V

2

X5R-CERM

01005

ROOM=SOC

AM19

AM17

AM25

AM23

D

C

ALT FUNC's

|

|

|

V

AOP_LPPLL

AOP_PDM_CLK4

AOP_PDM_CLK3

VDDIO18_AOP

U1000

CYP-4GB-M-TMJA47A0-C7

WLCSP

SYM 7 OF 16

5

AOP_TO_DDR_SLEEP1_READY_PROBE

OUT

IMU_TO_AOP_DATARDY

56

SPI_AOP_TO_IMU_CS_L

56

AOP_TO_SPKAMP_BOT_RESET_L

56

SPI_AOP_TO_PHOSPHORUS_CS_L

56

PHOSPHORUS_TO_AOP_INT

56

ROMEO_TO_AOP_B2B_DETECT

56

RACER_TO_AOP_INT_L

56

AOP_TO_CODEC_RESET_L

56

NC_AOP_FUNC8

56

IMU_TO_AOP_INT

56

NC_AOP_FUNC10

56

NC_AOP_FUNC11

56

NC_AOP_FUNC12

56

AOP_TO_CODEC_CLP_EN

56

AOP_TO_BBPMU_COEX

56

PROX_BI_AOP_INT_L

56

POTASSIUM_TO_AOP_INT

56

HALL_CASE_TO_AOP_SOUTH_L

56

ALS_TO_AOP_INT_L

56

NFC_TO_AOP_HOST_WAKE

56

COMPASS_TO_AOP_INT

56

HALL_FLAP_TO_AOP_IRQ_L

56

SPKAMP_BOT_ARC_TO_AOP_INT_L

56

AU21

AP8

AP10

AT6

AR8

AT17

AP11

AP18

AR9

AP12

AR11

AU17

AR15

AR12

AT7

AR18

AT9

AP19

AT18

AT8

AU18

AT11

AU4

AT12

AON_SLEEP1_RESET*

AOP_FUNC[0]

AOP_FUNC[1]

AOP_FUNC[2]

AOP_FUNC[3]

AOP_FUNC[4]

AOP_FUNC[5]

AOP_FUNC[6]

AOP_FUNC[7]

AOP_FUNC[8]

AOP_FUNC[9]

AOP_FUNC[10]

AOP_FUNC[11]

AOP_FUNC[12]

AOP_FUNC[13]

AOP_FUNC[14]

AOP_FUNC[15]

AOP_FUNC[16]

AOP_FUNC[17]

AOP_FUNC[18]

AOP_FUNC[19]

AOP_FUNC[20]

AOP_FUNC[21]

AOP_FUNC[22]

<--

SCM_SPI CS & Trig

<

SCM_I2CM0 TRIGGER

SCM_I2CM1 TRIGGER

<

AOP_PDM_CLK0

AOP_PDM_DATA0

AOP_PDM_DATA1

RT_CLK32768

SWD_TMS2

SWD_TMS3

AOP_I2CM0_SCL

AOP_I2CM0_SDA

AOP_I2CM1_SCL

AOP_I2CM1_SDA

AOP_PDM_OUT0_CLK

AOP_PDM_DATAOUT

AT21

AT22

AU23

AP26

C19

B16

AP17

AP5

AR17

AT5

AT23

AU22

NC_SWD_TMS3

HALL_CASE_TO_AOP_NORTH_L

AOP_TO_CODEC_GPIO1

CODEC_TO_AOP_GPIO2

AOP_TO_GECKO_RESET_L

PMU_TO_AOP_CLK32K

SWD_AP_BI_NAND_SWDIO

I2C0_AOP_SCL

I2C0_AOP_SDA

I2C1_AOP_SCL_SOC

I2C1_AOP_SDA

GECKO_TO_AOP_IRQ_L

OUT

IN

OUT

IN

BI

OUT

BI

OUT

BI

56

56

40

40

56

54

54

54

54

C

23 5

19 5

ALT FUNC's

SMC_UART1_TXD

SMC_UART1_RXD

I2C bus descriptions on 66-68

B

A

50 43 42 41 40 5

50 43 42 41 40

28 5

ALT FUNC

AOP_PDM_CLK2

I2S_CODEC_ASP1_TO_AOP_AMPS_BCLK

IN

I2S_CODEC_ASP1_TO_AOP_AMPS_LRCLK

IN

40

SPI_AOP_TO_IMU_SCLK

OUT

I2S_AOP_TO_CODEC_MCLK2

OUT

R1604

49.9

1%

1/32W

MF

01005

ROOM=SOC

R1605

49.9

1/32W

01005

ROOM=SOC

21

1%

MF

R1601

R1602

21

33.2

1%

1/32W

MF

01005

ROOM=SOC

33.2

1%

1/32W

MF

01005

ROOM=SOC

28 5

28 5

21

57

57

58

58

58

58

40

40

21

40

40

SPI_IMU_TO_AOP_MISO

IN

SPI_AOP_TO_IMU_MOSI

OUT

SPI_AOP_TO_IMU_SCLK_R

UART_BB_TO_AOP_RXD

IN

UART_AOP_TO_BB_TXD

OUT

AOP_TO_WLAN_CONTEXT_A

OUT

AOP_TO_WLAN_CONTEXT_B

OUT

UART_RACER_TO_AOP_RXD

IN

UART_AOP_TO_RACER_TXD

OUT

I2S_AOP_TO_CODEC_ASP2_BCLK

OUT

I2S_CODEC_ASP2_TO_AOP_DIN

IN

I2S_AOP_TO_CODEC_MCLK2_R

I2S_AOP_TO_CODEC_ASP2_LRCLK

OUT

I2S_AOP_TO_CODEC_ASP2_DOUT

OUT

I2S_CODEC_ASP1_TO_AOP_AMPS_BCLK_R

43 42 41 40

I2S_CODEC_ASP1_TO_AOP_AMPS_DIN

IN

AOP_TO_HALOGEN_AFE_EN

56

I2S_CODEC_ASP1_TO_AOP_AMPS_LRCLK_R

50 43 40

I2S_AOP_AMPS_TO_CODEC_ASP1_DOUT

OUT

AP6

AP7

AP16

AR5

AR6

AU16

AT16

AP4

AT4

AU11

AU19

AR20

AU7

AU8

AU5

AT19

AU12

AU6

AP20

AOP_SPI_MISO

AOP_SPI_MOSI

AOP_SPI_SCLK

AOP_UART0_RXD

AOP_UART0_TXD

AOP_UART1_RXD

AOP_UART1_TXD

AOP_UART2_RXD

AOP_UART2_TXD

AOP_I2S0_BCLK

AOP_I2S0_DIN

AOP_I2S0_MCK

AOP_I2S0_LRCK

AOP_I2S0_DOUT

AOP_I2S1_BCLK

AOP_I2S1_DIN

AOP_I2S1_MCK

AOP_I2S1_LRCK

AOP_I2S1_DOUT

AOP_PDM_CLK2

ALT FUNC's

AOP_PDM_IN1_CLK

AOP_PDM_IN2_CLK

AOP_PDM_IN2_DAT

B

NUB_DOCK_CONNECT

NUB_DOCK_ATTENTION

NUB_SWD_TCK_OUT

NUB_SPMI_SCLK

NUB_SPMI_SDATA

NUB_SWD_TMS0

NUB_SWD_TMS1

|

V

AR27

AP25

AP24

AR21

AR29

AR26

AP22

HYDRA_TO_NUB_DOCK_CONNECT

HYDRA_TO_NUB_INT

SWD_AOP_TO_MANY_SWCLK

SPMI_PMGR_TO_PMU_SCLK_R

SPMI_PMU_BI_PMGR_SDATA

SWD_AOP_BI_RACER_SWDIO

SWD_AOP_BI_BB_SWDIO

IN

IN

OUT

BI

BI

BI

ALT FUNC's

49

49

NUB_PDM_CLK1

58 19 5

23 5

58

57

|

V

R1603

0.00

0%

1/32W

MF

01005

ROOM=SOC

21

SPMI_PMGR_TO_PMU_SCLK

OUT

23

A

PAGE TITLE

8

67

SOC: AOP

DRAWING NUMBER

051-02545

Apple Inc.

REVISION

7.0.0

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

35 4

2

BRANCH

PAGE

16 OF 85

SHEET

13 OF 60

1

SIZE

D

Page 19

678

VIETMOBILE.VN

3 245

1

D

C

B

A

SOC - CPU, GPU & SOC RAILS

1.06V @ 13.8A MAX

0.905V @ 12.9A MAX

0.527V @ 2.4A MAX

PP_CPU_PCORE

17

Remote sense XW's for Buck0 Buck1 and Buck11 live off page

U1000

CYP-4GB-M-TMJA47A0-C7

WLCSP

AD9

AD17

AE10

AE12

AE16

AF13

AF15

AG10

AJ10

AK13

AK15

V11

V13

W10

W14

W16

Y9

Y17

AL16

AL18

AL22

AL24

AM21

AL20

AB9

AB17

AE14

AF11

AH15

AK11

N12

U10

W12

F13

H11

H15

H19

J24

K13

K21

G22

M15

M19

M23

VDD_PCPU

VDD_LOW

VDD_LOW_ULPPLL

VDD_LOW_FLPPLL

VDD_CPU_SRAM

VDD_GPU_SRAM

SYM 8 OF 16

VDD_FIXED_PLL_SOC

VDD_FIXED_PLL_GPU

VDD_FIXED_PLL_ANE

VDD_FIXED_PLL_DDR0

VDD_FIXED_PLL_DDR1

VDD_FIXED_PLL_DDR2

VDD_FIXED_PLL_DDR3

ROOM=SOC

C1705

14UF

20%

4V

X5R

0402-D2X-1

1

432

ROOM=SOC

C1711

14UF

20%

4V

X5R

0402-D2X-1

1

432

ROOM=SOC

C1708

14UF

20%

4V

X5R

0402-D2X-1

1

3

4

2

ROOM=SOC

C1709

14UF

20%

4V

X5R

0402-D2X-1

1

3

4

2

ROOM=SOC

C1704

14UF

20%

4V

X5R

0402-D2X-1

1

432

ROOM=SOC

C1710

14UF

20%

4V

X5R

0402-D2X-1

1

432

VDD_LOW: 0.691V - 0.756V @ 75mA MAX

VDD_LOW_ULPPLL: 0.691V - 0.756V @ 0.3mA MAX

PP0V7_VDD_LOW_S2

17

R1702

C1751

4UF

20%

4V

X5R

0201

ROOM=SOC

1

2

C1750

4UF

20%

4V

X5R

0201

ROOM=SOC

1

2

100

5%

1/32W

MF

01005

ROOM=SOC

21

R1701

10

21

5%

1/32W

MF

01005

ROOM=SOC

1.02V @ 2.1A MAX

0.975V @ 1.4A MAX

0.765V @ 0.33A MAX

PP_CPU_SRAM

17

ROOM=SOC

C1773

14UF

20%

4V

X5R

0402-D2X-1

1

432

1.06V @ 0.6A MAX

0.725V @ 0.41A MAX

0.685V @ 0.39A MAX

PP_GPU_SRAM

17

ROOM=SOC

C1772

14UF

20%

4V

X5R

0402-D2X-1

1

4

2

3

1

C1702

4UF

20%

4V

2

X5R

0201

ROOM=SOC

1

ROOM=SOC

C1706

14UF

20%

4V

X5R

0402-D2X-1

1

432

ROOM=SOC

C1712

14UF

20%

4V

X5R

0402-D2X-1

1

432

PP0V7_VDD_LOW_ULPPLL_R

1

C1742

4UF

20%

4V

2

X5R

0201

ROOM=SOC

PP0V7_VDD_LOW_FLPPLL_R

1

C1743

0.47UF

20%

6.3V

2

X5R

01005

ROOM=SOC

ROOM=SOC

C1781

14UF

20%

4V

X5R

0402-D2X-1

1

432

C1703

4UF

20%

4V

2

X5R

0201

ROOM=SOC

ROOM=SOC

C1707

14UF

20%

4V

X5R

0402-D2X-1

1

ROOM=SOC

C1713

14UF

20%

4V

X5R

0402-D2X-1

1

ROOM=SOC

C1782

14UF

20%

4V

X5R

0402-D2X-1

1

432

432

432

for dev board compapability

VDD_GPU

VDD_ECPU

VDD_FIXED_ECPU

VDD_FIXED_MTR

VDD_FIXED_PCPU

VDD12_PLL_SOC

VDD12_PLL_ANE

VDD12_PLL_PCPU

VDD12_PLL_ECPU

VDD12_PLL_GPU

F11

F15

G10

G12

G14

G16

G20

K25

G24

G26

H13

H17

H21

H25

J12

J14

J20

J22

H23

J26

K11

K15

K23

L10

L12

L14

L20

L22

L24

L26

M13

M17

M21

M25

N20

N22

N24

N26

N10

P9

P13

T9

T13

V9

U11

M11

AD31

U12

AE24

AE22

AD23

AH5

AJ29

D7

N29

AE23

AD24

U13

M12

AD22

1

C1730

2.2UF

20%

6.3V

2

X5R-CERM

0201

ROOM=SOC

ROOM=SOC

C1732

14UF

20%

4V

X5R

0402-D2X-1

1

432

ROOM=SOC

C1737

14UF

20%

4V

X5R

0402-D2X-1

1

432

1

C1731

2.2UF

20%

6.3V

2

X5R-CERM

0201

ROOM=SOC

ROOM=SOC

C1733

14UF

20%

4V

X5R

0402-D2X-1

1

432

ROOM=SOC

C1738

14UF

20%

4V

X5R

0402-D2X-1

1

432

C1734

0402-D2X-1

1

ROOM=SOC

C1739

0402-D2X-1

1

ROOM=SOC

C1791

14UF

20%

4V

X5R

0402-D2X-1

1

432

14UF

20%

4V

X5R

432

14UF

20%

4V

X5R

432

ROOM=SOC

C1792

14UF

0402-D2X-1

1

0402-D2X-1

20%

4V

X5R

432

1.06V @ 14.5A MAX

0.725V @ 6.3A MAX

0.570V @ 3.1A MAX

ROOM=SOCROOM=SOC

C1735

14UF

4V

X5R

1

432

ROOM=SOC

C1736

14UF

20%20%

4V

X5R

0402-D2X-1

1

432

0.945V @ 2.9A MAX

0.626V @ 1.2A MAX

0.517V @ 0.62A MAX

PP_CPU_ECORE

ROOM=SOC

C1793

14UF

20%

4V

X5R

0402-D2X-1

1

3

4

2

1

C1794

2.2UF

20%

6.3V