ANALOG DEVICES SSM2166 Service Manual

Microphone Preamplifier with

V

www.BDTIC.com/ADI

Variable Compression and Noise Gating

FEATURES

Complete microphone conditioner in a 14-lead SOIC package

Single 5 V operation

Adjustable noise gate threshold

Compression ratio set by external resistor

Automatic limiting feature—prevents ADC overload

Adjustable release time

Low noise and distortion

Power-down feature

20 kHz bandwidth (±1 dB)

APPLICATIONS

Microphone preamplifiers/processors

Computer sound cards

Public address/paging systems

Communication headsets

Telephone conferencing

Guitar sustain effects generators

Computerized voice recognition

Surveillance systems

Karaoke and DJ mixers

GENERAL DESCRIPTION

The SSM2166 integrates a complete and flexible solution for

conditioning microphone inputs in computer audio systems. It

is also excellent for improving vocal clarity in communications

and public address systems. A low noise, voltage-controlled

amplifier (VCA) provides a gain that is dynamically adjusted by

a control loop to maintain a set compression characteristic. The

compression ratio is set by a single resistor and can be varied

from 1:1 to over 15:1 relative to a user-defined rotation point;

signals above the rotation point are limited to prevent overload

and to eliminate popping. In the 1:1 compression setting, the

SSM2166

SSM2166 can be programmed with a fixed gain of up to 20 dB;

this gain is in addition to the variable gain in other compression

settings. The input buffer can also be configured for front-end

gains of 0 dB to 20 dB. A downward expander (noise gate) prevents

amplification of noise or hum. This results in optimized signal

levels prior to digitization, thereby eliminating the need for

additional gain or attenuation in the digital domain that may

add noise or impair accuracy of speech recognition algorithms.

The compression ratio and time constants are set externally. A

high degree of flexibility is provided by the VCA gain, rotation

point, and noise gate adjustment pins.

The SSM2166 is an ideal companion product for audio codecs

used in computer systems, such as the AD1845. The SSM2166 is

available in a 14-lead SOIC package and is guaranteed for

operation over the extended industrial temperature range of

−40°C to +85°C.

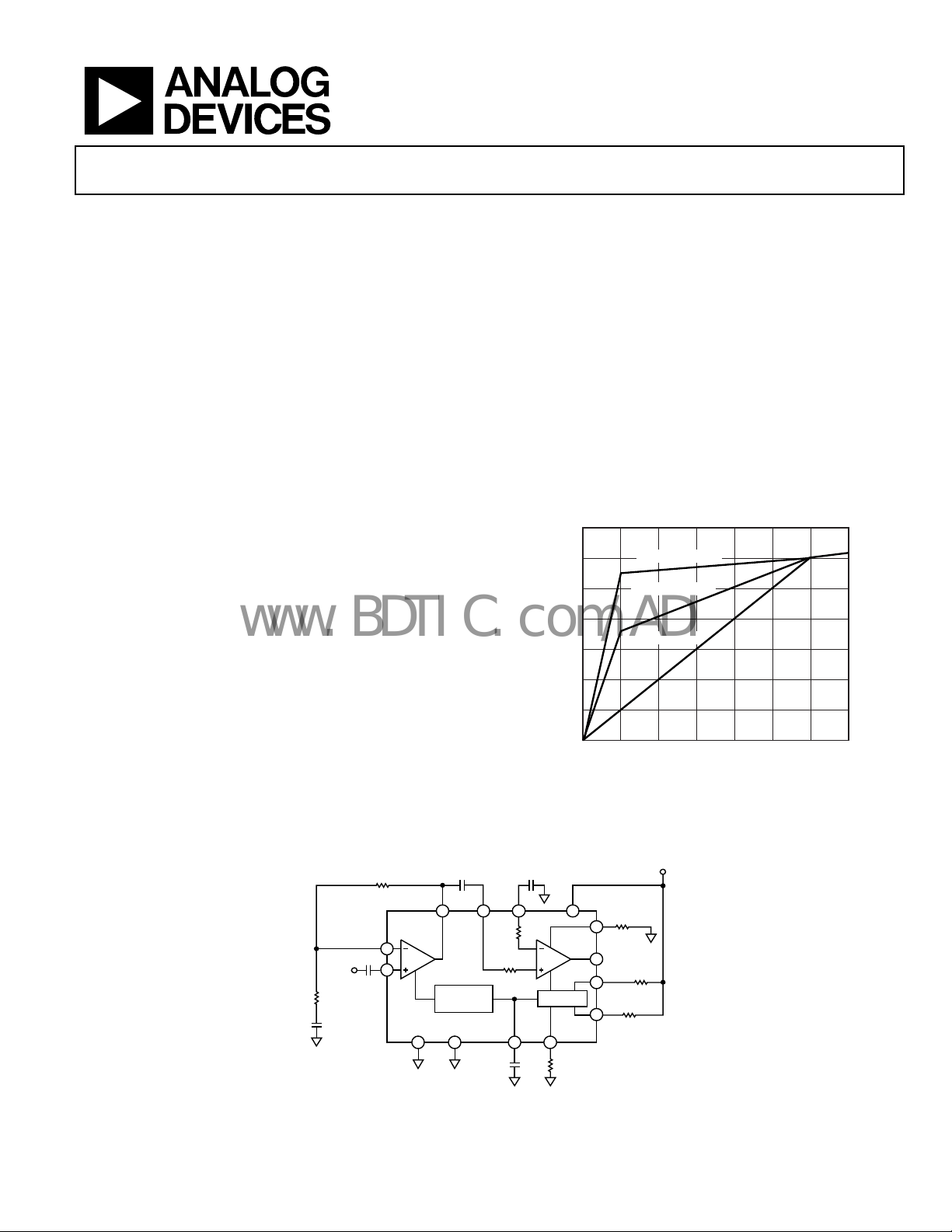

10

0

–10

–20

–30

OUTPUT (dBu)

–40

–50

–60

–70 –60 –50 –40 –30 –20 –10 0

Figure 1. Compression and Gating Characteristics with 10 dB of Fixed Gain (The

Gain Adjust Pin Can Be Used to Vary This Fixed Gain Amount)

COMP RATIO = 10: 1

COMP RATIO = 2: 1

COMP RATIO = 1: 1

INPUT (dBu)

00357-002

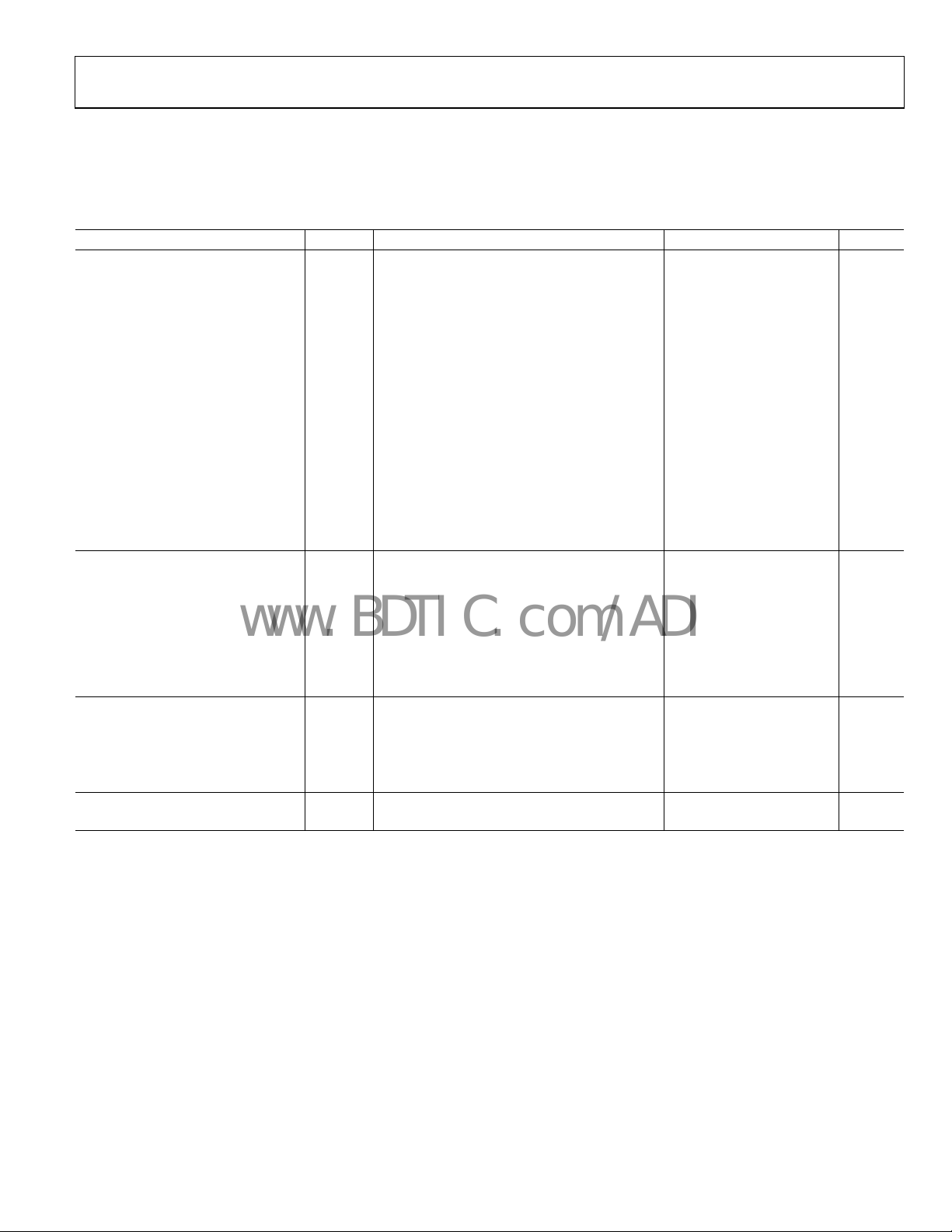

FUNCTIONAL BLOCK DIAGRAM AND TYPICAL SPEECH APPLICATION

R1

10kΩ

BUF OUT

BUFFER

–IN

6

0.1µF

AUDIO

+IN

R2

10kΩ

+

1µF

Rev. D

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

7

SSM2166

POWER DOWN GND AVG CAP COMP RATIO SE T

10µF 10µF (OPTI ONAL)

VCA

LEVEL

DETECT OR

++

VCA

IN

R

1kΩ

8112

V+

435 14

1kΩ

VCA

CONTROL

10

+

25kΩ22µF

Figure 2.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©1996–2008 Analog Devices, Inc. All rights reserved.

GAIN

ADJUST

2

2.3kΩ

OUTPUT

13

NOISE GATE

SET

9

17kΩ

11

ROTATION

SET

500kΩ

+

00357-001

SSM2166

www.BDTIC.com/ADI

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications ....................................................................................... 1

General Description ......................................................................... 1

Functional Block Diagram and Typical Speech Application ...... 1

Revision History ............................................................................... 2

Specifications ..................................................................................... 3

Absolute Maximum Ratings ............................................................ 4

Thermal Resistance ...................................................................... 4

ESD Caution .................................................................................. 4

Pin Configuration and Function Descriptions ............................. 5

Typical Performance Characteristics ............................................. 6

Theory of Operation ........................................................................ 8

Applications Information ............................................................ 8

REVISION HISTORY

7/08—Rev. C to Rev. D

Changes to Figure 4 through Figure 9 ........................................... 6

Changes to Figure 11 and Figure 12 ............................................... 7

Changes to Figure 19 ...................................................................... 10

Changes to Figure 26 ...................................................................... 13

Added Top Branding Revision Reflecting Die Replacement

Table ................................................................................................. 17

5/08—Rev. B to Rev. C

Updated Format .................................................................. Universal

Changes to Features Section and General Description

Section ................................................................................................ 1

Changes to Table 1 ............................................................................ 3

Changes to Table 2 ............................................................................ 4

Deleted TPC 3; Renumbered Sequentially .................................... 4

Changes to Table 4, Pin 8 Description Column ........................... 5

Changes to Figure 5, Figure 6, Figure 8, and Figure 9 ................. 6

Change to Figure 11 ......................................................................... 7

Changes to Signal Path Section ...................................................... 9

Signal Path ......................................................................................8

Level Detector ................................................................................9

Control Circuitry ........................................................................ 10

Power-Down Feature ................................................................. 12

PCB Layout Considerations ...................................................... 12

Evaluation Board ............................................................................ 13

Evaluation Board Examples ...................................................... 14

Evaluation Board Setup Procedure .......................................... 15

Test Equipment Setup ................................................................ 15

Setup Summary .......................................................................... 16

Outline Dimensions ....................................................................... 17

Ordering Guide .......................................................................... 17

Added Figure 19 ............................................................................. 10

Deleted Figure 14 and Figure 17 .................................................. 12

Deleted Other Versions Section ................................................... 13

Changes to Figure 26 ...................................................................... 13

Changes to Figure 27 ...................................................................... 14

Changes to Test Equipment Section ............................................ 15

Added Table 6 ................................................................................. 16

Added Table 7 ................................................................................. 16

Updated Outline Dimensions ....................................................... 17

Changes to Ordering Guide .......................................................... 17

3/03—Rev. A to Rev. B

Deleted PDIP Package ....................................................... Universal

Change to General Description ....................................................... 1

Changes to Thermal Characteristics ............................................... 2

Changes to Ordering Guide ............................................................. 2

Deleted 14-Lead PDIP, Outline Dimensions .............................. 15

Updated 14-Lead Narrow-Body SOIC, Outline Dimensions ... 15

Rev. D | Page 2 of 20

SSM2166

www.BDTIC.com/ADI

SPECIFICATIONS

V+ = 5 V, f = 1 kHz, RL = 100 kΩ, R

V

= 300 mV rms.

IN

Table 1.

Parameter Symbol Conditions Min Typ Max Unit

AUDIO SIGNAL PATH

Voltage Noise Density en 15:1 Compression 17 nV/√Hz

Noise 20 kHz bandwidth, VIN = GND −109 dBu1

Total Harmonic Distortion and

Noise

Input Impedance ZIN 180 kΩ

Output Impedance Z

Load Drive Resistive 5 kΩ

Capacitive 2 nF

Buffer

Input Voltage Range 1% THD 1 V rms

Output Voltage Range 1% THD 1 V rms

VCA

Input Voltage Range 1% THD 1 V rms

Output Voltage Range 1% THD 1.4 V rms

Gain Bandwidth Product 1:1 compression, VCA gain = 60 dB 30 MHz

CONTROL SECTION

VCA Dynamic Gain Range 60 dB

VCA Fixed Gain Range −60 to +19 dB

Compression Ratio, Minimum 1:1

Compression Ratio, Maximum

Control Feedthrough

POWER SUPPLY

Supply Voltage Range V+ 4.5 5.5 V

Supply Current ISY 7.5 10 mA

Quiescent Output Voltage Level 2.2 V

Power Supply Rejection Ratio PSRR 50 dB

POWER DOWN

Supply Current Pin 12 = V+2 10 100 μA

1

0 dBu = 0.775 V rms.

2

Normal operation for Pin 12 is 0 V.

= 600 kΩ, R

GATE

THD + N

75 Ω

OUT

= 3 kΩ, R

ROT PT

Second and third harmonics, VIN = −20 dBu,

22 kHz low-pass filter

See Figure 19 for R

point = 100 mV rms

15:1 compression, rotation point = −10 dBu,

R2 = 1.5 kΩ

= 0 Ω, R1 = 0 Ω, R2 = ∞ Ω, TA = 25°C, unless otherwise noted;

COMP

COMP/RROT PT

, rotation

0.25 0.5 %

15:1

±5 mV

Rev. D | Page 3 of 20

SSM2166

www.BDTIC.com/ADI

ABSOLUTE MAXIMUM RATINGS

Table 2.

Parameter Rating

Supply Voltage 10 V

Audio Input Voltage Supply voltage

Operating Temperature Range −40°C to +85°C

Storage Temperature Range −65°C to +150°C

Junction Temperature (TJ) 150°C

Lead Temperature (Soldering, 60 sec) 300°C

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

THERMAL RESISTANCE

Table 3.

Package Type θJA θ

14-Lead SOIC 120 36 °C/W

Unit

JC

ESD CAUTION

Rev. D | Page 4 of 20

SSM2166

G

www.BDTIC.com/ADI

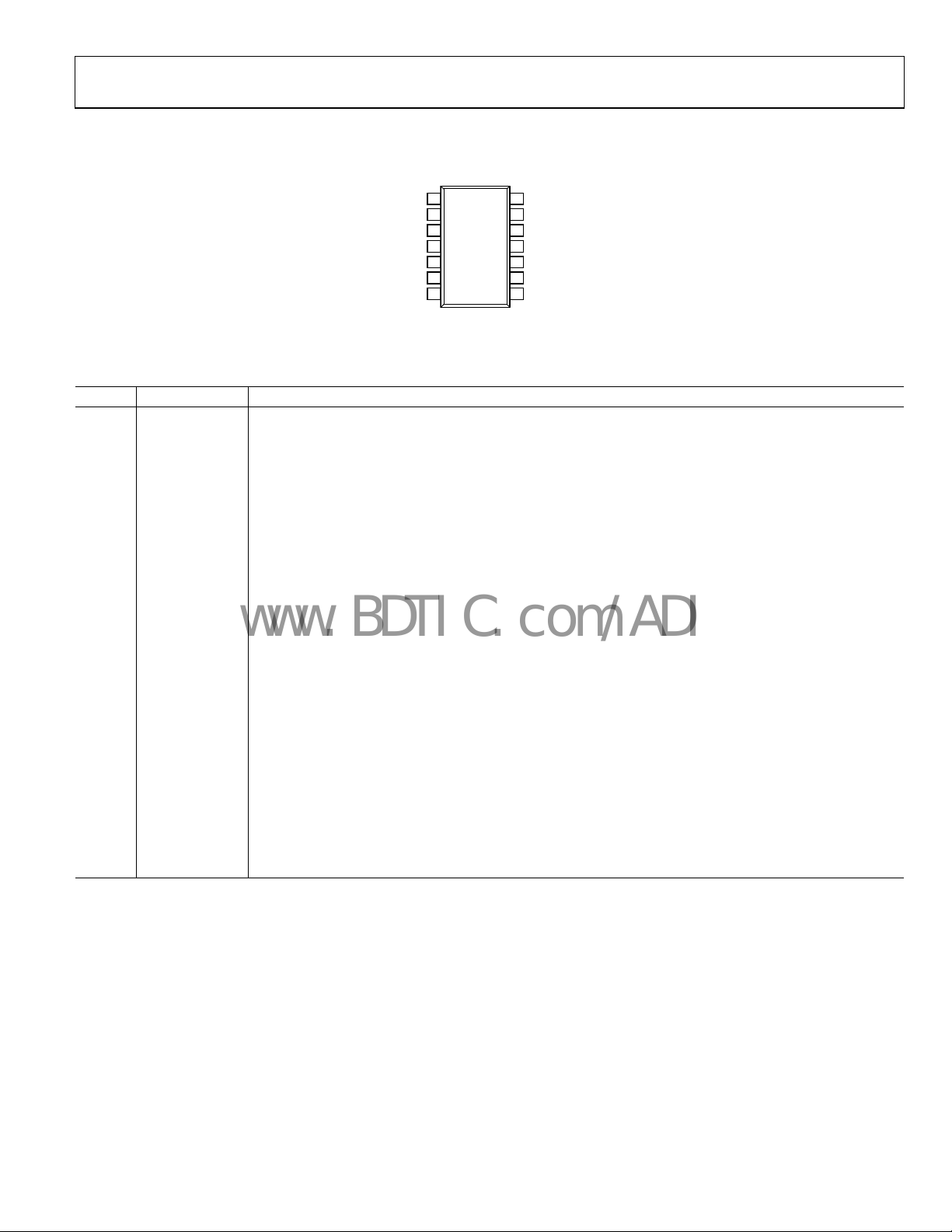

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

GND 1

AIN ADJUST 2

3

VCA

IN

SSM2166

VCA

BUF OUT 5 COMP RATIO SET10

AUDIO +IN

TOP VIEW

4

R

(Not to Scale)

–IN 6 NOISE GATE SET9

7

Figure 3. Pin Configuration

V+14

OUTPUT13

12

POWER DOWN

ROTATION SET11

8

AVG CAP

00357-003

Table 4. Pin Function Descriptions

Pin No. Mnemonic Description

1 GND Ground.

2 GAIN ADJUST

VCA Gain Adjust Pin. A resistor from this pin to ground sets the fixed gain of the VCA. To check the setting of

this pin, make sure the compression ratio set pin (Pin 10) is grounded for no compression. The gain can be

varied from 0 dB to 20 dB. For 20 dB, leave the pin open. For 0 dB of fixed gain, a typical resistor value is

approximately 1 kΩ. For 10 dB of fixed gain, the resistor value is approximately 2 kΩ to 3 kΩ. For resistor values

<1 kΩ, the VCA can attenuate or mute (see Figure 6).

3 VCAIN VCA Input Pin. A typical connection is a 10 μF capacitor from the buffer output pin (Pin 5) to this pin.

4 VCAR

Inverting Input to the VCA. This input can be used as a nonground reference for the audio input signal (see the

Applications Information section).

5 BUF OUT Input Buffer Amplifier Output Pin. This pin must not be loaded by capacitance to ground.

6 −IN

Inverting Input to the Buffer. A 10 kΩ feedback resistor, R1, from the buffer output (Pin 5) to this input pin and

a resistor, R2, from this pin through a 1 μF capacitor to ground give gains of 6 dB to 20 dB for R2 = 10 kΩ to 1.1 kΩ.

7 AUDIO +IN Input Audio Signal. The input signal should be ac-coupled (0.1 μF typical) into this pin.

8 AVG CAP

Detector Averaging Capacitor. A capacitor, 1 μF to 22 μF, to ground from this pin is the averaging capacitor

for the detector circuit.

9 NOISE GATE SET

Noise Gate Threshold Set Point. A resistor to V+ sets the level below which input signals are downward

expanded. For a 0.7 mV threshold, the resistor value is approximately 380 kΩ. Increasing the resistor value

reduces the threshold (see Figure 5).

10 COMP RATIO SET

Compression Ratio Set Pin. A resistor to ground from this pin sets the compression ratio, as shown in Figure 2.

Figure 19 gives resistor values for various rotation points.

11 ROTATION SET

Rotation Point Set Pin. This pin is set by adding a resistor to the positive supply. This resistor together with

the gain adjust pin determines the onset of limiting. A typical value for this resistor is 17 kΩ for a 100 mV

rotation point. Increasing the resistor value reduces the level at which limiting occurs (see Figure 9).

12 POWER DOWN

Power-Down Pin. Connect this pin to ground for normal operation. Connect this pin to the positive supply

for power-down mode.

13 OUTPUT Output Signal.

14 V+ Positive Supply, 5 V Nominal.

Rev. D | Page 5 of 20

SSM2166

www.BDTIC.com/ADI

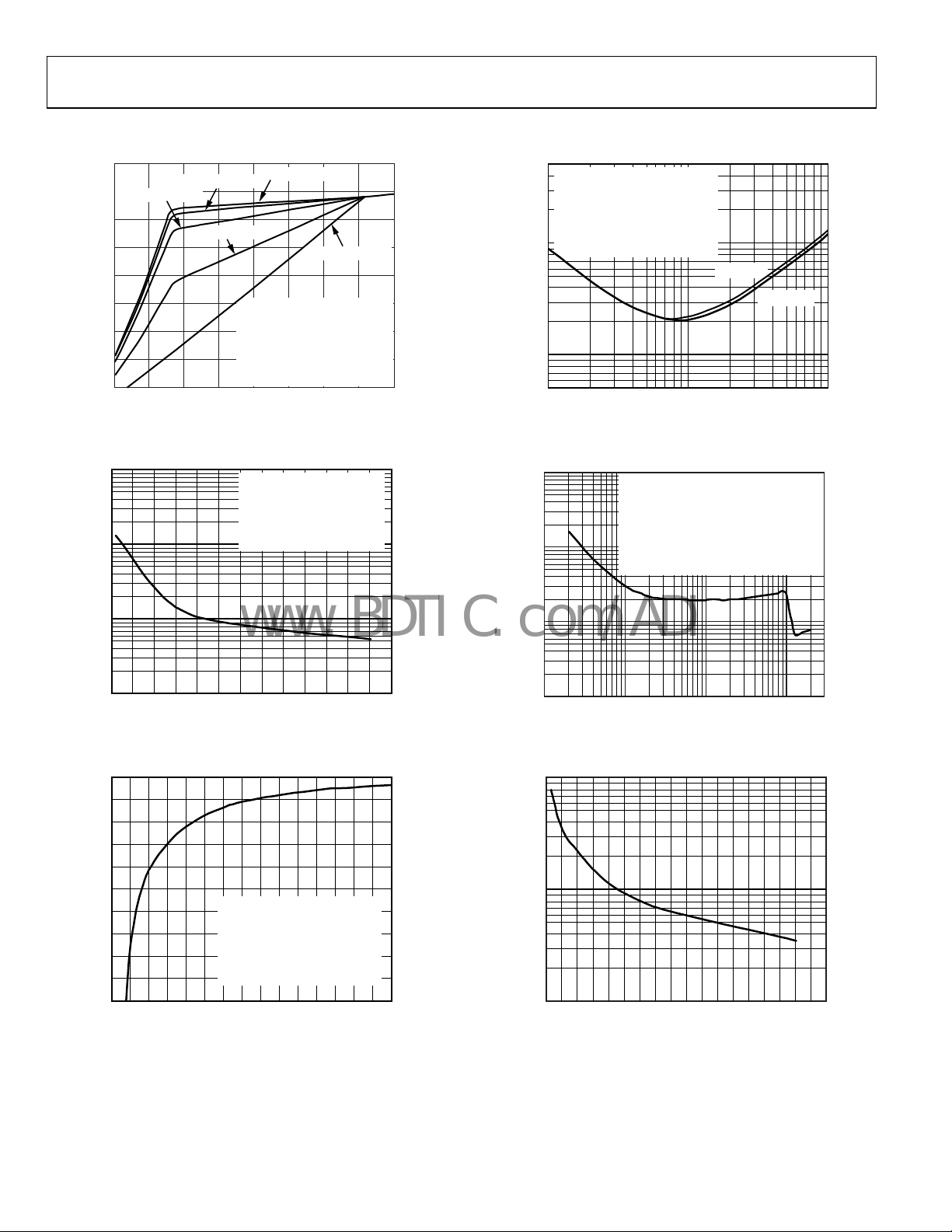

TYPICAL PERFORMANCE CHARACTERISTICS

0

COMP RATIO = 5:1

–10

–20

–30

–40

–50

OUTPUT (d Bu)

–60

–70

–80

100

10

COMP RATIO = 10:1

COMP RATIO = 2:1

–70–80 –60 –50 –40 –30 –20 –10 0

COMP RATIO = 15:1

COMP RATIO = 1:1

TA = 25°C

V+ = 5V

V

= 300mV rms @ 1kHz

IN

R

= 100kΩ

L

NOISE GATE SETTING ≈ 550µV rms

ROTATION SET ≈ 300mV rms

GAIN ADJUST = 1.25kΩ

INPUT (dBu)

Figure 4. Output vs. Input Characteristics

TA = 25°C

V+ = 5V

R

= 100kΩ

L

COMPRESSION RATIO = 2:1

ROTATION SET ≈ 700mV rms

GAIN ADJUST = 1.56kΩ

00357-004

5

TA = 25°C

V+ = 5V

COMPRESSION RATIO = 1:1

NOISE GATE SETTING ≈ 550µV rms

ROTATION SET ≈ 1V rms

GAIN ADJUST = 1.25kΩ

1

V

FREQUENCY = 1kHz

IN

RL = 10kΩ

THD + N (%)

0.1

0.05

0.01 0.1 1

INPUT VOLTAGE (V rms)

RL = 100kΩ

Figure 7. THD + N (%) vs. Input (V rms)

10

1

TA = 25°C

V+ = 5V

V

= 77.5mV rms @ 1kHz

IN

COMPRE SSIO N RATIO = 1:1

NOISE GATE SETTING ≈ 550µV rms

ROTATION SET ≈ 1V rms

GAIN ADJUST = 156kΩ

MEASUREMENT F ILTER BW: 20Hz TO 20kHz

00357-007

1

NOISE GATE (mV rms)

0.1

0 50 100 150 200 250 300 350 400 450 500 550 600 650

Figure 5. Noise Gate vs. R

R

GATE

(kΩ)

GATE

(Pin 9 to V+)

20

18

16

14

12

10

8

VCA GAIN (dB)

6

4

2

0

0 2 4 6 8 1012141618202224262830

Figure 6. VCA Gain vs. R

TA = 25°C

V+ = 5V

V

= 77.5mV rms @ 1kHz

IN

R

= 100kΩ

L

NOISE GATE SETTING ≈ 550µV rms

ROTATION SET ≈ 1V rms

COMPRESSION RATIO = 1:1

GAIN ADJUST RESISTOR (kΩ)

(Pin 2 to GND)

GAIN

THD + N (%)

0.1

0.01

00357-005

10 100 1k 10k 30k

FREQUENCY (Hz)

00357-008

Figure 8. THD + N (%) vs. Frequency (Hz)

1

0.1

ROTATION POINT (V rms)

0.01

0 5 10 15 20 25 30 35 40 45 50 55 60 65 70 75 80 85 90

00357-006

Figure 9. Rotation Point vs. R

R

ROT PT

RESISTOR (kΩ)

(Pin 11 to V+)

ROT PT

00357-009

Rev. D | Page 6 of 20

Loading...

Loading...