Dual Very Low Noise Precision

FEATURES

Very low noise density of 5 nV/√Hz at 1 kHz maximum

Excellent input offset voltage of 75 μV maximum

Low offset voltage drift of 1 μV/°C maximum

Very high gain of 1500 V/mV minimum

Outstanding CMR of 106 dB minimum

Slew rate of 2.4 V/μs typical

Gain bandwidth product of 5 MHz typical

Industry-standard 8-lead dual pinout

GENERAL DESCRIPTION

The OP270 is a high performance, monolithic, dual operational

amplifier with exceptionally low voltage noise density (5 nV/√Hz

maximum at 1 kHz). It offers comparable performance to the

industry-standard OP27 from Analog Devices, Inc.

The OP270 features an input offset voltage of less than 75 μV

and an offset drift of less than 1 μV/°C, guaranteed over the full

military temperature range. Open-loop gain of the OP270 is more

than 1,500,000 into a 10 kΩ load, ensuring excellent gain accuracy

and linearity, even in high gain applications. The input bias

current is less than 20 nA, which reduces errors due to signal

source resistance. With a common-mode rejection (CMR) of

greater than 106 dB and a power supply rejection ratio (PSRR)

of less than 3.2 μV/V, the OP270 significantly reduces errors

due to ground noise and power supply fluctuations. The power

consumption of the dual OP270 is one-third less than two OP27

Operational Amplifier

OP270

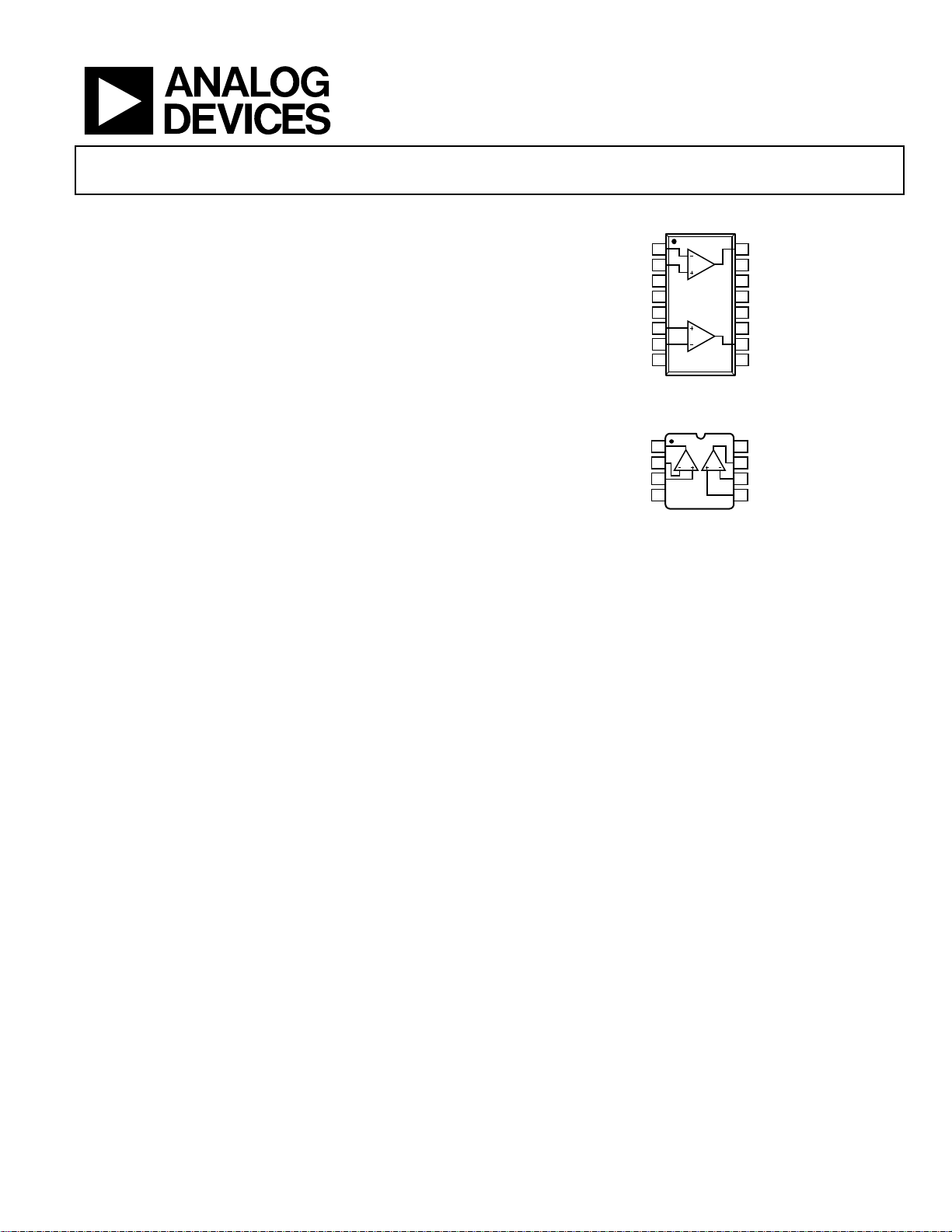

FUNCTIONAL BLOCK DIAGRAMS

1

–IN A

2

+IN A

NC

3

V–

4

OP270

5

NC

+IN B

6

–IN B

7

8

NC

NC = NO CONNECT

Figure 1. 16-Lead SOIC

(S-Suffix)

OUT A

1

AB

2

–IN A

3

+IN A

4

V–

OP270

Figure 2. 8-Lead PDIP (P-Suffix)

8-Lead CERDIP

(Z-Suffix)

devices, a significant advantage for power conscious applications.

The OP270 is unity-gain stable with a gain bandwidth product

of 5 MHz and a slew rate of 2.4 V/μs.

The OP270 offers excellent amplifier matching, which is

important for applications such as multiple gain blocks, low

noise instrumentation amplifiers, dual buffers, and low noise

active filters.

The OP270 conforms to the industry-standard 8-lead DIP

pinout. It is pin compatible with the MC1458, SE5532/A,

RM4558, and HA5102 dual op amps, and can be used to

upgrade systems using those devices.

For higher speed applications, the ADA4004-2 or the AD8676 are

recommended. For a quad op amp, see the OP470 data sheet.

16

15

14

13

12

11

10

9

8

7

6

5

OUT A

NC

NC

V+

NC

NC

OUT B

NC

V+

OUT B

–IN B

+IN B

00325-001

00325-002

Rev. E

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2001–2010 Analog Devices, Inc. All rights reserved.

OP270

TABLE OF CONTENTS

Features .............................................................................................. 1

Functional Block Diagrams ............................................................. 1

General Description ......................................................................... 1

Revision History ............................................................................... 2

Specifications ..................................................................................... 3

Electrical Specifications ............................................................... 4

Absolute Maximum Ratings ............................................................ 5

ESD Caution .................................................................................. 5

Typical Performance Characteristics ............................................. 6

Test Circuits ..................................................................................... 11

Applications Information .............................................................. 12

REVISION HISTORY

2/10—Rev. D to Rev. E

Change to General Description Section ........................................ 1

Change to Input Noise Current Density Parameter, Table 1 ...... 3

Change to Figure 18 ......................................................................... 8

Changes to Total Noise and Source Resistance Section ............ 13

Changes to Figure 41 ...................................................................... 16

2/09—Rev. C to Rev. D

Updated Format .................................................................. Universal

Reorganized Layout ............................................................ Universal

Changes to Figure 7 .......................................................................... 6

Changes to Figure 22 ........................................................................ 9

Deleted Applications Heading ...................................................... 11

Changes to Figure 44 ...................................................................... 17

Changes to Figure 46 ...................................................................... 18

Updated Outline Dimensions ....................................................... 19

Changes to Ordering Guide .......................................................... 20

Voltage and Current Noise ........................................................ 12

Total Noise and Source Resistance ........................................... 12

Noise Measurements .................................................................. 14

Capacitive Load Driving and Power Supply Considerations .. 15

Unity-Gain Buffer Applications ............................................... 15

Low Phase Error Amplifier ....................................................... 16

Five-Band, Low Noise, Stereo Graphic Equalizer .................. 16

Digital Panning Control ............................................................ 17

Dual Programmable Gain Amplifier ....................................... 17

Outline Dimensions ....................................................................... 19

Ordering Guide .......................................................................... 20

4/03—Rev. B to Rev. C

Deletion of OP270A model ............................................... Universal

Edits to Features ................................................................................. 1

Changes to Specifications ................................................................. 2

Deletion of Wafer Limits and Dice Characteristics ...................... 4

Changes to Absolute Maximum Ratings ........................................ 4

Changes to Ordering Guide ............................................................. 4

Changes to Equations in Noise Measurements section ............. 10

Change to Figure 10 ....................................................................... 11

Updated Outline Dimensions ....................................................... 14

11/02—Rev. A to Rev. B

Updated Ordering Guide .............................................................. 15

9/02—Rev. 0 to Rev. A

Edits to Absolute Maximum Ratings .............................................. 5

Edits to Ordering Guide ................................................................ 15

2/01—Revision 0: Initial Version

Rev. E | Page 2 of 20

OP270

SPECIFICATIONS

VS = ±15 V, TA = 25°C, unless otherwise noted.

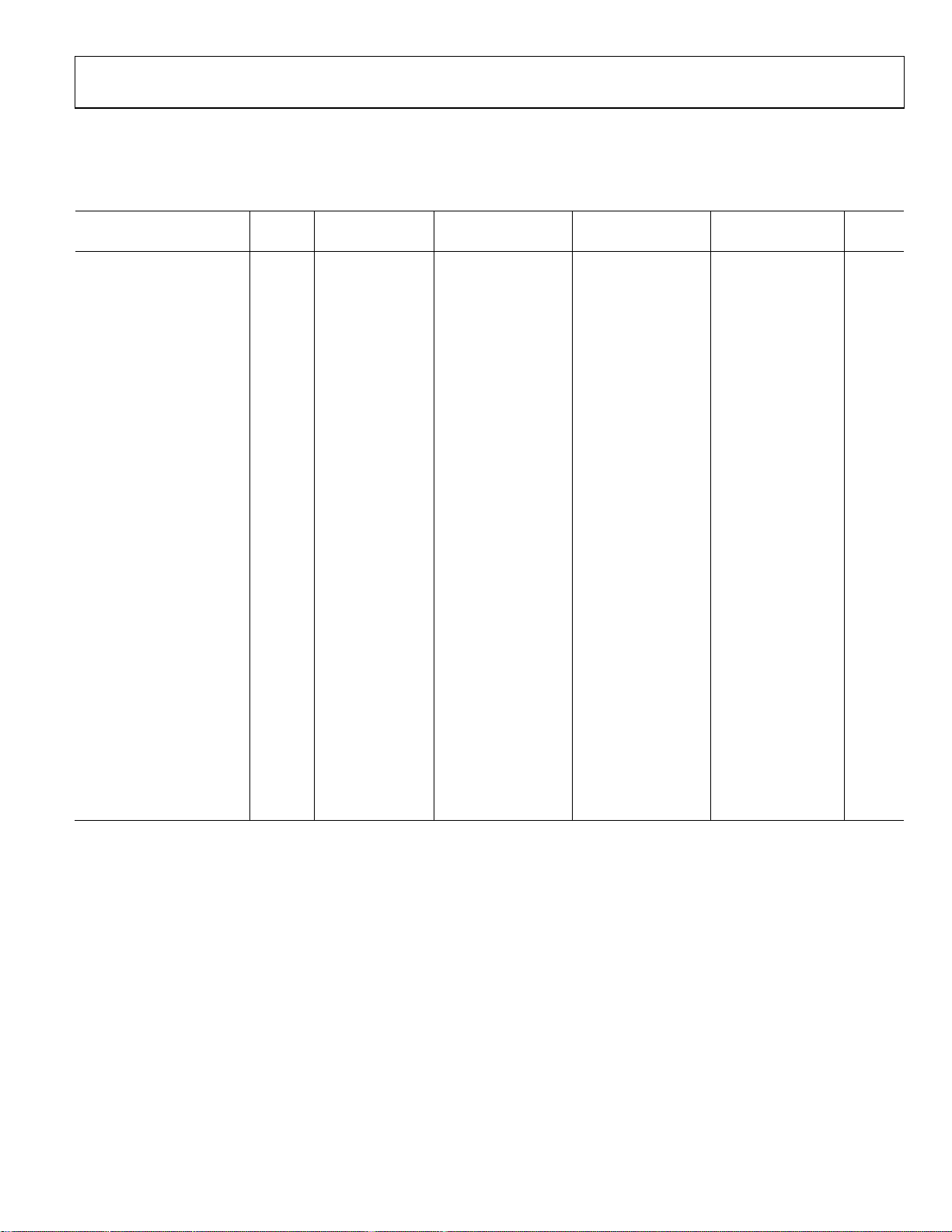

Table 1.

OP270E OP270F OP270G

Parameter Symbol Test Conditions

Input Offset Voltage VOS 10 75 20 150 50 250 μV

Input Offset Current IOS V

Input Bias Current IB V

Input Noise Voltage1 e

p-p 0.1 Hz to 10 Hz 80 200 80 200 80 nV p-p

n

Input Noise Voltage Density2 en f

e

e

f

n

f

n

Input Noise Current Density in f

i

i

f

n

f

n

Large-Signal Voltage Gain AVO

= 0 V 1 10 3 15 5 20 nA

CM

= 0 V 5 20 10 40 15 60 nA

CM

= 10 Hz 3.6 6.5 3.6 6.5 3.6 nV/√Hz

O

= 100 Hz 3.2 5.5 3.2 5.5 3.2 nV/√Hz

O

= 1 kHz 3.2 5.0 3.2 5.0 3.2 nV/√Hz

O

= 10 Hz 1.1 1.1 1.1 pA/√Hz

O

= 100 Hz 0.7 0.7 0.7 pA/√Hz

O

= 1 kHz 0.6 0.6 0.6 pA/√Hz

O

= ±10 V,

V

O

= 10 kΩ

R

L

= ±10 V,

V

O

R

= 2 kΩ

L

1500 2300 1000 1700 750 1500 V/mV

750 1200 500 900 350 700 V/mV

Input Voltage Range3 IVR ±12 ±12.5 ±12 ±12.5 ±12 ±12.5 V

Output Voltage Swing VO R

≥ 2 kΩ ±12 ±13.5 ±12 ±13.5 ±12 ±13.5 V

L

Common-Mode Rejection CMR VCM = ±11 V 106 125 100 120 90 110 dB

Power Supply Rejection

Ratio

PSRR

= ±4.5 V

V

S

to ±18 V

0.56 3.2 1.0 5.6 1.5 5.6 μV/V

Slew Rate SR 1.7 2.4 1.7 2.4 1.7 2.4 V/μs

No load 4 6.5 4 6.5 4 6.5 mA

Supply Current

I

SY

(All Amplifiers)

Gain Bandwidth Product GBP 5 5 5 MHz

Channel Separation1 CS

= ±20 V p-p,

V

O

f

= 10 Hz

O

125 175 125 175 175 dB

Input Capacitance CIN 3 3 3 pF

Input Resistance

Differential Mode RIN 0.4 0.4 0.4 MΩ

Common Mode R

Settling Time tS

20 20 20 GΩ

INCM

= +1, 10 V,

A

V

5 5 5 μs

step to 0.01%

1

Guaranteed but not 100% tested.

2

Sample tested.

3

Guaranteed by CMR test.

Unit Min Typ Max Min Typ Max Min Typ Max

Rev. E | Page 3 of 20

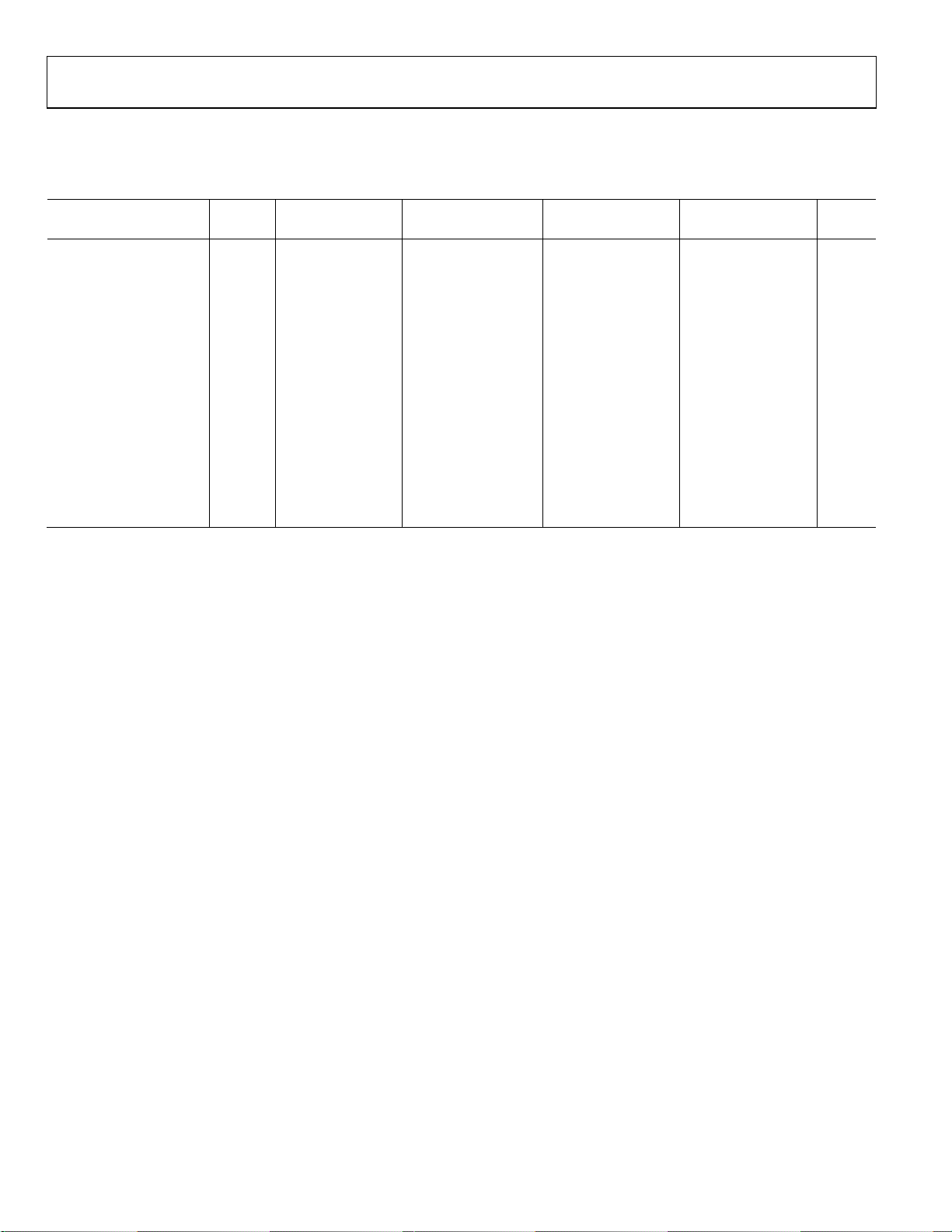

OP270

ELECTRICAL SPECIFICATIONS

VS = ±15 V, −40°C ≤ TA ≤ 85°C, unless otherwise noted.

Table 2.

OP270E OP270F OP270G

Parameter Symbol Test Conditions

Input Offset Voltage VOS 25 150 45 275 100 400 μV

TCV

Average Input Offset

0.2 1 0.4 2 0.7 3 μV/°C

OS

Voltage Drift

Input Offset Current IOS V

Input Bias Voltage IB V

Large-Signal Voltage Gain AVO

A

Input Voltage Range

1

VO

IVR ±12 ±12.5 ±12 ±12.5 ±12 ±12.5 V

Output Voltage Swing VO R

= 0 V 1.5 30 5 40 15 50 nA

CM

= 0 V 6 60 15 70 19 80 nA

CM

= ±10 V,

V

O

= 10 kΩ

R

L

= ±10 V,

V

O

R

= 2 kΩ

L

≥ 2 kΩ ±12 ±13.5 ±12 ±13.5 ±12 ±13.5 V

L

1000 1800 600 1400 400 1250 V/mV

500 900 300 700 225 670 V/mV

Common-Mode Rejection CMR VCM = ±11 V 100 120 94 115 90 100 dB

Power Supply Rejection

PSRR V

= ±4.5 V to ±18 V 0.7 5.6 1.8 10 2.0 1.5 μV/V

S

Ratio

No load 4.4 7.2 4.4 7.2 4.4 7.2 mA

Supply Current

I

SY

(All Amplifiers)

1

Guaranteed by CMR test.

Unit Min Typ Max Min Typ Max Min Typ Max

Rev. E | Page 4 of 20

OP270

ABSOLUTE MAXIMUM RATINGS

Table 3.

Parameter Rating

Supply Voltage 18 V

Differential Input Voltage1 1.0 V

Differential Input Current1 ±25 mA

Input Voltage Supply voltage

Output Short-Circuit Duration Continuous

Storage Temperature Range −65°C to +150°C

Lead Temperature Range (Soldering, 60 sec) 300°C

Junction Temperature (TJ) −65°C to +150°C

Operating Temperature Range −40°C to +85°C

1

The OP270 inputs are protected by back-to-back diodes. To achieve low noise

performance, current-limiting resistors are not used. If the differential voltage

exceeds +10 V, the input current should be limited to ±25 mA.

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

For military processed devices, refer to the Standard Microcircuit Drawing (SMD) available at the Defense Logistics

Agency website.

Table 4. Analog Devices Equivalent to SMD

SMD Part Number Analog Devices Equivalent

5962-8872101PA OP270AZMDA

ESD CAUTION

Rev. E | Page 5 of 20

OP270

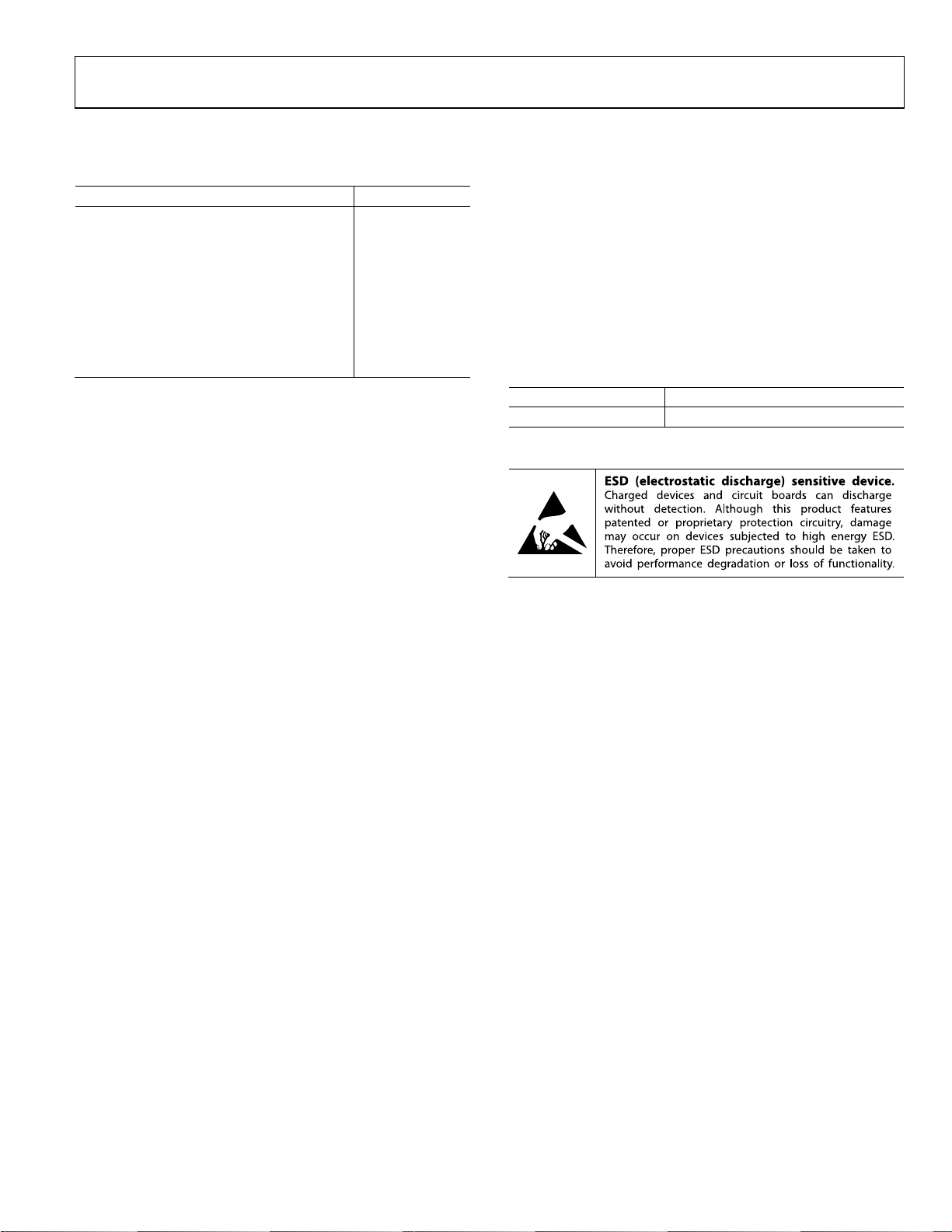

TYPICAL PERFORMANCE CHARACTERISTICS

VOLTAGE NOISE DENSITY (nV/√Hz)

10

9

8

7

6

5

4

3

2

TA = 25°C

V

= ±15V

S

1/f CORNER = 5Hz

CURRENT NOISE DE NSITY (pA/ √Hz)

10

1

TA = 25°C

V

= ±15V

S

1/f CORNER = 200Hz

1

1 10 100 1k

FREQUENCY (Hz)

Figure 3. Voltage Noise Density vs. Frequency

5

TA = 25°C

4

AT 10kHz

3

2

VOLTAGE NOISE DENSITY (nV/√Hz)

1

0 ±5 ±10 ±15 ±20

SUPPLY VOLTAGE (V)

AT 1kHz

Figure 4. Voltage Noise Density vs. Supply Voltage

0.1Hz TO 10Hz NOISE

00352-004

0.1

10 100 1k 10k

FREQUENCY (Hz)

00352-007

Figure 6. Current Noise Density vs. Frequency

40

VS = ±15V

30

20

10

0

VOLTAGE (µV)

–10

–20

00352-005

–30

–75 –50 –25 25 50 75 100 1250

TEMPERATURE (° C)

00352-008

Figure 7. Input Offset Voltage vs. Temperature

5

TA = 25°C

V

= ±15V

S

4

NOISE VO LTAGE ( 100nV/DIV )

TA = 25°C

T

= ±15V

S

TIME (1 sec/DIV)

Figure 5. 0.1 Hz to 10 Hz Input Voltage Noise

00352-006

Rev. E | Page 6 of 20

3

2

1

CHANGE IN OFF SET VOL TAGE (µA)

0

02341

TIME (Minutes)

Figure 8. Warm-Up Offset Voltage Drift

00352-009

5

OP270

7

VS = ±15V

V

= 0V

CM

6

5

4

INPUT BIAS CURRENT (nA)

3

2

–75 –50 –25 25 50 75 100 1250

TEMPERATURE (° C)

Figure 9. Input Bias Current vs. Temperature

00352-010

130

120

110

100

90

80

70

60

CMR (dB)

50

40

30

20

10

1 10 1k 10k 100k 1M100

FREQUENCY (Hz)

Figure 12. CMR vs. Frequency

TA = 25°C

V

= ±15V

S

00352-013

5

VS = ±15V

V

= 0V

CM

4

3

2

INPUT OFFSET CURRENT (nA)

1

0

–75 –50 –25 25 50 75 100 1250

TEMPERATURE (° C)

Figure 10. Input Offset Current vs. Temperature

7

TA = +25°C

V

= ±15V

S

6

5

4

6

5

4

+125°C

+25°C

3

TOTAL SUPPLY CURRENT (mA)

00352-011

2

–55°C

00352-014

0 ±5 ±10 ±15 ±20

SUPPLY VOLTAGE (V)

Figure 13. Total Supply Current vs. Supply Voltage

8

VS = ±15V

7

6

5

4

3

INPUT BIAS CURRENT (nA)

3

2

–10.0 –5. 0 0 5.0

–12.5 –7. 5 –2.5 2.5

COMMON-MODE VOLTAGE (V)

7.5 12.5

Figure 11. Input Bias Current vs. Common-Mode Voltage

10.0

00352-012

Rev. E | Page 7 of 20

2

TOTAL SUPPLY CURRENT (mA)

1

0

–75 –50 –25 25 50 75 100 1250

TEMPERATURE (° C)

Figure 14. Total Supply Current vs. Temperature

00352-015

OP270

= ±15V

80

100

120

140

160

180

PHASE SHIF T (Degrees)

00352-019

140

120

100

80

60

PSR (dB)

40

20

0

1 10 1k 10k 100k 1M 10M 100M100

140

120

100

80

–PSR

+PSR

FREQUENCY (Hz)

Figure 15. PSR vs. Frequency

TA = 25°C

TA = 25°C

V

= ±15V

S

25

20

15

10

5

0

OPEN-LOOP GAIN (dB)

–5

00352-016

–10

12345678910

FREQUENCY (MHz )

PHASE

MARGIN = 62°

GAIN

PHASE

TA = 25°C

V

S

Figure 18. Open-Loop Gain and Phase Shift vs. Frequency

5000

4000

3000

60

40

OPEN-LOOP GAIN (dB)

20

0

1 10 1k 10k 100k 1M 10M 100M100

FREQUENCY (Hz)

Figure 16. Open-Loop Gain vs. Frequency

80

60

40

20

CLOSED-LOOP GAIN (dB)

0

–20

1k 10k 100k 1M 10M

FREQUENCY (Hz)

Figure 17. Closed-Loop Gain vs. Frequency

TA = 25°C

V

= ±15V

S

2000

OPEN-LOOP GAIN (V/mA)

1000

00352-017

0

0 ±5 ±10 ±15 ±20 ±25

SUPPLY VOLTAGE (V)

00352-020

Figure 19. Open-Loop Gain vs. Supply Voltage

80

8

70

60

50

PHASE MARGIN ( Degrees)

00352-018

40

–75 –50 –25 25 50 75 100 125 1500

Ф

GBP

TEMPERATURE (° C)

7

6

5

GAIN BANDWIDTH P RODUCT (MHz)

4

00352-021

Figure 20. Phase Margin and Gain Bandwidth Product vs. Temperature

Rev. E | Page 8 of 20

OP270

28

24

20

16

12

8

MAXIMUM OUTPUT SWING (V)

4

TA = 25°C

V

= ±15V

S

THD = 1%

100

TA = 25°C

V

= ±15V

S

A

= 1

75

50

A

= 100

V

OUTPUT IMPEDANCE (Ω)

25

A

= 10

V

V

0

1k 10k 100k 1M 10M

FREQUENCY (Hz)

Figure 21. Maximum Output Swing vs. Frequency

15

TA = 25°C

V

= ±15V

14

S

13

12

11

10

9

8

7

MAXIMUM OUTPUT VOLTAGE (V)

6

5

100 1k 10k

POSITIVE

SWING

NEGATIVE

SWING

LOAD RESIST ANCE (Ω)

Figure 22. Maximum Output Voltage vs. Load Resistance

50

TA = 25°C

V

= ±15V

S

V

= 100mV

IN

A

= +1

40

V

30

20

10

SMALL-SIGNAL OVERSHOOT (%)

0

0 200 400 600 800 1000

CAPACITIVE L OAD (pF)

Figure 23. Small-Signal Overshoot vs. Capacitive Load

00352-022

0

1k 10k 100k 1M 10M

FREQUENCY (Hz)

00352-025

Figure 24. Output Impedance vs. Frequency

2.8

VS = ±15V

2.7

2.6

2.5

2.4

SLEW RATE (V/µs)

2.3

00352-023

2.2

–75 –50 –25 25 50 75 100 1250

TEMPERATURE (° C)

–SR

+SR

00352-026

Figure 25. Slew Rate vs. Temperature

190

180

170

160

150

140

130

120

110

100

CHANNEL SEPARATIO N (dB)

90

TA = 25°C

V

= ±15V

S

80

V

= 20V p-p TO 10kHz

00352-024

O

70

1 10 1k 10k 100k 1M100

00352-027

FREQUENCY (Hz)

Figure 26. Channel Separation vs. Frequency

Rev. E | Page 9 of 20

OP270

0.1

TA = 25°C

V

= ±15V

S

V

= 20V p-p

O

R

= 2kΩ

L

AV = 10

0.01

AV = 1

TOTAL HARMO NIC DISTO RTION (%)

0.001

10 100 1k 10k

FREQUENCY (Hz)

Figure 27. Total Harmonic Distortion vs. Frequency

TA = 25°C

V

= ±15V

S

A

= +1

V

R

= 2kΩ

L

00352-028

TA = 25°C

V

= ±15V

S

A

= +1

V

R

= 2kΩ

L

50mV 200ns

Figure 29. Small-Signal Transient Response

00352-030

5V 20µs

00352-029

Figure 28. Large-Signal Transient Response

Rev. E | Page 10 of 20

OP270

V

TEST CIRCUITS

5kΩ

500Ω

1/2

OP270

5kΩ

50Ω

1/2

OP270

CHANNEL SEPARATION = 20 LOG

Figure 30. Channel Separation Test Circuit

+18

20V

V

1

p-p

V

2

V

1

V2/1000

00325-031

1/2

OP270

1/2

OP270

–18V

8

1

7

4

00325-032

100kΩ

200kΩ

100kΩ

2

3

6

5

Figure 31. Burn-In Circuit

Rev. E | Page 11 of 20

OP270

√

√

APPLICATIONS INFORMATION

VOLTAGE AND CURRENT NOISE

The OP270 is a very low noise dual op amp, exhibiting a typical

voltage noise density of only 3.2 nV/√Hz at 1 kHz. Because the

voltage noise is inversely proportional to the square root of the

collector current, the exceptionally low noise characteristic of

the OP270 is achieved in part by operating the input transistors

at high collector currents. Current noise, however, is directly

proportional to the square root of the collector current. As a

result, the outstanding voltage noise density performance of the

OP270 is gained at the expense of current noise performance,

which is normal for low noise amplifiers.

To obtain the best noise performance in a circuit, it is vital to

understand the relationships among voltage noise (e

noise (i

), and resistor noise (et).

n

), current

n

TOTAL NOISE AND SOURCE RESISTANCE

The total noise of an op amp can be calculated by

222

)()()(

eRieE ++=

tsnnn

where:

E

is the total input-referred noise.

n

e

is the op amp voltage noise.

n

i

is the op amp current noise.

n

e

is the source resistance thermal noise.

t

R

is the source resistance.

S

The total noise is referred to the input and at the output is

amplified by the circuit gain.

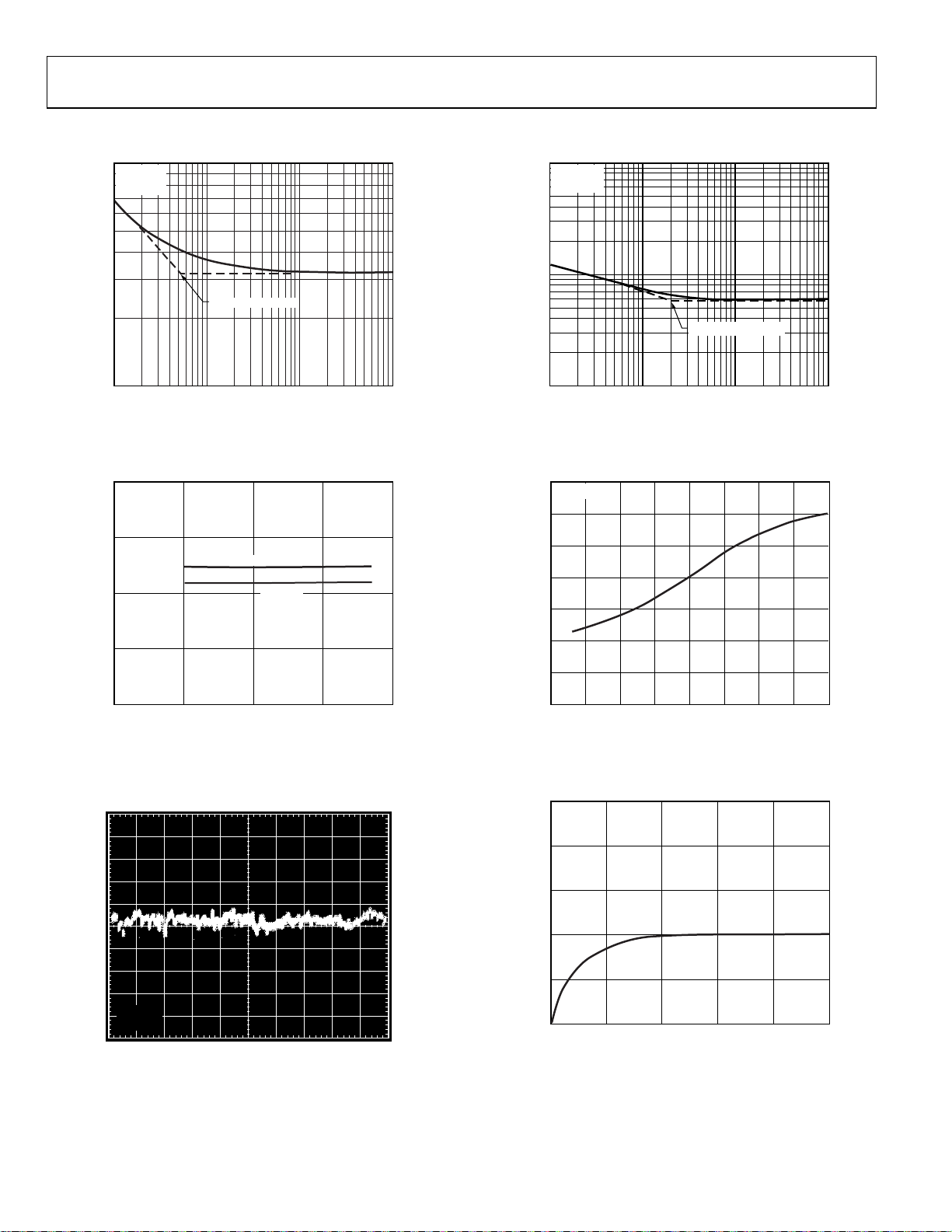

Figure 32 shows the relationship between total noise at 1 kHz

and source resistance. When R

is dominated by the voltage noise of the OP270. As R

above 1 kΩ, total noise increases and is dominated by resistor

noise rather than by the voltage or current noise of the OP270.

When R

exceeds 20 kΩ, the current noise of the OP270

S

becomes the major contributor to total noise.

100

is less than 1 kΩ, the total noise

S

rises

S

Figure 33 also shows the relationship between total noise and

source resistance, but at 10 Hz. Total noise increases more

quickly than shown in Figure 32 because current noise is

inversely proportional to the square root of frequency. In

Figure 33, the current noise of the OP270 dominates the total

noise when R

is greater than 5 kΩ.

S

Figure 32 and Figure 33 show that to reduce total noise, source

resistance must be kept to a minimum. In applications with a

high source resistance, the OP200, with lower current noise

than the OP270, can provide lower total noise.

100

Hz)

OP200

10

OP270

TOTAL NOISE (nV/

RESISTOR

NOISE ONLY

1

100 1k 10k 100k

SOURCE RESIST ANCE (Ω)

00352-034

Figure 33. Total Noise vs. Source Resistance

(Including Resistor Noise) at 10 Hz

Figure 34 shows peak-to-peak noise vs. source resistance over

the 0.1 Hz to 10 Hz range. At low values of R

, the voltage noise

S

of the OP270 is the major contributor to peak-to-peak noise,

with current noise becoming the major contributor as R

S

increases. The crossover point between the OP270 and the

OP200 for peak-to-peak noise is at a source resistance of 17 kΩ.

1k

OP200

Hz)

OP200

10

OP270

TOTAL NOISE (nV/

RESISTOR

NOISE ONLY

1

100 1k 10k 100k

SOURCE RESIST ANCE (Ω)

00352-033

100

OP270

PEAK-TO-PEAK NOISE (nV )

10

100

RESISTOR

NOISE ONLY

1k

SOURCE RESIST ANCE (Ω)

10k 100k

Figure 34. Peak-to-Peak Noise (0.1 Hz to 10 Hz) vs. Source Resistance

(Including Resistor Noise)

00352-035

Figure 32. Total Noise vs. Source Resistance

(Including Resistor Noise) at 1 kHz

Rev. E | Page 12 of 20

OP270

For reference, typical source resistances of some signal sources are listed in Table 5.

Table 5. Typical Source Resistances

Device Source Impedance Comments

Strain Gage <500 Ω Typically used in low frequency applications.

Magnetic Tapehead, Microphone <1500 Ω

Magnetic Phonograph Cartridge <1500 Ω

Linear Variable Differential Transformer <1500 Ω

R3

1.24kΩ

R1

5Ω

OP270

R2

5Ω

DUT

R4

200Ω

OP27E

909Ω

C1

2µF

R5

600Ω

R6

Figure 35. Peak-to-Peak Voltage Noise Test Circuit (0.1 Hz to 10 Hz)

R8

10kΩ

D1, D2

1N4148

is very important to reduce self-magnetization problems when

Low I

B

direct coupling is used. OP270 I

is important to reduce self-magnetization problems in direct-coupled

Low I

B

can be disregarded.

B

applications. OP270 does not introduce any self-magnetization problems.

Used in rugged servo-feedback applications. The bandwidth of interest is

400 Hz to 5 kHz.

C4

0.22µF

OP27E

306Ω

C2

0.032µF

R10

65.4kΩ

R9

R11

65.4kΩ

0.22µF

R14

C3

10kΩ

R12

OP42E

R13

5.9kΩ

4.99kΩ

C5

1µF

GAIN = 50,000

V

= ±15V

S

e

OUT

00325-036

Rev. E | Page 13 of 20

OP270

(

(

(

)

(

)

(

NOISE MEASUREMENTS

Peak-to-Peak Voltage Noise

The circuit of Figure 35 is a test setup for measuring peak-topeak voltage noise. To measure the 200 nV peak-to-peak noise

specification of the OP270 in the 0.1 Hz to 10 Hz range, the

following precautions must be observed:

• The device has to be warmed up for at least five minutes.

As shown in the warm-up drift curve (see Figure 8), the

offset voltage typically changes 2 μV due to increasing chip

temperature after power-up. In the 10 sec measurement

interval, these temperature-induced effects can exceed tens

of nanovolts.

• For similar reasons, the device has to be well shielded from

air currents. Shielding also minimizes thermocouple effects.

• Sudden motion in the vicinity of the device can also feed

through to increase the observed noise.

• The test time to measure noise of 0.1 Hz to 10 Hz should

not exceed 10 sec. As shown in the noise-tester frequency

response curve of Figure 36, the 0.1 Hz corner is defined by

only one pole. The test time of 10 sec acts as an additional

pole to eliminate noise contribution from the frequency

band below 0.1 Hz.

• A noise voltage density test is recommended when measuring

noise on several units. A 10 Hz noise voltage density measurement correlates well with a 0.1 Hz to 10 Hz peak-to-peak

noise reading because both results are determined by the

white noise and the location of the 1/f corner frequency.

• Power should be supplied to the test circuit by well bypassed

low noise supplies, such as batteries. Such supplies will minimize output noise introduced via the amplifier supply pins.

100

80

60

GAIN (dB)

40

20

0

0.01 0.1 1 10 100

Figure 36. 0.1 Hz to 10 Hz Peak-to-Peak Voltage Noise

Test Circuit Frequency Response

FREQUENCY (Hz)

00352-037

Noise Measurement—Noise Voltage Density

The circuit of Figure 37 shows a quick and reliable method for

measuring the noise voltage density of dual op amps. The first

amplifier is in unity gain, with the final amplifier in a noninverting

gain of 101. Because the noise voltages of the amplifiers are

uncorrelated, they add in rms to yield

OUT

101

2

)

nA

2

)

eee +=

nB

The OP270 is a monolithic device with two identical amplifiers.

Therefore, the noise voltage densities of the amplifiers match,

giving

2

R1

100Ω

e

(nV/√Hz) ≈ 101 (√2en)

OUT

= ±15V

V

S

==

OP270

OUT

1/2

OP270

Figure 37. Noise Voltage Density Test Circuit

)

eee 21012101

nn

R2

10kΩ

1/2

TO SPECTRUM ANALYZER

e

OUT

00325-038

Noise Measurement—Current Noise Density

The test circuit shown in Figure 38 can be used to measure current

noise density. The formula relating the voltage output to the current

noise density is

2

e

⎞

⎛

nOUT

⎜

G

⎝

i

=

n

()

⎟

⎠

R

S

2

HznV

/40−

where:

G is a gain of 10,000.

R

= 100 kΩ source resistance.

S

R3

1.24kΩ

R15ΩR2

100kΩ

OP270

DUT

200Ω

Figure 38. Current Noise Density Test Circuit

OP27E

R5

8.06kΩ

R4

e

nOUT

TO SPECTRUM ANALYZER

GAIN = 10,000

V

= ±15V

S

00325-039

Rev. E | Page 14 of 20

OP270

V

V

CAPACITIVE LOAD DRIVING AND POWER SUPPLY CONSIDERATIONS

The OP270 is unity-gain stable and capable of driving large

capacitive loads without oscillating. Nonetheless, good supply

bypassing is highly recommended. Proper supply bypassing

reduces problems caused by supply line noise and improves the

capacitive load driving capability of the OP270.

In the standard feedback amplifier, the output resistance of the

op amp combines with the load capacitance to form a low-pass

filter that adds phase shift in the feedback network and reduces

stability. A simple circuit to eliminate this effect is shown in

Figure 39. The components C1 and R3 decouple the amplifier

from the load capacitance and provide additional stability. The

values of C1 and R3 shown in Figure 39 are for a load capacitance

of up to 1000 pF when used with the OP270.

+

+

C2

10µF

C3

0.1µF

R1

IN

OP270

C1

200pF

C5

0.1µF

V–

Figure 39. Driving Large Capacitive Loads

R2

R3

50Ω

C4

10µF

+

PLACE SUPPLY D ECOUPL ING

CAPACIT OR AT O P270

V

OUT

C1

1000pF

00325-040

UNITY-GAIN BUFFER APPLICATIONS

When Rf ≤ 100 Ω and the input is driven with a fast, large signal

pulse (>1 V), the output waveform looks like the one in Figure 40.

During the fast feedthrough-like portion of the output, the input

protection diodes effectively short the output to the input, and

a current, limited only by the output short-circuit protection, is

drawn by the signal generator. With R

capable of handling the current requirements (I

the amplifier stays in its active mode and a smooth transition occurs.

When R

> 3 kΩ, a pole created by Rf and the input capacitance

f

(3 pF) of the amplifier creates additional phase shift and reduces

phase margin. A small capacitor (20 pF to 50 pF) in parallel with

helps eliminate this problem.

R

f

R

f

OP270

Figure 40. Pulsed Operation

≥ 500 Ω, the output is

f

≤ 20 mA at 10 V);

L

2.4V/µs

00325-041

Rev. E | Page 15 of 20

OP270

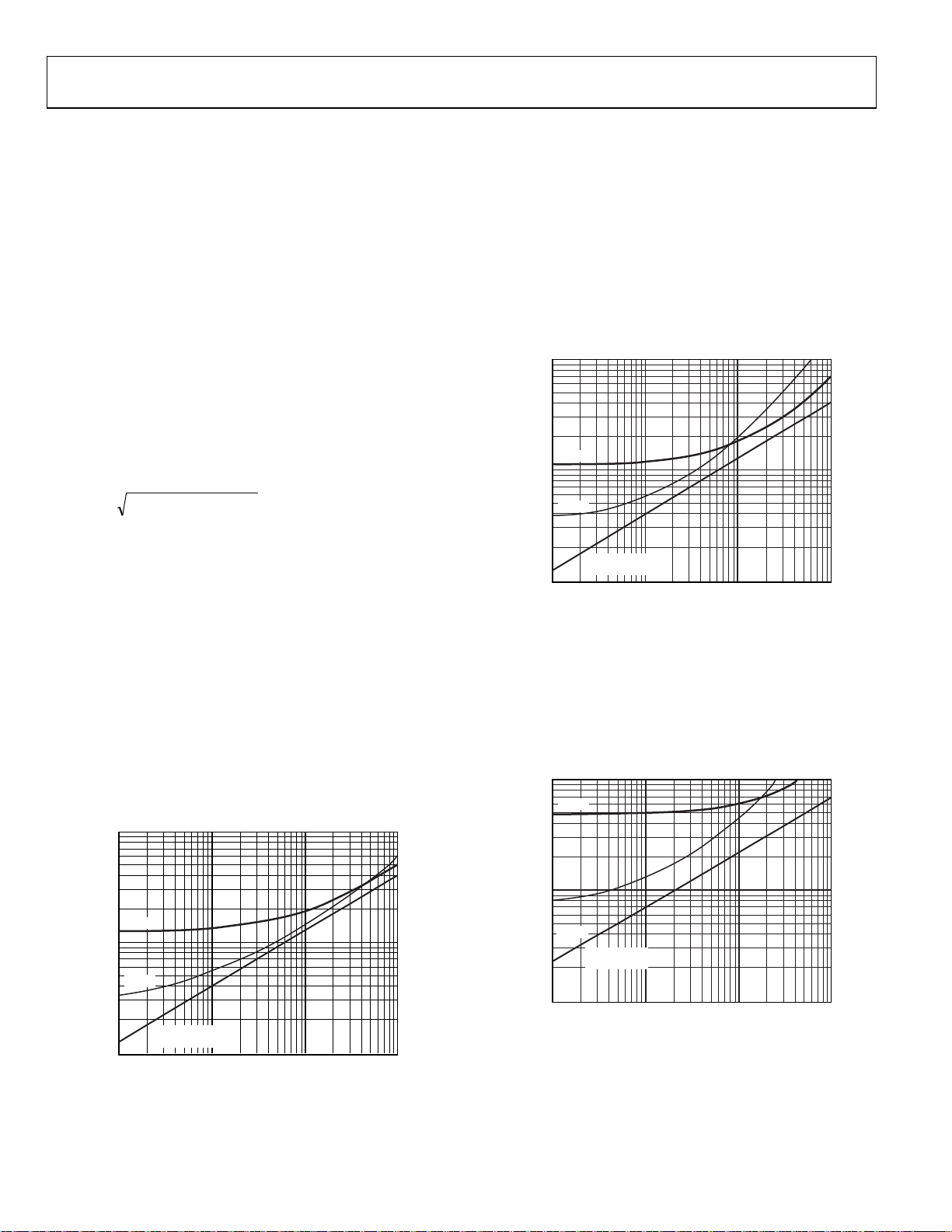

LOW PHASE ERROR AMPLIFIER

The simple amplifier depicted in Figure 41 utilizes a monolithic

dual operational amplifier and a few resistors to substantially

reduce phase error compared with conventional amplifier

designs. At a given gain, the frequency range for a specified

phase accuracy is more than a decade greater than that of a

standard single op amp amplifier.

The low phase error amplifier performs second-order frequency compensation through the response of Op Amp A2 in

the feedback loop of A1. Both op amps must be extremely well

matched in frequency response. At low frequencies, the A1

feedback loop forces V

forces V

function of V

/(K1 + 1) = V2/(K1 + 1), yielding an overall transfer

O

O/VIN

resistor divider at the output, V

the resistor divider around A2. Note that, like a conventional

single op amp amplifier, the dc gain is set by resistor ratios only.

Minimum gain for the low phase error amplifier is 10.

R2

K2

V

IN

ASSUME A1 AND A2 ARE MATCHED.

Figure 42 compares the phase error performance of the low

phase error amplifier with a conventional single op amp

amplifier and a cascaded two-stage amplifier. The low phase

error amplifier shows a much lower phase error, particularly for

frequencies where ω/βω

−0.1° occurs at 0.002 ω/βω

at 0.11 ω/βω

for the low phase error amplifier.

T

/(K1 + 1) = VIN. The A2 feedback loop

2

= K1 + 1. The dc gain is determined by the

, and is not directly affected by

O

R2 R2 = R1

1/2

OP270E

A2

1/2

OP270E

A1

ω

T

A

(s) =

O

s

Figure 41. Low Phase Error Amplifier

< 0.1. For example, a phase error of

T

for the single op amp amplifier, but

T

R1

V

2

R1

K1

VO = (K1 + 1)V

V

O

IN

00325-042

0

PHASE SHIF T (Degrees)

–1

–2

–3

–4

–5

–6

–7

0.001

SINGLE OP AMP.

CONVENTIO NAL DESIGN

CASCADED

(TWO STAGES)

LOW PHASE E RROR

0.01 0.1 1

0.005

FREQUENCY RATI O (1/βω)(ω/ωT)

AMPLIFI ER

00352-043

0.05 0.5

Figure 42. Phase Error Comparison

FIVE-BAND, LOW NOISE, STEREO GRAPHIC EQUALIZER

The graphic equalizer circuit shown in Figure 43 provides 15 dB

of boost or cut over a five-band range. Signal-to-noise ratio over

a 20 kHz bandwidth is better than 100 dB and referred to a 3 V

rms input. Larger inductors can be replaced by active inductors,

but consequently reduces the signal-to-noise ratio.

C1

0.47µF

V

IN

R1

47kΩ

R3

680Ω

R5

680Ω

R7

680Ω

R9

680Ω

R11

680Ω

1/2

OP270E

C2

6.8µF

+

TANTALUM

C3

1µF

+

TANTALUM

C4

0.22µF

+

C5

0.047µF

+

C6

0.022µF

+

Figure 43. Five-Band, Low Noise Graphic Equalizer

3.3kΩ

L1

1H

L2

600mH

L3

180mH

L4

60mH

L5

10mH

R2

R14

100Ω

V

OUT

1kΩ

R6

1kΩ

R8

1kΩ

R10

1kΩ

R12

1kΩ

1/2

60Hz

200Hz

800Hz

3kHz

10kHz

OP270E

R13

3.3kΩ

R4

00325-044

Rev. E | Page 16 of 20

OP270

A

A

DIGITAL PANNING CONTROL

Figure 44 uses a DAC8221 (a dual 12-bit CMOS DAC) to pan a

signal between two channels. One channel is formed by the

current output of DAC A driving one-half of an OP270 in a

current-to-voltage converter configuration. The other channel

is formed by the complementary output current of DAC A,

which normally flows to ground through the AGND pin. This

complementary current is converted to a voltage by the other

half of the OP270, which also holds AGND at virtual ground.

Gain error due to mismatching between the internal DAC

ladder resistors and the current-to-voltage feedback resistors is

eliminated by using feedback resistors internal to the DAC8221.

Only DAC A passes a signal; DAC B provides the second

feedback resistor. With V

voltage converter, using R

B unconnected, the current-to-

REF

, is accurate and not influenced by

FBB

digital data reaching DAC B. Distortion of the digital panning

control is less than 0.002% over the 20 Hz to 20 kHz audio

range. Figure 45 shows the complementary outputs for a 1 kHz

input signal and a digital ramp applied to the DAC data input.

DUAL PROGRAMMABLE GAIN AMPLIFIER

The dual OP270 and the DAC8221 (a dual 12-bit CMOS DAC)

can be combined to form a space-saving, dual programmable

amplifier. The digital code present at the DAC, which is easily

set by a microprocessor, determines the ratio between the internal

feedback resistor and the resistance that the DAC ladder presents

to the op amp feedback loop. Gain of each amplifier is

V

where n is the decimal equivalent of the 12-bit digital code

present at the DAC.

If the digital code present at the DAC consists of all 0s, the

feedback loop opens, causing the op amp output to saturate. A

20 MΩ resistor placed in parallel with the DAC feedback loop

eliminates this problem with only a very small reduction in gain

accuracy.

4096

O

IN

−=

nV

V

IN

DAC DATA BUS

PINS 6 (MSB) TO 17 (LSB)

NC

18

19

WRITE

CONTROL

20

OUT

OUT

DAC8221P

V

A

REF

DAC A

B

V

REF

DAC B

DAC A/DAC B

CS

WR

+5V

V

DD

DGND

21

R

FBA

3

I

A

OUT

24

AGND

1

R

FBB

23

B

I

OUT

2422

5

2

OP270G P

3

6

OP270G P

5

+15V

–15V

Figure 44. Digital Panning Control

5V5V 1 ms

Figure 45. Digital Panning Control Output

0.01µF

+

10µF

–

8

1/2

1

4

0.1µF

1/2

7

+

10µF

–

OUT

OUT

00352-046

0325-045

Rev. E | Page 17 of 20

OP270

V

–

V

+5V

21

V

DD

V

A

REF

4

R

FBA

I

A

2

DAC A

R

FBB

DAC B

DGND

OUT

1

AGND

B

I

24

OUT

20MΩ

V

B

REF

22

5

VINA

VINB

WRITE

CONTROL

DAC8221P

3

23

DAC DATA BUS

PINS 6 (MSB) TO 17 (L SB)

18

19

20

20MΩ

2

3

OP270EZ

6

OP270GP

5

+15

1/2

–15V

1/2

0.01µF

+

10µF

–

8

1

V

A

+

–

V

OUT

10µF

OUT

B

00325-047

4

0.1µF

7

Figure 46. Dual Programmable Gain Amplifier

+

BIAS

OUT

IN

+IN

V–

00325-003

Figure 47. Simplified Schematic

(One of Two Amplifiers Is Shown)

Rev. E | Page 18 of 20

OP270

OUTLINE DIMENSIONS

0.005 (0.13)

0.200 (5.08)

MAX

0.200 (5.08)

0.125 (3.18)

0.023 (0.58)

0.014 (0.36)

CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETER DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 48. 8-Lead Ceramic Dual In-Line Package [CERDIP]

Dimensions shown in inches and (millimeters)

0.400 (10.16)

0.365 (9.27)

0.355 (9.02)

8

1

0.100 (2.54)

0.210 (5.33)

0.150 (3.81)

0.130 (3.30)

0.115 (2.92)

0.022 (0.56)

0.018 (0.46)

0.014 (0.36)

MAX

BSC

0.070 (1.78)

0.060 (1.52)

0.045 (1.14)

0.055 (1.40)

MIN

14

0.100 (2.54) BSC

0.405 (10.29) MAX

5

4

MAX

58

0.070 (1.78)

0.030 (0.76)

0.280 (7.11)

0.250 (6.35)

0.240 (6.10)

0.015

(0.38)

MIN

SEATING

PLANE

0.005 (0.13)

MIN

0.310 (7.87)

0.220 (5.59)

0.060 (1.52)

0.015 (0.38)

0.150 (3.81)

MIN

SEATING

PLANE

Z-Suffix

(Q-8)

0.060 (1.52)

0.015 (0.38)

GAUGE

MAX

PLANE

0.320 (8.13)

0.290 (7.37)

15°

0°

0.325 (8.26)

0.310 (7.87)

0.300 (7.62)

0.430 (10.92)

MAX

0.015 (0.38)

0.008 (0.20)

0.195 (4.95)

0.130 (3.30)

0.115 (2.92)

0.014 (0.36)

0.010 (0.25)

0.008 (0.20)

CONTROLL ING DIMENS IONS ARE IN INCHES; MILLIMETER DI MENSIONS

(IN PARENTHESES) ARE ROUNDED-OF F INCH EQUI VALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRI ATE FOR USE IN DESIGN.

CORNER LEADS MAY BE CONFIGURED AS WHOL E OR HALF LEADS.

COMPLIANT TO JEDEC STANDARDS MS-001

070606-A

Figure 49. 8-Lead Plastic Dual In-Line Package [PDIP]

Narrow Body

P-Suffix

(N-8)

Dimensions shown in inches and (millimeters)

Rev. E | Page 19 of 20

OP270

C

0.30 (0.0 118)

0.10 (0.0039)

OPLANARITY

0.10

10.50 (0.4134)

10.10 (0.3976)

BSC

9

7.60 (0.2992)

7.40 (0.2913)

8

10.65 (0.4193)

10.00 (0.3937)

2.65 (0.1043)

2.35 (0.0925)

SEATING

PLANE

8°

0°

0.33 (0.0130)

0.20 (0.0079)

5

0

.

7

0

.

2

5

16

1

1.27 (0.0500)

0.51 (0.0201)

0.31 (0.0122)

CONTROLL ING DIMENS IONS ARE IN MILLIM ETERS; INCH DI MENSIONS

(IN PARENTHESES) ARE ROUNDED-O FF MIL LIMETE R EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRI ATE FOR USE IN DESIGN.

COMPLIANT TO JEDEC STANDARDS MS-013- AA

(

0

.

0

2

9

0

0

9

(

0

.

1.27 (0.0500)

0.40 (0.0157)

5

)

45°

8

)

032707-B

Figure 50. 16-Lead Standard Small Outline Package [SOIC_W]

Wide Body

S-Suffix

(RW-16)

Dimensions shown in millimeters and (inches)

ORDERING GUIDE

1

θ

JA

(°C/W) Temperature Range Package Description

is specified for device soldered to

JA

Package

Option

Model

T

= +25°C

A

Max (μV)

V

OS

θ

JC

(°C/W)

OP270EZ 75 12 134 −40°C to +85°C 8-Lead CERDIP Q-8 (Z-Suffix)

OP270FZ 150 12 134 −40°C to +85°C 8-Lead CERDIP Q-8 (Z-Suffix)

OP270GP 250 37 96 −40°C to +85°C 8-Lead PDIP N-8 (P-Suffix)

OP270GPZ

2

−40°C to +85°C 8-Lead PDIP N-8 (P-Suffix)

OP270GS 250 27 92 −40°C to +85°C 16-Lead SOIC_W RW-16 (S-Suffix)

OP270GS-REEL −40°C to +85°C 16-Lead SOIC_W RW-16 (S-Suffix)

OP270GSZ

OP270GSZ-REEL

1

θ

JA

printed circuit board for SOIC package.

2

Z = RoHS Compliant Part.

2

−40°C to +85°C 16-Lead SOIC_W RW-16 (S-Suffix)

2

−40°C to +85°C 16-Lead SOIC_W RW-16 (S-Suffix)

is specified for worst-case mounting conditions, that is, θJA is specified for device in socket for CERDIP and PDIP packages; θ

©2001–2010 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

D00325-0-2/10(E)

Rev. E | Page 20 of 20

Loading...

Loading...