ANALOG DEVICES OP249 Service Manual

Dual, Precision

O

0

www.BDTIC.com/ADI

JFET High Speed Operational Amplifier

FEATURES

Fast slew rate: 22 V/s typical

Settling time (0.01%): 1.2 µs maximum

Offset voltage: 300 µV maximum

High open-loop gain: 1000 V/mV minimum

Low total harmonic distortion: 0.002% typical

Improved replacement for AD712, LT1057, OP215, TL072,

and MC34

APPLICATIONS

Output amplifier for fast DACs

Signal processing

Instrumentation amplifiers

Fast sample-and-holds

Active filters

Low distortion audio amplifiers

Input buffer for ADCs

Servo controllers

082

OP249

PIN CONFIGURATIONS

UT A

1

OP249

A

2

–IN A

+IN A

3

V–

4

B

Figure 1. 8-Lead CERDIP (Q-8) and

8-Lead

PDIP (N-8)

1

+IN A

+IN B

–IN B

2

V–

3

4

A

OP249

B

Figure 2. 8-Lead SOIC (R-8)

8

7

6

5

8

7

6

5

V+

OUT B

–IN B

+IN B

–IN A

OUT A

V+

OUT B

00296-001

00296-002

GENERAL DESCRIPTION

The OP249 is a high speed, precision dual JFET op amp, similar to

the popular single op amp, the OP42. The OP249 outperforms

available dual amplifiers by providing superior speed with

excellent dc performance. Ultrahigh open-loop gain (1 kV/mV

minimum), low offset voltage, and superb gain linearity makes

the OP249 the industry’s first true precision, dual high speed

amplifier.

With a slew rate of 22 V/μs typical and a fast settling time of less

n 1.2 μs maximum to 0.01%, the OP249 is an ideal choice for

tha

high speed bipolar DAC and ADC applications. The excellent

dc performance of the OP249 allows the full accuracy of high

resolution CMOS DACs to be realized.

0.01

.001

TA = 25°C

= ±15V

V

S

= 10V p-p

V

O

= 10kΩ

R

L

= 1

A

V

20

100 1k 10k 20k

100

870ns

90

10

0%

500ns10mV

00296-003

Figure 3. Fast Settling (0.01%) Figure 4. Low Distortion, A

Symmetrical slew rate, even when driving large load, such as,

600 Ω o

r 200 pF of capacitance and ultralow distortion, make

the OP249 ideal for professional audio applications, active filters,

high speed integrators, servo systems, and buffer amplifiers.

The OP249 provides significant performance upgrades to the

TL072, AD712,

= 1, RL = 10 kΩ Figure 5. Excellent Output Drive, RL = 600 Ω

V

OP215, MC34082, and LT1057.

100

90

10

0%

00296-004

5V 1µs

00296-005

Rev. F

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2007 Analog Devices, Inc. All rights reserved.

OP249

www.BDTIC.com/ADI

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications....................................................................................... 1

Pin Configurations ........................................................................... 1

General Description......................................................................... 1

Revision History ............................................................................... 2

Specifications..................................................................................... 3

Electrical Characteristics............................................................. 3

Absolute Maximum Ratings............................................................ 6

ESD Caution.................................................................................. 6

REVISION HISTORY

5/07—Rev. E to Rev. F

Updated Format..................................................................Universal

Changes to Table 1............................................................................ 3

Changes to Table 2............................................................................ 4

Changes to Table 3 and Table 4....................................................... 5

Changes to Table 5............................................................................ 6

Changes to Figure 31...................................................................... 11

Changes to Figure 37 and Figure 38............................................. 12

Deleted OP249 SPICE Macro-Model Section ............................ 14

Deleted Figure 18; Renumbered Sequentially ............................ 14

Deleted Table I ................................................................................ 15

Changes to Discussion on Driving ADCs Section..................... 17

Updated Outline Dimensions....................................................... 18

Changes to Ordering Guide.......................................................... 19

Typical Perf or m an c e Charac t e r istics ..............................................7

Applications Information.............................................................. 13

Open-Loop Gain Linearity ....................................................... 14

Offset Voltage Adjustment........................................................ 14

Settling Time............................................................................... 14

DAC Output Amplifier.............................................................. 15

Disscusion on Driving ADCs ................................................... 16

Outline Dimensions ....................................................................... 18

Ordering Guide .......................................................................... 19

9/01—Rev. D to Rev. E

E

dits to Features and Pin Connections ..........................................1

Edits to Electrical Characteristics .............................................. 2, 3

Edits to Absolute Maximum Ratings, Package Type, and

Ordering Guide..................................................................................4

Deleted Wafer Test Limits and Dice Characteristics Section ......5

Edits to Typical Performance Characteristics................................8

Edits to Macro-Model Figure........................................................ 15

Edits to Outline Dimensions......................................................... 17

Rev. F | Page 2 of 20

OP249

www.BDTIC.com/ADI

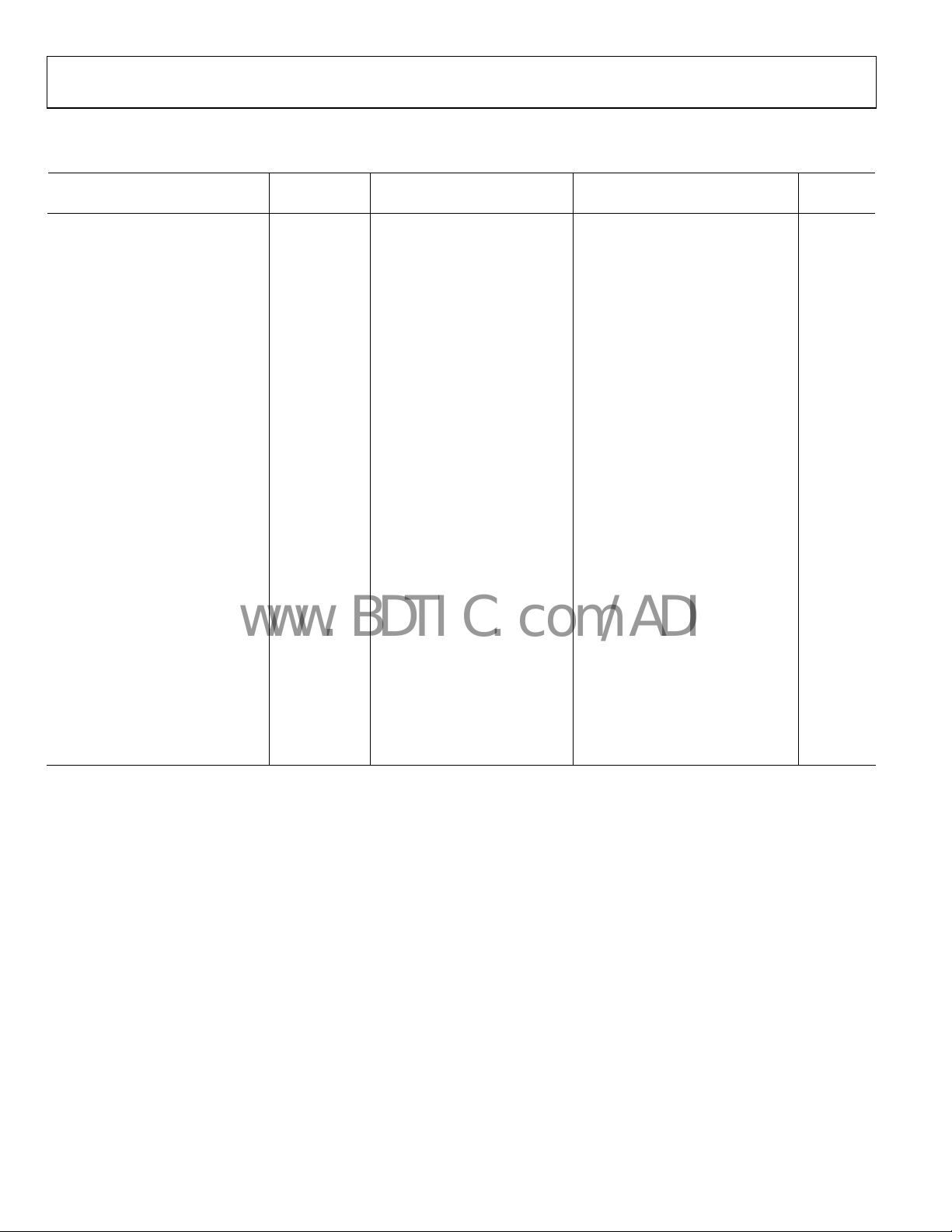

SPECIFICATIONS

ELECTRICAL CHARACTERISTICS

VS = ±15 V, TA = 25°C, unless otherwise noted.

Table 1.

OP249A OP249F

Parameter Symbol Conditions

Min Typ Max Min Typ Max

Offset Voltage VOS 0.2 0.5 0.2 0.7 mV

Long Term Offset Voltage

1

VOS 0.8 1.0 mV

Offset Stability 1.5 1.5 µV/month

Input Bias Current IB VCM = 0 V, TA = 25°C 30 75 30 75 pA

Input Offset Current IOS VCM = 0 V, TA = 25°C 6 25 6 25 pA

Input Voltage Range

2

IVR 12.5 12.5 V

±11 ±11 V

−12.5 –12.5 V

Common-Mode Rejection CMR VCM = ±11 V 80 90 80 90 dB

Power-Supply Rejection Ratio PSRR VS = ± 4.5 V to ±18 V 12 31.6 12 50 µV/V

Large Signal Voltage Gain AVO VO = ±10 V, RL = 2 kΩ 1000 1400 500 1200 V/mV

Output Voltage Swing VO RL = 2 kΩ 12.5 12.5 V

±12.0 ±12.0 V

−12.5 –12.5 V

Short-Circuit Current Limit ISC

Output shorted to

ound

gr

36 36 mA

±20 ±50 ±20 ±50 mA

−33 –33 mA

Supply Current ISY No load, VO = 0 V 5.6 7.0 5.6 7.0 mA

Slew Rate SR RL = 2 kΩ, CL = 50 pF 18 22 18 22 V/µs

Gain Bandwidth Product

Settling Time tS 10 V step 0.01%

Phase Margin Θ

3

GBW 3.5 4.7 3.5 4.7 MHz

4

M

0 dB gain 55 55 Degrees

0.9 1.2 0.9 1.2 µs

Differential Input Impedance ZIN 1012||6 1012||6 Ω||pF

Open-Loop Output Resistance RO 35 35 Ω

Voltage Noise en p-p 0.1 Hz to 10 Hz 2 2 µV p-p

Voltage Noise Density en fO = 10 Hz 75 75 nV/√Hz

f

f

f

= 100 Hz 26 26 nV/√Hz

O

= 1 kHz 17 17 nV/√Hz

O

= 10 kHz 16 16 nV/√Hz

O

Current Noise Density in fO = 1 kHz 0.003 0.003 pA/√Hz

Voltage Supply Range VS ±4.5 ±15 ±18 ±4.5 ±15 ±18 V

1

Long-term offset voltage is guaranteed by a 1000 hour life test performed on three independent wafer lots at 125°C with LTPD of three.

2

Guaranteed by CMR test.

3

Guaranteed by design.

4

Settling time is sample tested.

Unit

Rev. F | Page 3 of 20

OP249

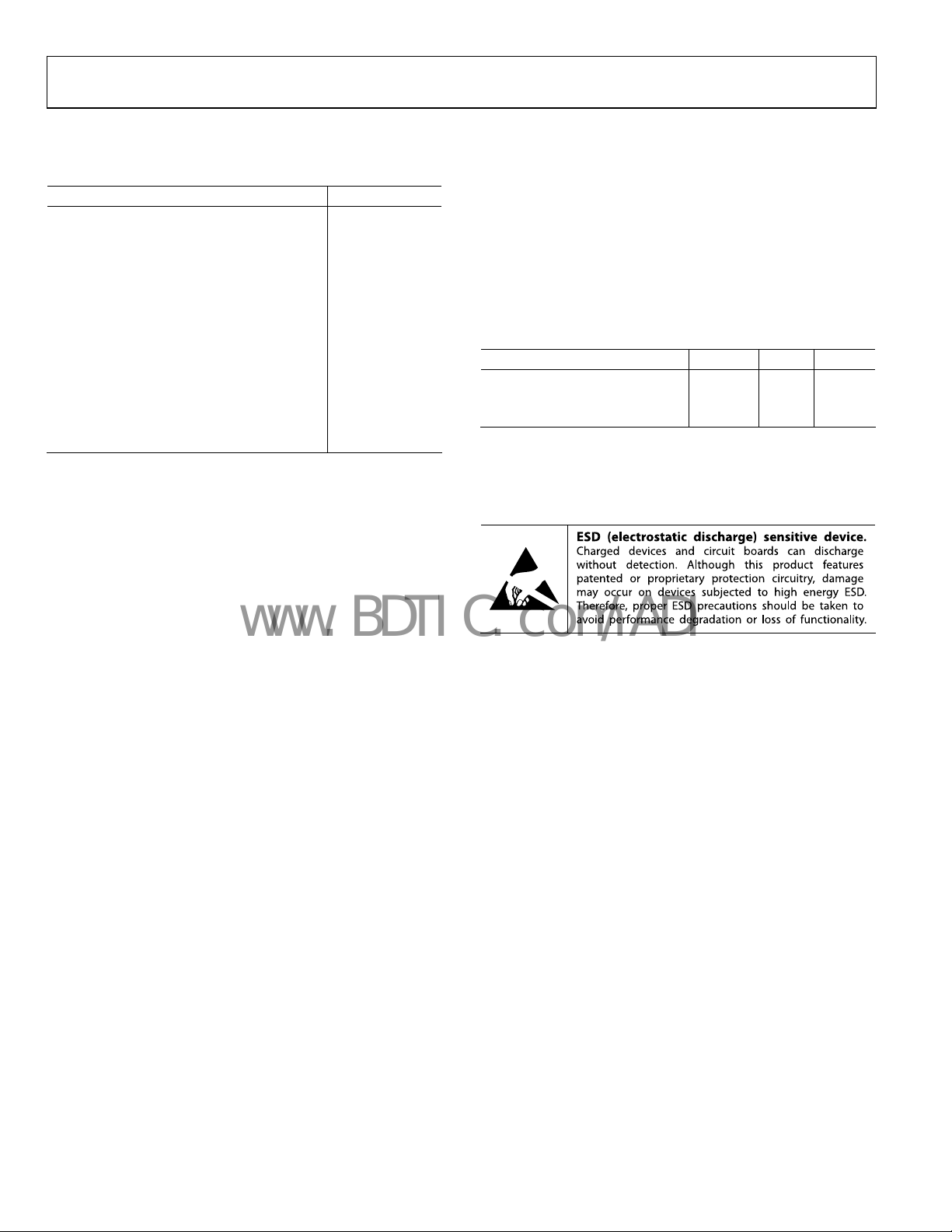

www.BDTIC.com/ADI

VS = ±15 V, TA = 25°C, unless otherwise noted.

Table 2.

OP249G

Parameter Symbol Conditions

Min Typ Max

Offset Voltage VOS 0.4 2.0 mV

Input Bias Current IB VCM = 0 V, TA = 25°C 40 75 pA

Input Offset Current IOS VCM = 0 V TA = 25°C 10 25 pA

Input Voltage Range

1

IVR 12.5 V

±11 V

−12.0 V

Common-Mode Rejection CMR VCM = ±11 V 76 90 dB

Power Supply Rejection Ratio PSRR VS = ±4.5 V to ±18 V 12 50 µV/V

Large Signal Voltage Gain AVO VO = ±10 V; RL = 2 kΩ 500 1100 V/mV

Output Voltage Swing VO RL = 2 kΩ 12.5 V

±12.0 V

−12.5 V

Short-Circuit Current Limit ISC Output shorted to ground 36 mA

±20 ±50 mA

−33 mA

Supply Current ISY No load; VO = 0 V 5.6 7.0 mA

Slew Rate SR RL = 2 kΩ, CL = 50 pF 18 22 V/µs

Gain Bandwidth Product

2

GBW 4.7 MHz

Settling Time tS 10 V step 0.01% 0.9 1.2 µs

Phase Margin Θ

M

0 dB gain 55 Degree

Differential Input Impedance ZIN 1012||6 Ω||pF

Open-Loop Output Resistance RO 35 Ω

Voltage Noise en p-p 0.1 Hz to 10 Hz 2 V p-p

Voltage Noise Density en fO = 10 Hz 75 nV/√Hz

f

f

f

= 100 Hz 26 nV/√Hz

O

= 1 kHz 17 nV/√Hz

O

= 10 kHz 16 nV/√Hz

O

Current Noise Density in fO = 1 kHz 0.003 pA/√Hz

Voltage Supply Range VS ±4.5 ±15 ±18 V

1

Guaranteed by CMR test.

2

Guaranteed by design.

Unit

Rev. F | Page 4 of 20

OP249

www.BDTIC.com/ADI

VS = ±15 V, −40°C ≤ TA ≤ +85°C for F grade and −55°C ≤ TA ≤ +125°C for A grade, unless otherwise noted.

Table 3.

OP249A OP249F

Parameter Symbol Conditions

Offset Voltage VOS 0.12 1.0 0.5 1.1 mV

Offset Voltage Temperature Coefficient TCVOS 1 5 2.2 6 V/°C

Input Bias Current

Input Offset Current

Input Voltage Range

1

1

2

IB 4 20 0.3 4.0 nA

IOS 0.04 4 0.02 1.2 nA

IVR 12.5 12.5 V

±11 ±11 V

−12.5 −12.5 V

Common-Mode Rejection CMR VCM = ±11 V 76 110 80 90 dB

Power Supply Rejection Ratio PSRR VS = ±4.5 V to ±18 V 5 50 7 100 V/V

Large Signal Voltage Gain AVO RL = 2 kΩ; VO = ±10 V 500 1400 250 1200 V/mV

Output Voltage Swing VO RL = 2 kΩ 12.5 12.5 V

±12 ±12 V

−12.5 −12.5 V

Supply Current ISY No load, VO = 0 V 5.6 7.0 5.6 7.0 mA

1

TA = 85°C for F grade; TA = 125°C for A grade.

2

Guaranteed by CMR test.

V

= ±15 V, −40°C ≤ TA ≤ +85°C, unless otherwise noted.

S

Min Typ Max Min Typ Max

Unit

Table 4.

OP249G

Parameter Symbol Conditions

Min Typ Max

Unit

Offset Voltage VOS 1.0 3.6 mV

Offset Voltage Temperature Coefficient TCV

Input Bias Current

Input Offset Current

Input Voltage Range

1

1

2

IB 0.5 4.5 nA

IOS 0.04 1.5 nA

IVR 12.5 V

OS

6 25 µV/°C

±11 V

−12.5 V

Common-Mode Rejection CMR VCM = ±11 V 76 95 dB

Power Supply Rejection Ratio PSRR VS = ±4.5 V to ±18 V 10 100 µV/V

Large Signal Voltage Gain AVO RL = 2 kΩ; VO = ±10 V 250 1200 V/mV

Output Voltage Swing VO RL = 2 kΩ 12.5 V

±12.0 V

−12.5 V

Supply Current ISY No load, VO = 0 V 5.6 7.0 mA

1

TA = 85°C.

2

Guaranteed by CMR test.

Rev. F | Page 5 of 20

OP249

www.BDTIC.com/ADI

ABSOLUTE MAXIMUM RATINGS

Table 5.

Parameter

Supply Voltage ±18 V

Input Voltage

Differential Input Voltage

Output Short-Circuit Duration Indefinite

Storage Temperature Range −65°C to +175°C

Operating Temperature Range

OP249A (Q) −55°C to +125°C

OP249F (Q) −40°C to +85°C

OP249G (N, R) −40°C to +85°C

Junction Temperature Range

OP249A (Q), OP249F (Q) −65°C to +175°C

OP249G (N, R) −65°C to +150°C

Lead Temperature (Soldering, 60 sec) 300°C

1

Absolute maximum ratings apply to packaged parts, unless otherwise noted.

2

For supply voltages less than ±18 V, the absolute maximum input voltage is

equal to the supply voltage.

1

2

2

Rating

±18 V

36 V

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

Table 6. Thermal Resistance

Package Type θ

8-Lead CERDIP (Q) 134 12 °C/W

8-Lead PDIP (N) 96 37 °C/W

8-Lead SOIC (R) 150 41 °C/W

1

θJA is specified for worst-case mounting conditions, that is, θJA is specified for

device in socket for CERDIP and PDIP packages; θJA is specified for device

soldered to printed circuit board for SOIC package.

1

JA

θ

JC

Unit

ESD CAUTION

Rev. F | Page 6 of 20

Loading...

Loading...