Dual, Low Noise, Low Offset

a

Instrumentation Operational Amplifier

FEATURES

Excellent Individual Amplifier Parameters

Low VOS, 80 V Max

Offset Voltage Match, 80 V Max

Offset Voltage Match vs. Temperature, 1 V/ⴗC Max

Stable V

vs. Time, 1 V/MO Max

OS

Low Voltage Noise, 3.9 nV/÷Hz Max

Fast, 2.8 V/s Typ

High Gain, 1.8 Million Typ

High Channel Separation, 154 dB Typ

GENERAL DESCRIPTION

The OP227 is the first dual amplifier to offer a combination of

low offset, low noise, high speed, and guaranteed amplifier matching

characteristics in one device. The OP227, with a VOS match of

25 mV typical, a TCVOS match of 0.3 mV/∞C typical and a 1/f corner

of only 2.7 Hz is an excellent choice for precision low noise designs.

These dc characteristics, coupled with a slew rate

typical and a small-signal bandwidth of 8 MHz typical,

of 2.8 V/ms

allow the

designer to achieve ac performance previously unattainable with

op amp based instrumentation designs.

When used in a three op amp instrumentation configuration, the

OP227 can achieve a CMRR in excess of 100 dB at 10 kHz. In

addition, this device has an open-loop gain of 1.5 M typical with

a 1 kW load. The OP227 also features an I

of ± 10 nA typical,

B

an IOS of 7 nA typical, and guaranteed matching of input currents

between amplifiers. These outstanding input current specifications

are realized through the use of a unique input current cancellation

circuit which typically holds IB and IOS to ± 20 nA and 15 nA

respectively over the full military temperature range.

Other sources of input referred errors, such as PSRR and CMRR,

are reduced by factors in excess of 120 dB for the individual

amplifiers. DC stability is assured by a long-term drift application

of 1.0 mV/month.

Matching between channels is provided on all critical parameters including offset voltage, tracking of offset voltage versus

temperature, noninverting bias current, CMRR, and power

supply rejection ratio. This unique dual amplifier allows the

elimination of external components for offset nulling and

frequency compensation.

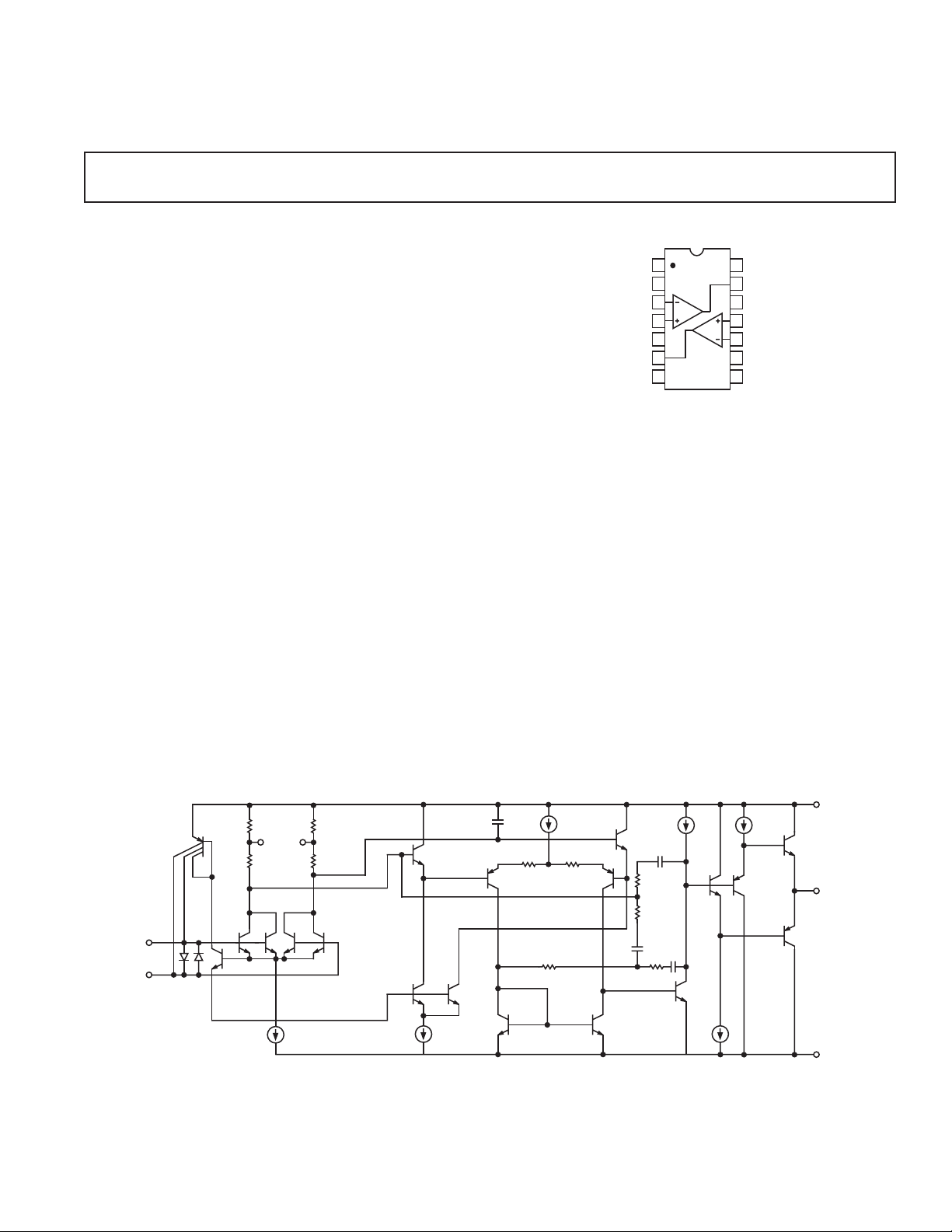

PIN CONNECTIONS

–IN (A)

+IN (A)

V– (B)

OUT (B)

V+ (B)

1

2

3

A

4

5

6

7

NULL (A)

NULL (A)

NOTE

DEVICE MAY BE OPERATED EVEN IF INSERTION

1.

IS REVERSED; THIS IS DUE TO INHERENT SYMMETRY

OF PIN LOCATIONS OF AMPLIFIERS A AND B

V–(A) AND V–(B) ARE INTERNALLY CONNECTED VIA

2.

SUBSTRATE RESISTANCE

14

V+ (A)

13

OUT (A)

12

V– (A)

11

+IN (B)

B

10

–IN (B)

9

NULL (B)

8

NULL (B)

OP227

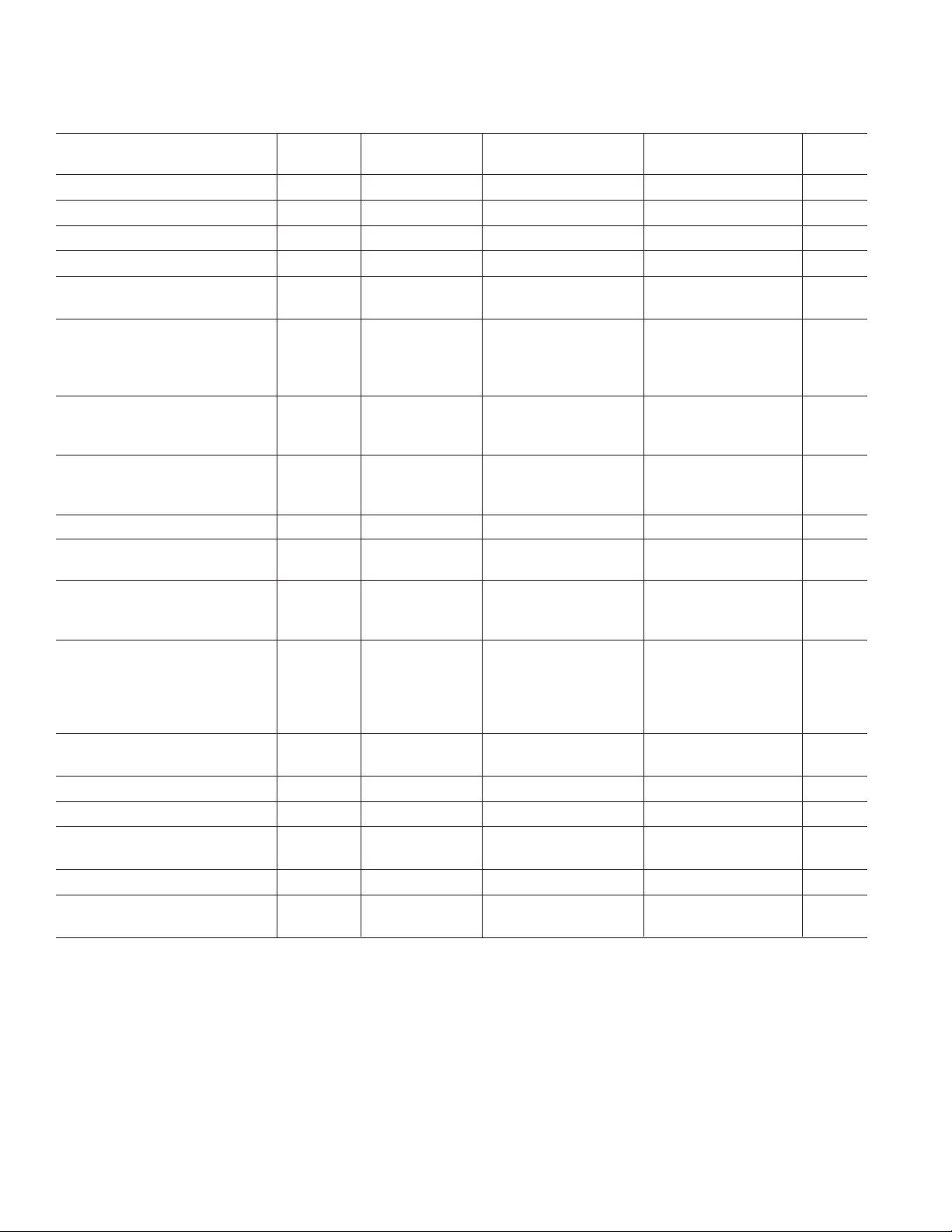

SIMPLIFIED SCHEMATIC

NON

INVERTING

INPUT (+)

INVERTING

INPUT (–)

Q6

Q3

*

R1 AND R2 ARE PREMATURELY ADJUSTED AT WAFER TEST FOR MINIMUM OFFSET VOLTAGE.

R3

NULL

*

R1

Q1A Q1B Q2B Q2A

R4

R2

*

Q21

Q11 Q12

REV. A

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

V+

C2

Q22

R23 R24

Q23 Q24

R5

Q27

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2002

Q28

C1

R9

R12

C3

R11

Q20 Q19

C4

Q26

Q46

OUTPUT

Q45

V-

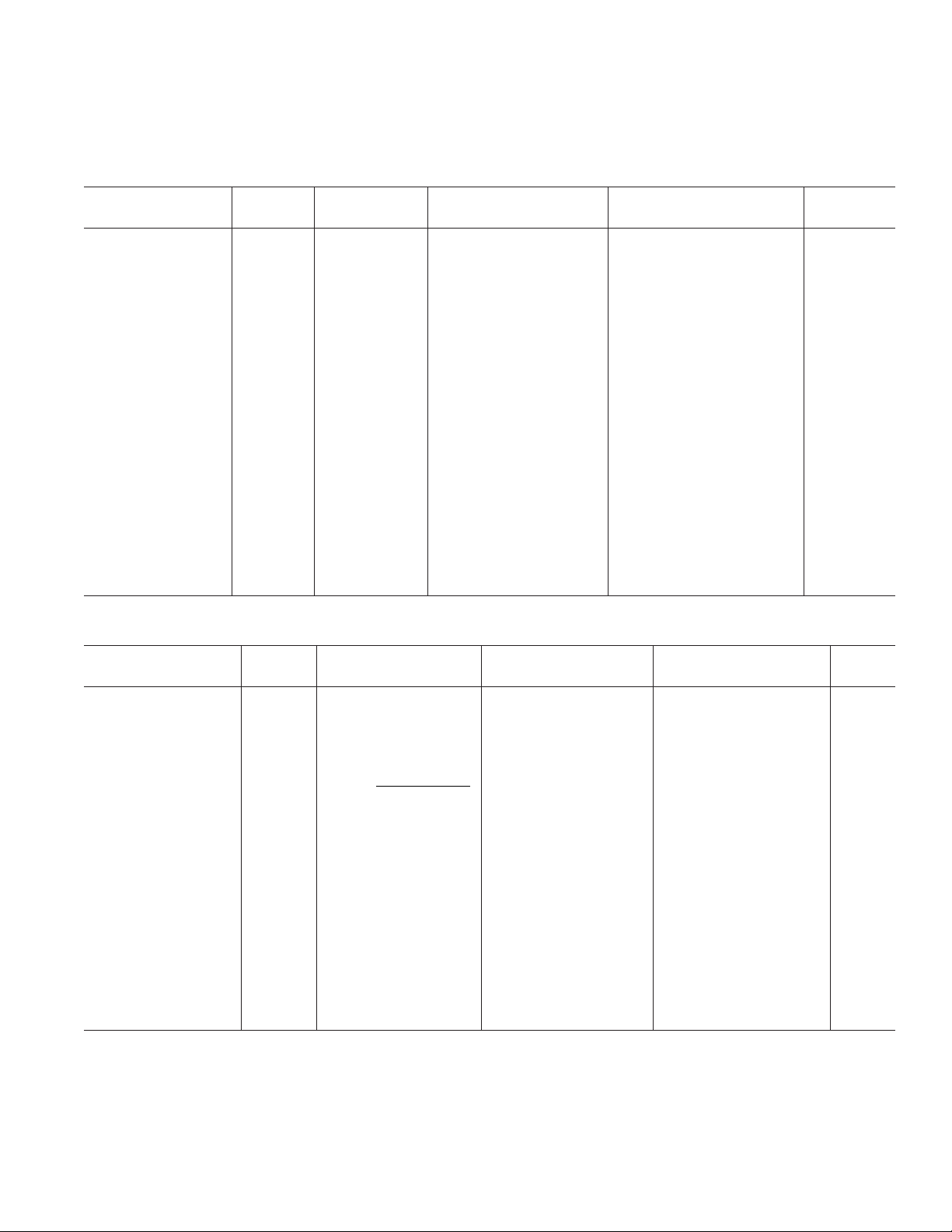

OP227–SPECIFICATIONS

Individual Amplifier Characteristics

(VS = ⴞ15 V, TA = 25ⴗC, unless otherwise noted.)

OP227E OP227G

Parameter Symbol Conditions Min Typ Max Min Typ Max Unit

INPUT OFFSET VOLTAGE V

OS

LONG-TERM VOS STABILITY VOS/Time Notes 2,4 0.2 1.0 0.4 2.0 mV/M

INPUT OFFSET CURRENT I

INPUT BIAS CURRENT I

INPUT NOISE VOLTAGE e

OS

B

n p-p

Note 1 20 80 60 180 mV

O

735 1275nA

± 10 ± 40 ± 15 ± 80 nA

0.1 Hz to 10 Hz 0.08 0.20 0.09 0.28 mV p-p

Notes 3,5

INPUT NOISE VOLTAGE

DENSITY e

INPUT NOISE DENSITY i

n

fO = 10 Hz

f

= 30 Hz

O

fO = 1000 Hz

n

fO = 10 Hz

= 30 Hz

f

O

fO = 1000 Hz

3

3

3, 6

3, 6

3

3, 6

3.5 6.0 3.8 9.0 nV/Hz

3.1 4.7 3.3 5.9 nV/Hz

3.0 3.9 3.2 4.6 nV/Hz

1.7 4.5 1.7 pA/Hz

1.0 2.5 1.0 pA/Hz

0.4 0.7 0.4 0.7 pA/Hz

INPUT RESISTANCE

Differential Mode R

Common Mode R

IN

INCM

Note 7 1.3 6 0.7 4 MW

32GW

INPUT VOLTAGE RANGE IVR ± 11.0 ± 12.3 ± 11.0 ± 12.3 V

COMMON-MODE

REJECTION RATIO CMRR VCM = ± 11 V 114 126 100 120 dB

POWER SUPPLY

REJECTION RATIO PSRR VS = ± 4 V to

± 18 V 1 10 2 20 mV/V

LARGE-SIGNAL

VOLTAGE GAIN A

VO

RL ⱖ 2 kW,

V

= ± 10 V 1000 1800 700 1500 V/mV

O

ⱖ 600 kW,

R

L

VO = ± 10 V 800 1500 600 1500 V/mV

OUTPUT VOLTAGE SWING V

O

RL ⱖ 2 kW±12.0 ± 13.8 ± 11.5 ± 13.5 V

RL ⱖ 600 W±10.0 ± 11.5 ± 10.0 ± 11.5 V

SLEW RATE SR RL ⱖ 2 kW

4

1.7 2.8 1.7 2.8 V/ms

GAIN BANDWIDTH PROD. GBW Note 4 5 8 5 8 MHz

OPEN-LOOP OUTPUT

RESISTANCE R

POWER CONSUMPTION P

O

d

VO = 0, IO = 0 70 70 W

Each Amplifier 90 140 100 170 mW

OFFSET ADJUSTMENT

RANGE Rp = 10 kW±4 ± 4mV

NOTES

1

Input offset voltage measurements are performed by automated test equipment approximately 0.5 seconds after application of power. E Grade specifications are

guaranteed fully warmed up.

2

Long term input offset voltage stability refers to the average trend line of VOS vs. time over extended periods after the first 30 days of operation. Excluding the initial

hour of operation, changes in VOS during the first 30 days are typically 2.5 mV. Refer to the Typical Performance Curve.

3

Sample tested.

4

Parameter is guaranteed by design.

5

See test circuit and frequency response curve for 0.1 Hz to 10 Hz tester.

6

See test circuit for current noise measurement.

7

Guaranteed by input bias current.

Specifications subject to change without notice.

–2–

REV. A

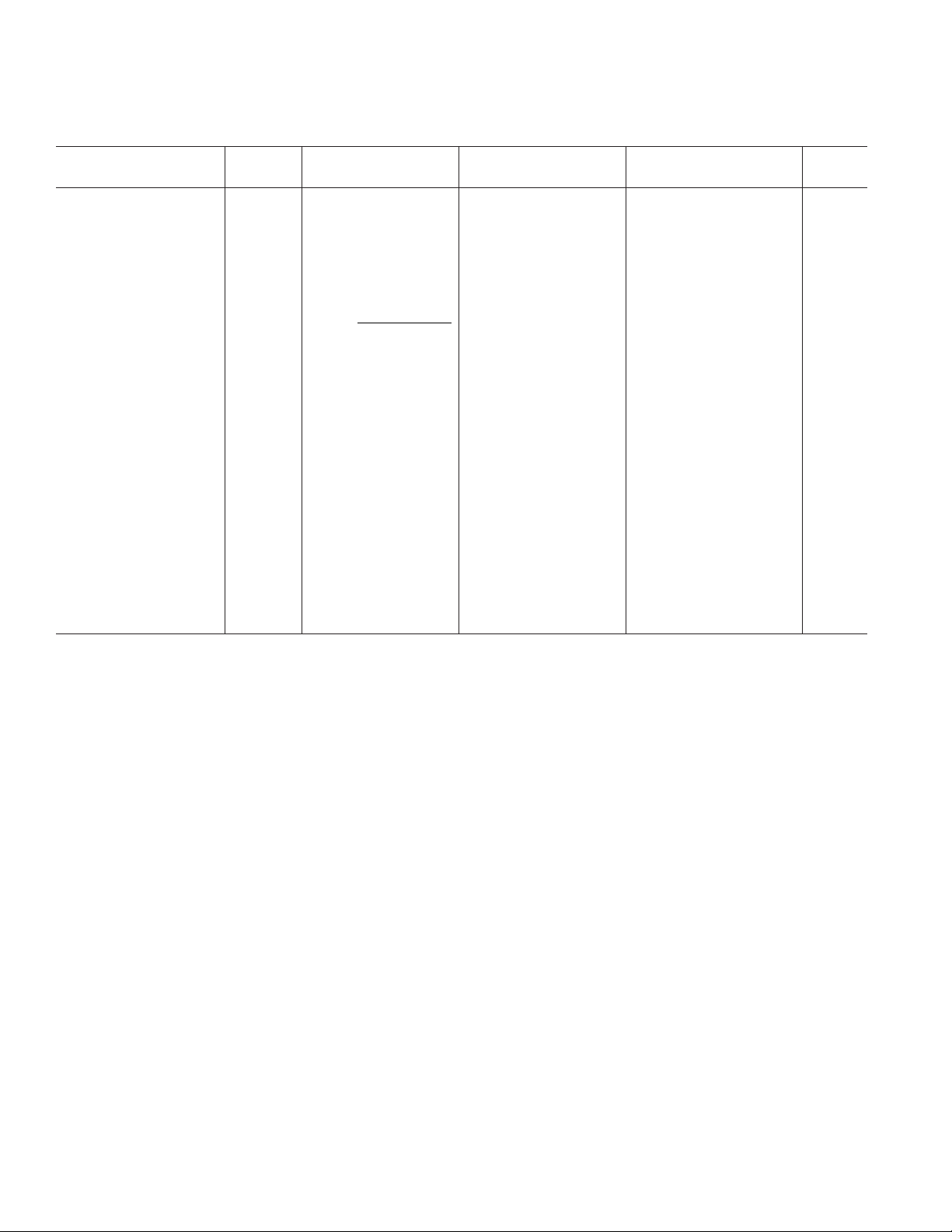

SPECIFICATIONS

OP227

Individual Amplifier Characteristics

(VS = ⴞ15 V, –25ⴗC £ TA £ +85ⴗC, unless otherwise noted.)

OP227E OP227G

Parameter Symbol Conditions Min Typ Max Min Typ Max Unit

INPUT OFFSET

VOLTAGE V

OS

Note 1 40 140 85 280 mV

AVERAGE INPUT

OFFSET DRIFT TCV

TCV

OS

OSn

Note 2 0.5 1.0 0.5 1.8 mV/ⴗC

INPUT OFFSET

CURRENT I

OS

10 50 20 135 nA

INPUT BIAS

CURRENT I

B

± 14 ± 60 ± 25 ± 150 nA

INPUT VOLTAGE

RANGE IVR ± 10 ± 11.8 ± 10 ± 11.8 V

COMMON-MODE

REJECTION RATIO CMRR V

= ± 10 V 110 124 96 118 dB

CM

POWER SUPPLY

REJECTION RATIO PSRR V

= ± 4.5 V to

S

± 18 V 2 15 2 32 mV/V

LARGE-SIGNAL

VOLTAGE GAIN A

VO

RL ⱖ 2 kW,

V

= ± 10 V 750 1500 450 1000 V/mV

O

OUTPUT VOLTAGE

SWING V

O

RL ⱖ 2 kW±11.7 ± 13.6 ± 11.0 ± 13.3 V

Matching Characteristics

(VS = ± 15 V, TA = 25ⴗC, unless otherwise noted.)

OP227E OP227G

Parameter Symbol Conditions Min Typ Max Min Typ Max Unit

INPUT OFFSET

VOLTAGE MATCH ⌬V

OS

25 80 55 300 mV

AVERAGE

NONINVERTING Bias

CURRENT I

+

B

II

I

+=

B

++ +

BA BB

2

± 10 ± 40 ± 15 ± 90 nA

NONINVERTING

OFFSET CURRENT IOS+I

+ = IB+A-I

OS

B+B

± 12 ± 60 ± 20 ± 130 nA

INVERTING OFFSET

CURRENT I

-I

OS

- = IB-A-IB-

OS

B

± 12 ± 60 ± 20 ± 130 nA

COMMON-MODE

REJECTION RATIO

MATCH ⌬CMRR V

= ± 11 V 110 123 97 117 dB

CM

POWER SUPPLY

REJECTION RATIO

MATCH ⌬PSRR V

= ± 4 V to

S

± 18 V 2 10 2 20 mV/V

CHANNEL

SEPARATION CS Note 1 126 154 126 154 dB

NOTES

1

Input Offset Voltage measurements are performed by automated equipment approximately 0.5 seconds after application of power.

2

The TCVOS performance is within the specifications unnulled or when nulled with RP = 8 kW to 20 kW, optimum performance is obtained with RP = 8 kW.

3

Sample tested.

Specifications subject to change without notice.

REV. A

–3–

OP227–SPECIFICATIONS

Matching Characteristics

(VS = ⴞ15 V, TA = -25ⴗC to +85ⴗC, unless otherwise noted.)

OP227E OP227G

Parameter Symbol Conditions Min Typ Max Min Typ Max Unit

INPUT OFFSET

VOLTAGE MATCH ⌬V

OS

40 140 90 400 mV

INPUT OFFSET

TRACKING TC⌬V

Nulled or Unnulled* 0.3 1.0 0.5 1.8 mV/ⴗC

OS

AVERAGE

NONINVERTING

BIAS CURRENT I

+

B

II

I

+=

B

++ +

BA BB

2

± 14 ± 60 ± 25 ± 170 nA

AVERAGE DRIFT OF

NONINVERTING BIAS

CURRENT TCI

+80180 pA/ⴗC

B

NONINVERTING

OFFSET CURRENT I

+I

OS

+ = IB+A–IB+

OS

B

± 20 ± 90 ± 35 ± 250 nA

AVERAGE DRIFT OF

NONINVERTING

OFFSET CURRENT TCI

+ 130 250 pA/ⴗC

OS

INVERTING OFFSET

CURRENT I

–I

OS

– = IB–A–IB–

OS

B

± 20 ± 90 ± 35 ± 250 nA

COMMON-MODE

REJECTION RATIO

MATCH ⌬CMRR V

= ± 10 V 106 120 90 112 dB

CM

POWER SUPPLY

REJECTION RATIO

MATCH ⌬PSRR V

= ± 4.5 V to ± 18 V 2 15 3 32 mV/V

S

NOTES

*Sample tested.

Specifications subject to change without notice.

–4–

REV. A

OP227

WARNING!

ESD SENSITIVE DEVICE

ABSOLUTE MAXIMUM RATINGS

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±22 V

Input Voltage

Output Short-Circuit Duration . . . . . . . . . . . . . . . . . Indefinite

Differential Input Voltage

Differential Input Current

1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2

. . . . . . . . . . . . . . . . . . . . . . . ±0.7 V

2

. . . . . . . . . . . . . . . . . . . . . ±25 mA

±22 V

Storage Temperature Range . . . . . . . . . . . . . –65∞C to +150∞C

Operating Temperature Range

OP227E, OP227G . . . . . . . . . . . . . . . . . . . . –25∞C to +85∞C

Lead Temperature (Soldering 60 sec) . . . . . . . . . . . . . . 300∞C

NOTES

1

For supply voltages less than ±22 V, the absolute maximum input voltage is equal

to the supply voltage.

2

The OP227 inputs are protected by back-to-back diodes. Current limiting resistors

are not used in order to achieve low noise. If differential input voltage exceeds ±0.7

V, the input current should be limited to 25 mA.

3

is specified for worst-case mounting conditions, i.e.,

JA

in socket for CERDIP package.

is specified for device

JA

THERMAL CHARACTERISTICS

Thermal Resistance

14-Lead CERDIP

3

= 106∞C/W

JA

= 16∞C/W

JC

ORDERING GUIDE

TA = 25ⴗCHermetic Operating

VOS MAX (V) DIP 14-Lead Temperature Range

80 OP227EY IND

180 OP227GY IND

For military processed devices, please refer to the Standard

Microcircuit Drawing (SMD) available at

www.dscc.dla.mil/programs/milspec/default.asp.

SMD Part Number ADI Equivalent

5962-8688701CA

*Not recommended for new design, obsolete April 2002.

*

OP227AYMDA

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although

the OP227 features propriety ESD protection circuitry, permanent damage may occur on devices

subjected to high energy electrostatic discharges. Therefor, proper ESD precautions are

recommended to avoid performance degradation or loss of functionality.

REV. A

–5–

Loading...

Loading...