Universal

a

FEATURES

Single Chip Solution, Contains Internal Oscillator and

Voltage Reference

No Adjustments Required

Interfaces to Half-Bridge, 4-Wire LVDT

DC Output Proportional to Position

20 Hz to 20 kHz Frequency Range

Unipolar or Bipolar Output

Will Also Decode AC Bridge Signals

Outstanding Performance

Linearity: 0.05%

Output Voltage: 611 V

Gain Drift: 20 ppm/8C (typ)

Offset Drift: 5 ppm/8C (typ)

PRODUCT DESCRIPTION

The AD698 is a complete, monolithic Linear Variable Differential Transformer (LVDT) signal conditioning subsystem. It is

used in conjunction with LVDTs to convert transducer mechanical position to a unipolar or bipolar dc voltage with a high degree of accuracy and repeatability. All circuit functions are

included on the chip. With the addition of a few external passive

components to set frequency and gain, the AD698 converts the

raw LVDT output to a scaled dc signal. The device will operate

with half-bridge LVDTs, LVDTs connected in the series opposed configuration (4-wire), and RVDTs.

The AD698 contains a low distortion sine wave oscillator to

drive the LVDT primary. Two synchronous demodulation

channels of the AD698 are used to detect primary and secondary amplitude. The part divides the output of the secondary by

the amplitude of the primary and multiplies by a scale factor.

This eliminates scale factor errors due to drift in the amplitude

of the primary drive, improving temperature performance and

stability.

The AD698 uses a unique ratiometric architecture to eliminate

several of the disadvantages associated with traditional approaches to LVDT interfacing. The benefits of this new circuit are: no adjustments are necessary; temperature stability is

improved; and transducer interchangeability is improved.

The AD698 is available in two performance grades:

Grade Temperature Range Package

AD698AP –40°C to +85°C 28-Pin PLCC

AD698SQ –55°C to +125°C 24-Pin Cerdip

LVDT Signal Conditioner

AD698

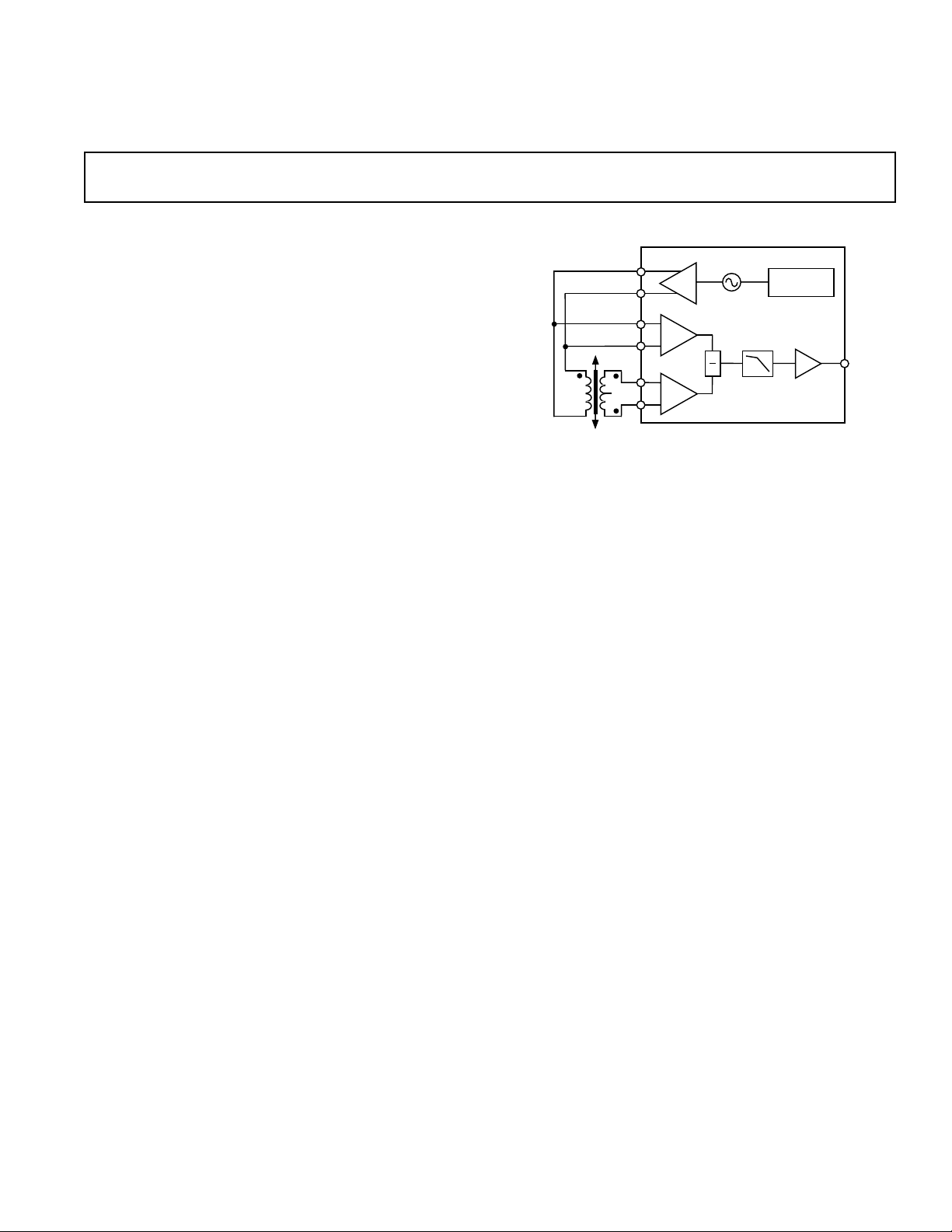

FUNCTIONAL BLOCK DIAGRAM

AD698

FILTER

VOLTAGE

REFERENCE

AMP

AMP

OSCILLATOR

B

A

B

A

PRODUCT HIGHLIGHTS

1. The AD698 offers a single chip solution to LVDT signal

conditioning problems. All active circuits are on the monolithic chip with only passive components required to complete the conversion from mechanical position to dc voltage.

2. The AD698 can be used with many different types of position sensors. The circuit is optimized for use with any

LVDT, including half-bridge and series opposed, (4 wire)

configurations. The AD698 accommodates a wide range of

input and output voltages and frequencies.

3. The 20 Hz to 20 kHz excitation frequency is determined by a

single external capacitor. The AD698 provides up to 24 volts

rms to differentially drive the LVDT primary, and the

AD698 meets its specifications with input levels as low as

100 millivolts rms.

4. Changes in oscillator amplitude with temperature will not affect overall circuit performance. The AD698 computes the

ratio of the secondary voltage to the primary voltage to determine position and direction. No adjustments are required.

5. Multiple LVDTs can be driven by a single AD698 either in

series or parallel as long as power dissipation limits are not

exceeded. The excitation output is thermally protected.

6. The AD698 may be used as a loop integrator in the design of

simple electromechanical servo loops.

7. The sum of the transducer secondary voltages do not need to

be constant.

REV. B

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

© Analog Devices, Inc., 1995

One Technology Way, P.O. Box 9106, Norwood. MA 02062-9106, U.S.A.

Tel: 617/329-4700 Fax: 617/326-8703

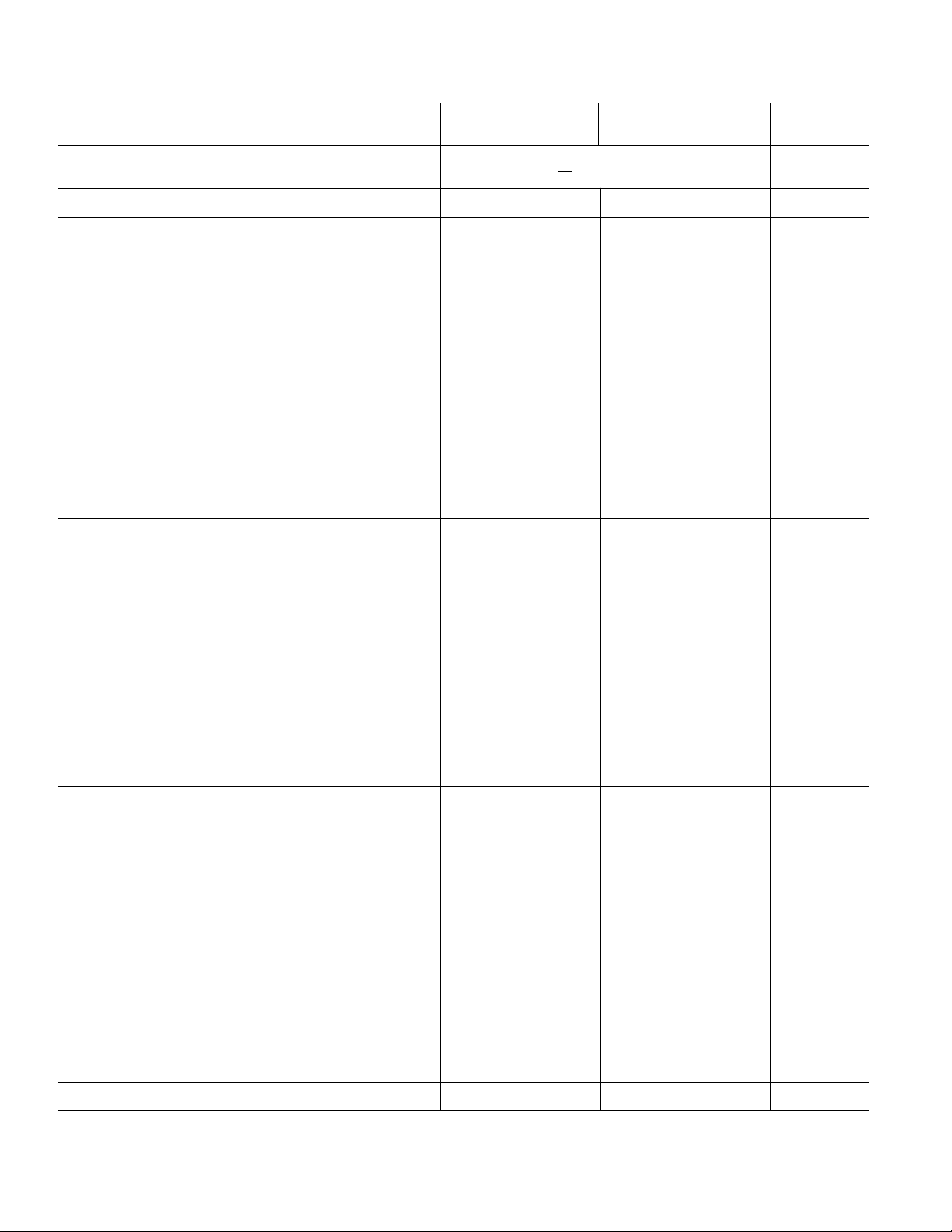

AD698–SPECIFICA TIONS

(@ TA = +258C, VCM = 0 V, and V+, V– = 615 V dc, unless otherwise noted)

AD698SQ AD698AP

Parameter Min Typ Max Min Typ Max Unit

TRANSFER FUNCTION

OVERALL ERROR T

MIN

to T

1

MAX

V

0.4 1.65 0.4 1.65 % of FS

OUT

A

=

× 500 µA × R2

B

V

SIGNAL OUTPUT CHARACTERISTICS

Output Voltage Range 611 611 V

Output Current, T

Short Circuit Current 20 20 mA

Nonlinearity

Gain Error

2

T

3

MIN

MIN

to T

to T

MAX

MAX

11 11 mA

75 6500 75 6500 ppm of FS

0.1 61.0 0.1 61.0 % of FS

Gain Drift 20 6100 20 6100 ppm/°C of FS

Output Offset 0.02 61 0.02 61 % of FS

Offset Drift 5 625 5 625 ppm/°C of FS

Excitation Voltage Rejection

4

100 100 ppm/dB

Power Supply Rejection (±12 V to ±18 V)

PSRR Gain 50 300 50 300 ppm/V

PSRR Offset 15 100 15 100 ppm/V

Common-Mode Rejection (±3 V)

CMRR Gain 25 100 25 100 ppm/V

CMRR Offset 2 100 2 100 ppm/V

Output Ripple

5

4 4 mV rms

EXCITATION OUTPUT CHARACTERISTICS (@ 2.5 kHz)

Excitation Voltage Range 2.1 24 2.1 24 V rms

Excitation Voltage (Resistors Are 1% Absolute Values)

(R1 = Open)

6

1.2 2.15 1.2 2.15 V rms

(R1 = 12.7 kΩ) 2.6 4.35 2.6 4.35 V rms

(R1 = 487 Ω) 14 21.2 14 21.2 V rms

Excitation Voltage TC

7

100 100 ppm/°C

Output Current 30 50 30 50 mA rms

T

MIN

to T

MAX

40 40 mA rms

Short Circuit Current 60 60 mA

DC Offset Voltage (Differential, R1 = 12.7 kΩ)

T

MIN

to T

MAX

30 6100 30 6100 mV

Frequency 20 20 k 20 20 k Hz

Frequency TC 200 200 ppm/°C

Total Harmonic Distortion –50 –50 dB

SIGNAL INPUT CHARACTERISTICS

A/B Ratio Usable Full-Scale Range 0.1 0.9 0.l 0.9

Signal Voltage B Channel 0.1 3.5 0.1 3.5 V rms

Signal Voltage A Channel 0.0 3.5 0.0 3.5 V rms

Input Impedance 200 200 kΩ

Input Bias Current (BIN, AIN) 1 5 1 5 µA

Signal Reference Bias Current 2 10 2 10 µA

Excitation Frequency 0 20 k 0 20 k Hz

POWER SUPPLY REQUIREMENTS

Operating Range 13 36 13 36 V

Dual Supply Operation (±10 V Output) ±13 ±13 V

Single Supply Operation

0 V to +10 V Output 17.5 17.5 V

0 V to 10 V Output 17.5 17.5 V

Current (No Load at Signal and Excitation Outputs) 12 15 12 15 mA

T

MIN

to T

MAX

18 18 mA

OPERATING TEMPERATURE RANGE –55 +125 –40 +85 °C

–2–

REV. B

AD698

13

16

15

14

24

23

22

21

20

19

18

17

TOP VIEW

(Not to Scale)

12

11

10

9

8

1

2

3

4

7

6

5

AD698

–V

S

SIG REF

OFFSET2

OFFSET1

+V

S

EXC1

EXC2

LEV1

OUT FILT

FEEDBACK

SIG OUT

LEV2

FREQ1

FREQ2

BFILT1

BFILT2

–BIN

–ACOMP

AFILT2

AFILT1

+BIN

–AIN

+ACOMP

+AIN

WARNING!

ESD SENSITIVE DEVICE

NOTES

1

A and B represent the Mean Average Deviation (MAD) of the detected sine waves VA and VB. The polarity of V

multiply V

2

Nonlinearity of the AD698 only in units of ppm of full scale. Nonlinearity is defined as the maximum measured deviation of the AD698 output voltage from a

straight line. The straight line is determined by connecting the maximum produced full-scale negative voltage with the maximum produced full-scale positive voltage.

3

See Transfer Function.

4

For example, if the excitation to the primary changes by 1 dB, the gain of the system will change by typically 100 ppm.

5

Output ripple is a function of the AD698 bandwidth determined by C1 and C2. A 1000 pF capacitor should be connected in parallel with R2 to reduce the output

ripple. See Figures 7, 8 and 13.

6

R1 is shown in Figures 7, 8 and 13.

7

Excitation voltage drift is not an important specification because of the ratiometric operation of the AD698.

8

From T

error for the AD698AP from T

(20 ppm/°C × 65°C) + Offset Drift from –40°C to +25°C (5 ppm/ °C × 65 °C) = ±0.36% of full scale. Note that 1000 ppm of full scale equals 0.1% of full scale.

OUT

MIN

× +1 for A

to T

the overall error due to the AD698 alone is determined by combining gain error, gain drift and offset drift. For example, the typical overall

MAX

COMP+

> A

MIN

COMP–

to T

, and V

MAX

× –1 for A

OUT

COMP–

> A

COMP+

.

is calculated as follows: Overall Error = Gain Error at +25°C ( ±0.2% Full Scale) + Gain Drift from –40°C to +25°C

Specifications subject to change without notice.

Specifications shown in boldface are tested on all production units at final electrical test. Results from those tested are used to calculate outgoing quality levels.

All min and max specifications are guaranteed, although only those shown in boldface are tested on all production units.

is affected by the sign of the A comparator, i.e.,

OUT

ABSOLUTE MAXIMUM RATINGS

Total Supply Voltage (+VS to –VS) . . . . . . . . . . . . . . . . . 36 V

Storage Temperature Range

P Package . . . . . . . . . . . . . . . . . . . . . . . . . –65°C to +150°C

Q Package . . . . . . . . . . . . . . . . . . . . . . . . –65°C to +150°C

Operating Temperature Range

AD698SQ . . . . . . . . . . . . . . . . . . . . . . . . –55°C to +125°C

AD698AP . . . . . . . . . . . . . . . . . . . . . . . . . –40°C to +85°C

Lead Temperature Range (Soldering 60 sec) . . . . . . . . +300°C

Power Dissipation Derates above +65°C

P Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 mW/°C

Q Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 mW/°C

THERMAL CHARACTERISTICS

θ

JC

θ

JA

P Package 30°C/W 60°C/W

Q Package 26°C/W 62°C/W

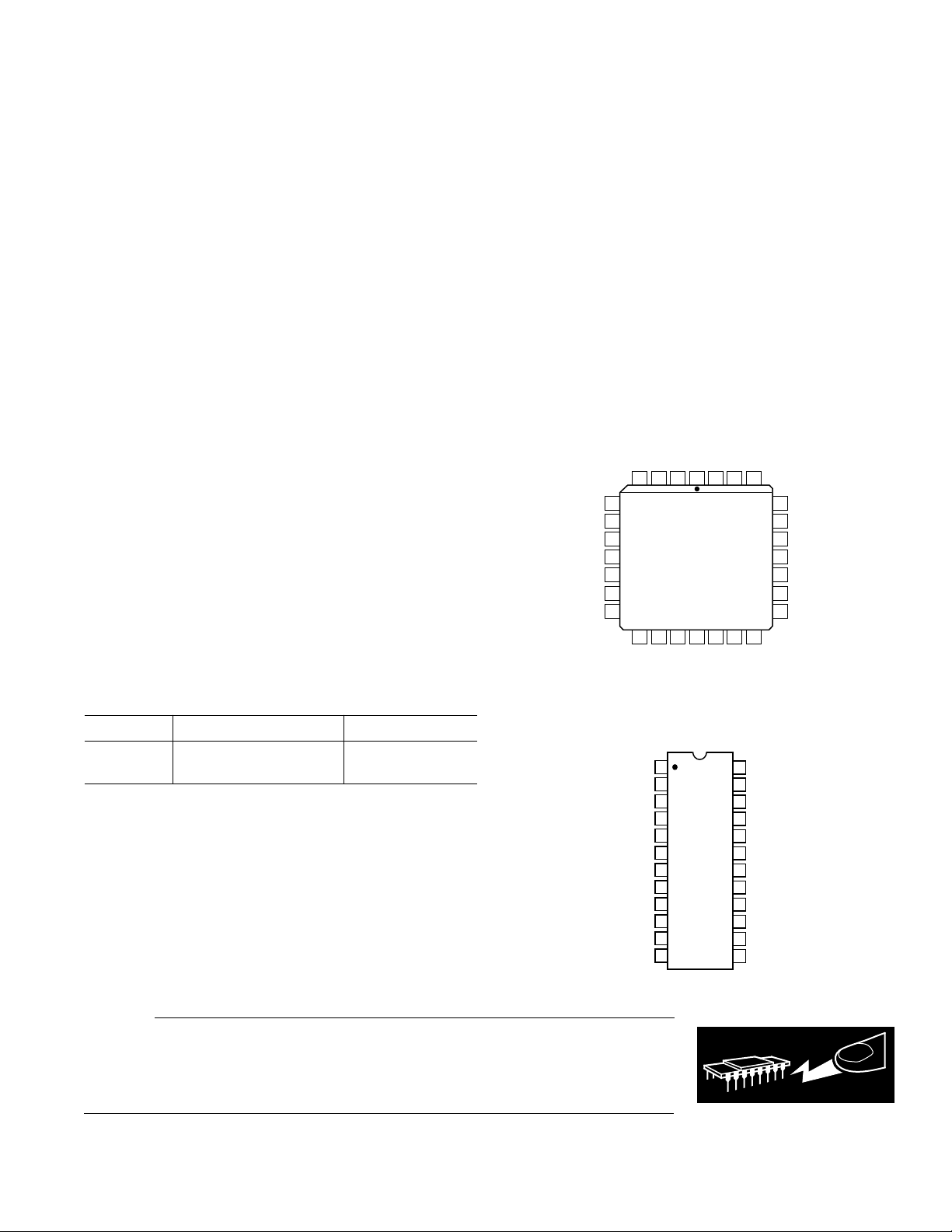

ORDERING GUIDE

Model Package Description Package Option

AD698AP 28-Pin PLCC P-28A

AD698SQ 24-Pin Double Cerdip Q-24A

CONNECTION DIAGRAMS

28-Pin PLCC

S

–V

EXC1

EXC2

AD698

TOP VIEW

(Not to Scale)

–BIN

–AIN

+BIN

28 27 261234

LEV1

5

LEV2

6

FREQ1

7

FREQ2

8

NC

9

BFILT1

10

BFILT2

11

121314 15 16 17 18

NC = NO CONNECT

NC

NC

24-Pin Cerdip

S

OFF1

OFF2

+V

+ACOMP

–ACOMP

+AIN

25

NC

24

SIG REF

23

SIG OUT

22

FEEDBACK

21

OUT FILT

20

AFILT1

19

AFILT2

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD698 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

REV. B

–3–

AD698

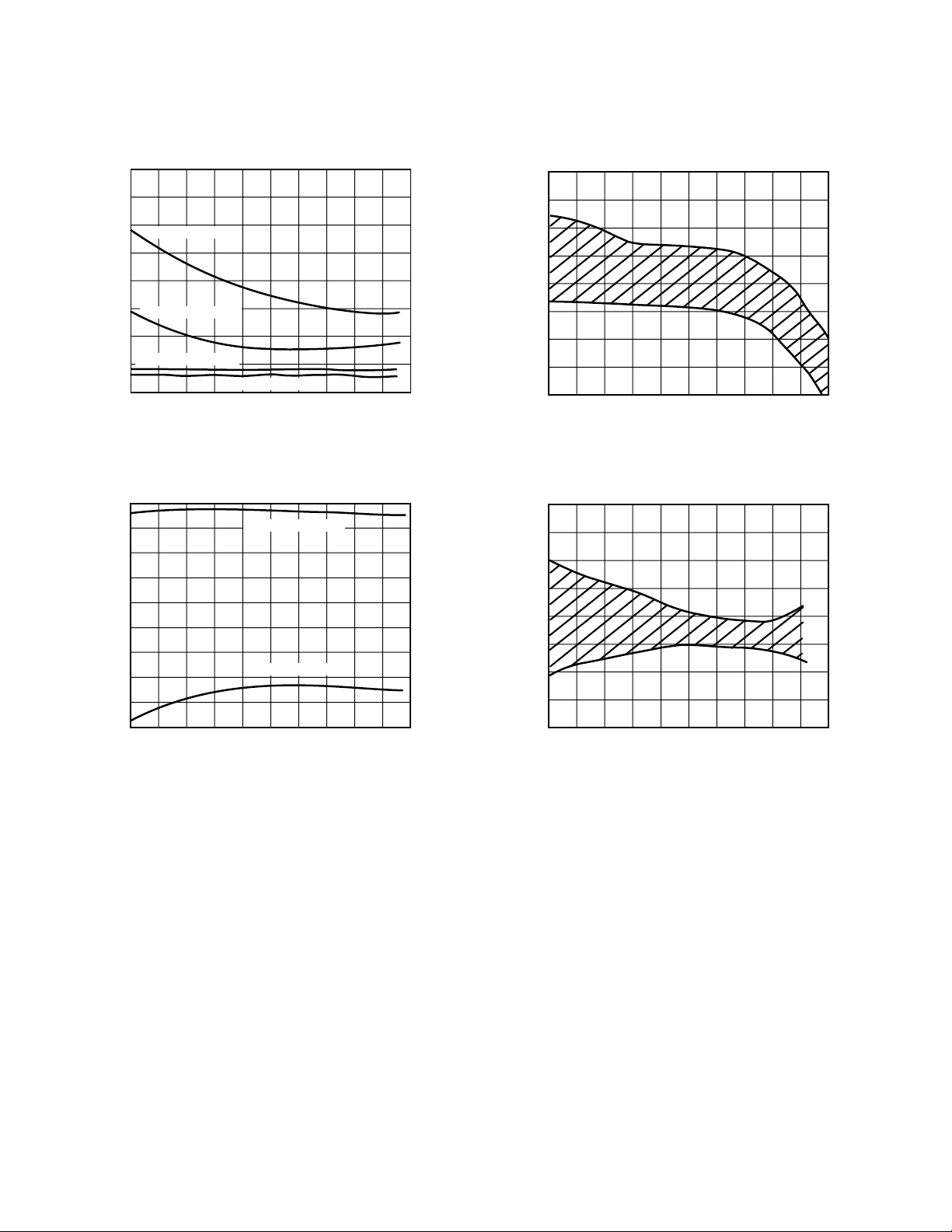

Typical Characteristics

240

200

160

GAIN PSRR 15–18V

120

80

40

GAIN PSRR 12–15V

20

GAIN AND OFFSET PSRR – ppm/V

OFFSET PSRR 12–15V

0

–20

–40–60

OFFSET PSRR 15–18V

TEMPERATURE – °C

(at +25°C and VS = ±15 V unless otherwise noted)

Figure 1. Gain and Offset PSRR vs. Temperature

0

–05

–10

–15

–20

–25

–30

–35

GAIN AND OFFSET CMRR – ppm/V

–40

–45

OFFSET CMRR ± 3V

GAIN CMRR ± 3V

TEMPERATURE – °C

Figure 2. Gain and Offset CMRR vs. Temperature

120

80

40

20

0

–20

–40

TYPICAL GAIN DRIFT – ppm/°C

–60

140

120100806040200–20

–80

–40–60

TEMPERATURE – °C

140

120100806040200–20

Figure 3. Typical Gain Drift vs. Temperature

20

15

10

5

0

–5

–10

TYPICAL OFFSET DRIFT – ppm/°C

–15

140–40–60 120100806040200–20

–20

–40–60

TEMPERATURE – °C

140

120100806040200–20

Figure 4. Typical Offset Drift vs. Temperature

–4–

REV. B

Loading...

Loading...